Page 1

5

4

3

2

1

13"/15"

D D

C C

B B

Home Capacitve button

ENE SB35884

G-Sensor

HP3DC2TR

Keyboard

Touch Pad

TCP-15G24

A A

https://t.me/schematicslaptop

https://t.me/biosarchive

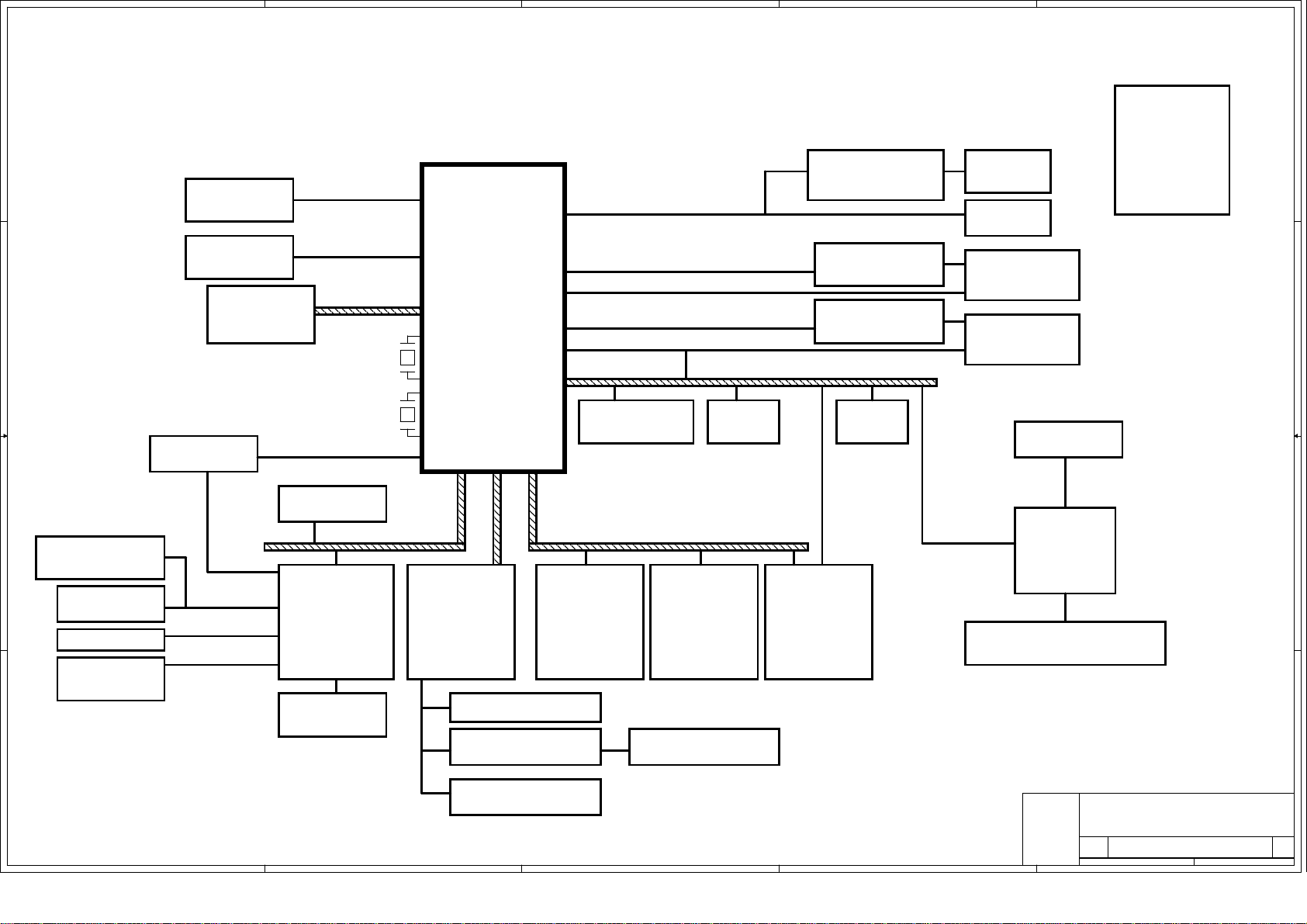

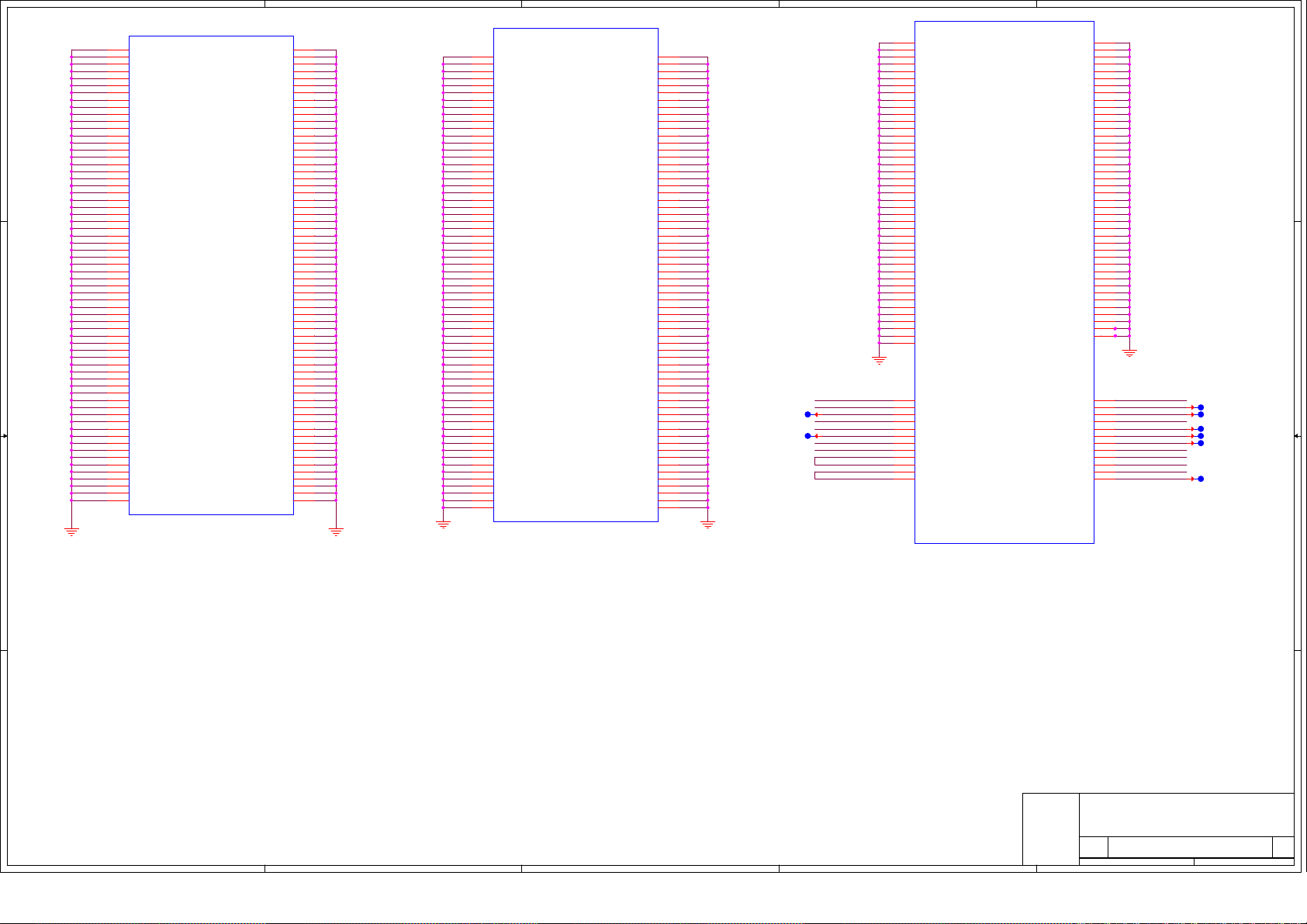

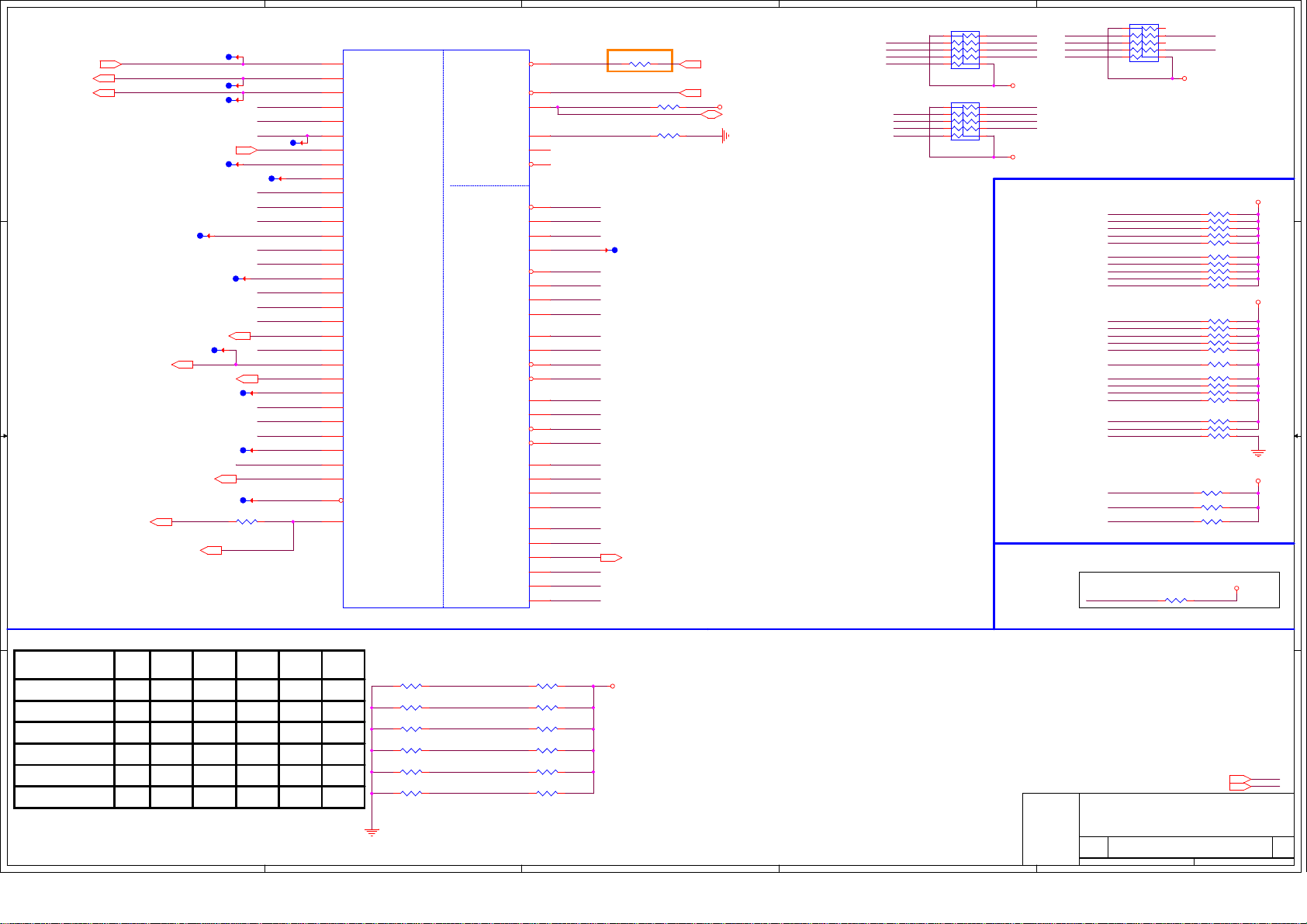

Y61 Intel Cresent Bay ULT Platform Block Diagram

DDR3L SODIMM1

Maxima 8GBs

PAGE 12

DDR3L SODIMM2

Maxima 8GBs

PAGE 13

SATA - 1st HDD

Package : 9.5 (mm)

Power :

System BIOS

SPI ROM

PAGE 23

SM BUS

PAGE 22

PAGE 22

PAGE 22

5

DDR3L x1600MHz 1.35V

DDR3L x1600MHz 1.35V

SATA0 6GB/s Gen3

Port 0

PAGE 21

SPI Interface

TPM

SLB9656 V1.2

ITE 8987

Embedded Controller

Power :

Package : LQPF128

Size : 14 x 14 (mm)

FAN

Crystal

48MHz

Crystal

32MHz

Audio Codec

ALC3227

Power :

Package : MQFN

PAGE 25

PAGE 18

Size : 6 x 6 (mm)

4

Broadwell U

Processor

Processor : Daul Core

Power : 15 (Watt)

Package : BGA1168

Size : 40 X 24 (mm)

USB3.0 Interface

INT

PAGE 17

Speaker

Headphone amplifier

HPA0022642RTJR

Di

PAGE 2~10

Az

alia

PCIE Gen 1 x 1 LaneLPC Interface

Port2 Port3Port4

Carde Reader

RTS5237

Power :

Package : LQPF48

Size : 6 x 6 (mm)

Int

PAGE 17

PAGE 18

gital MIC

PAGE 17

P X2

eD

DP Port 1

USB2.0 Interface

USB2.0 Port x 1(USB board)

Port1

(2A)

PAGE 18

PAGE 26

Combo Jack

iPHONE type

USB 3.0 Port 1,2(USB 2.0 Port 0,5)

Camera

Port2

PAGE 24

LAN Controller

RTL8176EH-CG

Halt Mini Card

WLAN / BT Combo

USB2.0 Port 6

Power :

Package : OFN32

Int

PAGE 28

PAGE 18

3

RTD2136

Package : QFN-32

PS8201A

Package : QFN-40

N36241B*2

PT

Package : QFN-24

Touch Screen

Port3

PAGE 24

PAGE 23

PAGE 14

PAGE 16

PAGE 20

https://t.me/schematicslaptop

https://t.me/biosarchive

2

LVDS (2CH)

PAGE 15

eDP

PAGE 15

HDMI Conn

USB3.0 Port x 2

Accelerometer/Compass/Gryoscope

PAGE 16

(total 2.5A)

PAGE 20

G-Sensor

HP3DC2TR

IT8350

Sensor Hub

Size : 14 x 14 (mm)

Port4

I2C

HP9DS0TR

ICT

PCB 6L STACK UP

LAYER 1 : TOP

LAYER 2 : SGND

LAYER 3 : IN1(High)

LAYER 4 : IN2(Low)

LAYER 5 : SVCC

LAYER 6 : BOT

PAGE 24

SM BUS

PAGE 24

PROJECT :Y61

PROJECT :Y61

PROJECT :Y61

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Si

ze Document Number Rev

Custom

Custom

Custom

Block Diagram

Block Diagram

Block Diagram

Date: Sheet

Date: Sheet

Date: Sheet

1

132Monday, April 21, 2014

132Monday, April 21, 2014

132Monday, April 21, 2014

of

of

of

1A

1A

1A

01

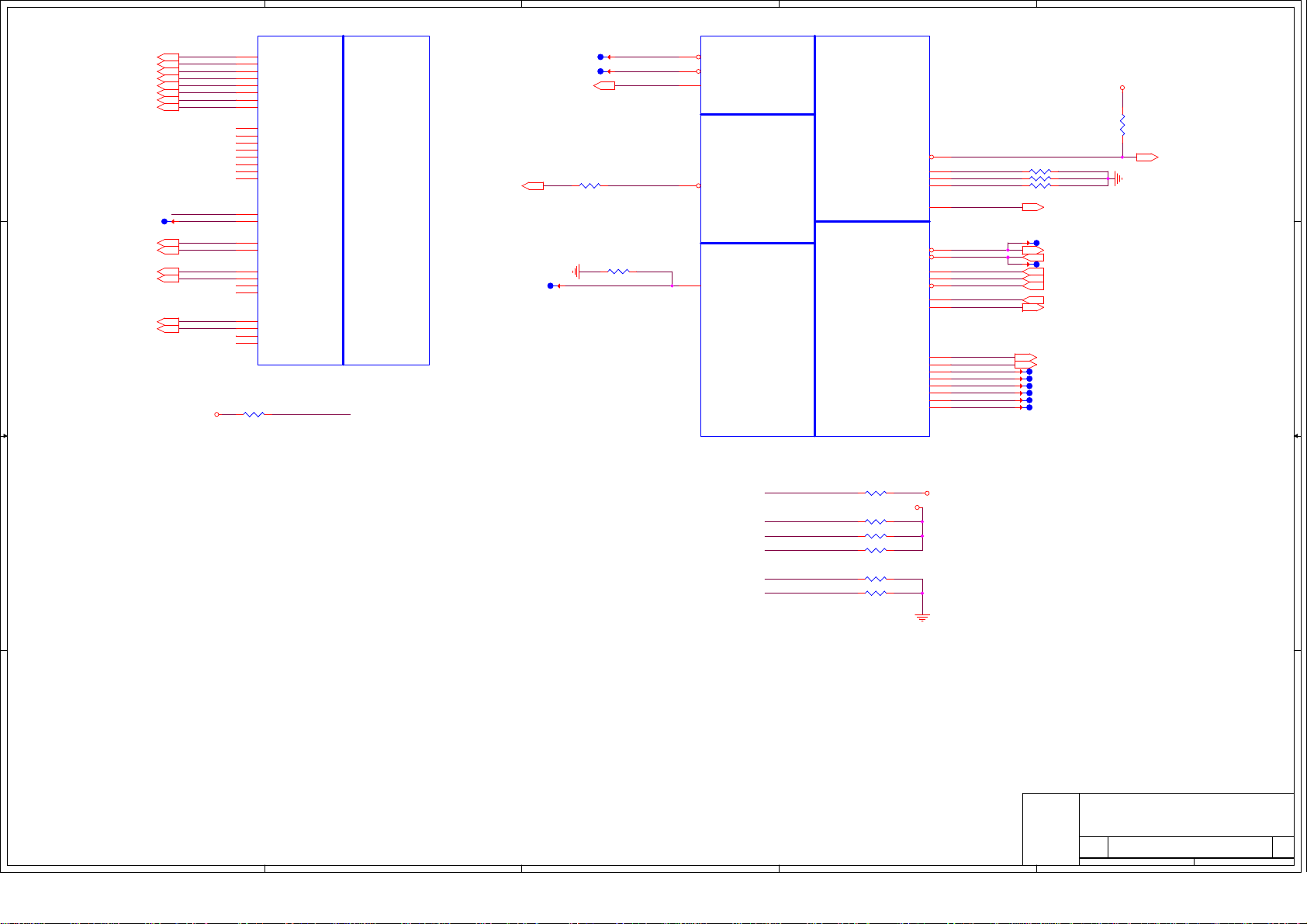

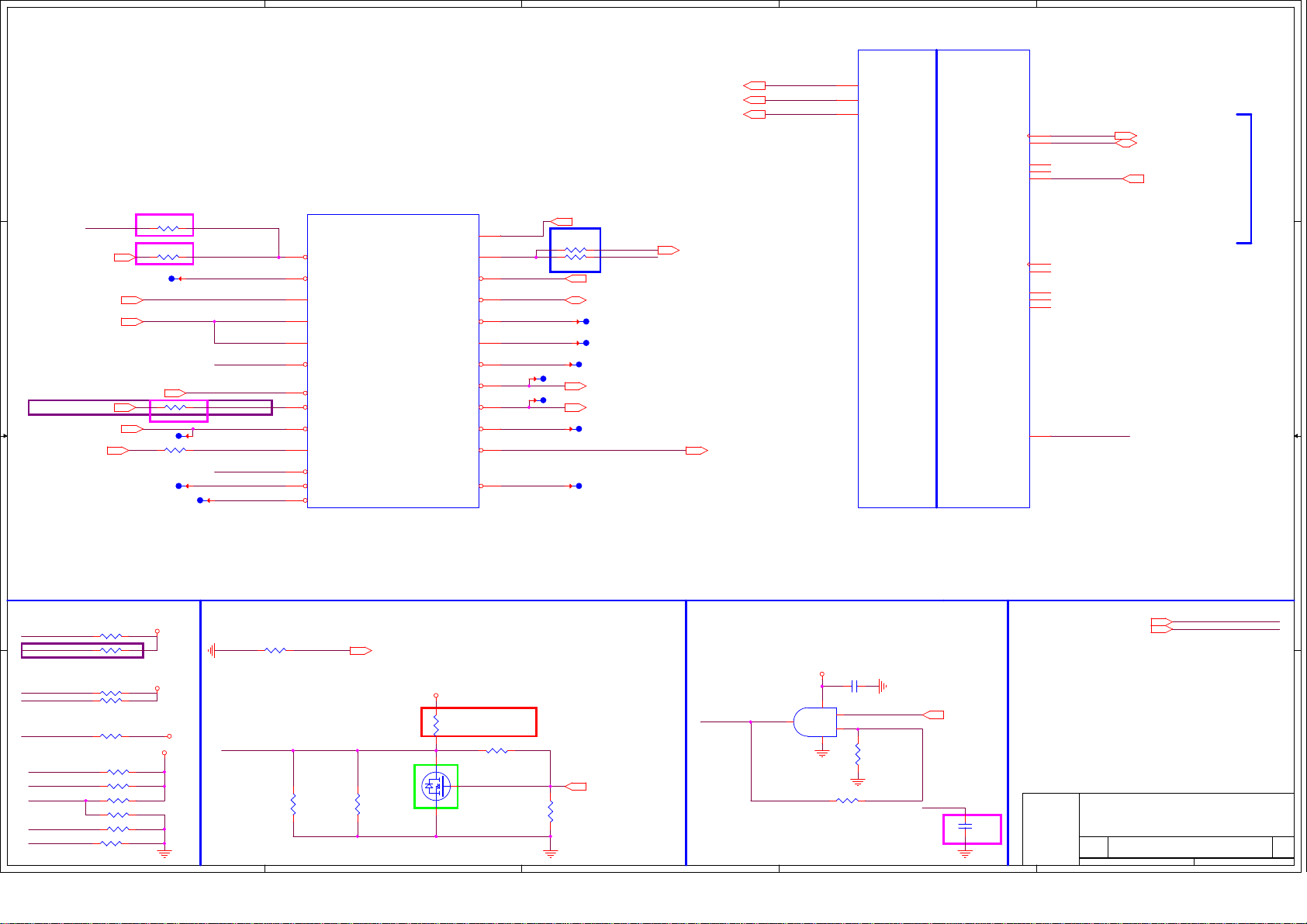

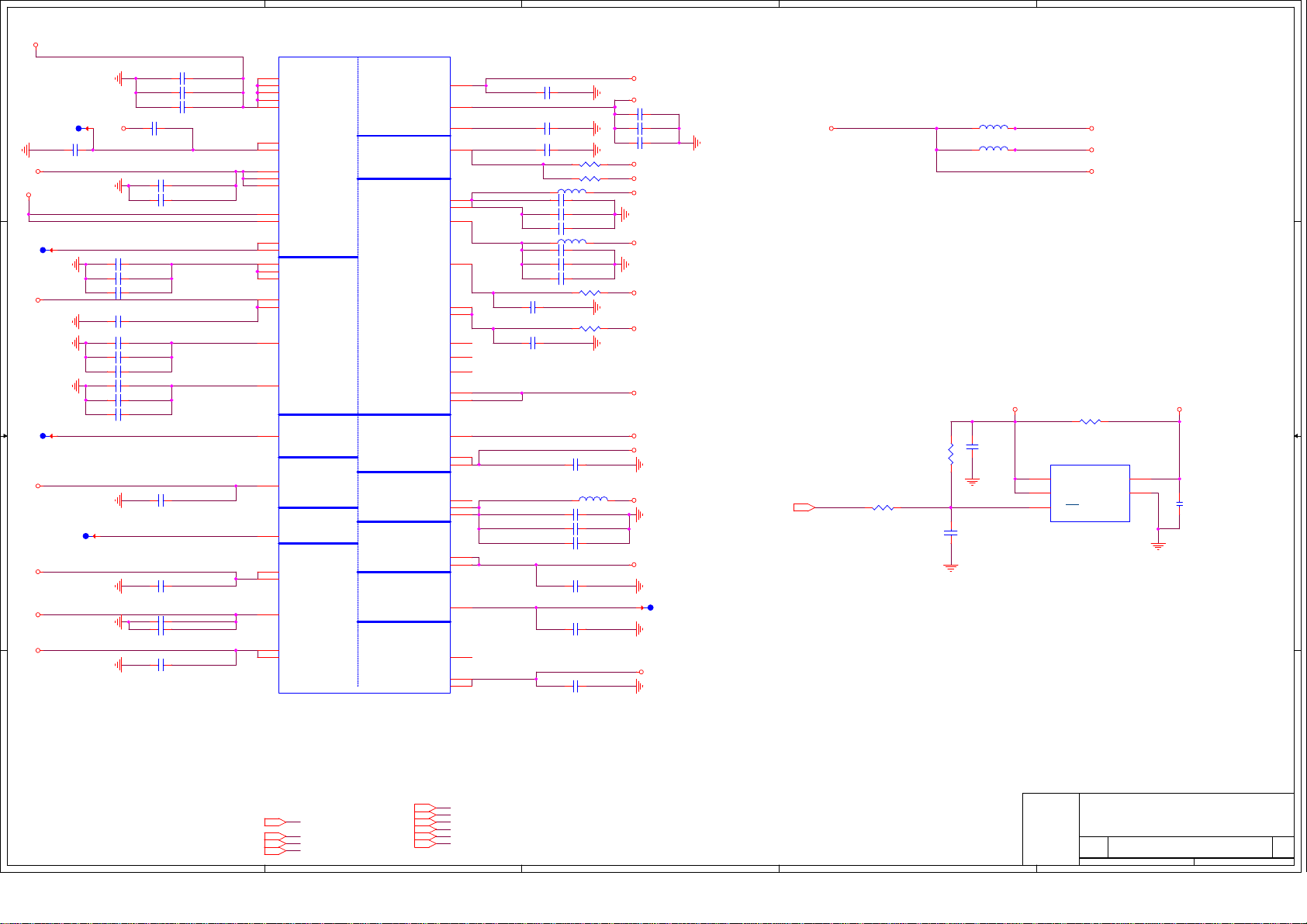

Page 2

5

4

3

2

1

2A

U2

_D2#16

IN

IN

_D1#16

IN

_D0#16

IN

_CLK#16

_D216

IN

_D116

IN

IN

_D016

IN

D D

eDP_COMPIO and ICOMPO signals should be shorted

near balls and routed with typical impedance <25 mohms

C C

_CLK16

TP

T_eDP_AUXP14

IN

T_eDP_AUXN14

IN

T_eDP_TXP014

IN

T_eDP_TXP114

IN

T_eDP_TXN014

IN

IN

T_eDP_TXN114

B B

DP

DP

B_LANE1_N

DP

B_LANE2_N

DP

B_LANE3_N

B_LANE0_P

DP

B_LANE1_P

DP

DP

B_LANE2_P

DP

B_LANE3_P

P_RCOM P

eD

ED

P_DISP_UTIL

106

T_eDP_AUXP

IN

T_eDP_AUXN

IN

T_eDP_TXP0

IN

T_eDP_TXP1

IN

T_eDP_TXN0

IN

IN

T_eDP_TXN1

+V

CCIOA_OUT

eDP_COMPIO and ICOMPO signals should be shorted

near balls and routed with typical impedance <25 mohms

DDI

1_TXN0

B58

1_TXN1

DDI

B55

DDI

1_TXN2

A57

1_TXN3

DDI

C55

DDI1_TXP0

C58

1_TXP1

DDI

A55

DDI1_TXP2

B57

1_TXP3

DDI

C51

DDI2_TXN0

C53

DDI

2_TXN1

C49

2_TXN2

DDI

A53

DDI

2_TXN3

C50

2_TXP0

DDI

B54

DDI

2_TXP1

B50

2_TXP2

DDI

B53

DDI

2_TXP3

D20

P_RCOMP

ED

A43

P_DISP_UTIL

ED

B45

ED

P_AUXP

A45

B46

B47

C46

B49

C45

A47

C47

A49

16 24.9/F_4

R1

P_AUXN

ED

eD

P_TXP 0

eD

P_TXP 1

eD

P_TXP 2

eD

P_TXP 3

eD

P_TXN 0

P_TXN 1

eD

eDP_TX N2

P_TXN 3

eD

*HSW_ULT_D DR3L

eD

P_RCOM P

H_

PROCHOT#25,31

eDP

PCI EXPRESS* - GRAPHICS

TP

TP

TP

_PECI25

EC

11 56.2/F_4

R5

130

C54

B_LANE0_N

126

123

R5

OC_DETECT#

PR

CA

TERR#

_PECI

EC

PR

20 10K/F_4

OCPWRGD

PR

OCHOT#

2B

U2

D61

PR

OC_DETECT#

K61

CA

TERR#

N62

PECI

K63

PR

C61

PR

*HSW_ULT_D DR3L

OCHOT#

OCPWRGD

MISCTHERMALPWR MANAGEMENT

Processor pull-up (CPU)

H_

PROCHOT#

XD

P_TDO_CPU

XD

P_TMS_CPU

XD

P_TDI_CPU

P_TRST#_CPU

XD

P_TCK0

XD

_DRAMRST#

SM

_RCOMP0

SM

SM

_RCOMP1

_RCOMP2

SM

DDR3JTAG & BPM

_PG_CNTL1

SM

DY#

PR

PR

EQ#

PR

OC_TCK

PR

OC_TMS

PR

OC_TRST#

OC_TDI

PR

PR

OC_TDO

#0

BPM

#1

BPM

BPM

#2

#3

BPM

BPM

#4

#5

BPM

BPM

#6

#7

BPM

17 62_4

R5

1.05S_VCCST

+V

16 51_4

R5

19 *51_4

R5

R5

18 *51_4

14 *51_4

R5

23 51_4

R5

+V

AV15

SM

AU60

SM

AV60

SM_RCOMP_1

AU61

SM

AV61

J62

K62

E60

XD

E61

XD

E59

XD

F63

XD

F62

XD

J60

H60

H61

BPM

H62

BPM

K59

BPM

H63

BPM

K60

BPM#6

J61

BPM

1.05S_VCCST

_DRAMRST#

_RCOMP_0

_RCOMP_2

P_TCK0

P_TMS_CPU

P_TRST#_CPU

P_TDI_CPU

P_TDO_CPU

#2

#3

#4

#5

#7

R2

27 200/F_4

36 121/F_4

R2

37 100/F_4

R2

TP

TP

XD

XD

TP

124

TP

40

41

TP

38

TP

TP42

TP

39

DDR_PG_CNTL 13

49

P_PRDY#_CPU 11

XD

XD

P_PREQ#_CPU 11

64

P_TCK0 7,11

XD

P_TMS_CPU 11

XD

P_TRST#_CPU 7,11

XD

P_TDI_CPU 11

XD

P_TDO_CPU 11

XD

P_BPM0 11

P_BPM1 11

+1

.35VSUS

R109

470_4

_DRAMRST# 12,13

DDR3

02

A A

https://t.me/schematicslaptop

https://t.me/biosarchive

PROJECT :Y61

PROJECT :Y61

PROJECT :Y61

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

ULT 1/9(eDP/DDI)

ULT 1/9(eDP/DDI)

ULT 1/9(eDP/DDI)

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

1

1A

1A

1A

232Monday, April 21, 2014

232Monday, April 21, 2014

232Monday, April 21, 2014

of

of

of

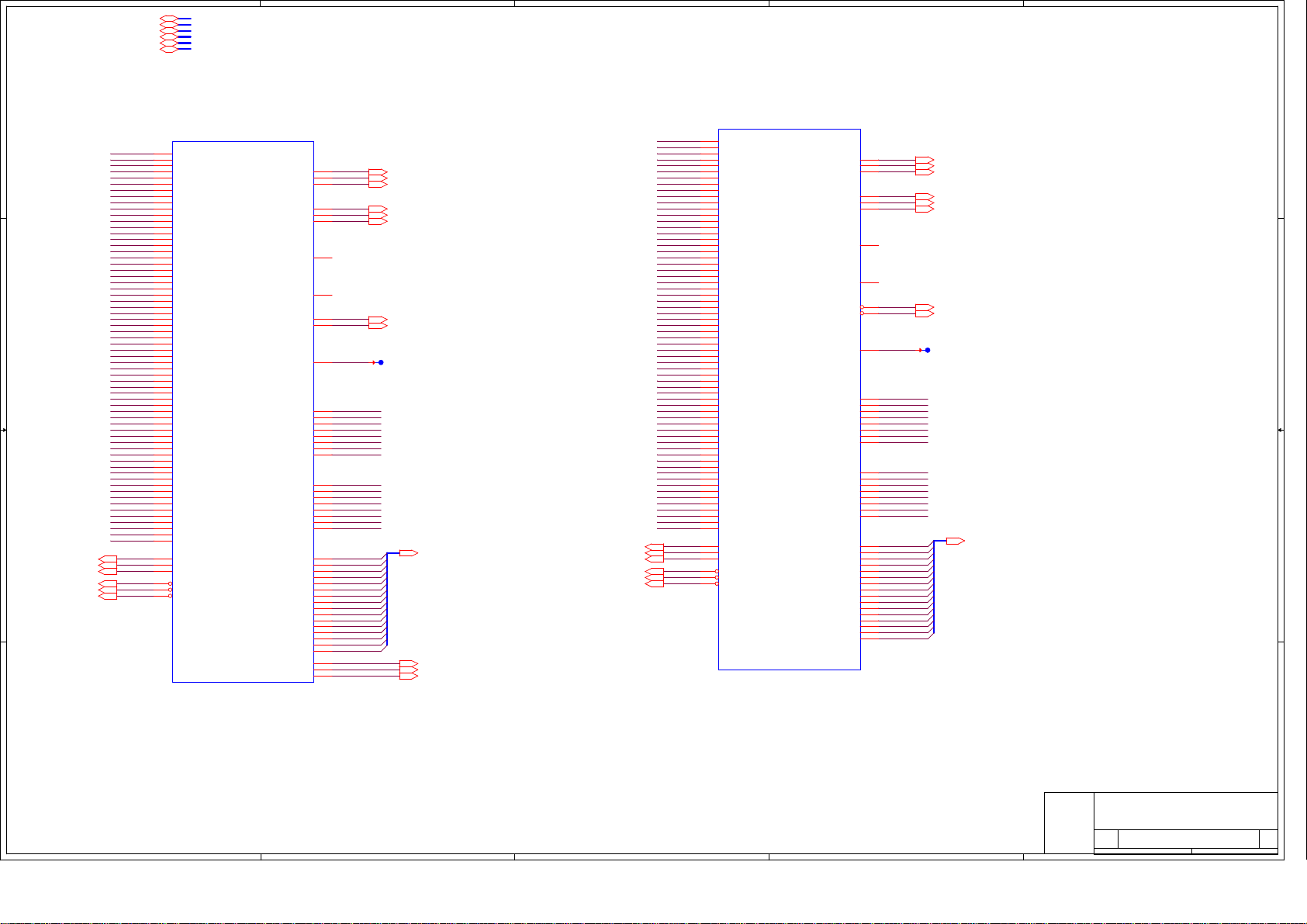

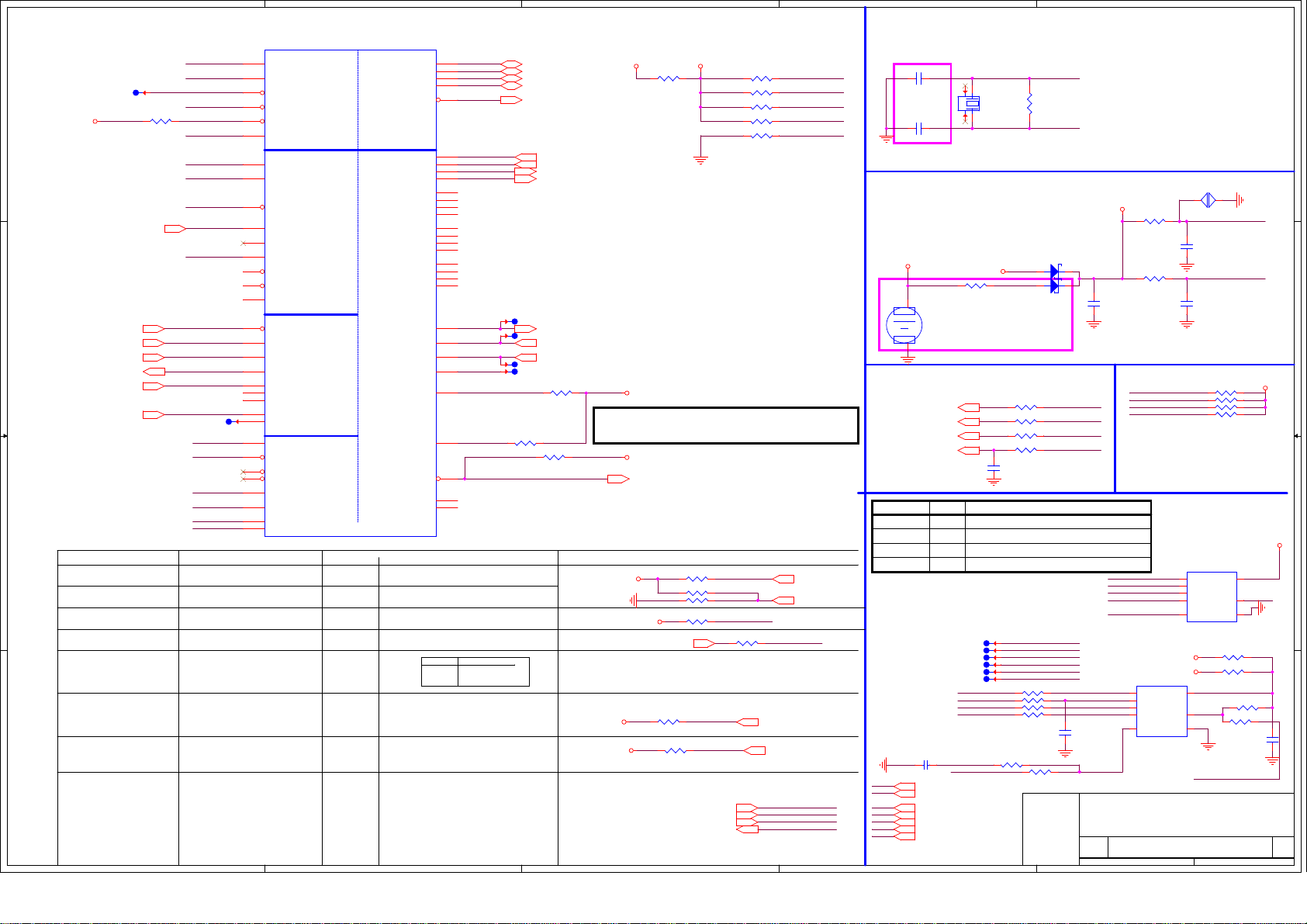

Page 3

5

A_DQ[ 63:0]12

M_

B_DQ[ 63:0]13

M_

M_

A_DQS N[7:0]12

M_

A_DQS P[7:0]12

M_

B_DQS N[7:0]13

M_

B_DQS P[7:0]13

4

swell ULT Processor (DDR3L)

Ha

3

2

1

03

D D

A_DQ0

M_

A_DQ1

M_

A_DQ2

M_

A_DQ3

M_

A_DQ4

M_

A_DQ5

M_

A_DQ6

A_DQ7

M_

A_DQ8

M_

A_DQ9

M_

A_DQ1 0

M_

A_DQ1 1

M_

A_DQ1 2

M_

M_A_DQ 13

M_

A_DQ1 4

M_

A_DQ1 5

M_

B_DQ0

M_

B_DQ1

M_

B_DQ2

M_

B_DQ3

M_

B_DQ4

B_DQ5

M_

B_DQ6

M_

B_DQ7

M_

B_DQ8

M_

B_DQ9

M_

B_DQ1 0

M_

B_DQ1 1

M_

M_

C C

B B

M_

A_BS#012

A_BS#112

M_

M_

A_BS#212

M_

A_CAS#12

M_

A_RAS#12

M_A_W E#12

A A

B_DQ1 2

M_

B_DQ1 3

M_

B_DQ1 4

M_

B_DQ1 5

M_

A_DQ1 6

M_

A_DQ1 7

M_

A_DQ1 8

A_DQ1 9

M_

A_DQ2 0

M_

A_DQ2 1

M_

A_DQ2 2

M_

A_DQ2 3

M_

A_DQ2 4

M_

A_DQ2 5

M_

M_A_DQ 26

M_

A_DQ2 7

M_

A_DQ2 8

M_

A_DQ2 9

M_

A_DQ3 0

M_

A_DQ3 1

M_

B_DQ1 6

M_

B_DQ1 7

B_DQ1 8

M_

B_DQ1 9

M_

B_DQ2 0

M_

B_DQ2 1

M_

B_DQ2 2

M_

B_DQ2 3

M_

M_B_DQ 24

M_

B_DQ2 5

M_

B_DQ2 6

M_

B_DQ2 7

M_

B_DQ2 8

M_

B_DQ2 9

M_

B_DQ3 0

M_

B_DQ3 1

SA

_DQ0

AH62

SA

_DQ1

AK63

SA

_DQ2

AK62

SA

_DQ3

AH61

SA

_DQ4

AH60

SA

_DQ5

AK61

SA

_DQ6

AK60

SA

_DQ7

AM63

SA

_DQ8

AM62

SA

_DQ9

AP63

SA

_DQ10

AP62

SA

_DQ11

AM61

SA

_DQ12

AM60

SA

_DQ13

AP61

SA

_DQ14

AP60

SA

_DQ15

AP58

SA

_DQ16

AR58

SA

_DQ17

AM57

SA

_DQ18

AK57

SA

_DQ19

AL58

SA

_DQ20

AK58

SA

_DQ21

AR57

SA

_DQ22

AN57

SA

_DQ23

AP55

SA

_DQ24

AR55

SA

_DQ25

AM54

SA

_DQ26

AK54

SA

_DQ27

AL55

SA

_DQ28

AK55

SA

_DQ29

AR54

SA

_DQ30

AN54

SA

_DQ31

AY58

SA

_DQ32

AW58

SA

_DQ33

AY56

SA

_DQ34

AW56

SA

_DQ35

AV58

SA

_DQ36

AU58

SA

_DQ37

AV56

SA

_DQ38

AU56

SA

_DQ39

AY54

SA

_DQ40

AW54

SA

_DQ41

AY52

SA

_DQ42

AW52

SA

_DQ43

AV54

SA

_DQ44

AU54

SA

_DQ45

AV52

SA

_DQ46

AU52

SA

_DQ47

AK40

SA

_DQ48

AK42

SA

_DQ49

AM43

SA

_DQ50

AM45

SA

_DQ51

AK45

SA

_DQ52

AK43

SA

_DQ53

AM40

SA

_DQ54

AM42

SA

_DQ55

AM46

SA

_DQ56

AK46

SA

_DQ57

AM49

SA

_DQ58

AK49

SA

_DQ59

AM48

SA

_DQ60

AK48

SA

_DQ61

AM51

SA

_DQ62

AK51

SA

_DQ63

AU35

SA_BA0

AV35

SA_BA1

AY41

_BA2

SA

AU34

SA_CAS#

AY34

SA_RAS#

AW34

_WE#

SA

*HSW_ULT_DDR3L

5

DDR SYSTEM MEMORY A

SM

SM_VREF_DQ1

AV37

SA

_CLK0

AU37

SA

_CLK#0

AU43

SA

_CKE0

AY36

SA

_CLK1

AW36

SA

_CLK#1

AW43

SA

_CKE1

AY42

SA

_CKE2

AY43

SA

_CKE3

AP33

SA

_CS#0

AR32

SA

_CS#1

AP32

SA

_ODT0

AJ61

SA

_DQSN0

AN62

SA

_DQSN1

AM58

SA

_DQSN2

AM55

SA

_DQSN3

AV57

SA

_DQSN4

AV53

SA

_DQSN5

AL43

SA

_DQSN6

AL48

SA

_DQSN7

AJ62

SA

_DQSP0

AN61

SA

_DQSP1

AN58

SA

_DQSP2

AN55

SA

_DQSP3

AW57

SA

_DQSP4

AW53

SA

_DQSP5

AL42

SA

_DQSP6

AL49

SA

_DQSP7

AU36

SA_MA0

AY37

SA_MA1

AR38

_MA2

SA

AP36

_MA3

SA

AU39

SA_MA4

AR36

SA_MA5

AV40

_MA6

SA

AW39

_MA7

SA

AY39

SA_MA8

AU40

SA_MA9

AP35

SA_MA10

AW41

SA_MA11

AU41

SA_MA12

AR35

_MA13

SA

AV42

SA_MA14

AU42

SA_MA15

AP49

_VREF_CA

SM

AR51

_VREF_DQ0

AP51

A_CLKP 0 12

M_

A_CLKN 0 12

M_

A_CKE0 12

M_

A_CLKP 1 12

M_

M_

A_CLKN 1 12

M_

A_CKE1 12

M_

A_CS#0 12

M_

A_CS#1 12

32

TP

M_A_DQ SN0

M_

A_DQS N1

M_

B_DQS N0

M_

B_DQS N1

M_

A_DQS N2

M_

A_DQS N3

M_

B_DQS N2

M_

B_DQS N3

A_DQS P0

M_

A_DQS P1

M_

M_B_DQ SP0

M_

B_DQS P1

M_

A_DQS P2

M_

A_DQS P3

M_

B_DQS P2

M_

B_DQS P3

M_A_A0

M_

A_A1

A_A2

M_

M_A_A3

A_A4

M_

M_A_A5

M_

A_A6

A_A7

M_

M_A_A8

A_A9

M_

M_

A_A10

M_

A_A11

M_A_A12

M_

A_A13

A_A14

M_

M_A_A15

SM_VREF

SM

DDR_VREF_DQ0_M3

SMDDR_VREF_DQ1_M3

20mils width

4

M_A_A[1 5:0] 12

SM

_VREF 12

SMDDR_VREF_DQ0_M3 12

SM

DDR_VREF_DQ1_M3 13

M_

M_B_BS# 113

M_

M_

B_CAS#13

B_RAS#13

M_

M_

B_W E#13

https://t.me/schematicslaptop

https://t.me/biosarchive

2C

U2

AH63

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_A_DQ 47

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_A_DQ 60

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_B_DQ 58

M_

M_

M_

M_

M_

B_BS#013

B_BS#213

3

A_DQ3 2

A_DQ3 3

A_DQ3 4

A_DQ3 5

A_DQ3 6

A_DQ3 7

A_DQ3 8

A_DQ3 9

A_DQ4 0

A_DQ4 1

A_DQ4 2

A_DQ4 3

A_DQ4 4

A_DQ4 5

A_DQ4 6

B_DQ3 2

B_DQ3 3

B_DQ3 4

B_DQ3 5

B_DQ3 6

B_DQ3 7

B_DQ3 8

B_DQ3 9

B_DQ4 0

B_DQ4 1

B_DQ4 2

B_DQ4 3

B_DQ4 4

B_DQ4 5

B_DQ4 6

B_DQ4 7

A_DQ4 8

A_DQ4 9

A_DQ5 0

A_DQ5 1

A_DQ5 2

A_DQ5 3

A_DQ5 4

A_DQ5 5

A_DQ5 6

A_DQ5 7

A_DQ5 8

A_DQ5 9

A_DQ6 1

A_DQ6 2

A_DQ6 3

B_DQ4 8

B_DQ4 9

B_DQ5 0

B_DQ5 1

B_DQ5 2

B_DQ5 3

B_DQ5 4

B_DQ5 5

B_DQ5 6

B_DQ5 7

B_DQ5 9

B_DQ6 0

B_DQ6 1

B_DQ6 2

B_DQ6 3

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

AL35

AM36

AU49

AM33

AM35

AK35

U2

2D

SB_

DQ0

SB_

DQ1

SB_

DQ2

SB_

DQ3

SB_

DQ4

SB_

DQ5

SB_

DQ6

SB_

DQ7

SB_

DQ8

SB_

DQ9

SB_

DQ10

SB_

DQ11

SB_

DQ12

SB_

DQ13

SB_

DQ14

SB_

DQ15

SB_

DQ16

SB_

DQ17

SB_

DQ18

SB_

DQ19

SB_

DQ20

SB_

DQ21

SB_

DQ22

SB_

DQ23

SB_

DQ24

SB_

DQ25

SB_

DQ26

SB_

DQ27

SB_

DQ28

SB_

DQ29

SB_

DQ30

SB_

DQ31

SB_

DQ32

SB_

DQ33

SB_

DQ34

SB_

DQ35

SB_

DQ36

SB_

DQ37

SB_

DQ38

SB_

DQ39

SB_

DQ40

SB_

DQ41

SB_

DQ42

SB_

DQ43

SB_

DQ44

SB_

DQ45

SB_

DQ46

SB_

DQ47

SB_

DQ48

SB_

DQ49

SB_

DQ50

SB_

DQ51

SB_

DQ52

SB_

DQ53

SB_

DQ54

SB_

DQ55

SB_

DQ56

SB_

DQ57

SB_

DQ58

SB_

DQ59

SB_

DQ60

SB_

DQ61

SB_

DQ62

SB_

DQ63

SB_

BA0

SB_

BA1

SB_BA2

CAS#

SB_

RAS#

SB_

SB_WE#

INT

*HSW_ULT_DDR3L

AN38

SB_

CLK0

AM38

SB_

CLK#0

AY49

SB_

CKE0

AL38

SB_

CLK1

AK38

SB_

CLK#1

AU50

SB_

CKE1

AW49

SB_

CKE2

AV50

SB_

CKE3

AM32

SB_

CS#0

AK32

SB_

CS#1

AL32

SB_

ODT0

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

M_

M_

M_B_DQ SN4

M_

M_

M_

M_

M_

M_

M_

M_

M_

M_A_DQ SP6

M_

M_

M_

M_B_A0

M_

M_B_A2

M_

M_

M_B_A5

M_

M_B_A7

M_

M_

M_B_A10

M_

M_

M_

M_B_A14

M_

SB_

DQSN0

SB_

DQSN1

SB_

DQSN2

SB_

DQSN3

SB_

DQSN4

SB_

DQSN5

SB_

DQSN6

SB_

DQSN7

SB_

DQSP0

SB_

DQSP1

SB_

DQSP2

SB_

DQSP3

SB_

DQSP4

SB_

DQSP5

SB_

DQSP6

SB_

DQSP7

SB_

MA0

SB_

MA1

SB_MA2

SB_MA3

DDR SYSTEM MEMORY B

SB_

SB_

SB_MA6

SB_MA7

SB_

SB_

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

MA15

SB_

MA4

MA5

MA8

MA9

A_DQS N4

A_DQS N5

B_DQS N5

A_DQS N6

A_DQS N7

B_DQS N6

B_DQS N7

A_DQS P4

A_DQS P5

B_DQS P4

B_DQS P5

A_DQS P7

B_DQS P6

B_DQS P7

B_A1

B_A3

B_A4

B_A6

B_A8

B_A9

B_A11

B_A12

B_A13

B_A15

2

TP

M_

M_

M_

M_

M_

M_

M_

M_

31

B_CLKP 0 13

B_CLKN 0 13

B_CKE0 13

B_CLKP 1 13

B_CLKN 1 13

B_CKE1 13

B_CS#0 13

B_CS#1 13

M_B_A[1 5:0] 13

PROJECT :Y61

PROJECT :Y61

PROJECT :Y61

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document N umber Rev

Size Document N umber Rev

ze Document Num ber Rev

Si

Custom

Custom

Custom

ULT 2/9 (DDR3 I/F)

ULT 2/9 (DDR3 I/F)

ULT 2/9 (DDR3 I/F)

Date: Sheet

Date: Sheet

Date: Sheet

1

332Monday, Apri l 21, 2014

332Monday, Apri l 21, 2014

332Monday, Apri l 21, 2014

of

of

of

1A

1A

1A

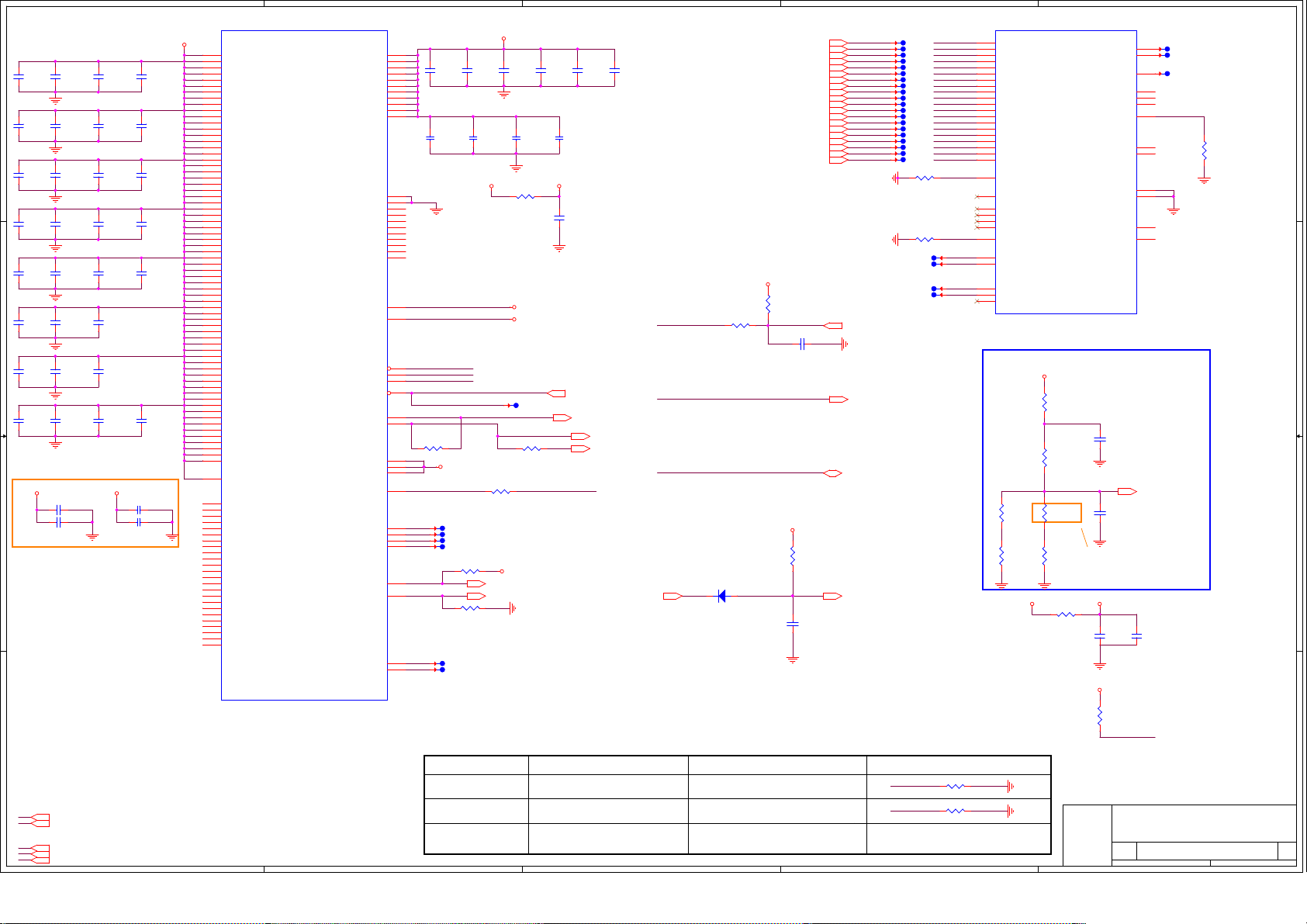

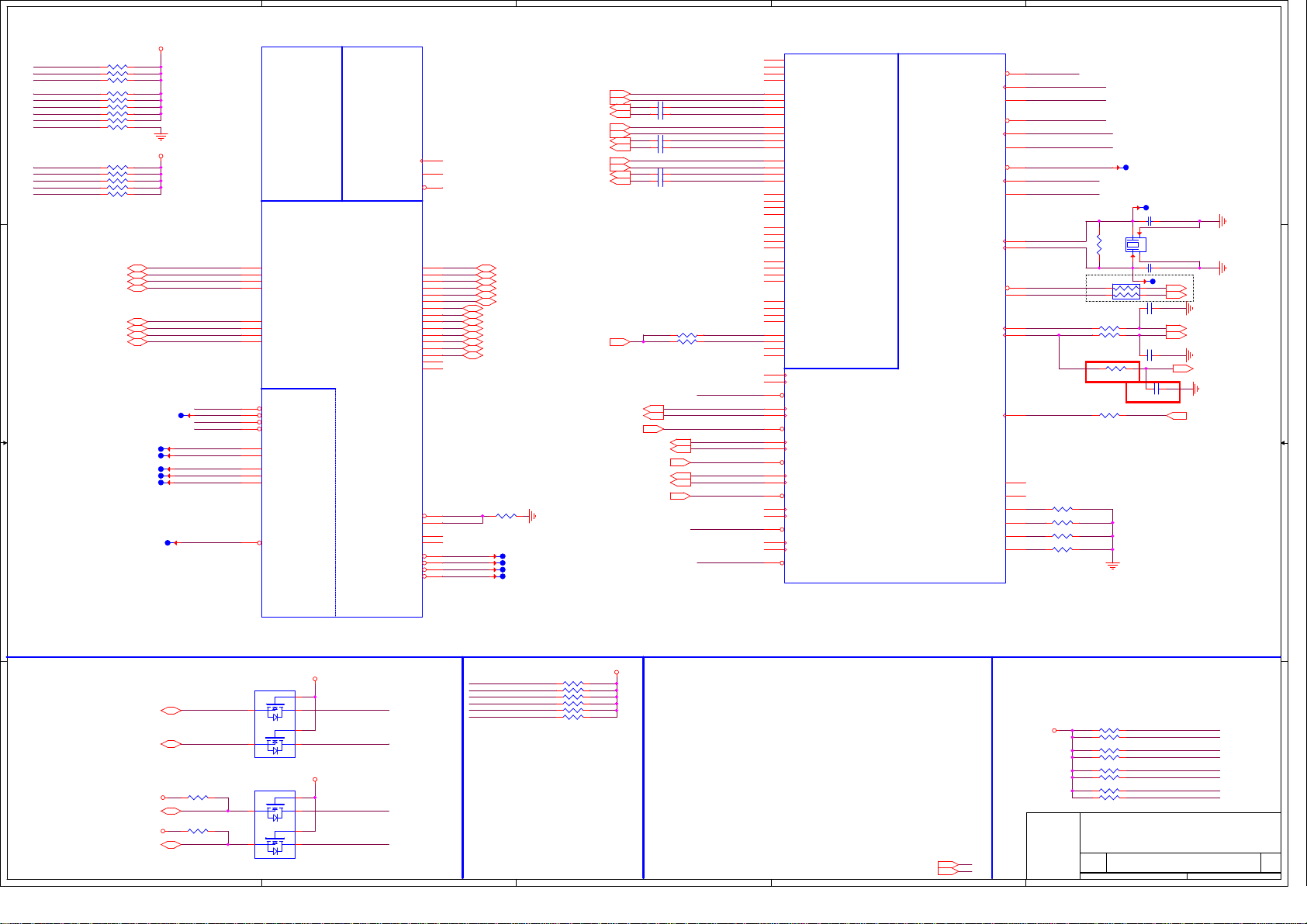

Page 4

5

U2

2F

32A

CC_CORE

+V

C36

C40

C44

C48

8

25

C9

C1

C1

C1

C164

C1

C1

C2

22U/6.3V_8

C1

79

22U/6.3V_8

43

C1

22U/6.3V_8

C1

10

22U/6.3V_8

C163

22U/6.3V_8

81

C2

22U/6.3V_8

C2

82

22U/6.3V_8

C4

22U/6.3V_8

22U/6.3V_8

D D

C2

08

22U/6.3V_8

22U/6.3V_8

6

C9

22U/6.3V_8

22U/6.3V_8

C1

80

22U/6.3V_8

22U/6.3V_8

C97

22U/6.3V_8

22U/6.3V_8

09

C2

22U/6.3V_8

22U/6.3V_8

C C

C1

65

22U/6.3V_8

22U/6.3V_8

22

24

C4

22U/6.3V_8

C4

22U/6.3V_8

CC_CORE

+V

C4

22U/6.3V_8

CC_CORE

+V

55 *47U/6.3V_8

EC

56 *47U/6.3V_8

EC

B B

42

07

C1

22U/6.3V_8

C4

11

20

22U/6.3V_8

05

41

C4

22U/6.3V_8

C1

78

62

22U/6.3V_8

C206

22U/6.3V_8

05

04

17

12

C1

22U/6.3V_8

65 *12P/50V_4

EC

66 *12P/50V_4

EC

PV reserve for RF request

A A

https://t.me/schematicslaptop

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G33

G35

G37

G39

G41

G43

G45

G47

G49

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

AB57

AD57

AG57

C24

C28

C32

F59

L59

J58

N58

AC58

AB23

AD23

AA23

AE59

AT2

AU44

AV44

D15

F22

H22

J21

N23

R23

T23

U10

AL1

AM11

AP7

AU10

AU15

*HSW_ULT_DDR3L

POWER

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

VC

C

RS

VD

RS

VD

RS

VD

RS

VD

RS

VD

RS

VD

RS

VD

RS

VD

RS

VD

RSVD

RSVD

VD

RS

VD

RS

RSVD

RSVD

VD

RS

VD

RS

RSVD

RSVD

RSVD

RSVD

RSVD

VD

RS

RSVD

PW

HSW ULT POWER

VC

https://t.me/biosarchive

+VCCIOA_OUT 2

+VCCIO_OUT 6

+1.35VSUS 2,12,13,29

+1.05V 7,10,11,25,30,32

+VCC_CORE 31

5

4

1.4A

.35VSUS

+1

AH26

VD

DQ

AJ31

VD

DQ

AJ33

VD

DQ

AJ37

VD

DQ

AN33

VD

DQ

AP43

VD

DQ

AR48

VD

DQ

AY35

VD

DQ

AY40

VD

DQ

AY44

VD

DQ

AY50

VD

DQ

D63

VS

S

P62

VS

S

T59

RS

VD

AD60

RS

VD

AD59

RS

VD

AA59

RS

VD

AE60

RS

VD

AC59

RS

VD

AG58

RS

VD

U59

RS

VD

V59

RS

VD

A59

VC

CIO_OUT

E20

VC

CIOA_OUT

L62

VI

DALERT #

N63

VI

DSCLK

L63

VI

DSOUT

H59

R_DEBUG#

F60

VR

_EN

C59

VR

_READY

AC22

VC

CST

AE22

VC

CST

AE23

VC

CST

B59

CST_P WRGD

P60

RS

VD_TP

P61

RS

VD_TP

N59

RS

VD_TP

N61

RS

VD_TP

E63

VCC_SE NSE

E62

S_SEN SE

VS

AW14

VD

RS

AY14

VD

RS

83

C1

10U/6.3V_6

Direct tie to CPU VCC/VSS-Ball

89

C1

2.2U/6.3V_4

CPU_SVIDALRT#

H_

_SVID_CLK

VR

CPU_SVIDDAT

H_

R_DEBUG

PW

22 10K_4

R5

1.05S_VCCST

+V

VCCST_PWRGD_R

H_

122

TP

44

TP

TP36

TP

45

100- ±1% pull-up to VCC near processor.

R513 100/F_4

R5

12 100/F_4

TP101

TP

100

Close to CPU

46

C1

C1

10U/6.3V_6

10U/6.3V_6

88

C1

2.2U/6.3V_4

+1

.05V

R5

01 *0_8

IM

27 *0_4/S

R5

R5

05 *0_4/S

+V

CC_CORE

VC

C_SENSE 31

VSS_SENSE 31

Processor Strapping

CFG3

(Physcial Debug Enable)

DFX Priv acy

CFG4

(DP Presence Strap)

4

3

CFG0-19 need Reserve TP

68

16

C1

2.2U/6.3V_4

+V

C4

28

4.7U/6.3V_6

+V

CCIO_OUT

+V

CCIOA_OUT

TP

119

VP_PW RGD_R

H_

45

C1

10U/6.3V_6

15

C1

2.2U/6.3V_4

CCIO_OUT

PW

H_

VCCST_PWRGD

R_DEBUG 11

VR_ENABLE_MCP 31

33

C1

10U/6.3V_6

VP_PW RGD_R 25

IM

VP_PW RGD 6,31

IM

69

C1

10U/6.3V_6

yout note: need routing

La

together and ALERT need

between CLK and DATA.

H_

CPU_SVIDALRT#

_SVID_CLK

VR

CPU_SVIDDAT

H_

10 43_4

R5

+V

1.05S_VCCST

R5

15

75/F_4

36 *0.1U/10V_4

C4

+V

1.05S_VCCST

21

HWPG11,25,28,29,30 H_VCCST_PWRGD 11

D9

The CFG signals have a default value of '1' if not terminated on the board.

1 0

sable: Enable: Set DFX Enable in DFX i nterface MSR

Di

Disable; No physical DP attached to eDP

Enable; An ext DP dev ice is connected to eDP

3

RB500V-40

CF

G011

CF

G111

CF

G211

CF

G311

CF

G411

CF

G511

G611

CF

G711

CF

G811

CF

G911

CF

G1011

CF

G1111

CF

CFG1211

CF

G1311

CF

G1411

CF

G1511

CF

G1611

CF

G1711

CF

G1811

G1911

CF

SVI

SVID CLK

SVID DATA

06

R5

10K_4

35

C4

*10P/50V_4

D ALERT

VR

_SVID_ALERT# 31

VR

_SVID_CLK 31

_SVID_DATA 31

VR

CF

CF

CFG2

CF

CF

CF

CF

CF

CF

CF

CF

CF

CF

CF

CF

CF

CF

CF

CF

CF

2

U2

2E

AC60

09

R5

CF

49.9/F_4

TD

71

R4

8.2K/F_4

120

129

125

132

R5

08 *1K_4

R272 1K_4

CF

CF

CFG2

CF

CF

CF

CF

CF

CF

CF

CF

CF

CF

CF

CF

CF

CF

CF

CF

CF

G_RCOMP

_IREF

rcuit

Ci

G0

G1

G3

G4

G5

G6

G7

G8

G9

G10

G11

G12

G13

G14

G15

G16

G17

G18

G19

AC62

AC63

AA63

AA60

AA62

AA61

AV63

AU63

Y62

Y61

Y60

V62

V61

V60

U60

T63

T62

T61

T60

U63

U62

V63

A5

E1

D1

J20

H18

B12

C63

C62

B43

CF

G0

CF

G1

CF

G2

CF

G3

CF

G4

CF

G5

CF

G6

CF

G7

CF

G8

CF

G9

CF

G10

CF

G11

CF

G12

CF

G13

CF

G14

CF

G15

CF

G16

CF

G17

CF

G18

CF

G19

CF

G_RCOMP

RS

VD

RS

VD

RS

VD

RS

VD

RS

VD

TD

_IREF

RS

VD_TP

RS

VD_TP

RS

VD_TP

RS

VD_TP

RS

VD

*HSW_ULT_DDR3L

85

R4

*0_4

TH

ER_CPU2

87

R4

*100K_4 NTC

+3

VPCU

R1

R3

16.5K/F_4

TH

R3

*0_4/S

TH

ER_CPU

R3

100K_4 NTC

19 *0_8/S

RS

VD_TP

RS

VD_TP

RS

VD_TP

PR

OC_OPI_RCOMP

RESERVED

hrm Protect

IO T

For

65 degree, 1.8v limit, (SW)

71

RM_MOINTOR

53

C3

0.1U/10V_4

1 2

R3

70

3.3K/F_4

For

75 degree, 1.2v limit, (HW)

60

59

49

C3

0.1U/10V_4

1 2

change to shortpad

PV

+V1.05S_VCCST+1.05V

C114

*1U/6.3V_4

+V1.05S_VCCST

R5

150/F_4

PWR_DEBUG

Size Document N umber Rev

Size Document N umber Rev

Size Document N umber Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

RS

RS

RS

RS

RS

RS

RS

07

G0

TP

48

G1

TP

67

TP

50

G3

65

TP

G4

47

TP

G5

131

TP

G6

46

TP

G7

66

TP

G8

53

TP

G9

TP54

G10

TP

55

G11

TP

56

G12

TP

59

G13

TP

60

G14

TP

61

G15

TP

62

G16

52

TP

G17

51

TP

G18

58

TP

G19

57

TP

TP

TP

TP

TP

CFG3

CFG4

2

1

A51

TP

111

B51

TP

110

L60

43

TP

N60

VD

W23

VD

Y22

VD

AY15

OC_OPI_RCOMP

PR

AV62

VD

D58

VD

P22

VS

S

N21

VS

S

P20

VD

R20

VD

TH

RM_MOINTOR1 25

C113

*22U/6.3V_8

PROJECT :Y61

PROJECT :Y61

PROJECT :Y61

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

04 -- ULT 3/9 (POWER-1)

04 -- ULT 3/9 (POWER-1)

04 -- ULT 3/9 (POWER-1)

74

R4

49.9/F_4

1

04

of

of

of

432Monday, Apri l 21, 2014

432Monday, Apri l 21, 2014

432Monday, Apri l 21, 2014

1A

1A

1A

Page 5

5

2G

U2

1

A1

VSS

4

A1

VSS

8

A1

VSS

4

A2

VSS

8

A2

VSS

A32

VSS

6

A3

VSS

A40

VSS

4

A4

VSS

A48

D D

C C

B B

VSS

2

A5

VSS

A56

VSS

AA1

VSS

AA58

VSS

0

AB1

VSS

0

AB2

VSS

2

AB2

VSS

AB7

VSS

61

AC

VSS

21

AD

VSS

3

AD

VSS

63

AD

VSS

0

AE1

VSS

AE5

VSS

8

AE5

VSS

AF

11

VSS

12

AF

VSS

AF

14

VSS

15

AF

VSS

AF

17

VSS

18

AF

VSS

AG

1

VSS

11

AG

VSS

AG

21

VSS

23

AG

VSS

60

AG

VSS

61

AG

VSS

62

AG

VSS

63

AG

VSS

17

AH

VSS

19

AH

VSS

20

AH

VSS

22

AH

VSS

24

AH

VSS

28

AH

VSS

30

AH

VSS

AH32

VSS

34

AH

VSS

36

AH

VSS

38

AH

VSS

40

AH

VSS

42

AH

VSS

44

AH

VSS

49

AH

VSS

51

AH

VSS

53

AH

VSS

55

AH

VSS

57

AH

VSS

13

AJ

VSS

14

AJ

VSS

AJ

23

VSS

25

AJ

VSS

AJ

27

VSS

29

AJ

VSS

*HSW_ULT_D DR3L

VSS

35

AJ

VSS

39

AJ

VSS

41

AJ

VSS

43

AJ

VSS

45

AJ

VSS

AJ47

VSS

50

AJ

VSS

AJ52

VSS

54

AJ

VSS

AJ56

VSS

58

AJ

VSS

AJ60

VSS

63

AJ

VSS

AK23

VSS

AK3

VSS

2

AK5

VSS

10

AL

VSS

13

AL

VSS

17

AL

VSS

20

AL

VSS

22

AL

VSS

23

AL

VSS

26

AL

VSS

29

AL

VSS

31

AL

VSS

AL

33

VSS

36

AL

VSS

AL

39

VSS

40

AL

VSS

AL

45

VSS

46

AL

VSS

AL

51

VSS

52

AL

VSS

AL

54

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

57

AL

60

AL

61

AL

1

AM

17

AM

23

AM

31

AM

52

AM

17

AN

23

AN

31

AN

32

AN

AN35

36

AN

39

AN

40

AN

42

AN

43

AN

45

AN

46

AN

48

AN

49

AN

51

AN

52

AN

60

AN

63

AN

AN

7

0

AP1

AP1

7

0

AP2

4

U2

2H

2

AP2

VSS

3

AP2

VSS

6

AP2

VSS

9

AP2

VSS

AP3

VSS

1

AP3

VSS

AP38

VSS

9

AP3

VSS

AP48

VSS

2

AP5

VSS

AP54

VSS

7

AP5

VSS

AR11

VSS

15

AR

VSS

17

AR

VSS

23

AR

VSS

31

AR

VSS

33

AR

VSS

39

AR

VSS

43

AR

VSS

49

AR

VSS

5

AR

VSS

52

AR

VSS

13

AT

VSS

AT

35

VSS

37

AT

VSS

AT

40

VSS

42

AT

VSS

AT

43

VSS

46

AT

VSS

AT

49

VSS

61

AT

VSS

AT

62

VSS

63

AT

VSS

1

AU

VSS

16

AU

VSS

18

AU

VSS

20

AU

VSS

22

AU

VSS

24

AU

VSS

26

AU

VSS

28

AU

VSS

30

AU

VSS

33

AU

VSS

51

AU

VSS

AU53

VSS

55

AU

VSS

57

AU

VSS

59

AU

VSS

4

AV1

VSS

6

AV1

VSS

0

AV2

VSS

4

AV2

VSS

8

AV2

VSS

3

AV3

VSS

4

AV3

VSS

6

AV3

VSS

9

AV3

VSS

1

AV4

VSS

AV4

3

VSS

6

AV4

VSS

AV4

9

VSS

1

AV5

VSS

AV5

5

VSS

*HSW_ULT_D DR3L

VSS

INT

3

9

AV5

VSS

AV8

VSS

16

AW

VSS

24

AW

VSS

AW33

VSS

35

AW

VSS

AW37

VSS

4

AW

VSS

AW40

VSS

42

AW

VSS

AW44

VSS

47

AW

VSS

AW50

VSS

51

AW

VSS

59

AW

VSS

60

AW

VSS

1

AY1

VSS

6

AY1

VSS

8

AY1

VSS

2

AY2

VSS

4

AY2

VSS

6

AY2

VSS

0

AY3

VSS

3

AY3

VSS

AY4

VSS

1

AY5

VSS

AY5

3

VSS

7

AY5

VSS

AY5

9

VSS

AY6

VSS

B2

0

VSS

4

B2

VSS

B2

6

VSS

8

B2

VSS

2

B3

VSS

6

B3

VSS

B4

VSS

0

B4

VSS

4

B4

VSS

8

B4

VSS

2

B5

VSS

6

B5

VSS

0

B6

VSS

1

C1

VSS

4

C1

VSS

C18

VSS

0

C2

VSS

5

C2

VSS

7

C2

VSS

8

C3

VSS

9

C3

VSS

7

C5

VSS

2

D1

VSS

4

D1

VSS

8

D1

VSS

D2

VSS

1

D2

VSS

3

D2

VSS

5

D2

VSS

D2

6

VSS

7

D2

VSS

D2

9

VSS

0

D3

VSS

D3

1

VSS

DC_TEST_AY2_AW2

DC_

117

TP

DC_

DC_

DC_

98

TP

DC_

DC_

DC_

TEST_AY3_AW3

TE

ST_AY60

TEST_AY61_AW61

TEST_AY62_AW62

ST_B2

TE

TEST_A3_B3

TEST_A61_B61

TEST_B62_B63

TEST_C1_C2

2

U2

3

D3

4

D3

5

D3

7

D3

8

D3

9

D3

D41

2

D4

D43

5

D4

D46

7

D4

D49

D5

D50

1

D5

3

D5

4

D5

5

D5

7

D5

9

D5

2

D6

D8

1

E1

7

E1

0

F2

F2

6

0

F3

F3

4

8

F3

F4

2

6

F4

F5

0

4

F5

F5

8

1

F6

8

G1

2

G2

G3

G5

G6

G8

3

H1

AY2

AY3

AY60

AY61

AY62

B2

B3

B61

B62

B63

C1

C2

*HSW_ULT_D DR3L

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

DA

DA

DA

DA

DA

DA

DA

DA

DA

DA

DA

DA

2I

VSS

ISY_CHAIN_NTCF_AY2

ISY_CHAIN_NTCF_AY3

ISY_CHAIN_NTCF_AY60

ISY_CHAIN_NTCF_AY61

ISY_CHAIN_NTCF_AY62

ISY_CHAIN_NTCF_B2

ISY_CHAIN_NTCF_B3

ISY_CHAIN_NTCF_B61

ISY_CHAIN_NTCF_B62

ISY_CHAIN_NTCF_B63

ISY_CHAIN_NTCF_C1

ISY_CHAIN_NTCF_C2

DA

ISY_CHAIN_NTCF_A3

ISY_CHAIN_NTCF_A4

DA

DA

ISY_CHAIN_NTCF_A60

ISY_CHAIN_NTCF_A61

DA

DA

ISY_CHAIN_NTCF_A62

ISY_CHAIN_NTCF_AV1

DA

ISY_CHAIN_NTCF_AW1

DA

ISY_CHAIN_NTCF_AW2

DA

ISY_CHAIN_NTCF_AW3

DA

ISY_CHAIN_NTCF_AW61

DA

ISY_CHAIN_NTCF_AW62

DA

DA

ISY_CHAIN_NTCF_AW63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

7

H1

7

H5

0

J1

2

J2

9

J5

3

J6

K1

2

K1

L13

L15

L17

L18

L20

L58

L61

L7

2

M2

0

N1

N3

9

P5

3

P6

0

R1

2

R2

R8

T1

8

T5

U2

0

2

U2

U6

1

U9

V1

0

V3

V7

0

W2

W2

2

0

Y1

9

Y5

3

Y6

8

V5

46

AH

3

V2

16

AH

A3

DC_TEST_A3_B3

A4

TE

A60

TE

A61

DC_

A62

TE

AV1

TE

AW1

TE

AW2

DC_

AW3

DC_

AW61

DC_

AW62

DC_

AW63

TE

ST_A4

ST_A60

TEST_A61_B61

ST_A62

ST_AV1

ST_AW1

TEST_AY2_AW2

TEST_AY3_AW3

TEST_AY61_AW61

TEST_AY62_AW62

ST_AW63

1

05

TP

99

128

TP

TP

127

TP

80

89

TP

TP

121

A A

PROJECT :Y61

PROJECT :Y61

PROJECT :Y61

Quanta Computer Inc.

Quanta Computer Inc.

https://t.me/schematicslaptop

https://t.me/biosarchive

5

4

3

2

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Si

ze Document Number Rev

Custom

Custom

Custom

ULT 4/9 (RSV,GND)

ULT 4/9 (RSV,GND)

ULT 4/9 (RSV,GND)

Date: Sheet

Date: Sheet

Date: Sheet

1

532Monday, April 21, 2014

532Monday, April 21, 2014

532Monday, April 21, 2014

of

of

of

1A

1A

1A

Page 6

5

4

3

2

1

https://t.me/schematicslaptop

https://t.me/biosarchive

D D

SI R67 no stuff

SWARN#

for DS3

C C

SU

SU

SACK#_EC25

S_PWROK11

SY

_PWROK25

EC

for DS3

SWARN#_EC25

_PRESENT_EC25

SWON#11,25

DNB

R381 10K_4

R5

R7

R6

R54 *10K_4

R2

R59 8.2K/F_4

R412 10K_4

R4

R456 10K_4

R4

3 1K_4

4 10K_4

6 10K_4

6 *1K_4

32 *1K_4

55 100K_4

SU

AC

B B

PC

H Pull-high/low(CLG)

_BATLOW#

PM

PCIE_WAKE#

Change to 1k for LAN wake from OBFF state issue

SUSACK#

SWARN#

SU

PWRBTN# internally PU in PCH to 3.3V_DSW

AC_PRESENT_R

A A

SYS_PWROK

KRUN#

CL

SYS_RESET#

RSMRST#

DP

WROK_EC

7 *0_4

R6

R7

6 0_4

SI R76 stuff

TP

94

MRST#25

RS

R6

8 0_4

TP

5 0_4

R3

TP

+3

VS5

+3V_DEEP_SUS

+3

5

SACK#

SU

SU

SACK#

S_RESET#

SY

_PWROK

EC

EC

_PWROK

PL

TRST#

MRST#

RS

SU

SWARN#

SI R68 stuff

17

85

AC

_PRESENT_R

_BATLOW#

PM

PC

H_SLP_S0_N

H_SLP_WLAN_N

PC

TP93

PL

TRST#(CLG)

8 100K_4

R9

for DS3

+3

VS5

V

IN

T_eDP_HPD _Q

2L

U2

AK2

SU

SACK#

AC3

SYS_

RESET#

AG2

PWROK

SYS_

AY7

AB5

AG7

AW6

AV4

AL7

AJ8

AN4

AF3

AM5

R2

*100K_4

PC

H_PWROK

ROK

APW

TRST#

PL

MRST#

RS

SWARN#/SUSPW RDNACK/GPIO30(SUS)

SU

PW

RBTN#

PRESENT / GPIO31(DSW)

AC

LOW# / GPIO72(DSW )

BAT

P_S0#

SL

P_WLAN#/ GPIO29(DSW )

SL

*HSW_ULT_D DR3L

PLTRST#

24

DS

WVRMEN 7

WVRMEN

DS

DP

WROK

WA

KE#

KRUN#/ GPIO32

CL

SU

S_STAT# / GPIO61 (SUS)

SCLK / GPIO62 (SUS)

SU

P_S5# / GPIO63 ( DSW)

SL

SL

System Power Management

PLTRST# 11,19,21,23,25,26

P_S4#

P_S3#

SL

SL

P_A#

P_SUS#

SL

P_LAN#

SL

Check Q16 Rise/Fall time less than 100ns

AW7

AV5

AJ5

V5

AG4

AE6

AP5

AJ6

AT4

AL5

AP4

AJ7

DS

DP

PC

CL

SU

PC

WVRMEN

WROK

IE_WAKE#

KRUN#

S_STAT#

H_SUSCLK

SL

P_S5#

P_A#

SL

SL

P_LAN#

Ra

R4

45 0_4

R4

46 *0_4

Rb

19

TP

TP

23

DP

RS

IE_WAKE# 19,23,25,26

PC

KRUN# 25

CL

TP

18

TP

11

TP

20

SC# 25

SU

SU

SB# 25

TP

12

9

TP

For DS3 -->Ra

Non-DS3 -->Rb

WROK_EC

MRST#

SL

P_SUS#_EC

Reserve EDP_HPD opposites circuit!

+V

CCIO_OUT

25

R2

*100K_4

IN

T_eDP_HPD

4

26

R2

V0.7 -> 10 K

DG

*10K/F_4

SCH V0.7 -> 1K

R2

3

2

6

Q1

*DMG1012T-7(SOT523)

1

13 *0_4/S

UL

T_EDP_HPD 14,15

R1

99

100K_4

RTD2132R Vender request PD 100kohm

for DS3

3

Lynx Point-LP Platform Controller Hub (LVDS,DDI)

U2

2M

H_LVDS_BLON15

PC

PC

H_DISP_ON15

H_DPST_PWM14,15

PC

WROK_EC 25

DP

SL

P_SUS#_EC 25

Sy

stem PWR_OK(CLG)

SYS_PWROK

H_LVDS_BLON

PC

PC

H_DISP_ON

H_DPST_PWM

PC

4

U2

*TC7SH08FU

A9

EDP_BKLEN

C6

EDP_VDDEN

B8

EDP_BKLCTL

*HSW_ULT_D DR3L

+3VS5

C27 *0.1U/10V_4

2

1

EC_PWROK

3 5

R40 *0_4/S

R4

10K_4

1

SI reserve for RF request

2

DDP

B_CTRLCLK

B_CTRLDATA

DDP

EDP SIDEBAND

VP_PWR GD

IM

DDP

DDP

DDP

DDP

C_CTRLCLK

DDP

C_CTRLDATA

DDP

DDP

DISPLAY

DDP

IMVP_PW RGD 4,31

C514

*10P/50V_4

B_AUXN

B_AUXP

B_HPD

C_AUXN

C_AUXP

C_HPD

P_HPD

ED

B9

C9

C5

B5

C8

D9

D11

B6

A6

A8

D6

SD

VO_CLK

SD

VO_DATA

HDMI_HPD_CON

T_eDP_HPD _Q

IN

+3

PROJECT :Y61

PROJECT :Y61

PROJECT :Y61

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

Size Document Number Rev

Size Document Number Rev

Si

ze Document Number Rev

Custom

Custom

Custom

ULT 5/9(Power Manger)

ULT 5/9(Power Manger)

ULT 5/9(Power Manger)

Date: Sheet

Date: Sheet

Date: Sheet

SD

VO_CLK 16

SD

VO_DATA 16

I_HPD_CON 16

HDM

+3V7,8,9,10,11,12,13,14,15,16,17,18,19,21,22,23,24,25,26,31,32

VS57,9,10,20,23,24,25,28,30,32

1

06

INT. HDMI

632Monday, April 21, 2014

632Monday, April 21, 2014

632Monday, April 21, 2014

of

of

of

1A

1A

1A

Page 7

5

4

3

2

1

Lynx Point-LP Platform Controller Hub

(HDA,JTAG,SATA)

U2

2J

RT

RT

21

TP

D D

C C

B B

V_RTC

+3

PCH Strap Table

R457 1M_4

Z_SDIN017

AC

XD

P_TRST#_CPU2,11

AG_TCK_PCH11

JT

JT

AG_TDI_PCH11

AG_TDO_PCH11

JT

JT

AG_TMS_PCH11

AGX_PCH2,11

JT

Pin Name Strap description Sampled Configuration

SPKR

IO_D0 /GPIO66 Top-Block Swap

SD

RT

SR

SM

PC

AC

ACZ_SYNC

AC

AC

XD

P_TRST#_CPU

JT

AG_TCK_PCH

AG_TDI_PCH

JT

JT

AG_TDO_PCH

AG_TMS_PCH

JT

JT

AGX_PCH

reboot mode setting PWROK

No

AW5

C_X1

C_X2

C_RST#

TC_RST#

_INTRUDER#

H_INVRMEN

Z_BCLK

Z_RST#

Z_SDOUT

TP

90

PC

H_SPI1_CLK

H_SPI_CS0#

PC

PC

H_SPI1_SI

H_SPI1_SO

PC

PC

H_SPI_IO2

H_SPI_IO3

PC

CX1

RT

AY5

CX2

RT

AU7

CRST#

RT

AV6

SR

AU6

IN

TRUDER#

AV7

IN

TVRMEN

AW8

HDA

AV11

HDA

AU8

HDA

AY10

HDA

AU12

HDA

AU11

HDA

AW10

HDA

AV10

HDA

AY8

S1_SCLK

I2

AU62

PC

AE62

PC

AD61

PC

AE61

PC

AD62

PC

AL11

RS

AC4

RS

AE63

JT

AGX

AV2

RS

AA3

SPI

Y7

SPI

Y4

SPI

AC2

SPI

AA2

SPI

AA4

SPI

Y6

SPI

AF1

SPI

*HSW_ULT_D DR3L

TCRST#

_BCLK / I2S0_SCLK

_SYNC/ I2S0_SFRM

_RST#/ I2S_MCLK

_SDIN0/ I2S0_RXD

_SDIN1/ I2S1_RXD

_SDO/ I2S0_TXD

_DOCK_EN# / I2S1_TXD

_DOCK_RST/ I2S1_SFRM

H_TRST#

H_TCK

H_TDI

H_TDO

H_TMS

VD

VD

VD

_CLK

_CS0#

_CS1#

_CS2#

_MOSI

_MISO

_IO2

_IO3

PWROK

RTC

LPC

A_RN0/ PERN6_L3

SAT

SAT

A_RP0/ PERP6_L3

A_TN0/ PETN6_L3

SAT

SAT

A_TP0/ PETP6_L3

A_RN1/ PERN6_L2

SAT

A_RP1/ PERP6_L2

SAT

A_TN1/ PETN6_L2

SAT

A_TP1/ PETP6_L2

SAT

SAT

A_RN2/ PERN6_L1

A_RP2/ PERP6_L1

SAT

SAT

A_TN2/ PETN6_L1

A_TP2/ PETP6_L1

SAT

SAT

A_RN3/ PERN6_L0

AUDIO

SAT

A_RP3/ PERP6_L0

SAT

A_TN3/ PETN6_L0

SAT

A_TP3/ PETP6_L0

A0GP/ GPIO34

SAT

A1GP/ GPIO35

SAT

A2GP/ GPIO36

SAT

SAT

A3GP/ GPIO37

SAT

SATA

SPI JTAG

0 = Default (weak pull-down 20K)

= Setting to No-Reboot mode

1

0 = "top-block swap" mode

1 = Default (weak pull-up 20K)

AU14

D0

LA

AW12

LA

D1

AY12

D2

LA

AW11

LAD3

AV12

LFRAME#

J5

SAT

H5

SAT

B15

SAT

A15

SATA_TXP0

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17

D17

V1

AC

C_LED#

U1

SI

O_EXT_SMI#

V6

I_SERR#

PC

AC1

SAT

A3GP

C12

A_RCOMP

A_RCOMP

A_IREF

SAT

SAT

ALED#

SAT

A12

SAT

A_IREF

U3

L11

VD

RS

K10

RS

VD

A_RXN0

A_RXP0

A_TXN0

LA

LA

LA

LA

LF

TP

TP

TP

TP

70 *0_6/S

R4

D0 21,23,25

D1 21,23,25

D2 21,23,25

D3 21,23,25

RAME# 21,23,25

SAT

A_RXN0 21

SAT

A_RXP0 21

SAT

A_TXN0 21

A_TXP0 21

SAT

70

C_LED# 21

AC

75

O_EXT_SMI# 25

SI

PC

I_SERR# 25

26

74

R4

69 3.01K/F_4

35 10K_4

R4

INTVRMEN Integrated 1.05V VRM enable ALWAYS Should be always pull-up

Flash Descriptor Security

ly for Interposer

HDA_SDO /I2S0_TXD

GSPI0_MOSI /GPIO86 PWROK

GPIO15

DS

WVRMEN

A A

5

On

Bo

ot BIOS Selection

TLS Confidentiality PWROK

Deep Sx Well

On-Die Voltage

Regulator Enable

PWROK

ALWAYS Should be always pull-up

0 = Default (weak pull-down 20K)

1 = Can be Overridden

GN

T0#

Boot Location

1

LP

C

SPI

(Default)

0 = ME Crypto Transport Layer Sec urity

cipher suite with no confidentiality(Default)

1 = Intel ME Crypto TLS cipher suite with

confidentiality

0

4

+3V_DEEP_SUS

.05V

+1

54 *0_4

R2

HDD0

1.05S_ASATA3PLL

+V

recommended that SATA AC coupling capacitors should be

DG

close to the connector (<100 mils) for optimal signal quality.

V

+3

SAT

A_LED# 21

Circuit

V

+3

+3V_RTC

GPIO33_EC25

3 *1K_4

R3

+3

V_RTC

.05VS5

+1

84 *51_4

R2

R5

26 51_4

25 51_4

R5

R252 51_4

R5

28 *51_4

Close to Chipset

(SATA3 6.0Gb/s) 15.6"

14 *1K_4

R4

59 *1K_4

R4

R4

58 *1K_4

R4

63 330K_4

R4

PC

PCH_SPI1_CLK_R25

PC

PC

3

60 330K_4

H_SPI_CS0#_R25

H_SPI1_SI_R25

H_SPI1_SO_R25

PCH_INVRMEN

67 1K_4

R4

SPKR

IO15_ULT 9

GP

DS

PC

PCH_SPI1_CLK_R

PCH_SPI1_SI_R

PCH_SPI1_SO_R

JT

JT

JT

JT

JT

SPKR

IO66_ULT 9

GP

Z_SDOUT

AC

WVRMEN 6

H_SPI_CS0#_R

AGX_PCH

AG_TMS_PCH

AG_TDI_PCH

AG_TDO_PCH

AG_TCK_PCH

9

RTC Clock 32.768KHz

SI

change to 12pF

68 12P/50V_4

C3

C3

67 12P/50V_4

RT

+3

V_RTC_0

V_RTC_0

+3

12

23

Y2

768KHZ

32.

4 1

C Circuitry(RTC)

RTC Power trace width 20mils.

VPCU

+3

R2

04

V_RTC_1

+3

*1K_4

CN16

*RTC SOCKET

HDA

R4

AC

Z_SYNC_AUDIO17

Z_RST#_AUDIO17

AC

Z_SDOUT_AUDIO17

AC

BI

T_CLK_AUDIO17

*10P/50V_4

Vender

EON

Wi

nbond

GigaDevice

Size

8MB AKE3EZN0Q01 (EN25QH64-104HIP (QE))

8MB

8MB

Socket

H SPI ROM(CLG)

PC

TP1-6 need place to TOP

0 1U/10V_4

C1

PCH_SPI_IO2

+3V 6,8,9,10,11,12,13,14,15,16,17,18,19,21,22,23,24,25,26,31,32

+5V 16,17,18,21,22,23,32

.05V 4,10,11,25,30,32

+1

+3VS5 6,9,10,20,23,24,25,28,30,32

VPCU 4,22,23,25,27,28

+3

V_RTC 10,27

+3

+V1.05S_ASATA3PLL 10

2

68 33_4

7 33_4

R8

R4

62 33_4

61 33_4

R4

C3

88

P/N

AKE3EFP0N07 (W25Q64FVSSIQ (QE))

AKE3EGN0Q01 (GD25B64BSIGR (QE))

DFHS08FS023

TP5

3

TP

1

TP

4

TP

TP2

6

TP

PCH_SPI_CS0#

H_SPI1_CLK

PC

PCH_SPI1_SI PCH_SPI1_SI_R

H_SPI1_SO

PC

+3

R9

VSPI

RT

C_X1

47

R4

10M_4

C_X2

RT

2 1

D6

2 1

D5

Bus(CLG)

H_SPI_CS0#_R

PC

PCH_SPI1_CLK_R

H_SPI1_SI_R

PC

PCH_SPI1_SO_R

OS_WP#

BI

HOLD#

R1

7 15/F_4

0 15/F_4

R1

R4

33 15/F_4

R12 15/F_4

3.3K/F_4

15/F_4

R8

J1

OLDERJUMPER -2

1 2

C2

39

1U/6.3V_4

C2

12

1U/6.3V_4

*S

SR

MEK500V-40

*MEK500V-40

C2

1U/6.3V_4

30m

+3

40

SI

no stuff

V_RTC

ils

40

R2

20K/F_4

03

R2

20K/F_4

GPIO Pull UP

C_LED#

AC

AC

Z_SYNC

Z_RST#

AC

Z_SDOUT

AC

AC

Z_BCLK

PCH_SPI_CS0#_R

H_SPI1_CLK_R

PC

H_SPI1_SO_R

PC

C33

22P/50V_4

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

SIO_EXT_SMI#

PC

I_SERR#

SAT

A3GP

H_SPI_CS0#_R

PC

PC

H_SPI1_CLK_R

H_SPI1_SI_R

PC

PC

H_SPI1_SO_R

OS_WP#

BI

V_DEEP_SUS

+3

U16

1

#

CE

6

K

SC

5

SI

2

SO

3

#

WP

GD25B64BSIGR

AKE3EGN0Q01

BIOS_WP#

PROJECT :Y61

PROJECT :Y61

PROJECT :Y61

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

ULT 6/9(SATA/HDA)

ULT 6/9(SATA/HDA)

ULT 6/9(SATA/HDA)

R3

91 10K_4

R3

92 10K_4

R3

0 10K_4

88 10K_4

R3

4M

SPI ROM Socket

5

U1

1

#

CE

VD

6

SCK

5

SI

2

LD#

SO

HO

3

WP#

VSS

*50960-0084N-001

DFHS08FS023

91960-0084L-8P-SOCKET

8 *0_4

R1

VS5

+3

9 0_4

R1

+3VSPI

8

D

VD

LD#

HO

VSS

1

LD#

HO

7

4

PCH_SPI_IO3

R1

R4

07

RT

C_RST#

TC_RST#

+3

+3

8

D

7

HO

LD#

4

3 3.3K/F_4

11 15/F_4

C9

0.1U/10V_4

732Monday, April 21, 2014

732Monday, April 21, 2014

732Monday, April 21, 2014

of

of

of

V

VSPI

1A

1A

1A

https://t.me/schematicslaptop

https://t.me/biosarchive

Page 8

5

PC

I/USBOC# Pull-up(CLG)

_INTB#

TS

RQC#

PI

RQD#

PI

IO77_ULT

GP

IO78_ULT

GP

U_EVENT#

GP

6_FB_EN

GC

PU_HOLD_RST#

DG

D D

PU_HOLD_RST#

DG

BALERT#

SM

B_OC1#

US

B_OC2#

US

B_OC3#

US

B_OC4#

US

USB3.0

C C

39 10K_4

R4

8 10K_4

R2

18 10K_4

R4

8 10K_4

R4

93 10K_4

R3

95 *10K_4

R3

9 *10K_4

R4

7 *10K_4

R2

0 100K_4

R2

83 10K_4

R3

09 10K_4

R4

05 10K_4

R4

86 10K_4

R3

04 10K_4

R4

US

B30_RX1-20

US

B30_RX1+20

US

B30_TX1-20

US

B30_TX1+20

US

B30_RX2-20

US

B30_RX2+20

US

B30_TX2-20

US

B30_TX2+20

Lynx Point-LP Platform Controller Hub

(HDA,JTAG,SATA)

V

+3

V_DEEP_SUS

+3

for DS3

2N

U2

G20

US

B3RN1

H20

US

B3RP1

C33

US

B3TN1

B34

US

B3TP1

E18

US

B3RN2

F18

US

B3RP2

B33

US

B3TN2

A33

US

B3TP2

83

TP

97

TP

7

TP

78

TP

14

TP

TP

B B

8

IO77_ULT

GP

IO78_ULT

77

GP

TP

RQC#

PI

RQD#

PI

_INTB#

TS

PU_PWR_EN_R

DG

PU_HOLD_RST#

DG

U_EVENT#

GP

6_FB_EN

GC

I_PME#

PC

SMBus/Pull-up(CLG) CLK_REQ/Strap Pin(CLG)

CLK214,25

MB

DATA214,25

MB

A A

R3

49 4.7K_4

V

+3

B_RUN_DAT11,12,13,14,22

SM

R3

58 4.7K_4

V

+3

B_RUN_CLK11,12,13,14,22

SM

5

U6

PI

RQA#/ GPIO77

P4

PI

RQB#/ GPIO78

N4

PI

RQC#/ GPIO79

N2

PI

RQD#/ GPIO80

L1

GP

IO52

L3

GP

IO54

R5

GP

IO51

L4

GP

IO53

U7

GP

IO55

PCI

AD4

PM

E#

*HSW_ULT_ DDR3L

+3

3

Q2

4 3

1

*2N7002kDW

2

Q2

4 3

1

2N7002kDW

V

5

2

6

+3

V

5

2

6

C- Link

USB

OC

0# / GPIO40(SUS)

OC

1# / GPIO41(SUS)

OC

2# / GPIO42(SUS)

OC

3# / GPIO43(SUS)

K501UB

SMB_ME1_CLK

SM

B_ME1_DAT

SMB_PCH_DAT

SM

B_PCH_CLK

4

AF2

CL

_CLK

AD2

CL

_DATA

AF4

CL

_RST#

USB2. 0(M/B- 1)

USB2. 0(M/B- 2)

USB2. 0 Sma ll board

Se

nsor Hub

Ca

mera

WLAN

TS

AN8

US

B2N0

AM8

US

B2P0

AR7

US

B2N1

AT7

US

B2P1

AR8

US

B2N2

AP8

US

B2P2

AR10

US

B2N3

AT10

US

B2P3

AM15

US

B2N4

AL15

US

B2P4

AM13

US

B2N5

AN13

US

B2P5

AP11

US

B2N6

AN11

US

B2P6

AR13

US

B2N7

AP13

US

B2P7

TIE TRACES TOGETHER

CLOSE TO PINS WITH LENGTH

TO RESISTOR

AJ10

B_BIAS

US

BRBIAS#

US

BRBIAS

RS

RS

4

US

AJ11

AN10

VD

AM10

VD

AL3

B_OC1#

US

AT1

B_OC2#

US

AH2

B_OC3#

US

AV3

B_OC4#

US

Cardreader

WLAN

N

LA

(USBP0)

(USBP5)

(USBP1)

(USBP4)

(USBP2)

(USBP6)

(USBP3)

US

BP0- 20

US

BP0+ 20

US

BP1- 18

US

BP1+ 18

US

BP2- 15

US

BP2+ 15

US

BP3- 24

US

BP3+ 24

US

BP4- 24

US

BP4+ 24

US

BP5- 20

US

BP5+ 20

US

BP6- 23

US

BP6+ 23

Cardreader

9

R9

22.6/F_4

84

TP

91

TP

73

TP

88

TP

PCIE_CLKREQ0#

PC

PC

PC

PCIE_CLKREQ_CR#

PC

IE_CLKREQ5#

IE_CLKREQ_WL AN#

IE_CLKREQ_LAN#

IE_CLKREQ_VGA#

PC

IE_RXN2_CARD26

PC

IE_RXP2_CARD26

PC

IE_TXN2_CARD26

PC

IE_TXP2_CARD26

PC

IE_RXN3_WLAN23

PC

IE_RXP3_WLAN23

PC

IE_TXN3_WLAN23

PC

IE_TXP3_WLAN23

PC

IE_RXN4_LAN19

PC

IE_RXP4_LAN19

PC

IE_TXN4_LAN19

PC

IE_TXP4_LAN19

+V

1.05S_AUSB3PLL10

CL

K_PCIE_CRN26

CL

K_PCIE_CRP26

PC

IE_CLKREQ_CR#26

CL

K_PCIE_WLANN23

CL

WLAN

LAN

K_PCIE_WLANP23

PC

IE_CLKREQ_WL AN#23

CL

CL

PC

IE_CLKREQ_LAN#19

+3

R416 10K_4

R4

36 10K_4

R3

87 10K_4

R4

38 10K_4

R50 10K_4

R2

1 10K_4

V

C1

C1

C4

C4

C4

C4

K_PCIE_LANN19

K_PCIE_LANP19

3

30 0.1U/10V_4

29 0.1U/10V_4

10 0.1U/10V_4

14 0.1U/10V_4

16 0.1U/10V_4

15 0.1U/10V_4

44 *0_4/S

R1

37 3.01K/F_4

R1

3

IE_TXN2_CARD_C

PC

IE_TXP2_CARD_C

PC

IE_TXN3_WLAN_C

PC

IE_TXP3_WLAN_C

PC

IE_RXN4_LAN

PC

IE_RXP4_LAN

PC

IE_TXN4_LAN_C

PC

IE_TXP4_LAN_C

PC

PC

IE_RCOMP

PC

IE_CLKREQ0#

PC

K_PCIE_CRN

CL

K_PCIE_CRP

CL

IE_CLKREQ_CR#

PC

K_PCIE_WLANN

CL

K_PCIE_WLANP

CL

IE_CLKREQ_WL AN#

PC

K_PCIE_LANN

CL

K_PCIE_LANP

CL

IE_CLKREQ_LAN#

PC

IE_CLKREQ_VGA#

PC

IE_CLKREQ5#

PC

2

U2

2K

G17

PER

N1 / USB3RN3

F17

PER

P1 / USB3RP3

C30

PET

N1 / USB3TN3

C31

PET

P1 / USB3TP3

F15

PER

N2/ USB3RN4

G15

PER

P2/ USB3RP4

B31

PET

N2/ USB3TN4

IE_IREF

A31

PET

G11

PER

F11

PER

C29

PET

B30

PET

F13

PER

G13

PER

B29

PET

A29

PET

F10

PER

E10

PER

C23

PET

C22

PET

F8

PER

E8

PER

B23

PET

A23

PET

H10

PER

G10

PER

B21

PET

C21

PET

E6

PER

F6

PER

B22

PET

A21

PET

B27

PC

A27

PC

E15

RS

E13

RS

C43

CL

C42

CL

U2

PC

B41

CL

A41

CL

Y5

PC

C41

CL

B42

CL

AD1

PC

B38

CL

C37

CL

N1

PC

A39

CL

B39

CL

U5

PC

B37

CL

A37

CL

T2

PC

*HSW_ULT_ DDR3L

P2/ USB3TP4

N3

P3

N3

P3

N4

P4

N4

P4

N5_L0

P5_L0

N5_L0

P5_L0

N5_L1

P5_L1

N5_L1

P5_L1

N5_L2

P5_L2

N5_L2

P5_L2

N5_L3

P5_L3

N5_L3

P5_L3

IE_IREF

IE_RCOMP

VD

VD

KOUT_PCIE0N

KOUT_PCIE0P

IECLKRQ0# / GPIO1 8

KOUT_PCIE_N1

KOUT_PCIE_P1

IECLKRQ1# / GPIO1 9

KOUT_PCIE_N2

KOUT_PCIE_P2

IECLKRQ2# / GPIO2 0

KOUT_PCIE_N3

KOUT_PCI_P3

IECLKRQ3# / GPIO2 1

KOUT_PCIE_N4

KOUT_PCIE_P4

IECLKRQ4# / GPIO2 2

KOUT_PCIE_N5

KOUT_PCIE_P5

IECLKRQ5# / GPIO2 3

SMBUS

SM

SM

L1ALERT# / PCHHOT# / GPIO73(SUS)

PCI-E*

CLOCK SIGNALS

https://t.me/schematicslaptop

https://t.me/biosarchive

V_DEEP_SUS6,7,9,10,11

+3

2

SM

BALERT# / GPIO11(SUS)

SM

SM

L0ALERT# / GPIO60( SUS)

SM

SM

SM

L1CLK / GPIO75( SUS)

SM

L1DATA / GPIO74(SUS)

XT

XT

AL24_OUT

CL

KOUT_ITPXDP#

CL

KOUT_ITPXDP_P

CL

KOUT_LPC_0

CL

KOUT_LPC_1

DI

FFCLK_BIASREF

TE

STLOW_C3 5

TE

STLOW_C3 4

TE

STLOW_AK8

TE

STLOW_AL 8

V6,7,9,10,11,12,13,14,15,16,17,18,19,21,22,23,24,25,26,31,32

+3

BCLK

BDATA

L0CLK

L0DATA

AL24_IN

RS

RS

AN2

AP2

AH1

AL2

AN1

AK1

AU4

AU3

AH3

A25

B25

B35

A35

AN15

AP15

C26

K21

VD

M21

VD

C35

C34

AK8

AL8

for DS3

V_DEEP_SUS

+3

BALERT#

SM

B_PCH_CLK

SM

B_PCH_DAT

SM

L0ALERT#

SM

B_ME0_CLK

SM

B_ME0_DAT

SM

L1ALERT#

SM

B_ME1_CLK

SM

B_ME1_DAT

SM

AL24_IN

XT

AL24_OUT

XT

_XDP_N_R

CK

CK

_XDP_P_R

RP

*0_4P2R_4

RP1 install for XDP

K_PCI_EC_R

CL

K_PCI_LPC_R

CL

MV un-stuff

LK_BIASREF

XC

89 10K/F_4

R4

96 10K/F_4

R4

5 10K/F_4

R7

3 10K/F_4

R7

R3

82 2.2K_4

R410 2.2K_4

R4

28 2.2K_4

R3

84 2.2K_4

R379 2.2K_4

R3

85 2.2K_4

R425 10K_4

R4

30 1K_4

Size Docum ent Number Rev

Size Docum ent Number Rev

Size Docum ent Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

1

TP

82

TP

102

04 12P/50 V_4

C4

1

2

81

R4

24M

Y3

4

3

09 12P/50 V_4

C4

1

3

3 18P/50V_4

EC

5 18P/50V_4

EC

4 *18P/50V_4

EC

HZ +-30PPM

TP

103

I(near PCH)

EM

I(near PCH)

EM

CK

_XDP_N 11

CK

_XDP_P 11

CL

K_24M_KBC 25

CL

K_24M_DEBUG 23

CL

K_PCI_TPM 21

+V

1.05S_AXCK_LCPLL 10

4

00 22_4

R1

02 22_4

R1

01 *22_4

R1

R1

3.01K/F_4

1M_4

2

4

38

SMBus/Pull-up(CLG)

SM

B_PCH_CLK

SMB_PCH_DAT

SM

B_ME0_CLK

SM

B_ME0_DAT

SMB_ME1_CLK

SM

B_ME1_DAT

SML1ALERT#

SM

L0ALERT#

PROJECT :Y61

PROJECT :Y61

PROJECT :Y61

Quanta Computer Inc.

Quanta Computer Inc.

Quanta Computer Inc.

ULT 7/9 (PCIE/USB/CLK)

ULT 7/9 (PCIE/USB/CLK)

ULT 7/9 (PCIE/USB/CLK)

1

08

832Monday, April 21, 2014

832Monday, April 21, 2014

832Monday, April 21, 2014

of

of

of

1A

1A

1A

Page 9

5

TP

81

SI

SI

O_EXT_SCI#25

_OFF23

BT

RF

_OFF23

D D

C C

B B

Mo

del

13" clamshell wo/TS

13" convertible w/TS

15" convertible w/TS+

Giga NIC

clamshell w/TS

13"

(Reserve)

A A

13" convertible wo/TS

(Reserve)

15" convertible w/TS

(Reserve)

TP for DG

BT

_COMBO_EN#23

Z_SPKR17

AC

0 1

0

0

0

00

5

TP

TP

GP

IO15_ULT7

TP

TP

13

AC

CEL_INTA#22

86

TP

AC

CEL_INTH#24

HY_PWREN32

MP

SPKR7

0

00

0

0

O_EXT_SCI#

BT

72

92

95

TP

_OFF

_OFF

RF

LA

N_DISABLE#

IO13_ULT

GP

GP

IO14_ULT

16

TP

D_PRSNT# _R

OD

15

TP

IO24_ULT

GP

IO25_ULT

GP

GP

IO26_ULT

W_WAKE#

DS

IO28_ULT

GP

VSLP0

DE

VSLP1

DE

87

DE

VSLP2

GP

IO44_ULT

ARD_ID4

BO

AC

CEL_INTA#

ARD_ID5

BO

BT

_COMBO_EN#

AC

CEL_INTH#

ESB_R

XR

TP