Page 1

THIS DRAWING AND SPECIFICATIONS, HEREIN, ARE THE PROPERTY OF INVENTEC

CORPORATION AND SHALL NOT BE REPODUCED, COPIED, OR USED IN WHOLE OR

IN PART AS THE BASIS FOR THE MANUFACTURE OR SALE OF ITEMS WITHOUT

WRITTEN PERMISSION, INVENTEC CORPORATION 2009 ALL RIGHT RESERVED

DATE

AMD DANUBE PLATFORM

CHANGE NO.

REV

SI - R Build

U811 Hynix DDR3 6019B0647101

R1206 Install , R1186 Open

U811 Samsung DDR3 6019B0648501

R1206 Open , R1186 Install

U805 Change to 6019B0653601

CN804 Change to 6026B0184301

CN807 Change to 6026B0184301

CN808 Change to 6026B0121002

DRAWER

DESIGN

CHECK

RESPONSIBLE

SIZE =

FILE NAME :

P/N

XXXXXXXXXXXX

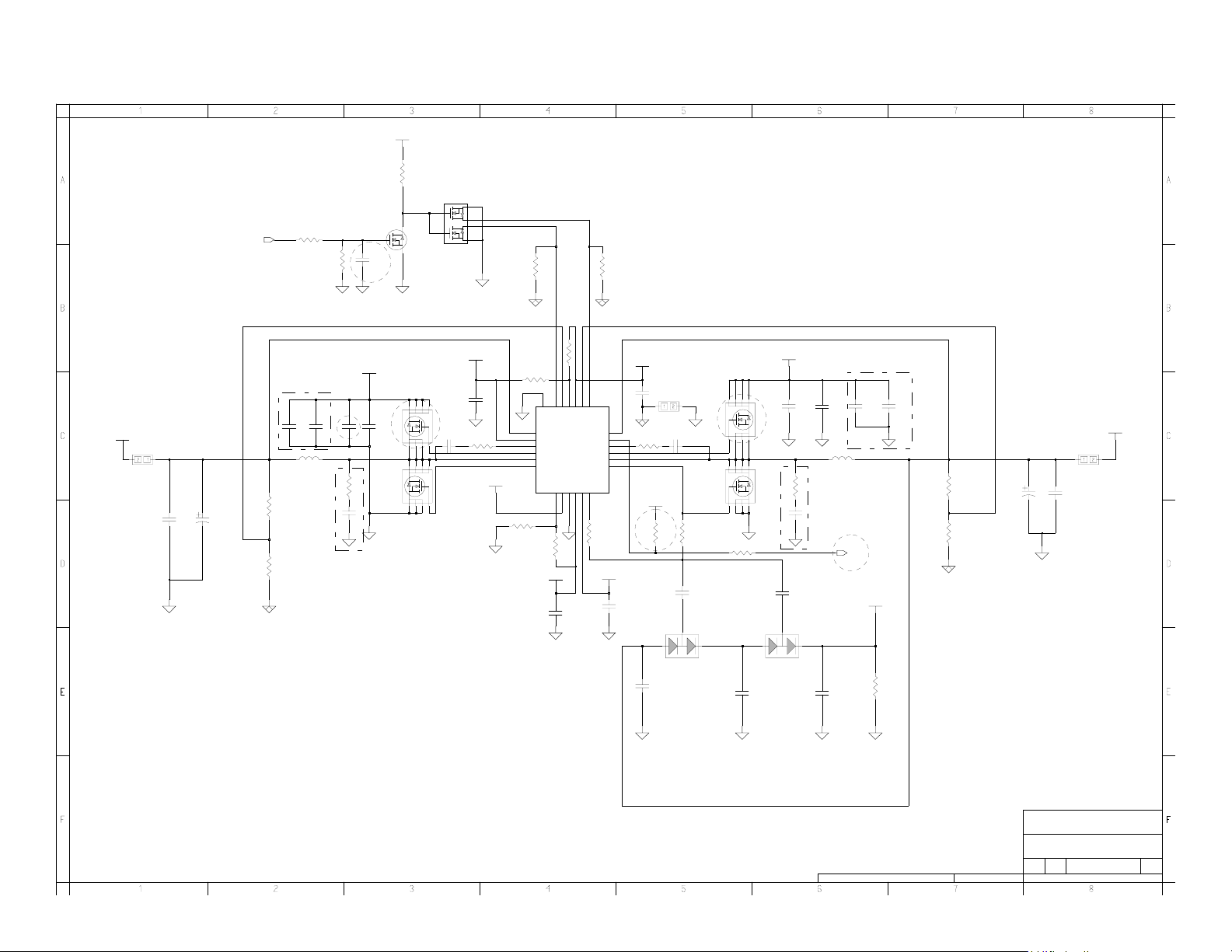

EE POWER

3

XXXX-XXXXXX-XX

2009/12/21

DATE

VER :

DATE

TITLE

SIZE

A3

INVENTEC

ST145a-UMA

Project Name

DOC. NUMBER REV

CODE

Model_No X01

CS

SHEET

511

OF

Page 2

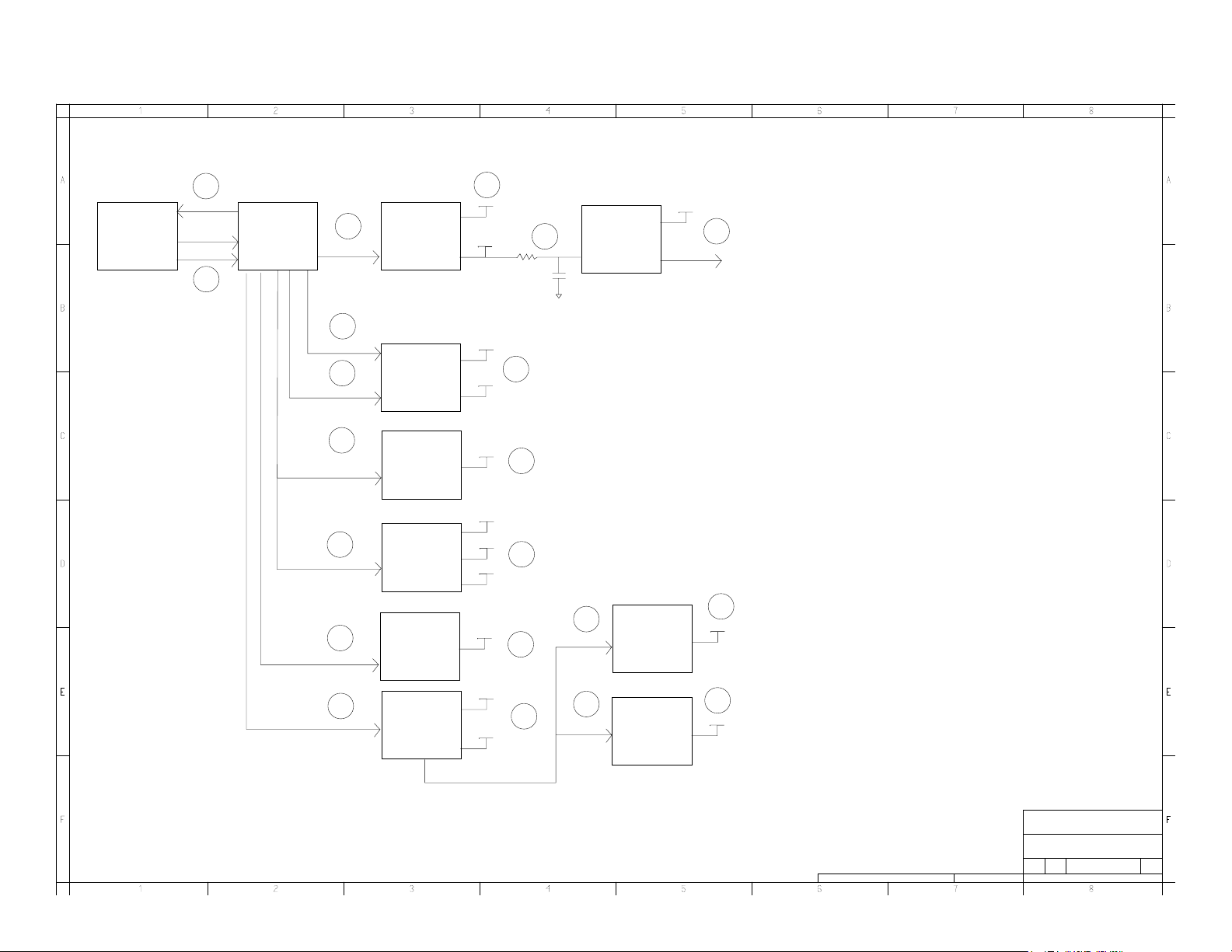

Index Of Content

PAGE

01- Project Name

02- Index

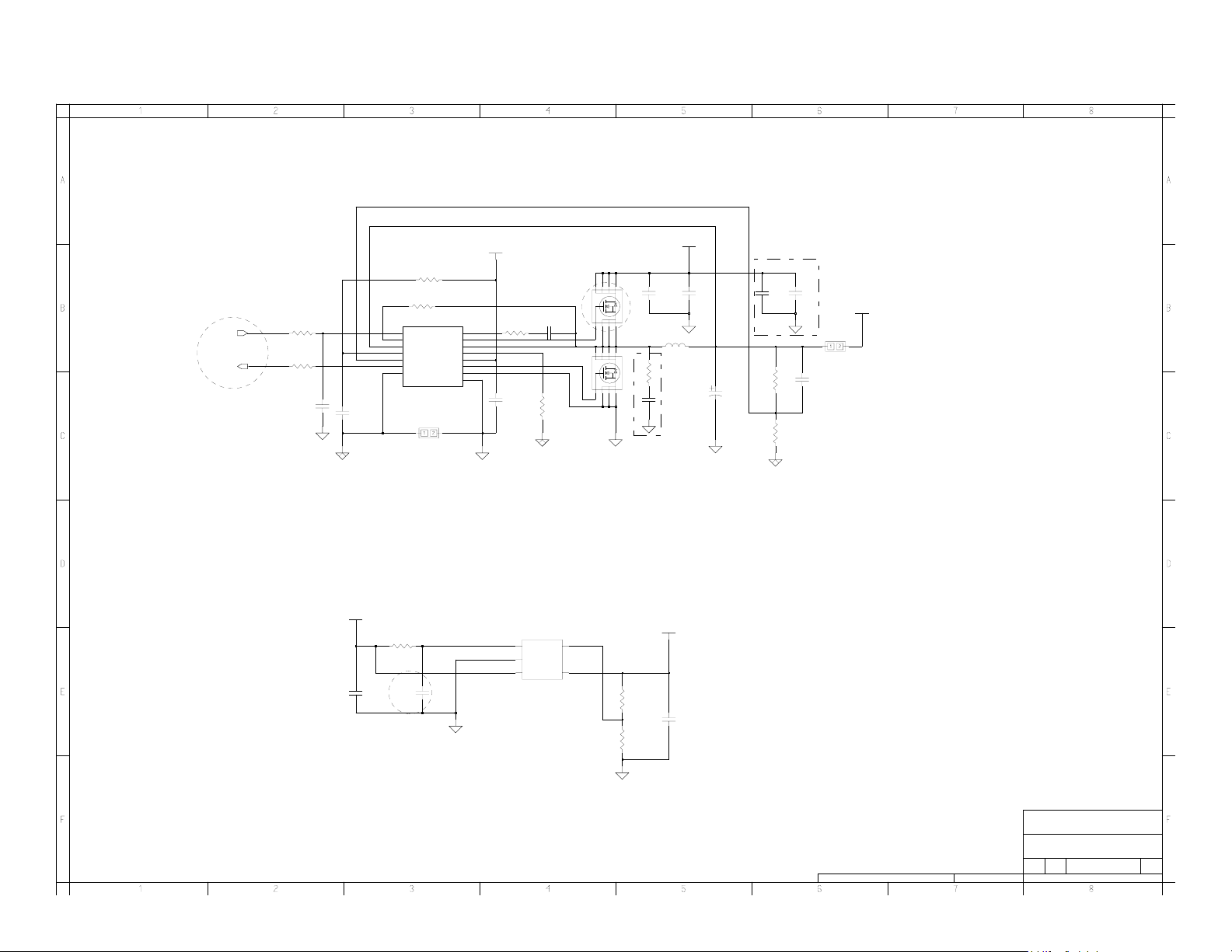

03- Block Diagram

04- Power Procedure

05- NOTE

06- DC & BATTERY CHARGER

07- BATTERY CONN

08- +V5A & +V3A & +V2.5S

09- +V1.2A & +VCC_NB

10- +VCC_CORE & +VCC_CORE_NB

11- +V1.1S & +V1.1A & +V1.05S

12- NOTE

13- +V1.5 & +V1.8S

14- POWER (SLEEP)

15- CLK GEN-RTM880N

16- CPU-1

17- CPU-2

18- CPU-3

19- CPU-4

20- FAN & THERMAL IC

21- RS880M-1

22- RS880M-2

23- RS880M-3

PAGE

24- RS880M-4

25- DDR3 DIMM0

26- DDR3 DIMM1

27- DDR3 SIDE-PORT

28- SB820M-1

29- SB820M-2

30- SB820M-3

31- SB820M-4

32- SB820M-5

33- CRT

34- NOTE

35- LCM

36- HDMI

37- KBC

38- Keyboard CONN & Indicate LED

39- Card reader

40- SATA HDD & SATA ODD CONN

41- Touch screen & FingerPrint CONN

42- ESATA CONN & USB Board CONN

43- LAN

44- RJ45 CONN

45- AUDIO CODEC & SPEAKER CONN

46- HP JACK & MIC JACK

47- NOTE

48- WLAN & BLUETOOTH

49- WWAN

PAGE

50- NOTE

51- USB BOARD & BUTTON BOARD

52- HDD Board & ODD Board

CHANGE by

ALAN W 27-Jul-2009

INVENTEC

TITLE

ST145a-UMA

Index

DOC. NUMBERSIZE

CODE

A3

Model_No X01

CS

SHEET

OF

REV

512

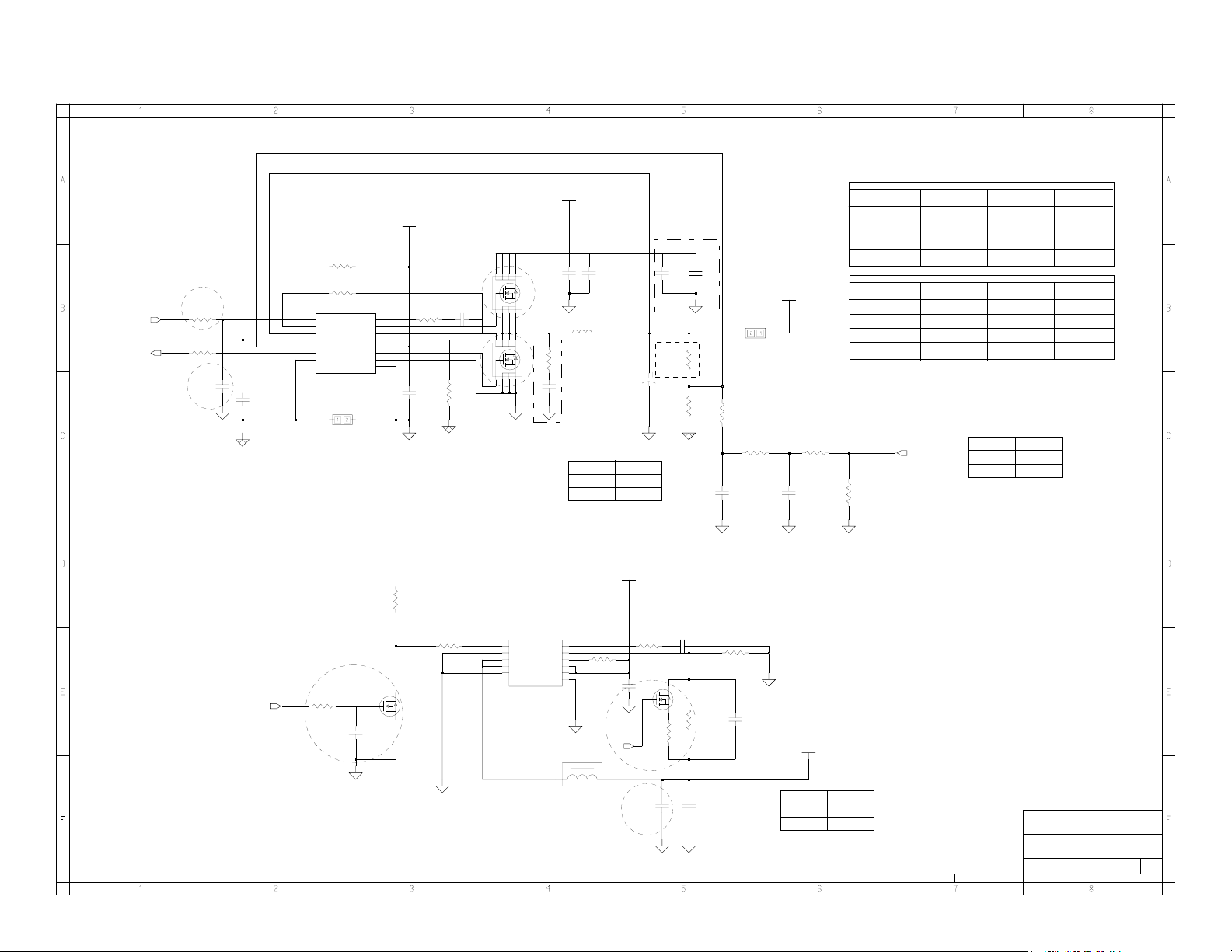

Page 3

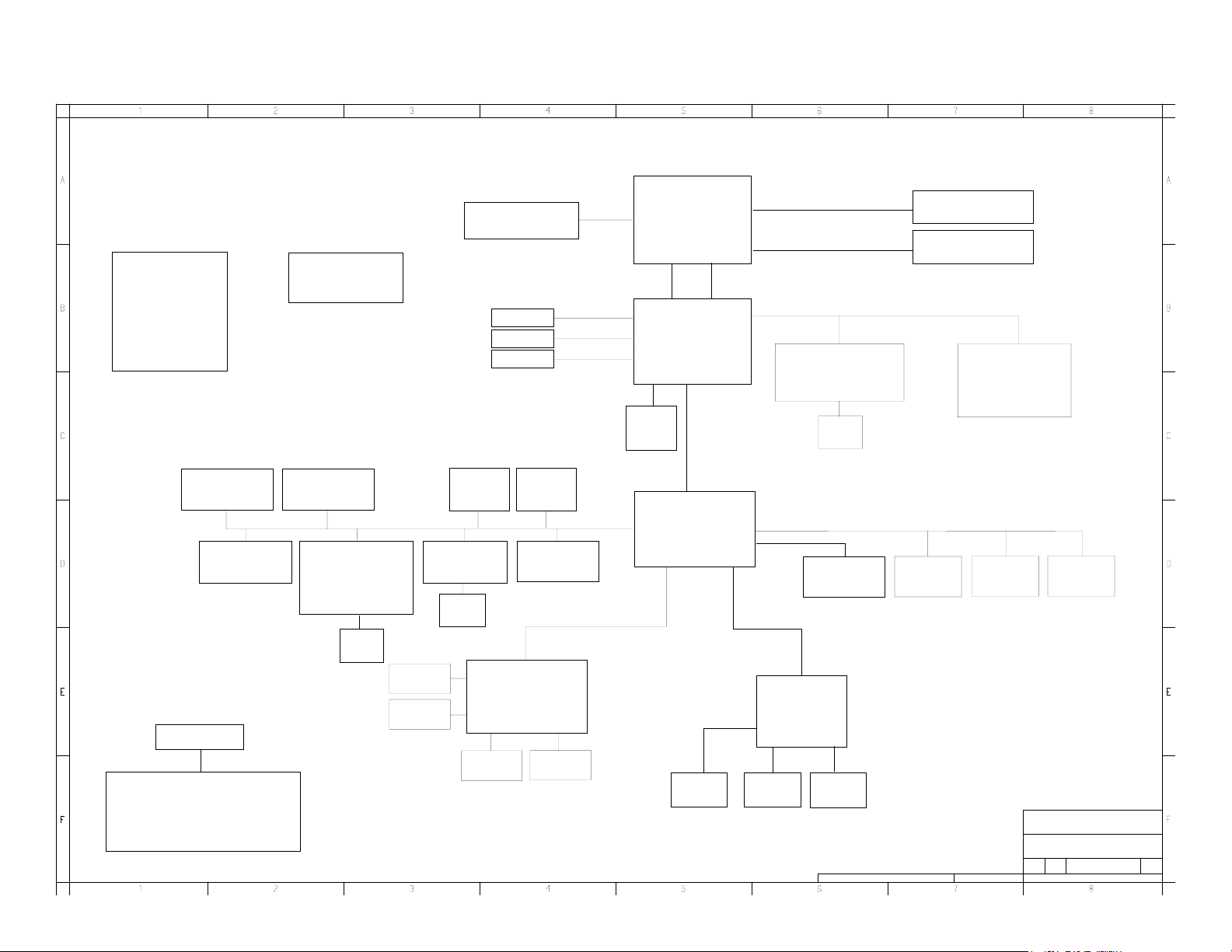

Inventec Confidential

PCB STACK UP

LAYER 1 : TOP

LAYER 2 : GND

LAYER 3 : IN1

LAYER 4 : IN2

LAYER 5 : VCC

LAYER 6 : BOT

FINGER PRINT

TOUCH SCREEN

MAIN BATT

P.07

System Charger &

DC/DC System power

USB_6

CLK GEN

REA-RTM880N-796

WEB CAM

P.42

USB_7

P.42

P.06

P.16

USB_4

P.36

USB_8

MINI CARD

CONN

(WWAN)

SIMCARD

CONN

P.50

CARD READER

P.50

Speaker

DMIC

P.47

P.36

Thermal Sensor

HDMI

LCM

VGA

USB_3

USB2 CONN

(DB)

P.50

USB_1

AU6433

5 in 1

Conn

P.40

P.40

AUDIO CODEC

IDT 92HD80B1

HP JACK

P.47

P.20

P.37

P.36

P.35

USB_2

USB1 CONN

(DB)

P.50

BLUE TOOTH

MIC JACK

USB_2

P.47

P.47

TMDS

LVDS

CRT

USB2.0

P.49

638 P(PGA) 45W/35W

Side-port

Memory

128MB

HDA

AMD

Champlain

S1G4 Processor

35mm X 35mm

Transport 3

P.16~19

Hyper

P.21~24

AMD

RS880M

A12

21mm X 21mm, 528pin BGA

DDR3

P.26

A-link X 4

P.29~33

AMD

SB820M

21mm X 21mm, 528pin BGA

A12

4.5W (Ext)

4.3W (Int)

Keyboard

P.39

DDR3

DDR3

PCI_EXPRESS

REALTEK

GIGA RTL8111DL-VB-GR

SATA

SMBus

Accelerometer

LPC

KBC

ITE 8502E-KX

TouchPad

SYSTEM

P.39

CHANGE by OF

X1

LAN

RJ45

P.38

SPI

BIOS

channel A

channel B

PCIE_0

P.44

P.40

P.38

DDR III _SODIMM0

DDR III _SODIMM1

P.43

HDD

ALAN W 29-Nov-2009

Half MINI CARD

SATA_0

P.40

P.27

P.28

X1

PCIE_1 USB_8

CONN

(WLAN)

SATA_1

ODD

P.40

TITLE

SIZE

A3

P.48

SATA_2

USB_0

ESATA

P.42

INVENTEC

ST145a-UMA

Block Diagram

DOC. NUMBER

CODE

Model_No X01

CS

SHEET

513

REV

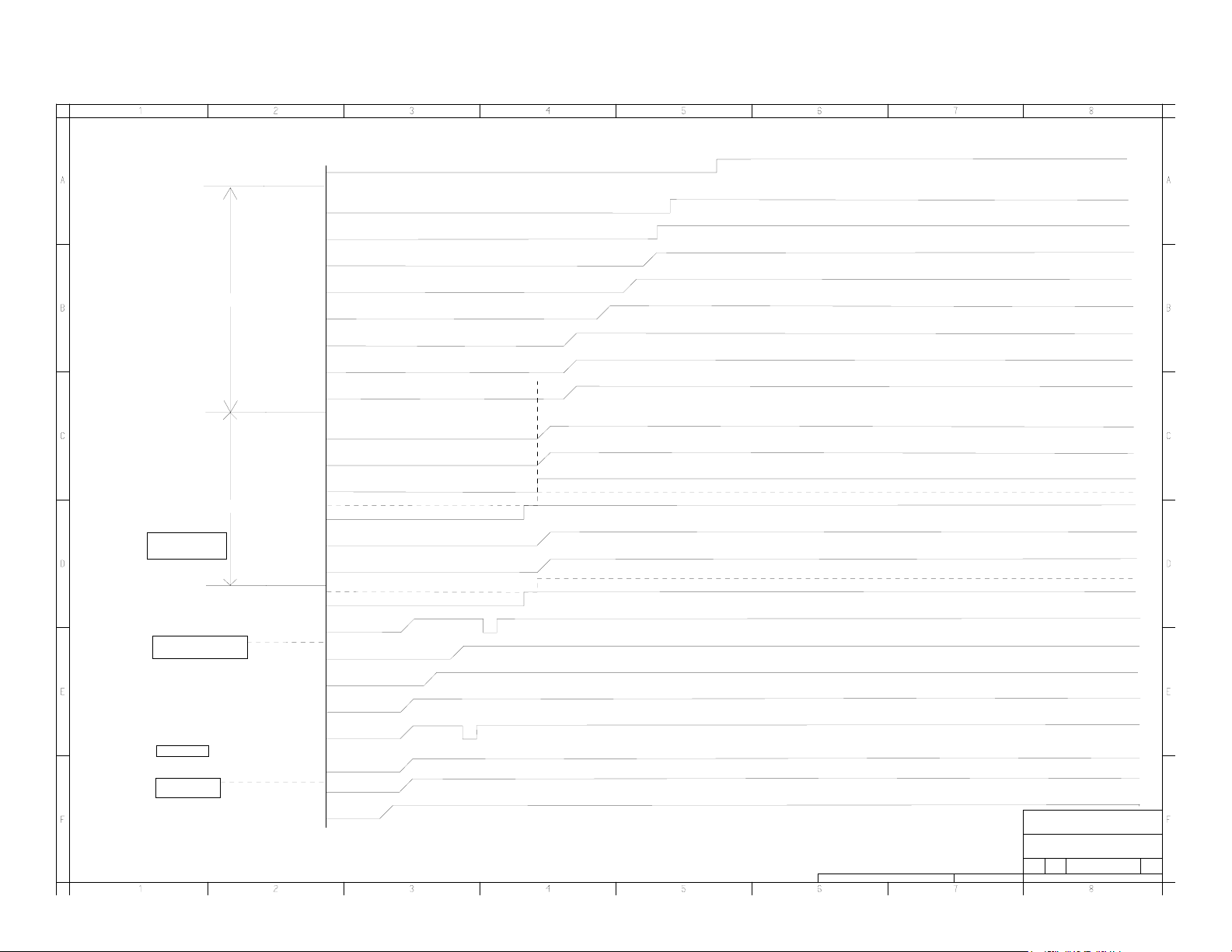

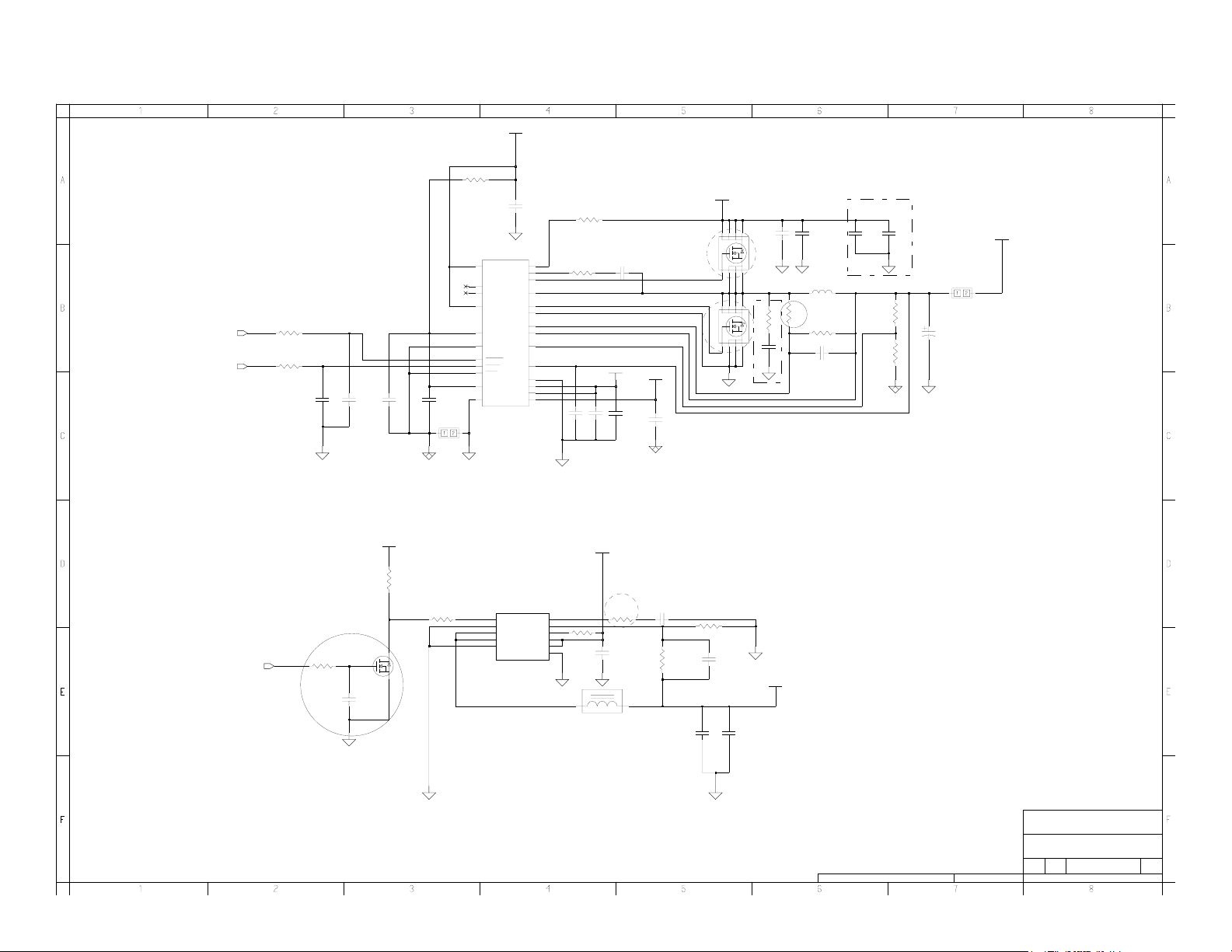

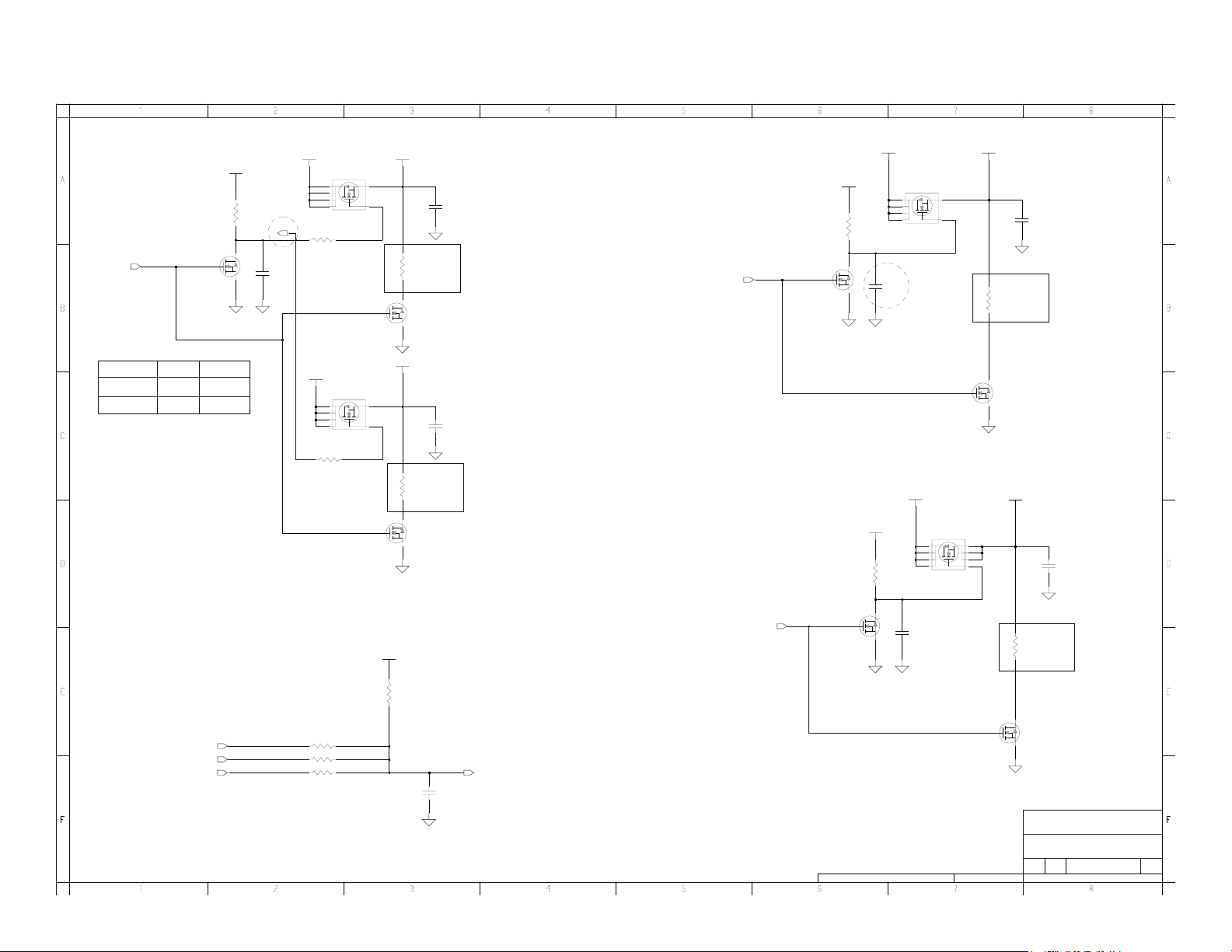

Page 4

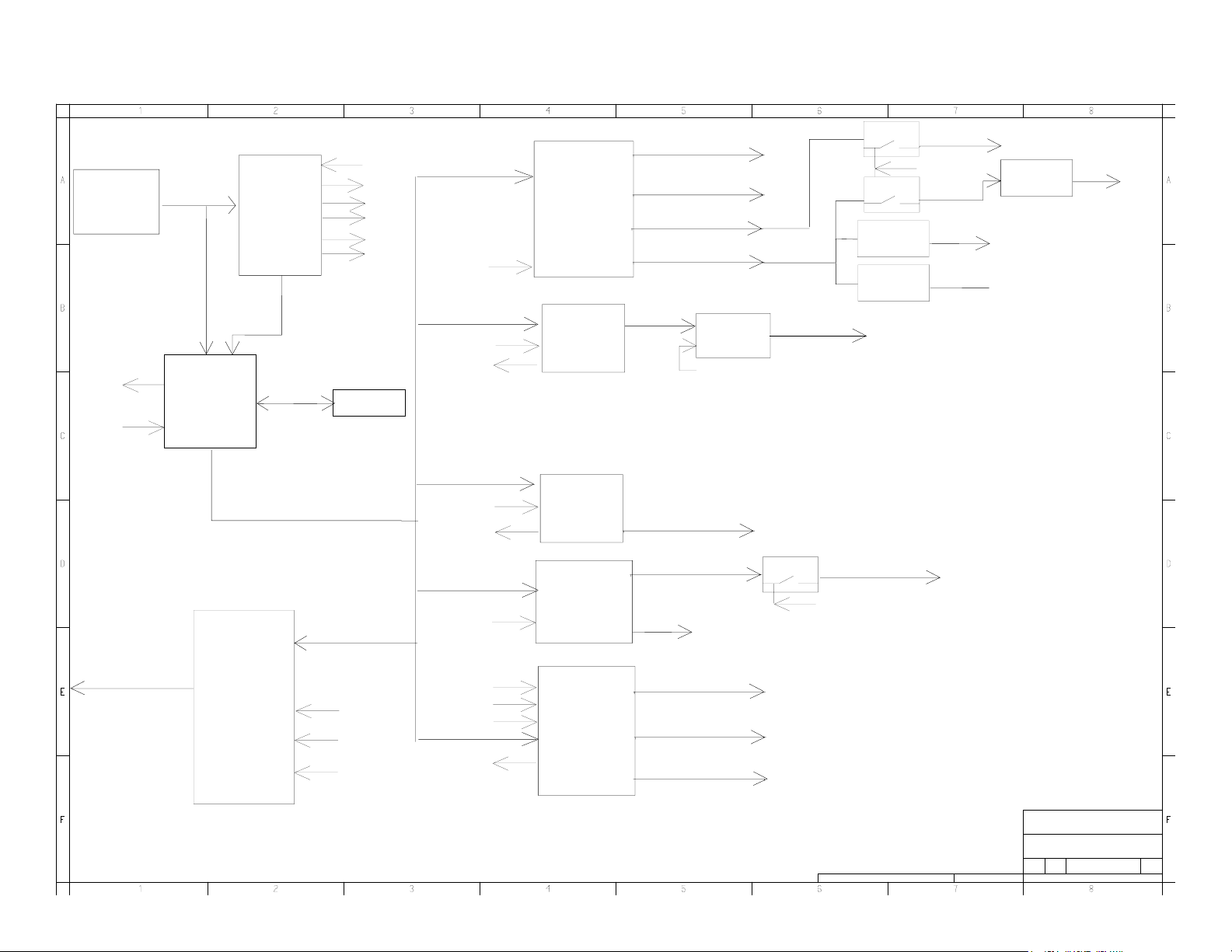

Adapter

(65W)

ADP_PRES

CHGCTRL_3

Selector

(Discrete)

Charger

(BQ24721C)

+VBDC

+VBADC

+VBATR

CHGCTRL_3

I_ADP

BATT_CLK

BATT_DATA

ADP_IP

ACOK

Main Battery

ALWAYS_EN

+V5A

+V1.2A_PG

VRM_PWRGD

VCC_NB_PG

RESUME_PWEN

5V/3.3V

(TPS51125)

+V1.1A

(TPS51117)

NB POWER

I/O POWER

(TPS51117)

DDR POWER

(Max17000ETG)

I = 0.02A

I = 0.05A

I = 8.6A

I = 9.593A

I = 7.42A

+V1.1A

+V0.75S

I = 1A

APL5610C

VRM_PWRGD

+VCC_NB

I = 9A

+V1.5

+V5AL

+V3AL

+V5A

+V3A

I = 7.6A

AM3402N

+V1.1S

CORE_PWEN#

AM3402N

CORE_PWEN#

AM3402N

CPU_VDDR

RT8015AP

+V1.8S

RT8015AP

I = 6.8A

+V1.5S

+V5S

I = 2.53A

+V3S

CPU_VDDR

I = 1.5A

+V1.8S

I = 1.3A

I = 1.23A

I = 2.6A

+V2.5S

(APL5315)

+V2.5S

I = 0.25A

+VDD_CORE

VGA POWER

(TPS51511)

VGAVCC_EN

VPCIE_SW

POW_SW1

SVC

SVD

CPU_PWEN

VRM_PWRGD

AMD Griff

MAX17480

+VDD_CORE

+VDD_CORE

+VDDNB_CORE

I = 38A

I = 4A

CHANGE by

INVENTEC

TITLE

ST145a-UMA

Power Procedure

CODE

CS

SHEET

DOC. NUMBER

REV

451

X01Model_No

OF

SIZE

10-Aug-2009ALAN W

A3

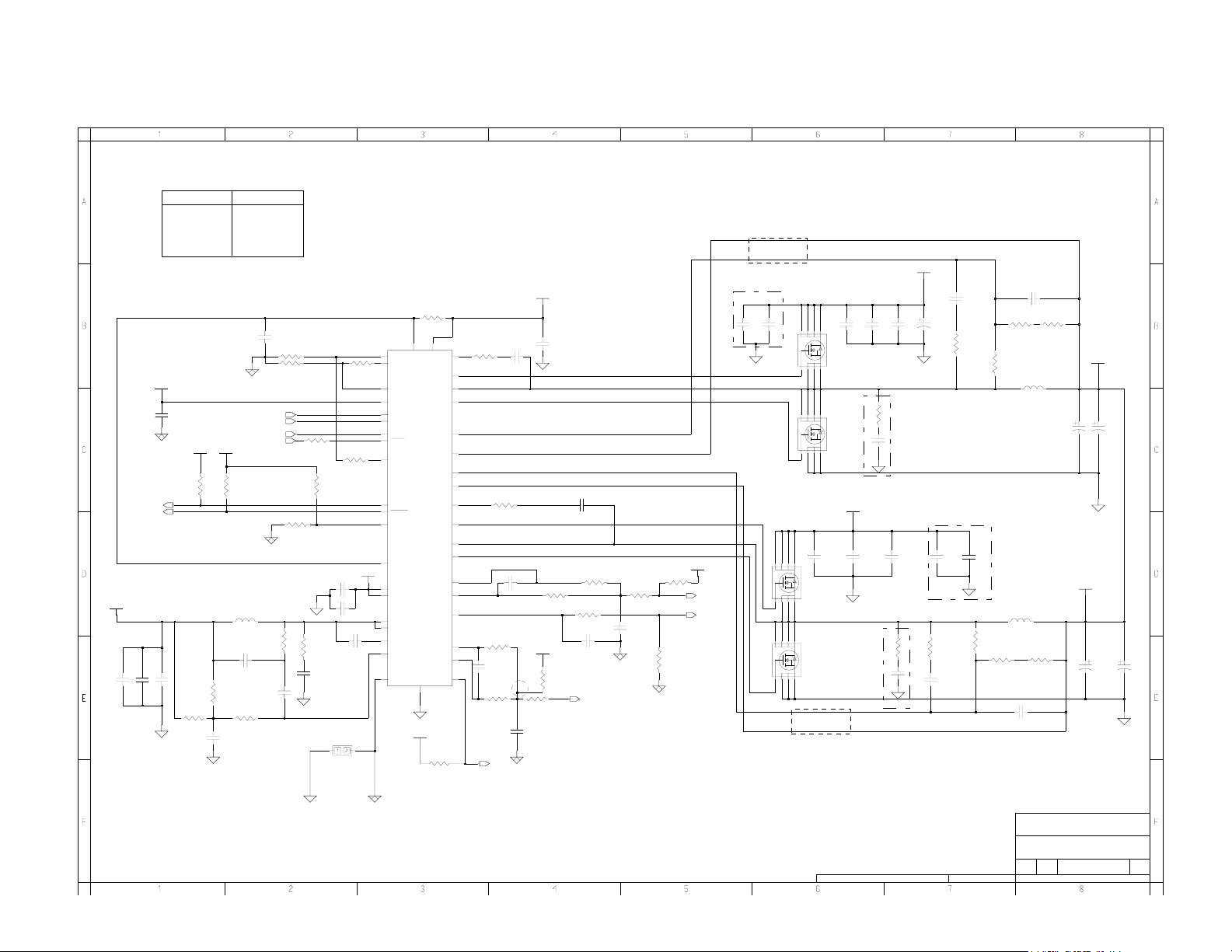

Page 5

SB800

3

SB_PWRBTN#

SLP_S3#

SLP_S5#

4

KBC

ITE8502E

1

ALWAYS_PW_EN

5

CORE_PWEN

5

RESUME_PWEN

TPS51125

MAX 17000E

2

+V3A

+V5A

+V1.5

+V0.75S

+V1.1A

2

TPS51117

3

V1.1A_PG

6

5

CORE_PWEN#

5

CORE_PWEN#

7

CORE_PWEN_D#

7

CPU_PWEN

RT8015A

MOSFET

SWITCH

RT8015A

MAX 17480G

+V1.8S

+V5S

+V3.3S

+V1.5S

CPU_VDDR

VDD_CORE

VDDNB_CORE

6

6

10

9

VRM_PWRGD

8

8

VRM_PWRGD

TPS51117

9

MOSFET

VCC_NB

10

+V1.1S

SWITCH

INVENTEC

TITLE

ST145a-UMA

Power Sequence

CHANGE by

ALAN W 13-Aug-2009

SIZE

A3

CODE

CS

SHEET

DOC. NUMBER

Model_No X01

REV

515

OF

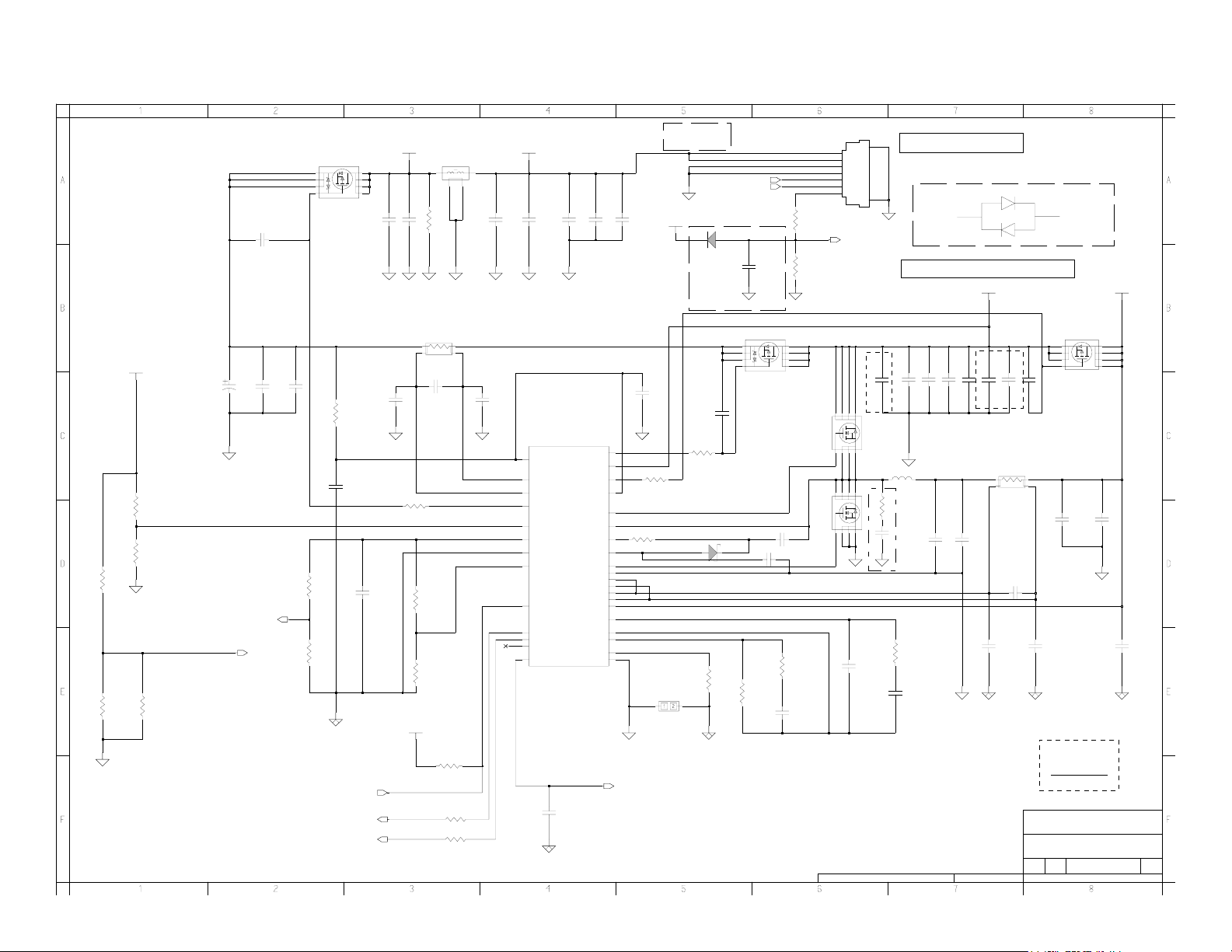

Page 6

POWER ON SEQUENCW REQUIRED.

SB820M

1. +V3.3A RAMP BEFORE +V1.1A

2. +V3.3S RAMP BEFORE +V1.8S

3. +V1.8S RAMP BEFORE +V1.1S

4. +V3.3S RAMP BEFORE +V1.1S

5. VDDIO_33_S RAMPING DOWN TIME <= 300uS

6. 50uS <= ALL POWER RAILS EXPECT VDDIO_33_S <= 40mS

7. 100uS <= VDDIO_33_S <= 40mS

RS880M

1. 0 <(+V3.3S) - (+V1.8S) < 2.1

2. +V1.8S RAMP BEFORE +V1.1S

3. +V1.1S RAMP BEFORE VCC_NB

SB_PWRGD

ALL_PWGD_IN

VCC_NB_PG

VCC_NB

10mS

GROUP B

GROUP A

CPU MEM CTL &

DDR3_SODIMM PWRS

CPU_THM/SB/SB_SCL1/2

SB_KB/SPI/LPC ROM PWRS

KBC IS READY

KBC IS POWERED

BY +V3AL

+V1.1S/+VLDT

VRM_PWRGD

CPU_VDDR

VDD_CORE

VDDNB_CORE

+V2.5S

(CPU_VDDA_2.5_RUN)

+V1.8S

+V3S/+V5S/+V1.5S

CORE_PWEN

SLP_S3#

M_VREF/+0.75S

+V1.5

(CPU_VDDIO_SUS)

RESUME_PWEN

SLP_S5#

SB_PWRBTN#

RSMRST#

DUAL RAILS

ALWAYS_PW_EN

EC_PWRBTN#

AC_OK

(AC_IN DETECT)

+V3AL/+V5AL

5ms

POWER BUTTON PRESSED

+VIN/+19V

CHANGE by

ALAN W 17-Aug-2009

INVENTEC

TITLE

ST145a-UMA

CPU_VDDR & +V1.1A & +V1.1S

CODE

SIZE

A3

DOC. NUMBER

Model_No X01

CS

SHEET

OF

REV

516

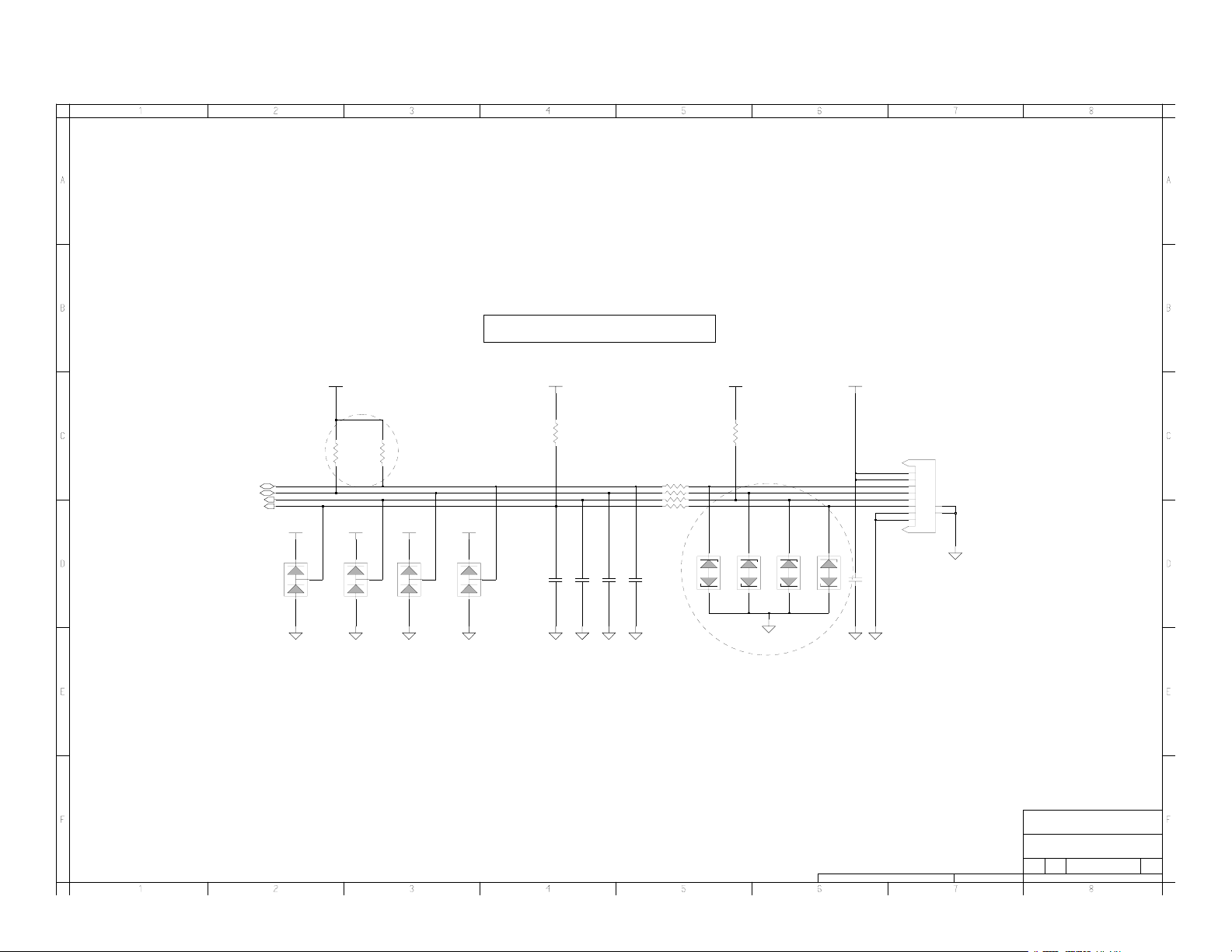

Page 7

R849

1

100K_1%

2

R847

1

26.7K_1%

2

+VADP

7-

PWR-E

R848

1

200K_1%

2

R845

1

24.3K_1%

2

DGND

R846

1

26.7K_1%

2

DGND

SINGA_2WA1554_107111_7P

DGND

PWR-A

PWR-A

PWR-A

1

R841

1K_1%

2

R842

1

13.7K_1%

2

DGND

Q815

FDMC8884

CN802

G1

AC IN_90W_5A

G

1

1

2

2

3

3

4

4

5

5

6

6

7

7

G2

G

37-

ADP_ID

N

E

P

1

V

5

O

5

8

_

2

1

1

C

V

_

0

F

5

u

_

2

1

2

F

.

0

p

0

0

2

2

RF

765

8

D

Q809

G

FDMC8884

S

4

123

L803

PWR-B

12

PCMB103T_8R2MS

8765

N

1

E

9

D

9

OP

8

_

G

2

R

0

4

2

0

N

E

1

PWR-B

OP

5

RF

_

41S23

CHANGE by

2

0

2

9

0

C817

C

4

0

DGND

1

2

4.7uF_25v

R850

1

10K_5%

2

C847

56pF_50v

C846

1

0.0015uF_50V

2

CELLSEL#=0,Vcharger=12.6V

CELLSEL#=1,Vcharger=16.8V

ALAN W 27-Jul-2009

AMBER

AC_LED

CN539 Pin6

WHITE

9 cell_2.8AHr_93W_8.78A

+VBATR

9-,10-,11-,12-,13-,35-,47-

PWR-A

1

2

7

5

2

5

5

5

v

v

8

8

8

5

5

C

C

2

C

2

1

1

_

_

F

F

u

u

7

7

.

2

2

.

4

4

DGND

PWR-E

1

2

Icharger=3A

v

5

2

1

_

F

u

7

2

.

4

1

2

C860

4.7uF_25v

3

5

8

C

CHARGE_GND

2

1

N

N

1

1

E

E

4

4

P

P

1

1

O

O

C

C

1

1

_

_

V

V

0

0

5

5

2

2

_

_

F

F

p

p

3

3

3

3

RF

R852

12

34

0.01_1%

C900

0.1uF_16v

1

C901

1

2

0.1uF_25V

3

1

2

C814

0.1uF_16V

1

2

DGND

2

C899

1

2

PWR-A

0.1uF_25V

CHARGE_GND

Note:

high power trace

INVENTEC

TITLE

ST145a-UMA

DC & BATTERY CHARGER

CODE

SIZE

A3

CS

SHEET

CHG_LED#

CN539 Pin5

Q801

S

G

AM7331P

C816

C859

4.7uF_25v

4.7uF_25v

0.1uF_25V

DOC. NUMBER

Model_No

D

1

2

C898

+VBDC

8

7

6

54

1

2

PWR-A

CHARGE_GND

OF

8-

PWR-E

517

REV

X01

AC IN

+V3AL

7-,8-,9-,29-,37-

PWR-B

1SS355W

D800

21

PWR-A

AMBER#

WHITE#

1

2

3838-

C843

0.0015uF_50V

DGND

PWR-E

C842

0603_OPEN

PWR-A

12

ANALOG_AM7333P_POWER33_8P

Q808

D8

1S

2

7

3

4

PWR-E

6

5

G

DGND

C838

10pF_50v

1

2

DGND

+VADP

7-

1

2

0.1uF_25V

C836

DGND

L802

NFM60R30T222

12

3

4

DGND

1

R837

15K_5%

2

+VADPTR

1

2

C837

10pF_50v

+VADPTR

1

2

DGNDDGND

PWR-E

C839

0.1uF_25V

C811

1uF_25v

1

2

1

2

DGND

C834

C835

0.1uF_25V

0.1uF_25V

1

2

prevent KBC latchup

1

2

D804

13

R896

1

33K_5%

2

Q800

D

S

8

1

2

7

3

6

5

4

G

ANALOG_AM7333P_POWER33_8P

PWR-B

C904

0.1uF_16v

1

2

12

C903

1uF_25v

1

R843

18K_5%

2

R844

1

200K_5%

2

1

C845

2

100pF_50v

SYS

PH

SRP

SRN

BAT

EAO

EAI

FBO

TML

DGND

PWR-A

2

23

24

32

30

29

PWR-A

12

31

PWR-A

28

27

26

DGND

22

21

20

19

18

7

8

9

16

33

PWR-E

C90212

0.1uF_25V

R904

PWR-A

12

1K_5%

R898

0_5%

PWR-A

PWR-A

PWR-A

PWR-A

DGND

C812

0.1uF_16V

R901

12

1K_5%

PWR-A

BAT54_30V_0.2A

PWR-A

PWR-A

R840

2

1

34

0.01_1%

1

C844

C841

C840

1

1

2

DGND

AC_OK

0.1uF_25V

2

0.1uF_25V

37-

PWR-A

R892

1

47K_5%

PWR-A

2

R890

1

100K_5%

2

R889

1

20_5%

2

C896

1

2

0.47uF_25V

C848

0.1uF_25V

DGND

C895

1

1uF_10v

2

2

33uF_25v

ADP_PRES

37-

PWR-APWR-A

1

2

R897

12

1K_5%

PWR-A

12

C849

0.1uF_16v

1

R891

100K_1%

2

PWR-A

1

R895

100K_1%

2

1

C850

2

0.1uF_25V

DGND

PWR-A

PWR-A

12

11

10

15

14

13

25

17

U802

VCC

3

ACN

4

ACP

6

BYPASS#

5

ACDET

VREF5

AGND

TS

1

CHGEN#

SCL

SDA

ALARM#

IOUT

TI_BQ24721C_QFN_32P

PWR-E

A

R

W

P

ACDRV#

BATDRV#

PVCC

HIDRV

BTST

REGN

LODRV

PGND

SYNP

SYNN

ISYNSET

PAD5001

POWERPAD1x1m

CHARGE_GND

I_ADP

CHARGE_GND

BATT_CLK

BATT_DAT

CHG_EN#

PWR-A

37-

8-,37-

8-,37-

PWR-B

+V3AL

7-,8-,9-,29-,37-

SMBUS

SMBUS

R851

12

200K_5%

R894

12

10_5%

R893

12

10_5%

PWR-A

PWR-A

PWR-A

CHARGE_GND

1

2

PWR-A

C897

0.1uF_10V

37-

Page 8

9cell_2.8AHr_93W_8.78A

BATT_DAT

BATT_CLK

BATT_ID

BATT_A_IN#

7-,377-,373737-

7-,8-,9-,29-,37-

+V3AL

9

9

V

A

PWR-B

B

_

O

K

M

N

E

H

C

DGND

+VBDC

7-

CN800

1

1

2

2

3

3

4

4

5

5

G1

6

G

6

G2

7

G

7

8

P

2

_

3

2

5

D

O

S

1

_

4

3

B

0

0

B

9

9

1

D

D

S

0

V

1

5

D

S

E

2

P

2

_

C815

P

0.1uF_25V

H

P

DGND

DGND

8

FOX_BP02083_B69B5_7H_8P

DGND

INVENTEC

TITLE

ST145a-UMA

BATTERY CONN

CODE

CS

SHEET OFCHANGE by

DOC. NUMBER REV

851

X01Model_No

SIZE

27-Jul-2009ALAN W

A3

PWR-B

DGND

+V3AL

3

1

1

8

C

2

7-,8-,9-,29-,37-

1

R1400

100K_5%

2

N

E

P

O

_

2

0

4

0

12

R807

1

R805

R803

1

R801

1

4

6

V

5

0

8

5

C

1

_

F

p

2

0

0

1

DGND

8

V

V

5

5

0

0

8

8

5

5

C

C

1

1

_

_

F

F

p

p

2

2

0

0

0

0

1

1

DGND

+V3AL

7-,8-,9-,29-,37- 7-,8-,9-,29-,37-

PWR-B

2009/10/14

1

1

R806

R802

2.2K_5%

2.2K_5%

2

2

7-,8-,9-,29-,37-

+V3AL

1

2

1

9

9

V

3

A

PWR-B

B

_

0

0

O

9

K

D

2

M

N

E

H

C

DGND

+V3AL

9

9

V

3

A

B

_

1

0

O

8

K

2

D

M

N

E

H

DGND

C

7-,8-,9-,29-,37-7-,8-,9-,29-,37-

+V3AL

1

3

1

PWR-B

9

9

V

3

A

B

DGND

3

_

0

8

O

D

K

2

M

N

E

H

C

2

0

8

D

+V3AL

PWR-B

1

R804

100K_5%

2

100_5%

100_5%

2

100_5%

2

PWR-A

2

100_5%

P

2

_

3

2

5

D

O

S

_

B

B

1

S

0

V

5

D

S

E

P

_

P

H

P

PWR-A

P

P

2

2

_

_

3

3

2

2

5

5

D

D

O

O

S

S

1

_

1

B

0

B

9

1

D

S

0

V

5

D

S

E

P

2

_

P

H

P

DGND

1

1

_

2

B

0

B

9

1

D

S

0

V

5

D

S

E

P

2

2

_

P

H

P

2009/11/26

Page 9

Typ@9.6A

+V3A OCP = 6.2A

Vout=(R1266/R1267+1)*2

+V3A

11-,13-,14-,18-,29-,30-,31-, 32-,33-,35-,40-,41-,43-,47-,48-

PAD804

POWERPAD_2_0610

C1333

10uF_6.3V

1

2

ALWAYS_PW_EN

1

C1359

DGND

330uF_6.3V

2

37-

RF

PCMC063T_3R3MN

1

R1266

6.8K_1%

2

1

R1267

10K_1%

2

PWR-A

51125GND

R1262

12

0_5%

R1261

10K_5%

DGND

7-,9-,10-,11-,12-,13-,35-,47-

N

E

4

5

P

7

7

O

3

3

_

1

1

V

C

C

1

1

0

5

_

2

2

F

p

0

0

2

2

L851

12

N

E

2009/12/21

OP

_

V

5

2

_

F

u

C2000

1

.

4.7uF_25v

0

1

2

PWR-C

1

2

N

E

OP

_

2

0

4

0

N

E

OP

_

2

0

4

0

RF

R1305

100K_5%

Q840

SSM3K7002FU

1

C1327

1

2

0.1uF_16V

DGND

2009/11/07

+VBATR

8/14

1

AON7410

2

C1380

4.7uF_25v

1

1

2

3

1

SI7716ADN_T1_GE3

R

2

1

0

0

2

4

1

C

+V5AL

PWR-A

9-

1

2

3

D

G

S

2

DGND

Typ@0.05A

D

Q850

S

D

Q851

S

PWR-A

8

123

765

8

12

765

G

G

DGND

3

4

4

U825

1

S1

2

G1

6

D1

3

D2

5

G2

4

S2

2N7002DW

+V3AL

7-,8-,9-,29-,37-

C1358

1

10uF_6.3V

DGND

2

C1357

0.1uF_16V

R1311

12

PWR-C

0_5%

12

RICH_RT8205EGQW_WQFN_24P

9-

7-,9-,10-,11-,12-,13-,35-,47-

DGND

2VREF

R1268

95.3K_1%

51125GND

R1308

12

0402_OPEN

DGND

7

8

PWR-C

PWR-C

10

11

PWR-C

R1309

12

330K_5%

R1310

1M_5%

C1356

4.7uF_25v

PWR-A

1

2

VREG3

BOOT2

PHASE2

LGATE2

PWR-A

1

R1263

90.9K_1%

2

PWR-APWR-A

51125GND

R1306

0_5%

1

1

2

1

P

I

R

T

N

E

VOUT1VOUT2

BOOT1

C

N

8

7

1

1

R1301

1

0402_OPEN

2

+V5AL+VBATR

1

2

2VREF

9-

C1328

1

PWR-A

2

51125GND

24

23

R1304

12

229

PWR-C

21

0_5%

20

1912

PWR-C

2009/11/07

+V3AL

Typ@0.02A

9-

C1355

10uF_6.3V

DGND

CHENMKO_BAV99

0.22uF_6.3v

POWERPAD1x1m

PAD5002

C1354

PWR-C

12

7-,8-,9-,29-,37-

1

%

0

5

1

_

5

K

1

0

R

0

2

1

1

2

2

0.1uF_16V

R1303

1

0_5%

2

C1352

0.1uF_16V

3

CHENMKO_BAV99

1

8/14

PWR-C

2

5

2

3

4

6

5

1

2

2

D

F

L

P

E

E

B

B

N

I

F

F

S

R

G

R

N

T

O

N

T

E

PGOOD

U826

UGATE1UGATE2

PHASE1

LGATE1

L

E

5

S

G

P

D

E

I

N

N

R

I

N

K

G

V

V

E

S

5

6

3

4

1

1

1

1

D

N

G

D

1

2

1

DGND

2

D826

C1350

1

2

0.1uF_25V

DGND DGND DGND DGND

8765

D

Q848

G

AON7410

41S23

765

8

D

Q849

G

SI7716ADN_T1_GE3

41S23

DGND

R1302

12

0_5%

2

C1349

1

2

0.1uF_25V

+VBATR

7-,9-,10-,11-,12-,13-,35-,47-

C1379

1

2

4.7uF_25v

DGND

PWR-C

N

E

OP

_

2

0

4

0

N

E

1

OP

_

2

2

0

4

0

DGNDDGND

C1353

1

2

0.1uF_16V

3

1

D825

C1378

1

2

4.7uF_25v

DGND

L850

12

PCMC063T_3R3MN

1

8

3

3

1

R

2

9

9

3

1

C

RF

10-

2009/11/07

C1351

1

2

1uF_25V

N

E

7

7

3

OP

1

_

V

C

1

5

2

_

2

F

u

1

RF

+V1.1A_EN

+V15A

.

0

14-,40-

R1299

1

5.1M_5%

2

1

2

DGND

N

E

6

P

7

O

3

_

1

V

C

0

5

_

F

p

0

0

2

2

1

R1265

15.4K_1%

2

1

R1264

10K_1%

2

PWR-A

51125GND

10-,11-,12-,13-,14-,35-,36-,37-,38-,42-,47-

1

C1373

2

330uF_6.3V

DGND

Typ@8.6A

+V5A OCP = 6.8A

Vout=(R1265/R1264+1)*2

+V5A

PAD806

PWR-E

C1398

1

10uF_6.3V

2

POWERPAD_2_0610

INVENTEC

TITLE

ST145a-UMA

+V3.3A & +V5A & +V2.5S

DOC. NUMBERSIZE

CODE

A3

CS

CHANGE by OF

27-Jul-2009ALAN W

SHEET

951

REV

X01Model_No

Page 10

2009/11/07

+V1.1A_EN

RSMRST#

9-

31-,37-

R1298

0_5%

12

R1293

0_5%

12

C1326

1

C1348

1

2

0402_OPEN

2

1uF_6.3v

DGND

+V1.2S_GND

12-,14-,20-,23-,24-,26-,27-,29-,30-,31-,32-,33-,35-,36-,37-,38-,39-,40-,41-,43-,45-,48-

+V3S

1

C1066

2

10uF_6.3v

V1.1A_PG

PWR-A

0.1uF_16V

U824

1

EN_PSV

2

TON

3

VOUT

4

V5FILT

5

VFB

6

PGOOD

7

GND

TI_TPS51117_QFN_14P

PWR-B

R1066

12

10K_5%

2009/09/28

C1501

R1296

2

1

10_5%

R1297

12

180K_5%

PAD5003

POWERPAD1x1m

1

2

+V5A

9-,11-,12-,13-,14-,35-,36-,37-,38-,42-,47-

PWR-E

R1260

0_5%

12

14

VBST

13

DRVH

12

LL

11

TRIP

10

V5DRV

9

DRVL

8

PGND

15

TML

DGND

1

DGND

2

C1324

1uF_6.3v

ANPEC_APL5315_BI_TRL_SOT23_5P

5

8/14

Q838

SI7716ADN_T1_GE3

R1259

10.7K_1%

5

SETSHDN

G

4

G

4

C1325

0.1uF_16V

12

1

PWR-A

2

+V1.2S_GND

U815

1

2

GND

34

VIN

VOUT

76

8

D

Q839

AON7410

S

123

8

765

D

S

123

DGND

R1002

1

22K_1%

2

R1062

1

10K_1%

2

DGND

+VBATR

7-,9-,11-,12-,13-,35-,47-

1

1

C1323

C1320

2

2

DGND

4.7uF_25v

4.7uF_25v

L845

12

PCMC063T_2R2MN

N

1

E

3

0

OP

2

_

1

2

R

0

4

2

0

C1301

N

E

1

330uF_2.5V

0

OP

0

_

2

3

2

1

0

C

4

0

DGND

RF

Typ@0.25A

Vout=(R1002/R1062)*0.8

+V2.5S

18-

C1061

10uF_6.3v

1

2

N

N

E

E

1

2

P

2

2

O

3

3

OP

1

_

V

C

1

5

2

_

2

F

u

1

.

0

RF

1

DGND

R1295

5.11K_1%

+V1.2S_GND

2

R1294

1

10K_1%

2

1

2

_

1

V

C

1

0

2

DGND

C1347

1

2

0402_OPEN

5

_

F

p

0

0

2

2

POWERPAD_2_0610

Typ@ 7.42A

+V1.1A OCP = 9A

Vout=(R1295/R1294)*0.75

+V1.1A

14-,32-

PAD803

CHANGE by

INVENTEC

TITLE

ST145a-UMA

+V1.2A & VCC_NB

SIZE

CODE

27-Jul-2009ALAN W

A3

DOC. NUMBER

CS

SHEET OF

10 51

REV

X01Model_No

Page 11

CORE_PWEN

RESUME_PWEN

DEFAULT_NET_TYPE

DEFAULT_NET_TYPE

11-,37-

37-,38-

R853

12

0_5%

R900

12

0_5%

C906

0.1uF_10V_OPEN

DEFAULT_NET_TYPE

DEFAULT_NET_TYPE

C1502

1

1

2

2

DGND

0.1uF_10V_OPEN

DGND

+V5A

9-,10-,11-,12-,13-,14-,35-,36-,37-,38-,42-,47-

PWR-A

R854

12

C907

1uF_6.3v

1

2

PWR-A

PWR-A

DEFAULT_NET_TYPE

3300pF_50v

1

C864

2

MAX_MAX17000ETG+_TQFN_24P

PAD5004

POWERPAD1x1m

17000GND

10_5%

DGND

C908

1

DGND

2

U801

1

OVP

TON

BST

DH

2

PGOOD1

3

LX

PGOOD2

19

VDD

DL

PGND1

CSH

23

VCC

CSL

21

FB

AGND

4

STDBY

24

SHDN

VTTI

22

SKIP

PGND2

10

VTT

REFIN

VTTS

25

GND

VTTR

NOTE: DDR3 REGULATOR

2.2uF_6.3v

14

17

15

16

18

20

13

12

11

9

7

8

5

6

10uF_6.3v

PWR-A

R857

0_5%

12

PWR-A

1

2

C865

DGND

R858

1

150K_5%

1

DGND

2

10uF_6.3v

2

DGND

C863

C867

0.1uF_16V

2

+V0.75S

PWR-A

26-,27-

1

2

C861

10uF_6.3v

+VBATR

7-,9-,10-,12-,13-,35-,47-

1

RF

N

E

OP

_

2

0

4

2

0

N

E

1

OP

_

2

2

0

4

0

DGND

1

DGND

DGND

2

2

PCMC063T_1R0MN

1

1

R925

2

3K_1%

0

9

R

2

C866

9

0

9

C

0.22uF_16v

12

5

76

8

8/14

8/14

D

G

S

123

4

6

5

87

D

G

DGND

41S23

Q817

AON7410

1

PWR-D

Q816

FDS6680S

M_VREF

26-,27PWR-A

C868

C869

4.7uF_25v

4.7uF_25v

L805

2009/09/09

R926

12

1K_1%

12

1

2

N

E

1

7

OP

_

8

V

C

5

2

_

F

u

1

.

0

RF

PWR-D

R855

5.36K_1%

R856

10K_1%

1

2

DGND

PWR-A

17000GND

N

E

P

0

O

7

_

8

V

C

0

5

_

F

p

0

0

2

2

1

2

1

PWR-A

2

C8621

0.33uF_10V

2

PWR-A

17000GND

+V1.5 OCP = 10.2A

Vout=(R855/R856+1)*1

12-,14-,18-,19-,26-,27-,32-,33-

+V1.5

PAD801

POWERPAD_2_0610

1

C929

330uF_2V_15mR_Pana_-35%

2

DGND

PWR-D

Typ@9A

CORE_PWEN

9-,10-,11-,12-,13-,14-,35-,36-,37-,38-,42-,47-

R1501

12

11-,37-

10K_5%

C1500

0.1uF_10V

SSM3K7002FU

1

2

DGND

+V5A

%

5

_

M

1

Q856

3

D

1

G

S

2

2009/09/09

9-,13-,14-,18-,29-,30-,31-,32-,33-,35-,40-,41-,43-,47-,48-

1

0

0

5

1

R

2

R1083

750K_1%

1

DGND

DEFAULT_NET_TYPE

RICH_RT8015APQW_WDFN_10P

1

SHDN-RT

2

2

GND

3

LX

U816

4

LX

5

PGND

COMP

PVDD

PVDD

FB

VDD

GND

DGND

+V3A

PWR-D

10

9

12

8

7

R1080

6

11

10_5%

L828

C1150

1

2

2.2uF_6.3v

DGND

12

LTF5022T_2R2N3R2_LC

2009/09/18

R1081

1000pF_50V

10K_5%

12

C1151

1

2

1

R1082

309K_1%

2

C1153

22uF_6.3V

DGND

12

240K_1%

C1152

1

0402_OPEN

2

1

2

R1079

18-,21-,23-,24-,31-

+V1.8S

PWR-D

Vout=(R1082/R1079+1)*0.8

1

C1154

DGND

22uF_6.3V

2

Typ@1.3A

TITLE

CHANGE by SHEET

ALAN W

27-Jul-2009

INVENTEC

ST145a-UMA

DDR3 POWER

CODE

SIZE REV

A3

DOC. NUMBER

Model_No X01

CS

OF

5111

Page 12

+V1.5

1

2

10-,14-,20-,23-,24-,26-,27-,29-,30-,31-,32-,33-,35-,36-,37-,38-,39-,40-,41-,43-,45-,48-

MAX17480

VRM_PWRGD

VRD_PROCHOT#

OCP@4A

Typ@4A

VDDNB_CORE

18-,19-

PWR-D

C918

1

1

C917

2

2

C919

47uF_6.3V

47uF_6.3V

47uF_6.3V

SVC

SVD1VDD_CORE

0

0

1

0

1

1

11-,12-,14-,18-,19-,26-,27-,32-,33-

C824

0.1uF_10V

CPU_PWRGD_SVID_REG

+V5A

+V3S

1

R819

4.7K_5%

2

1318-

PCMC063T_1R0MN

1

2

R918

12

0_5%

PWR-A

C888

4700pF_50V

1

2

1

2

1.1V

1.0V0

0.9V

0.8V

C831

2.2uF_6.3V

MAX17480

CPU_SVC_R

CPU_SVD_R

CPU_PWEN

DEFAULT_NET_TYPE

9-,10-,11-,12-,13-,14-,35-,36-,37-,38-,42-,47-

R825

1

100K_5%

2

MAX17480

L804

12

R882

511_1%

PWR-A

12

C889

0.22uF_16V

R919

C890

10_5%

1000pF_50V

R920

12

5.1K_5%

1

R874

2

143K_1%

1

1

R872

100K_1%

12

100K_5%

2

2

1818-

18-

12

13-,37-

R869

100_1%

PWR-E

R826

1

1

2

PWR-A

2

C884

1

2

2200pF_50V

1

2

1

R827

13K_1%

2

R870

2_5%

POWERPAD1x1m

MAX_MAX17480GTL+_TQFN_40P

2

1

R871

45.3K_1%

DEFAULT_NET_TYPE

R873

12

0_5%

CPU-I

+V5A

C887

10uF_6.3V

9-,10-,11-,12-,13-,14-,35-,36-,37-,38-,42-,47-

2

1

1

2

C886

0.1uF_10V

C885

12

PWR-A

0.1uF_16V

PWR-A

PAD800

(Should routed in 5/5/5 pair and need to

have 10mil clearance to other traces.)

RF

VDD_CORE

12-,19-

PWR-E

1

18-

18-

N

N

E

E

P

P

8

9

O

0

0

O

_

8

8

_

V

V

C

C

1

1

0

5

5

2

_

_

2

2

F

F

p

u

0

1

.

0

0

2

2

41S23

G

41S23

8765

D

G

S

123

4

8D765

G

S

3

4

12

(Should routed in 5/5/5 pair and need to

have 10mil clearance to other traces.)

C810

0.1uF_16V

2

2

C830

2200pF_50V

R821

3.01K_1%

2

C826

2200pF_50V

8/13

2

R820

1

PWR-A

MAX17480

+V5A

1

2

12

R800

1

12

VDD_CORE

12-,19-

1

R816

0402_OPEN

0.0047uF_50v

2

C823

C828

4.7uF_6.3V

R830

1

3.01K_1%

E

1

R

R817

W

P

51_5%

2

2

C827

2

1

2

R828

1

100_1%

2

0.0047uF_50v

18-

VDD1_FB

0.1uF_16V

1

R829

3.01K_1%

2

PWR-A

1

C832

2

MAX17480

R832

1

100_1%

1

C833

0.0047uF_50v

2

2

MAX17480

R831

2

R833

1

51_5%

2

51_5%

VDD0_FB

VDD0_FB#

DH1

LX1

DL1

DH2

LX2

DL2

27

29

28

26

33

34

18

17

23

21

22

24

36

35

37

15

16

14

1

18-

VDD1_FB#

9-,10-,11-,12-,13-,14-,35-,36-,37-,38-,42-,47-

R824

0_5%

0_5%

1

1

2

1

3.01K_1%

R823

12

10_5%

2

5

3

2

U800

39

C

D

BST1

OSC

C

TIME

ILIM12

VDDIO

SVC

SVD

PGD_IN

SHDN

OPTION

PWRGD

VRHOT

THRM

ILIM3

IN3

IN3

LX3

LX3

BST3

OUT3

AGDN

V

+V1.5

D

V

CSP1

CSN1

CSP2

CSN2

BST2

FBAC1

FBDC1

GNDS1

FBAC2

FBDC2

D

N

G

GNDS2

P

1

4

11-,12-,14-,18-,19-,26-,27-,32-,33-

R822

12

10_5%

40

1

13

12

11

19

8

38

20

30

31

2

3

4

5

6

7

9

10

G

1

2

Q802

FDMS8692

Q803

FDS6680S

8765

D

Q805

FDMS8692

8765

D

Q804

FDS6680S

C803

4.7uF_25v

7-,9-,10-,11-,12-,13-,35-,47-

C806

1

2

4.7uF_25v

4.7uF_25v

4.7uF_25v

+VBATR

7-,9-,10-,11-,12-,13-,35-,47-

C802

1

2

4.7uF_25v

+VBATR

PWR-A

C821

1

PWR-A

2

330pF_50V

1

C807

C805

1

1

2

1

3

1

8

R

2

2

2

8

C

RF

1

2

100uF_25V

C804

4.7uF_25v

C818

2

1

R818

1.5K_5%

2

N

N

E

E

P

P

0

1

O

0

0

O

_

8

8

_

V

V

C

C

1

1

0

5

5

2

_

_

2

2

F

F

p

u

0

1

.

0

0

2

2

2

N

E

P

O

_

2

0

4

0

N

E

1

P

O

_

2

2

0

4

0

RF

R811

1

1.5K_5%

2

C820

330pF_50V

1

R810

2.4K_1%

2

4.02K_1%

1

N

1

E

P

2

1

O

8

_

2

R

0

4

2

0

N

E

1

P

O

1

9

_

2

1

2

8

0

C

4

2

0

RF

C829

12

R815

12

10K_1%_THER_NTC

4.02K_1%

1

R814

2.4K_1%

2

L801

1

ETQP4LR45XFC

330uF_2V_6mR_OPEN

Typ@38A

L800

ETQP4LR45XFC

12

R808

R809

12

2

10K_1%_THER_NTC

C825

12

0.22uF_10v

0.22uF_10v

R868

12

2

C880

OCP@45A

VDD_CORE

C883

330uF_2V_6mR

VDD_CORE

12-,19-

1

1

2

C881

2

330uF_2V_6mR

12-,19-

1

2

1

C882

2

330uF_2V_6mR

MAX17480

CHANGE by

ALAN W 27-Jul-2009

INVENTEC

TITLE

ST145a-UMA

+VCC_CORE & +VCC_CORE_NB

SIZE

A3

DOC. NUMBERCODE

Model_No X01

CS

SHEET

OF

REV

5112

Page 13

VRM_PWRGD

DEFAULT_NET_TYPE

VCC_NB_PG

12-

14-

2009/09/28

R1068

47K_5%

2

R1106

0_5%

12

8/17

C1128

0.1uF_10V

1

DEFAULT_NET_TYPE

1

2

1

2

+VCC_NB_GND

CPU_PWEN

C1171

1uF_6.3v

1

2

3

4

5

6

7

TI_TPS51117_QFN_14P

R1504

12

12-,37-

10K_5%

R1105

12

10_5%

R1067

12

180K_5%

EN_PSV

TON

VOUT

U819

V5FILT

VFB

PGOOD

GND

PAD5005

POWERPAD1x1m

2009/09/28

C1601

1000pF_50V

2

+V5A

14

VBST

13

DRVH

12

LL

11

TRIP

10

V5DRV

9

DRVL

8

PGND

15

TML

+V5A

9-,10-,11-,12-,13-,14-,35-,36-,37-,38-,42-,47-

%

5

_

M

1

Q857

3

D

1

G

S

2

SSM3K7002FU

1

9-,10-,11-,12-,13-,14-,35-,36-,37-,38-,42-,47-

8/14

R1108

C1172

0_5%

0.1uF_16V

12

12

FDMS0310S

Q830

1

C1173

1

2

1

3

0

5

1

R

2

1uF_6.3v

PWR-A

+VCC_NB_GND

750K_1%

R1107

2

3.92K_1%

R1060

12

DEFAULT_NET_TYPE

+VBATR

7-,9-,10-,11-,12-,35-,47-

1

C1197

8D765

4.7uF_25v

Q832

AON7410

N

E

OP

_

2

0

4

0

N

E

OP

_

2

0

4

0

COMP

PVDD

PVDD

1

2

VDD

GND

2

PCMC063T_1R0MN

1

9

0

1

1

R

2

6

7

1

1

C

RF

10

9

FB

8

PWR-D

7

6

11

G

S

4

123

6

8

7

5

D

G

S

4

3

2

1

12/22

U814

RICH_RT8015APQW_WDFN_10P

1

SHDN-RT

2

GND

3

LX

4

LX

5

PGND

PWR-C

L824

12

LTF5022T_2R2N3R2_LC

1

C1198

4.7uF_25v

2

L830

12

C1199

330uF_2.5V

R1104 CHANGE TO 13.3K

VCC_NBSTRP_DATA

0

1.25

10.95

+V3A

9-,11-,14-,18-,29-,30-,31-,32-,33-,35-,40-,41-,43-,47-,48-

PWR-D

R1064

10K_5%

12

PWR-A

12

R1063

10_5%

C1127

2.2uF_6.3V

1

2

SSM3K7002FU

8/17

VDDR_0.9_EN

29-

C1051

22uF_6.3V

2009/09/28

R1104

10K_1%

1

2

23.2K_1%

PWR-A

Q827

1

G

N

E

4

7

1

OP

1

_

V

C

1

5

2

_

2

F

u

1

.

0

RF

1

2

1

R1102

PWR-A

2

+VCC_NB_GND

C1126

1000pF_50V

12

3

D

S

2

1

R998

20.5K_1%

2

1

1

2

2

5

7

1

1

C

1

2

PWR-A

R1061

1

31.6K_1%

2

C1052

22uF_6.3V

VCC_NB OCP = 10A

N

E

P

O

_

V

0

5

_

F

p

0

0

2

2

MAX 10A

Typ@7.6A

VCC_NB

24-,47-

PAD802

POWERPAD_2_0610

Vout={R1104/[(R1100+R1099+R1101)//R1102]}*0.75

PWR-A

R1101

1

226K_1%

PWR-A

2

PWR-A

2

12

5.1K_1%

C1169

11

2

4700pF_25V

R1100

R1099

1

16.2K_1%

C1170

2

0.0015uF_50V

R1065

12

100K_1%

Typ@1.5A

C1124

1

Vout=(R1061/R1065)*0.8

2

0402_OPEN

+V1.05S

CPU_VDDR

18-,19-

0.9_EN

0

1

CHANGE by

Power State

UVD Moe - High

UVD Mode - Low

Performance Mode

Battery Mode

Power State

UVD Moe - High

UVD Mode - Low

Performance Mode

Battery Mode

R1098

1

10K_5%

2

CPU_VDDR

1.05

0.9

RS880M

Enging Clock

500 MHz

380 MHz

500 MHz - 200MHz

200MHz

High Performance Variant

RS880M

Enging Clock

380 MHz

200MHz

23-

STRP_DATA

ALAN W 27-Jul-2009

Northbridge

Core Voltage

1.1 V

0.95 V

1.1 V

0.95 V

Northbridge

Core Voltage

1.25 V590 MHz 550 MHz / 400 MHz

0.95 V

1.25 V590 MHz - 200MHz

0.95 V

STRP_DATA

0

UVD Clocks

550 MHz / 400 MHz

400 MHz / 300 MHz

n / a

n / a

UVD Clocks

400 MHz / 300 MHz

n / a

n / a

VCC_NB

1.1

0.951

INVENTEC

TITLE

ST145a-UMA

CODE

SIZE

A3

DOC. NUMBER

Model_No X01

CS

SHEET

OF

REV

5113

Page 14

CORE_PWEN#

CORE_PWEN#

9-,11-,13-,18-,29-,30-,31-,32-,33-,35-,40-, 41-,43-,47-,48-

1

C1381

2200pF_50V

2

+V3A

PWR-D

Q843

6

D

S

5

2

1

G

AO6402AL

2009/11/29

R1323

V3_EN

12

34-

0_5%

DEFAULT_NET_TYPE

+V5A

9-,10-,11-,12-,13-,35-,36-,37-,38-,42-,47-

Q847

6

S

D

5

2

13

G

AO6402AL

R1320

12

V5_EN

0_5%

10-,12-,14-,20-,23-,24-,26-,27-,29-,30-,31-,32-,33-,35-,36-,37-,38-,39-,40-,41-,43-,45-,48-

100_5%

12

R1147

R1146

R1179

100_5%

12

100_5%_OPEN

2

1

+V15A

9-,14-,40PWR-A

1

R1322

750K_5%

2

+V15A_RC

Q852

14-,37-

V35_EN

SSM3K7002FU

L

H

H

L

V1.1A_PG

VCC_NB_PG

SYS_RST#

D

1

G

S

+V3S & +V5S

3V & 5V

0V

10-

13-

31-

3

2

10-,12-,14-,20-,23-,24-,26-,27-,29-,30-,31-,32-,33-,35-,36-,37-,38-,39-,40-,41-,43-,45-,48-

+V3S

470 OHM

1

R1325

470_5%

2

NA

3

D

Q853

SSM3K7002FU

S

2

+V5S

20-,34-,35-,36-,38-,40-,41-,45-,47-

Typ@2.72A

1

2

PWR-D

4

3

1

G

Typ@2.6A

4

1

2

PWR-E

470 OHM

1

R1300

470_5%

2

NA

3

D

1

G

Q842

SSM3K7002FU

S

2

+V3S

PWR-D

2

R1149

10K_5%

1

1

C1258

1000pF_50V

2

C1382

10uF_6.3V

C1372

10uF_10V

37-

ALL_PWGD_IN

CORE_PWEN#

CORE_PWEN_D#

14-,37-

37-

DEFAULT_NET_TYPE

Q818

SSM3K7002FU

1

G

SSM3K7002FU

+V15A

D

S

9-,14-,40-

PWR-A

1

R903

1M_5%

2

3

2

9-,14-,40-

Q837

1

G

+V15A

D

S

+V1.5

1

C910

3300pF_50V

2

PWR-A

1

R1204

1M_5%

2

3

2

11-,12-,18-,19-,26-,27-,32-,33-

PWR-D

Q820

6

4

S

D

5

2

13

G

AO6402AL

V1.5_EN

2009/11/12

+V1.1A

10-,32-

PWR-D

Q835

8

D

7

6

5

G

SI7716ADN_T1_GE3

1

C1302

2200pF_50V

2

S

+V1.5S

1

G

1

2

3

4

18-,24-,25-,45-,47-,48-

PWR-C

1

2

470 OHM

1

R905

470_5%

2

3

D

Q819

SSM3K7002FU

S

2

Typ@6.8A

+V1.1S

1

2

3

D

1

G

S

2

Typ@1.23A

C911

10uF_6.3V

NA

18-,19-,21-,22-,23-,24-,32-,47-

1

C1260

10uF_6.3V

2

470 OHM

R1181

470_5%

NA

Q836

SSM3K7002FU

CHANGE by

ALAN W 27-Jul-2009

INVENTEC

TITLE

ST145a-UMA

+V5S & +V3.3S & +V1.5S & +V1.2S

DOC. NUMBER

CODE

SIZE

A3

Model_No X01

CS

SHEET

OF

REV

5114

Page 15

ALAN W 21-Dec-2009

INVENTEC

TITLE

ST145a-UMA

CLK GEN

SIZE CODE REV

A3

DOC. NUMBER

Model_No X01

CS

SHEET

5115

OFCHANGE by

Page 16

L0_CLKIN1H

L0_CLKIN1L

L0_CLKIN0H

L0_CLKIN0L

L0_CTLIN1H

L0_CTLIN1L

L0_CTLIN0H

L0_CTLIN0L

L0_CADIN15H

L0_CADIN15L

L0_CADIN14H

L0_CADIN14L

L0_CADIN13H

L0_CADIN13L

L0_CADIN12H

L0_CADIN12L

L0_CADIN11H

L0_CADIN11L

L0_CADIN10H

L0_CADIN10L

L0_CADIN9H

L0_CADIN9L

L0_CADIN8H

L0_CADIN8L

L0_CADIN7H

L0_CADIN7L

L0_CADIN6H

L0_CADIN6L

L0_CADIN5H

L0_CADIN5L

L0_CADIN4H

L0_CADIN4L

L0_CADIN3H

L0_CADIN3L

L0_CADIN2H

L0_CADIN2L

L0_CADIN1H

L0_CADIN1L

L0_CADIN0H

L0_CADIN0L

CN810-1

21212121-

21212121-

21212121212121212121212121212121-

21212121212121-

2121212121212121-

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

N5

L0_CADIN_H15

P5

L0_CADIN_L15

M3

L0_CADIN_H14

M4

L0_CADIN_L14

L5

L0_CADIN_H13

M5

L0_CADIN_L13

K3

L0_CADIN_H12

K4

L0_CADIN_L12

H3

L0_CADIN_H11

H4

L0_CADIN_L11

G5

L0_CADIN_H10

H5

L0_CADIN_L10

F3

L0_CADIN_H9

F4

L0_CADIN_L9

E5

L0_CADIN_H8

F5

L0_CADIN_L8

N3

L0_CADIN_H7

N2

L0_CADIN_L7

L1

L0_CADIN_H6

M1

L0_CADIN_L6

L3

L0_CADIN_H5

L2

L0_CADIN_L5

J1

L0_CADIN_H4

K1

L0_CADIN_L4

G1

L0_CADIN_H3

H1

L0_CADIN_L3

G3

L0_CADIN_H2

G2

L0_CADIN_L2

E1

L0_CADIN_H1

F1

L0_CADIN_L1

E3

L0_CADIN_H0

E2

L0_CADIN_L0

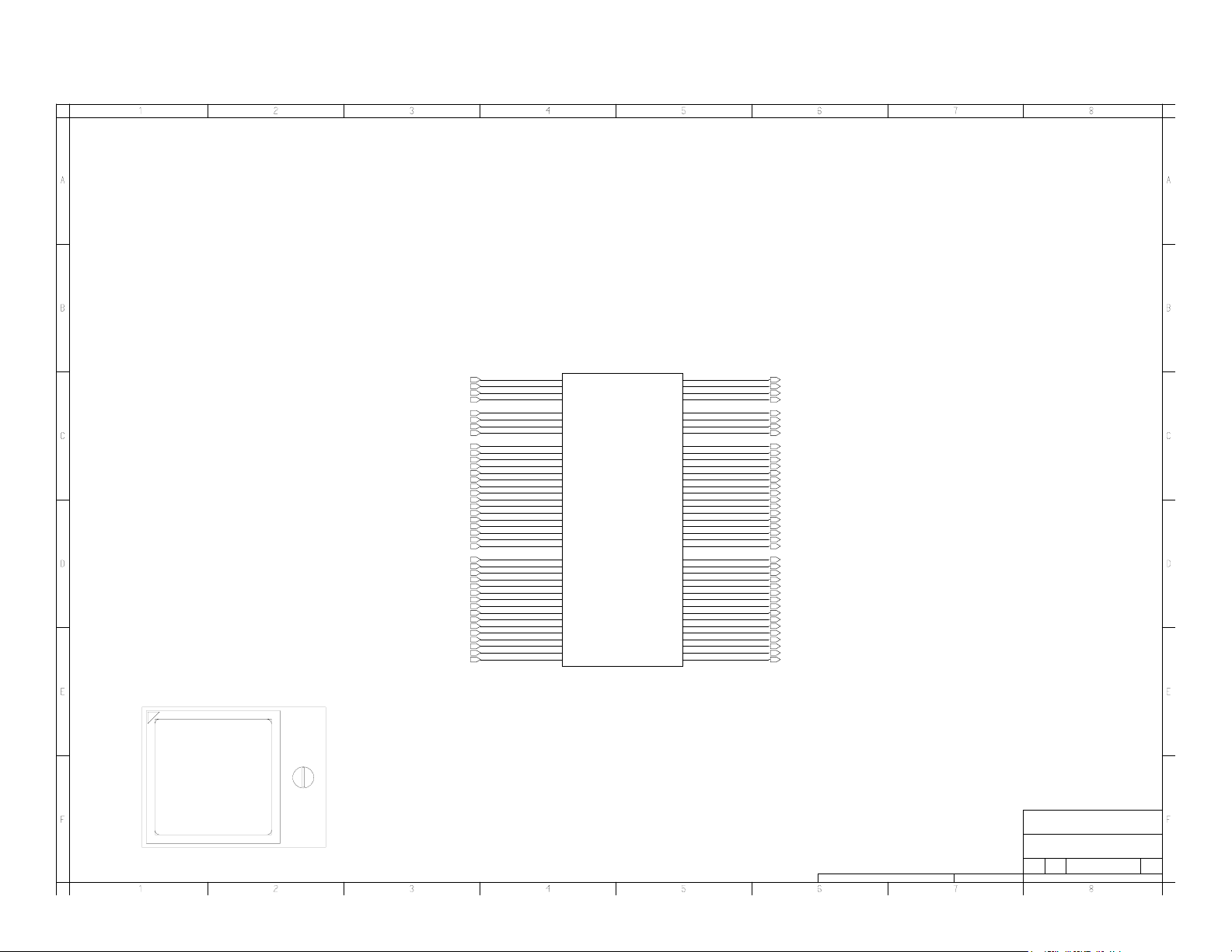

FOX_PZ63823_284S_41F_TEMP_638P

T

R

O

P

S

N

A

R

T

R

E

P

Y

H

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

Y4

Y3

Y1

W1

T5

R5

R2

R3

T4

T3

V5

U5

V4

V3

Y5

W5

AB5

AA5

AB4

AB3

AD5

AC5

AD4

AD3

T1

R1

U2

U3

V1

U1

W2

W3

AA2

AA3

AB1

AA1

AC2

AC3

AD1

AC1

21-

L0_CLKOUT1H

21-

L0_CLKOUT1L

21-

L0_CLKOUT0H

21-

L0_CLKOUT0L

21-

L0_CTLOUT1H

21-

L0_CTLOUT1L

21-

L0_CTLOUT0H

21-

L0_CTLOUT0L

21-

L0_CADOUT15H

21-

L0_CADOUT15L

21-

L0_CADOUT14H

21-

L0_CADOUT14L

21-

L0_CADOUT13H

21-

L0_CADOUT13L

21-

L0_CADOUT12H

21-

L0_CADOUT12L

21-

L0_CADOUT11H

21-

L0_CADOUT11L

21-

L0_CADOUT10H

21-

L0_CADOUT10L

21-

L0_CADOUT9H

21-

L0_CADOUT9L

21-

L0_CADOUT8H

21-

L0_CADOUT8L

21-

L0_CADOUT7H

21-

L0_CADOUT7L

21-

L0_CADOUT6H

21-

L0_CADOUT6L

21-

L0_CADOUT5H

21-

L0_CADOUT5L

21-

L0_CADOUT4H

21-21-

L0_CADOUT4L

21-

L0_CADOUT3H

21-

L0_CADOUT3L

21-

L0_CADOUT2H

21-

L0_CADOUT2L

21-

L0_CADOUT1H

21-

L0_CADOUT1L

21-

L0_CADOUT0H

21-

L0_CADOUT0L

A1

AF1

S1

Top View

A26

Layout: Add stitching caps if crossing plane split.

CHANGE by

ALAN W 27-Jul-2009

INVENTEC

TITLE

ST145a-UMA

CPU-1

CODE

SIZE

A3

DOC. NUMBER

Model_No X01

CS

SHEET

OF

REV

5116

Page 17

MA_CLK_DDR2

MA_CLK_DDR1

MA_CLK_DDR1#

MA_CLK_DDR2#

MA_CS1#

MA_CS0#

MA_ODT1

MA_ODT0

MA_CAS#

MA_WE#

MA_RAS#

MA_BA2

MA_BA1

MA_BA0

MA_CKE1

MA_CKE0

MA_A(15:0)

MA_DQS(7)

MA_DQS#(7)

MA_DQS(6)

MA_DQS#(6)

MA_DQS(5)

MA_DQS#(5)

MA_DQS(4)

MA_DQS#(4)

MA_DQS(3)

MA_DQS#(3)

MA_DQS(2)

MA_DQS#(2)

MA_DQS(1)

MA_DQS#(1)

MA_DQS(0)

MA_DQS#(0)

MA_DM(7:0)

26262626-

2626-

2626-

262626-

262626-

262626-

2626262626262626262626262626262626-

MA_A(15)

MA_A(14)

MA_A(13)

MA_A(12)

MA_A(11)

MA_A(10)

MA_A(9)

MA_A(8)

MA_A(7)

MA_A(6)

MA_A(5)

MA_A(4)

MA_A(3)

MA_A(2)

MA_A(1)

MA_A(0)

MA_DQS(7)

MA_DQS#(7)

MA_DQS(6)

MA_DQS#(6)

MA_DQS(5)

MA_DQS#(5)

MA_DQS(4)

MA_DQS#(4)

MA_DQS(3)

MA_DQS#(3)

MA_DQS(2)

MA_DQS#(2)

MA_DQS(1)

MA_DQS#(1)

MA_DQS(0)

MA_DQS#(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

CN810-2

P19

MA_CLK_H3

N19

MA_CLK_H0

N20

MA_CLK_L0

P20

MA_CLK_L3

Y16

MA_CLK_H2

AA16

MA_CLK_L2

E16

MA_CLK_H1

F16

MA_CLK_L1

V20

MA1_CS_L1

U20

MA1_CS_L0

U19

MA0_CS_L1

T20

MA0_CS_L0

V22

MA0_ODT1

T19

MA0_ODT0

V19 27-

MA1_ODT1

U21

MA1_ODT0

T22

MA_CAS_L

T24

MA_WE_L

R19

MA_RAS_L

J21

MA_BANK2

R23

MA_BANK1

R20

MA_BANK0

J20

MA_CKE1

J22

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

E

C

A

F

R

E

T

N

I

Y

R

O

M

E

M

K19

K24

V24

K20

L22

R21

K22

L19

L21

M24

L20

M22

M19

N22

M20

N21

W12

W13

Y15

W15

AB19

AB20

AD23

AC23

G22

G21

C22

C21

G16

G15

G13

H13

Y13

AB16

Y19

AC24

F24

E19

C15

E12

FOX_PZ63823_284S_41F_TEMP_638P

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

AA12

AB12

AA14

AB14

W11

Y12

AD13

AB13

AD15

AB15

AB17

Y17

Y14

W14

W16

AD17

Y18

AD19

AD21

AB21

AB18

AA18

AA20

Y20

AA22

Y22

W21

W22

AA21

AB22

AB24

Y24

H22

H20

E22

E21

J19

H24

F22

F20

C23

B22

F18

E18

E20

D22

C19

G18

G17

C17

F14

E14

H17

E17

E15

H15

E13

C13

H12

H11

G14

H14

F12

G12

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

26-

MA_DATA(63:0)

MB_CLK_DDR2

MB_CLK_DDR1

MB_CLK_DDR1#

MB_CLK_DDR2#

MB_CS1#

MB_CS0#

MB_ODT1

MB_ODT0

MB_CAS#

MB_WE#

MB_RAS#

MB_BA2

MB_BA1

MB_BA0

MB_CKE1

MB_CKE0

MB_A(15:0)

MB_DQS(7)

MB_DQS#(7)

MB_DQS(6)

MB_DQS#(6)

MB_DQS(5)

MB_DQS#(5)

MB_DQS(4)

MB_DQS#(4)

MB_DQS(3)

MB_DQS#(3)

MB_DQS(2)

MB_DQS#(2)

MB_DQS(1)

MB_DQS#(1)

MB_DQS(0)

MB_DQS#(0)

MB_DM(7:0)

27272727-

2727-

27-

272727-

272727-

272727-

2727272727272727272727272727272727-

MB_A(15)

MB_A(14)

MB_A(13)

MB_A(12)

MB_A(11)

MB_A(10)

MB_A(9)

MB_A(8)

MB_A(7)

MB_A(6)

MB_A(5)

MB_A(4)

MB_A(3)

MB_A(2)

MB_A(1)

MB_A(0)

MB_DQS(7)

MB_DQS#(7)

MB_DQS(6)

MB_DQS#(6)

MB_DQS(5)

MB_DQS#(5)

MB_DQS(4)

MB_DQS#(4)

MB_DQS(3)

MB_DQS#(3)

MB_DQS(2)

MB_DQS#(2)

MB_DQS(1)

MB_DQS#(1)

MB_DQS(0)

MB_DQS#(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

CN810-3

R26

MB_CLK_H3

P22

MB_CLK_H0

R22

MB_CLK_L0

R25

MB_CLK_L3

AF18

MB_CLK_H2

AF17

MB_CLK_L2

A17

MB_CLK_H1

A18

MB_CLK_L1

U22

MB1_CS_L0

W25

MB0_CS_L1

V26

MB0_CS_L0

W23

MB0_ODT1

W26

MB0_ODT0

Y26

MB1_ODT0

U24

MB_CAS_L

U23

MB_WE_L

U25

MB_RAS_L

J26

MB_BANK2

U26

MB_BANK1

R24

MB_BANK0

H26

MB_CKE1

J25

MB_CKE0

J24

MB_ADD15

J23

MB_ADD14

W24

MB_ADD13

L25

MB_ADD12

L26

MB_ADD11

T26

MB_ADD10

K26

MB_ADD9

M26

MB_ADD8

L24

MB_ADD7

N25

MB_ADD6

L23

MB_ADD5

N26

MB_ADD4

N23

MB_ADD3

P26

MB_ADD2

N24

MB_ADD1

P24

MB_ADD0

AF12

MB_DQS_H7

AE12

MB_DQS_L7

AE16

MB_DQS_H6

AD16

MB_DQS_L6

AF21

MB_DQS_H5

AF22

MB_DQS_L5

AC25

MB_DQS_H4

AC26

MB_DQS_L4

F26

MB_DQS_H3

E26

MB_DQS_L3

A24

MB_DQS_H2

A23

MA_DQS_L2

D16

MB_DQS_H1

C16

MA_DQS_L1

C12

MB_DQS_H0

B12

MA_DQS_L0

AD12

MB_DM7

AC16

MB_DM6

AE22

MB_DM5

AB26

MB_DM4

E25

MB_DM3

A22

MB_DM2

B16

MB_DM1

A12

MB_DM0

FOX_PZ63823_284S_41F_TEMP_638P

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

E

C

MB_DATA40

A

MB_DATA39

F

R

MB_DATA38

E

MB_DATA37

T

N

MB_DATA36

I

MB_DATA35

Y

MB_DATA34

R

O

MB_DATA33

M

MB_DATA32

E

MB_DATA31

M

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

AD11

AF11

AF14

AE14

Y11

AB11

AC12

AF13

AF15

AF16

AC18

AF19

AD14

AC14

AE18

AD18

AD20

AC20

AF23

AF24

AF20

AE20

AD22

AC22

AE25

AD26

AA25

AA26

AE24

AD24

AA23

AA24

G24

G23

D26

C26

G26

G25

E24

E23

C24

B24

C20

B20

C25

D24

A21

D20

D18

C18

D14

C14

A20

A19

A16

A15

A13

D12

E11

G11

B14

A14

A11

C11

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

27-

MB_DATA(63:0)

INVENTEC

TITLE

ST145a-UMA

CPU-2

CODE

SIZE

A3

CHANGE by SHEET

16-Sep-2009ALAN W

CS

DOC. NUMBER

17 51

OF

REV

X01Model_No

Page 18

+V1.5

11-,12-,14-,18-,19-,26-,27-,32-,33-

1

R929

1K_1%

2

1

R930

1K_1%

2

+V1.5

11-,12-,14-,18-,19-,26-,27-,32-,33-

1

R1000

510_5%

2

1

R999

0402_OPEN

2

+V1.5

11-,12-,14-,18-,19-,26-,27-,32-,33-

1

R1001

0402_OPEN

2

1

R1003

510_5%

2

+V1.5

11-,12-,14-,18-,19-,26-,27-,32-,33-

PWR-D

0402_OPEN

R160 300OHM

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

LDT_RST#

1

2

18-

18-

R971

1

300_5%

R972

1

N.C

C943

0.01uF_16V

TEST25_H

TEST25_L

2

18-

2

18-

18-

18-

18-

18-

18-

18-

18-

18-

CPU_MVREF

18-

1

C944

2

1000pF_50V

11-,12-,14-,18-,19-,26-,27-,32-,33-

CPU_DBREQ#

CPU_DBRDY

SMBUS

SMBUS

HDT Header

CPU_R_CLKP

CPU_R_CLKN

11-,12-,14-,18-,19-,26-,27-,32-,33-

+V1.5

PWR-D

31-

SCLK3

31-

SDATA3

CPU_MVREF

+V1.5

18-

+V1.5

11-,12-,14-,18-,19-,26-,27-,32-,33-

SAMTEC_ASP_68200_26P_OPEN

Keep trace to resistor less than 600mils from CPU pin

and trace to AC caps less than 1250mils.

C1064

29-

29-

R916 1K_5%

R917 0_5%_OPEN

CPU_VDDR

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

3900pF_16V

C1065

3900pF_16V

12

12

1K_5%R914

12

12

0_5%_OPENR915

C914

8/18

VDDNB_CORE

12-,19-

PWR-D

13-,19-

CN817

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

12

1

R1004

169_1%

2

12

C915

1

1

2

2

100pF_50V_OPEN

100pF_50V_OPEN

R907 39.2_1%

R906 39.2_1%

Keep trace to resistors less

than 1" from CPU pin.

CLK_CPUBCLK_C

CLK_CPUBCLK#_C

LDT_PG

LDTSTOP#

LDT_RST#

CPU_TDI

CPU_TRST#

CPU_TCK

CPU_TMS

CPU_DBREQ#

VDD0_FB

VDD0_FB#

12

1

2

MEMHOT#

TEST25_H

TEST25_L

R950 1K_5%

300 OHM N.C

R975

R974

R908

H_THERMDC

H_THERMDA

VDD1_FB

VDD1_FB#

LDTSTOP# NB_LDTSTOP#

CPU_VDDA

C1059

3300pF_50V

CN810-4

F8

F9

A9

A8

A7

B7

AF4

AF5

AF9

AD9

AC9

AA9

E10

F6

E6

H6

G6

Y10

W17

AE10

AF10

AA8

E9

E8

G9

H10

C2

D7

E7

F7

C7

AC8

C3

AA6

W7

W8

Y6

AB6

1

2

0_5%_OPEN

U860

1

2

3

C10581

0.22uF_6.3V

2

11-,12-,14-,18-,19-,26-,27-,32-,33-

VDDA

VDDA

MISC

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

SIC

SID

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

VDDNB_FB_H

VDDNB_FB_L

VDDR_SENSE

VTT_SENSE

M_VREF

M_ZN

M_ZP

MEMHOT_L

TEST25_H

TEST25_L

TEST19

TEST18

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

THERMDC

THERMDA

VDD1_FB_H

VDD1_FB_L

+V1.8S

11-,21-,23-,24-,31-

2009/11/19

R1573

12

1A61Y

5

VCC

GND

2A42Y

1

2

LDTREQ_L

THERMTRIP_L

PROCHOT_L

DBRDY

VDDIO_FB_H

VDDIO_FB_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

ALERT_L

TEST10

TEST8

V

0

1

1

_

8

F

6

u

1

2

1

1

.

0

C

1

2

R1007 0_5%

18-,2918-,2918-

CPU_SIC

CPU_SID

1818181818-

1212-

1K_5%R949

270_5%_OPEN

270_5%_OPEN

1K_5%

20201212-

18-

1818-

12

12

1K_5%

R954

100_5%

12

R931

12

2

1

R976

12

0_5%

12

1

2

12

THM

THM

THM

THM

PWRGD

TP816

TP817

THM

THM

TP815

FOX_PZ63823_284S_41F_TEMP_638P

+V1.5S

14-,18-,24-,25-,45-,47-,48-

1

R1092

300_5%

18-,29-

2

R1574

0402_OPEN

NXP_74LVC2G07GW_SC88A_6P

CO-LAYOUT FOR R1573 & U860

INSTALL R1573 AND R1574, REMOVE R1092 IF CPU CAN TOLERANCE 1.8

12

BLM11P600S

C1125

4.7uF_6.3V

+V1.5

C6F10

A6

SVC

A4

SVD

AF6

AC7

AE9

TDO

G10

W9

Y9

P6

R6

C9

C8

AE7

AD7

AE8

AB8

AF7

J7

H8

AF8

AE6

K8

C4

1

R1096

2.2K_5%

2

L817

2009/09/29

14-,18-,24-,25-,45-,47-,48-

23-

+V2.5S

10-

1

C1063

180pF_50V

2

+V1.5S

1

1

R1015

R1014

1K_5%

1K_5%

2

2

CPU_SVC

CPU_SVD

CPU_HTREF1

CPU_HTREF0

1

12

R1016 0_5%

THERMTRIP#

CPU_PROCHOT#_VDDIO

1

TP801

200_5%

44.2_1%

44.2_1%

R973

12

80.6_1%

Route as 80ohm, diff

1

12

12

1

12

TP804

TP805

12

CPU_ALERT

12

R117 300OHM

1K_5%_OPEN

250mA

2

0_5%R1013

18-

18-

R932

2

2

2

2

R912

R913

R910

2

R933

R911

R909

R952

NA

R1095

18-

18-,29-

LDT_REQ#

12-

CPU_SVC_R

12-

CPU_SVD_R

CPU_TDO

CPU_DBRDY

+V1.1S

R953

1

R951

1

1K_5%

1K_5%_OPEN

1K_5%

1K_5%

1K_5%

1K_5%

0402_OPEN

9-,11-,13-,14-,18-,29-,30-,31-,32-,33-,35-,40-,41-,43-,47-,48-

11-,12-,14-,18-,19-,26-,27-,32-,33-

+V1.5 +V3A

PWR-D

1

1

2

2

1

B

Q829

MMBT3904_OPEN

R878

300_5%

11-,12-,14-,18-,19-,26-,27-,32-,33-

+V1.5

14-,18-,19-,21-,22-,23-,24-,32-,47-

Keep trace to resistors less

than 1" from CPU pin.

+V1.5

11-,12-,14-,18-,19-,26-,27-,32-,33-

1

R1097

R1094

10K_5%

10K_5%_OPEN

2

26-,29-,31-

3CE2

CHANGE by

+V1.5

11-,12-,14-,18-,19-,26-,27-,32-,33-

1

1

R876

1K_5%

2

2

+V1.1S

14-,18-,19-,21-,22-,23-,24-,32-,47-

PWR-D

CPU_PWRGD_SVID_REG

CPU_LDT_RST#

CPU_MEMHOT#MEMHOT#

1

R877

10K_5%

2

Q814

1

B

MMBT3904

3CE2

11-,12-,14-,18-,19-,26-,27-,32-,33-

+V1.5

PWR-D

1

1

R834

1K_5%

2

2

1

B

Q813

MMBT3904_OPEN

LDT_PG

LDT_RST#

LDT_REQ#

27-Jul-2009ALAN W

R875

10K_5%

3CE2

18-,29-

12-

29-

18-

18-,29-

1

2

1

B

R1700

10K_5%

C32E

Q864

MMBT3904

11/05

C6016

12

0.01uF_16V

31-,37-

R879

12

0_5%

R880

12

0_5%

R881

12

0_5%

12-

30-

29-

+V3A

9-,11-,13-,14-,18-,29-,30-,31-,32-,33-,35-,40-,41-,43-,47-,48-

1

R883

4.7K_5%_OPEN

2

20-

CPU_Q_ALERT#

300_5%

R1010

R1008

0_5%_OPEN

R1006

12

0_5%

12

R1005

12

0_5%