Page 1

A

hexainf@hotmail.com

1 1

B

C

D

E

Compal Confidential

Schematics Document

2 2

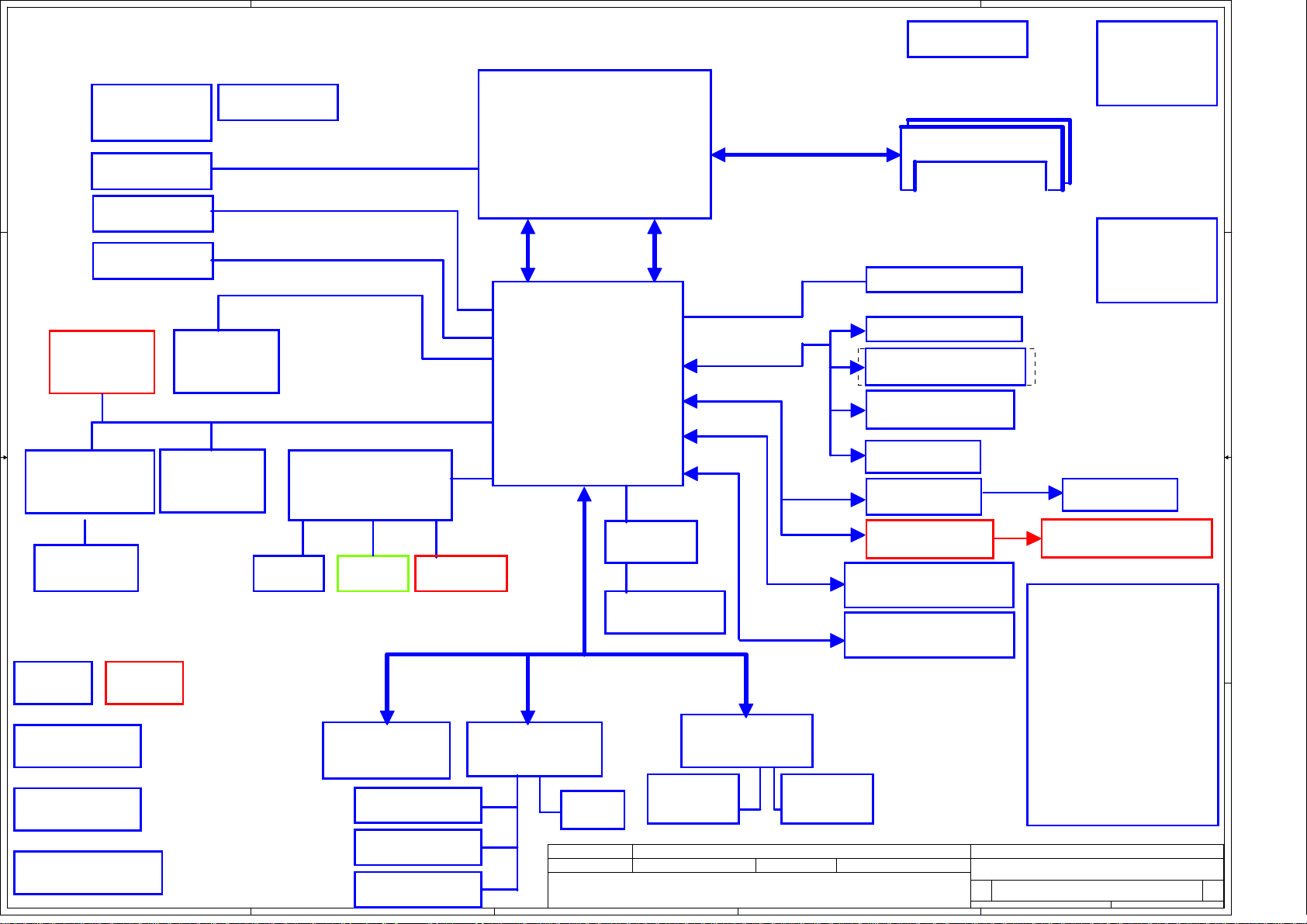

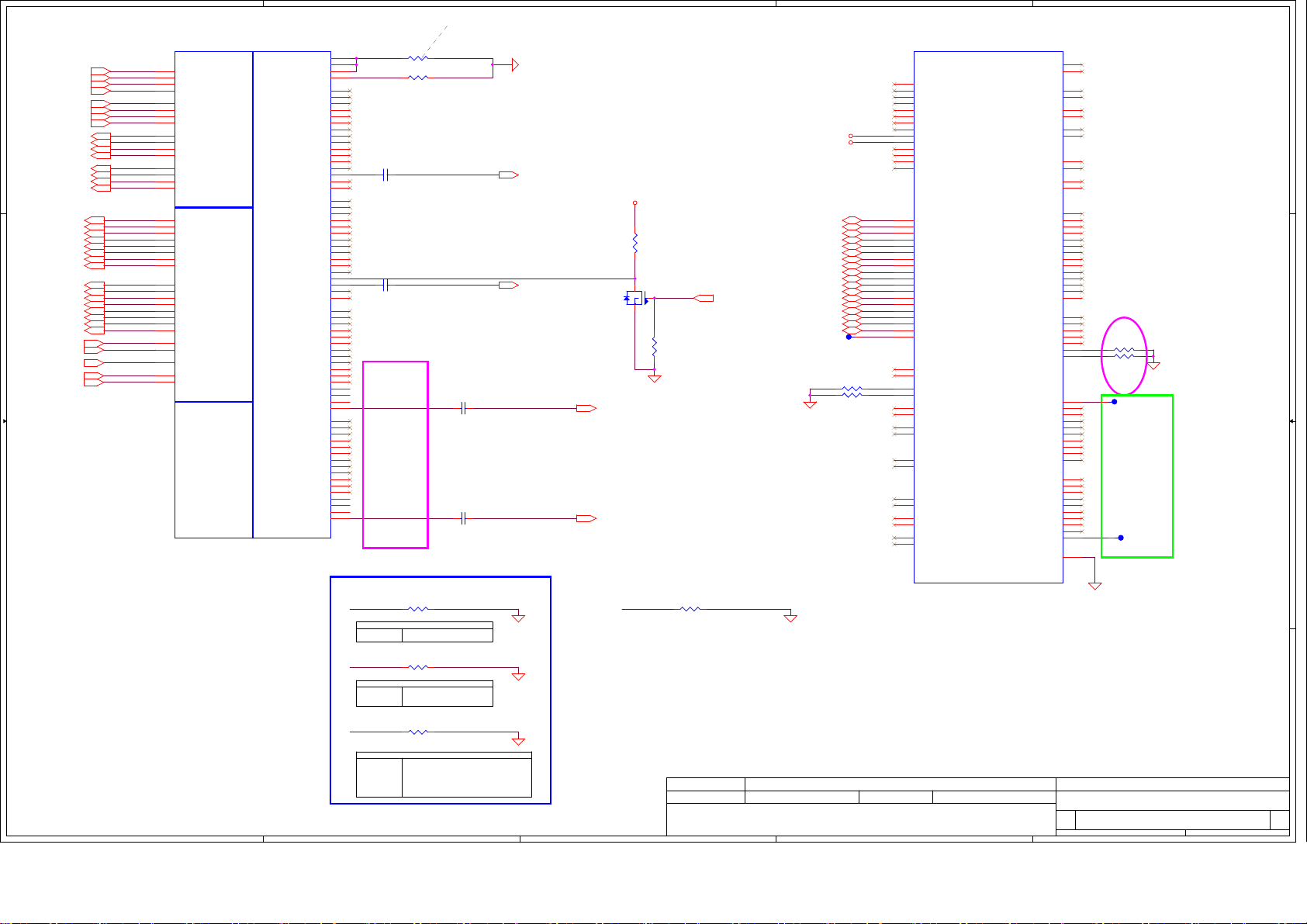

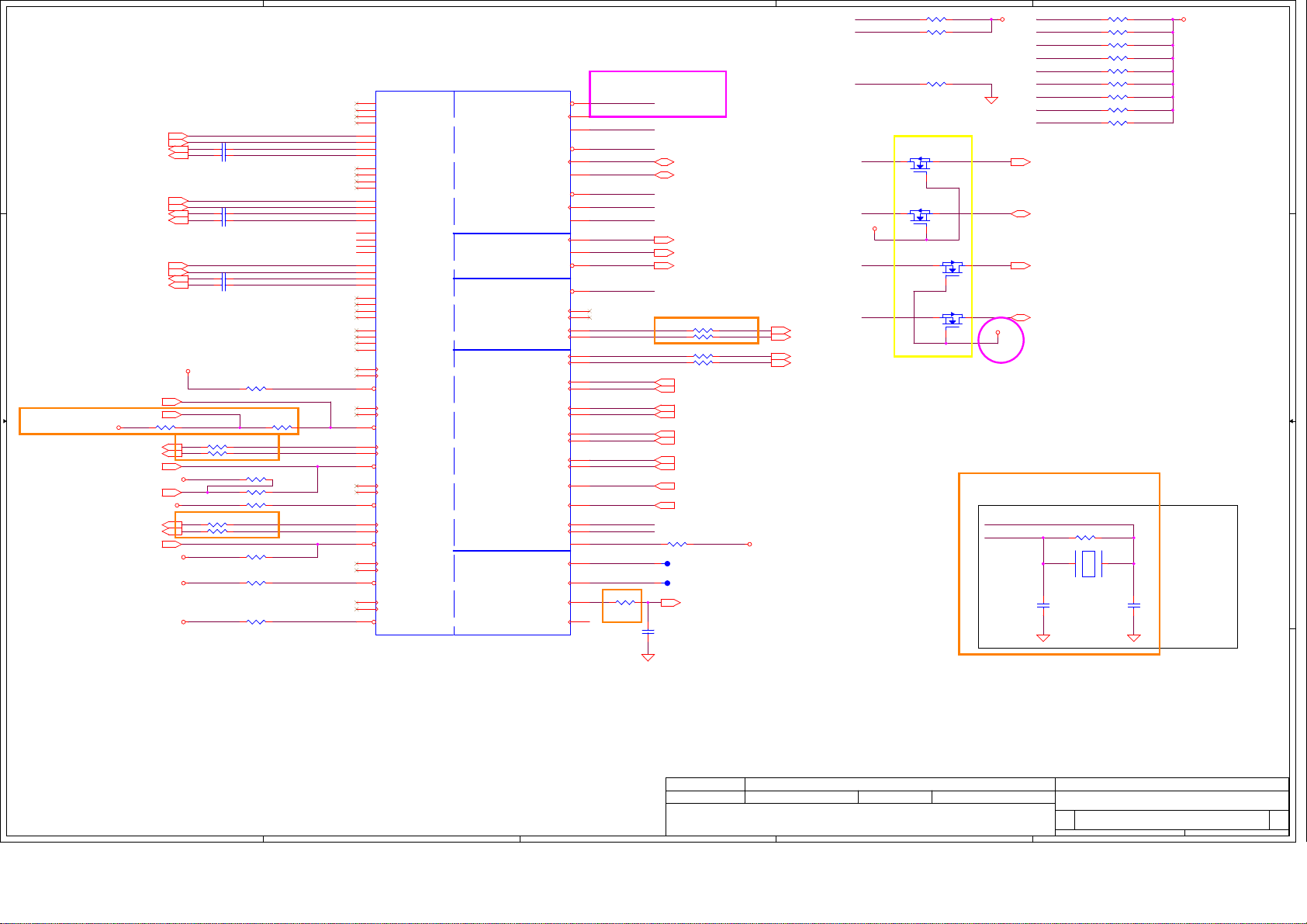

INTEL AUBURNDALE with IBEX core logic

Cartier UMA

3 3

LA-4902P

2009-12-07

4 4

A

B

REV:1.0

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/09/15 2009/12/31

Compal Secret Data

Deciphered Date

D

Title

Size Docume nt Number Re v

Cust om

Date : Sheet o f

Compal Electronics, Inc.

Cover Sheet

LA-4902P

E

1 47Monda y, December 1 4, 2009

0.3

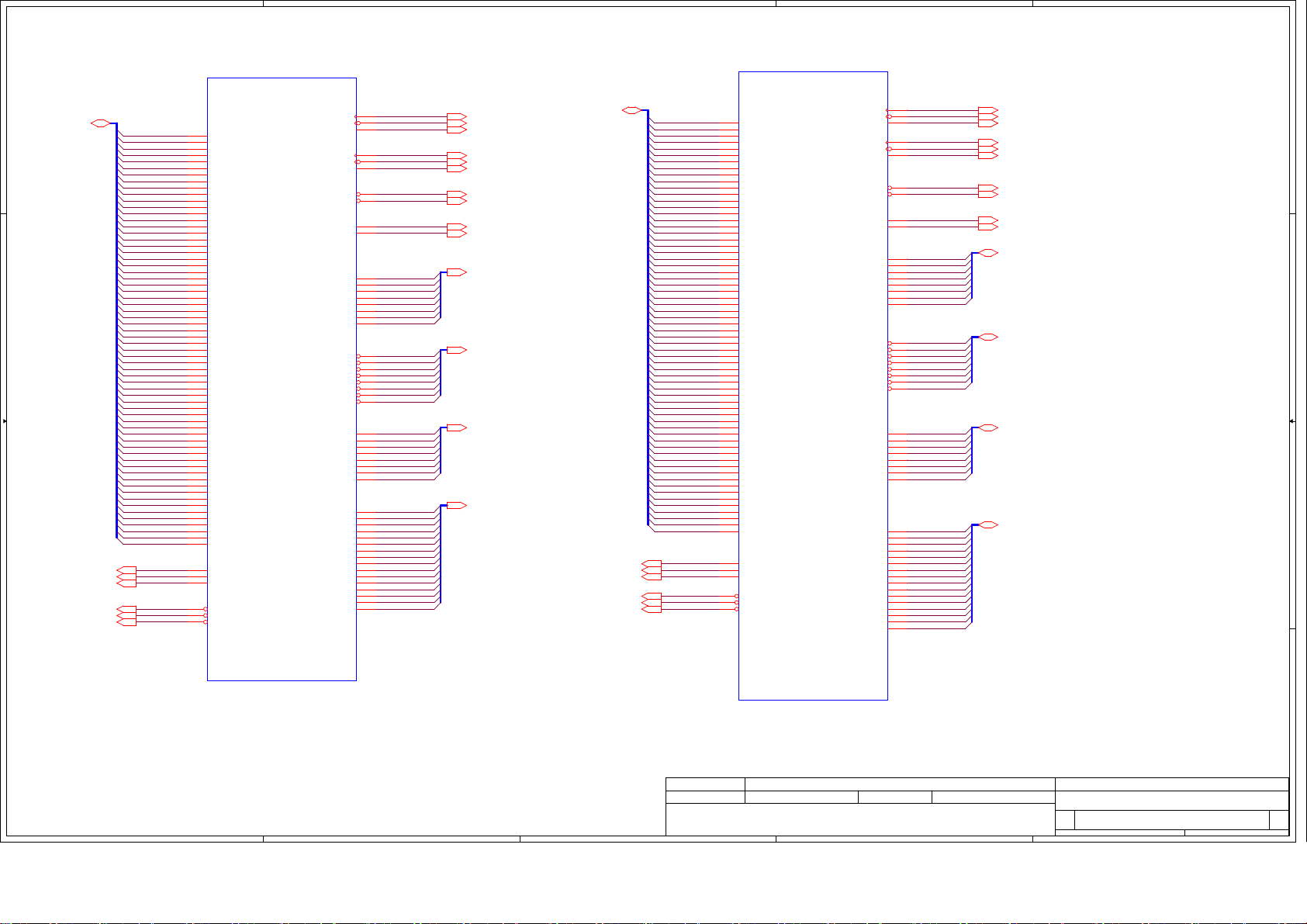

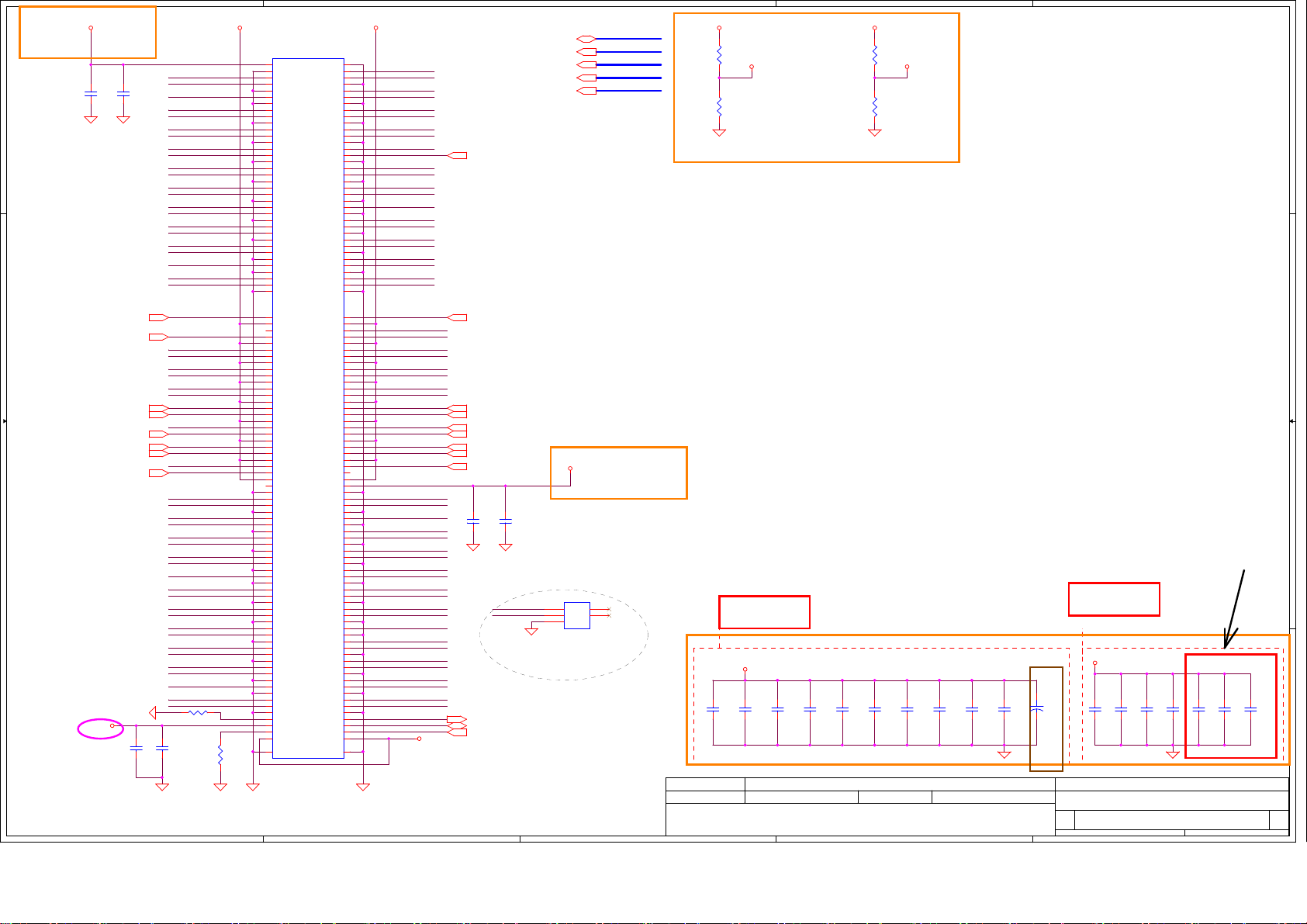

Page 2

A

Compal Confidential

B

C

Cartier UMA

D

XDP Conn.

Page 4

E

Accelerometer

LIS30 2DLTR

File Name : LA-4902P

1 1

2 2

Express Card 54

EM C 21 13

DP Panel

VGA

Display Port

PCIE X1 + USB X1

Audio Board

Page 4

Page 20

Page 18

Page 19

WWAN Card

PCIE X1

Thermal Sensor

Fan Con trol

Page 24

Page 4

USB2.0

eDP

DP-D

FDI

Intel Ibex Peak M

PCI-E BUS

10/1 00/1000 LAN

Intel Hansville GbE

PHY

Page 21

RJ45 CONN

3 3

Page 22

WLAN Card

WLAN + PCIE X1

Page 23

1394 port

Rico R5C835

PCI BUS

Controller

Page 27

Page 27 Audio Board

Smart Card

SD/MMC Slot

LPC BUS

RTC CKT.

Page 12

LE D

Audio Board

Mobile

CPU Dual Core

Socket-rPGA989

37.5mm*37. 5mm

Page 4,5,6,7,8

10 71p i ns

25mm*27mm

Page 12,13,14,15,16,17

ONFI Interface

Braidwood

NAND Flash Card

DMI X4

Page 24

Page 24

Dual Channel

DP-C ; DP-B

USB2.0

Azalia

SATA0

SATA1

DDR3 -SO-DIMM X 2DDR3 1066/1333M Hz 1.5V

BAN K 0, 1, 2, 3

DP X 2(Docking)

USB x2(Docking)

Page 28

Page 28

FingerPrinter VFM451

USBx1

Page 31

USB conn x 3(For I/O)

BT Conn USB x 1

USB x1(Camara)

MDC V1.5

Audio CKT

IDT 92HD75

Audio Board

SATA ODD Connector

Page 26

Page 20

Page 25

Page 12

2.5" SATA HDD Connector

Page 12

Page 9,10

Clock Generator

IC S9L PRS397

daughte r board

RJ1 1

TPA6047A

AMP & Audio Jack

Page 36

(2) PS/2 In terfaces

(2) USB 2.channels

(2) SATA Channels

(2) Display Port Channels

(1) Seria l Port

(1) Parall el Port

(1) Li ne In

Docking CONN.

(1) Lin e Out

Power OK CKT.

Page 32

4 4

Power On/Off CKT.

Page 25

DC/DC Interface CKT.

Page 33

A

TPM1.2

SLB9635TT

Page 31 page 29

Touch Pad CONN.

TrackPoint CONN.

SPI ROM

8 M B

B

SMSC KBC 1098

Page 25

Page 25

Page 31

Int.KBD

Page 25

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

SMSC Super I/O

SMCS47N217N

COM1 LPT

( Docking ) ( Docking )

Page 30 Page 30

2008/09/15 2009/12/31

Page 30

Compal Secret Data

Deciphered Date

D

Title

Size Docume nt Number Re v

Cust om

Date : Sheet o f

(1) RJ45 (10/100/1000)

(1) VGA

(1) 2 LAN indicator LED's

(1) Power Button

(1) I2C interface

Compal Electronics, Inc.

Block Diagram

LA-4902P

E

Page 26

CK505

Page 11

Page 25

Audio Board

0.3

2 47Wedn esday, De cember 09, 200 9

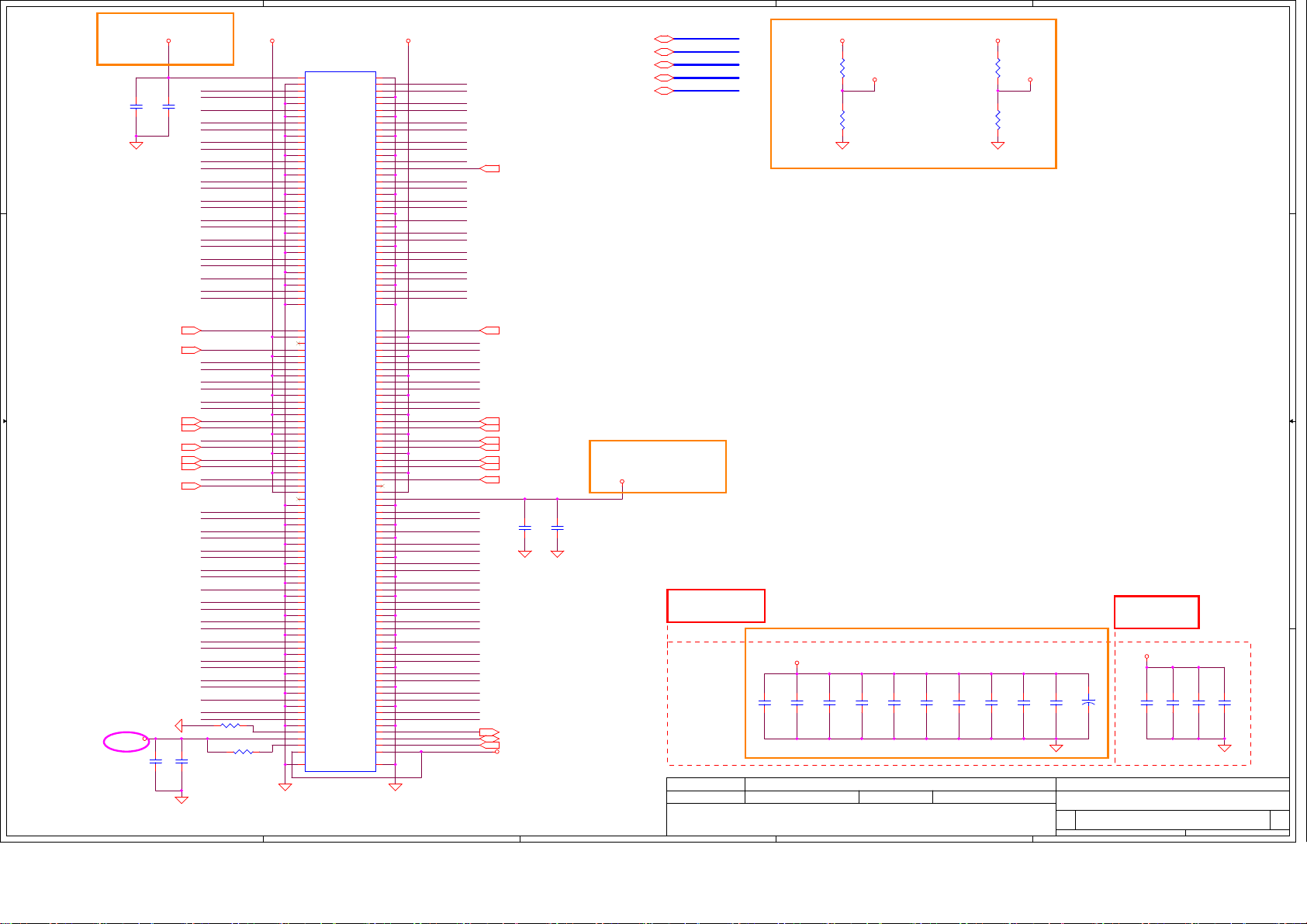

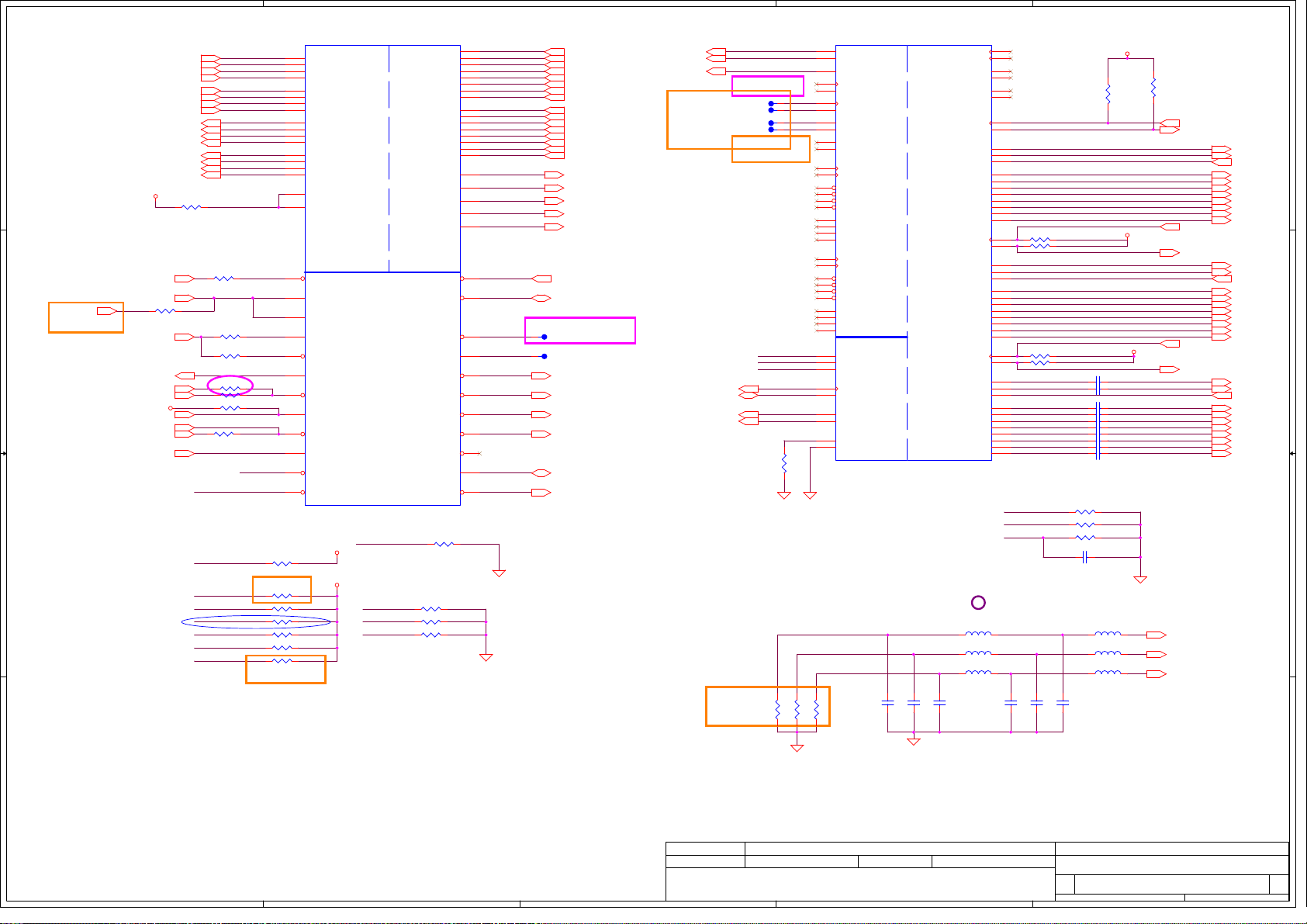

Page 3

A

hexainf@hotmail.com

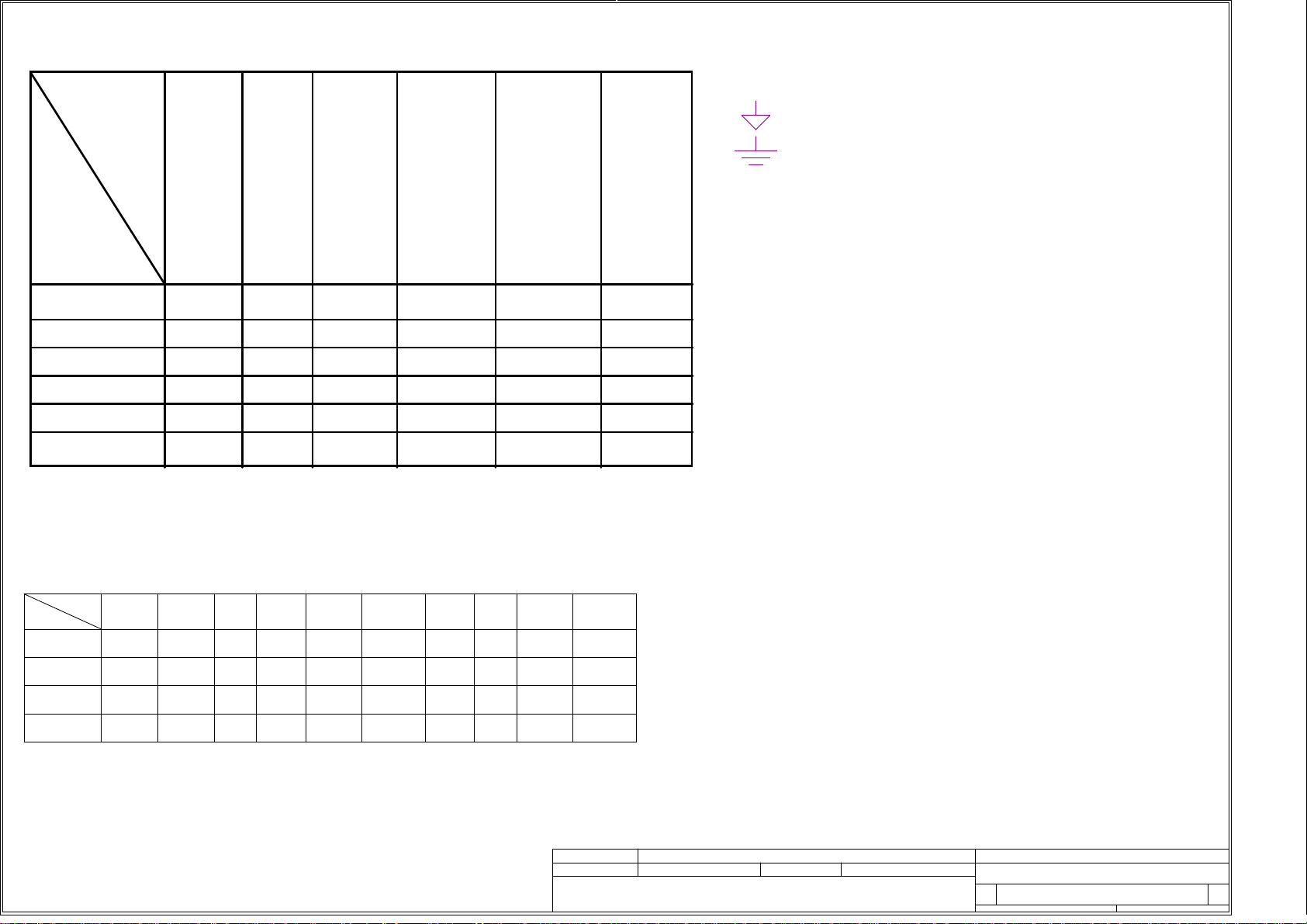

Voltage Rails

State

S0

S1

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

1 1

( O MEANS ON X MEANS OFF )

+RTCVCC

power

plane

O

O

O

O

O

O

+B

+3VL +0.75V

O

O

O

O

O

X

+5VALW

+3VALW

O

O

O

O

X

X X X

+3VM

+1.05VM

O

O

O

O

X

X

+1.5V

O

X X

X

+5VS

+3VS

+1.5VS

+VCCP

+CPU_CORE

+1.05V S

+1.8VS

OO

OO

X

X

Symbol Note :

: means Digital Ground

: means Analog Ground

@ : means just reserve , no build

CONN@ : means ME part.

Install below 45 level BOM structure for ver. 0.1

45@ : means just put it in the BOM of 45 level.

Install below 43 level BOM structure for ver. 0.1

DEBUG@ : means just build when PCIE port 80 CARD function enable.

N10M@ : Install for N10M Graphic controller

1098@ : Install for 1098 KBC controller

Remove before MP

SMBUS Control Table

SOURCE

SMB_EC_CK1

SMB_EC_DA1

SMBCLK

SMBDATA

SML0CLK

SML0DATA

SML1CLK

SML1DATA

SMSC1098

Calpella

Calpella

Calpella

BATT

V

X

X

X

THERMAL

SODIMM CLK CHIP

XDP G-SENSOR

X

X X

V V

X

X

X X

MINI CARD

X

V V

X

X

X X

DOCK

X

V

X

X

SENSOR

NIC

X X

X

V

X

X

X

V

X

V

X

V

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Reserve below BOM structure for ver. 0.1

1091@ : Install for 1091 KBC controller

2008/09/15 2009/12/31

A

Compal Secret Data

Deciphered Date

Title

Size Docume nt Number Re v

Cust om

Date : Sheet o f

Compal Electronics, Inc.

Notes List

LA-4902P

3 47Wedn esday, De cember 09, 200 9

0.3

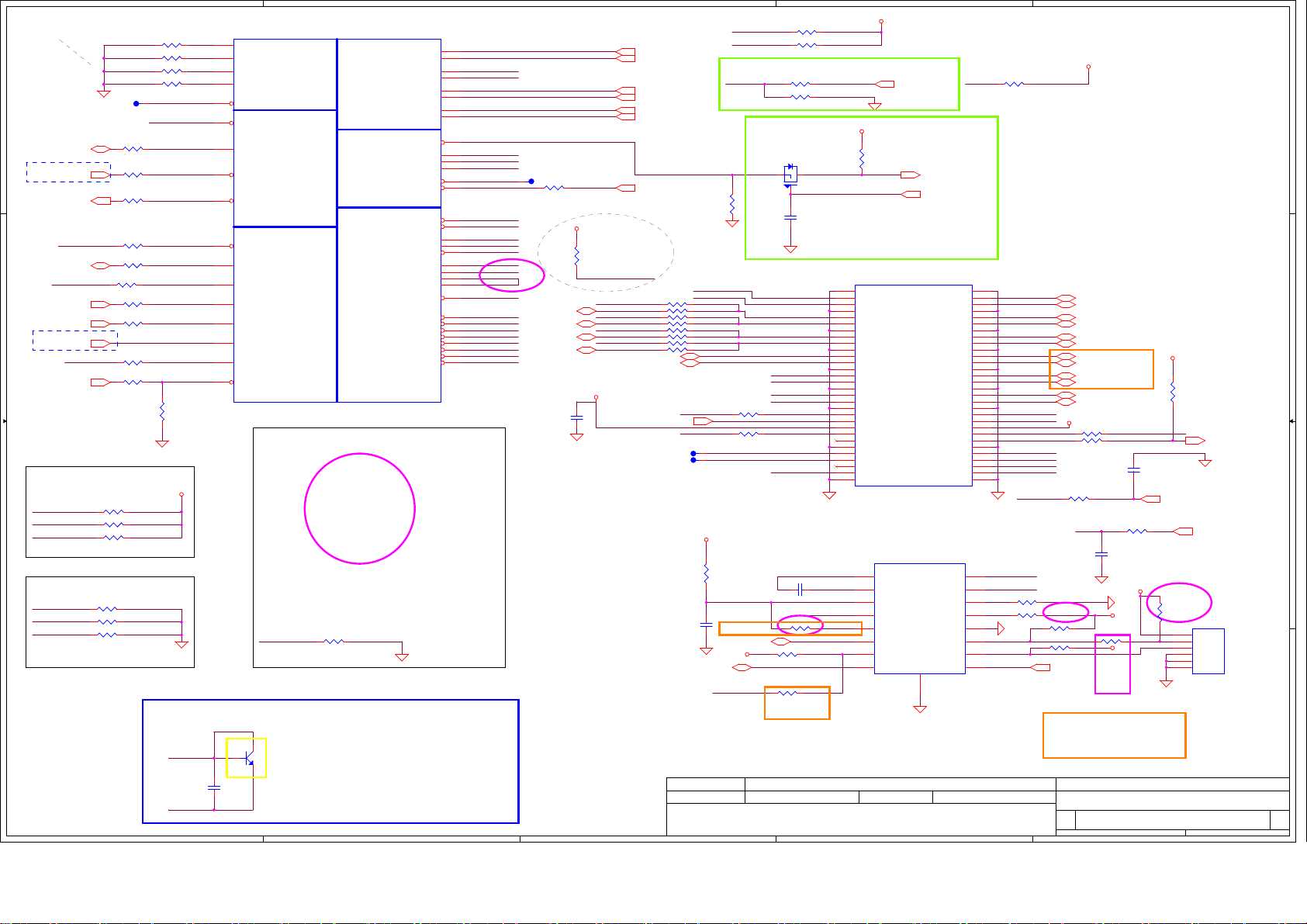

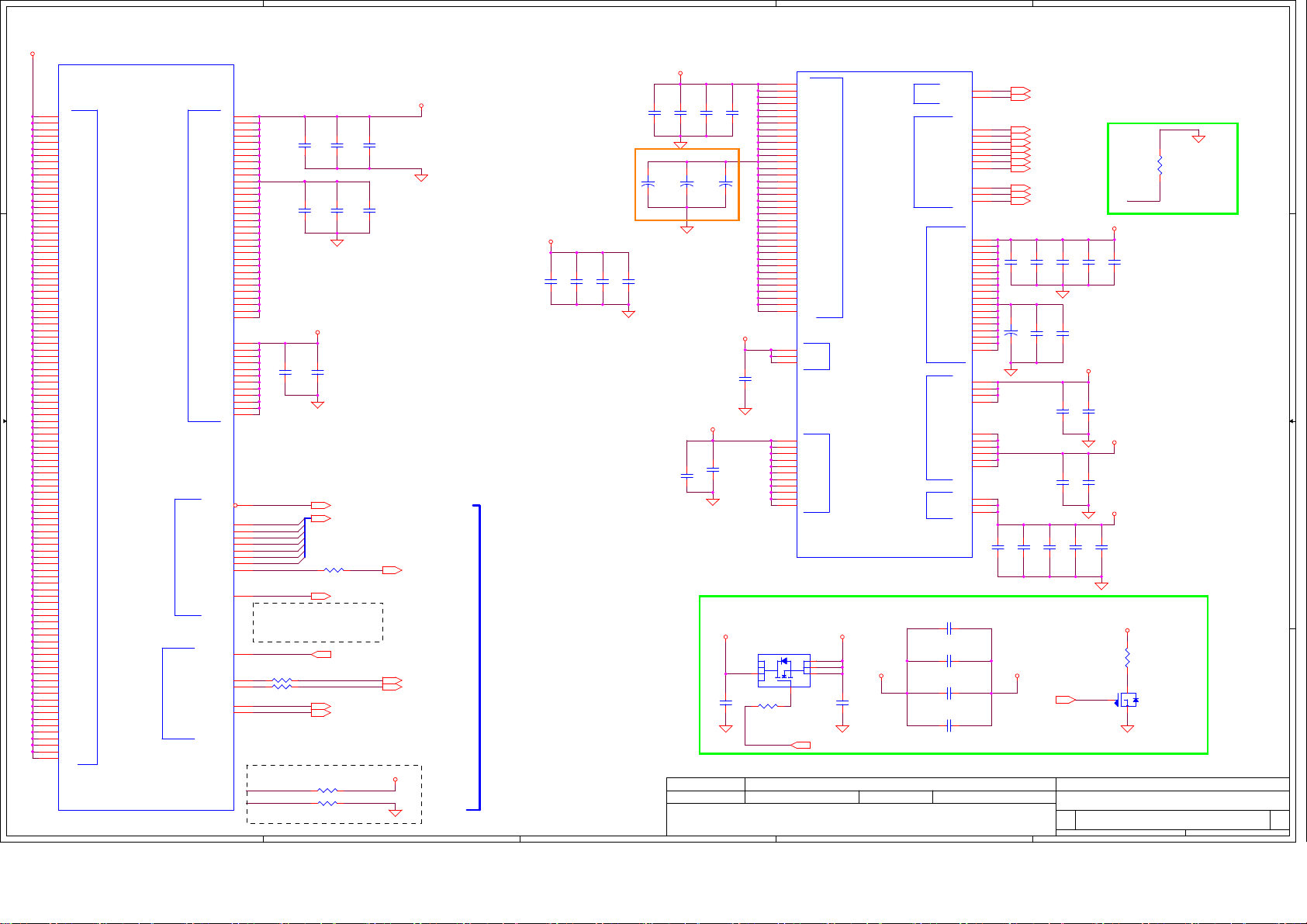

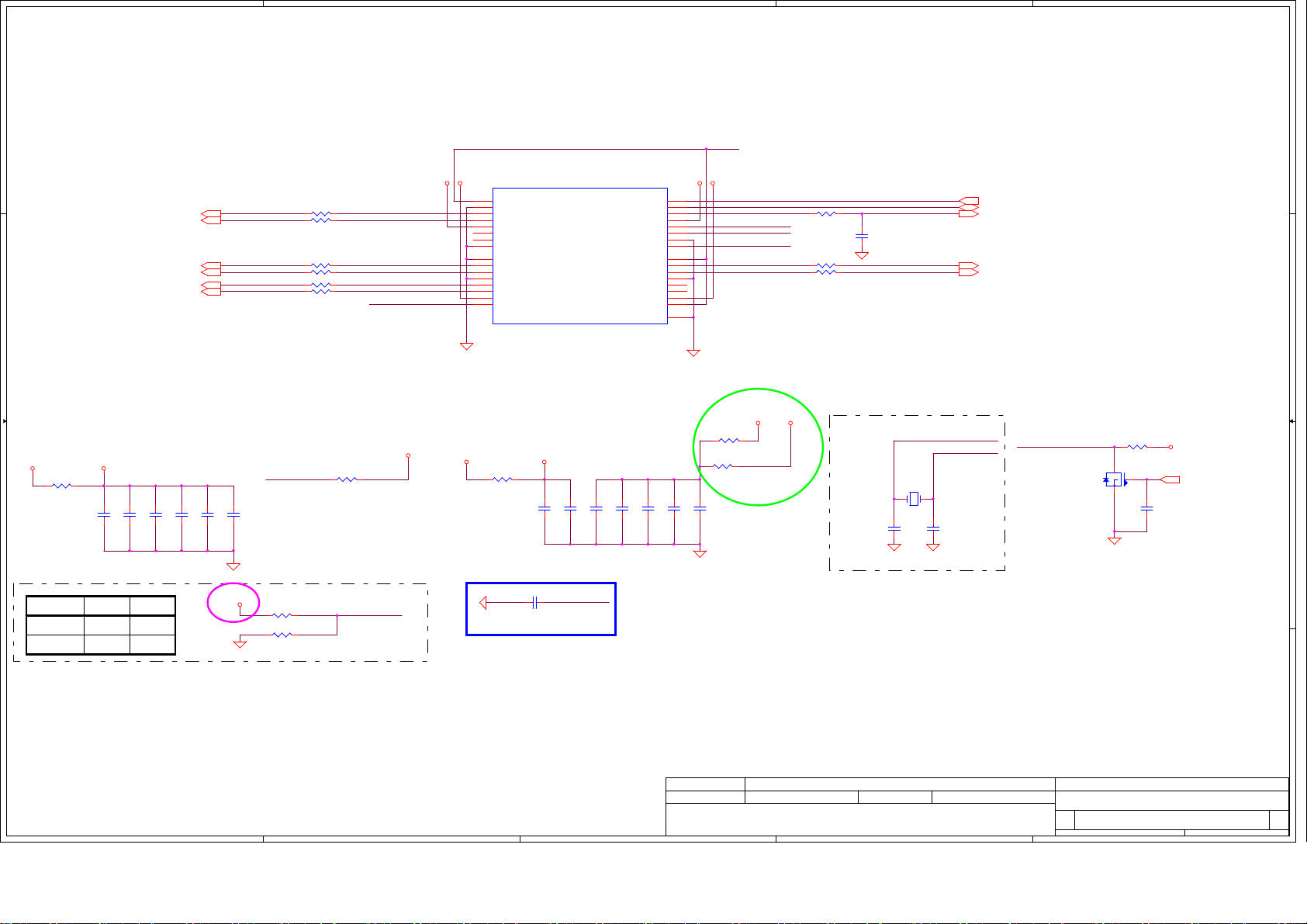

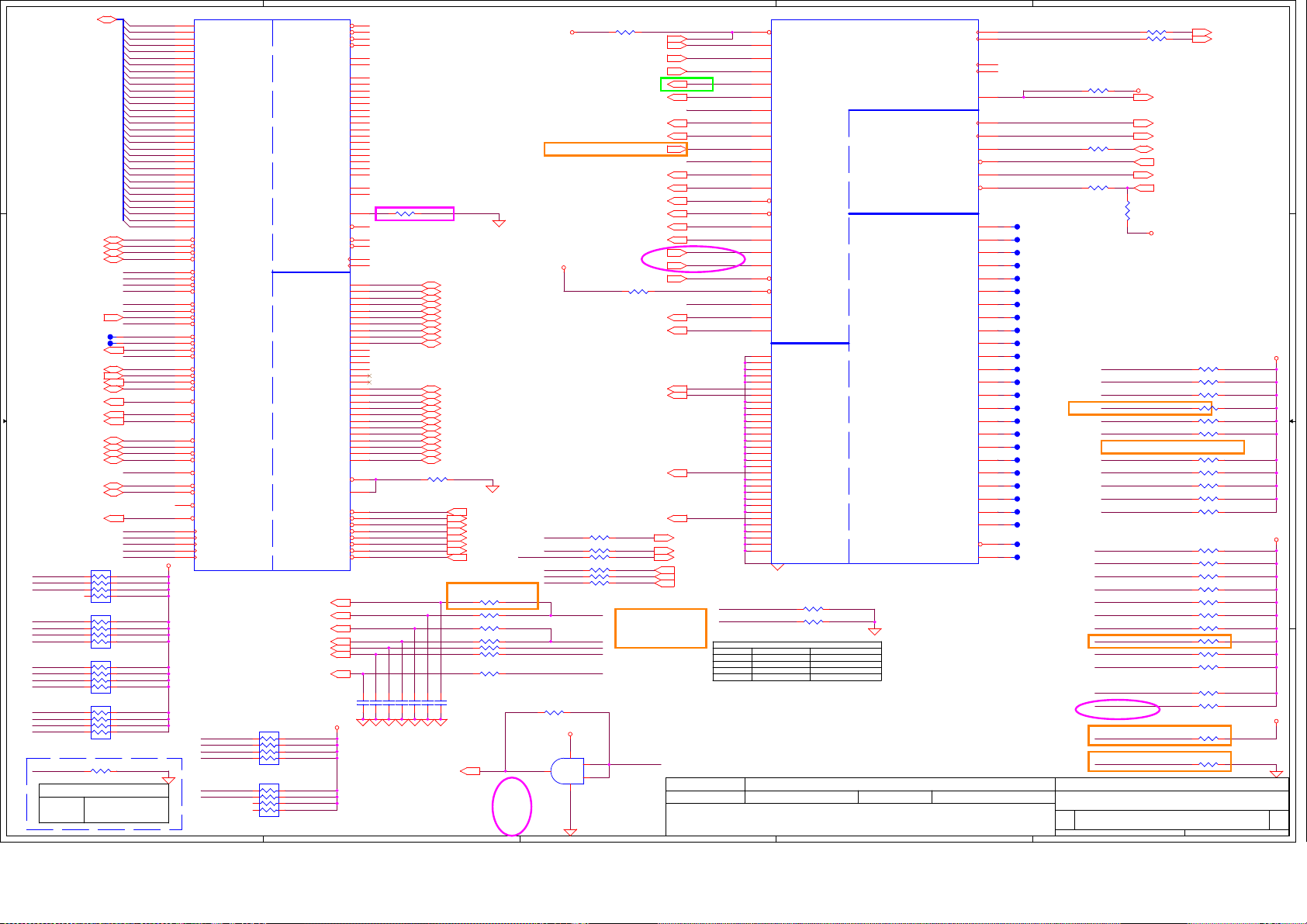

Page 4

Layout rule 1 0mil w i:dth trace

length < 0.5 ", spa cing 20mil

A A

H_PE CI15

to power; PU to VCCP at power side also

H_PRO CHOT#41

H_THER MTRIP#15

H_CPU RST#

H_PM _SYNC14

H_CP UPWR GD

H_CP UPWR GD15

B B

PM_DRA M_PWRGD14

from power

VTTPWR GOOD32

BUF_PLT_R ST#15

Processor P ullups

H_CAT ERR#

H_PRO CHOT#_D

C C

H_CPU RST#_R

DDR3 Compen sation Signals

SM_RCOMP0

R52 100_0402_1%

SM_RCOMP1

R53 24.9_0402_1%

SM_RCOMP2

R54 130_0402_1%

Layout Note :Please these

resistors n ear Processor

1

1 2

1 2

1 2

1 2

TP_SKTOCC#

T1TPC12

H_CAT ERR#

H_P ECI_ISO

R16

1 2

0_0402_5%

H_PRO CHOT#_D

R17

1 2

0_0402_5%

H_THE RMTRIP#_R

R19

1 2

0_0402_5%

R20

1 2

0_0402_5%

R21

1 2

0_0402_5%

SYS_AG ENT_PWR OK

R22

1 2

0_0402_5%

VCCPW RGOOD _0

R24

1 2

0_0402_5%

VDD PWRGO OD_R

R26

1 2

0_0402_5%

H_PW RGD_XDP_RH_PW RGD_XDP

R30

1 2

0_0402_5%

PLT_RST#_R

R31

1 2

1.5K_0402 _5%

R39 49.9_0402_1%

1 2

1 2

R42 68_0402_5%

1 2

R45 68_0402_5%@

1 2

1 2

1 2

COMP3

R220 _0402_1%

COMP2

R520 _0402_1%

COMP1

R74 9.9_0402_1%

COMP0

R94 9.9_0402_1%

H_CPU RST#_R

H_PM _SYNC_ R

12

R33

750_0402_1%

+VCCP

JCPU 1B

AT23

COMP3

AT24

COMP2

G16

COMP1

AT26

COMP0

AH24

SKTOCC#

AK14

CATERR#

AT15

PECI

AN26

PROCHOT#

AK15

THERMTRIP#

AP26

RESET_OBS#

AL15

PM_SYNC

AN14

VCCPWRGOOD_1

AN27

VCCPWRGOOD_0

AK13

SM_DRAMPWROK

AM15

VTTPWRGOOD

AM26

TAPPWRGOOD

AL14

RSTIN#

IC,A UB_CFD _rPGA,R 1P0

CON N@

JTAG MAPPING

XDP_TRST#

MISC THERMAL

PWR MANAGEMENT

09/2/5 HP

Close to XDP

1 2

R55 51_0402_5%

REMOTE thermal sensor

D D

REMOTE2+

C4

2200P_0402_ 50V7K

REMOTE2-

1

2

1

C

Q1

2

B

MMBT3904WH_SOT323-3

E

3 1

Layout Note:

place near t he hot test s pot area fo r

NB & t op SODI MM.

CLOCKS

DDR3

JTAG & BPM

2

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PM_EXT_TS#[0]

PM_EXT_TS#[1]

MISC

2

BCLK

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

PRDY#

PREQ#

TRST#

TDI_M

TDO_M

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

3

PM_EXTTS#0

CLK_C PU_BCLK

A16

CLK_C PU_BCLK#

B16

CLK_CP U_XDP

AR30

CLK_CP U_XDP#

AT30

CLK_EXP

E16

CLK_EXP#

D16

A18

A17

F6

SM_RCOMP0

AL1

SM_RCOMP1

AM1

SM_RCOMP2

AN1

PM_EXTTS#0

AN15

PM_EXTTS#1

AP15

XDP_ PRDY#

AT28

XDP_PREQ#

AP27

XDP_TCK

AN28

TCK

XDP_TMS

AP28

TMS

XDP_TRST#

AT27

XDP_TDI

AT29

TDI

XDP_TDO

AR27

TDO

XDP_TDI_M

AR29

XDP_TDO_M

AP29

XDP_DBRESET #

AN25

XDP_BPM#0

AJ22

XDP_BPM#1

AK22

XDP_BPM#2

AK24

XDP_BPM#3

AJ24

XDP_BPM#4

AJ25

XDP_BPM#5

AH22

XDP_BPM#6

AK23

XDP_BPM#7

AH23

T2 TPC12

1 2

R18 0_0402_5%

+VCCP

09/2/5 HP

CFG1 25

CFG1 35

CFG1 45

CFG1 55

C1

0.1U_0 402_16V4Z

@

R846

1K_0402_5%

1 2

+VCCP

1

2

CLK_C PU_BCLK 15

CLK_C PU_BCLK# 15

CLK_EXP 13

CLK_EXP# 13

CLK_D P 13

CLK_D P# 13

PM_EXTTS#1_R 9,10

10/09 HP

@

PM_PWR BTN#_R

XDP_BPM#0

R1013 0_0402_5%

R1010 0_0402_5%@

XDP_BPM#1

R1014 0_0402_5%

R1009 0_0402_5%@

XDP_BPM#2

R1015 0_0402_5%

R1011 0_0402_5%@

R1016 0_0402_5%

R1012 0_0402_5%@

PM_PWR BTN#_R12,14

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

CFG1 75 CFG1 0 5

CFG1 65

H_CP UPWR GD

H_PW RGD_XDP

T110TPC12

T111TPC12

C3

0.1U_0 402_16V4Z

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

PM_EXTTS#1

VDD PWRGO OD_R

09/07/02 HP

from DDR

12

XDP_PREQ#

XDP_ PRDY#

R25

1K_0402_5%

1 2

1 2

R27 0_0402_5%

Thermal Sensor EMC2113 with CPU PWM FAN

+3VS

R35

68_0402_5%

1 2

+3VS_THER

1

SI1 NO1 5

09/2/5 HP

2

THERM_ SCI#15

+3VS

H_THER MTRIP#

1 2

R1 10K_0402_5%

1 2

R3 10K_0402_5%

SI1 NO3 0

R14

1.5K_0402_ 1%

1 2

750_0402_1%

1 2

R15

+1.5V

Q88

SSM3K7002F _SC59-3

D

S

13

G

2

R1989

100K_0402_5%@

2

C1035

0.1U_0 402_16V4Z

1

09/07/02 HP

CPU XDP Connector

JP1

1

3

5

XDP_BPM#0_R

XDP_BPM#1_R

XDP_BPM#2_R

XDP_BPM#3_RXDP_BPM#3

XDP_BPM#4

XDP_BPM#5

XDP_BPM#6

XDP_BPM#7

H_CP UPW RGD_R

PM_PWR BTN#_R

XDP_TCK

1 2

C2 2200P_04 02_50V7K

FAN_P WM-R

R1082

1 2

@

1 2

R48 10K_0402_5%

1 2

R51 0_0402_5%

SI1 NO2 5

09/2/5 HP

2008/09/15 2009/12/31

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

SAMTE_BSH -030-01-L-D-A CON N@

H_THE RMDC

H_TH ERMDA

ADDR _SEL

10K_0402_5%

Add 0ohm a nd 0.1u

Compal Secret Data

4

+VCCP

VCCP_ 1.5VSPW RGD 32

R1133

1K_0402_5%

1 2

GPIO50 from PCH

S3 CPU Pow er Rail Change

GND0

OBSFN_A0

OBSFN_A1

GND2

OBSDATA_A0

OBSDATA_A1

GND4

OBSDATA_A2

OBSDATA_A3

GND6

OBSFN_B0

OBSFN_B1

GND8

OBSDATA_B0

OBSDATA_B1

GND10

OBSDATA_B2

OBSDATA_B3

GND12

PWRGOOD/HOOK0

HOOK1

VCC_OBS_AB

HOOK2

HOOK3

GND14

SDA

SCL

TCK1

TCK0

GND16

U54

1

DN

2

DP

3

VDD

4

PWM_IN

5

ADDR_SEL

6

ALERT#

7

SYS_SHDN#

8

SMDATA

Deciphered Date

4

XDP_TDO

DRAMRST # 9,10

PCH_ DDR_RS T 15

GND1

OBSFN_C0

OBSFN_C1

GND3

OBSDATA_C0

OBSDATA_C1

GND5

OBSDATA_C2

OBSDATA_C3

GND7

OBSFN_D0

OBSFN_D1

GND9

OBSDATA_D0

OBSDATA_D1

GND11

OBSDATA_D2

OBSDATA_D3

GND13

ITPCLK/HOOK4

ITPCLK#/HOOK5

VCC_OBS_CD

RESET#/HOOK6

DBR#/HOOK7

GND15

TD0

TRST#

TDI

TMS

GND17

DP2/DN3

DN2/DP3

TRIP_SET

SHDN_SEL

GND

PWM

TACH

SMCLK

GND

EMC2113-2-AX_QFN 16_4X4

17

1 2

R10 51_0402_5%

This shall place near XDP

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

CLK_CP U_XDP

40

CLK_CP U_XDP#

42

44

XDP_RST#_R

46

XDP_DBRE SET#_R

48

50

XDP_TDO

52

XDP_TRST#

54

XDP_TDI

56

XDP_TMS

58

60

XDP_RST#_R

REMOTE2+

16

REMOTE2-

15

R38

R43

FAN_PW M_OUT

TACH

2.05K_0402_1%

10K_0402_5%

14

13

12

11

10

9

5

+VCCP

CFG8 5

CFG9 5

CFG0 5

CFG1 5

CFG2 5

CFG3 5

CFG1 1 5

CFG4 5

CFG5 5

CFG6 5

CFG7 5

+VCCP

1K_0402_5%

R28

1 2

1 2

R29 0_0402_5%

@

1 2

R32 0_0402_5%

FAN_P WM-R

09/2/5 HP

R44

10K_0402_5%

@

R9980_04 02_5%

10K_0402_5%

SMB_CLK_S3 9,10, 11,13,26SMB_DATA_S39,10,1 1,13,26

1 2

R47

SI1 NO3

09/3/9 HP

H_CPU RST#

XDP_DBRESET #

PLT_RST#

1 2

R910 0_0402_5%

2

C884

0.1U_0 402_16V4Z

1

@

10/16 HP Add

+3VS

+3VS

2

@

C1047

0.1U_0 402_16V4Z

1

+5VS

+3VS

1 2

HP 10/21

R23

1K_0402_5%

1 2

XDP_DBRESET # 12,14

PLT_RST# 1 2,15,21,2 3,25,31

FAN_PW M 29

09/2/5 HP

R997

10K_0402_5%

ACES_85205 -04001

CON N@

1

2

3

4

5

6

JP2

1

2

3

4

G5

G6

DB1 No8 2

SI1 NO3 9

R997 : i nsta ll

R44: un inst all

09/4/10 HP

Title

Size Docum ent Num ber R ev

Cus tom

Dat e: Sheet o f

Compal Electronics, Inc.

Auburndale(1/5)-Thermal/XDP

LA-4902P

5

4 47Wed nesda y, Decem ber 09, 2 009

0.3

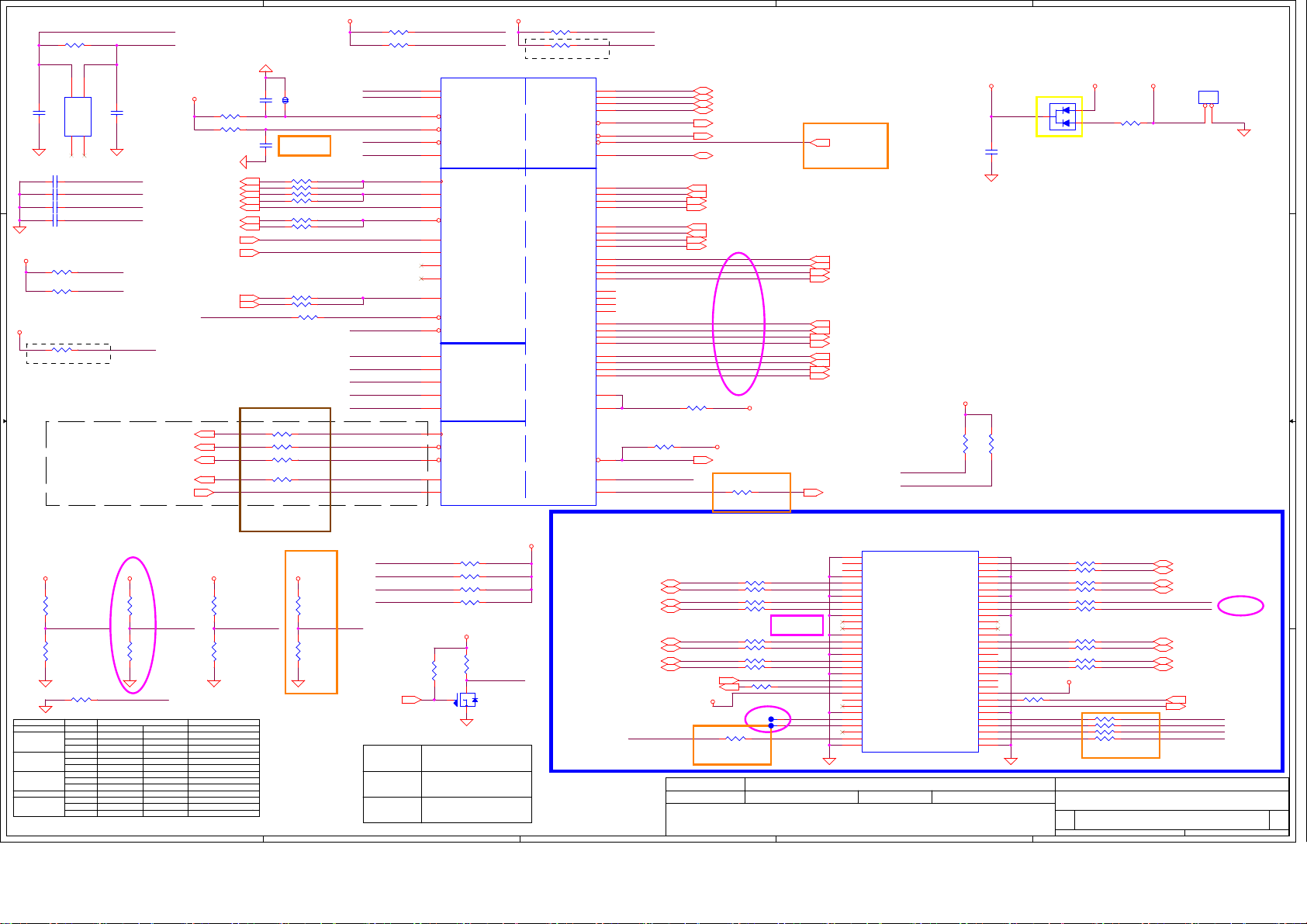

Page 5

1

hexainf@hotmail.com

JCP U1A

DMI_CRX_PTX_N014

DMI_CRX_PTX_N114

DMI_CRX_PTX_N214

DMI_CRX_PTX_N314

DMI_CRX_PTX_P014

DMI_CRX_PTX_P114

A A

DMI_CRX_PTX_P214

DMI_CRX_PTX_P314

DMI_CTX_PRX_N014

DMI_CTX_PRX_N114

DMI_CTX_PRX_N214

DMI_CTX_PRX_N314

DMI_CTX_PRX_P014

DMI_CTX_PRX_P114

DMI_CTX_PRX_P214

DMI_CTX_PRX_P314

FDI_CTX_ PRX_N014

FDI_CTX_ PRX_N114

FDI_CTX_ PRX_N214

FDI_CTX_ PRX_N314

FDI_CTX_ PRX_N414

FDI_CTX_ PRX_N514

FDI_CTX_ PRX_N614

FDI_CTX_ PRX_N714

FDI_CTX_ PRX_P014

FDI_CTX_ PRX_P114

FDI_CTX_ PRX_P214

FDI_CTX_ PRX_P314

FDI_CTX_ PRX_P414

FDI_CTX_ PRX_P514

B B

FDI_CTX_ PRX_P614

FDI_CTX_ PRX_P714

FDI _FSY NC014

FDI _FSY NC114

FDI_ INT14

FDI _LSYN C014

FDI _LSYN C114

FDI_CTX_ PRX_N0

FDI_CTX_ PRX_N1

FDI_CTX_ PRX_N2

FDI_CTX_ PRX_N3

FDI_CTX_ PRX_N4

FDI_CTX_ PRX_N5

FDI_CTX_ PRX_N6

FDI_CTX_ PRX_N7

FDI_CTX_ PRX_P0

FDI_CTX_ PRX_P1

FDI_CTX_ PRX_P2

FDI_CTX_ PRX_P3

FDI_CTX_ PRX_P4

FDI_CTX_ PRX_P5

FDI_CTX_ PRX_P6

FDI_CTX_ PRX_P7

FDI _FSY NC0

FDI _FSY NC1

FDI_ INT

FDI _LSY NC0

FDI _LSY NC1

A24

C23

B22

A21

B24

D23

B23

A22

D24

G24

F23

H23

D25

F24

E23

G23

E22

D21

D19

D18

G21

E19

F21

G18

D22

C21

D20

C18

G22

E20

F20

G19

F17

E17

C17

F18

D17

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

FDI_TX#[0]

FDI_TX#[1]

FDI_TX#[2]

FDI_TX#[3]

FDI_TX#[4]

FDI_TX#[5]

FDI_TX#[6]

FDI_TX#[7]

FDI_TX[0]

FDI_TX[1]

FDI_TX[2]

FDI_TX[3]

FDI_TX[4]

FDI_TX[5]

FDI_TX[6]

FDI_TX[7]

FDI_FSYNC[0]

FDI_FSYNC[1]

FDI_INT

FDI_LSYNC[0]

FDI_LSYNC[1]

PEG_ICOMPO

PEG_RCOMPO

DMI Intel(R) FDI

PCI EXPRESS -- GRAPHICS

C C

IC,A UB_CFD _rPGA,R1 P0

CON N@

PEG_ICOMPI

PEG_RBIAS

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

B26

A26

B27

A25

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

2

EXP_ICOMPI

EXP_RBIAS

C903 0.1U_04 02_10V7K

C904 0.1U_04 02_10V7K

1 2

1 2

R56 49.9_0402_1 %

1 2

R57 750_0402_1%

1 2

DB2: No . 69

MB_C_DP _DATA0_N

MB_C_DP_D ATA0_P

C905 0.1U_0402 _10V7K

C858 0.1U_0402 _10V7K

Layout rule:trace

length < 0.5"

MB_DP_AUXN 20

MB_DP_AUXP 20

1 2

1 2

Q65

SSM3K7002F _SC59-3

MB_DP_DAT A0_N 20

MB_DP_DAT A0_P 20

+VCCP

D

S

3

12

R801

7.5K_0402 _1%

13

2

G

12

R800

100K_0402_5%

MB_DP _HPD 20

+V_D DR_CPU_ REF0

+V_D DR_CPU_ REF1

CFG04

CFG14

CFG24

CFG34

CFG44

CFG54

CFG64

CFG74

CFG84

CFG94

CFG1 04

CFG1 14

CFG1 24

CFG1 34

CFG1 44

CFG1 54

CFG1 64

CFG1 74

T21 T PC12

R65

0_0402_5%@

1 2

1 2

0_0402_5%@

R66

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG 10

CFG 11

CFG 12

CFG 13

CFG 14

CFG 15

CFG 16

CFG 17

CFG 18

AP25

AL25

AL24

AL22

AJ33

AM30

AM28

AP31

AL32

AL30

AM31

AN29

AM32

AK32

AK31

AK28

AJ28

AN30

AN32

AJ32

AJ29

AJ30

AK30

AG9

M27

L28

J17

H17

G25

G17

E31

E30

H16

B19

A19

A20

B20

U9

T9

AC9

AB9

C1

A3

J29

J28

A34

A33

C35

B35

4

JCPU 1E

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

SA_DIMM_VREF

SB_DIMM_VREF

RSVD11

RSVD12

RSVD13

RSVD14

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

RSVD_TP_86

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD_NCTF_23

RSVD_NCTF_24

RSVD26

RSVD27

RSVD_NCTF_28

RSVD_NCTF_29

RSVD_NCTF_30

RSVD_NCTF_31

RESERVED

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD_NCTF_37

RSVD38

RSVD39

RSVD_NCTF_40

RSVD_NCTF_41

RSVD_NCTF_42

RSVD_NCTF_43

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

RSVD53

RSVD_NCTF_54

RSVD_NCTF_55

RSVD_NCTF_56

RSVD_NCTF_57

RSVD58

RSVD_TP_59

RSVD_TP_60

RSVD62

RSVD63

RSVD64

RSVD65

RSVD_TP_66

RSVD_TP_67

RSVD_TP_68

RSVD_TP_69

RSVD_TP_70

RSVD_TP_71

RSVD_TP_72

RSVD_TP_73

RSVD_TP_74

RSVD_TP_75

RSVD_TP_76

RSVD_TP_77

RSVD_TP_78

RSVD_TP_79

RSVD_TP_80

RSVD_TP_81

RSVD_TP_82

RSVD_TP_83

RSVD_TP_84

RSVD_TP_85

5

AJ13

AJ12

AH25

AK26

AL26

AR2

AJ26

AJ27

AP1

AT2

AT3

AR1

AL28

AL29

AP30

AP32

AL27

AT31

AT32

AP33

AR33

AT33

AT34

AP35

AR35

AR32

E15

F15

A2

KEY

D15

C15

AJ15

AH15

R60

0_0402_5%

1 2

1 2

0_0402_5%

R61

@

@

09/2/16 HP

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

AP34

VSS

T128TPC12

T129TPC12

6/30 HP

Deciphered Date

4

IC,A UB_CFD _rPGA,R 1P0

CON N@

Title

Size Docum ent Num ber R ev

Cus tom

Dat e: Sheet o f

Compal Electronics, Inc.

Auburndale(2/5)-DMI/PEG/FDI

LA-4902P

5

5 47Wed nesda y, Decem ber 09, 2 009

0.3

CFG Straps for PROCESSOR

CFG7CFG0

R67 3.01K_0402_ 1%@

1 2

PCI-Express Configurat ion Select

1: Single PEG

0: Bifurcat ion enabled

CFG0

Not applica ble for Cla rksfield Processor

CFG3

CFG3-PCI Ex press Stati c Lane Reversal

CFG3

D D

1

CFG4

CFG4-Displa y Port Presence

CFG4

@

R69 3.01K_0402_ 1%

1 2

1: Normal O peration

0: Lane Num bers Reversed

15 -> 0, 14 ->1, .....

R70 3.01K_0402_ 1%

1 2

1: Disabled ; No Physic al Display Port

attached to Embedded D isplay Port

0: Enabled; An externa l Display Port

device is c onnected to the Embedded

Display Port

2

-240mV for Pre-ES1

R68 3.01K_0402_ 1%

1 2

Only tempor ary for ear ly CFD samp les (rPGA/BGA)

@

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2008/09/15 2009/12/31

Compal Secret Data

Page 6

1

2

3

4

5

AR10

AT10

JCP U1D

W8

SB_CK[0]

W9

SB_CK#[0]

B5

SB_DQ[0]

A5

SB_DQ[1]

C3

SB_DQ[2]

B3

SB_DQ[3]

E4

SB_DQ[4]

A6

SB_DQ[5]

A4

SB_DQ[6]

C4

SB_DQ[7]

D1

SB_DQ[8]

D2

SB_DQ[9]

F2

SB_DQ[10]

F1

SB_DQ[11]

C2

SB_DQ[12]

F5

SB_DQ[13]

F3

SB_DQ[14]

G4

SB_DQ[15]

H6

SB_DQ[16]

G2

SB_DQ[17]

J6

SB_DQ[18]

J3

SB_DQ[19]

G1

SB_DQ[20]

G5

SB_DQ[21]

J2

SB_DQ[22]

J1

SB_DQ[23]

J5

SB_DQ[24]

K2

SB_DQ[25]

L3

SB_DQ[26]

M1

SB_DQ[27]

K5

SB_DQ[28]

K4

SB_DQ[29]

M4

SB_DQ[30]

N5

SB_DQ[31]

AF3

SB_DQ[32]

AG1

SB_DQ[33]

AJ3

SB_DQ[34]

AK1

SB_DQ[35]

AG4

SB_DQ[36]

AG3

SB_DQ[37]

AJ4

SB_DQ[38]

AH4

SB_DQ[39]

AK3

SB_DQ[40]

AK4

SB_DQ[41]

AM6

SB_DQ[42]

AN2

SB_DQ[43]

AK5

SB_DQ[44]

AK2

SB_DQ[45]

AM4

SB_DQ[46]

AM3

SB_DQ[47]

AP3

SB_DQ[48]

AN5

SB_DQ[49]

AT4

SB_DQ[50]

AN6

SB_DQ[51]

AN4

SB_DQ[52]

AN3

SB_DQ[53]

AT5

SB_DQ[54]

AT6

SB_DQ[55]

AN7

SB_DQ[56]

AP6

SB_DQ[57]

AP8

SB_DQ[58]

AT9

SB_DQ[59]

AT7

SB_DQ[60]

AP9

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

AB1

SB_BS[0]

W5

SB_BS[1]

R7

SB_BS[2]

AC5

SB_CAS#

Y7

SB_RAS#

AC6

SB_WE#

DDR SYSTEM MEMORY - B

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

M3

V7

V6

M2

AB8

AD6

AC7

AD1

D4

E1

H3

K1

AH1

AL2

AR4

AT8

D5

F4

J4

L4

AH2

AL4

AR5

AR8

C5

E3

H4

M5

AG2

AL5

AP5

AR7

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

DDR_B _DM0

DDR_B _DM1

DDR_B _DM2

DDR_B _DM3

DDR_B _DM4

DDR_B _DM5

DDR_B _DM6

DDR_B _DM7

DDR_B _DQS#0

DDR_B _DQS#1

DDR_B _DQS#2

DDR_B _DQS#3

DDR_B _DQS#4

DDR_B _DQS#5

DDR_B _DQS#6

DDR_B _DQS#7

DDR _B_DQS0

DDR _B_DQS1

DDR _B_DQS2

DDR _B_DQS3

DDR _B_DQS4

DDR _B_DQS5

DDR _B_DQS6

DDR _B_DQS7

DDR_B _MA0

DDR_B _MA1

DDR_B _MA2

DDR_B _MA3

DDR_B _MA4

DDR_B _MA5

DDR_B _MA6

DDR_B _MA7

DDR_B _MA8

DDR_B _MA9

DDR_B _MA10

DDR_B _MA11

DDR_B _MA12

DDR_B _MA13

DDR_B _MA14

DDR_B _MA15

M_CLK _DDR2 10

M_CLK _DDR#2 10

DDR_C KE2_DIMMB 10

M_CLK _DDR3 10

M_CLK _DDR#3 10

DDR_C KE3_DIMMB 10

DDR_C S2_DIMMB# 10

DDR_C S3_DIMMB# 10

M_ODT2 10

M_ODT3 10

DDR _B_DM[ 0..7] 10

DDR _B_DQS #[0..7] 10

DDR _B_DQ S[0..7] 10

DDR _B_MA[0.. 15] 10

JCP U1C

A A

DDR _A_D[0 ..63]9

B B

C C

DDR_A _BS09

DDR_A _BS19

DDR_A _BS29

DDR _A_CAS#9

DDR _A_RAS#9

DDR_A _WE#9

DDR _A_D0

DDR _A_D1

DDR _A_D2

DDR _A_D3

DDR _A_D4

DDR _A_D5

DDR _A_D6

DDR _A_D7

DDR _A_D8

DDR _A_D9

DDR _A_D10

DDR _A_D11

DDR _A_D12

DDR _A_D13

DDR _A_D14

DDR _A_D15

DDR _A_D16

DDR _A_D17

DDR _A_D18

DDR _A_D19

DDR _A_D20

DDR _A_D21

DDR _A_D22

DDR _A_D23

DDR _A_D24

DDR _A_D25

DDR _A_D26

DDR _A_D27

DDR _A_D28

DDR _A_D29

DDR _A_D30

DDR _A_D31

DDR _A_D32

DDR _A_D33

DDR _A_D34

DDR _A_D35

DDR _A_D36

DDR _A_D37

DDR _A_D38

DDR _A_D39

DDR _A_D40

DDR _A_D41

DDR _A_D42

DDR _A_D43

DDR _A_D44

DDR _A_D45

DDR _A_D46

DDR _A_D47

DDR _A_D48

DDR _A_D49

DDR _A_D50

DDR _A_D51

DDR _A_D52

DDR _A_D53

DDR _A_D54

DDR _A_D55

DDR _A_D56

DDR _A_D57

DDR _A_D58

DDR _A_D59

DDR _A_D60

DDR _A_D61

DDR _A_D62

DDR _A_D63

AJ10

AL10

AK12

AK11

AM10

AR11

AL11

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

A10

SA_DQ[0]

C10

SA_DQ[1]

C7

SA_DQ[2]

A7

SA_DQ[3]

B10

SA_DQ[4]

D10

SA_DQ[5]

E10

SA_DQ[6]

A8

SA_DQ[7]

D8

SA_DQ[8]

F10

SA_DQ[9]

E6

SA_DQ[10]

F7

SA_DQ[11]

E9

SA_DQ[12]

B7

SA_DQ[13]

E7

SA_DQ[14]

C6

SA_DQ[15]

H10

SA_DQ[16]

G8

SA_DQ[17]

K7

SA_DQ[18]

J8

SA_DQ[19]

G7

SA_DQ[20]

G10

SA_DQ[21]

J7

SA_DQ[22]

J10

SA_DQ[23]

L7

SA_DQ[24]

M6

SA_DQ[25]

M8

SA_DQ[26]

L9

SA_DQ[27]

L6

SA_DQ[28]

K8

SA_DQ[29]

N8

SA_DQ[30]

P9

SA_DQ[31]

AH5

SA_DQ[32]

AF5

SA_DQ[33]

AK6

SA_DQ[34]

AK7

SA_DQ[35]

AF6

SA_DQ[36]

AG5

SA_DQ[37]

AJ7

SA_DQ[38]

AJ6

SA_DQ[39]

SA_DQ[40]

AJ9

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

AK8

SA_DQ[44]

AL7

SA_DQ[45]

SA_DQ[46]

AL8

SA_DQ[47]

AN8

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

AM9

SA_DQ[52]

AN9

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

AC3

SA_BS[0]

AB2

SA_BS[1]

U7

SA_BS[2]

AE1

SA_CAS#

AB3

SA_RAS#

AE9

SA_WE#

DDR SYSTEM MEMORY A

SA_CK[0]

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AA6

AA7

P7

Y6

Y5

P6

AE2

AE8

AD8

AF9

B9

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

DDR_A _DM0

DDR_A _DM1

DDR_A _DM2

DDR_A _DM3

DDR_A _DM4

DDR_A _DM5

DDR_A _DM6

DDR_A _DM7

DDR_A _DQS#0

DDR_A _DQS#1

DDR_A _DQS#2

DDR_A _DQS#3

DDR_A _DQS#4

DDR_A _DQS#5

DDR_A _DQS#6

DDR_A _DQS#7

DDR _A_DQS0

DDR _A_DQS1

DDR _A_DQS2

DDR _A_DQS3

DDR _A_DQS4

DDR _A_DQS5

DDR _A_DQS6

DDR _A_DQS7

DDR_A _MA0

DDR_A _MA1

DDR_A _MA2

DDR_A _MA3

DDR_A _MA4

DDR_A _MA5

DDR_A _MA6

DDR_A _MA7

DDR_A _MA8

DDR_A _MA9

DDR_A _MA10

DDR_A _MA11

DDR_A _MA12

DDR_A _MA13

DDR_A _MA14

DDR_A _MA15

M_CLK _DDR0 9

M_CLK _DDR#0 9

DDR_C KE0_DIMMA 9

M_CLK _DDR1 9

M_CLK _DDR#1 9

DDR_C KE1_DIMMA 9

DDR_C S0_DIMMA# 9

DDR_C S1_DIMMA# 9

M_ODT0 9

M_ODT1 9

DDR _A_DM[ 0..7] 9

DDR _A_DQS #[0..7] 9

DDR _A_DQ S[0..7] 9

DDR _A_MA[0.. 15] 9

DDR _B_D[0 ..63]10

DDR_B _BS010

DDR_B _BS110

DDR_B _BS210

DDR_ B_CAS#10

DDR_ B_RAS#10

DDR_B _WE#10

DDR _B_D0

DDR _B_D1

DDR _B_D2

DDR _B_D3

DDR _B_D4

DDR _B_D5

DDR _B_D6

DDR _B_D7

DDR _B_D8

DDR _B_D9

DDR _B_D10

DDR _B_D11

DDR _B_D12

DDR _B_D13

DDR _B_D14

DDR _B_D15

DDR _B_D16

DDR _B_D17

DDR _B_D18

DDR _B_D19

DDR _B_D20

DDR _B_D21

DDR _B_D22

DDR _B_D23

DDR _B_D24

DDR _B_D25

DDR _B_D26

DDR _B_D27

DDR _B_D28

DDR _B_D29

DDR _B_D30

DDR _B_D31

DDR _B_D32

DDR _B_D33

DDR _B_D34

DDR _B_D35

DDR _B_D36

DDR _B_D37

DDR _B_D38

DDR _B_D39

DDR _B_D40

DDR _B_D41

DDR _B_D42

DDR _B_D43

DDR _B_D44

DDR _B_D45

DDR _B_D46

DDR _B_D47

DDR _B_D48

DDR _B_D49

DDR _B_D50

DDR _B_D51

DDR _B_D52

DDR _B_D53

DDR _B_D54

DDR _B_D55

DDR _B_D56

DDR _B_D57

DDR _B_D58

DDR _B_D59

DDR _B_D60

DDR _B_D61

DDR _B_D62

DDR _B_D63

IC,A UB_CFD _rPGA,R1 P0

CON N@

D D

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

1

2

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

IC,A UB_CFD _rPGA,R1 P0

CON N@

2008/09/15 2009/12/31

Compal Secret Data

Deciphered Date

Title

Size Docum ent Num ber R ev

Cus tom

4

Dat e: Sheet o f

Compal Electronics, Inc.

Auburndale(3/5)-DDR3

LA-4902P

5

6 47Wed nesda y, Decem ber 09, 2 009

0.3

Page 7

1

hexainf@hotmail.com

+CPU _CORE

JCP U1F

A A

B B

C C

D D

48A 15A18A

AG35

VCC1

AG34

VCC2

AG33

VCC3

AG32

VCC4

AG31

VCC5

AG30

VCC6

AG29

VCC7

AG28

VCC8

AG27

VCC9

AG26

VCC10

AF35

VCC11

AF34

VCC12

AF33

VCC13

AF32

VCC14

AF31

VCC15

AF30

VCC16

AF29

VCC17

AF28

VCC18

AF27

VCC19

AF26

VCC20

AD35

VCC21

AD34

VCC22

AD33

VCC23

AD32

VCC24

AD31

VCC25

AD30

VCC26

AD29

VCC27

AD28

VCC28

AD27

VCC29

AD26

VCC30

AC35

VCC31

AC34

VCC32

AC33

VCC33

AC32

VCC34

AC31

VCC35

AC30

VCC36

AC29

VCC37

AC28

VCC38

AC27

VCC39

AC26

VCC40

AA35

VCC41

AA34

VCC42

AA33

VCC43

AA32

VCC44

AA31

VCC45

AA30

VCC46

AA29

VCC47

AA28

VCC48

AA27

VCC49

AA26

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

IC,A UB_CFD _rPGA,R1 P0

CON N@

CPU CORE SUPPLY

1

POWER

SENSE LINES

1.1V RAIL POWER

PROC_DPRSLPVR

CPU VIDS

VSS_SENSE_VTT

VTT0_1

VTT0_2

VTT0_3

VTT0_4

VTT0_5

VTT0_6

VTT0_7

VTT0_8

VTT0_9

VTT0_10

VTT0_11

VTT0_12

VTT0_13

VTT0_14

VTT0_15

VTT0_16

VTT0_17

VTT0_18

VTT0_19

VTT0_20

VTT0_21

VTT0_22

VTT0_23

VTT0_24

VTT0_25

VTT0_26

VTT0_27

VTT0_28

VTT0_29

VTT0_30

VTT0_31

VTT0_32

VTT0_33

VTT0_34

VTT0_35

VTT0_36

VTT0_37

VTT0_38

VTT0_39

VTT0_40

VTT0_41

VTT0_42

VTT0_43

VTT0_44

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VTT_SELECT

ISENSE

VCC_SENSE

VSS_SENSE

VTT_SENSE

PSI#

AH14

AH12

AH11

AH10

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

AN33

AK35

AK33

AK34

AL35

AL33

AM33

AM35

AM34

G15

10U_0805_6 .3V6M

1

2

H_VI D0

H_VI D1

H_VI D2

H_VI D3

H_VI D4

H_VI D5

H_VI D6

PM_DP RSLPVR_R

C66

H_VTTVID1 = Low, 1.1V

H_VTTVID1 = High, 1.05V

AN35

R75 0_0402_5%

1 2

AJ34

AJ35

1 2

R76 0_0402_5%

B15

A15

Close to CPU

VCCS ENSE

VSSSENS E

10U_0805_6 .3V6M

C58

1

1

2

2

22U_0805_6 .3V6M

C45

1

1

2

2

+VCCP

22U_0805_6 .3V6M

C67

1

2

PSI# 41

H_VI D[0.. 6] 41

1 2

R74 0_0402_5%

H_VTTVID 1 38

IMVP_IMON 41

VCCS ENSE

VSSSENS E

VTT_SENSE 38

VSS_SENSE_VTT 38

1 2

R77 100_0402_1%

1 2

R78 100_0402_1%

2

+VCCP

10U_0805_6 .3V6M

10U_0805_6 .3V6M

C39

C40

1

2

10U_0805_6 .3V6M

22U_0805_6 .3V6M

C57

C49

1

2

+CPU _CORE

C59

1

@

2

47P_0402_5 0V8J

47P_0402_5 0V8J

C61

C60

1

@

@

2

11/6 add to follow des ign guide.

CPU

PROC _DPRSLP VR 41

VCCS ENSE 41

VSSSENS E 41

+CPU _CORE

2

3

+GFX_CORE

10U_0805_6 .3V6M

10U_0805_6 .3V6M

C879

C878

1

1

2

2

1

1

+

+

C974

C973

2

2

330U_X_2VM_R6M

47P_0402_5 0V8J

47P_0402_5 0V8J

C62

1

1

@

2

2

10U_0805_6 .3V6M

1

2

10U_0805_6 .3V6M

1

2

SI1 NO3 6

C972

330U_X_2VM_R6M

+VCCP

C72

1

2

10U_0805_6 .3V6M

C881

C880

1

2

1

+

2

330U_X_2VM_R6M

+VCCP

1

2

22U_0805_6 .3V6M

C73

10U_0805_6 .3V6M

C75

JCPU 1G

AT21

VAXG1

AT19

VAXG2

AT18

VAXG3

AT16

VAXG4

AR21

VAXG5

AR19

VAXG6

AR18

VAXG7

AR16

VAXG8

AP21

VAXG9

AP19

VAXG10

AP18

VAXG11

AP16

VAXG12

AN21

VAXG13

AN19

VAXG14

AN18

VAXG15

AN16

VAXG16

AM21

VAXG17

AM19

VAXG18

AM18

VAXG19

AM16

VAXG20

AL21

VAXG21

AL19

VAXG22

AL18

VAXG23

AL16

VAXG24

AK21

VAXG25

AK19

VAXG26

AK18

VAXG27

AK16

VAXG28

AJ21

VAXG29

AJ19

VAXG30

AJ18

VAXG31

AJ16

VAXG32

AH21

VAXG33

AH19

VAXG34

AH18

VAXG35

AH16

VAXG36

J24

VTT1_45

J23

VTT1_46

H25

VTT1_47

K26

VTT1_48

J27

VTT1_49

J26

VTT1_50

J25

VTT1_51

H27

VTT1_52

G28

VTT1_53

G27

VTT1_54

G26

VTT1_55

F26

VTT1_56

E26

VTT1_57

E25

VTT1_58

IC,A UB_CFD _rPGA,R 1P0

CON N@

GRAPHICS

FDI PEG & DMI

+1.5V to +1.5V_CPU_VDDQ Transfer

SI7326DN- T1-E3_PAK1212-8

Q89

0.1U_04 02_10V6K

C1023

1

R1984

1 2

0_0402_5%

2

RUN ON

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2008/09/15 2009/12/31

+1.5V_ CPU_VDD Q+1.5V

1

2

35

0.1U_04 02_10V6K

C1024

4

1

2

RUNON 33

Compal Secret Data

4

VAXG_SENSE

VSSAXG_SENSE

SENSE

LINES

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_DPRSLPVR

GFX_IMON

GRAP HIC S VI Ds

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

4

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

DDR3 - 1.5V RAILS

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT1_63

VTT1_64

VTT1_65

1.1V1.8V

VTT1_66

VTT1_67

VTT1_68

VCCPLL1

VCCPLL2

VCCPLL3

C1020

1 2

0.1U_04 02_10V6K

C1021

1 2

0.1U_04 02_10V6K

C1022

1 2

0.1U_04 02_10V6K

C1025

1 2

0.1U_04 02_10V6K

3A

POWER

0.6A

Stich CAP b etween 1.5V and 1.5V-CPU_VDDQ

Deciphered Date

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

AR25

AT25

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

1

2

1

@

+

2

1U_060 3_10V4Z

C78

1

2

+1.5V_ CPU_VDD Q+1.5V

5

VCC_AXG_S ENSE 43

VSS_AXG_SENSE 43

GFXVR_ VID_0 43

GFXVR_ VID_1 43

GFXVR_ VID_2 43

GFXVR_ VID_3 43

GFXVR_ VID_4 43

GFXVR_ VID_5 43

GFXVR_ VID_6 43

GFXVR_EN 43

GFXVR _DPRSLPVR 43

GFXVR_IMO N 43

1U_060 3_10V4Z

1U_060 3_10V4Z

C51

C50

1

2

10U_0805_6. 3V6M

330U_D 2_2VY_R7M

C63

C64

1

2

1U_060 3_10V4Z

C79

1

1

2

2

SLP_S333

1U_060 3_10V4Z

1

2

10U_0805_6. 3V6M

1

2

22U_0805_6 .3V6M

1

2

22U_0805_6 .3V6M

1

2

2.2U_0 603_6.3V4Z

C80

+1.5V_ CPU_VDD Q

1U_060 3_10V4Z

C52

C53

1

2

C65

+VCCP

10U_0805_6 .3V6M

C71

C70

1

2

+VCCP

22U_0805_6 .3V6M

C77

C76

1

2

+1.8VS

10U_0805_6 .3V6M

C81

1

1

2

2

+1.5V_ CPU_VDD Q

SLP_S3

11/10 for Auburndal e pre-ES1

GFXVR_E N

1U_060 3_10V4Z

C54

1

2

4.7U_0 603_6.3V6K

C82

R1135

220_0402_1%

1 2

13

D

Q90

2

SSM3K7002F _SC59-3

G

S

R967

4.7K_0402 _5%

1 2

7/2/2009 HP

Title

Size Docum ent Num ber R ev

Cus tom

Dat e: Sheet o f

Compal Electronics, Inc.

Auburndale(4/5)-PWR

LA-4902P

5

06/30HP

0.3

7 47Wed nesda y, Decem ber 09, 2 009

Page 8

1

JCP U1H

AT20

VSS1

AT17

VSS2

AR31

VSS3

AR28

VSS4

AR26

VSS5

AR24

VSS6

AR23

VSS7

AR20

A A

B B

C C

D D

VSS8

AR17

VSS9

AR15

VSS10

AR12

VSS11

AR9

VSS12

AR6

VSS13

AR3

VSS14

AP20

VSS15

AP17

VSS16

AP13

VSS17

AP10

VSS18

AP7

VSS19

AP4

VSS20

AP2

VSS21

AN34

VSS22

AN31

VSS23

AN23

VSS24

AN20

VSS25

AN17

VSS26

AM29

VSS27

AM27

VSS28

AM25

VSS29

AM20

VSS30

AM17

VSS31

AM14

VSS32

AM11

VSS33

AM8

VSS34

AM5

VSS35

AM2

VSS36

AL34

VSS37

AL31

VSS38

AL23

VSS39

AL20

VSS40

AL17

VSS41

AL12

VSS42

AL9

VSS43

AL6

VSS44

AL3

VSS45

AK29

VSS46

AK27

VSS47

AK25

VSS48

AK20

VSS49

AK17

VSS50

AJ31

VSS51

AJ23

VSS52

AJ20

VSS53

AJ17

VSS54

AJ14

VSS55

AJ11

VSS56

AJ8

VSS57

AJ5

VSS58

AJ2

VSS59

AH35

VSS60

AH34

VSS61

AH33

VSS62

AH32

VSS63

AH31

VSS64

AH30

VSS65

AH29

VSS66

AH28

VSS67

AH27

VSS68

AH26

VSS69

AH20

VSS70

AH17

VSS71

AH13

VSS72

AH9

VSS73

AH6

VSS74

AH3

VSS75

AG10

VSS76

AF8

VSS77

AF4

VSS78

AF2

VSS79

AE35

VSS80

IC,A UB_CFD _rPGA,R1 P0

CON N@

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

2

JCP U1I

K27

VSS161

K9

VSS162

K6

VSS163

K3

VSS164

J32

VSS165

J30

VSS166

J21

VSS167

J19

VSS168

H35

VSS169

H32

VSS170

H28

VSS171

H26

VSS172

H24

VSS173

H22

VSS174

H18

VSS175

H15

VSS176

H13

VSS177

H11

VSS178

H8

VSS179

H5

VSS180

H2

VSS181

G34

VSS182

G31

VSS183

G20

VSS184

G9

VSS185

G6

VSS186

G3

VSS187

F30

VSS188

F27

VSS189

F25

VSS190

F22

VSS191

F19

VSS192

F16

VSS193

E35

VSS194

E32

VSS195

E29

VSS196

E24

VSS197

E21

VSS198

E18

VSS199

E13

VSS200

E11

VSS201

E8

VSS202

E5

VSS203

E2

VSS204

D33

VSS205

D30

VSS206

D26

VSS207

D9

VSS208

D6

VSS209

D3

VSS210

C34

VSS211

C32

VSS212

C29

VSS213

C28

VSS214

C24

VSS215

C22

VSS216

C20

VSS217

C19

VSS218

C16

VSS219

B31

VSS220

B25

VSS221

B21

VSS222

B18

VSS223

B17

VSS224

B13

VSS225

B11

VSS226

B8

VSS227

B6

VSS228

B4

VSS229

A29

VSS230

A27

VSS231

A23

VSS232

A9

VSS233

IC,A UB_CFD _rPGA,R1 P0

CON N@

VSS

3

+CPU _CORE

10U_0805_6 .3V6M

22U_0805_6 .3V6M

C83

1

2

1

2

C84

1

2

@

10U_0805_6 .3V6M

22U_0805_6 .3V6M

C993

C96

1

2

10U_0805_6. 3V6M

C85

1

2

22U_0805_6 .3V6M

10U_0805_6 .3V6M

C113

C111

1

1

2

2

@

22U_0805_6 .3V6M

22U_0805_6 .3V6M

C97

1

2

1

2

C98

1

2

10U_0805_6. 3V6M

22U_0805_6. 3V6M

C112

C86

1

2

@

CPU CORE

10U_0805_6 .3V6M

C116

1

1

2

2

@

22U_0805_6 .3V6M

C99

1

1

2

2

10U_0805_6. 3V6M

C114

1

1

2

2

22U_0805_6 .3V6M

C88

22U_0805_6 .3V6M

C100

22U_0805_6. 3V6M

C115

@

Under cavity

SI1 NO3 0

VSS_N CTF1_R

AT35

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

NCTF

AT1

AR34

B34

B2

B1

A35

VSS_N CTF2_R

VSS_N CTF3_R

VSS_N CTF4_R

VSS_N CTF5_R

VSS_N CTF6_R

VSS_N CTF7_R

T98 TPC12

T99 TPC12

T100 TPC12

22U_0805_6 .3V6M

1

2

@

10U_0805_6 .3V6M

1

2

22U_0805_6 .3V6M

22U_0805_6 .3V6M

C989

C93

C987

1

1

2

C991

1

2

1

2

2

@

@

10U_0805_6 .3V6M

10U_0805_6 .3V6M

C992

C95

1

1

2

2

4

10U_0805_6 .3V6M

22U_0805_6 .3V6M

C90

C89

1

1

2

2

@

22U_0805_6 .3V6M

22U_0805_6 .3V6M

C101

1

2

1

2

@

C102

1

2

10U_0805_6. 3V6M

C87

22U_0805_6 .3V6M

C990

10U_0805_6 .3V6M

C104

22U_0805_6 .3V6M

1

2

10U_0805_6 .3V6M

1

2

330U_X_2VM_R6M

1

+

2

22U_0805_6 .3V6M

C91

1

2

22U_0805_6 .3V6M

C994

C103

1

2

330U_X_2VM_R6M

C105

1

+

2

VSS_N CTF2_R

VSS_N CTF1_R

VSS_N CTF6_R

0.1U_0 402_16V4Z

VSS_N CTF7_R

10U_0805_6 .3V6M

22U_0805_6 .3V6M

C92

C988

1

2

C94

1

2

Inside cavity

05/ 20

chan ge MLCC par t r efer enc es fo r

powe r t eam requ est

10u F: C10 3 C 993

C94 C97 C1 16 C 11

、、、、 、、、、 、、、、

C89 C98 C9 9 C1 00

、、、、 、、、、 、、、、

C10 2 C 91 C 84 C96

、、、、 、、、、 、、、、

C11 1

、、、、

C88

22uF : t he o ther s

between Inductor and socket

330U_X_2VM_R6M

330U_X_2VM_R6M

C106

1

+

2

R79

100K_0402_5%

R80

100K_0402_5%

R81

100K_0402_5%

R82

100K_0402_5%

C107

+3VS

12

+3VS

12

+3VS

12

2

1

+3VS

12

470U_D 2_2VM_R4.5M

1

+

2

C1048

C108

@

2

5

2

5

470U_D 2_2VM_R4.5M

C109

1

2

61

34

61

34

C110

1

+

+

@

2

05/ 20

chan ge C105 ~ C 108 to SGA 00001 Q80

Q2A

2N7002DW H_SOT363-6

CRACK _BGA

Q2B

2N7002DW H_SOT363-6

CRACK _BGA

Q3A

2N7002DW H_SOT363-6

CRACK _BGA

Q3B

2N7002DW H_SOT363-6

@

、、、、

22U_0805_6. 3V6M

C117

1

1

2

2

5

BC99 4 C9 88 C 92

、、、、 、、、、

3 C9 0

、、、、

C101

、、、、

BC83

22U_0805_6. 3V6M

22U_0805_6. 3V6M

CRACK _BGA 17 ,29

10U_0805_6. 3V6M

C119

C118

C120

1

1

2

2

@

BGA Ball Cracking Prevention and Detection

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

1

2

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2008/09/15 2009/12/31

Compal Secret Data

Deciphered Date

4

Title

Size Docum ent Num ber R ev

Cus tom

Dat e: Sheet o f

Compal Electronics, Inc.

Auburndale(5/5)-GND/Bypass

LA-4902P

5

8 47Wed nesda y, Decem ber 09, 2 009

0.3

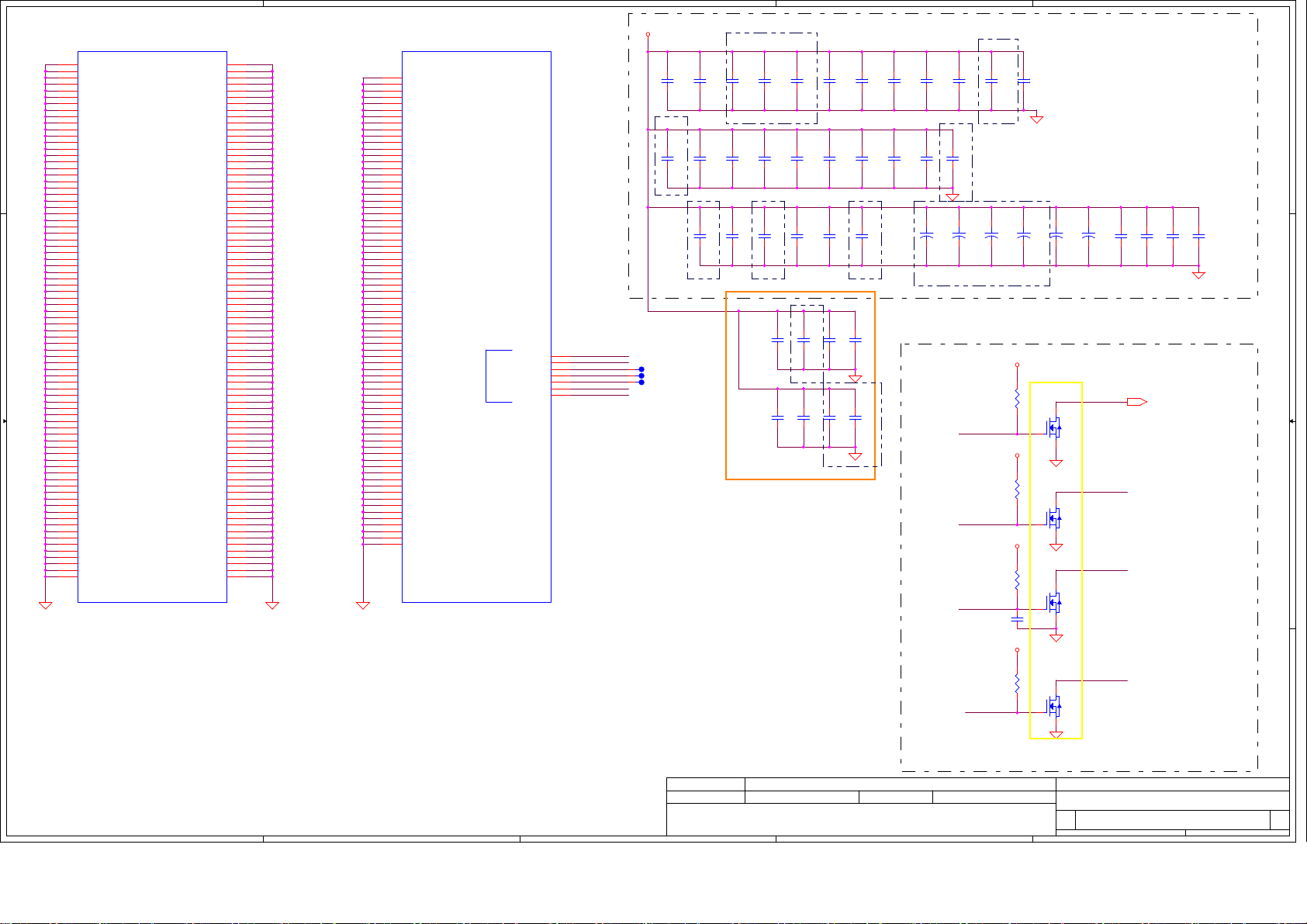

Page 9

+3VS

hexainf@hotmail.com

1

+1.5V +1.5V

DDR3 SO-DIMM A

3 A

3 A @1 . 5 V

@ 1 . 5 V

3 A3 A

@ 1 . 5 V@ 1 . 5 V

JDIMA 1

CON N@

VREF_DQ1VSS1

0.1U_0 402_16V4Z

2.2U_0 805_16V4Z

C121

1

1

2

2

1

2

DDR _A_D0

C122

DDR _A_D1

DDR_A _DM0

DDR _A_D2

DDR _A_D3

DDR _A_D8

DDR _A_D9

DDR_A _DQS#1

DDR _A_DQS1

DDR _A_D10

DDR _A_D11

DDR _A_D16

DDR _A_D17

DDR_A _DQS#2

DDR _A_DQS2

DDR _A_D18

DDR _A_D19

DDR _A_D24

DDR _A_D25

DDR_A _DM3

DDR _A_D26

DDR _A_D27

DDR_C KE0_DIMM A

DDR_A _BS2

DDR_A _MA12

DDR_A _MA9

DDR_A_ MA8

DDR_A _MA5

DDR_A _MA3

DDR_A _MA1

M_CLK _DDR0

M_CLK _DDR#0

DDR_A _MA10

DDR_A _BS0

DDR_A _WE#

DDR _A_CAS# M_ODT0

DDR_A _MA13

DDR_C S1_DIMMA #

DDR _A_D32

DDR _A_D33

DDR_A _DQS#4

DDR _A_DQS4

DDR _A_D34

DDR _A_D35

DDR _A_D40

DDR _A_D41

DDR_A _DM5

DDR _A_D42

DDR _A_D43

DDR _A_D48

DDR _A_D49

DDR_A _DQS#6

DDR _A_DQS6

DDR _A_D50

DDR _A_D51

DDR _A_D56

DDR _A_D57

DDR_A _DM7

DDR _A_D58

DDR _A_D59

R87

1 2

10K_0402_5%

0.1U_0 402_16V4Z

2.2U_040 2_6.3V6M

C144

C143

1

2

3

VSS2

5

DQ0

7

DQ1

VSS49DQS#0

11

DM0

13

VSS5

15

DQ2

17

DQ3

19

VSS7

21

DQ8

23

DQ9

VSS925VSS10

27

DQS#1

DQS129RESET#

VSS1131VSS12

33

DQ10

35

DQ11

VSS1337VSS14

39

DQ16

41

DQ17

VSS1543VSS16

45

DQS#2

DQS247VSS17

49

VSS18

51

DQ18

DQ1953VSS19

55

VSS20

57

DQ24

DQ2559VSS21

VSS2261DQS#3

63

DM3

VSS2365VSS24

67

DQ26

69

DQ27

VSS2571VSS26

73

CKE0

75

VDD1

77

NC1

79

BA2

81

VDD3

A12/BC#83A11

85

A9

87

VDD5

89

A8

91

A5

93

VDD7

95

A3

97

A1

VDD999VDD10

101

CK0

103

CK0#

105

VDD11

107

A10/AP

109

BA0

111

VDD13

113

WE#

115

CAS#

117

VDD15

119

A13

121

S1#

123

VDD17

125

NCTEST

127

VSS27

129

DQ32

131

DQ33

133

VSS29

135

DQS#4

137

DQS4

139

VSS32

141

DQ34

143

DQ35

145

VSS34

147

DQ40

149

DQ41

151

VSS36

153

DM5

155

VSS37

157

DQ42

159

DQ43

161

VSS39

163

DQ48

165

DQ49

167

VSS41

169

DQS#6

171

DQS6

173

VSS44

175

DQ50

177

DQ51

179

VSS46

181

DQ56

183

DQ57

185

VSS48

187

DM7

189

VSS49

191

DQ58

193

DQ59

195

VSS51

197

SA0

199

VDDSPD

201

SA1

203

10K_0402_5%

R88

12

VTT1

205

G1

FOX_AS0A 626-U2RN-7F

DQ4

DQ5

VSS3

DQS0

VSS6

DQ6

DQ7

VSS8

DQ12

DQ13

DM1

DQ14

DQ15

DQ20

DQ21

DM2

DQ22

DQ23

DQ28

DQ29

DQS3

DQ30

DQ31

CKE1

VDD2

VDD4

VDD6

VDD8

CK1#

VDD12

RAS#

VDD14

ODT0

VDD16

ODT1

NC2

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

DM4

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

DM6

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

SDA

VTT2

A15

A14

A7

A6

A4

A2

A0

CK1

BA1

S0#

SCL

G2

SI1: No 44

+V_DD R_REF_D IMMA_DQ

A A

B B

C C

D D

09/2/16 HP

DDR_C KE0_DIMMA6

DDR_A _BS26

M_CLK _DDR06

M_CLK _DDR#06

DDR_A _BS06

DDR_A _WE#6

DDR _A_CAS#6

DDR_C S1_DIMMA#6

Reserved

TOP

1

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

206

2

DDR _A_D4

DDR _A_D5

DDR_A _DQS#0

DDR _A_DQS0

DDR _A_D6

DDR _A_D7

DDR _A_D12

DDR _A_D13

DDR_A _DM1

DRAMRST #

DDR _A_D14

DDR _A_D15

DDR _A_D20

DDR _A_D21

DDR_A _DM2

DDR _A_D22

DDR _A_D23

DDR _A_D28

DDR _A_D29

DDR_A _DQS#3

DDR _A_DQS3

DDR _A_D30

DDR _A_D31

DDR_C KE1_DIMM A

DDR_A _MA15

DDR_A _MA14

DDR_A_ MA11

DDR_A _MA7

DDR_A_ MA6

DDR_A _MA4

DDR_A _MA2

DDR_A _MA0

M_CLK _DDR1

M_CLK _DDR#1

DDR_A _BS1

DDR _A_RAS#

DDR_C S0_DIMMA #

M_ODT1

DDR _A_D36

DDR _A_D37

DDR_A _DM4

DDR _A_D38

DDR _A_D39

DDR _A_D44

DDR _A_D45

DDR_A _DQS#5

DDR _A_DQS5

DDR _A_D46

DDR _A_D47

DDR _A_D52

DDR _A_D53

DDR_A _DM6

DDR _A_D54

DDR _A_D55

DDR _A_D60

DDR _A_D61

DDR_A _DQS#7

DDR _A_DQS7

DDR _A_D62

DDR _A_D63

PM_EXTTS#1_R

SMB_DATA_S3

SMB_CLK_S3

+0.75V

2

+0.75VS

0 . 6 5 A @ 0

0 . 6 5 A @ 0 .7 5 V

. 75 V

0 . 6 5 A @ 00 . 6 5 A @ 0

. 75 V. 75 V

DDR _A_D[0 ..63]6

DDR _A_DM[ 0..7]6

DDR _A_DQ S[0..7]6

DDR _A_DQS #[0..7]6

DDR _A_MA[0.. 15]6

DRAMRST # 4,10

DDR_C KE1_DIMMA 6

M_CLK _DDR1 6

M_CLK _DDR#1 6

DDR_A _BS1 6

DDR _A_RAS# 6

DDR_C S0_DIMMA# 6

M_ODT0 6

M_ODT1 6

0.1U_0 402_16V4Z

C141

1

1

2

2

SMB_DATA_S3

SMB_CLK_S3

2.2U_0 805_16V4Z

C142

SI1: No 44

+V_DD R_REF_D IMMA_CA

JP20

3

3

2

2

1

1

ACES_85204 -03001

CON N@

For ME/AMT debug

PM_EXTTS#1_R 4,10

SMB_DATA_S3 4,10,11 ,13,26

SMB_CLK_S3 4,10,1 1,13,26

3

+1.5V

12

R83

1K_0402_1%

R84

1K_0402_1%

SI1: No 21

SI1: No 27

5

G2

4

G1

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

12

09/4/10 HP

Layo ut N ote:

Pla ce n ea r D IMMA

10U_0603_6 .3V6M

1

2

+V_DD R_REF_D IMMA_DQ

SI1: No 44

09/4/27 HP

+1.5V

10U_0603_6 .3V6M

10U_0603_6 .3V6M

C127

C126

1

1

2

2

2008/09/15 2009/12/31

R1100

1K_0402_1%

R1101

1K_0402_1%

10U_0603_6 .3V6M

10U_0603_6 .3V6M

C129

C128

1

2

C130

1

2

Compal Secret Data

4

+1.5V

12

+V_DD R_REF_D IMMA_CA

12

10U_0603_6 .3V6M

C131

1

1

2

2

Deciphered Date

4

5

Layo ut N ote:

Sha red bet ween t he tw o

SO-D IMMs.

Pla ce two cap aci tors clo se

to the VR and o ne

be twe en the two SOD IMM s

Layo ut N ote:

Pla ce n ea r D IMMA

SI1: No 48

0.1U_0 402_16V4Z

0.1U_0 402_16V4Z

C132

C133

1

@

@

2

09/4/28 HP

SI2 NO9

0.1U_0 402_16V4Z

0.1U_0 402_16V4Z

C134

C135

1

@

2

1

1

+

@

2

2

+0.75VS

330U_D 2_2VY_R7M

C123

C136

1

2

Title

Size Docum ent Num ber R ev

Cus tom

LA-4902P

Dat e: Sheet

C138

C137

1U_0402 _6.3V6K

C139

1U_0402 _6.3V6K

C140

10U_0603_6 .3V6M

1U_0402 _6.3V6K

1

1

2

2

1U_0402 _6.3V6K

1

2

C124

1

1

2

2

Compal Electronics, Inc.

DDRIII-SODIMM SLOT1

5

9 47Wed nesda y, Decem ber 09, 2 009

10U_0603_6 .3V6M

of

C125

10U_0603_6 .3V6M

1

2

0.3

Page 10

1

2

3

4

5

SI1: No 44

+V_DD R_REF_D IMMB_DQ

2.2U_0 805_16V4Z

0.1U_0 402_16V4Z

1

+3VS

C145

2

DDR_C KE2_DIMMB6

DDR_B _BS26

M_CLK _DDR26

M_CLK _DDR#26

DDR_B _BS06

DDR_B _WE#6

DDR_ B_CAS#6

DDR_C S3_DIMMB#6

2.2U_04 02_6.3V6M

1

2

1

A A

B B

C C

D D

09/2/16 HP

+VREF _DQ_DIMMB

DDR _B_D0

DDR _B_D1

1

C146

DDR_B _DM0

2

DDR _B_D2

DDR _B_D3

DDR _B_D8

DDR _B_D9

DDR_B _DQS#1

DDR _B_DQS1

DDR _B_D10

DDR _B_D11

DDR _B_D16

DDR _B_D17

DDR_B _DQS#2

DDR _B_DQS2

DDR _B_D18

DDR _B_D19

DDR _B_D24

DDR _B_D25

DDR_B _DM3

DDR _B_D26

DDR _B_D27

DDR_C KE2_DIMM B

DDR_B _BS2

DDR_B _MA12

DDR_B _MA9

DDR_B_ MA8

DDR_B _MA5

DDR_B _MA3

DDR_B _MA1

M_CLK _DDR2

M_CLK _DDR#2

DDR_B _MA10

DDR_B _BS0

DDR_B _WE#

DDR _B_CAS# M_ODT2

DDR_B _MA13

DDR_C S3_DIMMB #

DDR _B_D32

DDR _B_D33

DDR_B _DQS#4

DDR _B_DQS4

DDR _B_D34

DDR _B_D35

DDR _B_D40

DDR _B_D41

DDR_B _DM5

DDR _B_D42

DDR _B_D43

DDR _B_D48

DDR _B_D49

DDR_B _DQS#6

DDR _B_DQS6

DDR _B_D50

DDR _B_D51

DDR _B_D56

DDR _B_D57

DDR_B _DM7

DDR _B_D58

DDR _B_D59

1 2

10K_0402_5%

0.1U_0 402_16V4Z

C165

C166

1

2

+1.5V +1.5V

DDR3 SO-DIMM B

3 A

3 A @1 . 5 V

@ 1 . 5 V

3 A3 A

@ 1 . 5 V@ 1 . 5 V

JDIMB 1 CON N@

VREF_DQ1VSS1

3

VSS2

5

DQ0

7

DQ1

VSS49DQS#0

11

DM0

13

VSS5

15

DQ2

17

DQ3

19

VSS7

21

DQ8

23

DQ9

VSS925VSS10

27

DQS#1

DQS129RESET#

VSS1131VSS12

33

DQ10

35

DQ11

VSS1337VSS14

39

DQ16

41

DQ17

VSS1543VSS16

45

DQS#2

DQS247VSS17

49

VSS18

51

DQ18

DQ1953VSS19

55

VSS20

57

DQ24

DQ2559VSS21

VSS2261DQS#3

63

DM3

VSS2365VSS24

67

DQ26

69

DQ27

VSS2571VSS26

73

CKE0

75

VDD1

77

NC1

79

BA2

81

VDD3

83

A12/BC#

85

A9

87

VDD5

89

A8

91

A5

93

VDD7

95

A3

97

A1

VDD999VDD10

101

CK0

103

CK0#

105

VDD11

107

A10/AP

109

BA0

111

VDD13

113

WE#

115

CAS#

117

VDD15

119

A13

121

S1#

123

VDD17

125

NCTEST

127

VSS27

129

DQ32

131

DQ33

133

VSS29

135

DQS#4

137

DQS4

139

VSS32

141

DQ34

143

DQ35

145

VSS34

147

DQ40

149

DQ41

151

VSS36

153

DM5

155

VSS37

157

DQ42

159

DQ43

161

VSS39

163

DQ48

165

DQ49

167

VSS41

169

DQS#6

171

DQS6

173

VSS44

175

DQ50

177

DQ51

179

VSS46

181

DQ56

183

DQ57

185

VSS48

187

DM7

189

VSS49

191

DQ58

193

R91

1 2

R92 10K_0402 _5%

DQ59

195

VSS51

197

SA0

199

VDDSPD

201

SA1

203

VTT1

205

G1

+0.75V

BOT

VSS3

DQS0

VSS6

VSS8

DQ12

DQ13

DQ14

DQ15

DQ20

DQ21

DQ22

DQ23

DQ28

DQ29

DQS3

DQ30

DQ31

CKE1

VDD2

VDD4

VDD6

VDD8

CK1#

VDD12

RAS#

VDD14

ODT0

VDD16

ODT1

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

VSS31

DQ38

DQ39

VSS33

DQ44