Page 1

P

f'

()

c:

~?~:;~:;

()

T'

Mod u 1 e

Manual

DATA

Part

TERMINAL

TECHNICAL

No.

13220-91087

REVISED

JAN···

()

4····B2

INFORMATION

Printed

in

HEWLETT~PACKARD

U.S.A.

Page 2

P

f'

0 c

(~~:;

~:;

0 7' M

()

d u 1 e

Manual

The

inforMation

w:i.ti"lou"t

HEWl..ETT····Pt-.CI{ARD t'\AI{EB

MATERIAL,

notic€~.

INCLUDING,

MERCHANTABILITY

shall

con~)f:~quf.·!n·t:i.al

or

use

not

of

be

this

contained

AND FITNESS

liable

dat

for

...

aqE~s

Material.

NO

BUT

in

Part

No.

13220-91087

I~EVISED

JAN···

()

4····0t?

NOTICE

in

this

WARI~ANTY

NOT

dOCUMent

OF ANY

LIMITED

FOR A PARTICULAR

errors

c()nn~:~ction

contained

with

TO

is

I{IND

THE

IMPLIED

PURPOSE.

herein

th(·!

fUl'nis;hinq,

subject

WITH

or

to

change

'~EGAI~l)

TO

WARRANTIES

Hewlett-Packard

for

incidental

~)E~l'for'Manc:~?,

THIS

OF

or

This

cop

dOCUMent

Y

7'

:i.

q h

photocopied

Pac k (;.

r'

d C

NOTE:

t.

All

or

()

i'\

pan

Thi~:;

~:)

0!

r'

contains

r' i

<;.I

reproduced

y .

Cop

yr'

iqh

docuME!nt

:i.

f:·!

s T

f..!

h t

~:;

t c

C h n i

proprietary

i:\ "

f..~

r'

f:'~

~:)

f:! r' v

without

j.9S;:-!.

is

cal

par't

I n

for'

by

inforMation

E!

d . N

the

HEWI...ETT--PACKARD COMPANY

of

Mat

()

prior

th(~

~?'6;:~XX

ion

P i:\

P a " t 0 f t h

c:

k a

which

written

DATA

(J

f!

(H P j. 3

is

:i.

~:;

consent

TERMINAl...

;:~

protected

cI

0 c

lJ

M

;:?

()

) .

~;!

n t

JII\

a y b

of

Hewlett-

pr'oduct

by

f:!

Page 3

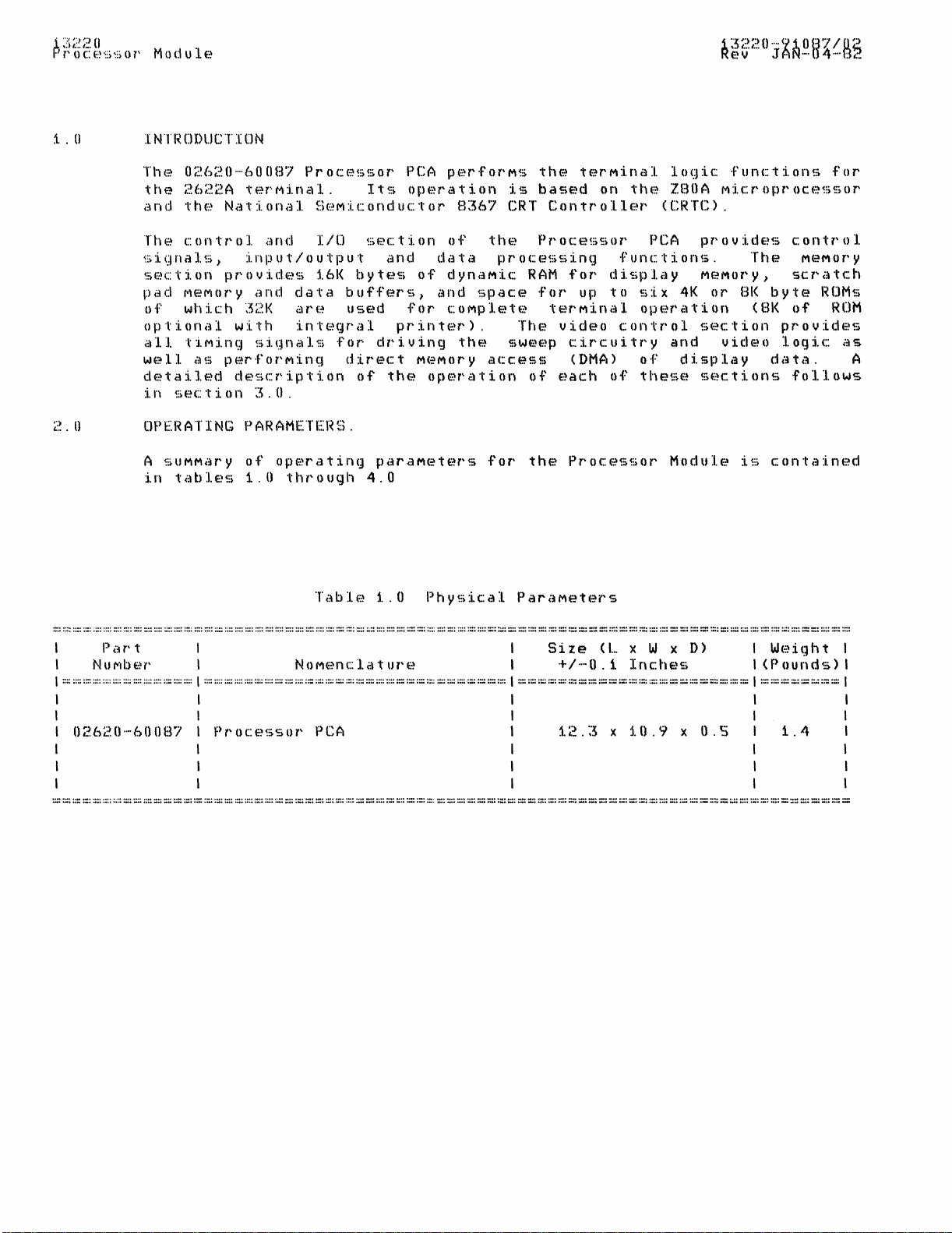

i.O

IN"l"RODUCTION

The

02620-60087

the

2622A

and

the

The

control

~;>

i q n a 1

section

pad

MeMory

of

which

optional

all

tiMing

well

detailed

:i.

n

~:;ec

as

terMinal.

National

~:>

,

:i.

n

provides

and

32K

with

signals

perforMing

description

t

ion

3.

and

put

0 .

Processor

Its

SeMiconductor

I/O

/ 0 u t

16K

data

are

integral

section

put

bytes

buffers,

used

for

driving

direct

of

PCA

operation

and

of

for

printer).

MeMory

the

operation

perforMs

8367

of

the

d

i~

tap

dynaMic

and

space

COMplete

the

access

the

is

based

CRT

Controller

Processor

roc

(~s~:;:i.

RAM

for

for

terMinal

The

video

sweep

of

circuitry

each

terMinal

on

n(J

display

up

to

CDMA)

of

the

(CRTC).

PCA

fun

c t j. 0

six

operation

control

of

these

logic

Z80A

provides

n~:;

MeMory,

4K

section

and

display

sections

functions

Microprocessor

control

.

or

video

The

8K

(8K

MeM

scratch

byte

of

provides

logic

data.

follows

for

0 r' y

RUMs

ROM

as

A

2.0

OPERATING

A

SUMMary

in

tables

PARAMETERS.

of

operating

1.0

through

Table

paraMeters

4.0

1.0

Physical

for

the

ParaMeters

Processor

Module

is

contained

===============================================================================

Par'

1

t S i z e (I... x W x

NUI"',IHH'

1

NOMf:·~nclatul'~~

1

+/

....

0.1

Inche~;

D)

1

W(~

i q h t 1

1

(Pounds>

1

1=============1==============================1=======================1========1

1 I 1 1 1

1 1 1 1 1

1

02620-60087

1

Processor

PCA

1

12.3

x

10.9

x

O.S

1

1 1 1

1.4

1

1

I 1 1 1

1 1 1 1

===============================================================================

Page 4

1

:'5;:~:~O

Pl'

()Cf.~<':;~;()l'

Mod

u Ie'

1

~5220

....

f/1 0 H'7 / ()

Rev JAN-()4····f32

~5

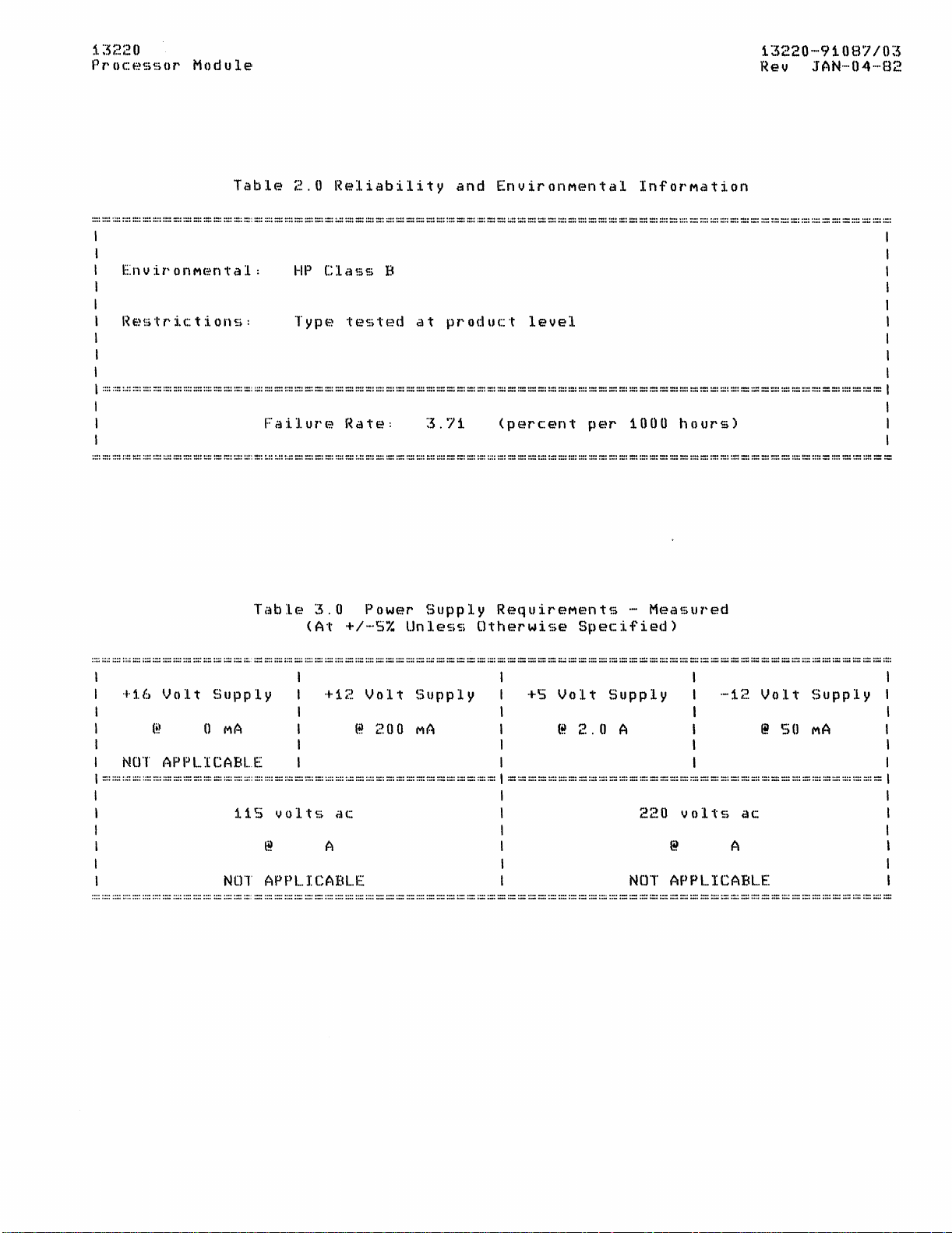

Table

================:========~======================================================

I

I

I

EnvironMental:

I

I

I

Restrictions:

I

I

I

I==~===========~==============================================================

I

I

I

===================~======~====================================================

Failure

Table

2.0

HP

Class

Type

3.0

(At

Reliability

B

tested

Rate:

Power

+/-5%

Unless

at

product

3.71

Supply

and

EnvironMental

(percent

RequireMents

Otherwise

level

InforMation

per

1000

-

Specified)

hours)

Measured

===~=============================~=============================================

+16

Volt

ill 0

I

NOT

I

:::

::;:

I I I

I

I I I

I

I I I

I

APPLICABLE I I I I

:~:

::::

::::::::

::::

Supply

MA

::::::::::::

::::::::

::::

::::

115

NOT

+12

Volt

@

:;::

::::

::::::::

:'~:::::

:::: ::::

::::

::::

:.::::::

:::: :::: :::: :::: ::::

volts

~

APPL.ICABL.E I

ac

A I

200

Supply

MA

:::::-.::::::

::::

::::::::

::::

::: I =::::::::::::

I

+5

Volt

@

:::: ::::

::::::::

Supply

2.0

A I @

::::

::::::::

:.~:::::

::::::::::::

220

NOT

I

I

-12

Volt

I

I

:::: ::::

::::::::::::

:::::::::".::

:::::::::::

volts

@.

APPLICABLE I

ae

A I

Supply

SO

MA

:::: :::: = :::: = ::::

::::

::::::::

= I

I

===============================================================================

Page 5

13~~2

()

P

f'

0 C

£~

~:;

~:)

()

:1.

3~~~:~

0 ···9108'7/04

R

(::~

f'

M

()

d u 1 e

v JAN···

()

4···B;?

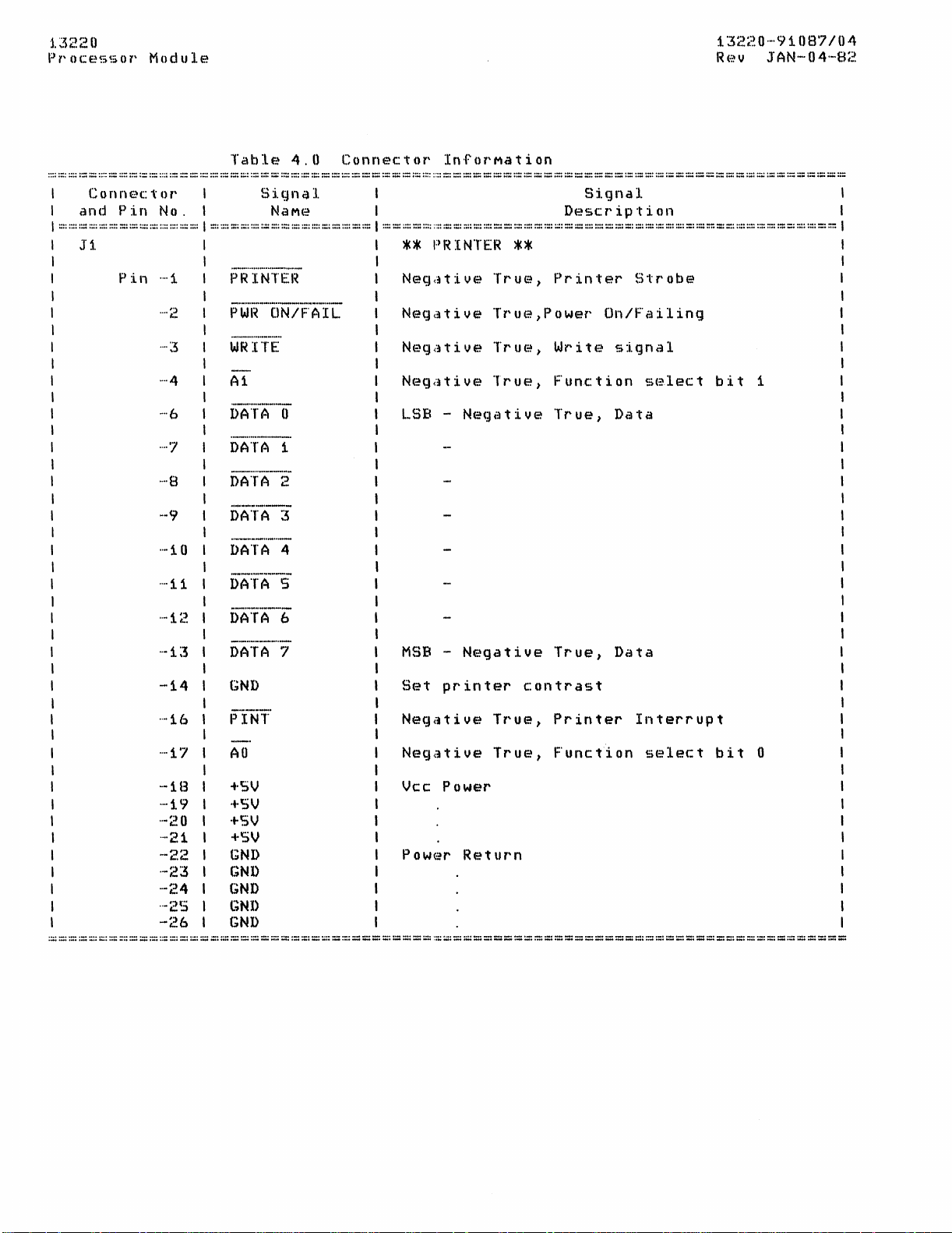

Table

===~==========~===~========~===================================================

Connector

1

and P in

No. 1

1==============1================

J1

Pin

···1

....

2

....

~5

....

4

·

..

··7

....

8

·-9

....

:1.

0 I

....

:1.1

....

:1.

;,?

"-L3 t

1

1

I

PRINTER

I

1

PWI~

I

WRITE

1

1

1

Ai

1

DATA

\

1

DATA

\

\

I

DATA 2

t

1

DATA

I

DATA

I

I

DATA

I

t

DATA

I

DATA

4.0

Signal

NaM(~

ON/FAIL

()

1

:5

4

S

6

7

Connector

InforMation

Signal

Description

=============================================\

**

PRINTER

Negative

Negative

Negative

Negative

LSB -Negative

MSB -Negative

**

True,

True,Power

True,

True,

Printer

Write

Fun~tion

True,

True,

Strobe

On/Failing

signal

select

Data

Data

bit

1

I

I

-14

·

..

·16

....

1·7

-1t3

-·19

"-20

....

21

·-22

..

-;~3

-24

"-25

-26

GND

PINT

AO

+SV

+SV

+SV

+SV

GND

GND

GND

GNU

GND

Set

printer

Negative

Negative

Vcc

Power

Power

Retul'n

contrast

True,

True,

Printer

Function

Interrupt

select

bit

0

Page 6

1.

~5~~2()

Pl'OC(~SS)Ol'

Module

13220-91.08'7/0S

Rev

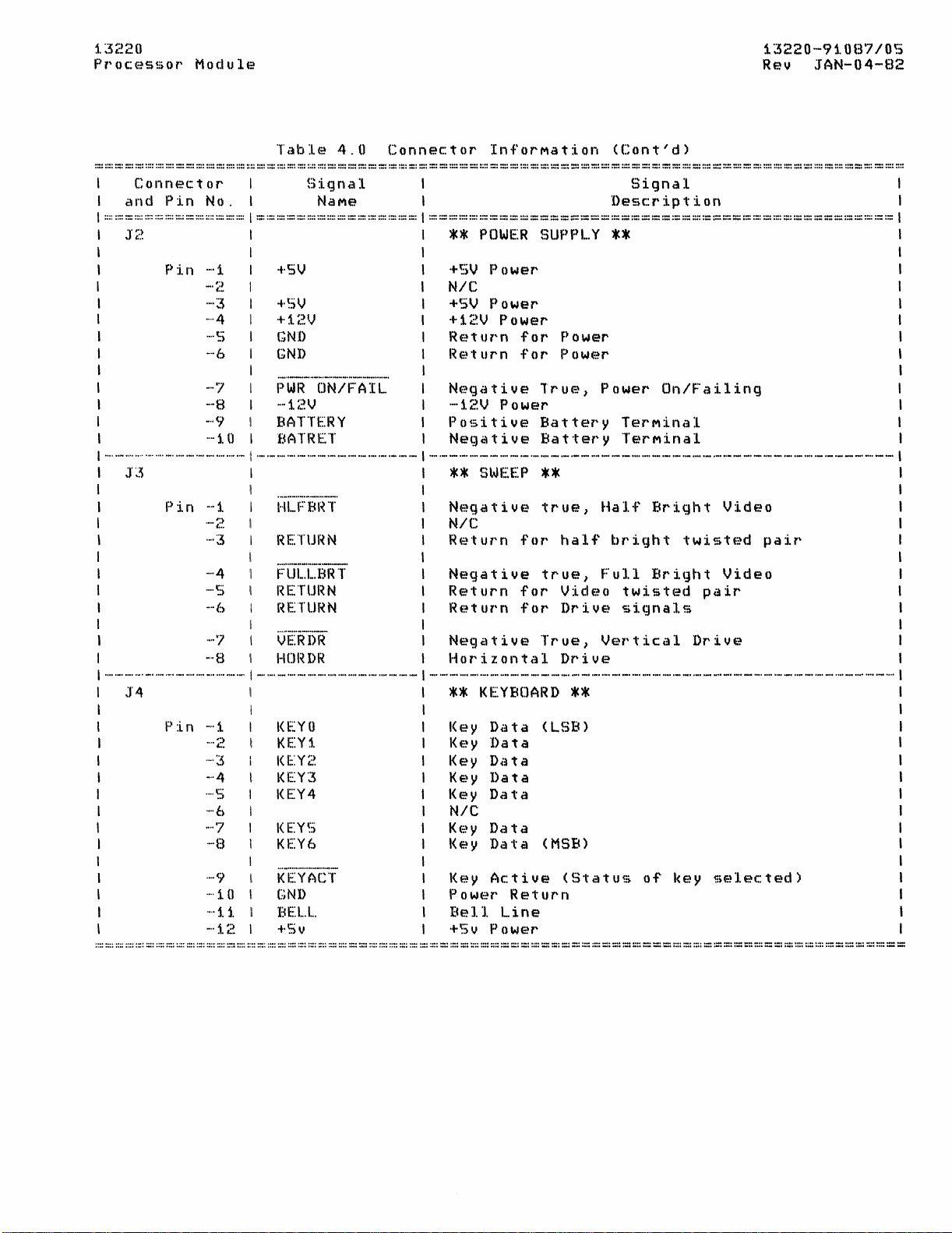

JAN-()4-B2

Table

===============================================================================~

I

Connector

I

and

Pin

No.

I

\==============1================

I

J;:.~

I 1

I

\

Pin

\

\

I

I

I

I

\

I

I

I

........................................ -............

I

J~3

I

I

I

\

\

I --4

\

Pin

\

I I

I

\

I

..... -........

, _

.......... -........ -...........

\

J4

\

I

I

I

I

\

I

I

)

Pin

I

-·1

-.~:~

-3

-4

-S

-6

-'7

-8

-9

-10

-1

-2

-3

-5

-6

....

'J

-8

....

1

....

2

·

..

·3

...

-4

·

..

·s

·

..

·6

....

·7

-·B

+5V

+SV

+12V

GND

GND

.. _ ...

_.

PWR

-1.2V

BATTERY

1

BATRET

'I

._.-

....

'''' .-..... -..................... -•• -.-.-

1 I

.....

__

HLFBRT

RETURN

........ _ ...........

FUL.L.BI~

RETURN

RETURN

iJ'f~:'ifi)rf

I

HORDR

-.

:1

.......... -............ -............... -............. -•.

\(EYO

KEYj

KEY2

KEY:~

I<EY4

KEYS

KEY6

Signal

NaMe

__

._

... _ ..

__

ON/FAIL

..

_.

__

....

__

. I

_._._.

.

4.0

.......... _ ......

T \

Connector

_.

-

InforMation

(Cont'd)

Signal

Description

==============================================

**

+SV

N/C

+5V

+1;':'~V

R€~t

Ret

Negative

-12V

Positive

I

Negative

I

..

-.--.-...... -.-

**

I

Negative

I

N/C

I

Return

I

Negative

I

Return

\

Return

I

Negative

I

Horizontal

**

Key

KE~y

Key

Key

Key

N/C

K(~~y

)(ey

POWER

Power

Power

ur'n f

urn

SWEEP

KEYBOARD

Data

Data

Data

Data

Data

Dc:l

Data

SUPPL.Y

Power

01'

for'

True,

Power

Battery

Battery

....... -.............

_.-.-

**

true,

for

true,

for

for

True,

(LSB)

ta

(MSS)

**

Power

P

ow(~r

Power

........... , ..... -..........

Half

half

bright

Full

Video

Drive

Vertical

Drive

**

On/Failing

TerMinal

TerMinal

-.-.-

.. -....

Bright

twisted

Bright

twisted

signals

'''' .-...

_.-

Video

Video

pair

Drive

.... _ .... -..... -.....

pair

_._.-

- -' -

..

_.-

I

·

..

·9

.... 1 ()

····1.1

....

12

================================~===============================================

KEYACT

GNI>

BELL..

+Sv

Key

Active

Pow(~r

Bell

+5v

Line

Power

Return

(Status

of

key

selected)

Page 7

j.

~5;.:!.2

0

Pr'oc(::~ssor'

Module

1

~5220'-91

Rev

08'7/06

JAN-()4'-B2

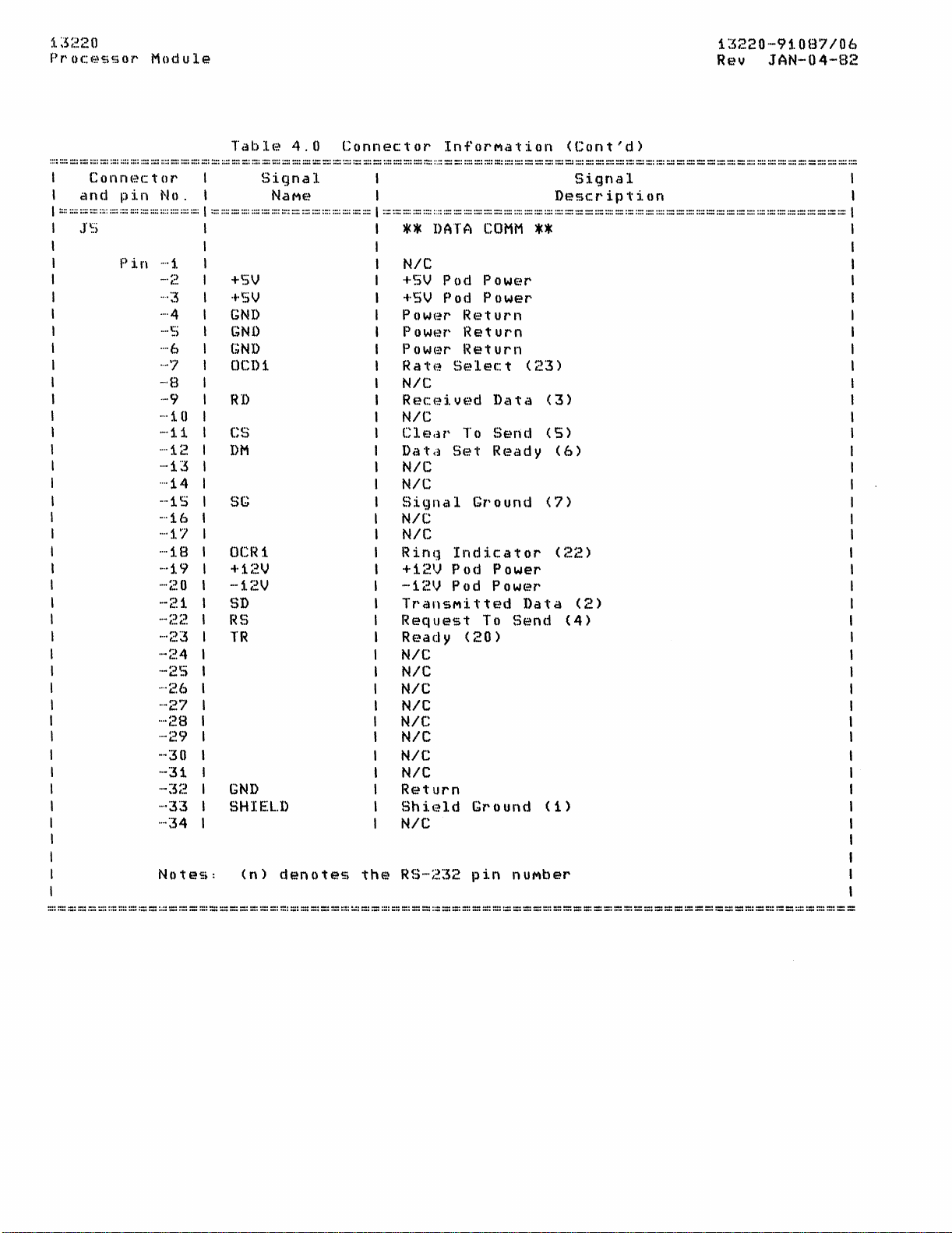

Table

~===============================================================================

Connector

and

pin

No. I

4.0

Signal

NaM€~

Connector

I

InforMation

(Cont'd)

Signal

Des;cr'iption

==============1================1==============================================

JS

Pin

....

j.

-.;~

"'~3

....

4

~~S

"~6

..

~'J

..

··8

..

~9

..

··10

·

..

·1 i

....

12

"~13

·

..

·14

....

1 S

-··16

....

j.

'J

....

18

·

..

·j.9

....

;?

0

--21

.. -;;!;,?

....

;:?~~

"-;?4

"-25

....

26

-~27

..

··;,?8

..

-29

-~3

()

"-31

"-3;.~

..

··33

....

~34

+SV

+SV

GN!)

GNl>

GND

DeDi

RD

(,(:'

.,,,:>

DM

SG

OCR1

+1;~V

--1;:!V

SD

RS

TR

GND

SHIEL.l)

DATA

COMM

**

N/C

+SV

Pod P

+SV

Pod

P()w(~r

P

OWf-~r'

P()w(~r

Rat(:~

Nit

R

(~c

f:d.

Nit

Clf~dr'

Di:l

ta

N/C

Nit

Si~}na

NIt

N/C

Rinq

+12V

'-1~~\)

Tr';HlSMl.

r~eqllest

Ready

Nit

N/C

NIt

N/C

N/C

N/C

Nit

N/C

Return

Shi(-.~ld

N/C

ow€~r

Power

R(~tul'n

I~et

urn

Return

S~~lect

l)clti:\

V

(·~d

To

Send

S(?t

Rei:ld

Gr' 0 und

1

Ind:i.cator

Pod

Power

Pod

Power

t

t(~d

To

(20)

Ground

**

(23)

y

Data

Send

(3)

(5)

(6)

(7)

(~~2

(4)

( 1 )

)

(2)

(n)

denotes

the

RS-232

pin

nUMber

================================================================================

Page 8

1

~3~!'~~0

Pl'

()c€-~~:;s()r'

M()d u le

1:3220·-91.

Rev

JAN····

OB'7

0 4'-(32

10'7

3.0

FUNCTIONAL

Refer

tiMing

parts

the

and

CONTROL.

t()

diagraMs

list

()peration

lID,

AND

Clock

A

25.7715

video

74LS244

then

is

clock

4.4V.

which

d()t

(US11)

divided

shaped

for

This

the

lOOA

The

laOA

tion

signals

It

which,

branch

bus

b u

functions

also

request

~:)es

.

to

responds

when

to

DESCRIPTION

bl()ck

diagraM

(figs.

(fig.

MeMory,

I/O

MHz

10)

of

the

and

SECTION

crystal

frequency.

to

beCOMe

by

seven

by

Q4

and

the

ZaOA,

clock

datacoMM

Microprocessor

of

the

read

and

to

enabled,

its

interrupt

signal,

located

three

video

is

This

by

its

associated

which

is

also

chip

processor

write

two

externally

interrupt

service

NBUSREQ,

(fig.

4-8),

Major

c()ntrol.

attached

DRCX,

the

748163

has

divided

(U613)

perforMS

data

1),

scheMatic

COMponent

in

the

appendix.

sections

to

is

buffered

buffered

(Ub11)

circuitry

a

zero

by

uses

to

the

peA.

frOM

generated

current

routine.

allowing

location

of

the

by

dot

level

two

to

produce

Major

It

provides

and

to

execution

the

diagraMs

the

CRTC

the

rate

to

produce

to

<

produce

baud

control

both

interrupts,

The

CRTC

diagraM

The

following

Processor

which

CRTC

clock.

produce

0.4SV

a

rates.

and

addresses

MeMory

and

ZBOA

also

control

(figs.

(fig.

peA)

oscillates

and

again

This

3.6816

MHz,

a

SYMMetrical

and a one

1.8408

data

and

and

I/O

NNMI

cause

the

responds

of

the

2,3),

9)

and

describes

control

at

the

by

clock

which

level>

MHz

clock

Manipula-

control

ports.

and

NINT,

ZaOA

to

systeM

a

is

to

a

At

power

prograM

initializes

non-volatile

an

error

indicate

enters

a

por'ts.

Three

frOM

MeMory

abled

74LS244's

the

into

during

instructi()n

in

an

instruction

signal

was

respond

frOM

full

be

the

latch

th~:~

address

speed.

used

ZaOA

U610

ZBOA.,

up

MeMory

variables

is

detected

the

Major

Z80A.

six

fetch

used

within

by

installing

to

wait

and

(or

reset)

beginning

at

and

MeM()ry

failing

10()P

(CMOS)

a

series

ROM

responding

(U4'7,U57,U511)

The 1 of a decoder,

blocks,

a MeMory

by

read

the

each

NMl

fetch

to

provide

the

required

or

300

ns

frOM

[PROMs

or

ROMs

JUMper

one

cycle

ass()ciated

the

ZaOA

address

devices

and

of

or

RAM.

BK

by

the

signal.

is

less

an

early

tiMe.

enable

with

l()nger

gating

begins

OOOOH.

according

perforMS

beeps

After

to

inputs

buffer

bytes

TNRD

than

enable

are

450

WS

and

during

provides

executing

A

to

a

self

are

issued

inintialization

frOM

the

U76,

long.

and

that

ROMs

ns

reMoving

is

TNMREQ

Since

for

of

with

required

access

instructi()n

the

routine

inforMation

test

the

of

to

the

keyboard

address

used

The

to

addressed

signals

the

tiMe

a

MeM()ry

the

ROM

access

t()

run

tiMes

JUMper

fetches.

required

instructions

is

executed

contained

ROM

and

keyboard

the

and

and

control

separate

ROM

()r

to

read

read,

allowing

tiMes

the

frOM

W6,

address

which

wait

frOM

which

RAM.

which

prograM

datacoMM

lines

prograM

is

en-

during

the

data

the

it

of

350

systeM

causes

The

quad

signal

in

If

an

NM1

to

ns

at

May

to

Page 9

13220

Processor

3.1.3

Module

I/O

Ports

CMUS

The

Z80A

I/O

addresses

accuMulator

used

to

configuration

respond

each

S

volts

Q3,

before

beCOMe

CMOS

May

be

standard

CMOS

within

tiMe

is

Makes

the

defined

contents.

replaced

read/COMpleMent/write

error

DATACOMM

is

capable

contents

access

data

the

CMOS

always

sure

l80A

since

froM

the

that

buses

at

If

by

the

of

the

appear

locations

is

stored.

I/O

cycle

RAM

is

on

t~e

during

power

power

an

HM7611

prOM

addressing

ZaOA

on

in

accessed.

CMOS

a

beCOMe

on.

on

configuration

PROM

cannot

2S6

appear

bits

the

Since

on

A8-A1S.

nonvolatile

the

tiMe a wait

Diodes

supply

power

pin.

off

undefined

During

(however

test

be

for

written).

different

address

CMOS

state

the

and

power

is

it

the

CMOS

bits

I/O

addresses

CMOS

RAM

is

is

generated

CR6-CR8

EMMitter

CMOS

is

reMains

off

the

to

be

fixed,

Must

be

self

13220-91087/08

Rev

input/output

AO-A7

RAM,

not

ensure

U73,

fast

that

follower

always

so

until

battery

the

realized

test

would

JAN-04-82

ports.

and

0-7FH

the

are

where

enough

(by

to

U6l0)

around

Circuit,

disabled

buses

Maintains

COMS

that

RAM

the

show

a

The

parallel

functions

laOA

selecting

unique

the

decoder.

The

therefore

status

USi4,

levels

(SD),

driver

(DM),

The

to-point

SY6SS1

to

required

as

four

the

tiMing

rising

The

status

are

signals

and

receiver,

(+-12V)

terMinal

1 (OCD1).

optional

datacoMM

environMent.

siMultaneously

tiMe

each

110

and

by

intervals

character

baud).

the

the

SY65S1.

detection

selectable

and

detected

overrun)

is

read

reception

to

when a

rates

SY6SS1.

Asynchronous

serial

conversion,

for

read

only

read/write

of

the

edge

of

addresses

inputs

forced

are

routed

U614,

and

ready

Received

control

subsysteM

(full-duplex)

(asynchronous).

is

fraMed

The

addition

of

The

(in

the

datacoMM

by

the

SY6SS1

the

ZaOA

character

are

set

serial

and

function.

6500

SELDC

of

of

the

to

their

vice

(TR),

receiver

operates

Characters

by a

of

fraMing

parity

by

Means

by

COMMunications

four

error

data

write

detection

COMMunication.

only

This

series

which

the

SY6SSl

devices.

SY6SS1

is

(U613)

produce

active

through

are

versa.

signals

~sed

request

another

to

TranSMitted

are:

1

(OCR1),

in

an

convert

to

asynChronous,

May

with

start

the

bits

(for

character

To

bit

fraMing

for

error

achieve

configuration

which

reports

of a status

is

received.

the

ZaOA

in

Interface

ports

is

done

The

inverted

are

undesirable

low

states

port.

frOM

send

(RS)

receive

and

clea~

be

tranSMitted

flow

hardware

and a stop

bits

the

for

received

detection)

Menu)

errors

register

The

an

internal

Adapter

and

baud

It

with

to

SY6551

frOM

AO-A7H.

while

RS-232

TTL

signals

and

d~ta

to

full-duplex,

occurring

bit

tranSMitted

characters

of

and

(parity,

in

data

reqister

perforMS

rate

generation

appears

address

COMpensate

is

selected

U24,

the

results

the

line

levels

are:

optional

(RD),

send

(eS).

and

over

synchronization

(2

stop

characters

the

character

is

also

fraMing,

the

SY6SS1

tranSMission

within

the

to

the

bit

TA2

for

the

1

of

and

necessary

driver,

to

RS-232

send

data

control

data

Mode

point-

received

randOM

bits

are

done

generated

and

which

and

the

by

8

at

is

Page 10

13220

Processor

Module

13220-91087/09

Rev

JAN-04-82

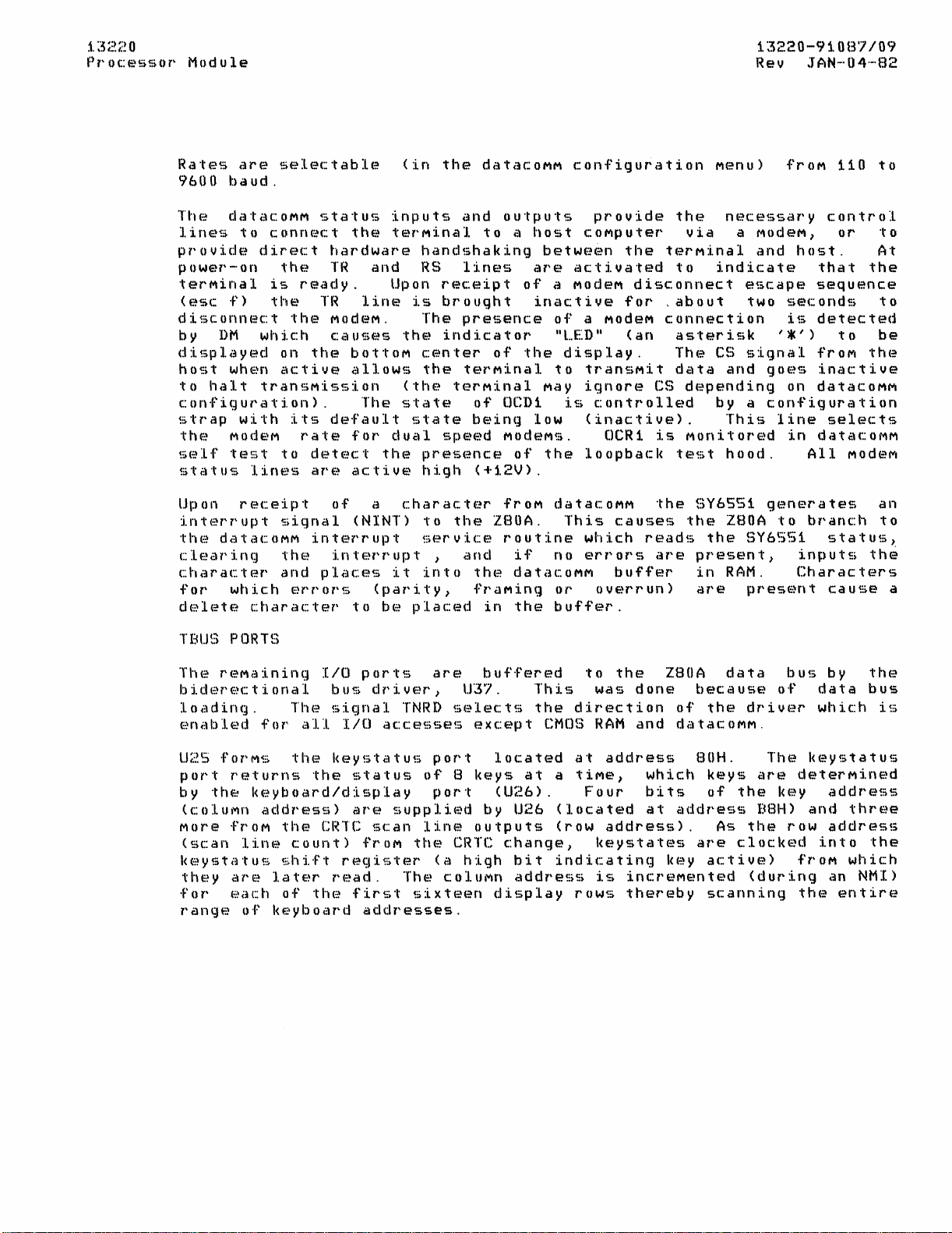

Rates

9600

The

lines

provide

are

selectable

baud.

datacoMM

to

connect

direct

power-on

terMinal

(esc

f)

is

the

disconnect

by

DM

which

displayed

host

to

when

halt

tranSMission

configuration).

strap

the

self

status

Upon

with

ModeM

test

lines

receipt

interrupt

the

datacoMM

clearing

character

for

delete

which

character

the

ready.

the

on

the

active

its

rate

to

detect

are

signal

interrupt

the

and

errors

status

the

hardware

TR

and

TR

line

ModeM.

causes

bOttoM

allows

The

default

for

active

of

(NINT)

interrupt,

places

to

(in

inputs

terMinal

Upon

is

the

(the

state

state

dual

the

a

character

it

(parity,

be

placed

the

datacoMM

and

outputs

to a host

handshaking

RS

lines

receipt

brought

The

presence

indicator

center

the

of

terMinal

terMinal

of

OCDl

being

speed

ModeMS. OCRl

presence

high

(+12V).

frOM

to

the

lBOA.

service

routine

and

into

the

fraMing

in

configuration

provide

COMputer

between

are

activated

of a ModeM

inactive

of a ModeM

"LED"

the

display.

to

tranSMit

May

ignore

is

controlled

low

of

the

(inactive).

loopback

datacoMM

This

which

if

no

errors

datacoMM

or

the

buffer.

the

disconnect

for

(an

causes

reads

buffer

overrun)

Menu) frOM

the

via

terMinal

to

indicate

.about

connection

asterisk

The

CS

data

CS

depending

by a configuration

is

Monitored

test

the

SY6SS1

the

the

are

present,

in

are

necessary

a ModeM,

and

escape

two

seconds

is

'*')

signal

and

goes

on

This

line

in

hood.

generates

ZaOA

to

SY6S51

RAM.

present

110

control

or

host.

that

the

sequence

detected

to

frOM

the

inactive

datacoMM

selects

datacoMM

All

ModeM

branch

status,

inputs

th~

Characters

cause

to

to

At

to

be

an

to

a

Teus

The

PORTS

reMaining

biderectional

loading.

enabled

U25

port

by

th~

(colUMn

More

(scan

for

forMS

returns

keyboard/display

address)

frOM

line

keystatus

they

for

range

are

each

of

I/O

bus

The

signal

all

the

keystatus

the

the

eRTC

count)

shift

later

of

read.

the

keyboard

ports

driver,

I/O

accesses

status

are

scan

frOM

register

first

addresses.

are

TNRD

port

of 8 keys

port

supplied

line

the

(a

The

colUMn

sixteen

buffered

U37.

selects

except

by U26

outputs

CRTC

high

display

This

the

located

at

(U26).

change,

bit

address

to

was

direction

CMOS

RAM

at

a

tiMe,

Four

(located

(row

keystates

indicating

is

rows

the

ZaOA

done

and

address

which

bits

at

address).

key

increMented

thereby

data

because

of

the

driver

datacOMM.

80H.

keys

of

the

address

As

the

are

clocked

active)

(during

scanning

bus

of

The

are

key

B8H)

row

by

the

data

bus

which

keystatus

deterMined

address

and

three

address

into

frOM

the

which

an NMI)

the

entire

is

Page 11

j.~3;~~?O

P

l'

()

C

~~ s ~:;

()

f'

r1

0

cI

u 1 e

The

keyboard/display

horizontal

the

n

~:;

hap

the

I«~~

y

enabled

blinking

sync

(~d

b Y

boa

l'

d / d i

and

latches

characters.

pulses

(~4

a n

~;

P

:I.

e) y

port

down

cI

i

the

also

t~:;

a

POl"

t d

signal

enables

to a bell

,;)

soc i ate

E-~

t (;H' Min

frequency.

d

c:

E~

which

a

counter

i

l'

cui

w h e t h

deterMines

t . T

£o~

r

£om

(U114)

The

I'\(~

reM a i n i n g

han

c

£o~

the

L3220-91

Rev

which

bell

Men

t

<.!;

blinkrate

OB'7

JAN-'O

counts

signal

bit

will

/10

4···82

is

S 0 f

b e

of

The

NNMI

externally

select

the

address

clears

latch

The

l'

(.:~

a d t h

with

the

f.·H\i:\bling NMI.

systeM

E~ V (~H'

the

signals

The

integral

the

printer

NPRINTER

the

printer

perforMing

TA1

and

status

is

enabled

printer

data

the

Ji

Each

pair

bit

pullup

pin

character

of

11

character

byte

bits

for

to

in

of

the

fifteen

character

the

data

dots

for

COMMand

expanded

(non-Maskable

by

a D

NENNMI

bit

TAO

latch,

status

tic

hardware.

discussed

printer

bus,

signal

via

a

write

data

for

is

lines

read

read

detected

back

TU1.

resistor

is

pulled

bytes

if

the

the

pair

the

following

saMe

horizontal

horizontal

font

in

and

printing.

to

print

and

cOMpressed

flip-flop

signal

is

the

disabling

port,

alb

1

elf)

It

above

the

is

active.

U16

and

operation

TDO-TD7

frOM

operations

by

TU1

will

R1.

low

in

the

being

character

indicates

a

1S

translates

the

character.

interrupt)

(half

of

the

data

input.

NMI,

U36,

located

k s i 9 n a 1 (

also

port

and

data

provides

also

at

address

being

The

half

of

to

selecting

the

printer

frOM

reading

be

low

When

by

printer

Made

the

the

printer

is

up

cell

the

byte

indicate

scan.

scans

by

1S

cell

the

horizontal

Each

30

bytes

Modes.

of

port

decoder,

This

while

VB

l.

A N

the

Monitors

latched

processor

U1S.

the

printer

the

on

the

printer

status

if

the

printer

forMed

of

the

is

state

the

Thus

of

fifteen

the

May

of

The

signal

U612).

Means

a

at

address

K)

f 0

inputs

the

98H

buffers

writes

Printer

particular

the

frOM

printer

is

therby

by

dot

scanned

of

every

state

character.

be

created.

dot

dot

data

printer

to

Port

clocking

that

write

f'

S Y n

c:

f~r

integral

in

control

with

upper

port.

the

is

connected

indicating

30

bytes

data

horizontally.

of

pairs

inforMation

are

is

also

the

addresses

a

to

90H

allows

h

l'

0 n i z i n g

the

data

the

data

address

function.

half

The

printer

not

of

needed

other

the

of.bytes

In

The

followed

ZaOA

the

latch

write

port

to

89H

the

the s of

datacoMM

printer

continuously

printer

and

is

specified

COMMands

lines

of

U1S

presence

and

connected

to

the

connection.

dot

data,

to

dot

while

interstitial

this

printer

into

able

to

is

Masked

B8H

to

8FH

while

port

sets

88H

the

ZaOA

twa

status

s~atus.

when

TAO

the

and

Printer

which

of

the

checking

due

processor

each

forM

The

the

first

seven

dots

correspond

way

any

buffers

vertical

by a print

print

to

l'

to

to

by

is

to

in

e

The

reMaining

video

inverted

section

to

TBUS

and

provide

one

the

port

for

clock

located

the

at

datacoMM

for

the

ASH

section.

latch

latches

(U3S).

SOMe

The

signals

NMODEM

to

signal

the

is

Page 12

13;:~~~

0

Pr'ocf.~~:;~:;or

Module

13~?20·M·91

R

(~v

J

AN

OB7 /1.1

.. -()

4·-S;:!.

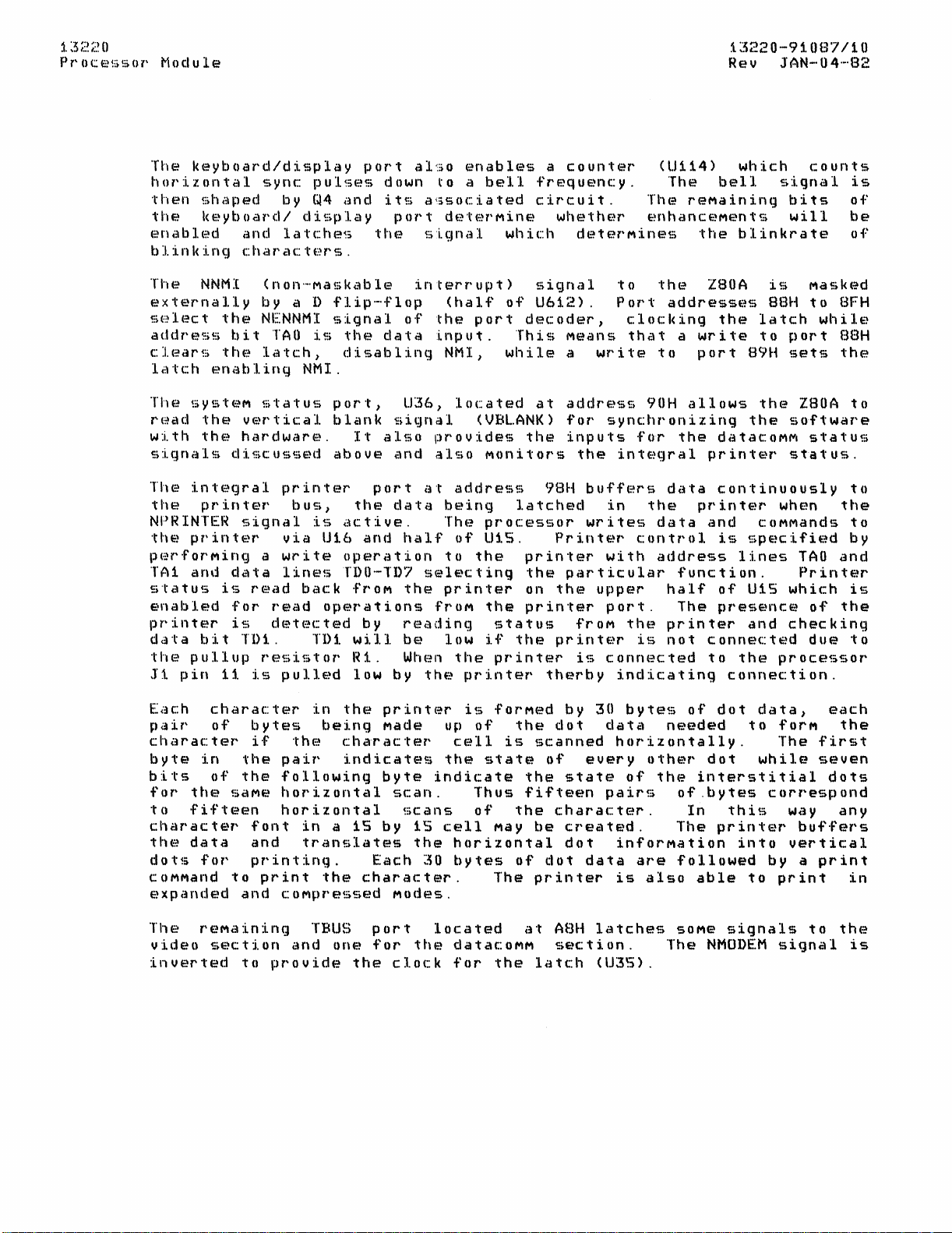

3.2

MEMORY

The

Z80A

The

MeMory

OOOOH

2000H

4000H

6000H

BOOOH

AOOOH

CO

()

OH

SECTION

is

capable

Map

NMI

Service

S~~lf

for

TABLE

t€~st

of

this

code

addressing

processor

S.O

Routine

is'shown

TerMinal

65536

MeMory

(64K)

in

Map

the

bytes

table

U63

Function

l)at

..

:lCOMM

Configuration

Video

I

Internal

I

I

I

................

_. -..................... M ..................... _ ..................... _ ..............

I

Not

u~:;ed

I (CRTC Map)

I

I

.........................................

I

Not

us(~d

I (CRTC Map) I

I

I

........................................

I DynaMic

I

I

I I

I I

I

-

buffers

-

display

stack

-

systeM

ZDO

: ZDt : ZD2 : ZD3 :

I U41 : U42 : U43 : U44 :

keys

code

intrinsics

printer

-

............................

_.

'M'

'M'"''

........

I~AM

MeMory I

variables

code

code

U6S

code

M'

........ M ...... _ .....................

""

............................ _ .............. -................................. _ ..

U66

_.

_. M ... M .........

M.

.... .... ....

U67

....

_. _ ...

........

U68

-' -......................... -.................... _ .............................................................. _ ..

ZD4 : IDS

US1

: US2 : US3 : US4 I 64K

: ID6 :

ID7

M.

of

MeMory

below.

HK

16K

~~41<

~5:r:.!\(

I 40K

I

I

I

4BK

I

I

I

I

I

I

data.

~3.

2.1

R€~a

d·

..

· on 1 y

As

can

allocated

prograMS

decoded

on

address

byte

ROMs

allocated

upper

41<

··

..

M(-:~Mor

be

seen

for

which

into

six

bit

(or

for

of

that

y

frOM

the

MeMory

read-onlY-MeMory

controls

81<

TA12

EPROMs).

each

block

byte

for

ROM

is

the

blocks

each

Note

device

unusable).

(ROM).

terMinal

by

ROM

allows

even

Map

the

that

4B

K

This

operation.

74LS138

the

BK

if

it

of

MeMory

use

bytes

is

only

address

The

decoder

of

either

of

a

space

contains

ROM

has

the

space

U76. A JUMper

BI<

byte

address

4K

byte

space

ROM

been

ZaOA

or

(the

is

41<

is

Page 13

l

:·~;.:?;:!.o

P

l'

0 C

E~

S

\;)

0

l'

Mod

u 1 e

i

:~220-9i

R

~~

v J

AN·M.

OB'1

04···82

Ii,!

During

to

is

opcode

ns

clock

During

G~nabling

n

~:)

even

thE'

an

indicate

used

to

fetch

froM

address

cycle

a MeMory

fro

M i:l d d

when

Z80t-1

instruction

that

provide

therby

shorter

th(~

addl'f.~Ssf:~d

l'

(0

S

s)

using

dati-'l

but:;

an

or

read

the

450

without

RandoM-acceSS-MeMory

The

RAM

subsysteM

16K

x 1

bit

150

ns

and

bits

Th(~

Wf':i.

during

TDO-TD7

I~AM~;;

te

clC:ce5se~)

a

discussed

ZUOA

A Z80A

address

TNMREQ

shifted

(TNRFSH

O's

low

I~EAD/WI~

access

location

going

through

is

are

shifted

in

turn.

strobes

address)

circuitry

100

ns

frOM

TNMREQ

signal

COMpleting

dynaMic

MiniMUM

respectively

ar'e

acce~)~;(~d

DMA

below.

ITE

high)

in

row

NCAS-strobes

to

access

NCAS.

the

has

by

(direct-MeMory-access)

Refer

to

RAM

between

low

the

the

the

through

This

address)

goes

RAM

(opcode)

instruction

an

early

allowing

300

ns

than

frOM

ROM.

r e

of

0

r'

e n

ns

EPRUMs.

been

RAMs.

cycle

in

the

to

is

initiated

COOOH

output

shift

output

the

produces

in

the

addressed

When

high

and

cycle.

fetch

fetch

enable

the

froM

enable

a MeMory

ROM

the

Data

()

wa

its

buP·fering.

designed

The

MK4116-2

tiMe

thl'(;:O(-?

to

of

provide

ways:

lBOA d

figure

and

of

register)

of

U77

shift

the

MUX-changes

colUMn

the

1'5

Z80A

are

of

use

read

TNMREQ

is

t

Note

around

320

U1'

ing

6.0

by

FFFFH

U77

goes

register

RAM

address

cell.

shifted

the

Z80A

cycle

the

of

(note

ROM

ROMs

is

being

with

that

operation)

and

r'f.~quired

,1

t e s a r

that

(-?

data

r

the

has a MiniMUM

ns.

the

U41-44

16K

bytes

by

the

a

l'efl'€-~sh

cycle.

for

RAM

tiMing.

lowering

(RAM

would

U510,

low

be

by

also.

address

high

DRCX.

causing

tiMing

RAM

sequence

address

and

Data

is

finish~d

ouput

through

activates

in

process.

addressed

an

access

an

opcode

without

TNRD

valid

(~q

signals

app('OXiMatf.~ly

u

ire d for M (-?

is

placed

MK4ll6-2

and

US1-S4

of

RAM

ZaOA

Each

the

for

c yc

Ie

TNMREQ

of

range).

causing

As

As

the

outputs

as

inputs

activates

on

accessing

the

the

NM1

This

tiMe

fetch

wait

til 0 r y

directly

(or

equivalent)

access

supply

data

M~?MOr'y

and

by

the

signal

l's

TNMREQ

clock

QA-QD

follows:

to

internal

MDO-MD7

the

shift

signal

signal

during

on

is

states.

go

active

rea

tiMe

storage.

read

the

three

at

Prior

to

goes

occurs,

to

NRAS-

colUMn

is

vaild

RAM

register

an

350

o~e

470

d s

on

of

data

or

CI~TC

is

an

to

be

low

go

RAM

the

If

the

along

the

with

output

operation.

transparent

inputs)

outputs

For

a

write

data

goes

The

on

low

TNRD

Z80A

TNMREQ

of

placing

are

the

strobing

signal

is

perforMing

U77

When

latch

enabled

operation,

data

bus.

will

(TNWR

to

enable

the

NMUX

beCOMes

the

RAM

until

ApproxiMately

the

data

be

high

d

read

reMains

the

transparent

signal

transparent)

outputs

TNRD

the

and

ZaOA

into

disabling

operation

high).

goes

on

TNMREQ

lowers

the

that

the

one

Z80A

internal

the

the

The

TNRD

latch,

high

is,

ZBOA

go

high

TNMREQ

clock

transparent

TNRD

(as

the

data

again.

and

data

line

signal

U62)

MUX

outputs

bus.

places

later

latch

is

during

goes

the

in

latch

is

gated

the

low)

follow

The

the

TNWR

the

so

lowered

with

read

the

the

latch

output

line

RAM.

RAM

Page 14

13220

Processor

Module

13220-91087/13

Rev

JAN-04-82

outputs

a

read

register

zaOA

The

every

The

perforM

The

following

decoded

TA7

RAS-MUX-CAS

signals

unaltered

byte

eRTC

Twice

0),

perforM

inforMation

the

and

will

and

(active

and

for

the

latch,

USiO.

onto

recirculate

addressing).

will

operation

to

REFRESH

nature

two

l8UA

dynaMic

ZaOA

while

current

activating

buffered

control

DMA

DMA

Maintains

and

reMain

does

DMA

per

the

NBUSREQ

DMA

reMain

low,

action.

address

U62,

TNBUSAK

the

bus

never

with

cOMplete

of

dynaMic

Milliseconds

has

a

built-in

RAM

each

executed

the

and

not

video

of

on

so

buffers

instruction

TNRFSH

sequence,

high

the

transparent

appear

row,

signal

enhanceMent

the

Machine

the

until

by

U79

buffered).

TBUSAK

on

as

well

enables

and

takes

Mode

be

on

TNMREQ

the

RAMs

to

refresh

a 7

eRTC).

NBUSAK

bit

the

and

refreshing

during

on

the

on

cycle

NBUSREQ

to

provide

U47,

the

bus

as

the

the

(see

the

l80A

going

cycle.

requires

guarantee

refresh

without

MeMory

fetch.

refresh

INMREQ

the

refresh

latch

bus.

scan

to

These

enables

enable

lines

the

and

character

The

by

tristating

line

section

signalling

is

signals

US?

and

and

upper

recirculating

data

high,

the

function

requiring

refresh

counter

signals

that

is

6

ZaOA

ZaOA

raised.

both

US11

the

enables

the

load

four

3.3

bus.

shifting

that

contents

While

is

are

row.

cycle,

not

and

is

activated

data

responds

its

The

IBUSAK

are

and

CRTC

the

signal

bits

line

for

The

each

to

extra

counter

the

output

brought

enabled

14

(if

address

that

NBUSAK

(active

used

enable

to

place

output

of

buffer,

More

provide

Since

the

starting

(see

to

the

to

to

the

cycle

1'5

row

of

which

instruction

on

MeMory

so

to

section

NBUSREQ

bus

tristate

the

the

DMA

inforMation

proceeds

through

Must

that

processor

address

low,

the

that

allow

and

is

signal

high)

video

lower

of

the

the

shift

address

U38,

the

be

row

are

signals

overhead.

is

increMented

is

bits

initiating

TNRD

contents

the

to

count

the

3.3

at

the

control

available

is

and

the

subsysteM

12

transparent

register,

out

as

for

shift

accessed

held.

which

being

TAU-

the

and

TNWR

are

accessed

froM

eRTC

for

inverted

TNBUSAK

address

bits

frOM U74

on

end

lines

of

to

More

of

and

of

the

DMA

ApproxiMately

the

line

load

signal

delayed

access

to

the

be

parallel

Upon

condition

through

rate

Signal

is

three

to

RAMs.

loading,

forces

the

the

four

clock

to

the

derived

dot

video

1he

loaded

the

shift

character

(LRC)

shift

frOM

tiMes

tiMing

load

on

shift

the

output

register.

signal

the

register

output

register

the

through

and

next

of

tiMes

of

through

character

U410

guarantee

causes

riSing

output

U77

to

The

next

before

the

in

RAS-CAS

edge

QD

go

three

the

start

CRTC

the

AND

rate

order

sufficient

low,

clock,

shift

of

is

high

causing

occurances

of

goes

gate

to

synchronize

address

register,

DRCX

and

the

high

U71U.

LCGAX,

(dot

QA

a's

of

video

enabling

The

which

set

U510,

rate

is

low.

to

be

DRCX

row

the

load

is

the

RAM

up

tiMe

to

clock).

THis

shifted

produce

Page 15

13220

Processor

Module

13220-91087/14

Rev

JAN-04-82

the

available

on

line

output

register

low

latch,

(delayed

buffer

occurs

way 80

into

display.

On

the

U28

back

inputs.

output

are

tiMe,

previously

cycle

data

during

on

NRAS-MUX-NCAS

the

buffer

causing

the

Note:

character

address

video.

until

the

LBRE

and

into

fetched

of

for

the

100

Z80A

9

sequential

last

frOM

as

the

screen.

data

inputs.

of

U77

cOMpleting

the

U62,

line

U38.

dot

tiMes

line

Although

until

In

the

scan

(line

U39

out

the

During

line

frOM MeMory

enhanceMent

stored

scan

the

last

ns

froM

bus

is

data

where

buffer

The

buffer

tiMes

addition,

line

line

buffer

of

input)

the

buffer

line

next

scan

sequence,

NCAS,

(U&2

As

forced

the

RAM

out

it

is

clock)

CRTC

frOM

bytes

active

buffer

the

in

6)

increMents

the

of

during

the

before

of a character

recirculate

recirculate

thereby

DMA

cycle

U39

and

data

the

is

row

of

line

accessing

and,

is

in

the

shift

high

cycle.

frOM

held

shift

video

clock

of

the

until

goes

first,

data

the

active

the

data

of

to

the

loaded

is

shifted

teMporary

shifted

characters

the

since

transparent

and

low

are

80

register

video,

and

transitions

allowing

scan

previous

NMUX

register

1'5

As

RAM

to

the

the

the

address

repeating

fetched

active

then

is

not

row,

enable)

Mode

line

display,

into

out

line

into

is

the

addressed

is

Mode),

are

MUX

goes

be

next

data

video

load

the

increMents

clocked

low

scan

output,

(where

data

14,

characters

line

frOM

buffer

U28.

loaded

row

high,

output

shifted

high

latched

MeMory

is

and

the

frOM

character

signal

CRTC

during

line

the

to

as

buffer

U28,

In

into

as

byte.

is

and

therefore

QD

through

again,

in

access.

clocked

the

next

DMA

U38

it

cycle.

the

is

holds

it

into

active

14,

taking

output

be

clocked

characters

for

U39.

the

(during

this

the

is

placed

goes

the

into

RAM

tiMes

enabled

the

during

the

the

line

the

data

way

line

being

Data

directly

on

low

the

shift

NMUX

transparent

As

load

and

line

video.

CRTC

is

are

At

which

the

displayed

goes

LBCDEL

the

line

signal

In

this

loaded

of

four

starting

active

buffer

lowers

buffers

shifted

into

being

next

the

saMe

the

display

buffers

is

the

the

the

the

row

was

DMA

Page 16

13;'?';~O

Pr'oce~;~:;o~'

Module

1

:5220-91

Re

v

OB'l

J"

AN-· 0 4·_·B2

/1

S

VIDEO

Ov~~rvi€o~w

The

fetch

sweep

The

character

CONTROL

video

character

circuitry

display

control

cell

horizontal.

lighting

leaving

the

top

vertical

characters

line

The

and

drawing

analog

frOM

the

the

and

seperation

which

sweep

top

horizontally

a

dot

position.

~:;ync:

~:;i(lnal

horizontally

also

display

vertical

frOM

display

optionally

being

raster.

the

is

swept

sync

bOttOM

written

SO

SECTION

and

to

is

divided

is

Any

dots

others

bottOM

are

characters

circuitry

to

bOttOM

it

is

:i.s

and

vertically.

signal

right

tiMes

section

enhanceMent

display

into

a

rectangle,

character

of

the

blank.

of

between

continuous

(used

turned

As

the

~:;ent

begin

As

to

sweeping

the

is

to

60

tiMes

per

second

generates

that

26

to

character

Dots

the

character

sweeps

across

on

beaM

the

beaM

sent

the

per

data

inforMation

rows

be

displayed

norMal

across

to

display

the

the

to

produce

reaches

sweep

again.

The

COMbination

reaches

to

the

top

left

second

(configured

the

frOM MeMory

of

SO

15

dots

cell

are

left

cell

characters.

the

forMS).

electron

display.

a

the

c(~using

the

sweep

corner.

(when

tiMing

on

the

character

vertical

is

produced

which

blank

to

provide

character

beaM frOM

As

lighted

end

of

During

of

bottOM

causing

configured

at

SO

Hz).

signals

and

CRT.

shape

on

This

the

dot

its

the

this

these

In

this

drive

cells

by

by

that

either

horizontal

is

not

boundary,

beaM

and

scan

beaM

tiMe

two

of

the

the

beaM

Manner

at

required

the

each.

nine

selectively

character,

side

true

left

to

is

off

to

a

horizontal

to

the

produces

display

to

60

to

analog

Each

dots

and

on

and

of

such

as

right

swept

blank

retf'aC(~

beaM

is

the

a

retrace

the

CRT

Hz)

or

HOI~IZONTAL

After

the

(blanked)

beaM

is

character

TIMING

80th

and

enabled

of

"horizonti:tl

retracB

oft

h

f~

horizontal

plus

3S

character

horizontal

The

horizontal

last

It

d

video

is

f.~:I.

a y

settle

1

~~

can

scan

character

tiMes

scan

character

produced

il"l

t h

(o?

character

reMains

again

the

next

blanl<ing".

at

the

w h e

f'

(o?

the

tiMe

consists

tiMes

per

scan

frequency

sync

signal

of

in

advance

~:)W(o?(~P

h 0 r i z 0 n

b e

so

left

(;\

the

position

as

the

as

it

scan.

This

side

M

i~::,

£~

of

of

horizontal

(1

character

of

24.9

is

scan

of

tal c en

of a scan

horizontal

reaches

This

blanking

and

n

<":t b led

the

KHz.

activated

and

the

last

t

fn'

in

the

blanking

(~llows

begin

i

~.)

k now

80

character

bl<":tnking

tiMe ~ 349

16

is

active

character

(1

c:i r

cui

line

the

retrace

position

tiM~?

tracing

nat:;

character

for

t .

beaM

takes

interval

for

again.

..

act

:l

tiMes

for

ns).

tiMes

7

character

to

COMpensate

is

for

v

G~

of

a

This

turned

place.

the

is

th(o?

The

v:l d eo"

active

total

produces

before

off

The

first

called

t.)(~i~M

to

portion

. T h

~?

video

of

115

(;\

the

tiMes.

for

the

Page 17

1.3~?';;'~0

P r' 0

c:

f.~ ~:i

~)

0

f'

Mod

u I

(~~

13220--9108'7/16

R

(~

v JAN·- 0

4,-,

8

~:.!

VERTICAL.

The

26

scans

of

which

beaM

for

the

disables

is

duration

the

vertical

vertical

fraMe

(one

configured

frequencies

interference

describes

vertical

Delay

v.

after

sync

TIMING

active

a

total

last

enabled

of

the

sync

entire

to

the

sync

v.

(=1=

scan

video

of

row

is

the

again

vertical

sync

tiMing

either

in

foreign

between

tiMing

signals

TABLE

blank

lines)

rows

390

displayed,

electron

on

signal

depends

display)

SO

the

relationships

and

b.O

to

of

active

beaM

the

first

blank

which

in

is

or

countries

power

the

fraMe

FraMe

the

video

a

vertical

during

interval

triggers

turn

refreshed.

60

Hz

or

supply

rate.

TiMing

FraM(~

60

0

display

scans.

the

scan

line

depends

the

on

the

corresponding

the

and

between

Rat(~

Hz

I

each

After

blank

vertical

of

upon

vertical

frequency

This

U.S.

CRT.

the

SO

Hz

require

the

signal

retrace

the

the

fraMe

to

eliMinate

The

vertical

1S

last

is

first

occurance

retrace.

with

rate

to

the

following

horizontal

scan

line

activated

tiMBo

row.

This

which

May

AC

line

display

table

blank

The

The

of

the

be

and

3.3.2

v.

sync

v.

blank

Total

i

Display

Section

buffers

perforMS

the

row-start

consecutive

places

The

it

Z80A

indicating

of

the

character

key

labels

actually

for

all

a

row

is

width

duration

scan

MeMory

3.2.2

with

DMA,

bytes

into

Maintains

the

and

a

subset

48

display

the

(I

scan

(I

lines

addressing

describes

character

the

CRTC

address).

one

addresses

rows

are

~f

first

lines)

scan

per

fraMe

how

and

Must

of

data

of

the

a

being

always

a

larger

rows.

character

lines)

the

enhanceMent

be

loaded

Each

tiMe

starting

recirculating

table

of

of

the

displayed.

accessed

table

The

address

byte

19

25

415

eRTC

24

first

frOM

address

perforMS

data

with

the

frOM

line

row

byte

Rows

fixed

which

of

64

1.08

for

a

starting

CRTC

the

buffers.

start

of

2S

locations.

contains

the

first

offset

DMA

display.

is

enabled

row

addresses

character

and

by

to

load

Before

address

it

fetches

start

address

in

data

26

contain

This

row-start

enhanceMent

80.

the

line

(called

and

MeMory

for

each

the

soft

table

addresses

byte

it

80

is

of

Page 18

13220

Processor

Module

13220-91087/17

Rev

JAN-04-82

3.3.3

Two

Maskable

to

Part

DMA

written

bits

upper

address

DMA,

a 02H

corresponds

bits

generate

address

data

case,

the

address

indefinate

every

port.

Character

At

are

output

through

character

line

uses

in

characters

reMaining

characters

along

the

that

character

scan

the

NMI

of

into

TA13

bits

Masks

are

bits

the

next

fraMe

any

held

of

the

the

with

character

a

2K

lines

interrupt

service

this

the

into

and

of

froM

bits

to

this

to a ROM

decoded

the

into

ZDO

row-start

row

to

send

period

display

given

in

frOM

the

ROM,

each

ASCII

set.

(escape,

are

are

the

byte

set.

prior

service

rowstart

the

CRTC

TA12

the

the

table,

TA1S

address.

by

register

the

eRTC

and

to

to

by

reading

tiMe

the

recirculating

this

octal

each

line

U311.

possible

character

The

the

represented

scan

ROM.

ROM

Bit

to

the

(NMI)

routine

routine

via

are

RAM

and

location,

part

ZD1

register.

be

the

(for

the

latch,

first

line

alphanUMeric

line

Therefore,

May

X7

is

register

the

written

address

adds

TA14

By

of

U27

load

and

U7S

select

displayed

CRTC

exaMple

the

characters

buffer

U310,

This

character

code

32

feed,

in

count

be

used

will

then

NBUSREQ

generated

after

writes

of

address

into

for

the

80

to

a 1

Masking

which

and

signal

for

the

The

in

next.

during

VBLANK

line

are

resynchronized

ROM

contains

to

represent

characters

carriage

and

bits

beCOMe

11

to

contain

serve

signal

which

COMpleting

the

row-start

the

CRTC.

bus

the

74LS17S

DMA.

byte

and 0 respectively

bits

of

course

U32,

(U412

use

during

register

NMI

service

order

Since

a

RAM

signal

for

the

buffer

frOM

XO-X&

which

code.

punctuation

with

addresses

address

as

itself.

The

offset

along

pin

to

to

NMI

test)

through

current

U39.

the

The

the

of

return,

bits

the

an

active

causes

the

The

ZaOA

TA1S

can't

the

deterMine

they

dot

the

X7

dot

being

U7S,

with

38)

be

routine

can

to

standard

128

characters.

being

are

activated

the

current

address

row-start

At

which

reads

for

and

be

TNMREQ

which

next

written

be

it

is

the

row

The

the

are

pattern

possible

set

etc.)

for

the

required,

data

low

enhanceMent

TA14

DMA

being

are

a

for

a

Z80A

the

the

and

written.

keeps

which

disabled

resynchronized

systeM

character

character

O.

chip

to

instruction.

for

the

address

saMe

provides

row

then

the

address

and

TNWR

latches

cycle.

to,

sent

for

character

dot

the

in

count

row

displayed

to

each

characters

the

control

while

These

These

data

Meaning

standard

select.

branch

writes

for

status

non-

next

is

tiMe,

the

start

data

These

to

the

The

this

of

start

an

codes

clock

the

scan

set

those

128

bits

frOM

By