HOLT HI-8583CJI, HI-8582PQT-10, HI-8582PQT, HI-8582PQI-10, HI-8582PQI Datasheet

...

June 2001

HI-8582, HI-8583

ARINC 429 System on a Chip

GENERAL DESCRIPTION

The HI-8582 from Holt Integrated Circuits is a silicon gate CMOS device for interfacing a 16-bit parallel data bus directly to the ARINC 429 serial bus. The HI-8582 design offers many enhancements to the industry standard HI8282 architecture. The device provides two receivers each with label recognition, 32 by 32 FIFO, and analog line receiver. Up to 16 labels may be programmed for each receiver. The independent transmitter has a 32 by 32 FIFO and a built-in line driver. The status of all three FIFOs can be monitored using the external status pins, or by polling the HI-8582’s status register. Other new features include a programmable option of data or parity in the 32nd bit, and the ability to unscramble the 32 bit word. Also, versions are available with different values of input resistance and output resistance to allow users to more easily add external lightning protection circuitry. The device can be used at nonstandard data rates when an option pin, NFD, is invoked.

The 16-bit parallel data bus exchanges the 32-bit ARINC data word in two steps when either loading the transmitter or interrogating the receivers. The databus, and all control signals are CMOS and TTL compatible.

The HI-8582 applies the ARINC protocol to the receivers and transmitter. Timing is based on a 1 Megahertz clock.

Although the line driver shares a common substrate with the receivers, the design of the physical isolation does not allow parasitic crosstalk, and thereby achieves the same isolation as common hybrid layouts.

APPLICATIONS

!Avionics data communication

!Serial to parallel conversion

!Parallel to serial conversion

FEATURES

!ARINC specification 429 compatible

!Dual receiver and transmitter interface

!Analog line driver and receivers connect directly to ARINC bus

!Programmable label recognition

!On-chip 16 label memory for each receiver

!32 x 32 FIFOs each receiver and transmitter

!Independent data rate selection for transmitter and each receiver

!Status register

!Data scramble control

!32nd transmit bit can be data or parity

!Self test mode

!Low power

!Industrial & full military temperature ranges

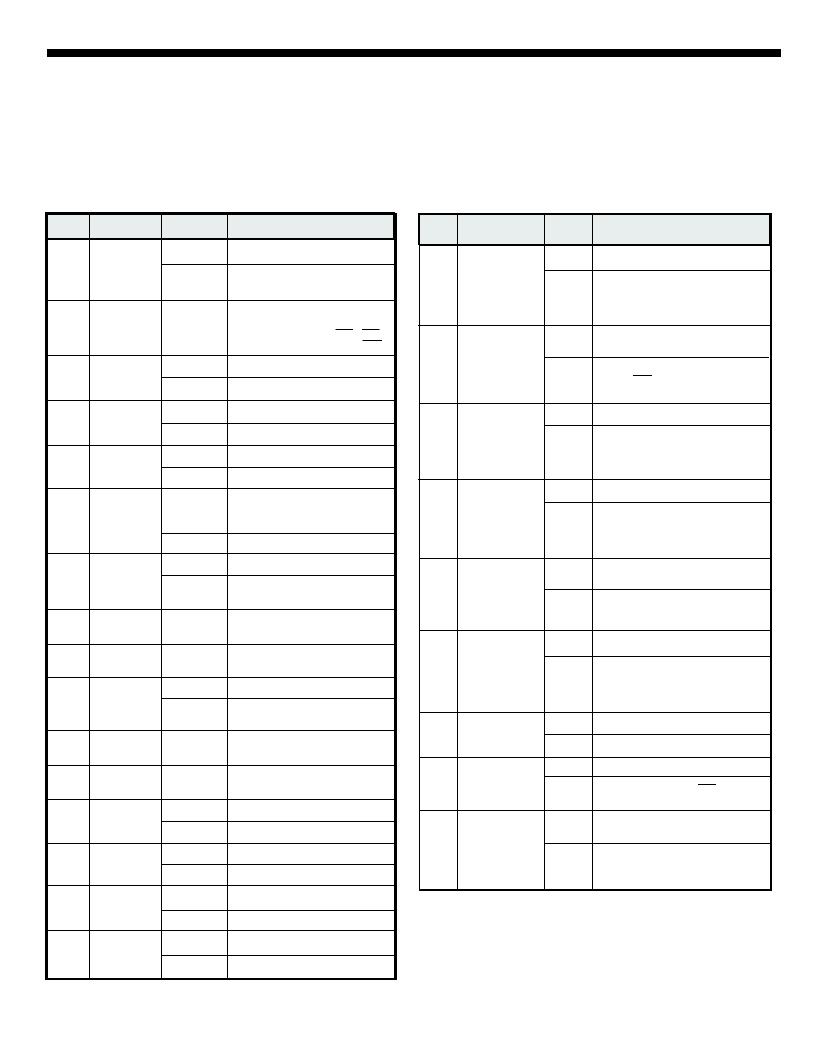

PIN CONFIGURATION (Top View)

FF1 |

- |

1 |

|

39 |

- N/C |

||

HF1 |

- |

2 |

|

38 |

- CWSTR |

||

D/R2 |

- |

3 |

|

37 |

- ENTX |

||

FF2 |

- |

4 |

HI-8582PQI |

36 |

- V+ |

||

HF2 |

- |

5 |

35 |

- TXBOUT |

|||

SEL |

- |

6 |

& |

34 |

- TXAOUT |

||

EN1 - |

7 |

HI-8582PQT |

33 |

- V- |

|||

EN2 - |

8 |

32 |

- FFT |

||||

|

|||||||

BD15 - |

9 |

|

31 |

- HFT |

|||

BD14 - 10 |

|

30 |

- TX/R |

||||

BD13 - 11 |

|

29 |

- PL2 |

||||

BD12 - 12 |

|

28 |

- PL1 |

||||

BD11 - 13 |

|

27 |

- BD00 |

||||

|

|

|

|

|

|

|

|

52 - Pin Plastic Quad Flat Pack (PQFP)

(See page 14 for additional pin configuration)

HOLT INTEGRATED CIRCUITS

(DS8582 Rev. H) |

1 |

06/01 |

HI-8582, HI-8583

PIN DESCRIPTIONS

SIGNAL |

FUNCTION |

DESCRIPTION |

|

VDD |

POWER |

+5V ±5% |

|

RIN1A |

INPUT |

ARINC receiver 1 positive input |

|

RIN1B |

INPUT |

ARINC receiver 1 negative input |

|

RIN2A |

INPUT |

ARINC receiver 2 positive input |

|

RIN2B |

INPUT |

ARINC receiver 2 negative input |

|

D/R1 |

OUTPUT |

Receiver 1 data ready flag |

|

FF1 |

OUTPUT |

FIFO full Receiver 1 |

|

HF1 |

OUTPUT |

FIFO Half full, Receiver 1 |

|

D/R2 |

OUTPUT |

Receiver 2 data ready flag |

|

FF2 |

OUTPUT |

FIFO full Receiver 2 |

|

HF2 |

OUTPUT |

FIFO Half full, Receiver 2 |

|

SEL |

INPUT |

Receiver data byte selection (0 = BYTE 1) (1 = BYTE 2) |

|

EN1 |

INPUT |

Data Bus control, enables receiver 1 data to outputs |

|

EN2 |

INPUT |

Data Bus control, enables receiver 2 data to outputs if EN1 is high |

|

BD15 |

I/O |

Data Bus |

|

BD14 |

I/O |

Data Bus |

|

BD13 |

I/O |

Data Bus |

|

BD12 |

I/O |

Data Bus |

|

BD11 |

I/O |

Data Bus |

|

BD10 |

I/O |

Data Bus |

|

BD09 |

I/O |

Data Bus |

|

BD08 |

I/O |

Data Bus |

|

BD07 |

I/O |

Data Bus |

|

BD06 |

I/O |

Data Bus |

|

GND |

POWER |

0 V |

|

BD05 |

I/O |

Data Bus |

|

BD04 |

I/O |

Data Bus |

|

BD03 |

I/O |

Data Bus |

|

BD02 |

I/O |

Data Bus |

|

BD01 |

I/O |

Data Bus |

|

BD00 |

I/O |

Data Bus |

|

PL1 |

INPUT |

Latch enable for byte 1 entered from data bus to transmitter FIFO. |

|

PL2 |

INPUT |

Latch enable for byte 2 entered from data bus to transmitter FIFO. Must follow PL1. |

|

TX/R |

OUTPUT |

Transmitter ready flag. Goes low when ARINC word loaded into FIFO. Goes high |

|

|

|

after transmission and FIFO empty. |

|

HFT |

OUTPUT |

Transmitter FIFO Half Full |

|

FFT |

OUTPUT |

Transmitter FIFO Full |

|

V- |

POWER |

-9.5V to -12.6V |

|

TXAOUT |

OUTPUT |

Line driver output - A side |

|

TXBOUT |

OUTPUT |

Line driver output - B side |

|

V+ |

POWER |

+9.5V to +12.6V |

|

ENTX |

INPUT |

Enable Transmission |

|

CWSTR |

INPUT |

Clock for control word register |

|

RSR |

INPUT |

Read Status Register if SEL=0, read Control Register if SEL=1 |

|

NFD |

INPUT |

No frequency discrimination if low (pull-up) |

|

|

|

|

|

CLK |

INPUT |

Master Clock input |

|

TX CLK |

OUTPUT |

Transmitter Clock equal to Master Clock (CLK), divided by either 10 or 80. |

|

MR |

INPUT |

Master Reset, active low |

|

TEST |

INPUT |

Disable Transmitter output if high (pull-down) |

|

HOLT INTEGRATED CIRCUITS 2

HI-8582, HI-8583

FUNCTIONAL DESCRIPTION

CONTROL WORD REGISTER

The HI-8582 contains a 16-bit control register which is used to configure the device. The control register bits CR0 - CR15 are loaded from BD00 - BD15 when CWSTR is pulsed low. The control register contents are output on the databus when SEL=1 and RSR is pulsed low. Each bit of the control register has the following function:

STATUS REGISTER

The HI-8582 contains a 9-bit status register which can be interrogated to determine the status of the ARINC receivers, data FIFOs and transmitter. The contents of the status register are output on BD00 - BD08 when the RSR pin is taken low and SEL = 0. Unused bits are output as zeros. The following table defines the status register bits.

CR |

|

Bit FUNCTION STATE |

DESCRIPTION |

CR0 |

Receiver 1 |

0 |

|

Data clock |

|

|

select |

1 |

CR1 |

Label Memory |

0 |

|

Read / Write |

|

|

|

1 |

CR2 |

Enable Label |

0 |

|

Recognition |

|

|

(Receiver 1) |

1 |

CR3 |

Enable Label |

0 |

|

Recognition |

|

|

(Receiver 2) |

1 |

CR4 |

Enable |

0 |

|

32nd bit |

|

|

as parity |

1 |

CR5 |

Self Test |

0 |

Data rate = CLK/10

Data rate = CLK/80

Normal operation

Load 16 labels using PL1 / PL2 Read 16 labels using EN1 / EN2

Disable label recognition

Enable label recognition

Disable Label Recognition

Enable Label recognition

Transmitter 32nd bit is data

Transmitter 32nd bit is parity

An internal connection is made passing TXAOUT and TXBOUT to the receiver inputs

|

|

1 |

Normal operation |

CR6 |

Receiver 1 |

0 |

Receiver 1 decoder disabled |

|

decoder |

|

|

|

|

1 |

ARINC bits 9 and 10 must match |

|

|

|

CR7 and CR8 |

CR7 |

- |

- |

If receiver 1 decoder is enabled, |

|

|

|

the ARINC bit 9 must match this bit |

CR8 |

- |

- |

If receiver 1 decoder is enabled, |

|

|

|

the ARINC bit 10 must match this bit |

CR9 |

Receiver 2 |

0 |

Receiver 2 decoder disabled |

|

Decoder |

|

|

|

|

1 |

ARINC bits 9 and 10 must match |

|

|

|

CR10 and CR11 |

CR10 |

- |

- |

If receiver 2 decoder is enabled, |

|

|

|

the ARINC bit 9 must match this bit |

CR11 |

- |

- |

If receiver 2 decoder is enabled, |

|

|

|

the ARINC bit 10 must match this bit |

CR12 |

Invert |

0 |

Transmitter 32nd bit is Odd parity |

|

Transmitter |

|

|

|

parity |

1 |

Transmitter 32nd bit is Even parity |

CR13 |

Transmitter |

0 |

Data rate=CLK/10, O/P slope=1.5us |

|

data clock |

|

|

|

select |

1 |

Data rate=CLK/80, O/P slope=10us |

CR14 |

Receiver 2 |

0 |

Data rate=CLK/10 |

|

data clock |

|

|

|

select |

1 |

Data rate=CLK/80 |

CR15 |

Data |

0 |

Scramble ARINC data |

|

format |

|

|

|

|

1 |

Unscramble ARINC data |

SR |

|

|

Bit |

FUNCTION |

STATE |

SR0 |

Data ready |

0 |

|

(Receiver 1) |

|

|

|

1 |

SR1 |

FIFO half full |

0 |

|

(Receiver 1) |

|

|

|

1 |

SR2 |

FIFO full |

0 |

|

(Receiver 1) |

|

|

|

1 |

SR3 |

Data ready |

0 |

|

(Receiver 2) |

|

|

|

1 |

SR4 |

FIFO half full |

0 |

|

(Receiver 2) |

|

|

|

1 |

SR5 |

FIFO full |

0 |

|

(Receiver 2) |

|

|

|

1 |

SR6 |

Transmitter FIFO |

0 |

|

empty |

|

|

|

1 |

SR7 |

Transmitter FIFO |

0 |

|

full |

|

|

|

1 |

SR8 |

Transmitter FIFO |

0 |

|

half full |

|

|

|

1 |

DESCRIPTION

Receiver 1 FIFO empty

Receiver 1 FIFO contains valid data Resets to zero when all data has been read. D/R1 pin is the inverse of this bit

Receiver 1 FIFO holds less than 16 words

Receiver 1 FIFO holds at least 16 words. HF1 pin is the inverse of this bit.

Receiver 1 FIFO not full

Receiver 1 FIFO full. To avoid data loss, the FIFO must be read within one ARINC word period. FF1 pin is the inverse of this bit

Receiver 2 FIFO empty

Receiver 2 FIFO contains valid data Resets to zero when all data has been read. D/R2 pin is the inverse of this bit

Receiver 2 FIFO holds less than 16 words

Receiver 2 FIFO holds at least 16 words. HF2 pin is the inverse of this bit.

Receiver 2 FIFO not full

Receiver 2 FIFO full. To avoid data loss, the FIFO must be read within one ARINC word period. FF2 pin is the inverse of this bit

Transmitter FIFO not empty

Transmitter FIFO empty.

Transmitter FIFO not full

Transmitter FIFO full. FFT pin is the inverse of this bit.

Transmitter FIFO contains less than 16 words

Transmitter FIFO contains at least 16 words.HFT pin is the

inverse of this bit.

HOLT INTEGRATED CIRCUITS 3

HI-8582, HI-8583

FUNCTIONAL DESCRIPTION (cont.)

ARINC 429 DATA FORMAT

Control register bit CR15 is used to control how individual bits in the received or transmitted ARINC word are mapped to the HI-8582 data bus during data read or write operations. The following table describes this mapping:

BYTE 1

DATA |

BD BD BD BD BD BD BD BD BD BD BD BD BD |

BD |

BD BD |

|||||||||||||

BUS |

15 |

14 |

13 |

12 |

11 |

10 |

09 |

08 |

07 |

06 |

05 |

04 |

03 |

02 |

01 |

00 |

ARINC |

13 |

12 |

11 |

10 |

9 |

31 |

30 |

32 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

BIT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CR15=0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ARINC |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

BIT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CR15=1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BYTE 2

DATA |

BD |

BD BD BD BD BD BD BD BD BD BD BD |

BD BD BD BD |

|||||||||||||

BUS |

15 |

14 |

13 |

12 |

11 |

10 |

09 |

08 |

07 |

06 |

05 |

04 |

03 |

02 |

01 |

00 |

ARINC |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

BIT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CR15=0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ARINC |

32 |

31 |

30 |

29 |

28 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

19 |

18 |

17 |

CR15=1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

The HI-8582 guarantees recognition of these levels with a common mode Voltage with respect to GND less than ±5V for the worst case condition (4.75V supply and 13V signal level).

The tolerances in the design guarantee detection of the above levels, so the actual acceptance ranges are slightly larger. If the ARINC signal is out of the actual acceptance ranges, including the nulls, the chip rejects the data.

RECEIVER LOGIC OPERATION

Figure 2 shows a block diagram of the logic section of each receiver.

BIT TIMING

The ARINC 429 specification contains the following timing specification for the received data:

|

HIGH SPEED |

LOW SPEED |

BIT RATE |

100K BPS ± 1% |

12K -14.5K BPS |

PULSE RISE TIME |

1.5 ± 0.5 µsec |

10 ± 5 µsec |

PULSE FALL TIME |

1.5 ± 0.5 µsec |

10 ± 5 µsec |

PULSE WIDTH |

5 µsec ± 5% |

34.5 to 41.7 µsec |

If the NFD pin is high, the HI-8582 accepts signals that meet these specifications and rejects outside the tolerances. The way the logic operation achieves this is described below:

THE RECEIVERS

ARINC BUS INTERFACE

Figure 1 shows the input circuit for each receiver. The ARINC 429 specification requires the following detection levels:

STATE |

DIFFERENTIAL VOLTAGE |

||

ONE |

+6.5 Volts |

to |

+13 Volts |

NULL |

+2.5 Volts |

to |

-2.5 Volts |

ZERO |

-6.5 Volts |

to |

-13 Volts |

FIGURE 1. ARINC RECEIVER INPUT

1.Key to the performance of the timing checking logic is an accurate 1MHz clock source. Less than 0.1% error is recommended.

2.The sampling shift registers are 10 bits long and must show three consecutive Ones, Zeros or Nulls to be considered valid data. Additionally, for data bits, the One or Zero in the upper bits of the sampling shift registers must be followed by a Null in the lower bits within the data bit time. For a Null in the word gap, three consecutive Nulls must be found in both the upper and lower bits of the sampling shift register. In this manner the minimum pulse width is guaranteed.

3.Each data bit must follow its predecessor by not less than 8 samples and no more than 12 samples. In this manner the bit rate is checked. With exactly 1MHz input clock frequency, the acceptable data bit rates are as follows:

|

HIGH SPEED |

LOW SPEED |

DATA BIT RATE MIN |

83K BPS |

10.4K BPS |

DATA BIT RATE MAX |

125K BPS |

15.6K BPS |

4. The Word Gap timer samples the Null shift register every 10 input clocks (80 for low speed) after the last data bit of a valid reception. If the Null is present, the Word Gap counter is incremented. A count of 3 will enable the next reception.

If NFD is held low, frequency discrimination is disabled and any data stream totaling 32 bits is accepted even with gaps between bits. The protocol still requires a word gap as defined in 4. above.

HOLT INTEGRATED CIRCUITS 4

HI-8582, HI-8583

FUNCTIONAL DESCRIPTION (cont.)

RECEIVER PARITY

The receiver parity circuit counts ones received, including the parity bit. If the result is odd, then "0" will appear in the 32nd bit.

RETRIEVING DATA

Once 32 valid bits are recognized, the receiver logic generates an End of Sequence (EOS). Depending upon the state of control register bits CR2-CR11, the received ARINC 32-bit word is then checked for correct decoding and label matching before being loaded into the 32 x 32 receive FIFO. ARINC words which do not meet the necessary 9th and 10th ARINC bit or label matching are ignored and are not loaded into the receive FIFO. The following table describes this operation.

CR2(3) |

ARINC word CR6(9) |

ARINC word |

FIFO |

|

|

matches |

|

bits 9,10 |

|

|

label |

|

match |

|

|

|

|

CR7,8 (10,11) |

|

|

|

|

|

|

0 |

X |

0 |

X |

Load FIFO |

1 |

No |

0 |

X |

Ignore data |

1 |

Yes |

0 |

X |

Load FIFO |

0 |

X |

1 |

No |

Ignore data |

0 |

X |

1 |

Yes |

Load FIFO |

1 |

Yes |

1 |

No |

Ignore data |

1 |

No |

1 |

Yes |

Ignore data |

1 |

No |

1 |

No |

Ignore data |

1 |

Yes |

1 |

Yes |

Load FIFO |

|

|

TO PINS |

|

|

|

|

|

SEL |

MUX |

32 TO 16 DRIVER |

R/W |

CONTROL |

|

|

|

|

|

|

|||||

EN |

CONTROL |

|

CONTROL |

BITS |

|

|

|

HF |

|

|

|

|

|

|

|

FF |

|

|

|

|

|

|

|

D/R |

|

32 X 32 |

|

|

|

|

|

|

FIFO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LOAD |

FIFO |

|

|

|

|

|

|

CONTROL |

|

|

|

|

|

|

CONTROL |

|

LABEL / |

|

|

|

|

|

|

/ DECODE |

|

|

|

|

|

|

BIT |

|

CONTROLBITS |

|

CLOCK |

|

||

|

|

COMPARE |

CR0, CR14 |

|

OPTION |

CLK |

|

|

|

|

|

|

|

|

CLOCK |

|

16 x 8 |

|

|

|

|

|

|

|

LABEL |

|

|

|

|

BIT |

|

|

MEMORY |

|

|

|

|

COUNTER |

|

|

|

|

|

|

32ND |

AND |

|

|

|

|

DATA |

|

END OF |

|

|

|

|

32 BIT SHIFT REGISTER |

PARITY |

BIT |

|

||

|

|

|

CHECK |

|

SEQUENCE |

|

|

|

|

|

BIT CLOCK |

|

|

|

|

|

EOS |

|

|

|

|

|

|

|

|

|

|

WORD GAP |

|

|

|

|

ONES |

SHIFT REGISTER |

WORD GAP |

TIMER |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

BIT CLOCK |

|

|

|

|

START |

SEQUENCE |

END |

|

|

|

NULL |

SHIFT REGISTER |

|

|

|

||

|

|

CONTROL |

|

|

|||

|

|

|

|

|

|

||

|

ZEROS |

SHIFT REGISTER |

|

ERROR |

ERROR |

|

|

|

|

|

|

||||

|

|

|

|

|

|

||

|

|

|

|

DETECTION |

CLOCK |

|

|

FIGURE 2. RECEIVER BLOCK DIAGRAM

HOLT INTEGRATED CIRCUITS 5

Loading...

Loading...