HOLT HI-3188PST, HI-3188PSI, HI-3187PST, HI-3187PSI, HI-3186PST Datasheet

...

HI-3182, HI-3183, HI-3184, HI-3185 HI-3186, HI-3187, HI-3188

March 2001

GENERAL DESCRIPTION

The HI-3182, HI-3183, HI-3184, HI-3185, HI-3186, HI-3187 and HI-3188 bus interface products are silicon gate CMOS devices designed as a line driver in accordance with the ARINC 429 bus specifications. In addition to being functional upgrades of Holt's HI-8382 & HI-8383 products, they are also alternate sources for the HS-3182 ( Intersil/Harris), the RM3182 (Fairchild /Raytheon) and a variety of similar DEI/DDC line driver products.

Inputs are provided for clocking and synchronization. These signals are AND'd with the DATA inputs to enhance system performance and allow the HI-318X series of products to be used in a variety of applications. Both logic and synchronization inputs feature built-in 2,000V minimum ESD input protection as well as TTL and CMOS compatibility.

The differential outputs of the HI-318X series of products are independently programmable to either the high speed or low speed ARINC 429 output rise and fall time specifications through the use of two external capacitors. The output voltage swing is also adjustable by the application of an external voltage to the VREF input. Products with 0, 13 or 37.5 ohm resistors in series with each ARINC output are available. In addition, the HI-3182, HI-3184 and HI-3187 products also have a fuse in series with each output.

The HI-318X series of line drivers are intended for use where logic signals must be converted to ARINC 429 levels such as when using an ASIC, the HI-8282 ARINC 429 Serial Transmitter/Dual Receiver, the HI-6010 ARINC 429 Transmitter/Receiver or the HI-8783 ARINC Interface Device. Holt products are readily available for both industrial and military applications. Please contact the Holt Sales Department for additional information.

FEATURES

!Low power CMOS

!TTL and CMOS compatible inputs

!Programmable output voltage swing

!Adjustable ARINC rise and fall times

!Plastic 14 & 16-pin thermally enhanced SOIC packages available

!Pin-for-Pin alternative for DEI/DDC/Intersil/Fairchild applications

!Operates at data rates up to 100 Kbits

!Overvoltage protection

!Industrial and Military temperature ranges

PIN CONFIGURATION (Top View)

VREF |

1 |

14 |

V1 |

GND (See Note * ) |

2 |

13 |

CLOCK |

SYNC |

3 |

12 |

DATA (B) |

DATA (A) |

4 |

11 |

CB |

CA |

5 |

10 |

BOUT |

AOUT |

6 |

9 |

+V |

-V |

7 |

8 |

GND |

HI-3184PS, HI-3185PS, HI-3186PS

& HI-3187PS

14 - PIN PLASTIC SMALL OUTLINE (ESOIC)**

Notes: * Pin 2 may be left floating

** Thermally Enhanced SOIC Package

(See Page 5 for additional package pin configurations)

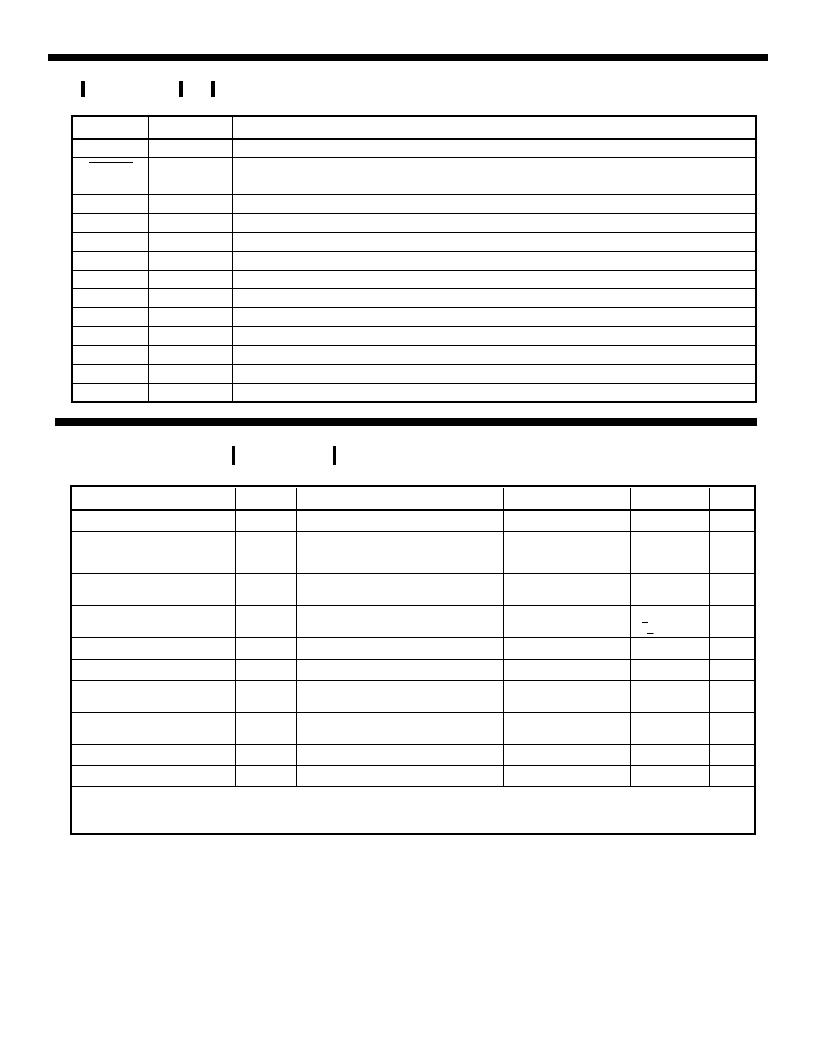

FUNCTION

+

+

ARINC 429 DIFFERENTIAL LINE DRIVER

TRUTH TABLE

SYNC CLOCK DATA(A) DATA(B) AOUT BOUT COMMENTS

X |

L |

X |

X |

0V |

0V |

NULL |

L |

X |

X |

X |

0V |

0V |

NULL |

H |

H |

L |

L |

0V |

0V |

NULL |

H |

H |

L |

H |

-VREF +VREF |

LOW |

|

H |

H |

H |

L |

+VREF -VREF |

HIGH |

|

H |

H |

H |

H |

0V |

0V |

NULL |

HOLT INTEGRATED CIRCUITS

(DS3182 Rev. B ) |

1 |

03/01 |

HI-3182, HI-3183, HI-3184, HI-3185, HI-3186, HI-3187, HI-3188

FUNCTIONAL DESCRIPTION

The SYNC and CLOCK inputs establish data synchronization utilizing two AND gates, one for each data input. Each logic input, including the power enable (STROBE) input, are TTL/CMOS compatible.

Figure 1 illustrates a typical ARINC 429 bus application. Three power supplies are necessary to operate the HI-3182; typically +15V, -15V and +5V. The chip also works with ±12V supplies. The +5V supply can also provide a reference voltage that determines the output voltage swing. The differential output voltage swing will equal 2VREF. If a value of VREF other than +5V is needed, a separate +5V power supply is required for pin V1.

With the DATA (A) input at a logic high and DATA (B) input at a logic low, AOUT will switch to the +VREF rail and BOUT will switch to the -VREF rail (ARINC HIGH state). With both data input signals at a logic low state, the outputs will both switch to 0V (ARINC NULL state).

The driver output impedance, ROUT, is nominally 75, 26 or 0 ohms depending on the option chosen. The rise and fall times of the outputs can be calibrated through the selection of two external capacitor values that are connected to the CA and CB input pins. Typical values for high-speed operation (100KBPS) are CA = CB = 75pF and for low-speed operation (12.5 to 14KBPS) CA = CB = 500pF.

The CA and CB pins swing between +5V and ground allowing the switching of capacitor values with an external singlesupply analog switch.

The ARINC outputs can be put in a tri-state mode by applying a logic high to the STROBE input pin. If this feature is not being used, the pin should be tied to ground. The STROBE function is not available in the 14 & 16-pin SOIC package configurations where the pin is internally connected to ground.

The ARINC outputs of the HI-3182, HI-3184 and HI-3187 are protected by internal fuses capable of sinking between 800 - 900 mA for short periods of time (125μs).

+5V |

+15V |

|

|

|

|

VREF |

V1 |

OUT |

|||

|

|||||

|

|

|

|

||

DATA (A) |

SYNC |

|

|

|

|

CLOCK |

|

|

|

||

|

|

|

|

||

INPUTS |

+V |

TO ARINC BUS |

|||

-V |

|||||

|

|

|

|

||

DATA (B) |

STROBE |

|

|

|

|

GND |

|

|

|

||

C |

C |

B |

|

|

|

|

|

|

|||

|

|

||||

-15V

Figure 1. ARINC 429 BUS APPLICATION

REF |

+V CA |

DATA (A) |

|

|

LEVEL SHIFTER |

|

AND SLOPE |

CLOCK |

CONTROL (A) |

|

|

SYNC |

|

|

LEVEL SHIFTER |

DATA (B) |

AND SLOPE |

|

CONTROL (B) |

V1 CURRENT

CURRENT

REGULATOR

REGULATOR

STROBE

Shorted on HI-3186, HI-3187, HI-3188

24.5Ω

24.5Ω

OUTPUT

DRIVER (A)

24.5Ω

OUTPUT

DRIVER (B)

Shorted on HI-3183, HI-3186 HI-3187, HI-3188

13Ω FA

CL

RL

13Ω  FB

FB

Shorted on

HI-3183, HI-3185

HI-3186, HI-3188

GND -V CB |

BOUT |

Figure 2. FUNCTIONAL BLOCK DIAGRAM

HOLT INTEGRATED CIRCUITS 2

HI-3182, HI-3183, HI-3184, HI-3185, HI-3186, HI-3187, HI-3188

SYMBOL |

FUNCTION |

DESCRIPTION |

VREF |

POWER |

Reference voltage used to determine the output voltage swing |

STROBE |

INPUT |

A logic high tri-states the ARINC outputs. Not available in the 14-pin SOIC package (tied to GND internally). |

SYNC |

INPUT |

Synchronizes data inputs |

DATA (A) |

INPUT |

Data input terminal A |

CA |

INPUT |

Connection for DATA (A) slew-rate capacitor |

AOUT |

OUTPUT |

ARINC output terminal A |

-V |

POWER |

-12V to -15V |

GND |

POWER |

0.0V |

+V |

POWER |

+12V to +15V |

BOUT |

OUTPUT |

ARINC output terminal B |

CB |

INPUT |

Connection for DATA (B) slew-rate capacitor |

DATA (B) |

INPUT |

Data input terminal B |

CLOCK |

INPUT |

Synchronizes data inputs |

V1 |

POWER |

+5V ±5% |

All Voltages referenced to GND, TA = Operating Temperature Range (unless otherwise specified)

|

PARAMETER |

SYMBOL |

|

CONDITIONS |

OPERATING RANGE |

MAXIMUM |

UNIT |

||

|

|

|

|

|

|

|

|

||

Differential Voltage |

VDIF |

Voltage between +V and -V terminals |

|

|

|

40 |

V |

||

Supply Voltage |

+V |

|

|

+10.8 to +16.5 |

|

V |

|||

|

|

-V |

|

|

-10.8 to -16.5 |

|

V |

||

|

|

V1 |

|

|

+5 |

±10% |

+7 |

V |

|

Voltage Reference |

VREF |

For ARINC 429 |

+5 |

±5% |

6 |

V |

|||

|

|

|

For Applications other than ARINC |

0 |

to |

6 |

6 |

V |

|

Input Voltage Range |

VIN |

|

|

|

|

|

> GND -0.3 |

V |

|

|

|

|

|

|

|

|

|

< V1 +0.3 |

V |

Output Short-Circuit Duration |

|

See Note: |

1 |

|

|

|

|

|

|

Output Overvoltage Protection |

|

See Note: |

2 |

|

|

|

|

|

|

Operating Temperature Range |

TA |

Hi-temp & Military |

-55 to |

+125 |

|

°C |

|||

|

|

|

Industrial |

|

-40 |

to |

+85 |

|

°C |

Storage Temperature Range |

TSTG |

Ceramic & Plastic |

-65 to +150 |

|

°C |

||||

Lead Temperature |

|

Soldering, 10 seconds |

|

|

|

+275 |

°C |

||

Junction Temperature |

TJ |

|

|

|

|

|

+175 |

°C |

|

Note |

1. Heatsinking may be required for Output Short Circuit at +125°C and for 100KBPS at +125°C. |

|

|

|

|||||

Note |

2. The fuses used for Output Overvoltage Protection may be blown by the presence of a voltage at either output that is greater |

|

|||||||

|

than ±12.0V with respect to GND. (HI-3182, 3184 & 3187 only) |

|

|

|

|

|

|||

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

HOLT INTEGRATED CIRCUITS 3

Loading...

Loading...