Page 1

H8S/2345 Series

H8S/2345, H8S/2344, H8S/2343,

H8S/2341, H8S/2340

TM

H8S/2345 F-ZTAT

Hardware Manual

ADE-602-129A

Rev. 2.0

1/12/98

Hitachi, Ltd.

Page 2

Cautions

1. Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s

patent, copyright, trademark, or other intellectual property rights for information contained in

this document. Hitachi bears no responsibility for problems that may arise with third party’s

rights, including intellectual property rights, in connection with use of the information

contained in this document.

2. Products and product specifications may be subject to change without notice. Confirm that you

have received the latest product standards or specifications before final design, purchase or

use.

3. Hitachi makes every attempt to ensure that its products are of high quality and reliability.

However, contact Hitachi’s sales office before using the product in an application that

demands especially high quality and reliability or where its failure or malfunction may directly

threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear

power, combustion control, transportation, traffic, safety equipment or medical equipment for

life support.

4. Design your application so that the product is used within the ranges guaranteed by Hitachi

particularly for maximum rating, operating supply voltage range, heat radiation characteristics,

installation conditions and other characteristics. Hitachi bears no responsibility for failure or

damage when used beyond the guaranteed ranges. Even within the guaranteed ranges,

consider normally foreseeable failure rates or failure modes in semiconductor devices and

employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi

product does not cause bodily injury, fire or other consequential damage due to operation of

the Hitachi product.

5. This product is not designed to be radiation resistant.

6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document

without written approval from Hitachi.

7. Contact Hitachi’s sales office for any questions regarding this document or Hitachi

semiconductor products.

Page 3

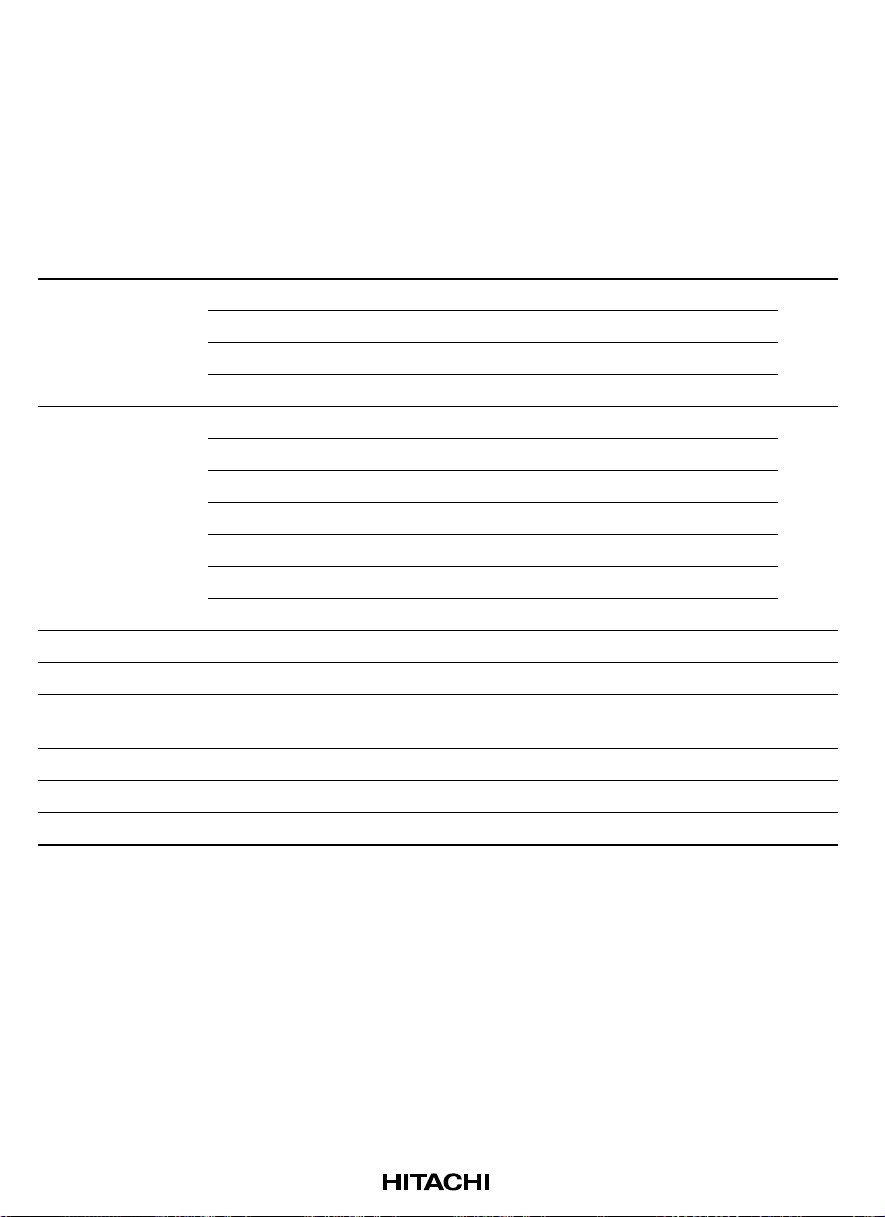

Main Amendments and Additions in this Edition

Page Item Revision

Throughout • H8S/2344, H8S/2341, and H8S/2340 added; F-ZTAT version of current H8S/2345

added. Generic name adopted: H8S/2345 Series, H8S/2345 F-ZTAT Hardware

Manual.

• Notes added where necessary indicating that the H8S/2340 is a ROMless version,

and only supports MCU operating modes 1, 4, and 5.

• Notes added where necessary indicating that the H8S/2345 F-ZTAT version only

supports MCU operating modes 4 to 7, 10, 11, 14, and 15 (and that modes 1 to 3

(normal modes) cannot be used).

• Notes added where necessary indicating that the FWE pin applies only to the FZTAT version, and that this pin is WDTOVF in the ZTAT, mask ROM, and ROMless

versions.

• Notes added where necessary indicating that the TFP-100G package is under

development.

1 to 5 1.1 Overview Amended (Information on newly added

products)

9 to 13 Table 1.2 Pin Functions in Each

Operating Mode

14 to 20 Table 1.3 Pin Functions Amended

69 to 72 3.1 Overview Amended (Description of F-ZTAT and

74 System Control Register 2 (SYSCR2) (F-

ZTAT Version Only)

76 3.3.7 Mode 7 Note 2 amended

76, 77 3.3.8 Mode 8 to 3.3.13 Mode 15 New

78 Table 3.3 Pin Functions in Each Mode Amended (Mode 10, 11, 14, and 15 pin

Amended

• PROM mode pin names partially

changed

• Flash memory mode pin names added

• Addition of F-ZTAT version operating

mode settings by pins MD2-MD0

• FWE pin description added

ROMless versions added)

New

descriptions added)

79 to 90 3.5 Memory Map in Each Operating Mode Amended (Information on newly added

products)

107 Table 5.3 Correspondence between

Interrupt Sources and IPR Settings

141 6.2.5 Bus Control Register L (BCRL) Description of bit 5 amended

Note amended

Page 4

Page Item Revision

160 Figure 6.14 Example of Wait Insertion

Timing

273 8.12.2 Register Configuration, Port G

Data Direction Register (PGDDR)

294 to 309 9.2.3 Timer I/O Control Register (TIOR) Amended (Register name added to tables)

420 12.2.5 Serial Mode Register (SMR) Description of bit 3 amended

429 to 431 Table 12.3 BRR Settings for Various Bit

Rates (Asynchronous Mode)

441 Figure 12.2 Data Format in Asynchronous

Communication (Example with 8-Bit Data,

Parity, Two Stop Bits)

461 Figure 12.15 Sample SCI Initialization

Flowchart

467 Figure 12.20 Sample Flowchart of

Simultaneous Serial Transmit and Receive

Operations

478, 479 13.2.2 Serial Status Register (SSR) Description of bits 4 and 2 amended

481 13.2.4 Serial Control Register (SCR) Description of bits 1 and 0 amended

483 Figure 13.2 Schematic Diagram of Smart

Card Interface Pin Connections

484 Figure 13.3 Smart Card Interface Data

Format

488, 489 Table 13.5 Examples of Bit Rate B (bit/s)

for Various BRR Settings (When n = 0)

Table 13.6 Examples of BRR Settings for

Bit Rate B (bit/s) (When n = 0)

491 to 493 13.3.6 Data Transfer Operations, Serial

Data Transmission

497, 498 13.3.7 Operation in GSM Mode Amended (Old section 13.3.7, Example of

510 14.2.3 A/D Control Register (ADCR) Description of bits 7 and 6 amended

519 to 524 14.6 Usage Notes (1) Amendment of setting range for analog

529 15.2.2 D/A Control Register (DACR) Bit 5 description amended

532 15.4 Usage Notes New

Amended

Description amended

Amendments to some Error column

entries (values not entered for error of 3%

or above)

Amended

Note added

Note amended

Amended

Amended

Amended (ø = 20.00 MHz column added)

Amended

Use in Software Standby Mode, replaced

with new section)

power supply pins etc.

(2) Deletion of module stop mode

interrupts

Page 5

Page Item Revision

533 16.1 Overview Description amended (Information on

newly added products)

534 Figure 16.1 Block Diagram of RAM

Title of figure amended

(H8S/2345, Advanced Mode)

535 16.3 Operation Description amended (Information on

newly added products)

Whole of

section 17

Whole of

section 20

Section 17 ROM

New flash memory description added, complete revision of section contents and layout

Section 20 Electrical Characteristics

Previous text used as electrical characteristics for ZTAT, mask ROM, and ROMless

versions; new F-ZTAT version electrical characteristics added.

"Preliminary" notation deleted and "TBD" replaced with values for ZTAT, mask ROM,

and ROMless versions.

666 Figure 20.9 Reset Input Timing Amended

669 Figure 20.12 Basic Bus Timing (Three-

State Access)

675 Figure 20.24 SCK Clock Input Timing Amended (t

Amended (t

specification)

WDS

specification)

SCKW

677 to 752 Appendix A Instruction Set Amended (Replaced with latest version)

753 to 759 B.1 Addresses Amended (Addition of registers used by F-

ZTAT version)

760 to 858 B.2 Functions Amended

• Addition of registers used by F-ZTAT

version

• Amendment of note on interrupt priority

registers A-K

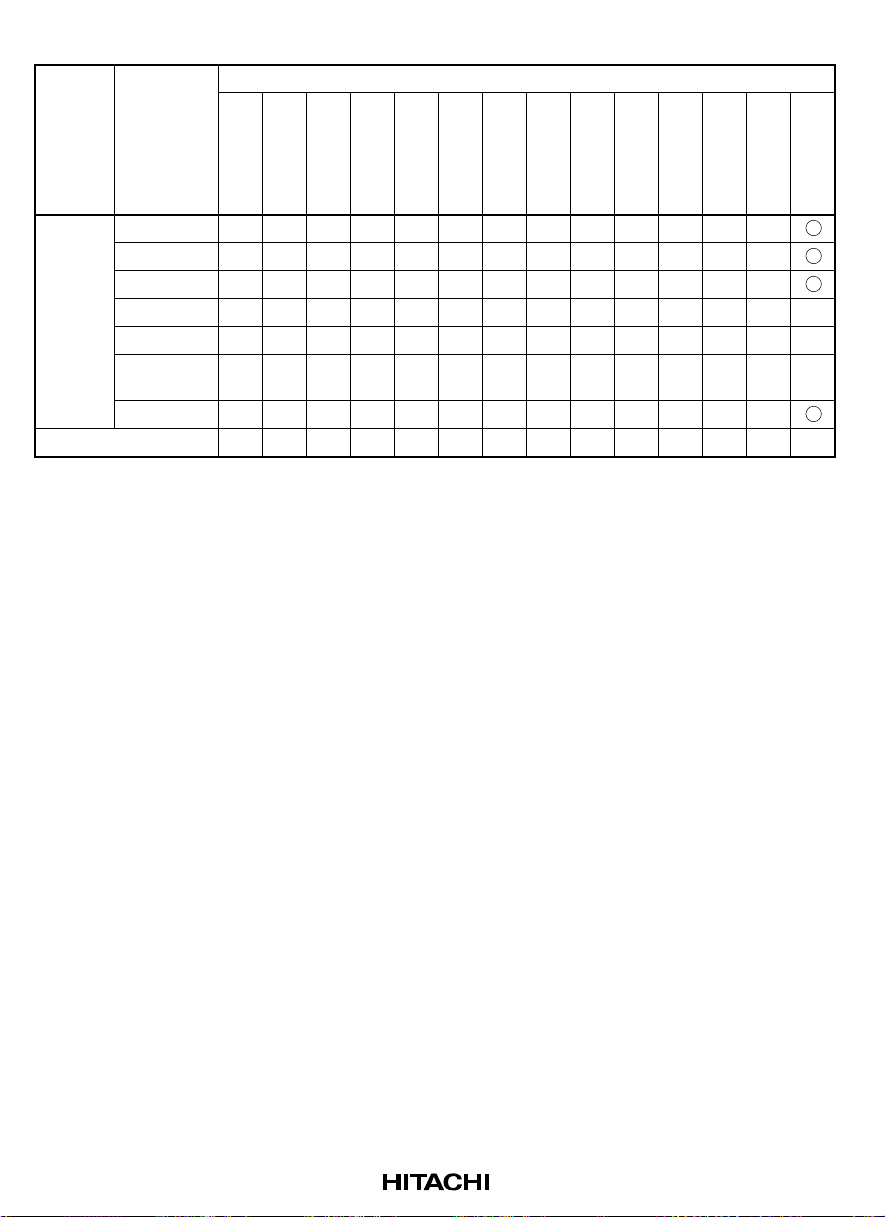

893 Table F.1 H8S/2345 Series Product Code

Lineup

Amended (Information on newly added

products)

Page 6

Preface

The H8S/2345 Series is a series of high-performance microcontrollers with a 32-bit H8S/2000

CPU core, and a set of on-chip supporting functions required for system configuration.

The H8S/2000 CPU can execute basic instructions in one state, and is provided with sixteen 16-bit

general registers with a 32-bit internal configuration, and a concise and optimized instruction set.

The CPU can handle a 16 Mbyte linear address space (architecturally 4 Gbytes). Programs based

on the high-level language C can also be run efficiently.

The address space is divided into eight areas. The data bus width and access states can be selected

for each of these areas, and various kinds of memory can be connected fast and easily.

1

On-chip memory consists of large-capacity ROM and RAM. With regard to on-chip ROM

single power supply flash memory (F-ZTAT™

2

*

), PROM (ZTAT™

2

*

), and mask ROM versions

are available, providing a quick and flexible response to conditions from ramp-up through fullscale volume production, even for applications with frequently changing specifications.

On-chip supporting functions include a 16-bit timer pulse unit (TPU), 8-bit timers, watchdog timer

(WDT), serial communication interface (SCI), A/D converter, D/A converter, and I/O ports.

An on-chip data transfer controller (DTC) is also provided, enabling high-speed data transfer

without CPU intervention.

*

,

Use of the H8S/2345 Series enables compact, high-performance systems to be implemented easily.

This manual describes the hardware of the H8S/2345 Series. Refer to the H8S/2600 Series and

H8S/2000 Series Programming Manual for a detailed description of the instruction set.

Notes: 1. The H8S/2345, H8S/2344, H8S/2343, and H8S/2341 have on-chip ROM.

The H8S/2340 does not have on-chip ROM.

2. F-ZTAT (Flexible-ZTAT) is a trademark of Hitachi, Ltd.

ZTAT is a trademark of Hitachi, Ltd.

Page 7

Contents

Section 1 Overview........................................................................................................... 1

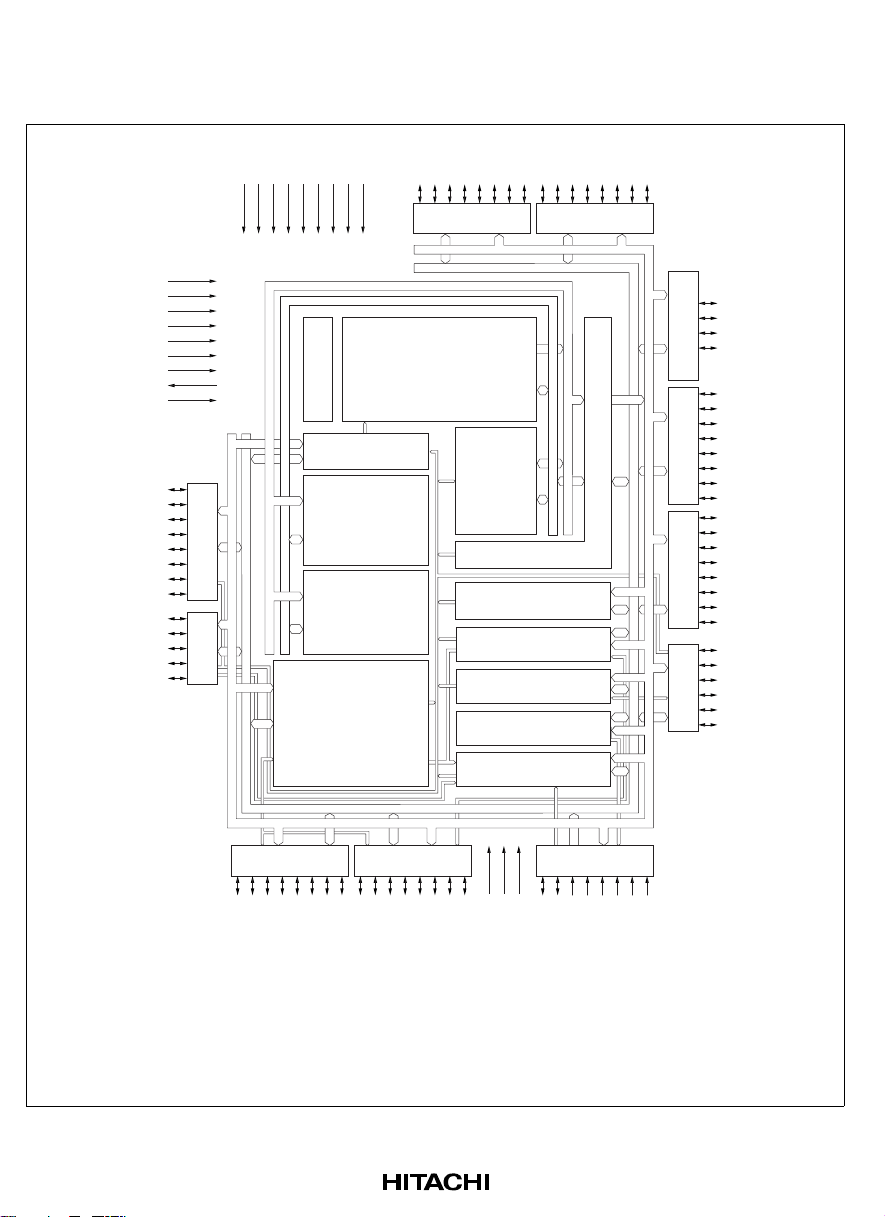

1.1 Overview............................................................................................................................ 1

1.2 Block Diagram................................................................................................................... 6

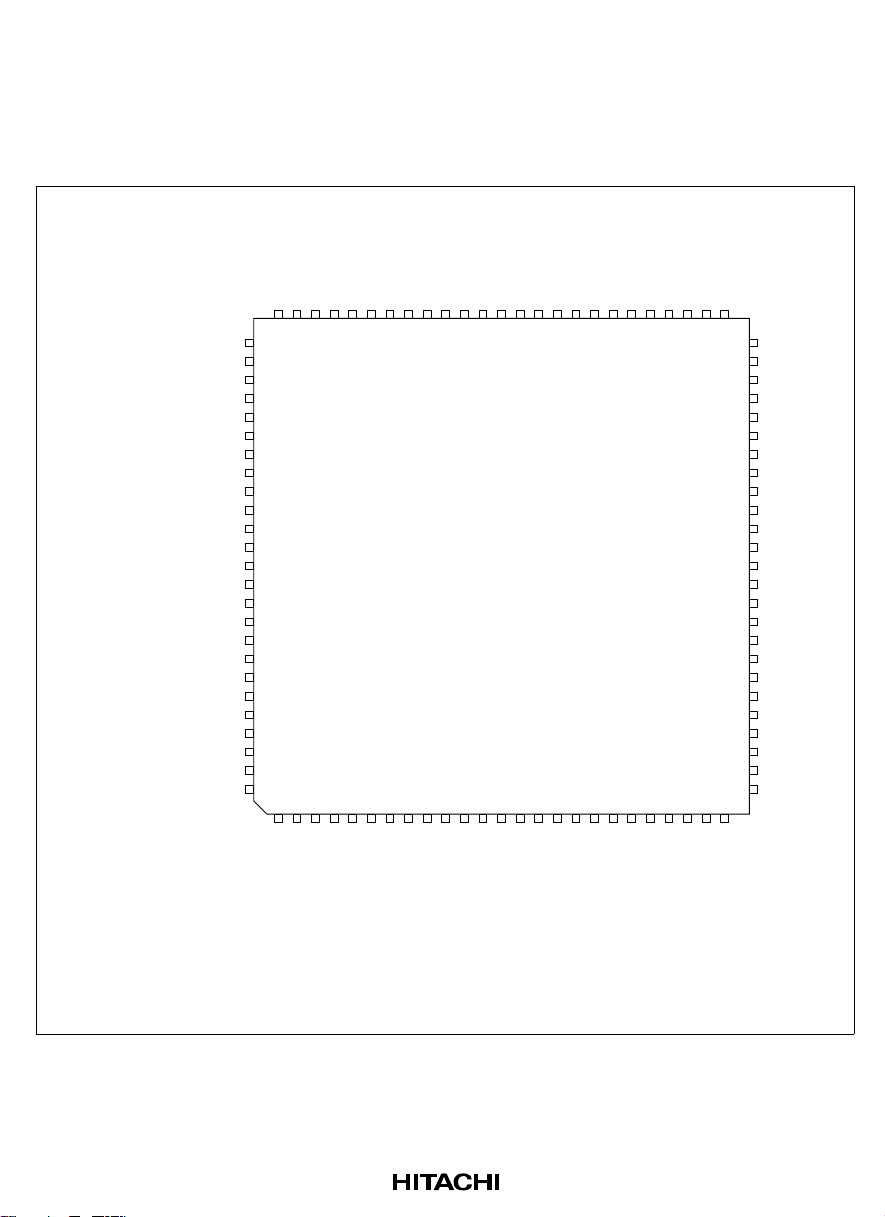

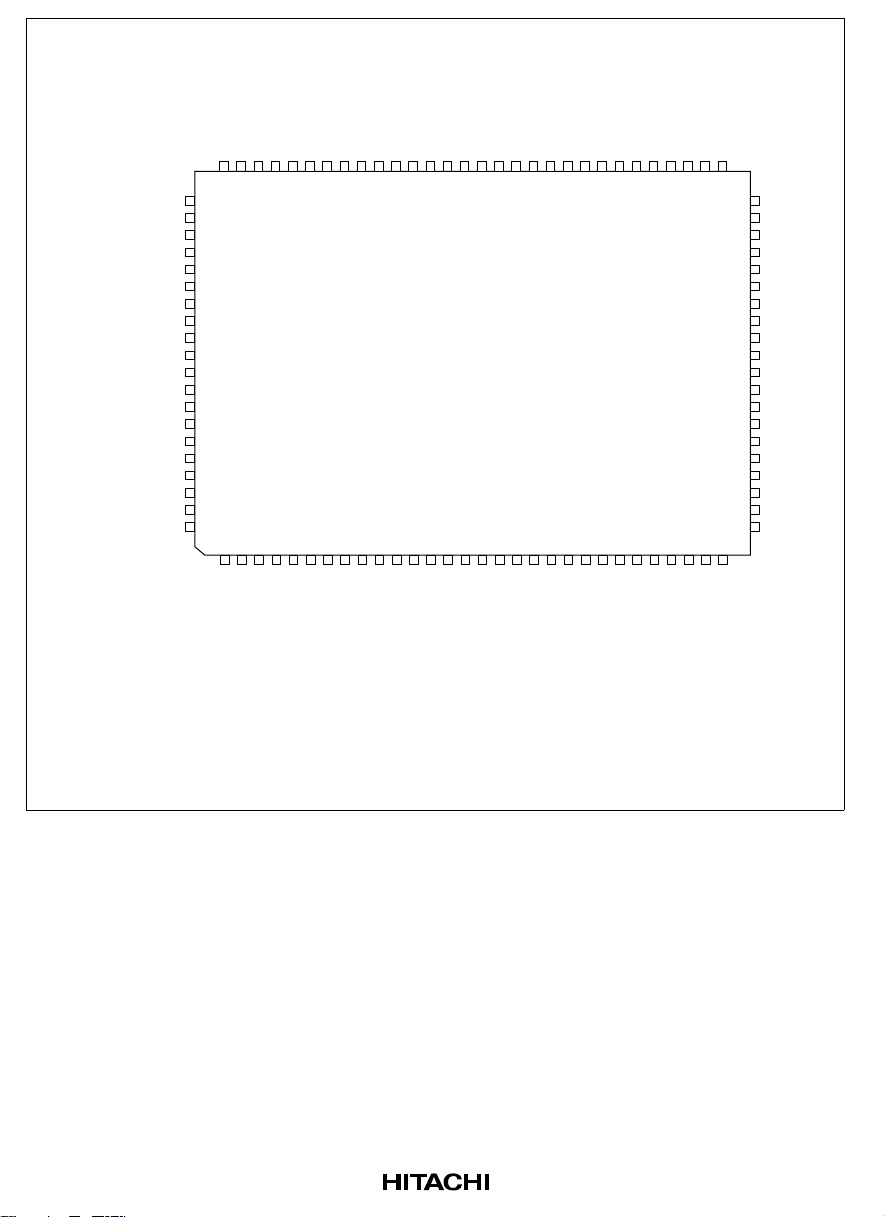

1.3 Pin Description.................................................................................................................. 7

1.3.1 Pin Arrangement .................................................................................................. 7

1.3.2 Pin Functions in Each Operating Mode................................................................ 9

1.3.3 Pin Functions........................................................................................................ 14

Section 2 CPU..................................................................................................................... 21

2.1 Overview............................................................................................................................ 21

2.1.1 Features ................................................................................................................ 21

2.1.2 Differences between H8S/2600 CPU and H8S/2000 CPU .................................. 22

2.1.3 Differences from H8/300 CPU............................................................................. 23

2.1.4 Differences from H8/300H CPU.......................................................................... 23

2.2 CPU Operating Modes ...................................................................................................... 24

2.3 Address Space.................................................................................................................... 29

2.4 Register Configuration ......................................................................................................30

2.4.1 Overview.............................................................................................................. 30

2.4.2 General Registers.................................................................................................. 31

2.4.3 Control Registers.................................................................................................. 32

2.4.4 Initial Register Values.......................................................................................... 34

2.5 Data Formats...................................................................................................................... 35

2.5.1 General Register Data Formats ............................................................................ 35

2.5.2 Memory Data Formats.......................................................................................... 37

2.6 Instruction Set.................................................................................................................... 38

2.6.1 Overview.............................................................................................................. 38

2.6.2 Instructions and Addressing Modes ..................................................................... 39

2.6.3 Table of Instructions Classified by Function........................................................ 41

2.6.4 Basic Instruction Formats..................................................................................... 51

2.7 Addressing Modes and Effective Address Calculation..................................................... 52

2.7.1 Addressing Mode.................................................................................................. 52

2.7.2 Effective Address Calculation.............................................................................. 55

2.8 Processing States ............................................................................................................... 59

2.8.1 Overview.............................................................................................................. 59

2.8.2 Reset State............................................................................................................ 60

2.8.3 Exception-Handling State .................................................................................... 61

2.8.4 Program Execution State...................................................................................... 64

2.8.5 Bus-Released State............................................................................................... 64

2.8.6 Power-Down State................................................................................................ 64

i

Page 8

2.9 Basic Timing...................................................................................................................... 65

2.9.1 Overview.............................................................................................................. 65

2.9.2 On-Chip Memory (ROM, RAM) ......................................................................... 65

2.9.3 On-Chip Supporting Module Access Timing....................................................... 67

2.9.4 External Address Space Access Timing............................................................... 68

Section 3 MCU Operating Modes................................................................................ 69

3.1 Overview............................................................................................................................ 69

3.1.1 Operating Mode Selection (F-ZTAT™ Version)................................................. 69

3.1.2 Operating Mode Selection (ZTAT, Mask ROM, and No On-Chip ROM

Versions) .............................................................................................................. 70

3.1.3 Register Configuration ......................................................................................... 72

3.2 Register Descriptions......................................................................................................... 72

3.2.1 Mode Control Register (MDCR).......................................................................... 72

3.2.2 System Control Register (SYSCR) ...................................................................... 73

3.2.3 System Control Register 2 (SYSCR2) (F-ZTAT Version Only) ......................... 74

3.3 Operating Mode Descriptions............................................................................................ 75

3.3.1 Mode 1 (ZTAT, Mask ROM, and No On-Chip ROM Versions Only)................ 75

3.3.2 Mode 2

3.3.3 Mode 3

3.3.4 Mode 4

3.3.5 Mode 5

3.3.6 Mode 6

3.3.7 Mode 7

3.3.8 Modes 8 and 9 (F-ZTAT Version Only) .............................................................. 76

3.3.9 Mode 10 (F-ZTAT Version Only)........................................................................ 77

3.3.10 Mode 11 (F-ZTAT Version Only)........................................................................ 77

3.3.11 Modes 12 and 13 (F-ZTAT Version Only) .......................................................... 77

3.3.12 Mode 14 (F-ZTAT Version Only)........................................................................ 77

3.3.13 Mode 15 (F-ZTAT Version Only)........................................................................ 77

3.4 Pin Functions in Each Operating Mode............................................................................. 78

3.5 Memory Map in Each Operating Mode............................................................................. 79

1

*

(ZTAT and Mask ROM Versions Only).............................................. 75

1

*

(ZTAT and Mask ROM Versions Only).............................................. 75

2

*

.............................................................................................................. 75

2

*

.............................................................................................................. 76

1

*

.............................................................................................................. 76

1

*

.............................................................................................................. 76

Section 4 Exception Handling........................................................................................ 91

4.1 Overview............................................................................................................................ 91

4.1.1 Exception Handling Types and Priority ............................................................... 91

4.1.2 Exception Handling Operation............................................................................. 92

4.1.3 Exception Vector Table........................................................................................ 92

4.2 Reset.................................................................................................................................. 94

4.2.1 Overview.............................................................................................................. 94

4.2.2 Reset Types .......................................................................................................... 94

4.2.3 Reset Sequence..................................................................................................... 95

4.2.4 Interrupts after Reset ............................................................................................ 96

ii

Page 9

4.2.5 State of On-Chip Supporting Modules after Reset Release ................................. 96

4.3 Traces ................................................................................................................................ 97

4.4 Interrupts............................................................................................................................ 98

4.5 Trap Instruction ................................................................................................................. 99

4.6 Stack Status after Exception Handling.............................................................................. 100

4.7 Notes on Use of the Stack.................................................................................................. 101

Section 5 Interrupt Controller........................................................................................ 103

5.1 Overview............................................................................................................................ 103

5.1.1 Features ................................................................................................................ 103

5.1.2 Block Diagram...................................................................................................... 104

5.1.3 Pin Configuration ................................................................................................. 105

5.1.4 Register Configuration ......................................................................................... 105

5.2 Register Descriptions......................................................................................................... 106

5.2.1 System Control Register (SYSCR) ..................................................................... 106

5.2.2 Interrupt Priority Registers A to K (IPRA to IPRK)............................................ 107

5.2.3 IRQ Enable Register (IER) .................................................................................. 108

5.2.4 IRQ Sense Control Registers H and L (ISCRH, ISCRL)..................................... 109

5.2.5 IRQ Status Register (ISR).................................................................................... 110

5.3 Interrupt Sources................................................................................................................ 111

5.3.1 External Interrupts................................................................................................ 111

5.3.2 Internal Interrupts................................................................................................. 112

5.3.3 Interrupt Exception Handling Vector Table......................................................... 112

5.4 Interrupt Operation............................................................................................................ 116

5.4.1 Interrupt Control Modes and Interrupt Operation................................................ 116

5.4.2 Interrupt Control Mode 0...................................................................................... 119

5.4.3 Interrupt Control Mode 2...................................................................................... 121

5.4.4 Interrupt Exception Handling Sequence .............................................................. 123

5.4.5 Interrupt Response Times..................................................................................... 125

5.5 Usage Notes....................................................................................................................... 126

5.5.1 Contention between Interrupt Generation and Disabling..................................... 126

5.5.2 Instructions that Disable Interrupts ...................................................................... 127

5.5.3 Times when Interrupts are Disabled..................................................................... 127

5.5.4 Interrupts during Execution of EEPMOV Instruction.......................................... 127

5.6 DTC Activation by Interrupt ............................................................................................. 128

5.6.1 Overview.............................................................................................................. 128

5.6.2 Block Diagram...................................................................................................... 128

5.6.3 Operation.............................................................................................................. 129

Section 6 Bus Controller.................................................................................................. 131

6.1 Overview............................................................................................................................ 131

6.1.1 Features ................................................................................................................ 131

6.1.2 Block Diagram...................................................................................................... 132

iii

Page 10

6.1.3 Pin Configuration ................................................................................................. 133

6.1.4 Register Configuration ......................................................................................... 133

6.2 Register Descriptions......................................................................................................... 134

6.2.1 Bus Width Control Register (ABWCR)............................................................... 134

6.2.2 Access State Control Register (ASTCR).............................................................. 135

6.2.3 Wait Control Registers H and L (WCRH, WCRL).............................................. 136

6.2.4 Bus Control Register H (BCRH).......................................................................... 139

6.2.5 Bus Control Register L (BCRL)........................................................................... 141

6.3 Overview of Bus Control................................................................................................... 142

6.3.1 Area Partitioning .................................................................................................. 142

6.3.2 Bus Specifications................................................................................................ 144

6.3.3 Memory Interfaces................................................................................................ 145

6.3.4 Advanced Mode.................................................................................................... 145

6.3.5 Areas in Normal Mode (ZTAT, Mask ROM, and No On-Chip ROM

Versions Only)...................................................................................................... 146

6.3.6 Chip Select Signals............................................................................................... 147

6.4 Basic Bus Interface............................................................................................................ 148

6.4.1 Overview.............................................................................................................. 148

6.4.2 Data Size and Data Alignment ............................................................................. 148

6.4.3 Valid Strobes........................................................................................................ 150

6.4.4 Basic Timing ........................................................................................................ 151

6.4.5 Wait Control......................................................................................................... 159

6.5 Burst ROM Interface ......................................................................................................... 161

6.5.1 Overview.............................................................................................................. 161

6.5.2 Basic Timing ........................................................................................................ 161

6.5.3 Wait Control......................................................................................................... 163

6.6 Idle Cycle........................................................................................................................... 164

6.6.1 Operation.............................................................................................................. 164

6.6.2 Pin States in Idle Cycle ........................................................................................ 167

6.7 Bus Release........................................................................................................................ 167

6.7.1 Overview.............................................................................................................. 167

6.7.2 Operation.............................................................................................................. 167

6.7.3 Pin States in External Bus Released State............................................................ 168

6.7.4 Transition Timing................................................................................................. 169

6.7.5 Usage Note ........................................................................................................... 170

6.8 Bus Arbitration.................................................................................................................. 170

6.8.1 Overview.............................................................................................................. 170

6.8.2 Operation.............................................................................................................. 170

6.8.3 Bus Transfer Timing ............................................................................................ 171

6.8.4 External Bus Release Usage Note........................................................................ 171

6.9 Resets and the Bus Controller............................................................................................ 171

iv

Page 11

Section 7 Data Transfer Controller .............................................................................. 173

7.1 Overview............................................................................................................................ 173

7.1.1 Features ................................................................................................................ 173

7.1.2 Block Diagram...................................................................................................... 174

7.1.3 Register Configuration ......................................................................................... 175

7.2 Register Descriptions......................................................................................................... 176

7.2.1 DTC Mode Register A (MRA)............................................................................. 176

7.2.2 DTC Mode Register B (MRB) ............................................................................. 178

7.2.3 DTC Source Address Register (SAR).................................................................. 179

7.2.4 DTC Destination Address Register (DAR).......................................................... 179

7.2.5 DTC Transfer Count Register A (CRA) .............................................................. 179

7.2.6 DTC Transfer Count Register B (CRB) ............................................................... 180

7.2.7 DTC Enable Registers (DTCER) ......................................................................... 180

7.2.8 DTC Vector Register (DTVECR)........................................................................ 181

7.2.9 Module Stop Control Register (MSTPCR) .......................................................... 182

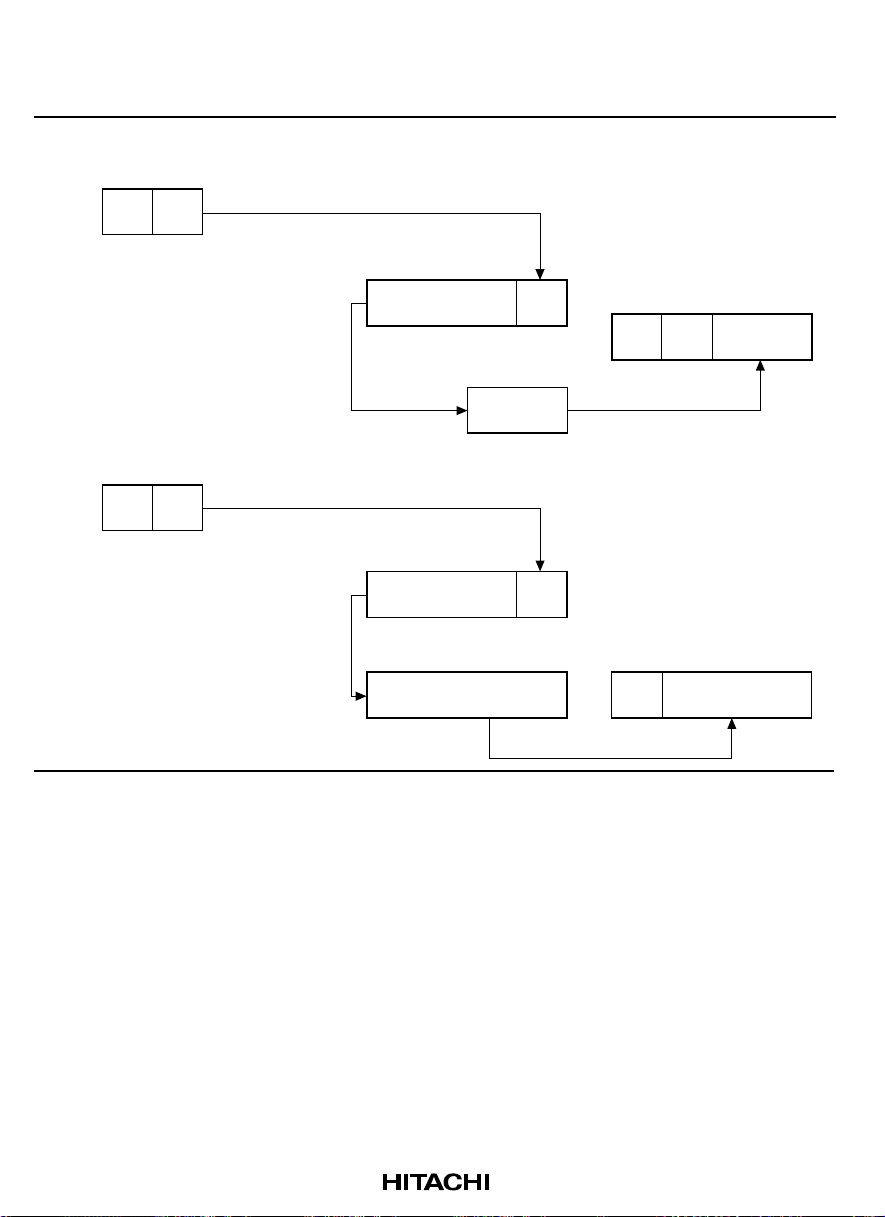

7.3 Operation ........................................................................................................................... 183

7.3.1 Overview.............................................................................................................. 183

7.3.2 Activation Sources................................................................................................ 185

7.3.3 DTC Vector Table................................................................................................ 186

7.3.4 Location of Register Information in Address Space ............................................ 189

7.3.5 Normal Mode........................................................................................................ 190

7.3.6 Repeat Mode ........................................................................................................ 191

7.3.7 Block Transfer Mode............................................................................................ 192

7.3.8 Chain Transfer...................................................................................................... 194

7.3.9 Operation Timing ................................................................................................. 195

7.3.10 Number of DTC Execution States........................................................................ 196

7.3.11 Procedures for Using DTC ................................................................................... 198

7.3.12 Examples of Use of the DTC................................................................................ 199

7.4 Interrupts............................................................................................................................ 201

7.5 Usage Notes....................................................................................................................... 201

Section 8 I/O Ports ............................................................................................................ 203

8.1 Overview............................................................................................................................ 203

8.2 Port 1.................................................................................................................................. 208

8.2.1 Overview.............................................................................................................. 208

8.2.2 Register Configuration ......................................................................................... 209

8.2.3 Pin Functions........................................................................................................ 210

8.3 Port 2.................................................................................................................................. 219

8.3.1 Overview.............................................................................................................. 219

8.3.2 Register Configuration ......................................................................................... 219

8.3.3 Pin Functions........................................................................................................ 221

8.4 Port 3.................................................................................................................................. 230

8.4.1 Overview.............................................................................................................. 230

v

Page 12

8.4.2 Register Configuration ......................................................................................... 230

8.4.3 Pin Functions........................................................................................................ 233

8.5 Port 4.................................................................................................................................. 235

8.5.1 Overview.............................................................................................................. 235

8.5.2 Register Configuration ......................................................................................... 236

8.5.3 Pin Functions........................................................................................................ 236

8.6 Port A................................................................................................................................. 237

8.6.1 Overview.............................................................................................................. 237

8.6.2 Register Configuration ......................................................................................... 238

8.6.3 Pin Functions........................................................................................................ 241

8.6.4 MOS Input Pull-Up Function............................................................................... 242

8.7 Port B................................................................................................................................. 243

8.7.1 Overview.............................................................................................................. 243

8.7.2 Register Configuration ......................................................................................... 244

8.7.3 Pin Functions........................................................................................................ 246

8.7.4 MOS Input Pull-Up Function............................................................................... 248

8.8 Port C................................................................................................................................. 249

8.8.1 Overview.............................................................................................................. 249

8.8.2 Register Configuration ......................................................................................... 250

8.8.3 Pin Functions........................................................................................................ 252

8.8.4 MOS Input Pull-Up Function............................................................................... 254

8.9 Port D................................................................................................................................. 255

8.9.1 Overview.............................................................................................................. 255

8.9.2 Register Configuration ......................................................................................... 256

8.9.3 Pin Functions........................................................................................................ 258

8.9.4 MOS Input Pull-Up Function............................................................................... 259

8.10 Port E................................................................................................................................. 260

8.10.1 Overview.............................................................................................................. 260

8.10.2 Register Configuration ......................................................................................... 261

8.10.3 Pin Functions........................................................................................................ 263

8.10.4 MOS Input Pull-Up Function ............................................................................... 264

8.11 Port F ................................................................................................................................. 265

8.11.1 Overview.............................................................................................................. 265

8.11.2 Register Configuration ......................................................................................... 266

8.11.3 Pin Functions........................................................................................................ 269

8.12 Port G................................................................................................................................. 271

8.12.1 Overview.............................................................................................................. 271

8.12.2 Register Configuration ......................................................................................... 272

8.12.3 Pin Functions........................................................................................................ 275

Section 9 16-Bit Timer Pulse Unit (TPU).................................................................. 277

9.1 Overview............................................................................................................................ 277

9.1.1 Features ................................................................................................................ 277

vi

Page 13

9.1.2 Block Diagram...................................................................................................... 281

9.1.3 Pin Configuration ................................................................................................. 282

9.1.4 Register Configuration ......................................................................................... 284

9.2 Register Descriptions......................................................................................................... 286

9.2.1 Timer Control Register (TCR) ............................................................................. 286

9.2.2 Timer Mode Register (TMDR) ............................................................................ 291

9.2.3 Timer I/O Control Register (TIOR) ..................................................................... 293

9.2.4 Timer Interrupt Enable Register (TIER) .............................................................. 310

9.2.5 Timer Status Register (TSR)................................................................................ 313

9.2.6 Timer Counter (TCNT) ........................................................................................ 316

9.2.7 Timer General Register (TGR) ............................................................................ 317

9.2.8 Timer Start Register (TSTR)................................................................................ 318

9.2.9 Timer Synchro Register (TSYR).......................................................................... 319

9.2.10 Module Stop Control Register (MSTPCR) .......................................................... 320

9.3 Interface to Bus Master...................................................................................................... 321

9.3.1 16-Bit Registers.................................................................................................... 321

9.3.2 8-Bit Registers...................................................................................................... 321

9.4 Operation ........................................................................................................................... 323

9.4.1 Overview.............................................................................................................. 323

9.4.2 Basic Functions .................................................................................................... 324

9.4.3 Synchronous Operation........................................................................................ 330

9.4.4 Buffer Operation .................................................................................................. 332

9.4.5 Cascaded Operation.............................................................................................. 336

9.4.6 PWM Modes ........................................................................................................ 338

9.4.7 Phase Counting Mode .......................................................................................... 343

9.5 Interrupts............................................................................................................................ 349

9.5.1 Interrupt Sources and Priorities............................................................................ 349

9.5.2 DTC Activation.................................................................................................... 351

9.5.3 A/D Converter Activation .................................................................................... 351

9.6 Operation Timing .............................................................................................................. 352

9.6.1 Input/Output Timing ............................................................................................ 352

9.6.2 Interrupt Signal Timing........................................................................................ 356

9.7 Usage Notes....................................................................................................................... 360

Section 10 8-Bit Timers ..................................................................................................... 371

10.1 Overview............................................................................................................................ 371

10.1.1 Features ................................................................................................................ 371

10.1.2 Block Diagram...................................................................................................... 372

10.1.3 Pin Configuration ................................................................................................. 373

10.1.4 Register Configuration ......................................................................................... 373

10.2 Register Descriptions......................................................................................................... 374

10.2.1 Timer Counters 0 and 1 (TCNT0, TCNT1).......................................................... 374

10.2.2 Time Constant Registers A0 and A1 (TCORA0, TCORA1) ............................... 374

vii

Page 14

10.2.3 Time Constant Registers B0 and B1 (TCORB0, TCORB1)................................ 375

10.2.4 Time Control Registers 0 and 1 (TCR0, TCR1) .................................................. 375

10.2.5 Timer Control/Status Registers 0 and 1 (TCSR0, TCSR1).................................. 377

10.2.6 Module Stop Control Register (MSTPCR) .......................................................... 380

10.3 Operation ........................................................................................................................... 381

10.3.1 TCNT Incrementation Timing.............................................................................. 381

10.3.2 Compare Match Timing ....................................................................................... 382

10.3.3 Timing of External RESET on TCNT.................................................................. 384

10.3.4 Timing of Overflow Flag (OVF) Setting.............................................................. 384

10.3.5 Operation with Cascaded Connection .................................................................. 385

10.4 Interrupts............................................................................................................................ 386

10.4.1 Interrupt Sources and DTC Activation................................................................. 386

10.4.2 A/D Converter Activation .................................................................................... 386

10.5 Sample Application ........................................................................................................... 387

10.6 Usage Notes....................................................................................................................... 388

10.6.1 Contention between TCNT Write and Clear........................................................ 388

10.6.2 Contention between TCNT Write and Increment ................................................ 389

10.6.3 Contention between TCOR Write and Compare Match ...................................... 390

10.6.4 Contention between Compare Matches A and B ................................................. 391

10.6.5 Switching of Internal Clocks and TCNT Operation............................................. 391

10.6.6 Usage Note ........................................................................................................... 393

Section 11 Watchdog Timer ............................................................................................. 395

11.1 Overview............................................................................................................................ 395

11.1.1 Features ................................................................................................................ 395

11.1.2 Block Diagram...................................................................................................... 396

11.1.3 Pin Configuration ................................................................................................. 397

11.1.4 Register Configuration ......................................................................................... 397

11.2 Register Descriptions......................................................................................................... 398

11.2.1 Timer Counter (TCNT) ........................................................................................ 398

11.2.2 Timer Control/Status Register (TCSR)................................................................ 398

11.2.3 Reset Control/Status Register (RSTCSR)............................................................ 400

11.2.4 Notes on Register Access ..................................................................................... 402

11.3 Operation ........................................................................................................................... 404

11.3.1 Watchdog Timer Operation.................................................................................. 404

11.3.2 Interval Timer Operation...................................................................................... 406

11.3.3 Timing of Setting Overflow Flag (OVF).............................................................. 406

11.3.4 Timing of Setting of Watchdog Timer Overflow Flag (WOVF) ......................... 407

11.4 Interrupts............................................................................................................................ 408

11.5 Usage Notes....................................................................................................................... 408

11.5.1 Contention between Timer Counter (TCNT) Write and Increment ..................... 408

11.5.2 Changing Value of CKS2 to CKS0...................................................................... 408

11.5.3 Switching between Watchdog Timer Mode and Interval Timer Mode................ 409

viii

Page 15

11.5.4 System Reset by WDTOVF Signal...................................................................... 409

11.5.5 Internal Reset in Watchdog Timer Mode ............................................................. 409

Section 12 Serial Communication Interface (SCI) .................................................... 411

12.1 Overview............................................................................................................................ 411

12.1.1 Features ................................................................................................................ 411

12.1.2 Block Diagram...................................................................................................... 413

12.1.3 Pin Configuration ................................................................................................. 414

12.1.4 Register Configuration ......................................................................................... 415

12.2 Register Descriptions......................................................................................................... 416

12.2.1 Receive Shift Register (RSR)............................................................................... 416

12.2.2 Receive Data Register (RDR) .............................................................................. 416

12.2.3 Transmit Shift Register (TSR).............................................................................. 417

12.2.4 Transmit Data Register (TDR) ............................................................................. 417

12.2.5 Serial Mode Register (SMR)................................................................................ 418

12.2.6 Serial Control Register (SCR).............................................................................. 421

12.2.7 Serial Status Register (SSR)................................................................................. 425

12.2.8 Bit Rate Register (BRR)....................................................................................... 428

12.2.9 Smart Card Mode Register (SCMR) .................................................................... 437

12.2.10 Module Stop Control Register (MSTPCR) .......................................................... 438

12.3 Operation ........................................................................................................................... 439

12.3.1 Overview.............................................................................................................. 439

12.3.2 Operation in Asynchronous Mode........................................................................ 441

12.3.3 Multiprocessor Communication Function............................................................ 452

12.3.4 Operation in Clocked Synchronous Mode ........................................................... 460

12.4 SCI Interrupts .................................................................................................................... 468

12.5 Usage Notes....................................................................................................................... 469

Section 13 Smart Card Interface...................................................................................... 473

13.1 Overview............................................................................................................................ 473

13.1.1 Features ................................................................................................................ 473

13.1.2 Block Diagram...................................................................................................... 474

13.1.3 Pin Configuration ................................................................................................. 475

13.1.4 Register Configuration ......................................................................................... 476

13.2 Register Descriptions......................................................................................................... 477

13.2.1 Smart Card Mode Register (SCMR) .................................................................... 477

13.2.2 Serial Status Register (SSR)................................................................................. 478

13.2.3 Serial Mode Register (SMR)................................................................................ 480

13.2.4 Serial Control Register (SCR).............................................................................. 481

13.3 Operation ........................................................................................................................... 482

13.3.1 Overview.............................................................................................................. 482

13.3.2 Pin Connections.................................................................................................... 482

13.3.3 Data Format.......................................................................................................... 484

ix

Page 16

13.3.4 Register Settings................................................................................................... 486

13.3.5 Clock .................................................................................................................... 488

13.3.6 Data Transfer Operations ..................................................................................... 490

13.3.7 Operation in GSM Mode...................................................................................... 497

13.4 Usage Note ........................................................................................................................ 498

Section 14 A/D Converter ................................................................................................. 503

14.1 Overview............................................................................................................................ 503

14.1.1 Features ................................................................................................................ 503

14.1.2 Block Diagram...................................................................................................... 504

14.1.3 Pin Configuration ................................................................................................. 505

14.1.4 Register Configuration ......................................................................................... 506

14.2 Register Descriptions......................................................................................................... 507

14.2.1 A/D Data Registers A to D (ADDRA to ADDRD).............................................. 507

14.2.2 A/D Control/Status Register (ADCSR)................................................................ 508

14.2.3 A/D Control Register (ADCR)............................................................................. 510

14.2.4 Module Stop Control Register (MSTPCR) .......................................................... 511

14.3 Interface to Bus Master...................................................................................................... 512

14.4 Operation ........................................................................................................................... 513

14.4.1 Single Mode (SCAN = 0)..................................................................................... 513

14.4.2 Scan Mode (SCAN = 1) ....................................................................................... 515

14.4.3 Input Sampling and A/D Conversion Time.......................................................... 517

14.4.4 External Trigger Input Timing ............................................................................. 518

14.5 Interrupts............................................................................................................................ 519

14.6 Usage Notes....................................................................................................................... 519

Section 15 D/A Converter ................................................................................................. 525

15.1 Overview............................................................................................................................ 525

15.1.1 Features ................................................................................................................ 525

15.1.2 Block Diagram...................................................................................................... 526

15.1.3 Pin Configuration ................................................................................................. 527

15.1.4 Register Configuration ......................................................................................... 527

15.2 Register Descriptions......................................................................................................... 528

15.2.1 D/A Data Registers 0 and 1 (DADR0, DADR1).................................................. 528

15.2.2 D/A Control Register (DACR)............................................................................. 528

15.2.3 Module Stop Control Register (MSTPCR) .......................................................... 530

15.3 Operation ........................................................................................................................... 531

15.4 Usage Notes....................................................................................................................... 532

Section 16 RAM ................................................................................................................... 533

16.1 Overview............................................................................................................................ 533

16.1.1 Block Diagram...................................................................................................... 534

16.1.2 Register Configuration ......................................................................................... 534

x

Page 17

16.2 Register Descriptions......................................................................................................... 535

16.2.1 System Control Register (SYSCR) ...................................................................... 535

16.3 Operation ........................................................................................................................... 535

16.4 Usage Note ........................................................................................................................ 535

Section 17 ROM................................................................................................................... 537

17.1 Overview.............................................................................................................................. 537

17.1.1 Block Diagram........................................................................................................ 537

17.1.2 Register Configuration............................................................................................ 538

17.2 Register Descriptions............................................................................................................ 538

17.2.1 Mode Control Register (MDCR)............................................................................ 538

17.2.2 Bus Control Register L (BCRL)............................................................................. 539

17.3 Operation.............................................................................................................................. 539

17.4 PROM Mode ........................................................................................................................ 542

17.4.1 PROM Mode Setting.............................................................................................. 542

17.4.2 Socket Adapter and Memory Map.......................................................................... 542

17.5 Programming........................................................................................................................ 545

17.5.1 Overview ................................................................................................................ 545

17.5.2 Programming and Verification............................................................................... 545

17.5.3 Programming Precautions ...................................................................................... 549

17.5.4 Reliability of Programmed Data............................................................................. 550

17.6 Overview of Flash Memory.................................................................................................. 551

17.6.1 Features................................................................................................................... 551

17.6.2 Block Diagram........................................................................................................ 552

17.6.3 Flash Memory Operating Modes............................................................................ 553

17.6.4 Pin Configuration.................................................................................................... 558

17.6.5 Register Configuration............................................................................................ 559

17.7 Register Descriptions............................................................................................................ 560

17.7.1 Flash Memory Control Register 1 (FLMCR1)....................................................... 560

17.7.2 Flash Memory Control Register 2 (FLMCR2)....................................................... 563

17.7.3 Erase Block Registers 1 and 2 (EBR1, EBR2)....................................................... 564

17.7.4 System Control Register 2 (SYSCR2).................................................................... 565

17.7.5 RAM Emulation Register (RAMER) ..................................................................... 566

17.8 On-Board Programming Modes........................................................................................... 568

17.8.1 Boot Mode.............................................................................................................. 569

17.8.2 User Program Mode................................................................................................ 573

17.9 Programming/Erasing Flash Memory.................................................................................. 575

17.9.1 Program Mode — Preliminary —.......................................................................... 576

17.9.2 Program-Verify Mode — Preliminary — .............................................................. 577

17.9.3 Erase Mode — Preliminary —............................................................................... 579

17.9.4 Erase-Verify Mode — Preliminary — ................................................................... 579

17.10 Flash Memory Protection................................................................................................... 581

17.10.1 Hardware Protection............................................................................................. 581

xi

Page 18

17.10.2 Software Protection.............................................................................................. 581

17.10.3 Error Protection.................................................................................................... 582

17.11 Flash Memory Emulation in RAM..................................................................................... 585

17.11.1 Emulation in RAM ............................................................................................... 585

17.11.2 RAM Overlap ....................................................................................................... 586

17.12 Interrupt Handling when Programming/Erasing Flash Memory........................................ 587

17.13 Flash Memory Writer Mode............................................................................................... 588

17.13.1 Writer Mode Setting............................................................................................. 588

17.13.2 Socket Adapters and Memory Map...................................................................... 589

17.13.3 Writer Mode Operation ........................................................................................ 590

17.13.4 Memory Read Mode............................................................................................. 592

17.13.5 Auto-Program Mode............................................................................................. 596

17.13.6 Auto-Erase Mode.................................................................................................. 598

17.13.7 Status Read Mode................................................................................................. 599

17.13.8 Status Polling........................................................................................................ 601

17.13.9 Writer Mode Transition Time .............................................................................. 602

17.13.10 Notes On Memory Programming ....................................................................... 602

17.14 Flash Memory Programming and Erasing Precautions...................................................... 603

Section 18 Clock Pulse Generator .................................................................................. 609

18.1 Overview............................................................................................................................ 609

18.1.1 Block Diagram...................................................................................................... 609

18.1.2 Register Configuration ......................................................................................... 609

18.2 Register Descriptions......................................................................................................... 610

18.2.1 System Clock Control Register (SCKCR)............................................................ 610

18.3 Oscillator............................................................................................................................ 611

18.3.1 Connecting a Crystal Resonator ........................................................................... 611

18.3.2 External Clock Input ............................................................................................ 613

18.4 Duty Adjustment Circuit.................................................................................................... 615

18.5 Medium-Speed Clock Divider........................................................................................... 615

18.6 Bus Master Clock Selection Circuit .................................................................................. 615

Section 19 Power-Down Modes...................................................................................... 617

19.1 Overview.............................................................................................................................. 617

19.1.1 Register Configuration............................................................................................ 618

19.2 Register Descriptions............................................................................................................ 619

19.2.1 Standby Control Register (SBYCR)....................................................................... 619

19.2.2 System Clock Control Register (SCKCR).............................................................. 620

19.2.3 Module Stop Control Register (MSTPCR) ............................................................ 621

19.3 Medium-Speed Mode........................................................................................................... 622

19.4 Sleep Mode........................................................................................................................... 623

19.5 Module Stop Mode............................................................................................................... 623

19.5.1 Module Stop Mode................................................................................................. 623

xii

Page 19

19.5.2 Usage Notes............................................................................................................ 624

19.6 Software Standby Mode....................................................................................................... 625

19.6.1 Software Standby Mode ......................................................................................... 625

19.6.2 Clearing Software Standby Mode .......................................................................... 625

19.6.3 Setting Oscillation Stabilization Time after Clearing Software Standby Mode..... 626

19.6.4 Software Standby Mode Application Example...................................................... 626

19.6.5 Usage Notes............................................................................................................ 627

19.7 Hardware Standby Mode...................................................................................................... 628

19.7.1 Hardware Standby Mode........................................................................................ 628

19.7.2 Hardware Standby Mode Timing ........................................................................... 628

19.8 ø Clock Output Disabling Function...................................................................................... 629

Section 20 Electrical Characteristics.............................................................................. 631

20.1 Electrical Characteristics of F-ZTAT Version .................................................................. 631

20.1.1 Absolute Maximum Ratings................................................................................. 631

20.1.2 DC Characteristics................................................................................................ 632

20.1.3 AC Characteristics................................................................................................ 639

20.1.4 A/D Conversion Characteristics........................................................................... 646

20.1.5 D/A Conversion Characteristics........................................................................... 647

20.1.6 Flash Memory Characteristics.............................................................................. 648

20.2 Electrical Characteristics of ZTAT, Mask ROM, and No On-chip ROM Versions.......... 650

20.2.1 Absolute Maximum Ratings................................................................................. 650

20.2.2 DC Characteristics................................................................................................ 651

20.2.3 AC Characteristics................................................................................................ 656

20.2.4 A/D Conversion Characteristics........................................................................... 663

20.2.5 D/A Conversion Characteristics........................................................................... 664

20.3 Operation Timing .............................................................................................................. 665

20.3.1 Clock Timing........................................................................................................ 665

20.3.2 Control Signal Timing.......................................................................................... 666

20.3.3 Bus Timing........................................................................................................... 667

20.3.4 Timing for On-Chip Supporting Modules............................................................ 673

20.4 Usage Note ........................................................................................................................ 676

Appendix A Instruction Set.............................................................................................. 677

A.1 Instruction List................................................................................................................... 677

A.2 Instruction Codes............................................................................................................... 701

A.3 Operation Code Map.......................................................................................................... 715

A.4 Number of States Required for Instruction Execution...................................................... 719

A.5 Bus States During Instruction Execution........................................................................... 733

A.6 Condition Code Modification............................................................................................ 747

xiii

Page 20

Appendix B Internal I/O Register.................................................................................. 753

B.1 Addresses........................................................................................................................... 753

B.2 Functions............................................................................................................................ 760

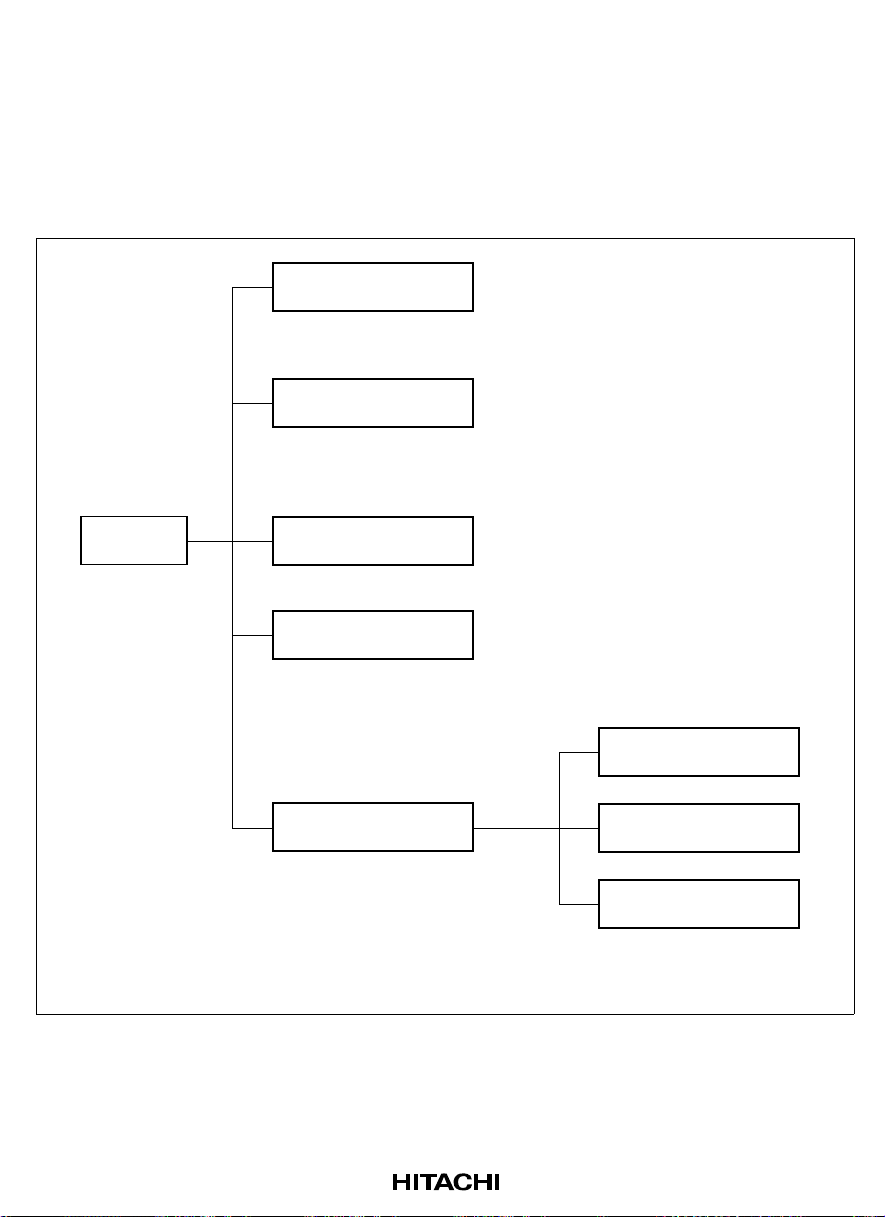

Appendix C I/O Port Block Diagrams.......................................................................... 859