Page 1

September 2006 (ver v)

HITACHI

PROJECTION

TELEVISION

2004 MODEL RELEASE

DIGITAL HD READY PTV

Model Chassis Remote P/N

57S715

51S715

65F710

57F710

51F710

51F510

57F510

DP-47 CLU-3842WL HL02062

DP-47 CLU-3842WL HL02062

DP-45 CLU-4341UG2 HL02071

DP-45 CLU-4341UG2 HL02071

DP-45 CLU-4341UG2 HL02071

*DP-43 CLU-4341UG2 HL02071

*DP-43 CLU-4341UG2 HL02071

* Does Not Have a

Digital Module. No

ATSC Tuner.

Service Web Site

http://www.hitachiserviceusa.com

CONTENTS... 2004 DP-4X Chassis Projection Television Information

Materials Prepared by… Alvie Rodgers C.E.T. (Chamblee, GA.)

Page 2

DP-4X BLANK PAGE (NOTES)

BLANK PAGE

Page 3

September 2006 (ver v)

TOPICS PAGE

SECTION (1) POWER SUPPLY DIAGRAMS:

DP-4X TABLE OF CONTENTS

• Generic Power Supply Circuits Explained ---------------------------------------------------------- 01-01

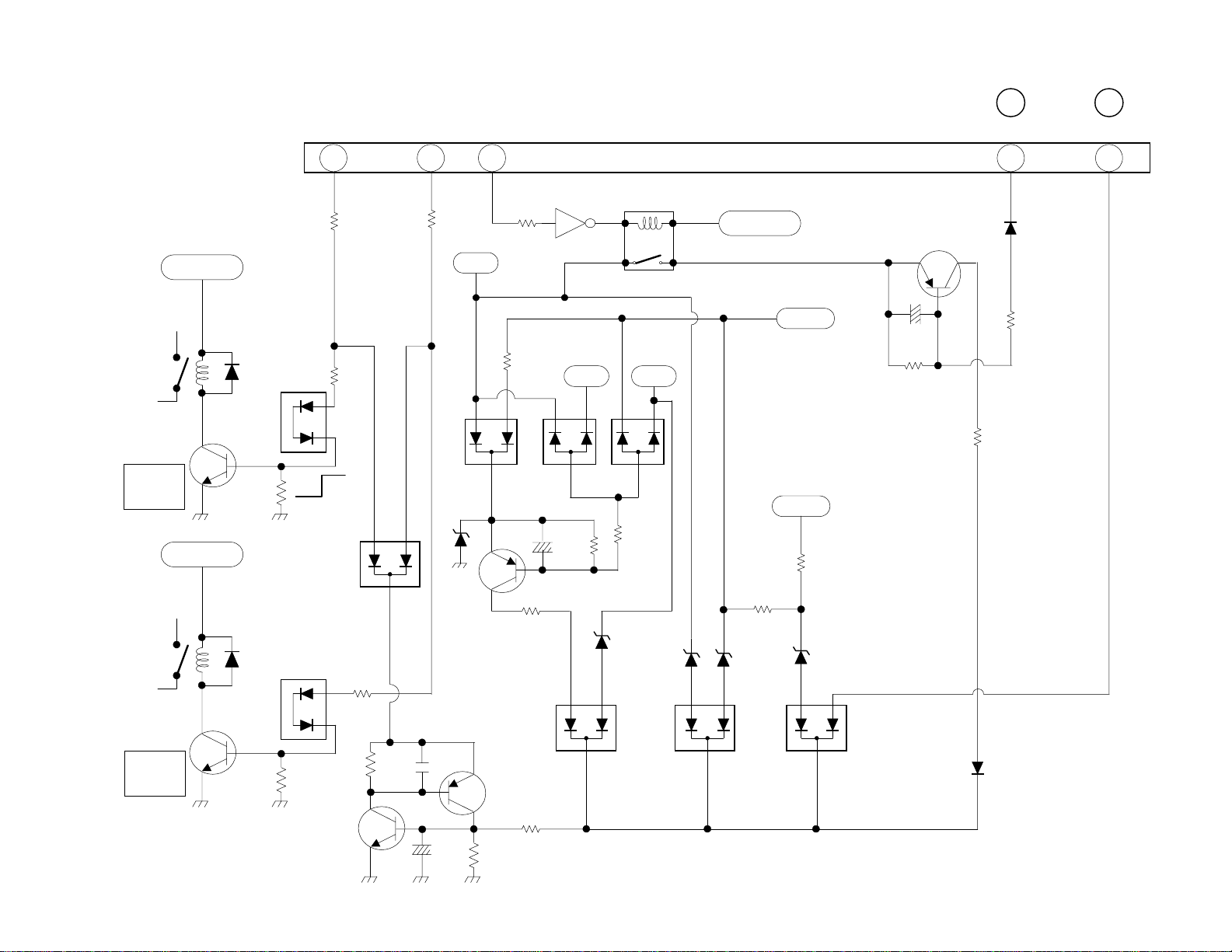

• Deflection Side Shutdown Circuit Diagram Explained ------------------------------------------- 01-04

• Deflection Side Shutdown Circuit Diagram Explained ------------------------------------------- 01-05

• PROT_OVP and PROT_OCP Shut Down Circuit Diagram Explanation -------------------- 01-06

• PROT_OVP and PROT_OCP Shut Down Circuit Diagram ----------------------------------- 01-07

• Deflection Power Supply Shutdown Output Circuit Diagram Explained -------------------- 01-08

• Deflection Power Supply Shutdown Output Circuit Diagram --------------------------------- 01-09

• Signal Power Supply Shutdown Circuit Diagram Explained ----------------------------------- 01-10

• Signal Power Supply Shutdown Circuit Diagram ------------------------------------------------ 01-12

• Stand By +5V Power Supply Generation Circuit Diagram and Explanation ----------------- 01-13

• Power Supply Relay Control Circuit Diagram Explained --------------------------------------- 01-14

• Power Supply Relay Control Circuit Diagram ---------------------------------------------------- 01-15

• SW +115V Hi Voltage Regulation Circuit Diagram Explained --------------------------------- 01-17

• SW +115V Hi Voltage Regulation Circuit Diagram ---------------------------------------------- 01-18

• IP01 Voltages and Waveforms ---------------------------------------------------------------------- 01-18A

• 5.7V Volt Regulation Circuit Diagram Explained ------------------------------------------------- 01-19

• 5.7V Volt Regulation Circuit Diagram -------------------------------------------------------------- 01-20

• LEDs (Visual Trouble Shooting) Deflection Power Supply Circuit Diagram Explained ----- 01-21

• LEDs (Visual Trouble Shooting) Deflection Power Supply Circuit Diagram ------------------ 01-22

SECTION (2) MICROPROCESSOR INFORMATION:

• Microprocessor DATA COMMUNICATION Explanation ------------------------------------- 02-01

• Microprocessor DATA COMMUNICATION Circuit Diagram ------------------------------------ 02-05

• Audio Video Mute Circuit Diagram Explanation -------------------------------------------------- 02-06

• Audio Video Mute Circuit Diagram ------------------------------------------------------------------ 02-09

• Microprocessor NTSC Sync Input Circuit Diagram Explained --------------------------------- 02-10

• Microprocessor NTSC Sync Input Circuit Diagram Circuit Diagram ------------------------------ 02-11

SECTION (3) VIDEO CIRCUIT INFORMATION:

• Video Signal Selection Circuit Diagram Explained ------------------------------------------ ----- 03-01

• Video Signal Selection Circuit Diagram ------------------------------------------------------------ 03-03

• Composite Video Signal Path 1H NTSC Circuit Diagram Explanation ----------------------- 03-04

• Composite Video Signal Path 1H NTSC Circuit Diagram ------ ----------------------- --------- 03-06

• RGB Processor (Rainforest) Circuit Explanation ------------------------------------------------- 03-07

• RGB Processor (Rainforest) Circuit Explanation ------------------------------------------------- 03-09

• ABL Circuit Diagram Explanation ------------------------------------ ----------------------------- --- 03-10

• ABL Circuit Di agram ----------------------------------------------------------------------------------- 03-11

• H and V Sync to the Rainforest IC Circuit Diagram Explanation ----------------------------- 03-12

• H and V Sync to the Rainforest IC Circuit Diagram --------------------------------------------- 03-14

Materials prepared by

Alvie Rodgers C.E.T.

Continued on Next Page

Table of Contents Page 1 of 2

Page 4

September 2006 (ver v)

TOPICS PAGE

SECTION (4) AUDIO CIRCUIT INFORMATION:

DP-4X TABLE OF CONTENTS

Materials prepared by

Alvie Rodgers C.E.T.

• Audio Signal Selection Circuit Diagram Explanation --------------------------------------------- 04-01

• Audio Signal Selection Circuit Diagram Explanation --------------------------------------------- 04-03

SECTION (5) DEFLECTION CIRCUIT:

• Horizontal Drive Circuit Diagram Explanation ----------------------- ----------------------------- 05-01

• Horizontal Drive Circuit Diagram ------------------------------------- ------------ --------- --------- 05-03

• IH01 Horizontal Drive IC Voltages and Waveforms (Also, Not Running Info.) ------------- 05-04

• Sweep Loss Detection Circuit Diagra m Explanation ----------------------------------------------- 05-05

• Sweep Loss Detection Circuit Diagram --------------------------------------------------------------- 05-06

• Vertical Output Circuit Diagram Explanation ----------------------------------------------------- 05-07

• Vertical Output Circuit Diagram --------------------------------------------------------------------- 05-08

• Side Pincushion Circuit Diagram --------------------------------------- --- --------------------------- 05-09

• Side Pincushion Circuit Diagram --------------------------------------- --- --------------------------- 05-10

SECTION (6) DIGITAL CONVERGENCE CIRCUIT INFORMATION:

• Digital Convergence Interconnect Circuit Diagram Explanation ------------------------------- 06-01

• Digital Convergence Interconnect Circuit Diagram ---------------------------------------------- 06-06

• CLU-3842WL Re mote Control ------------------------------------------------ ----------------------- 06-07

• CLU-4341UG2 Remote Control ------------------------- --------------------------------------------- 06-08

• Adjustment Marker On/Off Explanation ----------------------------------------------------------- 06-09

• Adjustment Marker Movement by CH UP and CH DOWN Explanation --------------------- 06-10

• Convergence Adjustment Using and Outside Signal Explanation ------------------------------ 06-12

• Sensor Error Codes Explanation and Chart ----------------------------- --------------------------- 06-13

SECTION (7) CHASSIS PICTURES:

• Main Chassis Picture ----------------------- ------------------------------------------- ---------------- 07-01

• Signal PWB Picture ------------------------------------------------------------------------------------ 07-01

• Deflection PWB Picture ------------------------------------------------------------------------------- 07-02

• Convergence Output PWB Picture ----------------------------------------------------------------- 07-02

• Digital Convergence Unit (DCU) Picture --------------------------------------------------------- 07-03

• Sub (Signal) Power Supply PWB Picture ------------------------------ ------------- -------------- 07-03

• Tuner PWB Picture ------------------------------------------------------------------------------------ 07-04

• HDMI to DVI Adaptor Cable Comparison Picture --------------------------------------------- 07-04

• DP-43 Rear Panel (Rear Inputs) Picture ---------------------------- ------------------------------ 07-05

• DP-45 Rear Panel (Rear Inputs) Picture ---------------------------- ------------------------------ 07-06

• DP-47 Rear Panel (Rear Inputs) Picture ---------------------------- ------------------------------ 07-07

SECTION (8) SERVICE ADJUSTMENTS:

• See the index for this section after the Section 8 Divider. -------------------------------------- 08-00

SECTION (9) THINGS YOU SHOULD KNOW: Must be downloaded separately.

• See the index for this section after the Section 9 Divider. -------------------------------------- 09-00

SECTION (10) SERVICE POLICY:

Service Policy and PWB Part Numbers. --------------- ------ ------- ----- ------ ------- ----- ------ ------- ----- 10-01

Table of Contents Page 2 of 2

Page 5

POWER SUPPLY

INFORMATION

DP-4X

CHASSIS INFORMATION

SECTION 1

Page 6

DP-4X BLANK PAGE “NOTES”

BLANK PAGE

Page 7

DP-4X GENERIC POWER SUPPLY SHUTDOWN EXPLANATION

GENERIC SHUTDOWN CIRCUITS EXPLAINED:

The following circuits are commonly used in Hitachi product and relate to the drawings for Shutdown:

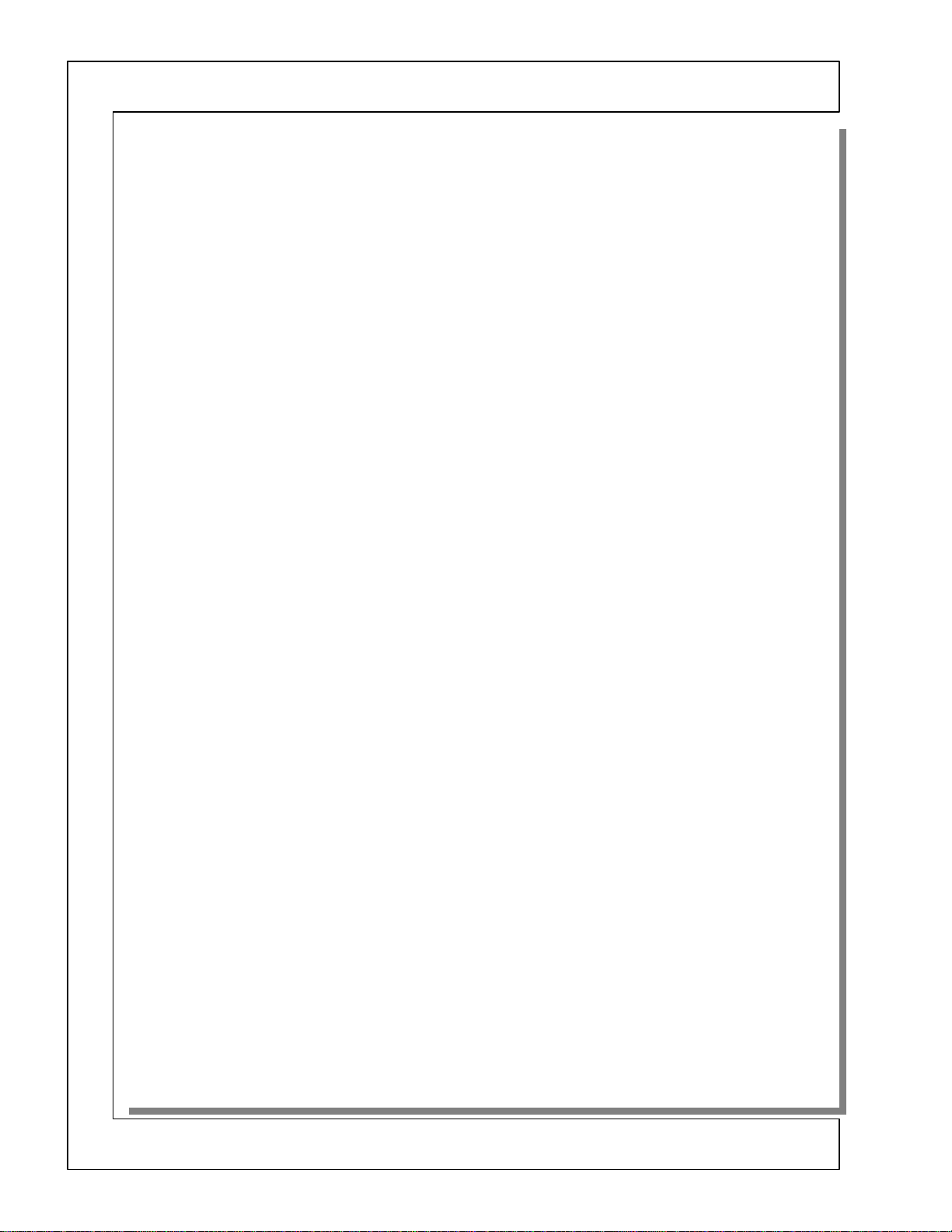

SW +115V EXCESSIVE CURRENT DETECTION

(See Figure 1)

One very common circuit used in many Hitachi television products is the B+

circuit. In this circuit is a low ohm resistor

ing

in series with the SW +115V. The value of this resistor is

0.39 ohm

creases, the voltage drop across the resistor increases. If the voltage drop is sufficient to reduce the

voltage on the base of

duct, producing a Shutdown signal that is directed to

the appropriate circuits indicated on the drawing for

Deflection Power Supply Shutdown Output Circuit,

OCP & OVP.

NEGATIVE VOLTAGE LOSS DETECTION

(See Figure 2)

The purpose of the Negative Voltage Loss detection circuit is to

compare the negative voltage with its counter part positive voltage. If at any time, the negative voltage drops or disappears, the

circuit will produce a Shutdown signal.

In Figure 2, there are two resistors. One to the positive voltage

+5V and one to the negative voltage –5V. At their tie point,

(neutral point), the voltage is effectually zero (0) volts, actually

about 1 Volt negative. If however, the negative voltage is lost,

the neutral point will go positive. This in turn will create a Shutdown Signal through

dicated on the drawing for Deflection Power Supply Shutdown

Output Circuit, OCP & OVP.

VOLTAGE TOO HIGH DETECTION

(See Figure 3)

Another circuit used is the

circuit. In the example shown in Figure 3, the

tion

zener diode

and

RP38

the voltage at the divider center point will rise as well

and trigger or fire the zener diode which produces a

Shutdown signal through

priate circuit indicated on the drawing for Deflection

Power Supply Shutdown Output Circuit, OCP & OVP.

. When the current demand in-

DP39

. If the voltage source rises too high,

RP39

Excessive Current Sens-

RP34

, the transistor will con-

QP05

and on to the appropriate circuit in-

DK18

Voltage Too High Detec-

is connected to a voltage divider

and on to the appro-

DP38

SW+115V

CP46

Voltage Loss

RK23

2.7K

DP39

DP38

RP34

Current Sensor

QP05

Figure 1

Shutdown Signal

Negative

Detector

SW +5V

RP38

RP39

Figure 3

0.39

RP35

Base

Bias

RP36

Shutdown Signal

DK18

RK22

1.8K

SW -5V

Figure 2

SW +115V

Voltage Too

High Detector

Shutdown

Signal

(Continued on page 6)

PAGE 01-01

Page 8

DP-4X GENERIC POWER SUPPLY SHUTDOWN EXPLANATION

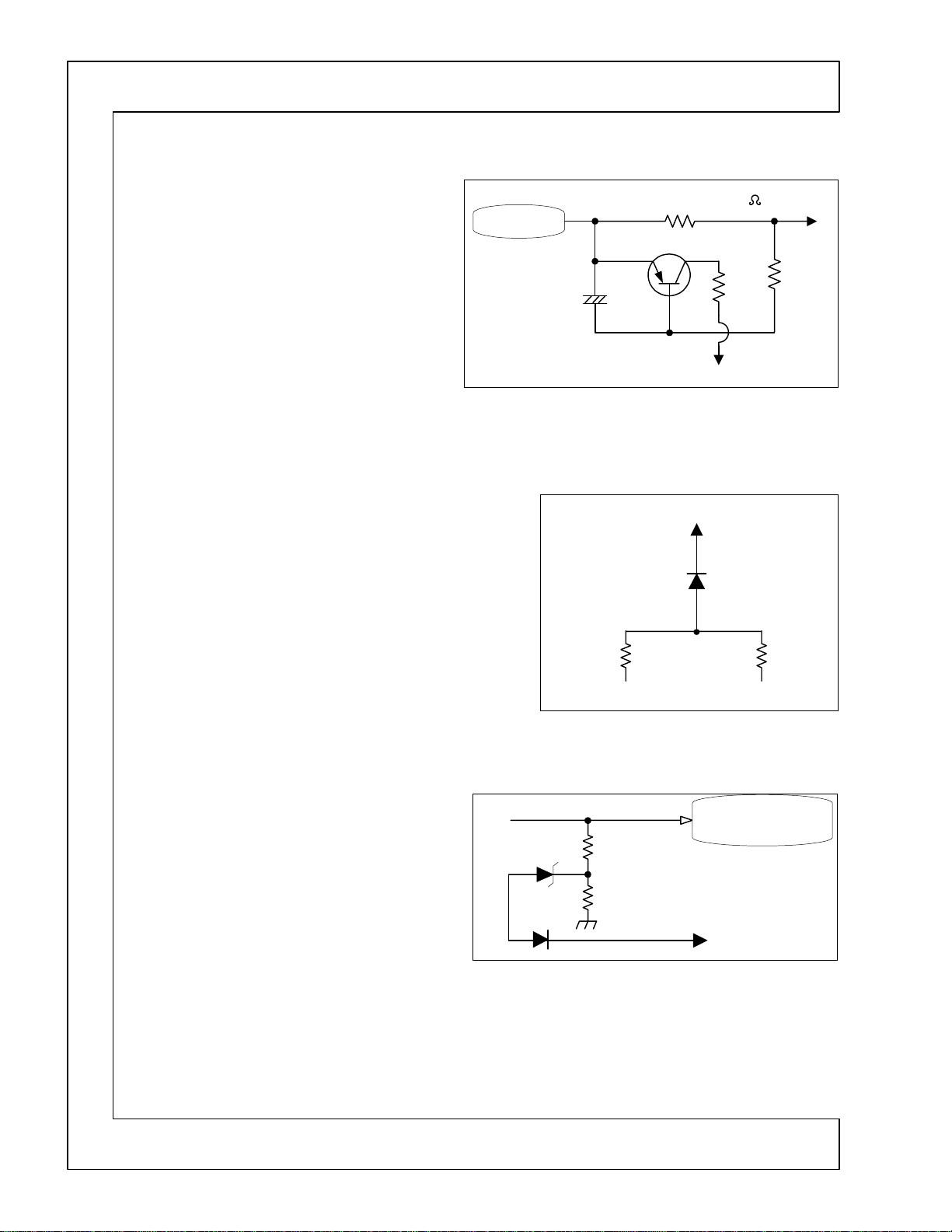

VOLTAGE LOSS or SHORT DETECTION

(See Figure 4)

One circuit used is the Voltage Loss Detection circuit. This is a very simple circuit that detects a loss of

a particular power supply and supplies a Pull-Down

path for the base of a PNP transistor.

This circuit consist of a diode connected by its cathode to a positive B+ power supply. Under normal

Voltage

Loss

Detector

conditions, the diode is reversed biases, which keeps

the base of Q1 pulled up, forcing it OFF. However, if

there is a short or excessive load on the B+ line that’s

being monitored, the diode in effect will have a LOW

on its cathode, turning it ON. This will allow a cur-

Figure 4

Shutdown Signal

rent path for the base bias of Q1, which will turn it

ON and generates a Shutdown Signal.

GENERAL INF O RMATION:

This explains the Overall Power Supply Shutdown Circuits:

Which turns off the Relay Driver for the Deflection Power Supply and the Relay for the Signal Power Supply.

DEFLECTION (High Voltage) POWER SUPPLY:

The Deflecti on Po wer supply is centered around th e Switching Transfor mer TP01 and the driver IC, IP01.

This power supply creates vo ltag es tha t are Swit ched on wh en the Set is turned on.

1. SW +115V 2. +220V

3. +28V 4. SW-28V

5. +7V 6. SW +6.3V

Other supplies are generated from these 6 main voltages.

SIGNAL (Low Voltage) POWER SUPPLY:

The Signal Power supply is centered around the Switching Transformer T201 and the driver IC, I201.

This power supply creates vo ltag es tha t are Swit ched on wh en the Set is turned on.

1. 38.5V or 29V 2. +10.5V

3. +21V 4. SW-5.6V

5. +16V 6. SW +5.7V

Other supplies are generated from these 6 main voltages.

Q204 and Q203 Relay Inhibit Activation. (SHUTDOWN) called COMMON ACTION CIRCUIT.

All Shutdown events will cause the main power relays to turn off. This action will stop all secondary power supplies.

The Low Voltage power supply (Stand-By) will Shutdown along with the Deflection Power Supply.

See the DP-4X Signal Power Supply Sh ut d ow n Circuit for detail s.

If any of the shutdown circuits activate, the base of Q203 will go High. This turn s on Q203 and r emoves the Power On Highs

from PPS1 connector pins 9 (Power_Sig) an d 11 (Power_Def) called Power_1 and Power_3. With this, the main power sup-

plies will STOP . Q204 ope r at es a s a “latch”. Th i s pr e vents Q203 from turning off if the shutdown signal disappears after

shutdown.

SOME SHUTD OW N CIRCUITS ARE DEF E AT ED IN STANDBY M O DE . (Set Off).

When the set is turned off (called Stand By), some of the shutdown inputs are not active because the voltages being monitored

are not on.

• Shorted FAN +10V (from from pin 3 of IC303). This voltage is monitored by D313.

• Stopped Fans PPF2 and PPF3 pin 2. This is monitored by D313.

• Shorted Drv 16.5V (from pin 2 of IC301) This voltage is monitored by D312.

• Prot_Drv (from pin 48 of PPS1) This voltage is monitored by D312.

• Prot_OCP (6 shutdown inputs) This voltage is monitored by D944.

1. SW +2.2V (IV01) * 2. SW +3.3V (IY01) * 3. SW +9V (IY07) *

4. VM +220V (QEA8) * 5. SW +6.3V (QP04) ** 6. SW +28V (DP30) **

* See the PROT_OVP and PROT_OCP Shutdown Diagram.

** See the Deflection Power Supply Shutdown Output Circuit Diagram.

Any Positive

B+ Supply

B+

Q1

(Continued on page 3)

PAGE 01-02

Page 9

DP-4X GENERIC POWER SUPPLY SHUTDOWN EXPLANATION

(Continued from page 2)

See the DP-4X Signal Power Supply Shutdown Circuit for details.

These shutdown circuits are defeated because the SW (Switched) power supplies are turned off in standby. So to prevent

faults triggering of the shutdown circuit, the sensing circuits are turned off also..

Q206

generates the shutdown high signal if any of the shutdown circuits attached to its base become low.

ter voltage to operated.

When the set is turned off,

SHUTDOWN INPUTS EXPLAINED:

GENERAL INFORMATION CONTINUED:

All of the Power Supply Shutdown circuitry can be broken down into the following categories;

Voltage Missing Detection or Short Detection or Negative Voltage Loss Detection

•

Voltage Too High Detection

•

Excessive Current Detection

•

COLD GROUND SIDE SHUTDOWN SENSING CIRCUITS.

All shutdown events arrive at the base of

The shutdown circuit are broken down into four pages. The shutdown outputs from each page are interconnected and indicated by symbols shown below;

A

B C D E F

Please refer to the following Diagrams as you continue to read the following explanations.

The DP-4X Deflection Side Shutdown Diagram for (A), (B), (C), (D).

1.

The DP-4X PROT_OVP and PROT_OCP Shutdown Diagram for (A), (B), (E), (F).

2.

The DP-4X Deflection Power Supply Shutdown Output Circuit Diagram for (C), (D).

3.

The DP-4X Signal Power Supply Shutdown Circuit for (E), (F).

4.

RY05

supplies the 5.7V to the Emitter of

RY05

opens and the 5.7V disappears so

(See previous two pages for generic shutdown circuit details)

Q203

. The shutdown events are categorized in the following pages.

Q206

. This voltage must be active for

Q206

can no longer operate.

(AC must be removed to recover).

Q206

requires emit-

Q206

to function.

:

PAGE 01-03

Page 10

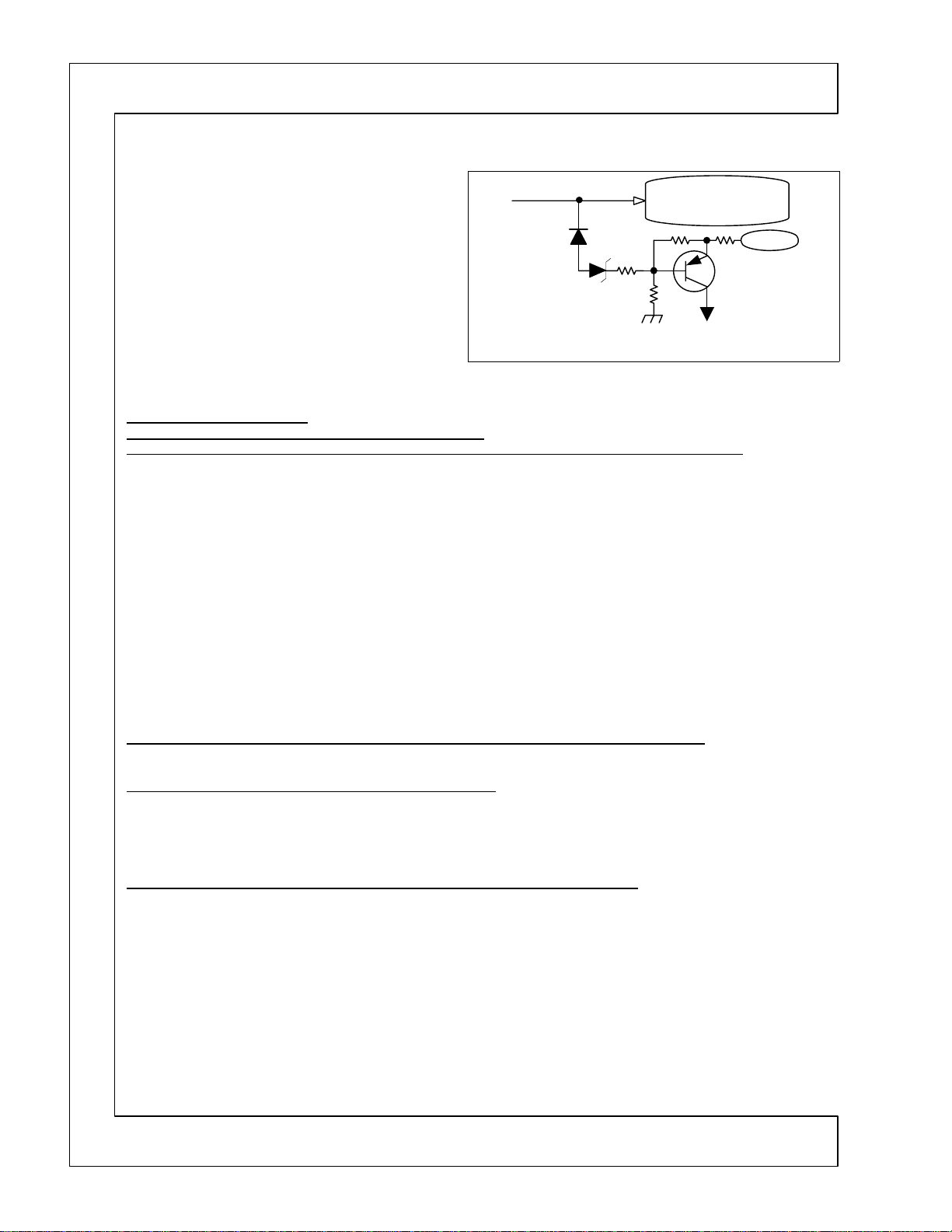

DP-4X DEFLECTION SIDE SHUTDOWN DIAGRAM EXPLANATION

See The DP-4X Deflection Side Shutdown Diagram for (A), (B), (C), (D).

HIGH VOLTAGE TOO HIGH DETECTION: One of the Shutdown circuits for outp ut (A).

•

DH15 High Voltage Too High Sensing Circuit.

This circuit monitors the

. If the voltage created by rectifier

7

zener will fire. This high will be routed to pin 8 of

PROT_OCP Shutdown Diagram

• At the same time, the zener diode

Horizontal Drive for High Voltage and this IC will shut off, turning off High Voltage drive pulses.

• The ABL is tied to the cathode of

as the screen brightness fluctuates and caused the High Voltage to bounce. By tying ABL to the Excessive

High Voltage detection voltage, the firing point is slightly altered.

VERTICAL OUTPUT CI RCUIT EXCESSIVE CURRENT DETECTION: One of the Shutd own circuits for

output (A).

•

Q604 Vertical Circuit Excessive Current Sensing Circuit.

This circuit monitors the

rent,

this transistor. When this happens, its collector will go high. This high will be routed through

pin 8 of

-5V NEGATIVE VOLTAGE LOSS DETECTION: One of the Shutdo wn circuits for output (A).

•

DK18 –5V Loss Detection Circuit.

The purpose of the Negative Voltage Loss detection circuit is to compare the negative voltage with its

counter part positive voltage. If at any time, the negative voltage drops or disappears, the circuit will produce a Shutdown signal.

There are two resistors. One to the positive voltage +5V

RK22

voltage is lost, the neutral point will go positive. This in turn will create a Shutdown Signal through

DK18

Shutdown Diagram.

PROT_OVP INPUT INDICATED BY (C) One of several Shutdown outputs for item (A).

• The

put from the Deflection Power Supply Shutdown Circuit Diagram. There are 3 circuits from the Deflection Power Supply Shutdown Circuit Diagram that provide inputs to this diagram.

• This is explained on Page 01-06.

SW +10.5V SHORT DETEC T INDICATED BY (D) Shutdown output for item (B).

•

D723

age disappears or is shorted,

output as a shutdown signal on the

will develop a larger voltage drop. This will cause the base voltage of

R629

PDS3 PROT_OVP (A)

. At their tie point, (neutral point), the voltage is approxima tely (-1V). If however, the negative

. This high wi l l be routed to pin 8 of

PROT_OVP

is attached to the B+

signal (Active High) is shown in the center left hand side of the diagram. This is an in-

High Voltage

SW+28V

SW +10.5V

D723

line generated by rectifying the pulse from the flyback

and capacitor

DH13

PDS3 PROT_OVP (A)

.

will fire and this high will be routed to pin 7 of

DH14

via

DH15

line going to

to the

PROT_OVP and PROT_OCP Shutdown Diagram.

PDS3 PROT_OVP (A)

line which is generated on the Signal PWB by

cathode will be pulled low generating a Low on Pin 9 of

PROTECT_OCP

. This resistor offers sli ght “Trigger Point” deviations

RH32

Vertical Output IC. If the IC draws too much cur-

I601

indicated as item

at the cathode of

CH17

and one to the negative voltage –5V

RK23

to the

(B)

DH15

to the

Q604

PROT_OVP and PROT_OCP

.

TH01

goes too high, this

PROT_OVP and

. This is the

IH01

to fall turning on

and to

D608

. If this volt-

QY62

and

PDS3

pin

PAGE 01-04

Page 11

DP-4X DEFLECTION SIDE SHUTDOWN DIAGRAM

Any fluctuations in High Voltage will also be

reflected by the 50P output P/P.

By monitoring the 50P (50 Pulse) rises in High Voltage

will be sensed. If High Voltage climbs too high, DH15

will fire and trigger a shut down event.

DH14 will fire and stop High Voltage Horz. Drive

Flyback

RH32 allows ABL fluctuations to

manipulate the Trigger Point of Shut

Down as screen brightness varies.

ABL is inverse proportionate to

brightness.

This prevents false Shut Down triggering.

C

3

Active

PROTECT _OVP

From Deflection Power Supply Shut

Down Output Circuits Diagram.

Vertical Output Circuit

I601

SW 28V

7

R629

C604

L603

Q604

R630

C610

Excessive Vertical Current Det.

0.68 Ohm

D608

R631

Normal

R632

TH01

TH02

8

5OP

4

RH25

Hi Volt

H. Drive

IH01

H. Drive

110

7

OVP

ABL

RH32

DH15

RH24

Excessive Hi

Voltage Det.

1

DK18 Monitors the -5V and +5V lines going to the DCU.

If the -5V line is loss, the +5V line provides the Shut Down Hi.

On the Convergence Circuit Diagram Power Def. page 2 of 3.

High Voltage

Sensing Circuit

RH23

LH06

29.01V

CH17

Stops H. Drive

7

DH13

DH14

RH26

CH10 RH09

+5V

DK18

RK23

2.7K

-5V Loss Det.

-5V

RK22

PDS3

1.8K

If the Vertical Output IC has a problem, R629

will sense the current rise. The voltage drop will

be reflected at the base of Q604 turning it on

and producing a Shut Down high.

SW +10.5V

D723

D

SW +10.5V From QY62 SW +10.5V Regulator on Signal 5 of 5 Schematic.

8

10

9

SW

+10.5V

6

1

PROTECT _OVP

To Signal PWB

See Protect_OVP and Protect_OCP

Shut Down Diagram for Details.

PROTECT _OCP

To Signal PWB

PAGE 01-05

A

B

Page 12

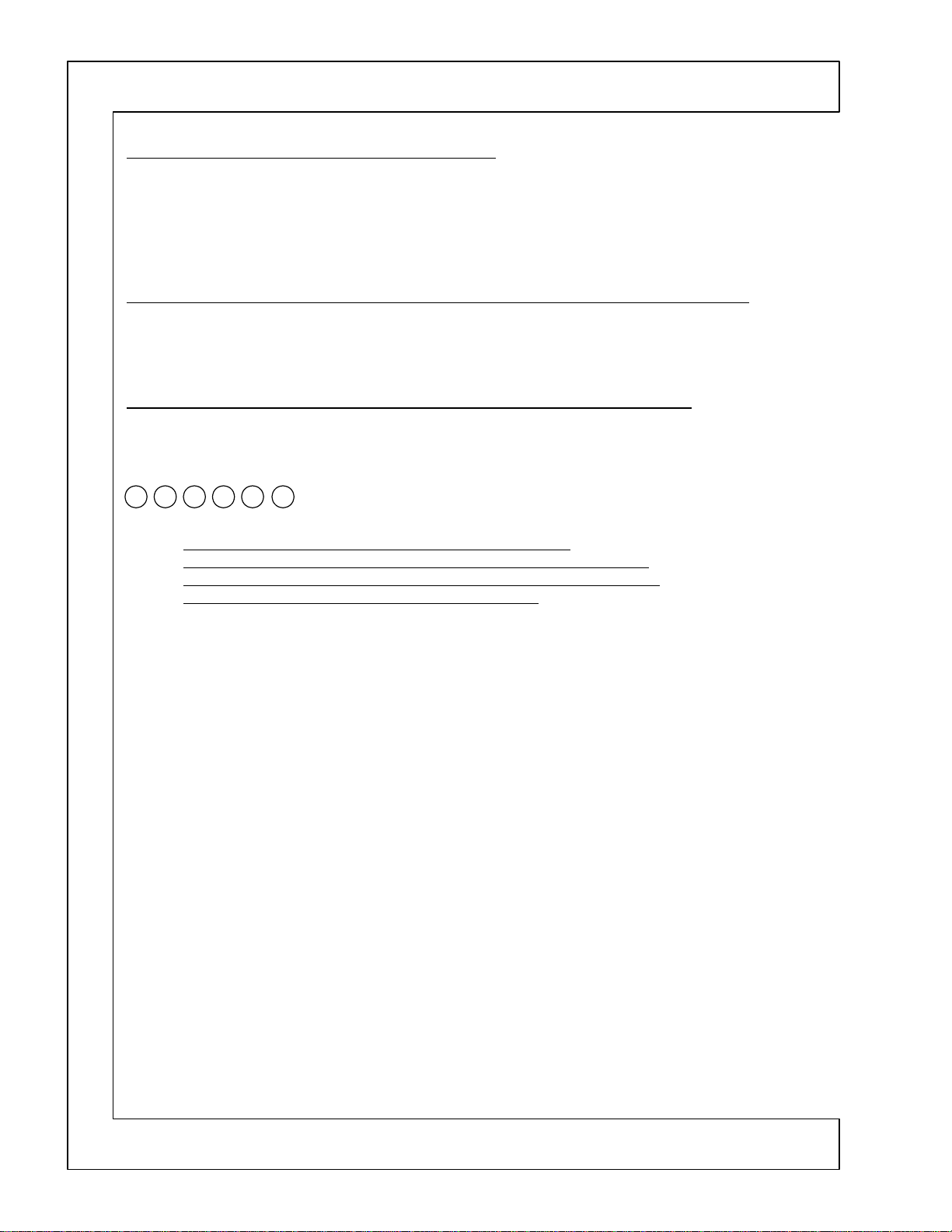

DP-4X PROT_OVP and PROT_OCP SHUTDOWN DIAGRAM EXPLANATION

PROT_OVP and PROT_OCP SHUTDOWN CIRCUITS EXPLAINED: (A) (B) (E) (F)

(See the PROT_OVP and PROT_OCP Shutdown Diagram for Details).

CPT PROTECT (+200V Excessive Current Detection):

•

On the RED CRT PWB +220V (VM 200V) Excessive Current Detection

Monitored by

The collector will go high. This high will go to the connector

high continues to the Green CRT PWB connector

and

CPT PROTECT

• This line is connected to the

Circuit, identified as

• Any High from this line is then routed to the

is routed to the Signal Power Supply Shutdown Circuit Diagram identified as

VM GAIN CONTROL (VM 200V Excessive Current Detection):

•

On the BLUE CRT PWB VM+220V Excessive Current Detectio n

Monitored by

it on.

The collector will go high. This high will go to the connector

high continues to the Green CRT PWB connector

• This line is connected to the

• This line is also connected to the base of

High to a Low on its collector.

• The collector of

and the

PROT_OCP (B)

VOLTAGE LOSS DETECTION CIRCUITS:

•

•

•

•

PROT_OCP

generates the SW +2.5V. If this line is shorted or missing, this line will drop Low.

IV01

generates the SW +3.3V.

IY01

missing, the cathode of

generates the SW +9V.

IY07

ing, the cathode of

PROT_OCP: LABELED AS OUTPUT (F).

Any low from this line is then routed to the

. From here this low is routed to the Signal Power Supply Shutdown Circuit Diagram and

(F)

again identified as

. If the

RE35

on the Signal PWB.

6 inputs active High.

(A)

. If the

REF1

is tied to several circuits. The

QY60

from the Deflection Side Shutdown Circuit from

which represents 1 shut down input from the Deflection Side Shutdown circuits.

DY04

draws too much current, the base voltage of

220V

connector which ties the inputs from the Deflection Side Shutdown

PDS3

VM220V

VM Signal

DY03

goes low which pulls the

(F)

draws too much current, the base voltage of

generation circuit and turns it off.

QY60

One of several Shutdown outputs for (F).

is connected to the SW +3.3V line. If this line is shorted or

DY03

goes low which pulls the

is connected to the SW +9V line. If this line is shorted or miss-

DY04

.

One of several Shutdown outputs for (E).

will fall turning it on.

QE08

pin 7 labeled as

ERG1

pin 3 labeled

PSC

connector pin

PPS1

One of several Shutdown outputs for (F).

EGB1

pin 2 labeled

PSC

. This transistor acts as an inverter to change the output

Voltage Loss Detection Circuits

PROT_OCP

PROT_OCP

connector pin

PPS1

VM PROT

identified as

47

pin 8 labeled

VM GAIN

PDS3

line low.

line low.

45

connector pin 9. Labeled as

identified as

VM PROT

on the Green CRT PWB

. From here thi s high

(E)

.

(E)

QEA8

GAIN CONT

.

will fall turning

explained below

PROT_OCP

. This

. This

PAGE 01-06

Page 13

DP-4X PROT_OVP and PROT_OCP SHUTDOWN DIAGRAM

PROT_OVP SHUT DOWN DIAGRAM

+220V

VM

220V

PDC1

EGB2

2

QEA8

1

RE35

2.2 Ohm

QE08

CE10

REF1

10 Ohm

REF2

REE9

SW +2.2V Reg

RED CRT PWB

R.G.B. Drives

RE27

RE31

VM 200V

RE34

VM PROT

ERG1

7

GREEN

CRT

PWB

PSC

VM PROT

SIGNAL PWB

3

CPT

PROTECT

RE29

Text Indicates the Labels on the Schematic

PROT_OCP SHUT DOWN DIAGRAM

BLUE CRT PWB

VM Circuit

REF4

REF5

CEC1

SIGNAL PWB 2 of 3

DEB6

REF5

CONT

GAIN

EGB1

8

GREEN

CRT

PWB

PSC

VM GAIN

CONT

Also Shuts Off

VM Signal

Generation Circuit

2

1

Active Hi

VM GAIN

CONT

DEF. PWB /

DEF. POWER

PDS3PDS3

6

8

PROT_OVP

From Deflection

Side Shut Down

Circuit

Active Hi

PROT_OVP

7

5

PROT_OCP

Active Lo

A

PPS1

47

45

SIG

POWER

PWB

See Signal

Power Supply

Shut Down

Circuit

E

F

SW +5.7V

DM +10.5V

IV01

1

3 8

SW +3.3V Reg

IY01

1

SW +9V Reg

IY07

7

SW +2.5V

DEF. PWB /

DEF. POWER

PDS3

CZ04

3

SW +3.3V

DY03

RZ62

4

RL50

QY60

RZ60

35

SW +9V

DY04

3

RZHD

1

9

B

PROT_OCP

From Deflection

Side Shut Down

Circuit

SIGNAL PWB

PAGE 01-07

Page 14

DP-4X DEFLECTION POWER SUPPLY SHUTDOWN OUTPUT DIAGRAM EXPLANATION

DEFLECTION POWER SUPPLY SHUTDOWN OUTPUT CIRCUIT DIAGRAM EXPLAINED: (C)

(See the Deflection Power Supply Shutdown Output Circuit Diagram for Details).

PROT_OVP: Identified as (C).

EXCESSIVE DEFLECTION 115V B+ CURRENT DETECTION: Part of several Shutdown outputs to (C).

•

•

•

•

EXCESSIVE DEFLECTION 115V B+ VOLTAGE DETECTION: Part of several Shutdown outputs to (C).

•

•

•

SW -28 VOLT SHORTED or MISSING DETECTION: Part of several Shutdown outputs to (C).

•

•

monitors

QP05

enough to turn on

ing an increase in the voltage drop across this resistor. If there is enough current the base voltage of

will drop enough to turn on t his transistor . When

fire zener diode

and

CP49

out and fluctuations on the anode of

DP37

and identified as

PROT_OVP

DP39

Deflection

DP37

and identified as

PROT_OVP

identified as

SW -28V Shorted or Missing Detection

Monitored by

zener to fire. This high will be routed through

PROT_OVP

PROT_OVP

identified as

RP37

cathode is connected the anode of

is routed to the Deflection Side Power Supply Shutdown Diagram also identified as

monitors the Deflection

115V B+

cathode is connected the anode of

Identified as

(C)

DP46

and identified as

Identified as

(C)

current draw.

RP34

. However, if there is a problem, the current draw through

QP05

and generate a high on the anode of

DP36

prevent faults triggering of the shut down line due to High Voltage bounce by smoothing

.

(C)

115V B+

line goes to o high,

.

(C)

is routed to the Deflection Side Power Supply Shutdown Diagram also

(C)

.

. If the

SW-28V

.

(C)

is routed to the Deflection Side Power Supply Shutdown Diagram also

(C)

.

is a 0.39 low ohm resistor. Normally the current draw isn’t

RP34

increases caus-

RP34

turns on, its collector goes high. This high will

QP05

DP37.

.

DP36

. This line is connected to the line labeled

DP38

line via the Voltage divider consisting of

will fire and generate a high on the anode of

DP39

. This line is connected to the line labeled

DP38

is shorted or missing, the cathode will be pulled high causing the

. This line is connected to the line labeled

DP47

RP38

PROT_OVP

and

RP39

.

DP37

PROT_OVP

QP05

(C)

. If the

.

PAGE 01-08

Page 15

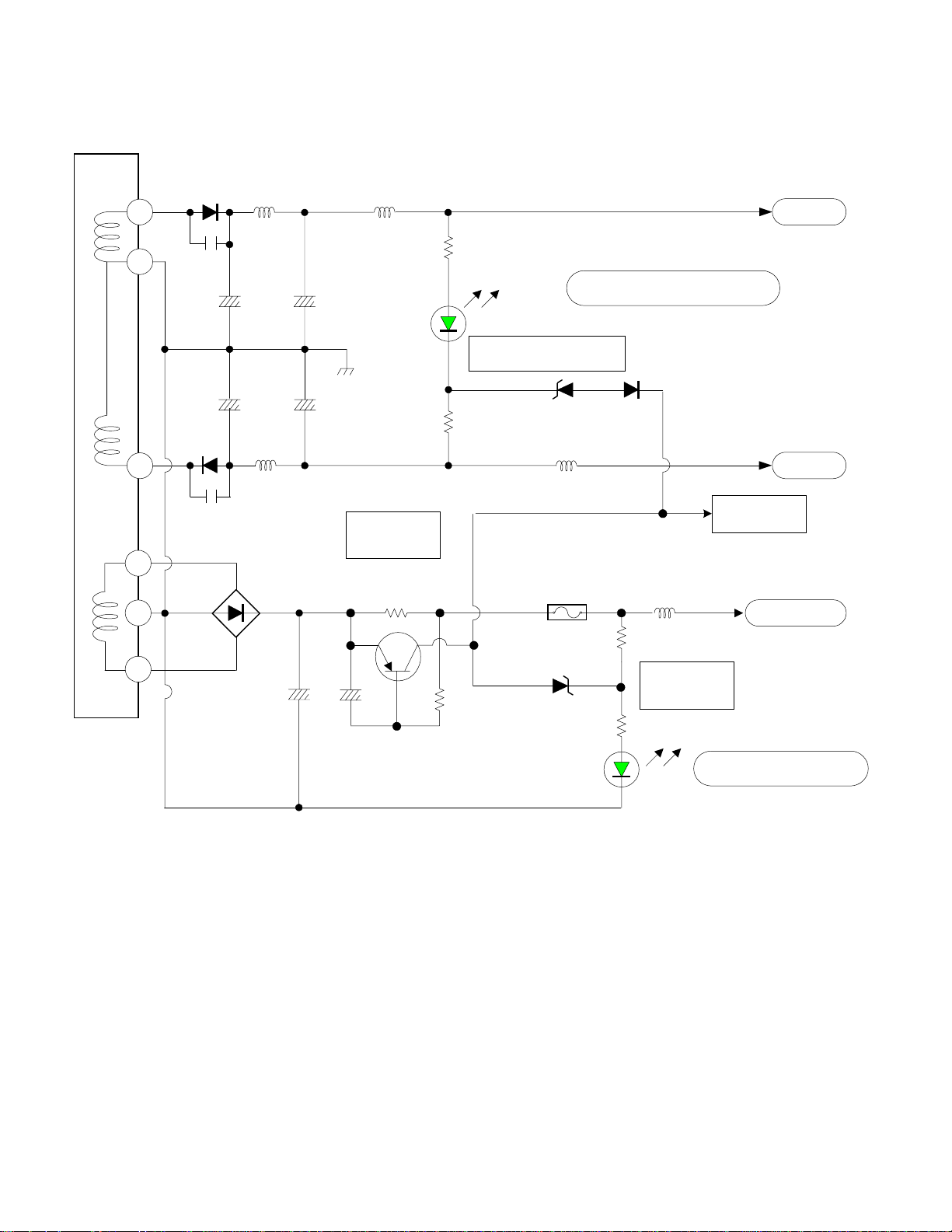

TP01

DP-4X CHASSIS

Deflection Power Supply Shutdown Output Circuit Diagram

OCP and OVP

+28V

-28V

16

15

14

DP30

CP30

CP32

CP33

DP31

CP31

+

+

CP49

RP37

LP30

LP31

LP33

RP46

+

CP34

DP50

+

CP35

RP47

DP37

DP36

GREEN

L.E.D.

-28V Short or Loss Detection

DP46 DP47

LP34

DP38

1.26A

0.65A

SW -28V

Active High

3

PROT_OVP

C

To Deflection Side

Power Supply Shut

Down Diagram

SW+ 28V

10

11

11

18

17

CP39

+115V

2

DP34

14

3

CP45

CP46

+7V

2

DP32

14

3

CP36

DP48DP49

0.39 Ohm

+115V Over Current

Detection

QP04

RP34

RP36

QP05

RP35

0.19A

0.69A

EP02

2 Amp

RP38

DP39

RP39

DP40

SW + 7V

SW + 6.3V

LP37

GREEN L.E.D.

SW + 115V

0.85A

+115V Over Voltage

Detection

PAGE 01-09

Page 16

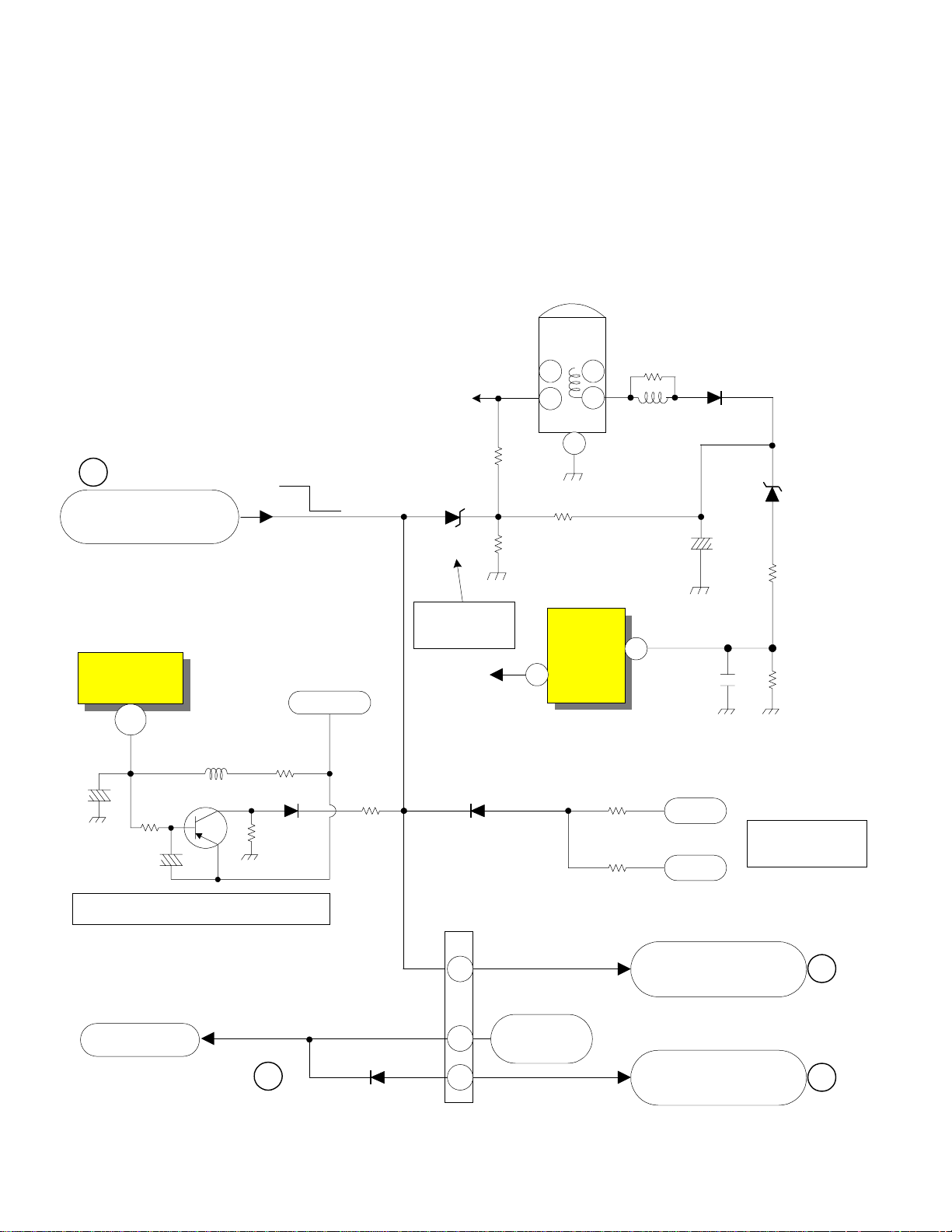

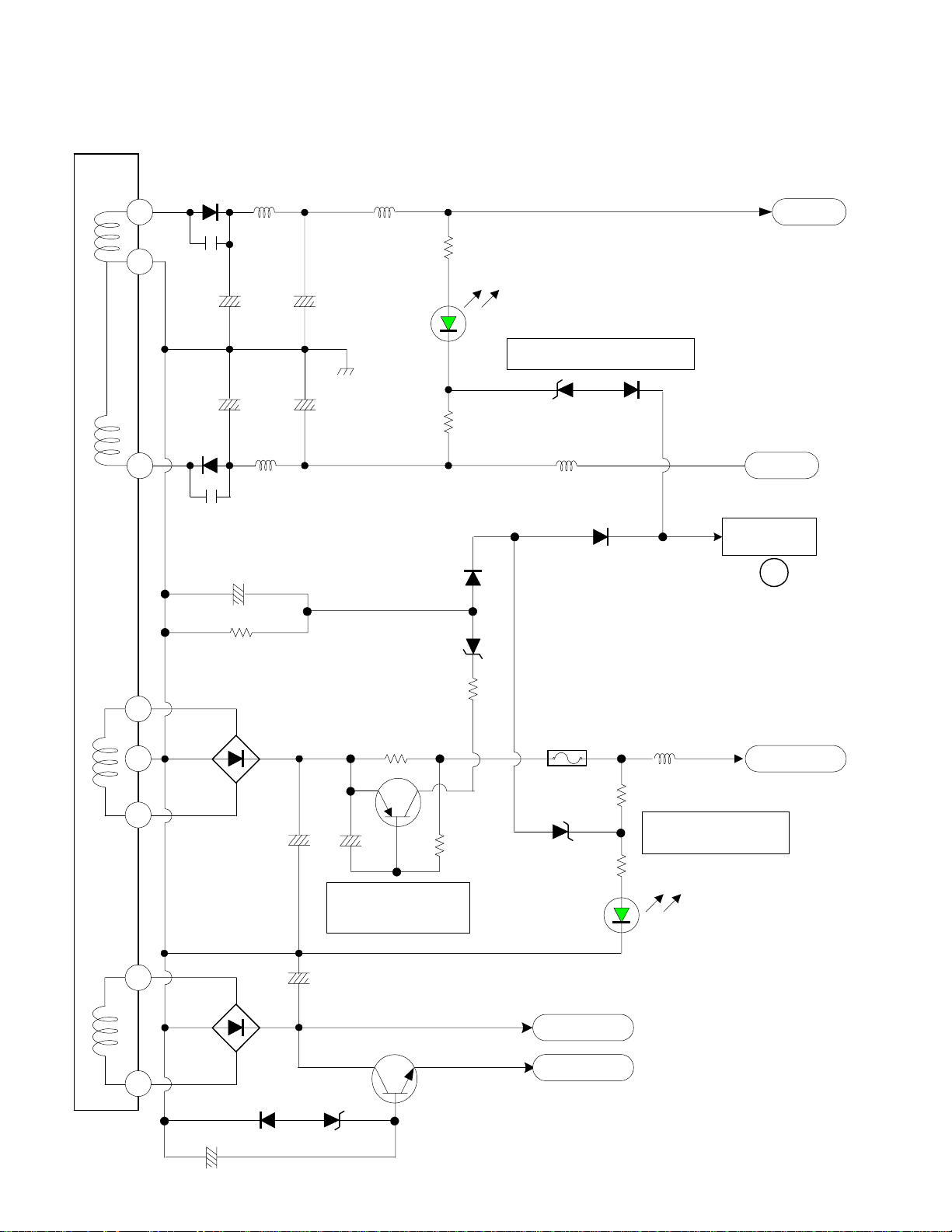

DP-4X SIGNAL POWER SUPPLY SHUTDOWN CIRCUIT EXPLANATION

See the DP-4X Signal Power Supply Shutdown Circuit for details. This includes inputs (E) and (F).

There are a total of 20 individual Shutdown inputs to the Relay Inhibit transistor Q203 shown on the Signal

Power Supply Shutdown Circuit.

• There are 8 individual Shutdown detection circuits on the Signal Power Supply Circuit Diagram.

• There are a total of 5 individual Shutdown inputs from the Deflection PWB via PROT_OCP (active

Low). Input from the PPS1 connector pin 45

• There are a total of 7 shutdown inputs from PROT_OVP (active High) input from the PPS1 connector

pin 47.

SHUTDOWN INPUTS EXPLAINED:

Q204 and Q203 Relay Inhibit Activation. (SHUTDOWN) called COMMON ACTION CIRCUIT.

All Shutdown events will cause the main power relays to turn off. This action will stop all secondary power

supplies. The Low Voltage Signal Power Supply will Shutdown along with the Deflection Power Supply.

• Q203 CIRCUIT EXPLAINED:

• If any of the shutdown circuits activate, the base of Q203 will go High. This turns on Q203 and removes

the Power On Highs from PPS1 connector pins 9 (Power_Sig) and 11 (Power_Def) called Power_1 and

Power_3. With this, the main power supplies will STOP. Q204 operates as a “latch”. This prevents

Q203 from turning off if the shutdown signal disappears after shutdown.

POWER ON/OFF RELAYS RY101 and RY102:

RY101 Explained:

• The Relay RY101 supplies AC to the Signal Power Supply bridge rectifier DS201. When this relay en-

gages, the Signal Power Supply starts up and supplies the voltages mentioned below.

SIGNAL (Low Voltage) POWER SUPPLY:

• The Signal Power supply is centered around the Switching Transformer T201 and the driver IC, IP01.

• This power supply creates voltages that are Switched on when the Set is turned on.

1. 38.5V or 29V 2. +10.5V 3. +21V

4. SW-5.6V 5. +16V 6. SW +5.7V

• Other supplies are generated from these 6 main voltages.

RY102 Explained:

• The Relay RY102 supplies AC to the Deflection Power Supply bridge rectifier DP01. When this relay

engages, the Deflection Power Supply starts up and supplies the voltages mentioned below.

DEFLECTION (High Voltage) POWER SUPPLY:

• The Deflection Power supply is cente r ed arou nd the Switching Transf o r me r TP01 and the driver IC, IC201.

• This power supply creates voltages that are Switched on when the Set is turned on.

1. SW +115V 2. +220V 3. +28V

4. SW-28V 5. +7V 6. SW +6.3V

• Other supplies are generated from these 6 main voltages.

CIRCUITS ATTACHED TO THE BASE OF Q203:

This year, Hitachi is utilizing a three legged diode OR gate style of input device for feeding shutdown inputs

to the base of Q203. These diode OR gates and circuits attached are explained next.

(Continued on page 11)

PAGE 01-10

Page 17

DP-4X SIGNAL POWER SUPPLY SHUTDOWN CIRCUIT EXPLANATION

(Continued from page 10)

D214 Left Hand Input Circuits:

The left hand input to

base inputs a re monitoring DC voltages for short s .

Q205 base input circuits.

•

•

The Emitter of

right hand i nput is

these voltages without fail. If either the

D214 Right Hand Input Circuit:

The right hand input to

over voltage condition. If this voltage rises too much, the zener will fire generating a high on its anode and

through

D217 input circuits.

•

D217 Left Hand Input:

1.

•

D217 Right Hand Input:

1.

D218 input circuits.

•

D218 Left Hand Input:

1.

•

D218 Right Hand Input:

1. This monitors the

D220 input circuits.

The anode of diode

input is monitoring the

inputs will be Low in nature. There are a total of 5 inputs fed to this pin described in the previous 9 pages.

• See references to (F) on the PROT_OVP and PROT_OCP SHUTDOWN DIAGRAM.

D115:

1. The left hand input monitors the 5.7V line for shorts.

2. The right hand input monitors the 35V line for shorts.

D116:

1. The left hand input monitors the 10.5V line for shorts.

2. The right hand input monitors the 3.3V line for shorts.

Q205

10.5V

to the

D214

ZD202

much, the zener will fire generating a high on its anode and through

Circuit

ZD203

much, the zener will fire generating a high on its anode and through

Circuit

ZD205

tive voltage fed through R241 will pull the cathode of zener diode

generating a high on its anode and through

total of 7 inputs fed to this pin described in the previous 9 pages. If this voltage goes high, the high

will be dir ected through

Common Action Circuit

. This monitors the DC voltage

.

. This monitors the DC voltage

.

. This monitors the DC voltage -

• See references to (E) on the PROT_OVP and PROT_OCP SHUTDOWN DIAGRAM.

D220

is connected to the collector of

D214

pull up voltage is supplied through

. This assures the emitter voltage is always present and allows

or the

10.5V

is connected to the anode of

D214

.

5.7V

10.5V

5.6V

PROT_OVP

is connected to the collector of

PROT_OCP

inputs also labeled as

to the

D218

inputs also identified as

Common Action Circuit

D213

3.3V

for an over voltage condition. If this voltage rises too

for an over voltage condition. If this voltage rises too

for a loss or short. If this voltage disappears, the posi-

D218

Q206

. This transistor works as an inverter. Its

Q205

. The left hand input to

line is shorted, this transistor will still function.

. This monitors the DC voltage 3.3V for an

ZD204

D217

D217

ZD205

to the

Common Action Circuit

to the connector

(E)

.

. This transistor works a s a n inverter. Its base

from the connector

(F)

is

D213

Q205

to the

Common Action

to the

Common Action

high. The zener will fire

.

pin 47. There are a

PPS1

pin 45. These

PPS1

and the

5.7V

to monitor

PAGE 01-11

Page 18

DP-4X SIGNAL POWER SUPPLY SHUTDOWN CIRCUIT

Power 1

Power 3

Power 2

PPS1

EF

PROT_OVPPROT_OCP

For

Signal

Power

Supply

DS201

Relay

Driver

For

Deflection

Power

Supply

DP01

AC

Q101

AC

SBY +5V

RY101

SBY +5V

RY102

D104

D109

R118

D105

R110

D110

9

onoff

D111

R122

11

R125R120

5.7V

12

R126

R236

Q104

35V 3.3V

RY105

SBY +5V

10.5V

Q206

C232

R238

45 47

5

Active Low Active High

D219

R237

R239

7

D213 D115 D116

ZD206

C237

R224

R235

-5.6V

R240

Q205

R233

ZD204

ZD202

R241

ZD203

ZD205

PAGE 01-12

Relay

Driver

Q102

R121

R230

Q203

C235

C238

Q204

R231

R232

D214 D217 D218

20

D220

5825

Page 19

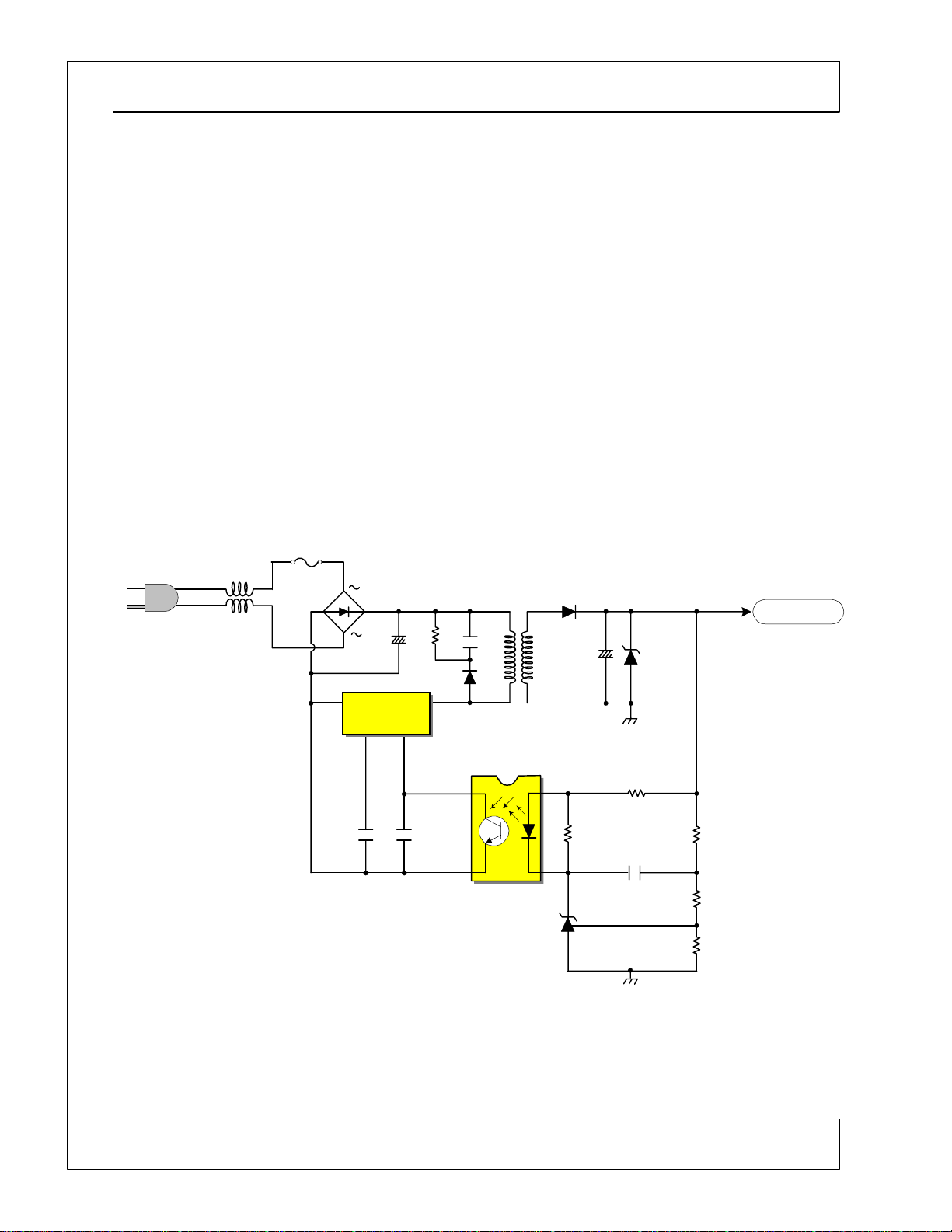

DP-4X STAND BY +5V POWER SUPPLY GENERATION EXPLANATION

STAND-BY +5V POWER SUPPLY GENERATION EXPLANATION:

The Stand By power supply operates anytime the set is plugged into an AC outlet. Shown

below in Figure 1 is the Stand By power supply.

a self contained Oscillator, Driver IC. It switches the primary of

The secondary of

the voltage is clamped by

T101

produces the SBY +5V via the rectifier

ZD101

.

A feedback to

IC101

is supplied by the photo coupler

IC102

•

IC102

works as a variable resistor attached to the cathode of the internal LED inside

. As the

SBY +5V

changes so will the resistance of

tance goes Down. As the Resistance goes down the Light emitted from the LED will increase. As the Light increases from the LED, the receiver will conduct more heavily.

This decreases the voltage fed back to

to reduce the primary switching of

IC101

T101

IC101

is the Driver IC for this supply. It’s

T101

.

D103

and filter

PC102

for regulation purposes.

IC102

. Voltage Up, Resis-

causing the internal circuits within

and reduce the

SBY 5.7V

line back to normal.

C106

. Then

IC101

L102

F103

DS101

-+

C105

IC101

D102

C110C107

C106R110

T101

PC102

IC102

D103

C106

R112

SBY +5V

ZD101

R111

R113

C109

R114

R115

Figure 1

PAGE 01-13

Page 20

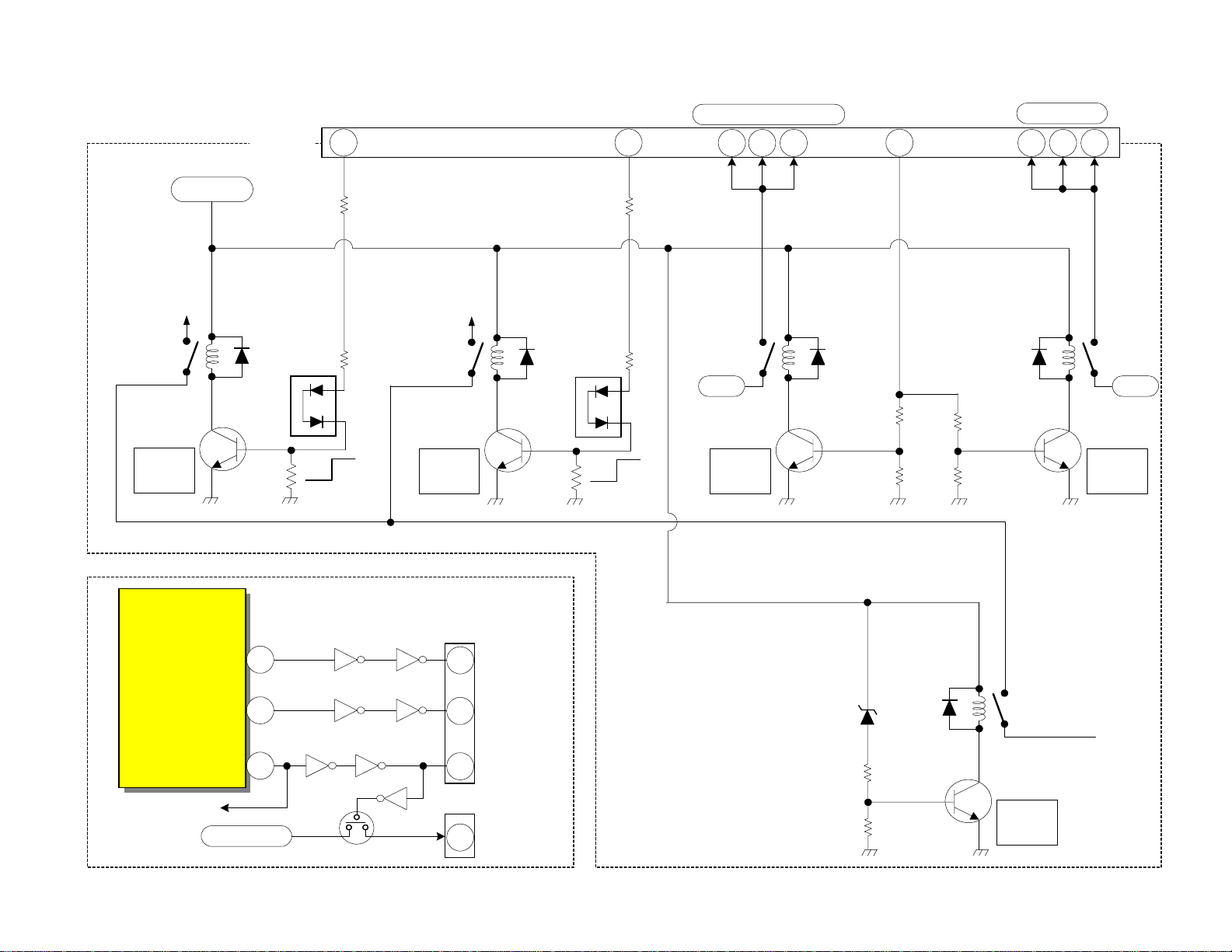

DP-4X POWER SUPPLY RELAY CONTROL EXPLANATION

See The DP-4X Stand By +5.7V Generation Circuit Explanation for details.

See The DP-4X Power On and Off Circuit Diagram for details.

Power Supply On and Off Circuit Explanation:

The DP-4X Chassis utilizes 5 relays.

RY101

1.

RY102

2.

RY103

3.

RY104

4.

RY105

5.

RY104

(4)

Starting with

supplies AC to the Bridge Rectifiers for the Signal and Deflection Power Supplies.

When The Stand By Power Supply develops the

voltage is delivered to the primary windings of

RY104

RY101

(1)

When the set is turned on, the

croprocessor

high is sent to

From here this high goes to the Deflection PWB through

Q101

of

coil inside

DS201

fier

RY102

(2)

When the set is turned on, the

croprocessor

high is sent to

From here this high goes to the Deflection PWB through

Q102

of

turn for the coil inside

Then to the Deflection Power Supply rectifier

gins to operate.

RY103

(3)

When the set is turned on, the

croprocessor

labeled

Base of

ground return for the coil inside

connector

on to the Audio Output IC

AC Supply to the Signal Power Supply Relay

AC Supply to the Deflection Power Supply Relay

DC Supply to the Audio Output Relay

AC Supply to all AC Relays Relay

DC (SW +5.7V) Supply to the Low Voltage Regulators Relay

AC Supply to all AC Relays Relay

RY104

. This turns on the relay and supplies AC to the above mentioned circuits.

AC Supply to the Signal Power Supply Relay

I004

Q018

goes high and the transistor turns on. This action supplies a ground return for the

RY101

and the Signal Power Supply begins to operate.

AC Supply to the Deflection Power Supply Relay

I004

Q023

. The base goes high and the transistor turns on. This action supplies a ground re-

DC Supply to the Audio Output Relay

I004

POWER 2

Q103

. The Base goes high and the transistor turns on. This action supplies a

PPS1

because this Relay supplies AC to

POWER SIG

. (This high also turns on the Power LED on the front of the set). This

Q021

and

and the relay turns on supplying AC to the Signal Power Supply recti-

. (This high also turns on the Power LED on the front of the set). This

and

RY102

. This high is sent to

. From here this high goes to the Deflection PWB through

pins 1,

2

then to the

POWER DEF

Q024

then to the

and the relay turns on supplying AC to the connector

POWER DM

RY103

and 3. Then to the Signal PWB and

IA02

.

SBY +5V

RY104

command is supplied from pin 59 of the Mi-

PPS1

connector pin 9 labeled

command is supplied from pin 58 of the Mi-

PPS1

connector pin

DP01

command is supplied from pin 91 of the Mi-

Q028

and the relay turns on supplying Audio B+ to the

and

Q029

(Page 01-16)

RY101

and to the relay driver Q105 for

R120, R110, D109

R125, R122, D110

and the Deflection Power Supply be-

then to the

and

, (see previous page) this DC

11

(Previous Page)

RY102

labeled

PPS1

Continued on Next Page

which in turn

POWER 1

to the Base

POWER 3

to the Base

connector pin

R124

.

.

PC2.

to the

12

PAGE 01-14

Page 21

DP-4X POWER SUPPLY RELAY CONTROL EXPLANATION

Continued from Previous Page

See The DP-4X Power On and Off Circuit Diagram for details. (Page 01-16)

RY105

(5)

DC (SW +5.7V) Supply to the Low Voltage Regulators Relay

When the set is turned on, the

Microprocessor

I004

. This high is sent to

pin 12. From here this high goes to the Deflection PWB through

Q104

. The Base goes high and the transistor turns on. This action supplies a ground

return for the coil inside

nector

PPS1

pins 25,

26

POWER DM

RY105

27.

and

command is supplied from pin

Q028

and

Q029

then to the

R126

and the relay turns on supplying

SW 5.7V

Then to the Signal PWB and on to the following Low

Voltage Regulators and ICs.

•

SIGNAL 5 of 5 DIAGRAM (AV Selector).

IY01 +

◊

IY02 +

◊

IY08

◊

•

SIGNAL 4 of 5 DIAGRAM (3D Y/C)

IV01 +

◊

•

SIGNAL 1 of 5 DIAGRAM (Micro).

I010

◊

I013

◊

I006

◊

I008

◊

3.3V Regulator.

5V Regulator.

SW +5V Regulator.

2.5V Regulator.

Bus Select Switch.

+3.3V Regulator.

AV Control IC

IR Blaster Select Switch.

91

of the

PPS1

connector

to the Base of

to the con-

PAGE 01-15

Page 22

DP-4X POWER ON and OFF CIRCUIT DIAGRAM

Audio 38.5V or 29V

SW +5.7V

For Signal

Power Supply

AC

Relay

Driver

SBY +5V

AC to

DS201

Q101

RY101

PPS1

D104

D109

R118

R120

R110

9

onoff

POWER 1

For Deflection

Power Supply

AC

Driver

Relay

AC to

PC2

Q102

RY102

R125

11

38V

531

12

POWER 3 POWER 2

RY103

For

D105

D110

R121

R122

onoff

Audio

Outputs

Q103

Relay

Driver

D106

R124

R123

R126

R127

28 27 25

5.7V

RY105

D108

5.7V38V

Q104

Relay

Driver

Microprocessor

PAGE 01-16

POWER LED

I004

POWER SIG

POWER DM

POWER DEF

SW +10.5V

59

91

58

Signal PWB

Q018 Q021

Q028 Q029

Q023 Q024

QY63

QY62

PPS1

9

12

11

PDS3

10

POWER 1

POWER 2

POWER 3

Signal Power Supply PWB

ZD102

R126

R125

D107

RY104

For Signal and

Deflection Power

Supply

AC Relays.

AC

Q105

Relay

Driver

Page 23

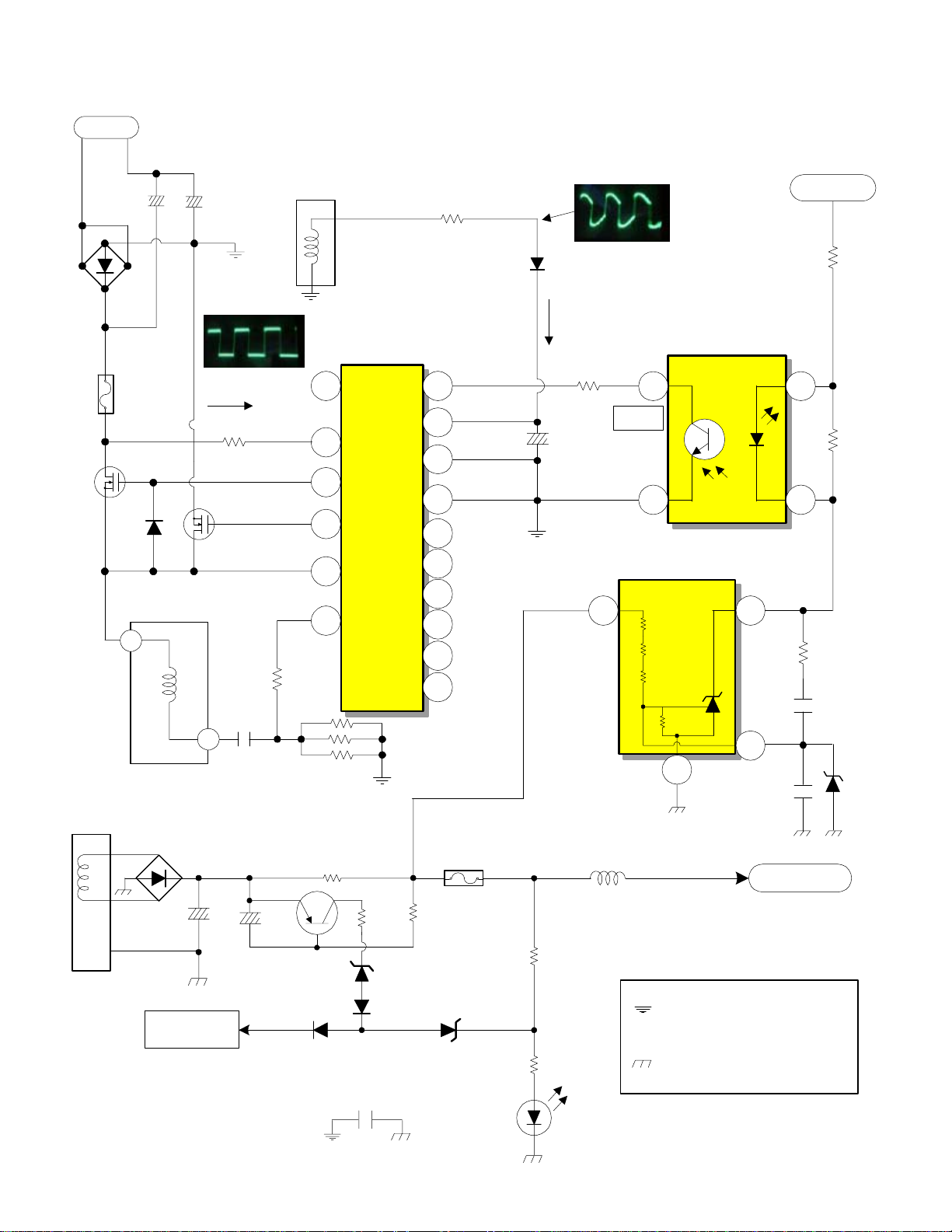

DP-4X POWER SUPPLY SW +115V REGULATION EXPLANATION

Hi-Voltage Power Supply Regulation Circuit Diagram explanation:

(See Power Supply SW+115V Regulation Circuit Diagram for details)

THIS POWER SUPPLY RUNS ONLY WHEN THE SET IS TURNED ON:

TURNING ON THE SW +115V POWER SUPPLY

RY102 AC Supply to the Deflection Power Supply Relay

When the set is turned on, the POWER DEF command is supplied from pin 58 of the Microprocessor I004.

(This high also turns on the Power LED on the front of the set). This high is sent to Q023 and Q024 then to the

PPS1 connector pin 11 labeled POWER 3. From here this high goes to the Deflection PWB through R125,

R122, D110 to the Base of Q102. The base goes high and the transistor turns on. This action supplies a ground

return for the coil inside RY102 and the relay turns on supplying AC to the connector PC2. Then to the Deflec-

tion Power Supply rectifier DP01 and the Deflection Power Supply begins to operate.

DP01 develops raw 300V via the doubler circuit comprised by CP03 and CP04. This voltage is routed through

FP01 to the Drain of QP01. A sample of this DC is routed through RP03 as Start Up voltage for IP01 at around

309V. From the Source of QP01 (when switched) the pulsed DC is routed to pin 9 of TP01. This voltage is

routed through the primary coil inside TP01 and out pins 7. One path from here is sent to pin 9 of IP01 which is

the Over Current Detection pin. The Ground return path for the primary voltage is routed through three 0.22 ohm

resistors R911, R912 and R913.

The Source of QP01 is also connected to the Drain of QP02. In this way, QP01 acts to connect raw B+ to the

primary of TP01 during the field build up period and QP02 acts as a ground switch during the collapse of the

primary field. QP01 gate control is via pin 16 of IP01.

After the Deflection Power Supply begins to operate, IP01 needs Run Voltage. This is accomplished by the pulse

from TP01 pin 5 being rectified by DP04, filtered by CP13 and the DC component arrives at pin 8 of IP01.

SW +115 REGULATION

SW +115V pulse is generated from pin 10 and 11 of T901. This pulse is rectified by DP34, filtered by CP45 and

then routed through the Excessive Current sensing circuit RP34 and QP05.

The primary route for the SW +115V is through EP02, LP37 and output as SW +115V to the Deflection and

High Voltage generation circuit.

However, the regulation route is to pin 1 of IP03. Internally, the regulator circuit works as a variable resistor

whose resistance is dependant upon the SW +115V voltage fluctuations. The internal variable resistor manipulates the current flow from pin 6 to pin 7 ground. This will cause the voltage at pin 2 of IP02 to be controlled.

Internally, the LED is illuminated by degrees dependant upon the SW +115V voltage fluctuations. The internal

receiver receives this light and acts as a variable resistor from pin 4 which is the regulation control signal to pin 3

hot ground.

This action causes pin 2 of IP01 to manipulate the internal oscillator within IP01. This in turn causes the timing

of the drive pulses delivered to the Gate of QP01 and QP02 SMOSFET (Switch Metal Oxide Semiconductor

Field Effect Transistor) to manipulate the frequency of the pulse generated on the primary of TP01. The current

drain of these SMOSFETs is monitored by three low ohm resistors mentioned above. If this current exceeds a

specific value, the voltage developed by these low ohm resistors is routed through RP14 ba ck into pin 9 of IP01

which is the Over Current Protection circuit. This pin will inhibit the drive signal to the ga te of the SMO SFETs.

As soon as the excessive current situation is eliminated, the IC will recover and continue functioning.

B+ GENERATION FOR THE POWER SUPPLY DRIVER IC:

Vcc for the Driver IC is first generated by the AC input. This voltage is called Start Up Voltage. IP01 requires

23.3V DC to operate normal. However, it will begin operation at a much smaller voltage on pin 18.

When AC is applied to the main full wave bridge rectifier DP01 where it is converted to Raw 300V DC voltage,

voltage doubler filter CP03 and CP04, routed through RP03 and made available to pin 18 of IP01 as start up

voltage. This voltage climbs to 300Vdc and the internal Regulator of IP01 is turned On and begins operation.

When the power supply begins to operate, the magnet field collapses and the EMF is coupled over to the secondary windings, as well as the drive windings. The drive windings at pin (5) produce a run voltage pulse of around

43 V p/p which is rectified by DP04, filtered by CP13 and becomes run voltage (20.3V) for IP01 pin 8.

: (See Relay Controls on previous page).

QP02 gate control is via pin 12 of IP01.

PAGE 01-17

Page 24

PPD3

AC

DP-4X CHASSIS POWER SUPPLY SW +115V REGULATION CIRCUIT DIAGRAM

Deflection Power Supply

From Relay RY102

13

AC Ground Side

-

CP03

4

-

3

2

+

1

+

CP04

+

-

Hot

Ground

DP01

FP01

Start Up

4Amp

RP03

D

QP01

G

S

DP02

S

D

G

QP02

TP01

9

TP01

5

3

Floating Ground

Pin 12, 14, 15, 16

All 58.5Khz

14

162V

309V

18

155V

16

4.87V

12

151V

15

0V

9

43.3Vp/p 42.5Vp/p

Primary

RP16

1 of 2

Run

1.83V

2

F/B

20.3V

8

Vc1

VD

P Gnd511

VG (H)

Gnd

VG (L)

VS

OCP

0V

0V

1 2.53V

3 2.27V

4

2.52V

6 4.46V

DP04

RP19

CP13

B+ 115V

58.5Khz

Regulator

Photocoupler

IP02

4

FB

3

IP03

1 6

7 19V

RP14

IP01

Driver IC

10

10.3V

SW +7V

RP30

1

RP31

2

RP32

CP47

7

CP07

Primary

2 of 2

TP01

11

10

CP45

DP34

QP05

15

Secondary

3 of 3

PROT_OVP

See PROT_OVP,

PROT_OCP Shut Down Diagram

R911, 12, 13

CP46

0.22 Ohm

RP34

0.39 Ohm

DP36

DP37

DP38

RP36

CP20

2 Amp

RP35

DP39

EP02

RP38

RP39

DP40

Regulator

LP37

Deflection

B+ 115V

5

7

CP48

0.85A

Hot Ground from pin 4 of

Bridge Rectifier DP01

Cold Ground from

pin 15 of TP01

DP35

SW +115V

PAGE 01-18

Page 25

V

4

DP-4X CHASSIS IP01 VOLTAGES AND WAVEFORMS

PAGE 01-18A

Pin

1 2.53V

2 1.83V

3 2.27V 2.76V P/P

4 2.52V

50V

6 4.46V

7 19V

8 20.3V

90V

10 10.39V

11 0V

12 4.87V 12.6V p/p 58.5Khz

13 0V

oltage Waveform

14 162V 314V p/p 58.5Khz

15 151V 308V p/p 58.5Khz

16 155V 317V p/p 58.5Khz

17 0V

18 309V

TP01

Pin 5 45.3V p/p 58.5Khz

Anode DP0

Anode 42.5V p/p 58.5Khz

Page 26

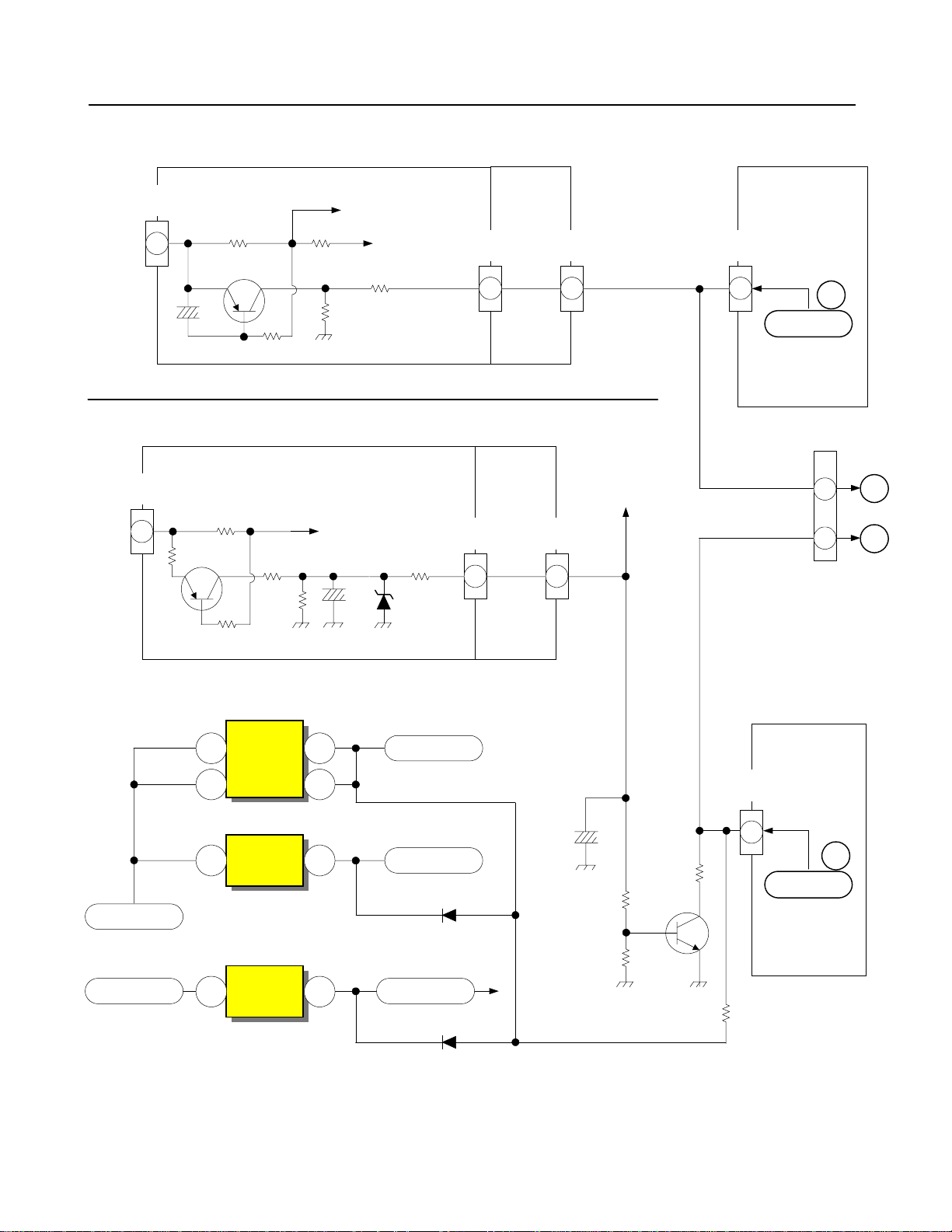

DP-4X SIGNAL POWER SUPPLY 5.7V REGULATION EXPLANATION

5.7V Power Supply Regulation Circuit Diagram explanation:

(See Signal Power Supply 5.7V Regulation Circuit Diagram for details)

THIS POWER SUPPLY RUNS ONLY WHEN THE POWER 1 COMMAND IS ACTIVE HIGH:

TURNING ON THE 5.7V POWER SUPPLY

directs AC to the Low Voltage Power Supply.

RY101

When the set is turned on, the

high is sent to

through

supplies a ground return for the coil inside

nal Power Supply rectifier

DS201

Q201

As the current draw across

IC201

until the over voltage condition disappears.

After the Signal Power Supply begins to operate,

from

5.7V REGULATION

5.7V pulse is generated from on the secondary of

C229

The primary route for the

However, the regulation route is to the cathode of

whose resistance is dependant upon the

flow from pin 2 of

tuations which causes the resistance of

variable resistor from pin 4 to pin 3, which is the regulation control signal to pin 2 labeled as

This action causes pin 2 of

ing of the drive pulses delivered to the Gate of

fect Transistor) to manipulate the frequency of the pulse generated on the primary of

these SMOSFETs is monitored by the low ohm resistor

value, the voltage developed by this low ohm resistor is routed through

the Over Current Protection circuit. This pin will inhibit the drive signal to the gate of the SMOSFETs. As soon

as the excessive current situation is eliminated, the IC will recover and continue functioning.

B+ GENERATION FOR THE POWER SUPPLY DRIVER IC201:

Vcc for the Driver IC is first generated by the AC input. This voltage is called

23.3V

When AC is applied to the main full wave bridge rectifier

filtered by

up voltage. When this voltage reaches 12Vdc, the internal Regulator of

When the power supply begins to operate, the magnet field collapses and the EMF is coupled over to the secondary windings, as well as the drive windings. One drive winding produces a run voltage pulse which is rectified

by

R110

develops raw 150V which is routed through

(when switched) the primary of

which is the Over Current Detection pin. If this voltage goes too high, the power supply will shut down

which is rectified by

T201

.

DC to operate normal. However, it will begin operation at a much smaller voltage on pin 6.

C201

, filtered by

D204

and

Q018

and then

PC201

and

C202

C206

POWER SIG

then to the

Q021

to the Base of

D109

and the Signal Power Supply begins to operate.

DS201

T201

rises and falls due to the load, the developed DC Voltage is sent to pin 3 of

R204

, filtered by

D204

is through

5.7V

5.7V

. Internally, the LED is illuminated by degrees dependant upon the

IC203

to manipulate the internal oscillator within

IC201

, routed through

and becomes run voltage (

(See Power On/Off Circuit Diagram).

:

command is supplied from pin 59 of the Microprocessor

connector pin 9 labeled

PPS1

. The base goes high and the transistor turns on. This action

Q101

and the relay turns on supplying AC through

RY101

primary to the Drain of

T201

is grounded through a 0.1 low ohm resistors

gate control is via pin 5 of

Q201

needs

IC201

and the DC component arrives at pin 6 of

C206

. This pulse is rectified by

T201

and output as

L204

. This regulator circuit works as a variable resistor

IC203

voltage fluctuations. This variable resistor manipulates the current

to fluctuate. The internal receiver receives this light and acts as a

SMOSFET (Switch Metal Oxide Semiconductor Field Ef-

Q201

R204

R202, R203

and

23.3V

I004

POWER 1

Run Voltage

DM 5.6V

mentioned above. If this current exceeds a specific

where it is converted to Raw 150V DC voltage,

DS201

and made available to pin 6 of

R210

) for

IC201

. This is accomplished by the pulse

to the Digital Module.

R213

IC201

pin 6.

. From here this high goes

to the Sig-

F102

. From the Source of

Q201

.

R204

.

IC201

.

IC201

, filtered by

D210

. This in turn causes the tim-

IC201

. The current drain of

T201

back into pin 3 of

Start Up Voltage

is turned On and begins operation.

voltage fluc-

5.7V

.

F/B

IC201

.

IC201

IC201

C228

which is

requires

as start

. This

and

PAGE 01-19

Page 27

DP-4X CHASSIS SIGNAL POWER SUPPLY 5.7V REGULATION CIRCUIT DIAGRAM

AC

Relay RY101

AC

Gnd

Side

-

F102

6 Amp

-

C202

Hot

C203

+

-

C201

+

Ground

Start Up

R209

C208

+

DS201

R208 R210

T201

6

1

Primary

1 of 2

IC201

Vcc

CS

F/B

Gnd

Out

FB202

2

4

5

D204

Run

R207

C206

T201

C212

D210

C228

FB

4

3

DM 5.6V

5.7V

C229

PC201

Regulator

Photocoupler

L204

R223

R225

1

R222

2

R226

R203

T201

Primary

2 of 2

C214

R213

D201

D202

3

OCP

D

S

C211

Q201

G

R204

0.1 Ohm

D203

R205

R206

ZD201

R224

C234

IC203

Regulator

R227

Hot Ground from pin 4 of

Bridge Rectifier DP01

Cold Ground from

pin 15 of TP01

PAGE 01-20

Page 28

DP-4X LED (Visual Trouble Detection) CIRCUIT EXPLANATION

This explains the LEDs used in the Deflection Power Supply used for Visual Trouble Shooting Circuit Diagram explanation:

(See the LED (Visual Troubleshooting) for the Deflection Power Supply Diagram on the next page for details)

2 GREEN LEDS

In the DP-4X chassis, there are 2 Green LEDs that can be used for Visual Trouble shooting. The Service Technician can use these LEDs to determine if the set is experiencing a problem within these two Power Supplies..

The LEDs can be used in the following ways.

OFF:

If the LED is off, then the power supply that is being monitored is unavailable. (Excluding the possibility that the LED itself is malfunctioning). NOTE: If

condition because of its current flow explained below.

If the LED turns on but then quickly goes off before the others, then the power supply that is being

monitored can be suspected.

ON:

If the LED is on, then the power supply that is being monitored is working normal. (There is the possibility that the power supply being monitored may in fact be present but low. If after making visual inspection and all seems OK, but there’s still a problem, be sure to check the accuracy of the power supply

in question.

GREEN LEDs DP50 and DP40.

DP50 (SW + & - 28V)

• Monitors the SW +28V output from

• Note: This LED requires the SW –28V power supply to be functioning to operate. Current flow for light-

ing DP50 is from the SW+28V through RP46, DP50, RP47 to the SW-28V. If the LED opens, or the

negative SW –28V is missing, this LED will not illuminate. If the SW –28V is missing, the set will shut

down.

DP40 (SW +115V)

• Monitors the

• This power supply is used for Deflection and High Voltage generation.

NOTE: Both of the Green LEDs are also involved in the Shut Down Circuit.

•

DP50

cause the zener to fire and supply a high through

(See the Deflection Power Supply Shutdown Output Diagram Explanation Page 01-08 for details).

•

DP40

turn are connected to the

the zener will fire and supply a high to the

(See the Deflection Power Supply Shutdown Output Diagram Explanation Page 01-08 for details).

There are additional components in the Shut Down circuit that are not shown in this diagram. Please see the Deflection Power Supply Shutdown Output Diagram Explanation Page 01-08 for details.

LED opens, then the set will be in shut down

DP40

pin 16 and rectifier

TP01

SW +115V

supplies

supplies the Ground return path for the Voltage divider comprised of

SW+28V

output from

to the Cathode of

SW +115V

pins 10 and 11. Rectified by

TP01

if the negative

DP46

to the

DP47

deflection B+. If the voltage on the cathode of

PROT_OVP

shut down Circuit.

. Filtered by

DP30

DP34

SW-28V

PROT_OVP

is missing. This action will

and

CP32

, filtered by

shut down Circuit.

and

RP38

DP39

CP34

CP45

. These in

RP39

goes too high,

.

.

PAGE 01-21

Page 29

TP01

DP-4X CHASSIS

L.E.D. (Visual Troubleshooting) for the Deflection Power Supply

2 Total L.E.D. for visual trouble sensing observation.

+28V

-28V

16

15

14

10

11

11

DP30

CP30

CP32

CP33

DP31

CP31

LP30

+

+

2

3

+

+

LP31

+115V

DP34

14

QP05

CP45

CP46

CP34

CP35

LP33

RP46

DP50

RP47

+115V Over

Current

RP34

0.39 Ohm

GREEN L.E.D.

SW-28V Loss Detection

RP35

+ & - SW 28V Active (LED)

DP46 DP47

LP34

See the Deflection Power Supply Shut

EP02

2 Amp

RP38

DP39

1.26A

0.65A

PROT_OVP

Down Circuit Diagram for details.

LP37

RP39

0.85A

+115V Over

Voltage

SW+ 28V

SW -28V

SW + 115V

SW +115V Active (LED)

DP40

GREEN L.E.D.

There are additional components within the Shut Down Circuit not shown here.

Please see the Deflection Power Supply Shut Down Output Circuit Diagram on Page 01-09 for details.

PAGE 01-22

Page 30

DP-4X BLANK PAGE “NOTES”

BLANK PAGE

Page 31

MICROPROCESSOR

INFORMATION

DP-4X

CHASSIS INFORMATION

SECTION 2

Page 32

DP-4X BLANK PAGE “NOTES”

BLANK PAGE

Page 33

DP-4X MICROPROCESSOR DATA COMMUNICATIONS CIRCUIT EXPLANATION

Microprocessor Data Communications circuit diagram.

(See DP-4X Microprocessor Data Communications Circuit Diagram for Details)

The Microprocessor

circuits. Some of the circuits must return information as well so the Microprocessor will know how to respond to

different request.

The Microprocessor uses two types of communication for control, I

lines . The I

2

C communication scheme only requires 2 lines for control. These lines are called SDA and SCL.

Serial Data and Serial Clock respectively.

Also, due to the fact that this Microprocessor operates at 3.3Vdc, it requires a Level Shift IC to bring the DC

level of the control lines up to make it compatible with the connected components. The Level Shift IC also brings

the DC levels down as outside circuits communicate with the microprocessor.

The Microprocessor communicates with the following ICs:

ON THE TUNER PWB:

•

U301 Main Tuner

•

U302 PinP Tuner

ON THE SIGNAL PWB:

•

UD2003 Digital Module

•

UY01 Flex Converter

•

I007 and I011 EEPROM

•

I009 Level Shift

•

IA01 Audio Control

•

IV01 A/V Selector

•

IV02 3D Y/C

•

IV08 1H Main Video Chroma

•

IV12 1H Sub Video Chroma Selector

•

IY04 Rainforest (RGB Processor)

•

I501 Sub Y Pr/Pb Selector

•

I502 Main Y Pr/Pb Selector

•

I401 Audio Selector

•

I402 Video Selector

ON THE SUB DEFLECTION PWB:

•

IB01 Vertical Drive

The following explanation will deal with the communication paths used between the Microprocessor and the respected ICs.

ON THE TUNER PWB:

U301 Main Tuner (with MTS outputs) and U302 Sub Tuner (mono Audio Output).

The Microprocessor

SCL2

and

lines for the Tuners are output from the Microprocessor

SDA2

respectively. These line s go through the c onnector

(5) and

at pin (4). These lines control band switching, programmable divider set-up information, pulse

SCL2

swallow tuning selection, etc...

must keep in communication with the Chassis to maintain control over the individual

I004

2

C Bus and the Serial Data, Clock and Load

(ATSC Tuner)

controls the Tuners by

I004

SDA2

PTU1

(Data) and

SCL2

(Clock) I

I004

pins (10 and 9) then directly to the Tuners,

2

C communication lines.

at pins (

31 SDA2 and 28 SCL2

SDA2

at pin

)

(Continued on page 2)

PAGE 02-01

Page 34

DP-4X MICROPROCESSOR DATA COMMUNICATIONS CIRCUIT EXPLANATION

ON THE SIGNAL PWB:

UD2003 Digital Tuner (ATSC Tuner) Not in the DP-43 Chassis.

The Microprocessor

•

DM RTS

•

DM CTS

pin (22) of the

•

DM TXD

and pin (24) of the

•

DM RXD

pin (23) of the

I007 EEPROM

The EEPROM is ROM for many different functions of the Microprocessor

Customer set ups for Video, Audio, Surround etc… Also, some of the Microprocessors internal sub routines have

variables that are stored in the EEPROM, such as the window for Closed Caption detection. Communication is

Data and Clock lines,

(39) of the Microprocessor to pin (6) of the

Note: In this chassis, if the EEPROM is removed or defective, the Microprocessor will LOCK the picture. No

functions other that the front Power Button will work. LOCK will appear on the screen, but the customer’s menu

can not be accessed.

I011 EEPROM

The EEPROM is ROM for the IR Blaster

remote control interaction with the Customer’s Menu. The External device remote codes are stored in the

EEPROM. When the Customer’s Remote for the TV activates the on screen selections in the Customer’s Menu,

these control codes are translated in the IR Blaster chip to the appropriate code for the external device. Communication is Data and Clock lines,

from pin (39) of the Microprocessor to pin (6) of the

SCL3

UY01 Flex Converter FC04

The projection television is capable of receiving NTSC as well as ATSC (SDTV) and HD (High Definition). The

Flex Converter is responsible for receiving any video input and converting it to 33.75 Khz output (2.14H). This

output is controlled by sync and by the customer’s screen format and how it is set up. The set up can be 4X3 with

grey side panels, Smooth Wide, Fill or Full and even 4X3 with Black Side panels. 16X9 for SDTV. This set will

automatically bypasses the Flex Converter completely and inputs the 1080i signal directly to the Rainforest IC

. This happens when a true 1080i signal or Antenna C is selected. The Flex Converter can take any NTSC,

IY04

S-In, Component, NTSC or any of the 18 formats of ATSC except 1080i which doesn’t route through the Flex

converter. Control for the Flex Converter is Clock, Data and Enable lines. The

must be routed through t he Level Shift IC

• The Clock line for the Flex Converter is output from the Microprocessor at pin (

at pins (

I009

• The Data line for the Flex Converter is output from the Microprocessor at pin (

at pins (

I009

• The Enable line for the Flex Converter is output from the Microprocessor at pin (

input to

Data from the Flex Converter is also sent back to the Microprocessor. Data from the Flex is sent out of the

connector pin (11) to pin (5) of

processor

I004.

I009

3 Clock

4 Data

at pins (

controls the Digital Tuner via communication lines. They are listed below;

I004

(Digital Module Receive Transmission) from pin (21) of

(Digital Module Serial Clock) this bi-directional signal is connected via pin (20) of

connector.

PMS1

(Digital Module Transmission Data) this bi-directional signal is connected via pin (4) of

connector.

PMS1

(Digital Module Receive Data) this bi-directional signal is connected via pin (3) of

connector.

PMS1

from pin (40) of the Microprocessor to pin (5) of the

SDA3

SDA3

) and is output at pins (17) then through the

) and is output at pins (16) then through the

2 Enable

I007

EEPROM

. The Customer’s Menu allows control of external equipment via

I012

from pin (40) of the Microprocessor to pin (5) of the

to be brought up to 5V which the Flex needs.

I009

) and is output at pins (18) then through the

, level shifted down to 3.3V and output at pin (15) into pin (51) of the Micro-

. Data travels in both directions on the Data line.

EEPROM

I004

.

connector pin 10

PFC1

connector pin 11

PFC1

connector to pin (27) of

PMS1

I004

I004

. Channel Scan or Memory List,

EEPROM

Clock, Data and Enable

53 Clock

52 Data

PFC1

and

SCL3

EEPROM

). Clock is input to

). Data is input to

54 FCENABLE

connector pin (12).

). Enable is

(Continued on page 3)

I004

and

I004

to

from pin

and

lines

PFC1

.

PAGE 02-02

Page 35

DP-4X MICROPROCESSOR DATA COMMUNICATIONS CIRCUIT EXPLANATION

I009 Level Shift

The Microprocessor

5Vdc. The Level Shift IC steps up the DC voltage to accommodate. This IC isn’t controlled by the Microprocessor, however it is in direct contact with Data transmission and is included in the communication circuit.

• Pin (17) outputs a 5V Clock signal, used by the Flex Converter

• Pin (18) outputs a 5V Enable signal, use d by the Flex Converter

• Pin (16) outputs a 5V Data signal, used by the Flex Converter.

• Pin (15) outputs a 3.3V Data, sent from the Flex Converter

IA01 BBE Audio Control (Surround)

This chassis utilizes BBE Surround.

Communica tion from the Microprocessor via pi ns (

(13 and 14) respectively.

IV02 3D Y/C

(IC mounted directly on the Terminal PWB).

The 3D Y/C IC is a Luminance/Chrominance separator, as well as a 3D adder. Separation takes place digitally.

Using advanced separation technology, this circuit separates usi ng multiple lines and doesn’t produce dot pattern

interference or dot crawl. The 3D effect is a process of adding additional emphasis signals to the Luminance and

Chrominance. These signals relate specifically to transitions. Transitions are the point where the signal goes from

dark to light or vice versa. The 3D adds a little more black before the transition goes to white and a little more

white just before it gets to white. It also adds a little more white just before it goes dark and a little more dark just

before it arrives. This gives the impression that the signal pops out of the screen or a 3D effect.

The Microprocessor communicates with the 3D Y/C IC via I

from the Microprocessor

tively.

The Microprocessor also is able to turn on and off circuits within the 3D Y/C circuit determined by customer’s

menu set-up.

IV08 1H Main Video Chroma

This IC is responsible for receiving the Main NTSC (1H) signal in separated format, (Y and C) and converting it

to a usable signal for the rest of the circuits. (Y Cr/Cb). Communication from the Microprocessor via pins (

and

SDA1

29 SCL1

IV12 1H Sub Video Chroma

This IC is responsible for receiving the Sub (PinP) NTSC (1H) signal in separated format, (Y and C) and converting it to a usable signal for the rest of the circuits. (Y Cr/Cb). Communication from the Microprocessor via pins

(

30 SDA1

and

29 SCL1

IY04 Rainforest (RGB Video/Chroma Processor)

The Video Processing IC (Rainforest) is responsible for controlling video/chroma processing before the signal is

made available to the CRTs. Some of the emphasis circuits are controlled by the customer’s menu. As well as

some of them being controlled by AI, (Artificial Intelligence).

Communication from the Microprocessor

(28 and 30) respectively.

operates at 3.3Vdc. Most of the Circuits controlled by the Microprocessor operate at

I004

) to

are pins (

I004

pins (34 and 33) respectively.

IV08

) to

IV08

30 SDA1