Page 1

June 2005

(ver n) Training Materials Prepared by: ALVIE RODGERS C.E.T.

HITACHI

PROJECTION

TELEVISION

http://www.hitachiserviceusa.com

2003

MODEL RELEASE

DIGITAL HD READY PTV

Model No Chassis

46W500 DP33W 2

51S700 DP36

57S700 DP36

65S700 DP36

51S500 DP37 3

57S500 DP37 3

65S500 DP37 3

57T500 DP37C

65T500 DP37C

57X500 DP37D

65X500 DP37D

1

Includes built in ATSC/QUAM tuner

2

Includes built in DVD Player

3

Includes built in Photo Card Reader

1,3

1,3

1,3

CONTENTS... 2003 DP-3X Chassis Projection Television Information

Materials Prepared by… Alvie Rodgers C.E.T. (Chamblee, GA.)

Page 2

DP-3X BLANK PAGE “NOTES”

BLANK PAGE

Page 3

June 2005

SECTION (1) POWER SUPPLY DIAGRAMS:

•

•

•

•

•

•

•

•

•

•

SECTION (2) MICROPROCESSOR INFORMATION:

•

•

•

•

•

•

SECTION (3) VIDEO CIRCUIT INFORMATION:

•

•

•

•

•

•

•

•

•

•

•

(ver n)

TOPICS PAGE

(Visual Trouble Shooting) Stand By Power S upply Circuit Diagram Explained -------

LEDs

(Visual Trouble Sh ooting) Stand By Po wer Supply Ci rcuit Diagram --------------------

LEDs

(Visual Trouble Shooting) Deflection Power Supply Circuit Diagram Explained -----

LEDs

(Visual Trouble Shooting) Defl ection Power Supply Circuit Diagram -------------------

LEDs

Power Supply Shut Down

Power Supply Shut Down

Protect (Deflection) Hi Volt Shut Down

Prot_CPT and PROT_SW Shut Down

SW +115V Hi Voltage Regulation

SW +115V Hi Voltage Regulation

Microprocessor

Microprocessor

Audio Video Mute

Audio Video Mute

Microprocessor

Microprocessor

Video NTSC

Video NTSC

Component Video

Component Video

Rainforest IC Pulse

Circuit Diagram Explanation

ABL

Circuit Diagram

ABL

Component Sync

Component Sync

ATSC (Digital Tuner)

Input Circuit Diagram

DVI

•

Audio Video Mute

•

Audio Video Mute

DP-3X TABLE OF CONTENTS

Circuit Diagram Expl ained -------------------------------------------Circuit Diagram ---------------------------------------------------------

Circuit Diagram ----------------------------------------Circuit Diagram Expl ained ---------------------------------Circuit Diagram -----------------------------------------------

DATA COMMUNICATION

DATA COMMUNICATION

Circuit Diagram Explanation

Circuit Diagram

NTSC Sync Input

NTSC Sync Input

Circuit Diagram Explained

Circuit Diagram

and

NTSC Continued

and

NTSC Continued

Explanation Explained

---------------------------------------------------------------------------------- 03-09

Circuit Diagram E xplanation ----------------------------------------------------Circuit Diagram ---------------------------------------------------------------------

Block Diagram

---------------------------------------------------------------------------- 03-13

Circuit Diagram Explanation (See Microprocessor Section)

Circuit Diagram (See Microprocessor Section)

----------------------------------------------------------------- 02-08

Circuit Diagram Explained

Circuit Diagram

----------------------------------------------------------- 03-01

Circuit Diagram

------------------------------------------------------------------- 03-08

DP-36 and DP-38 Only

Materials prepared by

Alvie Rodgers C.E.T.

01-01

01-02

01-03

01-04

01-05

01-10

Circuit Di agram and Explanation -------------------

Explanation

Circuit Diagram

------------------------------------------------- 02-06

Circuit Diagram

------------------------------------------------------ 03-03

Circuit Di agram Explanation ----------------------Circuit Diagram

-------------------------------------------------------- 03-07

------------------------------------- 02-01

------------------------------------ 02-05

--------------------------------- 02-09

----------------------------- 02-10

---------------------------------------

-------------------------------------- 03-12

--------

-----------------------

01-11

01-12

01-13

01-14

03-04

03-06

03-10

03-11

02-06

02-07

Continued on Next Page

Table of Contents Page 1 of 3

Page 4

June 2005

(ver n)

DP-3X TABLE OF CONTENTS

TOPICS PAGE

Materials prepared by

Alvie Rodgers C.E.T.

SECTION (4) AUDIO CIRCUIT INFORMATION:

Audio

•

•

•

•

SECTION (5) DEFLECTION CIRCUIT:

•

•

•

•

•

•

•

•

•

SECTION (6) DIGITAL CONVERGENCE CIRCUIT INFORMATION:

•

•

•

•

•

•

•

•

•

SECTION (7) ADJUSTMENT INFORMATION:

Only information that differs for the DP-2X (previous chassis) are included.

•

•

•

•

•

•

•

•

•

•

•

•

•

Main Terminal Circuit Diagram Explanation

Audio

Main Terminal Circuit Diagram

Main / Sub Audio

Main / Sub Audio

Horizontal Drive

Horizontal Drive

IH01 Horizontal Drive IC

Sweep Loss

Sweep Loss

Vertical Output

Vertical Output

Pincushion Circuit

Pincushion Circuit

Digital Convergence Interco nn ect

Digital Convergence Interco nn ect

Remote CLU5728TSI

Remote CLU5727TSI

Remote CLU5725TSI

46" Overlay

51" Overlay

57" Overlay

65" Overlay

DCU Crosshatch Phase Settings --------------------------------------------------------------------------------- 07-01

Off-Set for Red and Blue Raster Position

Vertical Size

Horizontal Size

DCU Character Set-Up

DCU Pattern (Sensor Position) Set-Up

Read from ROM Notes -------------------------------------------------------------------------------------------- 07-07

Remote CLU5728TSI

Remote CLU5727TSI

Remote CLU5725TSI

Adjusting Digital Convergence

Magic Focus

Magnet Locations --------------------------------------------------------------------------------------------------- 07-13

Overlay

•

Selection Circuit Diagram Explanation

Selection Circuit Diagram

Circuit Diagram Explanation

Circuit Diagram

Voltages and Waveforms (Also, Not Running Info.)

Detection Circuit Diagram Explanation

Detection Circuit Diagram

Circuit Diagram Explanation

Circuit Diagram

Diagram

Diagram

Dimensions

Dimensions

Dimensions

Dimensions

Adjustment

Adjustment

Error Codes

Dimensions (See Digital Convergence Section)

--------------------------------------------------------------------------------------- 05-09

--------------------------------------------------------------------------------------- 05-10

(Digital Convergence Mode Functions) DP-37

(Digital Convergence Mode Functions) DP-33W

(Digital Convergence Mode Functions) DP-37C and DP-37D

------------------------------------------------------------------------------------------- 06-09

------------------------------------------------------------------------------------------- 06-10

------------------------------------------------------------------------------------------- 06-11

------------------------------------------------------------------------------------------- 06-12

------------------------------------------------------------------------------------------- 07-03

--------------------------------------------------------------------------------------- 07-04

DCU Data Confirmation

and

(Digital Convergence Mode Functions) DP-37

(Digital Convergence Mode Functions) DP-33W

(Digital Convergence Mode Functions) DP-37C and DP-37D

------------------------------------------------------------------------------------------ 07-12

--------------------------------------------------------------------------- 04-02

-------------------------------------------------------------------------------- 05-03

--------------------------------------------------------------------------- 05-06

---------------------------------------------------------------------------------- 05-08

Circuit Diagram Explanation

Circuit Diagram

Adjustment

Using an External Sign al

----------------------------------------------------------- 04-01

--------------------------------------------------- 04-03

------------------------------------------------------------------- 04-04

---------------------------------------------------------------- 05-01

------------------------- 05-04

----------------------------------------------------------- 05-05

------------------------------------------------------------------ 05-07

------------------------------------------- 06-01

---------------------------------------------------------- 06-05

------------------------------------- 06-06

---------------------------------- 06-07

------------------- 06-08

Adjustment

------------------------------------------------------ 07-02

Adjustment

---------------------------------------------------------- 07-06

--------------------------------------------------- 07-11

--------------------------------------- 07-05

------------------------------------- 07-08

---------------------------------- 07-09

------------------- 07-10

--------------------------------------- 06-09 ~06-12

Continued on Next Page

Table of Contents Page 2 of 3

Page 5

June 2005

Use Contents on the Left Hand Side to Navigate to Topics

as this section can change often.

Or Go to the page after the Section 10 Things You Should

Know Section Divider for an Index.

SECTION (8) MISCELLANEOUS IN FOR MATI O N:

•

•

•

•

•

•

•

•

•

•

SECTION (9) DP-33W DVD TROUBLESHOOTING:

•

•

•

•

•

•

•

•

•

•

DVD PLAYER TROUBLESHOOTING PICTURES:

•

•

•

•

•

•

•

•

SECTION (10) THINGS YOUR SHOULD KNOW: ----------------------------------- 10-01

(ver n)

TOPICS PAGE

Signal PWB

Deflection PWB

Power Supply PWB

CRT PWBs

Front Control PWBs

Rear Panel

Rear Panel

Rear Panel

Rear Panel

Rear Panel

No DVD Player Picture ------------------------------------------------------------------------------ 09-01

No DVD Player Analog Audio ---------------------------------------------------------------------- 09-02

No DVD Player Digital Audio ---------------------------------------------------------------------- 09-03

DVD Player Power Supply Check ----------------------------------------------------------------- 09-04

DVD Player Control Check ------------------------------------------------------------------------- 09-05

DVD Player Audio / Video Check ------------------------------------------------------------------ 09-06

DVD Player Interface Block Diagram ------------------------------------------------------------ 09-07

DVD Player Video Signal Diagram ---------------------------------------------------------------- 09-08

DP-33W Microprocessor Data Communication Signal Diagram --------------------------- 09-09

DVD Player Audio Signal Path Signal Diagram ------------------------------------------------ 09-10

DVD Player Front View and Plastic Cover ------------------------------------------------------ 09-11

DVD Player Control Panel Removal and Plastic Cover Removal --------------------------- 09-12

DVD Player Removal and Dropped Down But Still Connected ----------------------------- 09-13

DVD Player Removed and Top View ------------------------------------------------------------- 09-14

DVD Player Top Screws Removal and Ribbon Cables Identified --------------------------- 09-15

Separation DVD Player From Power Supply PWB -------------------------------------------- 09-16

DVD Player Separated From Power Supply PWB --------------------------------------------- 09-17

Power Supply PWB Troubleshooting Layout --------------------------------------------------- 09-18

DP-3X TABLE OF CONTENTS

Drawing

Drawing

DP-36 (Terminal Input) Drawing (S700 Models)

DP-37 (Terminal Input) Drawing (S500 Models)

DP-37C (Terminal Input) Drawing (T500 Models)

DP-37D (Terminal Input) Drawing (X500 Models)

DP-33W (Terminal Input) Drawing (W750 Models)

--------------------------------------------------------------------------------- 08-01

Drawing

---------------------------------------------------------------------------- 08-02

Drawing

---------------------------------------------------------------------------------- 08-04

Drawing

----------------------------------------------------------------------- 08-03

---------------------------------------------------------------------- 08-05

------------------------------------ 08-06

----------------------------------- 08-07

--------------------------------- 08-08

-------------------------------- 08-09

------------------------------- 08-10

Materials prepared by

Alvie Rodgers C.E.T.

Table of Contents Page 3 of 3

Page 6

DP-3X BLANK PAGE “NOTES”

BLANK PAGE

Page 7

POWER SUPPLY

INFORMATION

DP-3X

CHASSIS INFORMATION

SECTION 1

Page 8

DP-3X BLANK PAGE “NOTES”

BLANK PAGE

Page 9

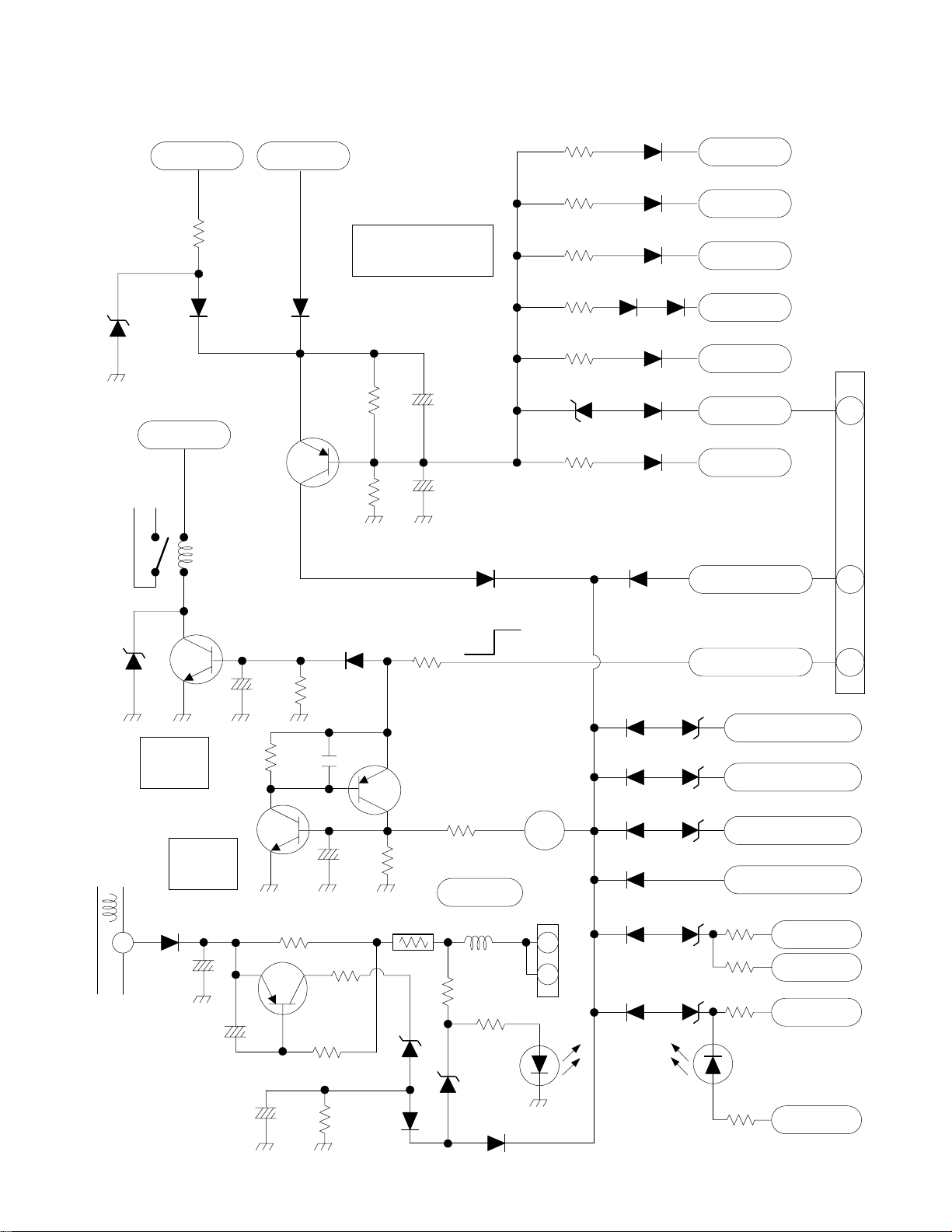

DP-3X LED (Visual Trouble Detection) CIRCUIT EXPLANATION

STAND BY POWER SUPPLY

This explains the LED used for Visual Trouble Shooting Circuit Diagram explanation:

(See DP-3X LED (Visual Trouble Detection) Diodes for Stand By Power Supply Diagram for details)

1 GREEN

In the DP-3X chassis, there is 1 Green LED in the Stand By power supply.

Use this LED to determine if the set is experiencing a problem.

The LEDs can be used in the following ways.

OFF:

• If the LED is off, then the power supply that is being monitored is unavailable. (Excluding the possibility

that the LED itself is malfunctioning).

• If the LED turns on but then quickly goes off, then the power supply that is being monitored can be sus-

pected.

ON:

• If the LED is on, then the power supply that is being monitored is working normal. (There is the possibility

that the power supply being monitored may in fact be present but low. If after making visual inspection and

all seems OK, but there’s still a problem, be sure to check the accuracy of the power supply in question.

GREEN LED D913.

D913 (Stand By +5V)

• Monitors the

• This is a new IC in the DP-3X chassis. It is a self contained DC-DC converter that provides the Stand

By +5V which keeps the necessary circuits alive when the set is turned off. Such as the Microprocessor,

etc…..

Stand By +5V

output from

U901

pin 1.

PAGE 01-01

Page 10

DP-3X CHASSIS

L.E.D. (Visual Troubleshooting) for the Stand By Power Supply

(1 Green L.E.D. for visual trouble sensing observation)

U901

Stand By

DC-DC

Converter

L924

9

C919

8

C918

GREEN

L.E.D.

C922

D913

PPS5

10

4 Gnd

5

6

7

Gnd

Gnd

Gnd

D913 illuminates when the Stand By +5V is available.

SBY + 5V

PAGE 01-02

Page 11

DP-3X LED (Visual Trouble Detection) CIRCUIT EXPLANATION

This explains the LEDs used in t he Def lect ion Power Supply used for Visual Trouble Shooting Circuit Diagram explanation:

(See DP-3X LED (Visual Troubleshooting) for the Deflection Power Supply Diagram for details)

5 LEDS, 4 GREEN AND 1 RED

In the DP-3X chassis, there are 5 total LEDs that can be used for Visual Trouble shooting. 4 Green and 1 Red.

Use these LEDs to determine if the set is experiencing a problem.

The LEDs can be used in the following ways.

OFF:

If the LED is off, then the power supply that is being monitored is unavailable. (Excluding the possibility that the LED itself is malfunctioning). NOTE: If

condition because of it’s current flow explained below.

If the LED turns on but then quickly goes off before the others, then the power supply that is being

monitored can be suspected.

ON:

If the LED is on, then the power supply that is being monitored is working normal. (There is the possibility that the power supply being monitored may in fact be present but low. If after making visual inspection and all seems OK, but there’s still a problem, be sure to check the accuracy of the power supply

in question.

RED LED D912

is used to monitor the Start Up and Run voltage for the Driver IC

D912

lowing voltages.

• Audio SW +30V

• SW +10V

• +220V

• SW+28V

• SW -28V

• SW +115V

The LED

GREEN LEDs D956, D955, D954 and D932.

D956 (Audio +30V)

D955 (SW +5.5V)

D954 (SW +28V)

D932 (SW +115V)

D912

• Monitors the

• Monitors the

D922

• Monitors the SW +28V output from

• Note: Th is LED requires the SW –28V power supply to be functioning to operated. If the LED opens, or

the negative SW –28V is missing, this LED will not illuminate. If the SW –28V is missing, the set will

shut down.

• Monitors the

• This power supply is used for Deflection and High Voltage generation.

is attached to pin 4 of

Audio +30V

SW +5.5V

cathode.

SW +115V

generated by the SW +5.5V regulator

. If the voltage is missing, the LED will not light.

I901

output from

output from

pin 18 and rectifier

T901

pin 15 and rectifier

T901

pin 11 and rectifier

T901

LED opens, then the set will be in shut down

D932

. This IC is used to generate the fol-

I901

cathode.

D919

I905

D922

D925

pin 1 from

cathode.

cathode.

pin 15 and rectifier

T901

PAGE 01-03

Page 12

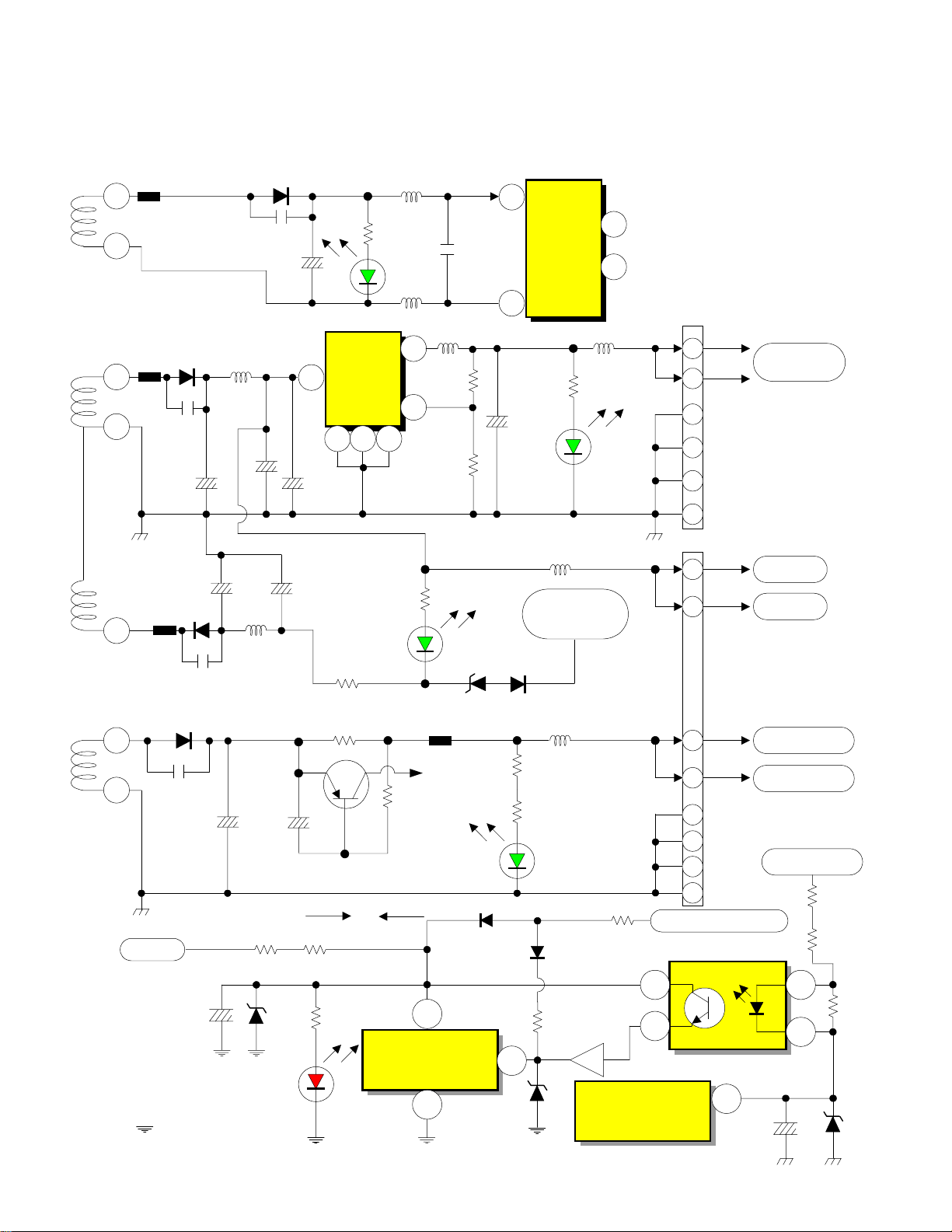

DP-3X CHASSIS

L.E.D. (Visual Troubleshooting) for the Main Power Supply

(5 Total L.E.D. for visual trouble sensing observation, 4 Green and 1 Red)

T901

T901

18

17

28V

15

13

-28V

14

E901

E904

E905

D922

C932

C933

C940

D923

C939

L918

L920

D919

C924

C925

1.77A

C934

3

C935

C941

GREEN

L.E.D.

R931

I905

SW+5.5V

Reg

2

5 8

R964

D954

R965

L909

C926

D956

L910

1

6

1.59A

L914

R932

R933

GREEN L.E.D.

D952 D953

9

10

R934

C936

GREEN

L.E.D.

IAA1

Ft. Audio

Out

L919

See Shut

Down Circuit

L915

D955

Right Audio

7

Left Audio

12

2.28A

1.00A

PPS5

8

9

3 Gnd

4 Gnd

5 Gnd

7 Gnd

PPD5

1

2

SW + 5.5V

SW+ 28V

SW+ 28V

+115V D925

T901

11

12

C942

C943

Osc B+

AC

From

Relay

S901

C911

RED L.E.D.

Hot Ground from

pin 9 of T901

Q905

C949

D912

R944 0.39 Ohm

Start Up

R907R906

D911

R918

E907

+115V

Over

Current

R946

D932

Run

16.3V

D907

4

I901

Driver/Output IC

5

R914

1

D910

L923

R952

R953

GREEN L.E.D.

D908

Q901

115V Regulator

0.85A

R913

I904

9

10

3

Gnd

4

Gnd

5

Gnd

6

Gnd

From Pin 8 T901

7.5P/P

4

3

Regulator Photocoupler

I906

2

SW + 115V

SW + 115V

SW + 115V

C946

R940

R941

1

R942

2

D927

PAGE 01-04

Page 13

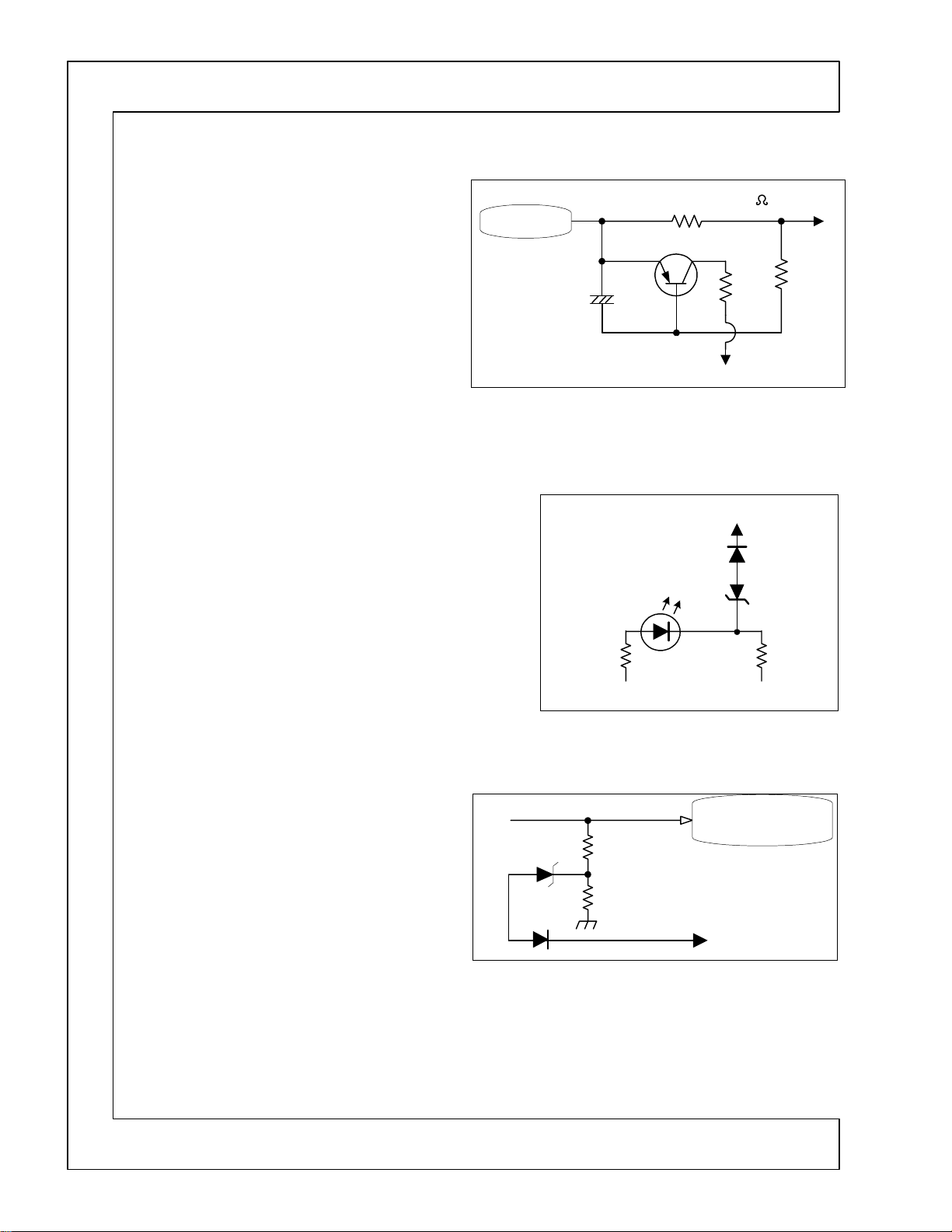

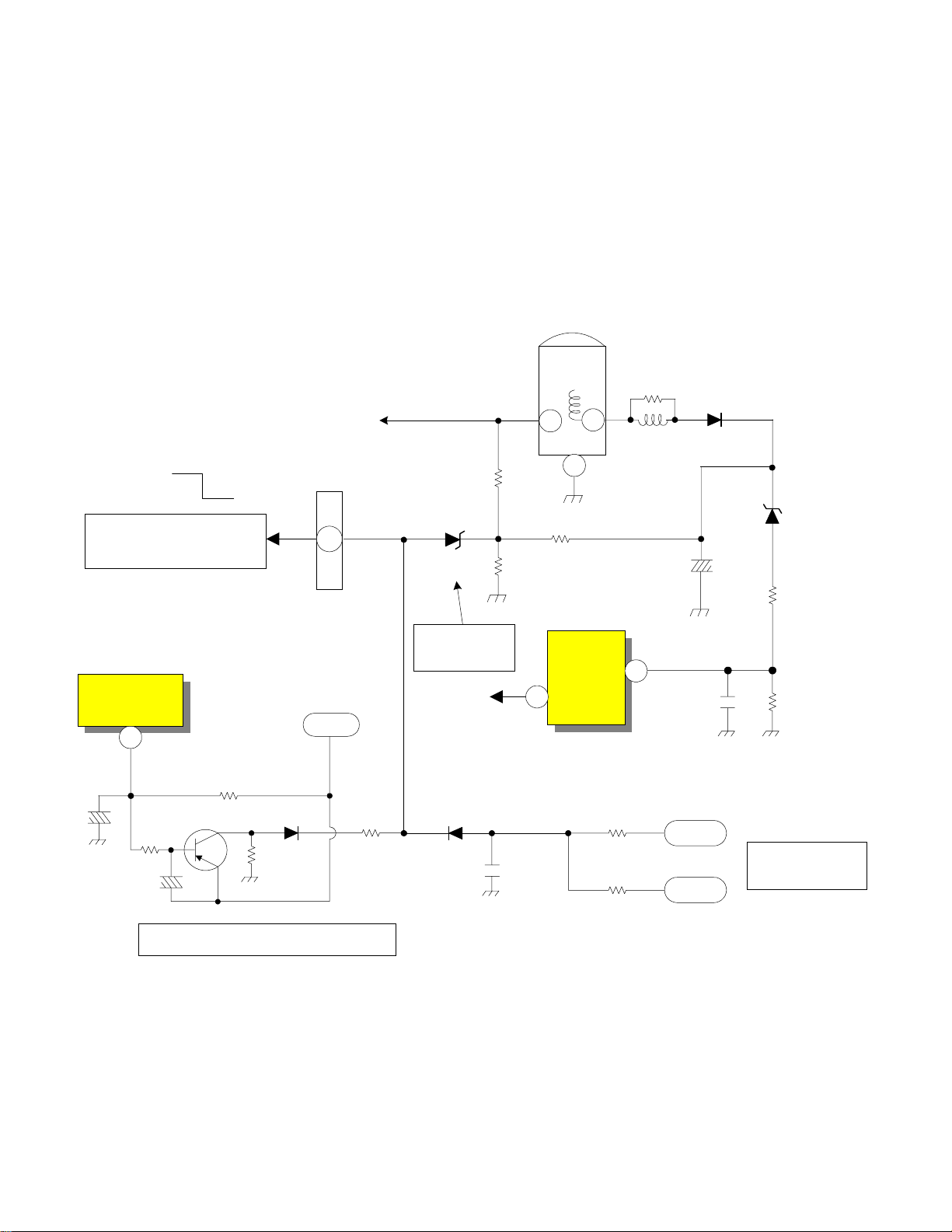

DP-3X POWER SUPPLY SHUT DOWN EXPLANATION

GENERIC SHUT DOWN C IRCUITS EXPLAINED:

The following circuits are commonly used in Hitachi product and relate to the drawing on page 01-10:

SW +115V EXCESSIVE CURRENT DETECTION

(See Figure 1)

One very common circuit used in many Hitachi television products is the B+

circuit. In this circuit is a low ohm resistor

series with the SW +115V. The value of this resistor

is

0.39 ohm

voltage drop across the resistor increases. If the voltage drop is sufficient to reduce the voltage on the

base of

Shutdown signal that is directed to the appropriate

circuit indicated on the drawing on page 01-10 as

point

NEGATIVE VOLTAGE LOSS DETECTION

(See Figure 2)

The purpose of the Negative Voltage Loss detection circuit is to

compare the negative voltage with its’ counter part positive voltage. If at any time, the negative voltage drops or disappears, the

circuit will produce a Shutdown signal.

In Figure 2, there are two resistors of equal value, (15K). One to

the positive voltage SW +28V and one to the negative voltage

SW –28V. At their tie point, (neutral point), the voltage is effectually zero (0) volts. If however, the negative voltage is lost, the

neutral point will go positive. This in turn will cause the zener

diode

and on to the appropriate circuit indicated on the drawing on

page 01-10 as point

Note: The LED

nated by the current draw from +28V to the –28V supply.

VOLTAGE TOO HIGH DETECTION

(See Figure 3)

Another circuit used is the

circuit. In the example shown in Figure 3, the

tion

zener diode

R952

the voltage at the divider center point will rise as well

and trigger or fire the zener diode which produces a

Shutdown sig na l through

ate circuit indicated on the drawing on page 01-10 as

point

. When the current demand increases, the

, the transistor will conduct, producing a

Q905

.

(A)

to fire, cre ating a Shutdown Signal through

D952

D954

D931

and

(A)

. If the voltage source rises to o high,

R953

.

Excessive Current Sensing

in

R944

.

(A)

used for visual trouble shooting is illumi-

Voltage Too High Detec-

is connecte d to a voltage divider

and on to the appropri-

D930

SW+115V

D953

C949

Voltage Loss

R964

15K

D931

D930

Detector

SW +28V

R952

R953

R944

0.39

Current Sensor

Q905

Shut-Down Signal

Figure 1

Shut-Down Signal

D954

Figure 2

High Detector

Figure 3

R946

R947

D953

D952

R965

15K

SW -28V

SW +115V

Voltage Too

Shut-Down

Signal

Base

Bias

(Continued on page 6)

PAGE 01-05

Page 14

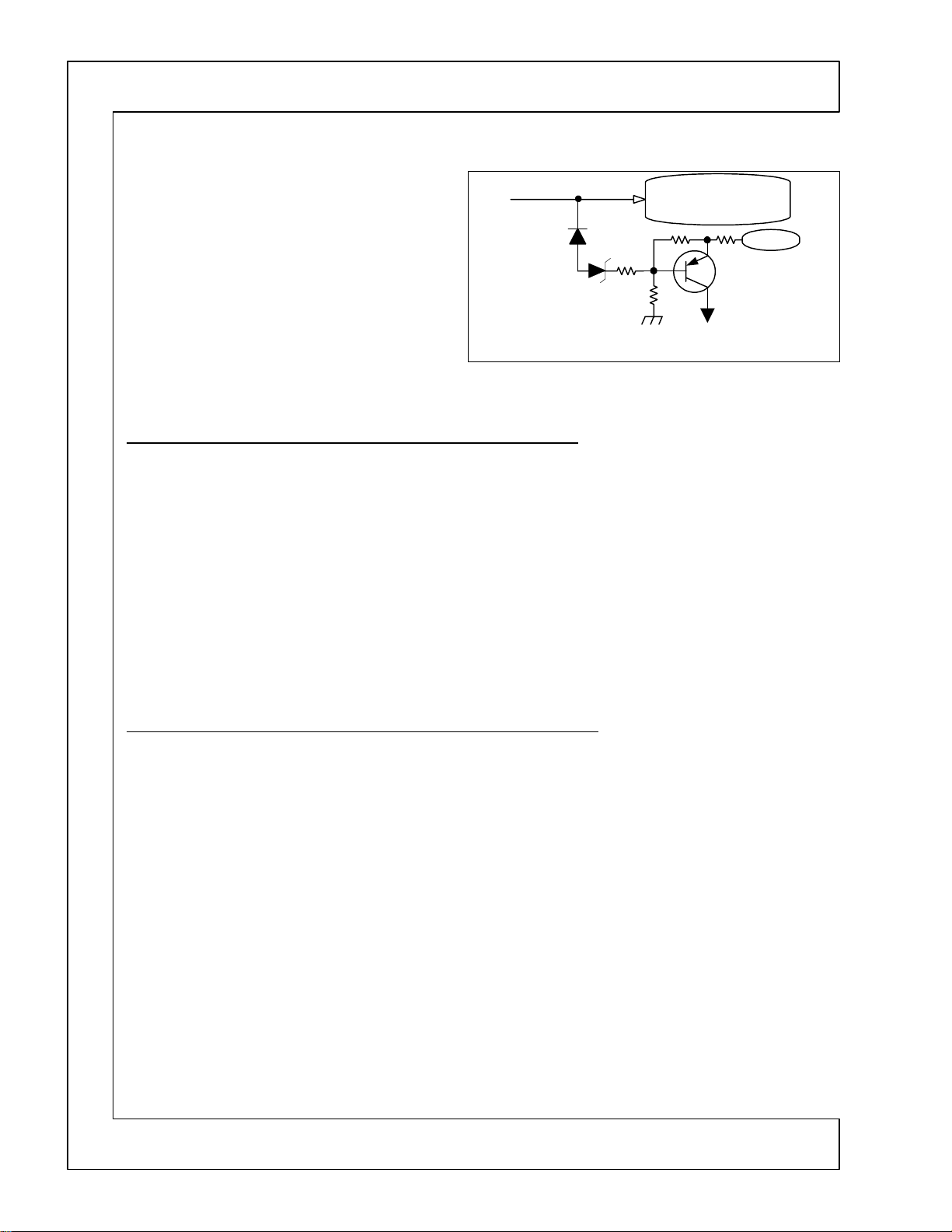

DP-3X POWER SUPPLY SHUT DOWN EXPLANATION

VOLTAGE LOSS or SHORT DETECTION

(See Figure 4)

One circuit used is the

Voltage Loss Detection

cuit. This is a very simple circuit that detects a loss

of a particular power supply and supplies a PullDown path for the base of a PNP transistor.

This circuit consist of a diode connected by its

cathode to a positive B+ power supply. Under normal conditions, the diode is reversed biases, which

cir-

Voltage

Loss

Detector

Any Positive

B+ Supply

B+

Q1

keeps the base of Q1 pulled up, forcing it OFF.

However, if there is a short or excessive load on the

B+ line that’s being monitored, the diode in effect

will have a L OW on its cat hode, turning it ON. This

Figure 4

Shut-Down Signal

will allow a current path for the base bias of Q1,

which will turn it ON and generates a Shutdown

Signal.

B+ GENERATION FOR THE MAIN POWER SUPPLY DRIVER IC I901:

Vcc for the Driver IC is first generated by the AC input. This voltage is called Start Up Voltage.

23.3V

. However, it will begin operation at

routed through the main fuse

radiation for radiating back into the AC power line. After passing

AC is routed through the relay

150V DC voltage to be supplied to the power supply switching transformer

However, one leg of the AC is routed to

D911

Zener

tor of

When the power supply begins to operate by turning on and off the internal Switch MOS FET, the Raw 150V DC routed

through

out of pin (2) through four low ohm resistors (

FET turns on, it causes the transformer to saturate building up the magnet field. When the internal Switch MOS FET turns off,

the magnet field collapses and the EMF is coupled over to the secondary windings, as well as the drive windings. The drive

windings at pin (8) produce a run voltage pulse which is rectified by

and now becomes run voltage (

HOT GROUND SIDE SHUT DOWN SENSING CIRCUITS. (Specific to I901).

In addition, there are 4 Hot Ground side Shutdown inputs that are specifically detected by the main power driver IC

These sensors circuits protect

LATCHED SHUT DOWN MONITORS:

1. (OVP)

2. (TSD)

3. (Trigger) Over Load Protection monitors the difference between the Hot Ground and Floating Ground.

RECOVERING SHUT DOWN INPUT:

4. (OCP)

and made available to pin (4) of

I901

is turned On and it begins to operate.

T901

, in on pin 3 (Drain) and out on pin 2 which is the Source. The Sou r ce of the internal Switch MOS FET is routed

Pin 4

is monitored for Over Voltage Protection at pin 4 of

I901

itself is monitored for Excessive Heat. This block is labeled TSD. (Thermal Sensing Device).

Pin 1

monitors the low ohm resistors,

condition caused by monitoring the current through the internal Switch MOS FET, the voltage will rise and pin 1 has an

internal Over Voltage detection op-amp. If this voltage rises enough to trigger this op-amp, the IC will stop producing a

drive signal.

F901

(a 10 Amp fuse), then through the Line filter

S901

23.3V

I901

from excessive current, temperature or over voltage.

12V

on pin (4) of

and AC arrives at the main full wave bridge rectifier

R906

I901

) for

(AC must be removed to recover).

(Driver IC will recover on it’s own when trouble is removed.)

R907

and

I901

as start up voltage. When this volt age reaches 13Vd c, the internal Regu la-

R908, R909, R910 and R911

pin 4.

R908, R909, R910

I901

. When the s et is tu rned on by

L901

(both a 3.9K ohm resistor), filtered by

D907

I901

and

I901

normal pin 4 voltage is

S901

, AC is applied. AC is

L901

to prevent any internal high frequency

filter it passes another filter

D901

T901

pins (1 and 2).

) to hot ground. When the internal Switch MOS

, filtered by

.

R911

C911

. If these resistors have an excessive curren t

L903

. The HOT leg of

where it is converted to Raw

C911

, clamped by a 36V

then routed clamped by

D911

I901

.

(Continued on page 7)

PAGE 01-06

Page 15

DP-3X POWER SUPPLY SHUT DOWN EXPLANATION

The next explanation discusses the Cold Ground side shut down circuit operation.

This explains the Pow er Supply Shut Down Circuit Diagram:

See DP-3X Power Supply Shut Down Diagram for details

Use this explanation and Diagram in conjunction with the following diagrams;

DP-3X Deflection Protect Power Supply Shut Down Circuit Diagram and

DP-3X PROT_CPT and PROT_SW Shut Down Circuit Diagram.

The Power supply is centered around the Switching Transformer

This power supply creates voltages that are Switched on when the Set is turned on.

1. Audio SW +30V 2. SW +10V

3. +220V 4. SW+28V

5. SW -28V 6. SW +115V

Other supplies are generated from these 6 main voltages.

Q904 Relay Inhibit Activation. (SHUT DOWN) called COMMON ACTION CIRCUIT.

All Shut Down events will cause the main power relay to turn off. This action will stop all secondary power suppli es.

The Low Voltage power supply (S tand-By) continues to operate.

If any of the 23 shut down circuits activate, the base of

High from

prevents

SOME SHUTDOWN CIRCUITS ARE DEFEATED IN STANDBY MODE. (Set Off).

When the set is turned off or in Stand By, 12 of the shut down inputs are not active.

These shut down circuits are d efeated because the SW (Switched) power supplies are turned off in standby. So to prevent

faults triggering of the shutdown circuit, the sensing circuits are turned off also..

Q906

voltage to operated. Emitter voltage is supplied from the

to function. When the set is turned off these switched voltages disappear, so

COLD GROUND SIDE SHUT DOWN INPUTS EXPLAINED

GENERAL INFORMATION

All of the Power Supply Shutdown circuitry can be broken down into the following categories;

PPS4

connector pin 7 called

Q904

from turning off is the shut down signal disappears after shutdown.

Shorted

•

monitored by

Shorted

•

Shorted

•

Shorted

•

Shorted

•

Prot_SW

•

1. SW +2.2V 2. SW +3.3V

3. SW +5V 4. SW +9V

5. SW +9.3V 6. Blue CRT VM 220V excessive current sensing circuit.

Shorted

•

supplies the high for shutdown if any of the shut down circuit attached to its base become low.

Voltage Missing Detection or Short Detection or Negative Voltage Loss Detection

•

Voltage Too High Detection

•

Excessive Current Detection

•

SW+35V

SW+10V

SW+5.5V

220V

SW+6.3V

(6 shut down inputs) This voltage is monitored by

SW+28V

(from voltage divider

D938

.

(from pin 16 of

(from pin 1 of

(from pin 10 of

(from pin 1 of

(from pin 15 of

Power_1

T901

I905

T901

) This voltage is monitored by

I906

T901

(See previous pages for generic circuit details)

Q904

and the main power supply will STOP.

R940

). This voltage is monitored by

) This voltage is monitored by

) This voltage is monitored by

) This voltage is monitored by

SW +6.3V

T901

and the driver IC,

will go High. This turns on

R941

and

off the SW+115V from pin 11 of

D944

SW +10V

and

I901.

Q903

and removes the Power On

Q903

operates as a “latch”. This

T901

D939

.

D940

.

D941

.

Q906

D942

and

D943

D943

line. This voltage must be active for

can no longer operate.

:

.

.

.

Q906

). This voltage is

requires emitter

Q906

(Continued on page 8)

PAGE 01-07

Page 16

DP-3X POWER SUPPLY SHUT DOWN EXPLANATION

COLD GROUND SIDE SHUT DOWN SENSING CIRCUITS.

Looking at the base of

SHUT DOWN CIRCUITS:

There are a total of 23 individual Shutdown inputs to the Relay Inhibit transistor

will be described later. However, there are some that are routed to the Power Supply from external circuits not shown on the

Power Supply Shut Down circuit diagram.

There are a total of 3 individual Shutdown inputs from the Deflection PWB via

•

ing diode

Vertical Output I601 Excessive Current Detection

1.

-5V Loss Detection

2.

Excessive High Voltage Detection

3.

There is 1 Shutdown input from the

•

QE08

VM Protect,

Power PWB via

sive current on the Red CRT PWB. (See PROT_CPT & PROT_SW Shut Down Circuit Diagram).

There are 6 individual Shutdown input from the

•

•

•

All of the Cold Ground side Shutdown detection circuits can be categorized by the previously described shut down circuits

which were discussed in the Generic Shut Down Circuits Explanation section.

In the following explanation, the Shutdown circuits will be grouped. This will assist the Service Technician with trouble

shooting the Chassis, by understanding these circuits and having the associated circuit routs, the technician can then

and Conquer”

Voltage Loss (or Short) Detection

signal to a (Hi) then throu gh

On the Signal PWB 2 of 3

PROT-SW

Prot_CPT & Prot_SW Shut Down Circuit Diagram)

Shorted SW+2.2V (

•

Shorted SW+3.3V (

•

Shorted SW+5V (

•

Shorted SW+9V monitored by

•

Shorted SW+9.3V monitored by

•

Q904

the shut down events are triggered by the following.

D951

. (See Deflection Protect Power Supply Shut Down Circuit Diagram).

Protect_CPT

on the Red CRT PWB. From the Red CRT PWB to the Green CRT PWB via

Green CRT PWB to Signal PWB via

PPS4

connector pin 6 called

1

of these inputs is from

EGB1

via

pin 2 called

From

PWB via

CRT PWB.

5

of these inputs are monitoring for a shorted B+ line. These circuits are on the Signal PWB 2 of 3. The y moni-

tor the following;

.

All routed through

connector pin 8 called

Gain.Cont

Q554

collector to the

PPS4

connector pin 5. This signal would be low if the +220V draws excessive current on the Blue

1. SW +2.2V from

2. SW +3.3V from

3. SW +9V monitored by

4. SW +9.3V monitored by

5. SW +5V from

(See PROT_CPT & PROT_SW Shut Down Circuit Diagram).

D933

I404

I403

I402

QEA8

on th the Blue CRT PWB. From the Blue CRT PWB to the Green CRT PWB

. From the

PPS4

I404

pin 4.

I403

pin 3 monitored by

D404.

D403.

I402

pin 3 monitored by

All short detections signals active (Lo). Routed to the base of Q906 which inverts the

to the base of

PPS4

pin 5 to

pin 4) monitored by

pin 3) monitored by

pin 3) monitored by

D404

D403

Protect_CPT

Protect_SW

Gain.Cont

PSC

connector pin 2 to the base of

connector pin

Q904,

Common Action Circuit.

D944

R420

D402

D401

(AC must be removed to recover).

Q904

. Many of these are discrete circuits and

Protect_Def

circuit routed through steering diode

PSC

connector pin 3 called

. This signal would be high if the +220V draws exces-

circuit monitored by

. From the Green CRT PWB to Signal PWB via

5

now called

D402.

D401.

on Power PWB. Labeled

Protect_SW

VM Protect

D944.

Q554

which inverts this High to a Low.

. From the Signal PWB to Power

PROT-SW

routed through steer-

D959

. This input is from

ERG1

connector pin 7 called

, from Signal PWB to

PSC

on the Schematic. (See

connector

“Divide

(Continued on page 9)

PAGE 01-08

Page 17

DP-3X POWER SUPPLY SHUT DOWN EXPLANATION

On the Power PWB

SW –7V Voltage Loss Detectio n

•

lost, the positive

SW –28V Voltage Loss Detection

•

lost, the positive

In the Deflection Circuit

–5V Voltage Loss Detection

•

DK90.

bias

connector pin 6 to

Voltage Too High Detect ion

Action Circuit. (See DP-3X Power Supply Shut-Down Circuit Diagram for details)

On the Power PWB.

SW +115V Voltage Too High Detection

•

Audio Ground

•

tored by

SW +10V Voltage Too High Detection

•

SW +5.5V Voltage Too High Detection

•

From, the Deflection circuit output called Protect_Def.

DH14 High Voltage Too High Sensing Circuit.

•

ing the pulse from the flyback

This high will be routed to pin 6 of

ate a high that will be routed through the

Circuit Diagram for details)

At the same time, the zener diode

•

Horizontal Drive for High Voltage and this IC will shut off, turning off High Voltage drive pulses.

Excessive Current Detection

On the Power PWB.

SW +115V Excessive Current Detection

•

tion/High Voltage Circuit draws too much current,

voltage of

routed to

relay.

In the Deflection Circuit on the Power/Deflection PWB.

Q604 Vertical Circuit Ex cessive Current Se nsing Circuit.

•

tical Output IC. If the IC draws too much current,

voltage of

routed through

erate a high that will be routed through the

Down Circuit Diagram for details)

On the CRT PWB PROT_CPT.

On the RED CRT PWB +220V Excessive Current Detection

•

current, the base voltage of

ERG1

pin 7,

On the BLUE CRT PWB VM+220V Excessive Current Detection

•

too much current, the base voltage of

through

lector goes low. This low is routed to the PPS4

base of Q906 low turning it on causing shut down.

EGB1

+6.3V

will forward bias

+28V

will forward bias

Any abnormality seen in the deflection circuit will generate a high that will be routed through the

D951.

(See DP-3X Deflection Protect Shut-Down Circuit Diagram for details)

All voltage too high detections circuits are active (Hi) and routed to the base of

If the Audio Output IC

D960

and routed through

(See DP-3X Power Supply Shut-Down Circuit Diagram for details)

Q905

to fall turning on this transistor. When this happens, it’s collector will go high. This high will be

D928

causing it to fire. This high will be routed through

Q604

to fall turning on this transistor. When this happens, it’s collector will go high. This high will be

D608

and to pin 6 of

(See PROT_CPT & PROT_SW Shut Down Circuit Diagram).

PSC

pin 8,

pin 3,

PSC

PPS4

pin 2, to the base of

Monitored by

D949

Monitored by

D952

Monitored by

Monitored by

IAA1

D961.

Monitored by

Monitored by

TH01

pin 5. If the voltage at the cathode of

PPD4

to

PPD4

DH14

PPD4

QE08

will fall turning it on. The collector will go high. This high will go through

pin 6 to

D959

QEA8

D949

and routed through

and it will fire causing shut down.

D952

and routed through

and it will fire causing shut down.

DK90

. In this circuit, if the

D931

and routed through

has an internal short, the Audio ground will go positive. This is Moni-

D957

and routed through

D947

and routed through

This circuit monitors the

Protect_Def

connector pin 6 to

will fire and this high will be routed to pin 7 of

Monitored by

Protect_Def

to

PPD4

.

will fall turning it on. The collector will go high. This high will go

Q554

. Any abnormality seen in the deflection circuit will gener-

D951.

Q905

R927

will develop a larger voltage drop. This will cause the base

R629

will develop a larger voltage drop. This will cause the base

. Any abnormality seen in the deflection circuit will gen-

connector pin 6 to

on the Signal PWB. This h igh turns on

pin 5 to the cathode of

D928

and

D930

This circuit monitors the

Monitored by

D950

. In this circuit, if the

D953

. In this circuit, if the

–5V

is lost, the positive

D930

.

D958

.

D948

.

High Voltage

DH15

goes too high, this zener will fire.

(See DP-3X Deflection Protect Shut-Down

and routed through

and to the base of

D951.

(See DP-3X Deflection Protect Shu t-

RE35

Monitored by

D944

causing D945 to fire and pull the

line generated by rectify-

D930.

Q904

+28V

line going to

220V

. If the

REF1

. If the

Q554B and it’s col -

SW –7V

SW –28V

+5V

will forward

Q904,

Common

IH01

. This is the

If the Deflec-

shutting off the

I601

draws too much

VM220V

PPD4

draws

is

is

Ver-

PAGE 01-09

Page 18

DP-3X MAIN POWER SUPPLY SHUT DOWN DIAGRAM

D938R958

SW +6.3VSW +10V

D939R959

SW +35V

SW +10V

D934

6V

SBY +5V

AC

R957

S901

Q902

Q906

SHORT

DETECTION

D936D935

R954 C951

Active Lo

R956 C952

12

D918

R929

D933

D940R960

SW +5.5V

D942R961

D941

+220V

D943R962

SW +6.3V

D944D945

Prot_SW

D946R963

PPS4

6

5

SW +28V

D959

Protect_CPT

Power On/Off

onoff

Power_1

1

6

7

T901

11

D917

Relay

Driver

D925

C943

C921

Relay

Inhibit

C949

R948

Q904

C950

R927

R944

R951

C947

C948

R947

Q905

R946

D928

D929

Q903

R949

E907

R950

SW+115

L923

R952

R953

D931

23

Point

A

PPD5

9

10

D932

D961 D960

D958 D957

D948 D947

D951

D950 D949

D953 D952

Audio Gnd

SW +10V

SW +5.5V

3

Protect_Def

R937

+6.3V

R939

SW -7V

R965

SW -28V

D954

R964

SW +28V

D930

PAGE 01-10

Page 19

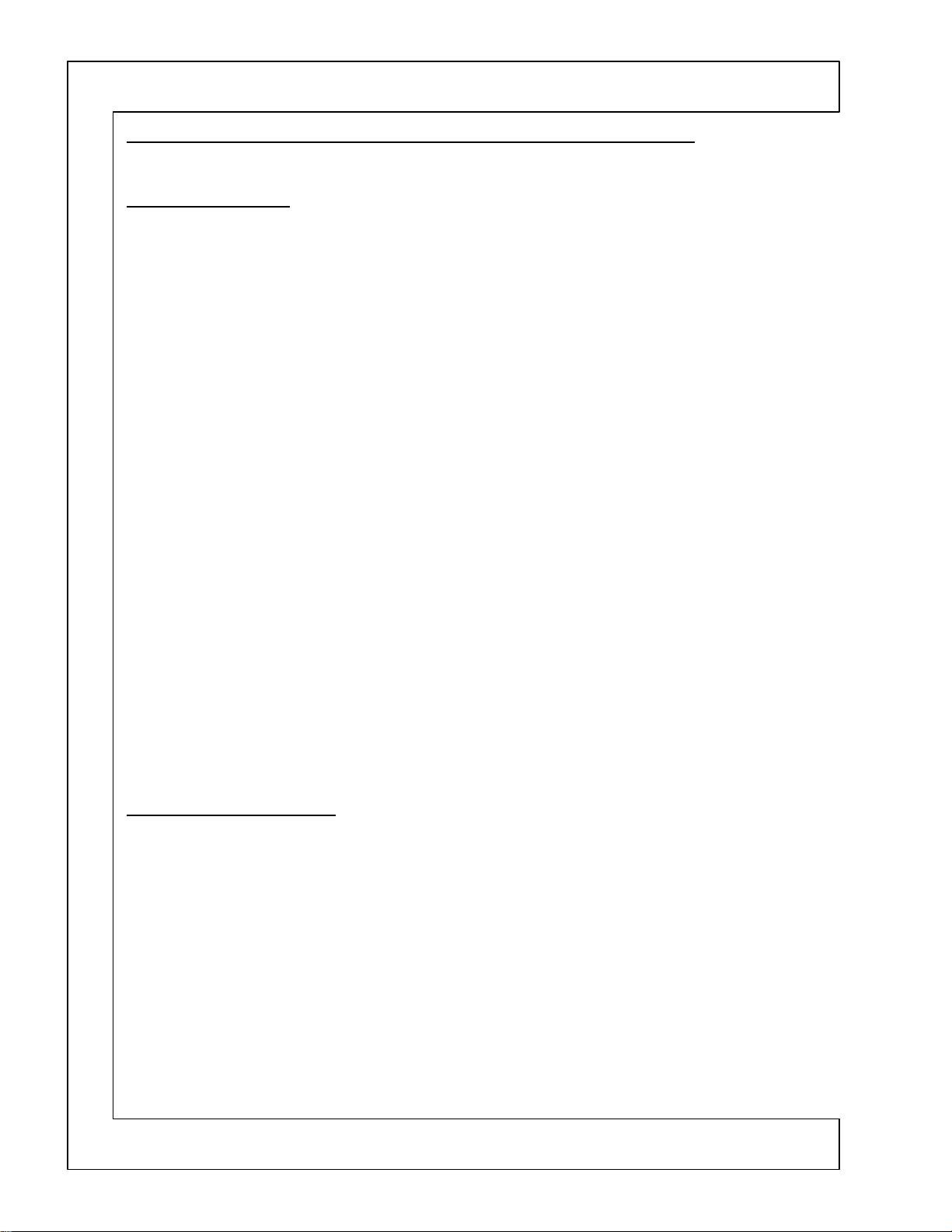

DP-3X DEFLECTION PROTECT POWER SUPPLY SHUTDOWN DIAGRAM

Any fluctuations in High Voltage will also be

reflected by the 50P output P/P.

By monitoring the 50P (50 Pulse) rises in High Voltage

will be sensed. If High Voltage climbs too high, DH15

will fire and trigger a shut down event.

DH14 will fire and stop High Voltage Horz. Drive

Flyback

RH32 allows ABL fluctuations to manipulate the Trigger

Point of Shut Down as screen brightness varies.

ABL is inverse proportionate to brightness.

This prevents false Shut Down triggering.

ABL

Active

Normal

PPD4

RH32

TH01

3

5

5OP

4

High Voltage

Sensing Circuit

RH23

LH06

DH13

PROTECT _DEF

See Power Supply Shut Down

Circuit Diagram for continuation.

Vertical Output Circuit

I601

10

R629

C604

0.68 Ohm

Q604

R630

C610

Excessive Vertical Current Det.

R631

D608

6

28V

R632

29.01V

RH24

1

RH25

Hi Volt

H. Drive

IH01

OVP

H. Drive

DH15

Excessive Hi

Voltage Det.

DK90 Monitors the -5V and +5V lines going to the DCU.

If the -5V line is loss, the +5V line provides the Shut Down Hi.

CH17

Stops H. Drive

7

CH10 RH09

RK98

DH14

RH26

+5V

DK90

CK90

RK97

-5V Loss Det.

-5V

If the Vertical Output IC has a problem, R629

will sense the current rise. The voltage drop will

be reflected at the base of Q604 turning it on

and producing a Shut Down high.

PAGE 01-11

Page 20

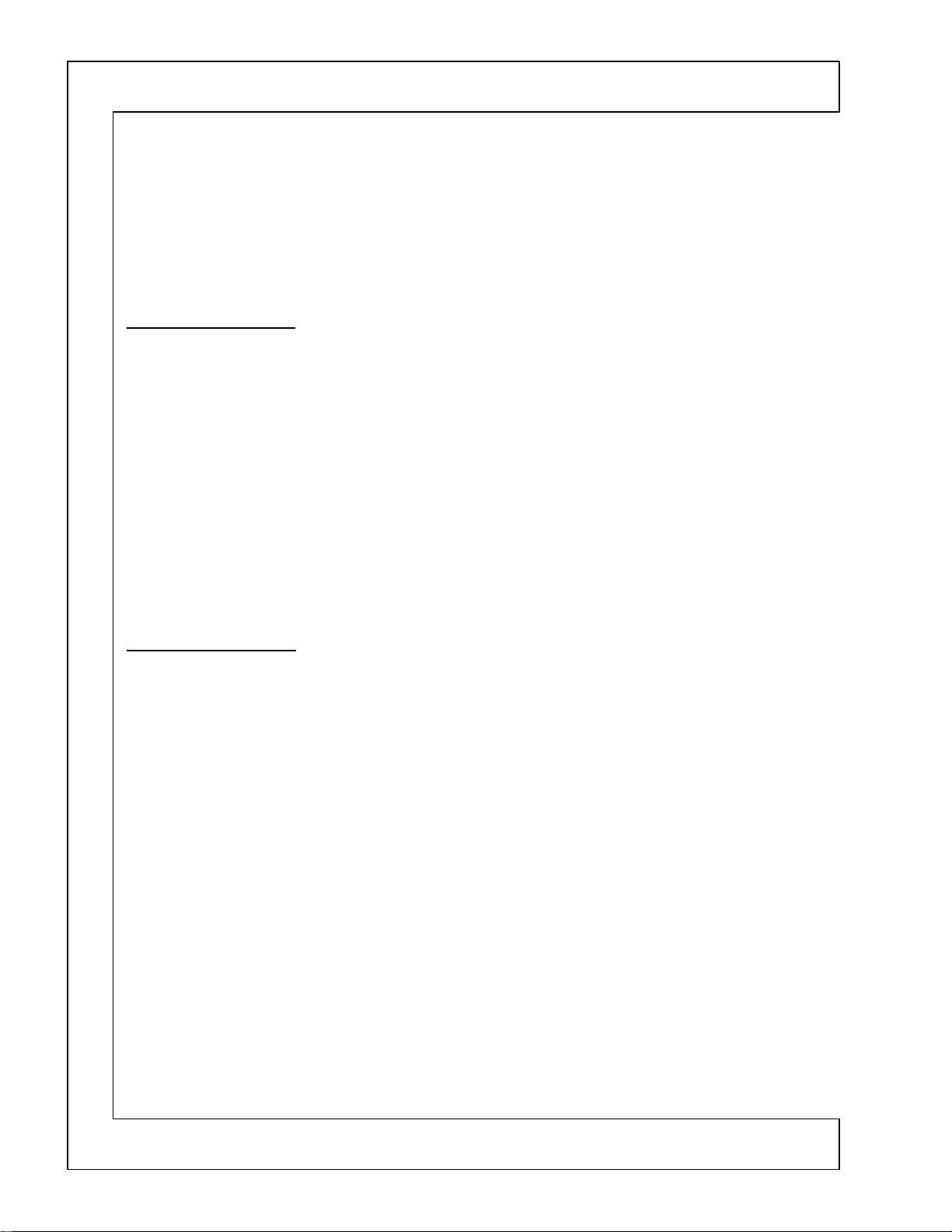

DP-3X PROT_CPT and PROT_SW SHUT DOWN DIAGRAM

PROT_CPT SHUT DOWN DIAGRAM

+220V

VM 220V

PDC1

CE10

W8A1

REF2

1

2

QEA8

RE35

2.2 Ohm

QE08

RE29

REF1

15 Ohm

REE9

RED CRT PWB

RGB Drives

VM Circuit

RE31

PROT_SW SHUT DOWN DIAGRAM

BLUE CRT PWB

VM Circuit

REF5

CEC1

RE34

VM

PROT

REF6

CONT

GAIN

RED

CRT

PWB

ERG1

7

BLUE

CRT

PWB

EGB1

8

VM

PROT

GAIN

CONT

GREEN

CRT

PWB

PSC

3

GREEN

CRT

PWB

PSC

2

VM

PROT

GAIN

CONT

SIGNAL

PWB

PSC

3

SIGNAL

PWB

PSC

2

SIGNAL

CPT

PROT

SIGNAL

GAIN

CONT

PWB

PPS4

Active

Hi

6

PROT

CPT

PWB

PPS4

Active

Lo

5 5

PROT

SW

POWER

PWB

PPS4

6

POWER

PWB

PPS4

D421~D424

SW +5.5V

SW +9V

SW +9.3V

SW +2.2V Reg

I404

5

SW +3.3V Reg

I403

1

SW +5V Reg

I402

SIGNAL PWB 2 of 3

4

3

32

SW +2.2V

SW +3.3V

SW +5V

D402

D401

D404

D403

C592

R5T4

RL50

Q554

R420

PAGE 01-12

Page 21

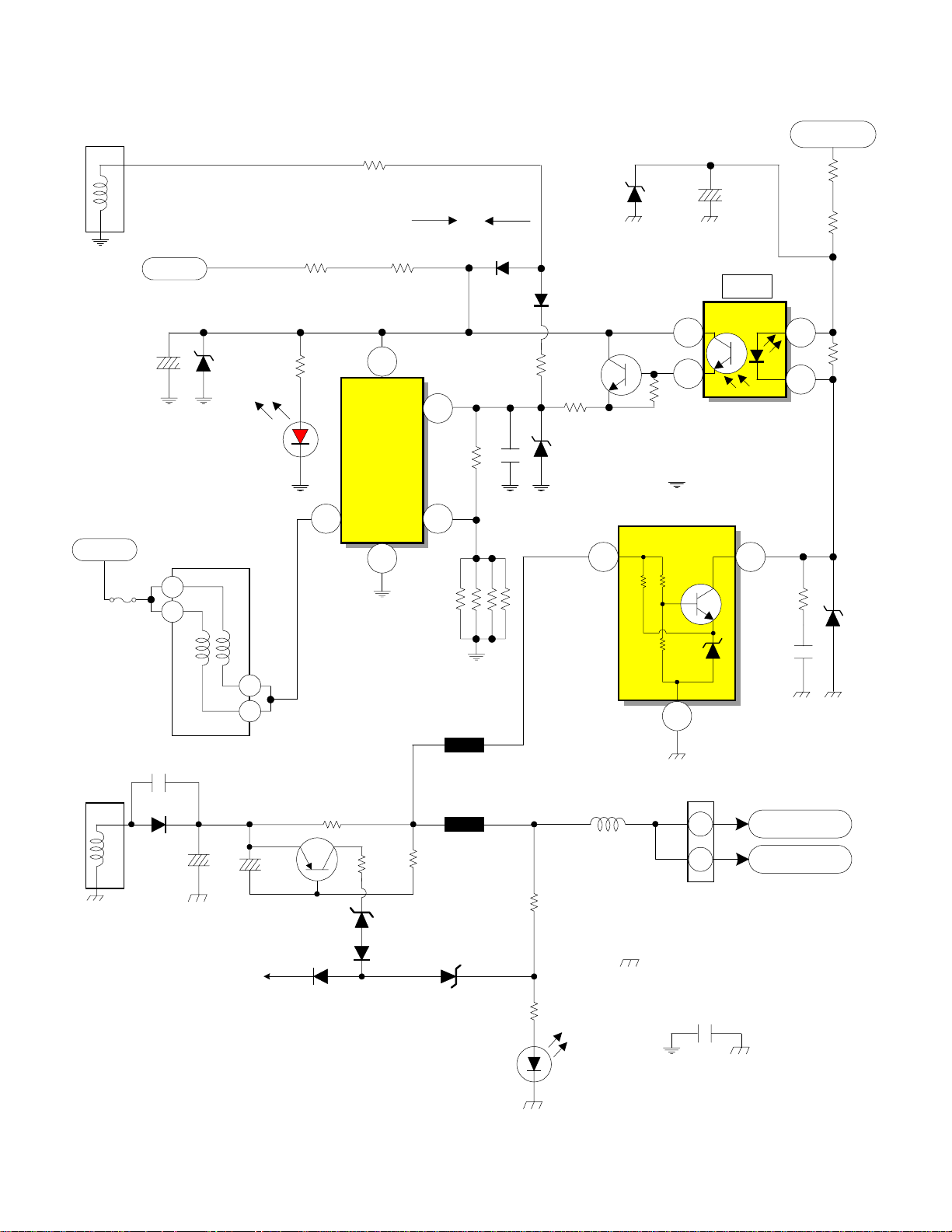

DP-3X SW +115V POWER SUPPLY REGULATION EXPLANATION

Hi-Voltage Power Supply Circuit Diagram explanation:

(See Power Supply SW+115V Regulation Circuit Diagram for details)

THIS POWER SUPPLY RU NS ONLY WHEN THE SET IS TURNED ON:

TURNING ON THE SW +115V POWER SUPPLY:

When the Set is turned on, the Microprocessor

Power On command is ro uted through

the base of

collector will go low. This will supply a ground path for the power on Relay

energized, AC is supplied to the Bridge rectifier

develops raw 150V which is routed through

D901

the primary coil inside

FET. The Ground return path for the primary voltage is out pin 2 of

Switch MOS FET and then through four 0.22 ohm resistors

See SW+115V Regulation Circuit Diagram for details.

SW +115 REGULATION

SW +115V pulse is generated from pin 11 of

routed thro ugh the Excessive Current sensing circui t

The primary route for the

to the Deflection circuit and High Voltage generation circuit.

However, the regulation route is through

variable resistor whose resistance is dependant upon the

resistor manipulates the current flow from pin 2 to pin 3 ground. This will cause the voltage at pin 2 of

manipulated. Internally, the LED is illuminated by degrees dependant upon the

The internal receiver receives this light and acts as a variable resistor from pin 4 to pin 3 which is the regulation

control signal.

This action causes pin 1 of

quency of the drive pulse delivered to the Gate of the internal SMOSFET (Switch Metal Oxide Semiconductor

Field Effect Transistor) to manipulate the frequency of the pulse generated on the primary of

drain of the internal SMOSFET is monitored by four low ohm resistors mentioned above. If this current exceeds

a specific value, the voltage developed by these low ohm resistors is routed through

is the Over Current Protection circuit as well as the Regulation Control pin. This pin will inhibit the drive signal

to the gate of the SMOSFET. As soon as the excessive current situation is eliminated, the IC will recover and

continue func ti o ni n g.

B+ GENERATION FOR THE POWER SUPPLY DR IVER IC:

Vcc for the Driver IC is first generated by the AC input. This voltage is called Start Up Voltage.

DC to operate normal. However, it will begin operation at

23.3V

When AC is applied to the main full wave bridge rectifier

to be supplied to the power supply switching transformer

However, one leg of the AC is routed to a half wave filter consisting of

tor), filtered by

When this voltage reaches 12Vdc, the internal Regulator of

When the power supply begins to operate by turning on and off the internal Switch MOS FET, the Raw 150V DC

routed through

MOS FET is routed out of pin (2) through four low ohm resi stors to hot gro und. When the internal Switch MOS

FET turns on, it causes the transformer to saturate building up the magnet field. When the internal Switch MOS

FET turns off, the magnet field collapses and the EMF is coupled over to the secondary windings, as well as the

drive windings. The drive windings at pin (8) produce a run voltage pulse which is rectified by

then clamped by

C911

The RED LED

provided the Shut Down sensor

Q902

and out pins 5 and 6 to pin 3 of

T901

SW +115V

I901

, clamped by a 36V Zener

C911

, in on pin 1 (Drain) and out on pin 2 which is the Source. The Source of the internal Switch

T901

and now becomes run voltage (

D911

can be used to determine if the B+ to pin 4 of

D912

Q027

is through

E906

to manipulate the internal oscillator within

Outputs a Power On/Off 1 high command via pin 59. This

I001

and

Q028

Q904

D901

F903

. This pulse is rectified by

T901

E907, L923

to pin 1 of

D911

to the

isn’t activated. When the base of

.

to Pins 1 and 2 of

R908, R909, R910

and

R944

I904

SW +115V

D901

T901

and made available to pin 4 of

I901

connector pin 7. This High will be passed to

PPS4

S901

. This voltage is routed through

T901

which is the Drain of the internal Switch MOS

I901

which is the Source of the internal

I901

and

D925

.

Q905

to pin 9 and 10 of

. Internally, the regulator transistor works as a

voltage fluctuations. The internal variable

12V DC

where it is converted to Raw 150V DC voltage

pin 1 and 2.

R906

is turned On and begins operation.

) for

23.3V

I901

I901

PPD5

SW +115V

. This in turn causes the fre-

I901

on pin 4 of

and

R907

pin 4.

is present.

goes high, it’s

Q902

turning it on. When the relay is

.

R911

, filtered by

and output as

voltage fluctuations .

T901

back into pin 1 which

R912

.

I901

(both a 3.9K ohm resis-

as start up voltage.

I901

and then

C943

SW +115V

I903

. The current

requires

I901

, filtered by

D907

to be

PAGE 01-13

Page 22

DP-3X CHASSIS POWER SUPPLY SW +115V REGULATION

T901

8

7.5P/P

9

1 of 3

C911 R918

AC for D902

Supplied from

Relay S901

From Bridge D902

150V

F903

AC

From Relay S901

D911

D912

RED L.E.D.

167V

T901

1

2

5A

5

6

High Voltage Power Supply

R913

R906

23.3V

4

I901

Driver/

Output IC

3 2

DS

5

R907

OCP

Start Up

Osc B+

1

R912

R908

R909

R910

R911

0.22

Ohm

11.6V

E906

0.5K

Run

D907

R914

C914

D908

Q901

R916

D910

B+ 115V

D927

23.3V

13.6V

R919

C946

FB

I903

4

3

Regulator

Photocoupler

Hot Ground from

pin 9 of T901

I904

1 2

3

SW + 115V

R940

R941

12.1V

1

R942

2

11.2V

11.2V

R943

D926

C944

T901

11

12

3 of 3

C942

D925

C943

2 of 3

C949

Q905

X-Ray

Protect

R944

0.39 Ohm

D928

D929

D930

R946

R942

D931

3K

E907

R952

R953

L923

Deflection

B+ 115V

D932

PPD5

0.86A

9

10

Cold Ground from

pin 12 of T901

C905

SW +115V

SW +115V

PAGE 01-14

Page 23

MICROPROCESSOR

INFORMATION

DP-3X

CHASSIS INFORMATION

SECTION 2

Page 24

DP-3X BLANK PAGE “NOTES”

BLANK PAGE

Page 25

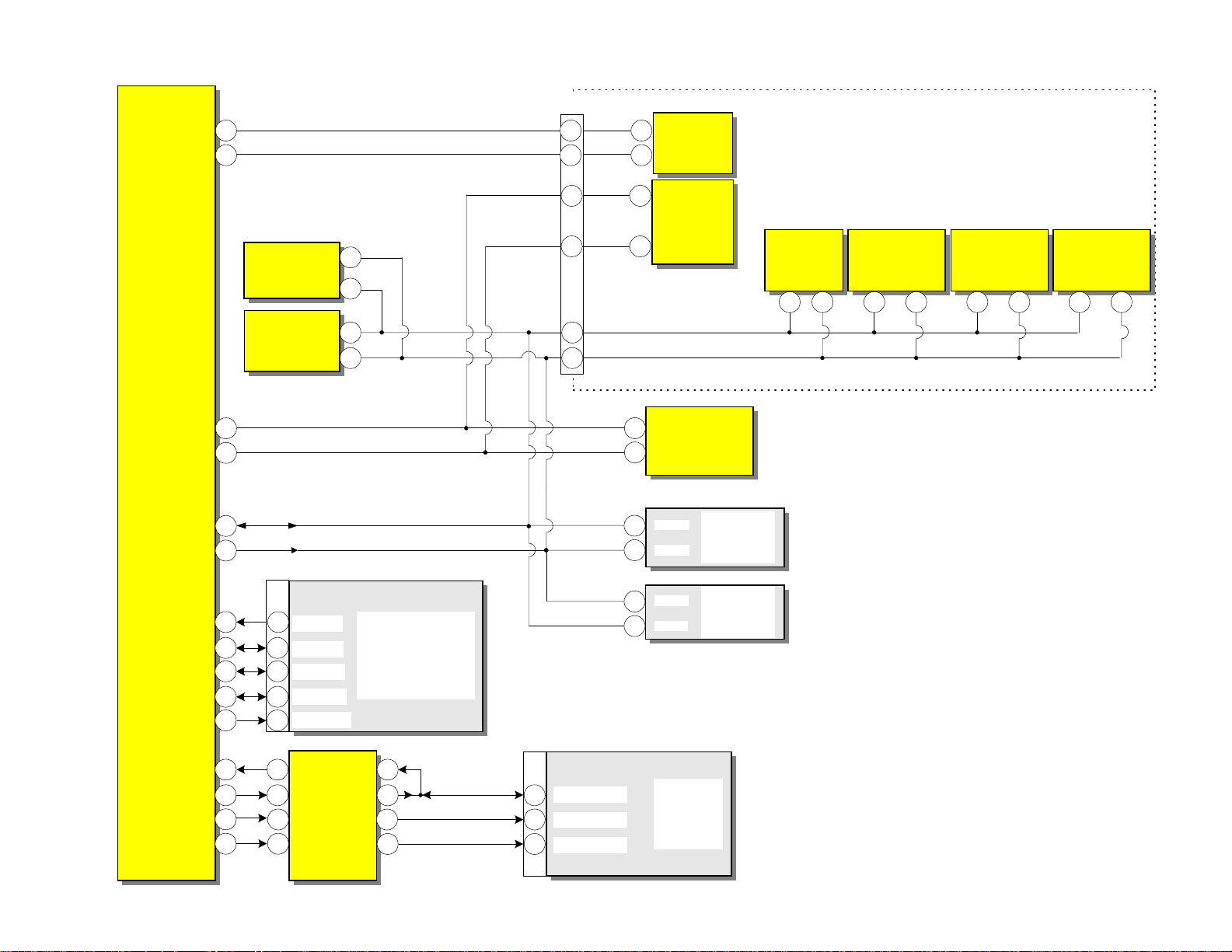

DP-3X MICROPROCESSOR DATA COMMUNICATIONS CIRCUIT EXPLANATION

Microprocessor Data Communications circuit diagram.

(See DP-3X Microprocessor Data Communications Circuit Diagram for Details)

The Microprocessor must keep in communication with the Chassis to maintain control over the individual circuits. Some of the circuits must return information as well so the Microprocessor will know how to respond to

different request.

The Microprocessor uses two types of communication for control, I

lines . The I

2

C communication scheme only requires 2 lines for control. These lines are called SDA and SCL.

Serial Data and Serial Clock respectively.

Also, due to the fact that this Microprocessor operates at 3.3Vdc, it requires a Level Shift IC to bring the DC

level of the control lines up to make it compatible with the connected components. The Level Shift IC also brings

the DC levels down as outside circuits communicate with the microprocessor.

The Microprocessor communicates with the following ICs:

ON THE SIGNAL PWB:

•

UD2003 Digital Module

•

U301 Main Tuner

•

U302 PinP Tuner

•

I003 EEPROM

•

U401 Flex Converter

•

I010 Level Shift

•

I501 Rainforest

•

IA01 Audio Control

(ATSC Tuner DP-36 and DP-38 Chassis Only)

ON THE TERMINAL PWB:

•

IY01 3D Y/C

•

IV01 A/V Selector

•

IV11 Digital to Analog Converter DAC

•

IV03 Y Pr/Pb Selector

•

IY04 Main Video Chroma Y Pr/Pb Selector

•

IY03 Sub Video Chroma Y Pr/Pb Selector

The following explanation will deal with the communication paths used between the Microprocessor and the respected ICs.

ON THE SIGNAL PWB:

UD2003 Digital Tuner (ATSC Tuner)

DP-36 and DP-38 Chassis Only

The Microprocessor controls the Digital Tuner via communication lines. They are listed below;

•

•

•

DM RTS

DM CTS

DM TXD

(Digital Module Receive Transmission) from pin 9 of

(Digital Module Serial Clock) bi-directional pin 20 of

(Digital Module Transmission Data) bi-directional pin 35 of

tor.

•

•

DM RXD

Power 2

of the

11

(Digital Module Receive Data) bi-directional pin 36 of

(Turns on Digital Module separate from the main Power On line) from pin 58 of

connector. The Table below shows the relationship between Power_1 and Power_2.

PMS1

2

C Bus and the Serial Data, Clock and Load

connector to pin 27 of the

PMS1

pin 7 of the

I001

to pin 5 of the

I001

pin 6 of the

I001

PMS1

PMS1

connector.

PMS1

I001

connec-

connector.

to pin

I001

.

MODE Power _1 Power _2

Stand By Lo Lo

Timer Lo Hi

TV On Hi Hi

When the Timer is set for an unattended Recording,

the Set turns on the Tuner and allows the "Video

Out (Monitor out) to become active so that a recording can be made without turning on the entire

set.

(Continued on page 2)

PAGE 02-01

Page 26

DP-3X MICROPROCESSOR DATA COMMUNICATIONS CIRCUIT EXPLANATION

U301 Main Tuner (with MTS outputs).

The Microprocessor controls the Main Tuner by SDA2 (Data) and SCL2 (Clock) I

SCL2 and SDA2 lines for the Main Tuner are output from the Microprocessor at pins (

2

C communication lines.

31 SDA2 and 28 SCL2

)

respectively. These lines go directly to the Main Tuner, SDA2 at pin (5) and SCL2 at pin (4). These lines control

band switching, programmable divider set-up information, pulse swallow tuning selection, etc...

U302 PinP Tuner (monaural only).

The Microprocessor controls the Sub Tuner by SDA2 (Data) and SCL2 (Clock) I

SCL2 and SDA2 lines for the Main Tuner are output from the Microprocessor at pins (

2

C communication lines.

31 SDA2 and 28 SCL2

)

respectively. These lines go directly to the Main Tuner, SDA2 at pin (5) and SCL2 at pin (4). These lines control

band switching, programmable divider set-up information, pulse swallow tuning selection, etc...

I003 EEPROM

The EEPROM is ROM for many different functions of the Microprocessor. Channel Scan or Memory List, Customer set ups for Video, Audio, Surround etc… are memorized as well. Also, some of the Microprocessors internal sub routines have variables that are stored in the EEPROM, such as the window for Closed Caption detection.

Data and Clock lines are

pin (29) of the Microprocessor to pin (6) of the

from pin (30) of the Microprocessor to pin (5) of the

SDA1

EEPROM

. Data travels in both directions on the Data line.

EEPROM

and

SCL1

from

Note: In this chassis, if the EEPROM is removed or defective, the Microprocessor will LOCK the picture. No

functions other that the front Power Button will work. LOCK will appear on the screen, but the customer’s menu

can not be accessed.

U401 Flex Converter FC04

The projection television is capable of displaying NTSC as well as ATSC (SDTV) and HD (High Definition).

The Flex Converter is responsible for receiving any video input and converting it to 33.75 Khz output (2.14H).

This output is controlled by sync and by the customer’s menu and how it is set up. The set up can be 4X3 with

grey side panels, Smooth Wide, Fill or Full and even 4X3 with Black Side panels. 16X9 for SDTV. This set will

automatically bypasses the Flex Converter completely and inputs the 1080i signal directly to the Rainforest IC

I501. This happens when a true 1080i signal or Antenna C is selected. The Flex Converter can take any NTSC, SIn, Component, NTSC or any of the 18 formats of ATSC except 1080i which doesn’t route through the Flex converter. Control for the Flex Converter is Clock, Data and Enable lines. The

be routed through the Level Shift IC

to be brought up to 5V.

I007

Clock, Data and Enable

lines must

• The Clock line for the Flex Converter is output from the Microprocessor at pin (

at pins (

I007

2 Clock

• The Data line for the Flex Converter is output from the Microprocessor at pin (

at pins (

I007

4 Data

) and is output at pins (18) then through the

) and is output at pins (16) then through the

connector pin 10

PFC1

connector pin 11

PFC1

52 Data

• The Enable line for the Flex Converter is output from the Microprocessor at pin (

input to

I007

at pins (

6 Enable

) and is output at pins (14) then through the

PFC1

53 Clock

54 FCENABLE

connector pin 12.

). Clock is input to

). Data is input to

). Enable is

Data from the Flex Converter is also sent back to the Microprocessor. Data from the Flex is sent out of the

connector pin 11 to pin 5 of

sor

I001

.

, level shifted down to 3.3V and output at pin 15 into pin 51 of the Microproces-

I007

PFC1

I007 Level Shift

The Microprocessor operates at 3.3Vdc. Most of the Circuits controlled by the Microprocessor operate at 5Vdc.

The Level Shift IC steps up the DC voltage to accommodate.

• Pin 18 outputs a Clock signal, used by the Flex Converter

• Pin 14 outputs an Enable signal, used by the Flex Converter

• Pin 16 outputs a Data signal, used by the Flex Converter.

• Pin 15 outputs 3.3V Data, sent from the Flex Converter

(Continued on page 3)

PAGE 02-02

Page 27

DP-3X MICROPROCESSOR DATA COMMUNICATIONS CIRCUIT EXPLANATION

I501 Rainforest (Video/Chroma Processor)

The Video Processing IC (Rainforest) is responsible for controlling video/chroma processing before the signal is

made available to the CRTs. Some of the emphasis circuits are controlled by the customer’s menu. As well as

some of them being controlled by AI, (Artificial Intelligence).

Communication from the Microprocessor

and 30) respectively.

IA01 BBE Audio Control (Surround)

This chassis utilizes BBE Surround.

Communication from the Microprocessor via pins (

) respectively.

14

ON THE TERMINAL PWB:

(Through the connector PST2)

IY01 3D Y/C

(IC mounted directly on the Terminal PWB).

The 3D Y/C IC is a Luminance/Chrominance separator, as well as a 3D adder. Separation takes place digitally.

Using advanced separation technology, this circuit separates using multiple lines and doesn’t produce dot pattern

interference or dot crawl. The 3D effect is a process of adding additional emphasis signals to the Luminance and

Chrominance. These signals relate specifically to transitions. Transitions are the point where the signal goes from

dark to light or vice versa. The 3D adds a little more black before the transition goes to white and a little more

white just before it gets to white. It also adds a little more white just before it goes dark and a little more dark just

before it arrives. This gives the impression that the signal pops out of the screen or a 3D effect.

The Microprocessor communicates with the 3D Y/C IC via I

from the Microprocessor are pins (

pins (47 and 46) respectively.

IY01

40 SDA3

The Microprocessor also is able to turn on and off circuits within the 3D Y/C circuit determined by customer

menu set-up.

IV01 A/V Selector

The A/V Selector IC is responsible for selecting the input source for the Main Picture as well as the source for

the PinP or Sub picture. Communication from the Microprocessor via pins (

connector pins (13 and 12) respectively then to

IV11 DAC (Digital to Analog Converter)

This IC works controlling different switches via the DAC0, DAC1 and DAC2 control lines.

•

•

pin 7 controls the V. Sync selector

DAC0

DVI 1/2 via pin 9.

IV06

pin 6 controls the Y selector

DAC1

Media Card via pin 10.

•

pin 5 controls the V. Sync selector

DAC2

Sync selector

for the DVI 1/2/Media Card via pin 11.

IV06

Communication from the Microprocessor via pins (

to

pins (14 and 15) respectively.

IV11

IV03 Main/PinP Y Pr/Pb Selector

Any input that is in the Y Pr/Pb or Y Cr/Cb state, will have be selected by this IC. Both for the Main Picture and

the PinP (Sub) picture.

The Main/PinP Y Pr/Pb Selector IC selects the appropriate input between Components 1 or 2, DVI 1 or 2, ATSC

Tuner and/or DVD Player, if provided. Communication from the Microprocessor via pins (

) to connector

SCL2

pins (15 and 14) to

PST2

I001

and

via pins (

31 SDA2

31 SDA2

and

and

28 SCL2

2

C bus data and clock. The communications ports

39 SCL3

IV01

IV07

IV03

) to connector

pins (34 and 33) respectively.

for DVI 1/2 input via pin 9 and H Sync selector

IV07

for DVI 1/2 input via pin 10 and Y selector

for DVI 1/2/Media Card input via pin 11 and V.

IV07

31 SDA2

and

28 SCL2

pins (26 and 27) respectively.

28 SCL2

) to the Rainforest IC pins (28

) to the Audio Control IC pins (13 and

pins (17 and 16) to the 3D Y/C

PST2

30 SDA1

and

) to connector

29 SCL1

PST2

31 SDA2

) to the

for the

IV06

pins (15 and 14)

and

28

PST2

(Continued on page 4)

PAGE 02-03

Page 28

DP-3X MICROPROCESSOR DATA COMMUNICATIONS CIRCUIT EXPLANATION

IY04 Main Video Chroma Y Pr/Pb Switch IC

This IC is responsible for selecting the Main picture source. It will be either Composite NTSC Y and C or component Y Pr/Pb or Y Cr/Cb dependant upon the customer’s selection.

• This IC processes the NTSC Luminance (Y) and Chroma (C) from the 3D Y/C circuit for the main picture if

this is the selection. It receives the Y (pin 4) and C (pin 19) and prepares it for the Flex Converter by outputting it as Y (pin 24) Cr (pin 22) / Cb (pin 23) NTSC Only 480i component to the Flex Converter .

• This IC selects the Y (pin 30) Pr or Cr (pin 28) / Pb or Cb (pin 29) if this is the selection by the customer and

outputs it as Y (pin 24) Pr or Cr (pin 22) / Pb or Cb (pin 23) to the Flex Converter. If the output is 1080i, it’s

routed directly to the Rainforest IC I501.

Communication from the Microprocessor via pins (

then to

Note: Y Pr/Pb indicates either 31.5Khz or 33.75Khz and Y Cr/Cb indicates 15.734KHz

IY03 Sub Video Chroma Y Pr/Pb Switch IC

This IC is responsible for selecting the PinP (Sub) picture source. It will be either Composite NTSC Y and C or

component Y Pr/Pb or Y Cr/Cb dependant upon the customer’s selection.

• This IC processes the NTSC Luminance (Y) and Chroma (C) from the 3D Y/C circuit for the main picture if

this is the selection. It receives the Y (pin 4) and C (pin 19) and prepares it for the Flex Converter by output-

ting it as Y (pin 24) Cr (pin 22) / Cb (pin 23) NTSC Only 480i component to the Flex Converter .

• This IC selects the Y (pin 30) Pr or Cr (pin 28) / Pb or Cb (pin 29) if this is the selection by the customer and

outputs it as Y (pin 24) Pr or Cr (pin 22) / Pb or Cb (pin 23) to the Flex Converter. If the output is 1080i, it’s

routed directly to the Rainforest IC I501.

Communication from the Microprocessor via pins (

then to

Note: Y Pr/Pb indicates either 31.5Khz or 33.75Khz and Y Cr/Cb indicates 15.734KHz

pins (13 and 14) respectively.

IY04

pins (13 and 14) respectively.

IY03

31 SDA2

31 SDA2

and

and

28 SCL2

28 SCL2

) to connector

) to connector

pins (15 and 14)

PST2

pins (15 and 14)

PST2

PAGE 02-04

Page 29

SDA3

SCL3

40

39

DP-3X Chassis Microprocessor Data Communications

PST2

SDA3

SCL3

47

46

IY01

3D-Y/C

17

16

Terminal PWB

IOO1

Micro

PAGE 02-05

Data / Key Out 2

Clock / Key Out 1

SDA1

SCL1

SDA2

SCL2

DM RTS

DM CTS

DM TXD

DM RXD

POWER 2

FCData

FCEnable

Audio Control

Rainforest

Sweep Cont.

30

29

31

28

PMS1

27

20 7

35 6

36 5

58

51

52 4

54

53

IA01

I501

9

11

15

2

DM RTS

DM CTS

DM TXD

DM RXD

POWER 2

I010

Level Shift

14

13

28

30

UD2003

Digital Module

ATSC Tuner

5

16

146

18

SDA2

SCL2

SDA1

SCL1

SDA2

SCL2

SDA1

SCL1

PFC1

FCData

11

12

FC Enable

10

FC Clock

12

15

14

SDA1

SCL1

SDA2

SCL2

3413

33

5

6

5

4

4

5

U401

SDA1

IV01

A/V Select

SCL1

SDA1

IOO3

EEPROM

SCL1

SDA2

SCL2

SCL2

SDA2

FC04

FLEX

&

PinP

U301

Tuner

Main

U302

Tuner

PinP

Main/PinP

IV11

DAC

14 15

IV03

Y Pr/Pb

SELECTOR

26 27

IY04 Main

Video/Chroma

Y Pr/Pb SW

13 14

SIGNAL PWB

MODE Power _1 Power _2

Stand B y Lo Lo

Timer Lo Hi

TV On Hi Hi

When the Timer is set for an unattended

Recording, the Set turns on the Tuner and

allows the "Video Out (Monitor out) to

become active so that a recording can be

made without turning on the entire set.

IY03 Sub

Video/Chroma

Y Pr/Pb SW

13 14

Page 30

DP-3X AUDIO VIDEO MUTE CIRCUIT EXPLANATION

(See DP-3X Series Chassis Audio Video Mute Circuit Diagram for details)

There are times in which the main picture and audio must be muted. This can be because of changing channels

where the noise between stations is unacceptable, same thing for Auto Programming channels. When the deflection circuit malfunctions, etc…

All this is done primarily to prevent damage to the CRTs or to external amplifiers or speakers connected to the

projection television.

MICROPROCESSOR OUTPUT:

The Microprocessor

high is routed to the Video and Audio Mute circuit.

VIDEO MUTE PATH.

The High fr om pin 49 is routed to

VATION here forward, please use the below explanation when Mute Activation is mentioned.

• MUTE ACTIVATION:

1. When

2. Another route for the high from

3. Another route for the high from

SPOT:

Another circuit attached to the Mute Activation circuit (

deflection PWB when either Horizontal or Vertical deflection is lost. This is to prevent a horizontal or vertical

line from being burnt into the CRTs. See Horizontal and Vertical Sweep Loss Detection circuit and explanation

and circuit diagram for details. This high is input from

. See the Mute Activation circuit explained previously.

Q529

H Blk Loss Det:

Another circuit attached to the Mute Activation circuit (

If the Horizontal Blanking signal is loss to the Signal PWB,

plied with H. Blanking on it’s base. By the activity of the pulse charging

it’s emitter are held high keeping it turned off. If H. Blk is lost, then

blocked by

to the base of

D508

AUDIO MUTE PATH:

See the Mute Activation circuit explained previously as to how

When Mute Activation is turned on, the following circuits are activated.

CRT MUTE PATH:

The high from

to the following diodes,

PWB. When the diodes are supplied with a low on their cathodes, they remove the base voltage fro the RGB

drivers,

Q853, Q803

Q529

to the HVcc 9.3V line through

routed to the following circuits. Through

This pin is also the same pin that FC H Blk and FC V Blk is input. Generally this input is a positive going pulse that blanks the video during the peak pulses which represent retrace. However, when the DC

component is forced high by the action of

RGB.

the Terminal PWB. This turns on

Monitor Out on the Terminal PWB.

and outputs the high from it’s emitter to mute the Audio described later.

and it holds the emitter of

D509

Q527

outputs V. Mute from pin

I001

to the base of

D507

turn on, the collector pulls the base of

and

R5A5

is through

Q528

QV08

is through

Q528

Q525

. See the Mute Activation circuit explained previously.

Q529

Labeled as V MUTE 2: (Emitter of Q527 Mute Activation Circuit)

Shown going to the CRT PWB. Labeled a s V MUTE 1:

is routed to

on the Green CRT PWB,

D853

and

Q8A3

pin 11. This high go es to

PSC

on the Green, Red and Blue CRT PWBs. This shuts off each CRT Drive.

See next page for continuation of Audio Mute Circuit explanation.

when changing channels, Auto Programming, etc… This

49

. The following actions will be labeled MUTE ACTI-

Q529

low and turns it on. It’s collector is connected

Q528

. When

D510

R564, D503

turning on, t his pin goes high and mutes the output of

Q528

D406

and

high. This action turns on

which grounds out the Audio Outputs from the

QV09

R5A1

base) is

Q529

pin (4), through

PPD3

base) is

Q529

Q525

on the Red CRT PWB

D803

turns on, it’s collector goes high. This is

Q528

, and

. This high continues to the

to the base of

will detect the loss. Normally,

Q527

Q856

and into the Rainforest IC

R561

Q527

This signal is generated from the

SPOT.

pin (4),

PPS3

H Blk Loss Det.

and

C546

will discharge through

C546

is turned on.

base. This turns on and supplies a ground

C545

and supplies a high through

Q525

pin 39.

I501

connector on

PST1

. This transistor turns On

to the base of

D511

is sup-

Q526

, the base of

on the Blue CRT

D8A3

R599. C545

Q525

and

is

PAGE 02-06

Page 31

DP-3X AUDIO VIDEO MUTE CIRCUIT EXPLANATION

FRONT AUDIO OUT H A RD MUTE PATH:

• The high from

base of

dio Out. (Note: This is not the same thing as the Mute selected fro m the customer’s re mote. This is controlled by the Front Audio Control IC

1/2 Mute = 50% and Full Mute = 0%.

OUT TO HI-FI MUTE PATH:

and then to the cathodes of

they grounds the Right and Left audio for the Out to Hi-Fi audio output jacks.

FRONT AUDIO OUT MUTE:

V MUTE 1:

High is sent to the following 4 circuits:

1. To the Front Audio Out Hard Mute circuit routed through

2. The high is also route d through

they ground the audio going into the Audio Output IC

of the

3.

CRT Mute:

4.

Out to Hi-Fi Mute Path:

and then to the cathodes of

turns on, they ground the audio going into the audio for Out to Hi-Fi audio output jacks.

A MUTE PATH: (Microprocessor Pin 71)

A MUTE:

This High is sent to the following 3 circuits:

1.

Front Audio signal mute:

and to the base of

the Audio Output IC

of

2.

Main Tuner U301 Mute:

Tuner

3.

Out to Hi-Fi Mute Path:

and then to the cathodes of

turns on, they ground the audio going into the audio for Out to Hi-Fi audio output jacks.

REC MUTE PATH: (Microprocessor Pin 70)

Record Mute signal path.

connector on the Terminal PWB. Here it is routed to

PST1

. When this line goes high, the Audio Left and Right is muted coming from the monitor o utputs. The DP-

QV09

36 utilizes a Digital Tuner (ATSC). The ATSC tuner also outputs NTSC video and Audio which is routed to the

Monitor outputs for VCR recordings. When the ATSC tuner (Antenna C) changes channels, the aud io is muted

briefly to avoid the unnecessary noise during switching.

Note too that the DP-36 does not utilize D406 like all the other chassis.

FRONT SPEAKER OFF: (IA01 Pin 17)

Front Speaker Off signal.

1. It goes to

sistor turns on, it supplies a Lo to pin 11 of

2. It goes through

audio going into the Audio Output IC

connector to pin 4 of

QAA2.

The high from the Microprocessor pin 49 to

connector to pin 4 of

PPS4

See CRT Mute Path explanation above.

Also, the high from the Microprocessor pin 71 to

. Left audio in pin 3 of the

IAA1