Haier HLC19W-A Servise Manual

HLC19W-A

1. Features

2. Safety Precautions

3. Images of Module and Circuit Boards

4. Key IC Description& Trouble Shooting Guide

5.Signal Flowing Chart

6. Bus Control Adjustment

7. Circuit Diagram

Features

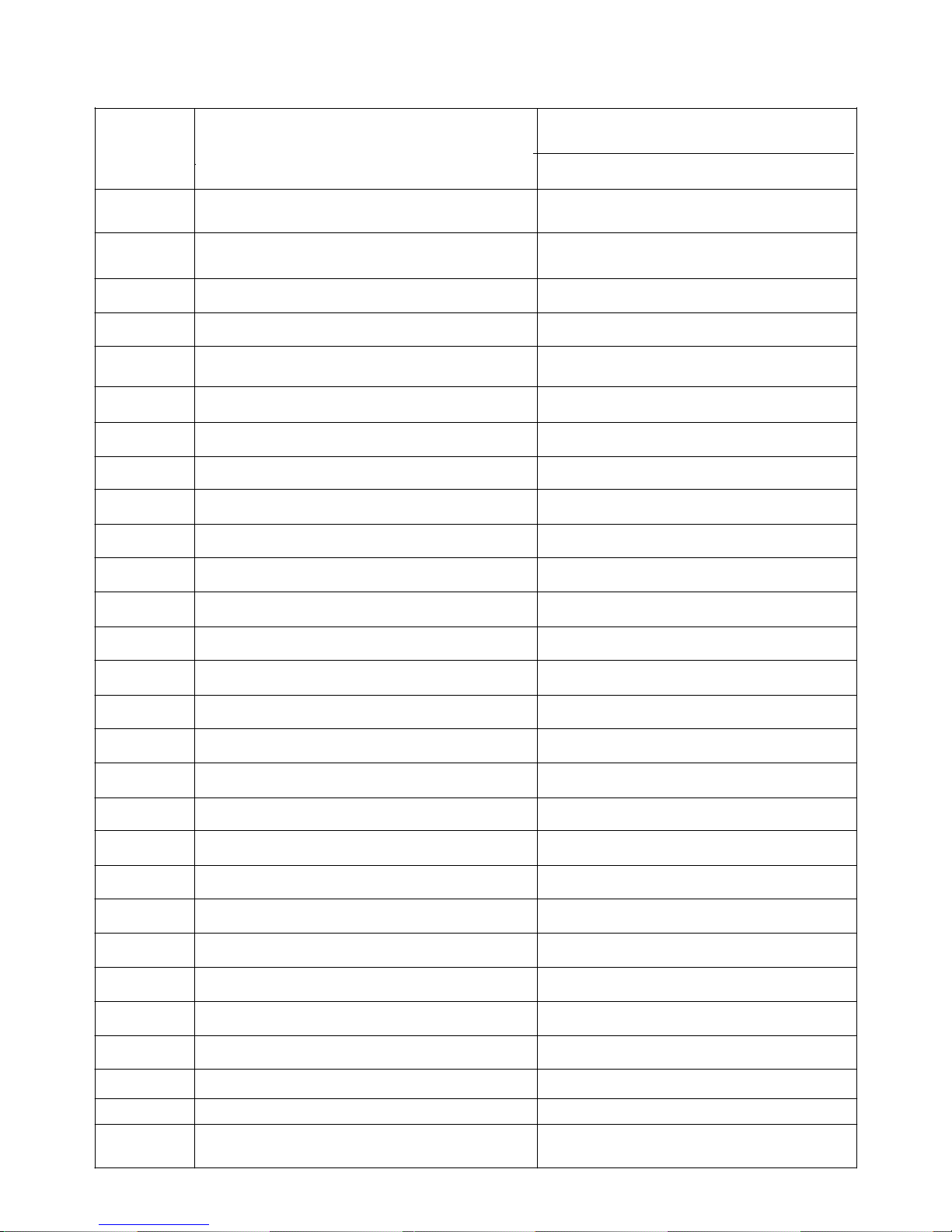

NO.

Functions

Model

HLC19W-A

1 TFT BOE

2 Screen size 19inch

3 Aspect ratio 16:10

4 Resolution 1440×900

5 Brightness 300cd/m

2

6 Contrast(Darkroom) 800:1

7 Response time(ms) 5

8 Color system ATSC/NTSC

9 NO. of preset channels 181

10 Picture mode Yes

11 Angel of view H:160

°

/ V:160

°

12 Color display 16,777,216

13 Color level 16

14 OSD languages ENGLISH \ FRENCH\ SPANISH

15 AV stereo Yes

16 Surrounding sound No

17 Audio system M

18 Bass Yes

19 Balance Yes

20 Sound mode Yes

21 Mute Yes

22 BTSC Yes

23 AV input Yes

24 AV output No

25 Y CB CR Yes

26 Y PB PR Yes

27 S-video jack Yes

28 TV in Yes

Model

NO.

Functions

HLC19W

29 D-SUB jack Yes

30 DVI socket No

31 SCART socket No

32 Ear-Phone Out Yes

33 CCD,V-CHIP Yes

34 Semitransparent menu Yes

35 ZOOM No

36 16:9 mode Yes

37 Child Lock Yes

38 Quick View Yes

39 NO. of built-in speakers 2

40 Audio output power(Built-in)(W) 2*1.5

41 Total power input(W) 80

42 Voltage range(V) 120

43 Power frequency(Hz) 60

44 Time of sleep timer(MINS) 120

45 Approval UL

46 Suitable market U.S.A

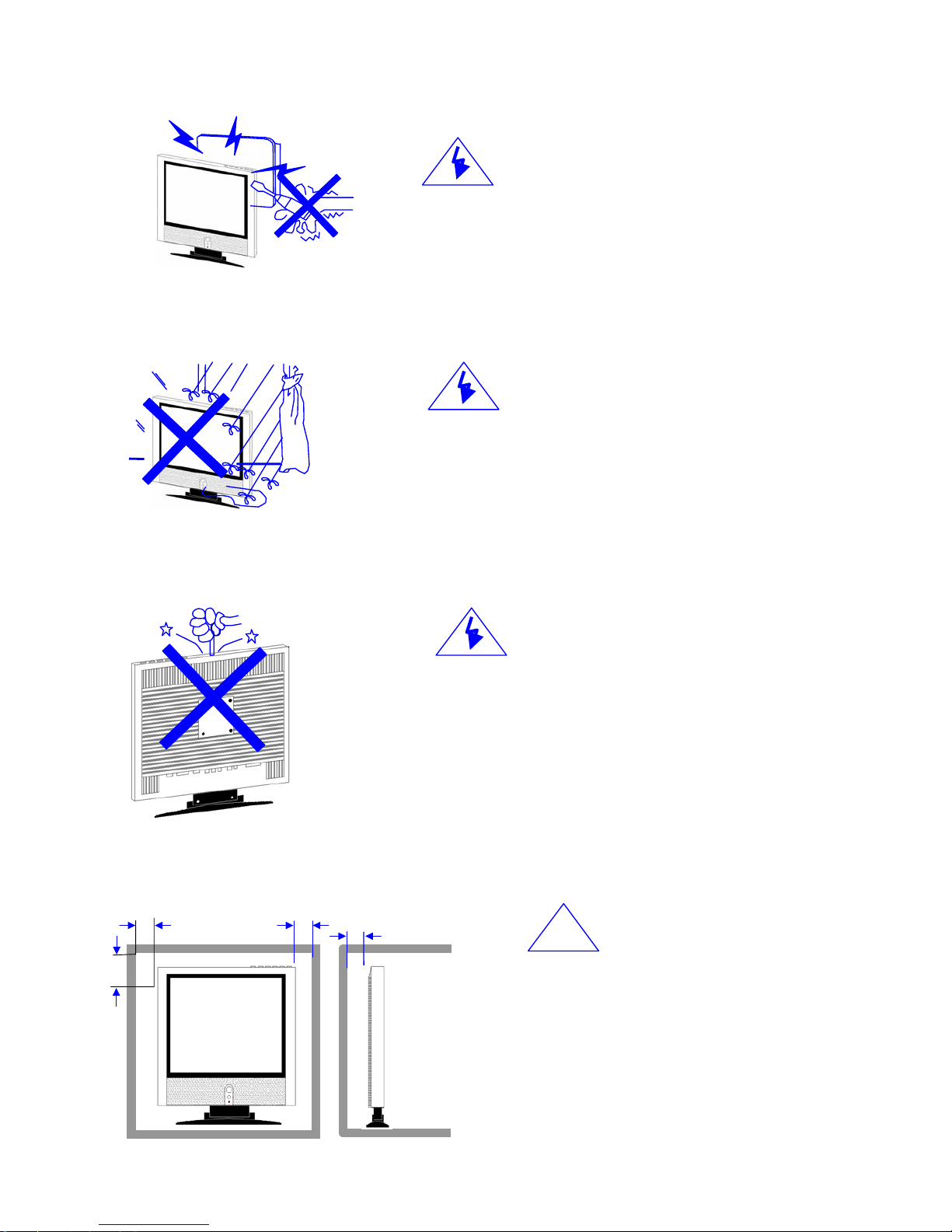

Safety Precautions

Warning

High voltages are used in the operation of this product.

Do not romove the cabinet back from your set. Refer

servicing to qualified service personnel.

Warning

To prevent fire or electrical shock hazard, Do not expose

the main unit to rain or moisture.

Warning

Do not drop or push objects into the television cabinet

slots or openings. Never spill any kind of liquid on the

television receiver.

Caution

If the television is to be built into a

compartment or similarly enclosed, the

minimum distances must be maintained.

Heat build-up can reduce the service life of

your television, and can also be dangerous.

!

Minimum

10c

20c

10c

5cm

Caution

Never stand on, lean on, push suddenly the product or its

stand. You should pay special attention to children to children.

Caution

Do not place the main unit on an unstable cart stand, shelf or

table. Serious injury to an individual, and damage to the

television, may result if it should fall.

Caution

When the product is not used for an extended period of time, it

is advisable to disconnect the AC power cord from the AC

outlet.

Caution

Avoid exposing the main unit to direct sunlight and other

source of the heat. Do not stand the television receiver

directly on other produces which give off heat. E. g. video

cassette players,Audio amplifiers. Do not block the

ventilation holes in the back cover. Ventilation is essential to

prevent failure of electrical component. Do not squash power

supply cord under the main unit.

Caution

The LCD panel used in this product is made of glass.

Therefore, it can break when the product is droppe d or

applied with impact. Be careful not to be injured by

broken glass pieces in case the LCD panel breaks.

!

!

!

!

!

Images of Module and Circuit Boards

1.images of Remote Board Subassembly

2.images of Control Panel Subassembly

3.images of Main Board

4.images of Power Supply

10/10/06 CONFIDENTIAL INFORMATION-DO NOT COPY 2

October 10, 2006 11:23 am

SupraHD-760-DTS-GEN-v1.0-Preliminary Release

Chapter 1. SupraHD-760 Overview

1.1 SupraHD Family

The ZR396xx family consists of:

• SupraHD-680 IC (ZR39680) - Digital TVs for the ATSC/DVB/OpenCable Market

• SupraHD-660 IC (ZR39660) - Digital TVs for the ATSC Market

• SupraHD-640 IC (ZR39640) - Digital ATSC upgrade for Analog TVs

The ZR397xx family consists of:

• SupraHD-760 IC (ZR39760) - Digital Flat Panel TVs for the ATSC Market

• SupraHD-740 IC (ZR39740) - Digital ATSC upgrade for Analog TVs

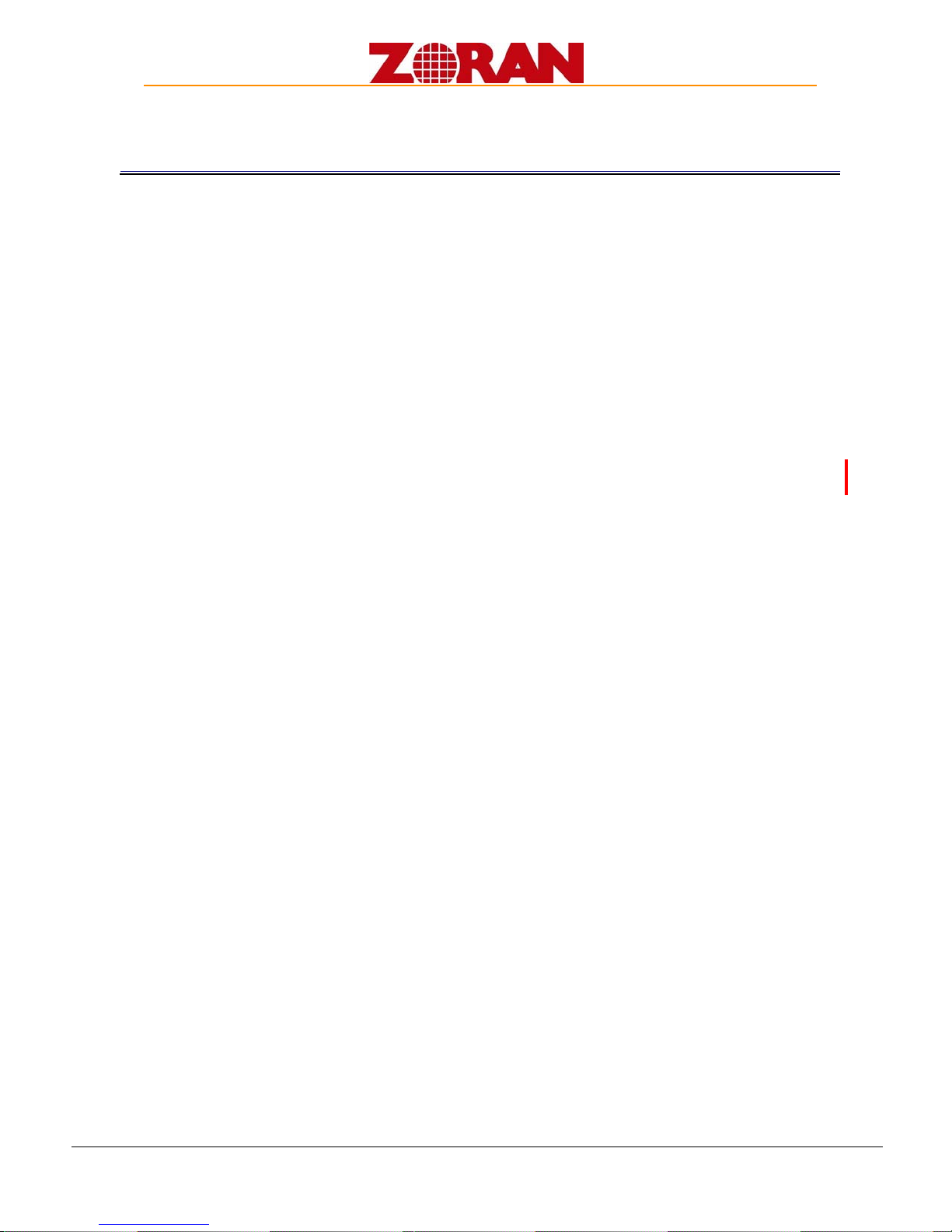

1.2 SupraHD-760 IC Description

The SupraHD-760 IC is a members of the SupraHD family of DTV controllers developed by Zoran. These

devices are intended to be used in ATSC-compliant television implementations. These devices include all of

the functionality required to support the television implementations shown in the following system block

diagrams.

SupraHD-760-DTS-GEN-v1.0-Preliminary Release

3 CONFIDENTIAL INFORMATION-DO NOT COPY 10/10/06

October 10, 2006 11:23 am

Figure 2 shows a typical system implementation using the SupraHD-760. This system can be designed and

manufactured in a very low-cost manner.

Figure 2: SupraHD-760 DTV System Diagram - FTA Implementation

Front

Panel

Rear Chassis

Connections

ZR39760

ATSC/

NTSC

Tuner

Analog

Mux

CVBS

IF

IF

CVBS/S-Video In

I2C0

HI2C

HCEC

HDMI

MIF

Stereo

D/A

Virtual

Suround

ACLK

LRCLK

ADATAO0

ADATAO1

ADATAO2

As appropriate

for the design

C

V

B

S

C

Y

Audio

A/D

I2S0

L

CLKI N

IEC958

Audio

Amp

IRR

UART0

R

GPIOx

GPIOx

L Audio

R Audio

Video

A/D

Unconpressed

Digit al HD I n*

LVDS Out

LCD/

PDP

FLASH

CS0

1pc 16MBx16 256Mb

DDR Memory

10/10/06 CONFIDENTIAL INFORMATION-DO NOT COPY 4

October 10, 2006 11:23 am

SupraHD-760-DTS-GEN-v1.0-Preliminary Release

Figure 3: SupraHD-760 Detailed Block Diagram

ZR39760

SADR[13:0], SBS[1:0]_n

SDQM[3:0]

SRAS_n, SCAS_n , SWE_n

SCLK, SCLK_ n, SCKE

SDQS[3:0],

SDATA[15 :0]

SVREF

Memor y

Interface Unit

(MIF)

16

4

3

3

4

16

Embedded

Processi ng Unit

(EPC)

MI PS 4Kec

I Cache

D Cache

MMU

EJTAG

Ctl r .

JTAG

Ctl r .

Counters /

Timer s

6

Transpor t

Processi ng Unit

(TRP)

Xport I /F

Xport Demux

Video Captur e

Uni t

HDMI

NTSC/ PAL

Decoder

8

Audio

Processi ng Unit

(APU)

Di spl ay

Processor

(DPC)

Graphic s

MPEG2 Decode

Uni t

(VDEC)

uControl ler

(MCU)

Sequencer

(MCE)

Flex Bus Unit

(FBU)

MIF BUS (64b)

I2 C Ctlr . 1

I2 C Ctlr . 2

I2 C Ctlr . 3

GPI O

2

2

2

4

IRR

1

I2 C0C, I 2C0D

I2 C1C, I 2C1D

I2 C2C, I 2C2D

GPIO[3:0]

IRR

UART0

2

UART0_TX, UART0_RX

BVCI

Modifi ed

Guest Bus

5

GADR[4:0]

GDAT[7:0]

6

GCS_n[5:0]

1

GWS_ACK

5

GDI R, GOE_n , GI OWR_n , GIORD_n , GWE_n

4

GIRQ[3:0]

CLKI N,

CLKOUT

BVCI/AVCI BUS (64b)

RESET_ n

Video I /F

2

9

13

HDMI_SCL , HDMI_SDA,

HDMI_CEC, HDMI_HPD, HDMI _REXT,

HDMI_D0P, HDMI_D0N, HDMI_D1P,

HDMI_ D1N, HDMI _D2P, HDMID2N,

HDMI_CLKP, HDMI_CLKN

TDO, TDI

TCK, TMS

TRST_N, TAPSEL

10

PVCI BUS (64b)

Link Li st

CLKGEN

DVCXO

PLL

2

BLT

UART1

2

UART1_TX, UART1_RX

ACLK

BCLK, LRCLK

ADATAO[ 2:0 ]

ADATAI [2 :0]

IEC958

PIXOUT[23:0],PCLK, DEN, OSDP,

AFHSI , AFVSI

HDMI

PHY

VFE_YI N, VFE_CI N,

VFE_CVBS, VFE_REFP, VFE_REFN,

VFE_VCM, VFE_I BEXT, VFE_BG

Unique 128- bit

ID

LVDS Output

1

9

LVDS_C_P, LVDS_C_N,

LVDS_D[7:0]_P, LVDS_D[7:0]_N

LVDS_REXT

L/R

Audio

DACs

4

ADATAO[ 2:0 ]

ADATAI [2 ]

Shared

with the

I2S

signal s

AGC

4

IF_AGC, AGC_SENSE, RF_AGC,

PWM_OUT

Demod

7

IFE_AI MP, I FE_VREFP, IFE_VREFN,

IFE_AINN, IFE_RBIAS, IFE_VCM, IFE_VINBIAS

Smart

Antenna

3

SADATA, GPIOx, GPIO,

8

4

TSO_CLK, TSO_FRAME,

TSO_VALID, TSO_DATA

4

TSI_CLK, TSI_FRAME,

TSI_VALID, TSI _DATA

SPI

5SPI_CLK, SPI_SI , SPI _SO,

SPI_HOLD, SPI_WEN

Loading...

Loading...