Page 1

Service Document

Service

Manual

Service

Training

Ergänzung

Supplement

Exchange Set

GDP 3560 GMK4100 / GML2900

GDP 3564 GMK9700

Es gelten die Vorschriften und Sicherheitshinweise

gemäß dem Service Manual "Sicherheit", Ma-

S

terialnummer 720108000001, sowie zusätzlich

Sicherheit

Safety

Materialnr./Part No.

720108000001

Dieses Service Dokument ist nur in Datenform verfügbar

This Service Document is only available as data

Änderungen vorbehalten/Subject to alteration

Made by GRUNDIG in Germany • TCC 0806 MP

http://www.grundig.com

die eventuell abweichenden, landesspezifischen

Vorschriften!

The regulations and safety instructions shall be valid

as provided by the "Safety" Service Manual, part

S

number 720108000001, as well as the respective

national deviations.

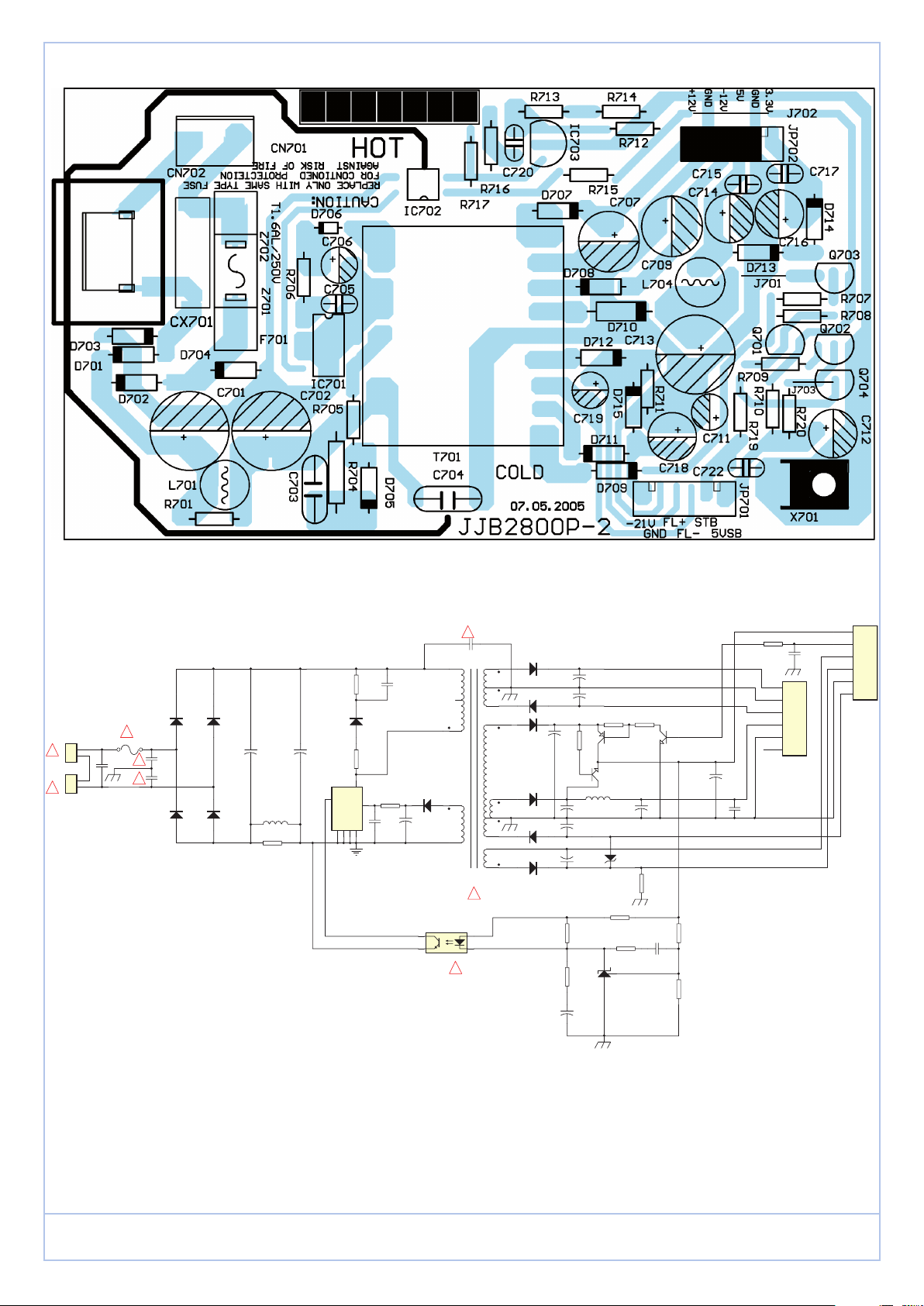

Page 2

+

C702

33uF/400V

D705

1N4007

R706

10K

D701

1N4007

D702

1N4007

D703

1N4007

D704

1N4007

+

C701

33uF/400V

R701

4.7K

L701

1.5mH

C705

0.1uF

R705

100

R704

68K/2W

C703

4n7/1KV

D712

FR102

D707

FR102

D710

1N5822

D708

FR102

D711

FR103

R711

4.7K

R712

10K

R713

10K

R715

150

+

C719

100uF/10V

+

C718

47uF/35V

+

C709

470uF/25V

+

C707

470uF/25V

+

C713

2200uF/16V

D715

6.2V

L704

10uH

C720

0.1uF

R716

3.3K

1

2 3

IC703

TL431

F701 T1.6AL/250V

D

S

S

S

S

BP

EN/UV

IC701

TNY266P

D706

1N4148

+

C706

10uF/35V

1

2

4

3

IC702

PC817

C715

0.1uF

+

C721

10uF/10V

R718

10

R717

1K

C704

2200pF

6

5

4

2

1

16

15

14

8

13

12

9

10

11

T701

TRANSFORMER

D709

FR103

R708

4.7K

R709

2K

Q701

2N5401

Q702

2N5551

+

C711

2.2uF/50V

+

C712

220uF/10V

Q703

2N5551

R707

10K

CY702

470pF

CY701

470pF

!

!

!

!

!

!

!

!

R719

1k

C722

100pF

1

2

3

4

5

6

JP701

1

2

3

4

5

6

JP702

12V

-12V

GND

GND

5V

3.3V

5VSB

STB

FLFL+

GND

-21V

+

C714

470uF/10V

1

2

ACIN

CN702

1

2

SW

CN701

CX701

0.1uF

GDP 3560, GDP 3564

Page 3

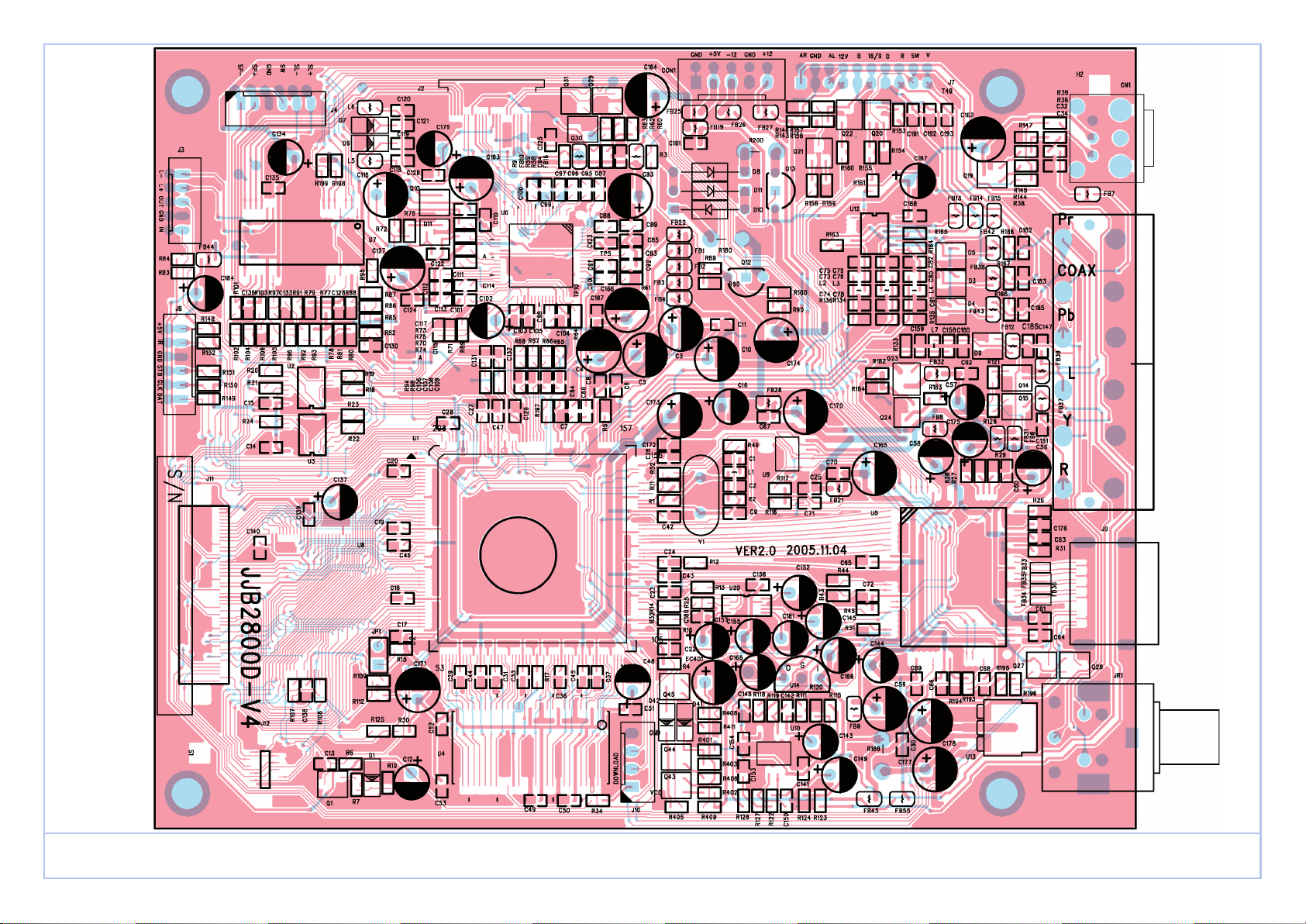

GDP 3560, GDP 3564

Page 4

HDMI_TYPE_A

SVIDEO&CVBS

AUDI O/VI DEO OUTPUT

TMDS_D2+

TMDS_D2-

TMDS_D0+

TMDS_D1+

TMDS_CLK-

TMDS_D0TMDS_CLK+

TMDS_D1-

RF33V

RFA5V

M5V

HDVCC33

DSPVCC18

IRRCV

FPC_DOUT

+12V

-12V

P5V

A-12V

CVBS_OUT

Y-R-V_OUTC-B-U_OUT

DDCCLK

DDCDAT

GND

HOTPLUG

AVCC33

COAX_SPDIF

SPDIF OPT_SPDIF

L_MAIN

C_B_U/OUT

RMAIN-OUT

LMAIN-OUT

CVBS_G_Y/OUT

COAX_SPDIF

Y_R_V/OUT Y-R-V_OUT

OPT_SPDIF

R_MAIN

FPC_STB

FPC_CLK

G-Y_OUT

C-B-U_OUT

16:9-4:3-TV

SCART_SWITCH

R_MAIN

Y_R_V/OUT

C_B_U/OUT

CVBS_G_Y/OUT

Y-R-V_OUT

C-B-U_OUT

G-Y_OUT

L_MAIN

16:9-4:3-TV

CVBS_OUT

SCART_SWITCH

IRRCV

TMDS_D2+

TMDS_CLK+

TMDS_D0-

TMDS_CLK-

FPC_DOUT

TMDS_D2TMDS_D1+

TMDS_D1TMDS_D0+

DUPTD0

DSPVCC33

HDVCC33

AVCC33

RF33V

DSPVCC18

HDVCC18

M5V

RFA5V

D+5V

A+12V

A-12V

DUPRD0

5V

CVBS_C-OUT

A+12V

DDCDAT

DDCCLK

HDMI5V

HOTPLUG

TMDSGND

SPDIF

CVBS_G_Y/OUT

RMAIN-OUT

Y_R_V/OUT

C_B_U/OUT

LMAIN-OUT

FS2

FS3

FS1

G/OUT

B/OUT

R/OUT

FPC_CLK

FPC_STB

SGND VGND AFEGNDRFGND

DSPVCC18

DA+5V

RFA5V

M5V

RF33V

D+5V

5V

D+5V

AVCC33

HDVCC33

HDVCC18

M5V

A+12V

D+5V

RFA5V

A-12V

HDVCC18

DSPVCC18

RF33V

AVCC33

HDVCC33

DSPVCC33

DSPVCC33

TDMSGND

A+12V

A-12V

DSPVCC33

5V

5V

A+12V

HDMI5V

TDMSGND

TMDSGND

HDMI5V

D+5V

DA+5V

DA+5V

A+12V

A+12V

D+5V

DSPVCC33

HDVCC33

HDVCC33

HDVCC33

JR1

RCA

12

34

6

57

8

9

1

0

C167

0.1uF

FB21 FBR(75R)

+

C164

220uF/16V

D3 BAT85

2

3

1

C34

22pF

N.C.

FB26 FBR(75R)

FB22 FBR(300R)

+

C170

100uF/10V

R150

4.7K

R167 NC

FB43 FBR(75R)

R145

180R

+

C166

220uF/16V

SMT02

1

.

C147

1nF

+

C165

100uF/16V

FB15 FBR(75R)

+

C169

47uF/16V

R152

4.7K

C161

0.1uF

FB12 FBR(75R)

+

C171

220uF/16V

SMT03

1

.

C32

0.1uF

FB38 FBR(75R)

R168 NC

T48

1

.

R157 330R

SMT04

1

.

R160 10K

CN1

OPTIC

3

2

1

GND

VCC

IN

C172

0.1uF

D5 BAT85

2

3

1

H1

1

.

C151

1nF

R146 0R

T47

1

.

+

C168

47uF/16V

1

2

3

4

5

6

7

8

9

R143 OPEN

1

2

3 4

5

678

9

1

2

3 4

5

678

9

TP23

1

.

T50

1

.

R144 68R

TP24

1

.

R196 1.8K

FB25 FBR(75R)

TP25

1

.

TP26

1

.

R147

91R

T49

1

.

R38 33R

1

2

3 4

5

678

9

1

2

3 4

5

678

9

FB42

FBR(75R)

CN8

4

9

6

11

10

5

2

3

14

1

3

1

12

78

MR

G/Y

COAX

R/V

B

/

U

ML

G

3

G2

G8

G7

G

1

G6

G5G5

1

2

3 4

5

678

9

1

2

3 4

5

678

9

FB19 FBR(75R)

FB13 FBR(75R)

C186

47P

Q20 2N3904

1

23

R151

4.7K

H2

1

.

T52

1

.

R158 10K

FB18 FBR(300R)

R156 1K

T26

1

.

R159 390R

T25

1

.

R39 68R

+

C163

220uF/16V

T51

1

.

R195 1.8K

+

C173

220uF/16V

+

C162

220uF/16V

FB44 FBR(75R)

T24

1

.

D4 BAT85

2

3

1

Q19

2N3904

1

2

3

C183

47P

T23

1

.

Q21

2N3904

1

2

3

FB37 FBR(75R)

SMT01

1

.

T22

1

.

Q22

2N3904

1

2 3

TT54

1

.

R153 150R

T38

1

.

R36 0R

T39

1

.

1

2

3 4

5

6

789

1

2

3 4

5

678

9

TT53

1

.

R155 4.7K

Q27

2N7002

1

32

FB28

FBR(75R)

T40

1

.

+

C174

220uF/16V

R148

(NC)

T41

1

.

C192

47P

T46

1

.

R149

4.7K

S1

1

.

R34 NC

T42

1

.

T43

1

.

FB39 FBR(75R)

T45

1

.

R154

4.7K

Q28

2N7002

1

32

J8

6x1 W/HOUSING

SIP6/P2.0

1

2

3

4

5

6

+

C184

47uF/16V

C193

47P

R166 NC

J9

HD port

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20212223

TDMS_D2+

TDMS_D2_SHIELD

TDMS_D2TDMS_D1+

TDMS_D1_SHIELD

TDMS_D1TDMS_D0+

TDMS_D0_SHIELD

TDMS_D0TDMS_CLK+

TDMS_CLK_SHIELD

TDMS_CLKCEC

NC

SCL

SDA

DDC/CEC_GND

+5V

HOTPLUG

GND

GN

D

GND

GND

C185

47P

1

2

3

4

5

C182

47P

FB7 FBR

C191

47P

J10

DOWN_LOAD_I/F

1

2

3

4

FB27 FBR(75R)

FB14 FBR(75R)

GND

GDP 3560, GDP 3564

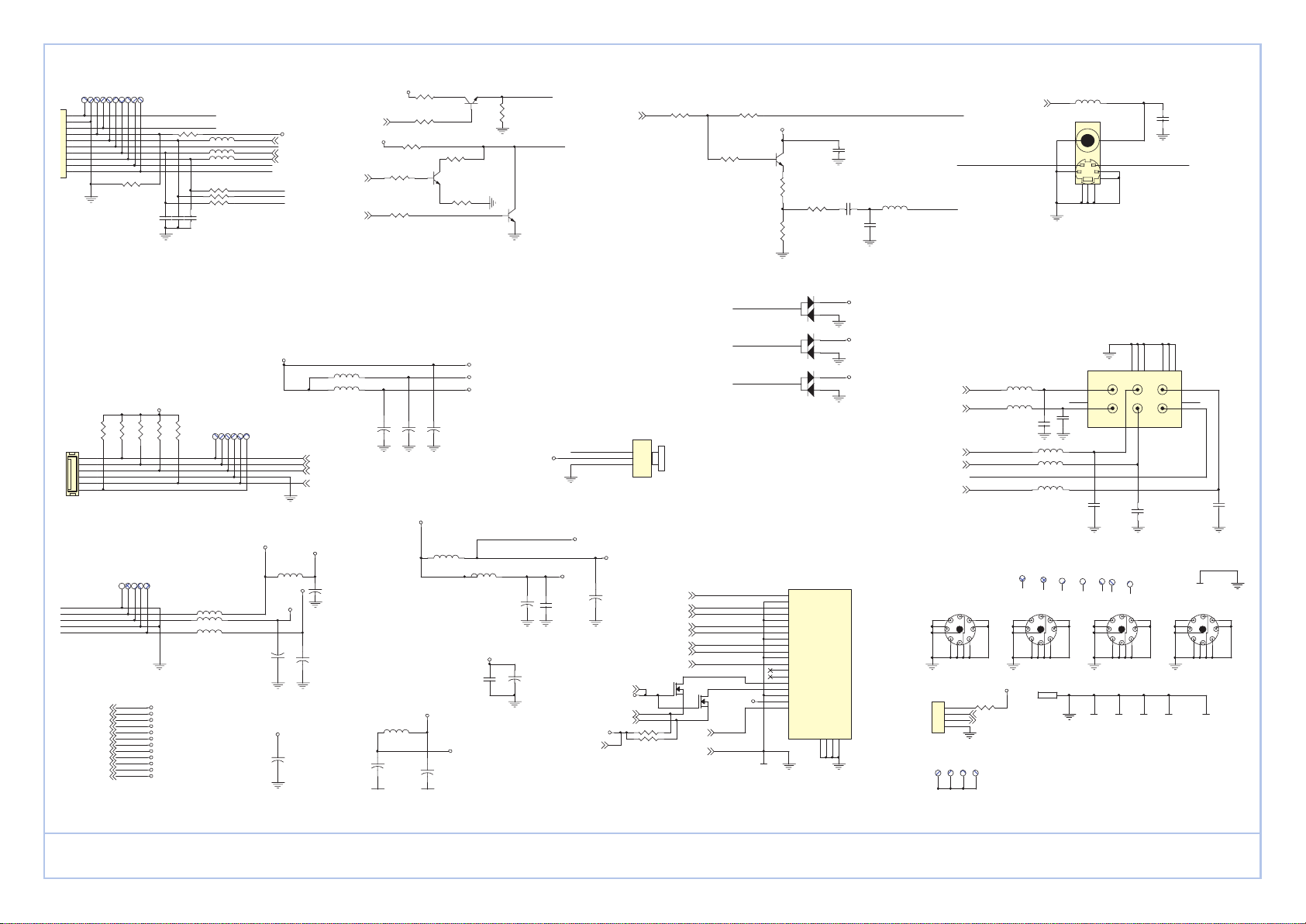

Page 5

High---mute

Low---operation

I2S UP TO 24-BIT DATA

POWER-UP/RESET

M UTE CI RCUIT

MUTE

A-L MAIN

A-R MAIN

LMAI N-OUT

HD_ DAT

HD_ CLK

RMAI N-OUT

MUTE

MUTE

ABCL K

AMCL K

VCCA

AOU T0

A-L MAIN

A-R MAIN

ALR CLK

VQ

Y_R _V-OU T

C_B _U-OU T

CVBS _G_Y- OUT

Y_R _V-OU T

CVBS _G_Y- OUT

C_B _U-OU T

HD_ CLK

LMAI N-OUT

RMAI N-OUT

HDV CC33

A+12 V

A-1 2V

HD_ DAT

AVCC 33

D+5 V

DSPV CC33

AMUTE

ALR CLK

ABCL K

AOU T0

AMCL K

GND

HDMI 5V

FS1

Y_R _V

C_B _U

CVBS _G_Y

CVBS _C-O UTCVBS _C

R/O UT

Y_R _V/OU T

B/O U T

C_B _U/O UT

G/O UT

CVBS _G_Y /OUT

A-1 2V

A+12 V

A+12 V

A-1 2V

HDV CC33

A-1 2V

A+12 V

VCC A

AVCC 33

D+5 V

DSPV CC33

A+12 V

VCCA

A+12 V

VCCA

AVCC 33

HDMI 5V

D+5 V

D+5 V

HDV CC33

R40 2

10K

C79

160 pF

C15 4

0.1 uF

+

C15 7

10u F/16V

R13 6

75R /1%

L3 1.1 uH

R11 8 12K

R16 4

NC

C14 8

1nF

C15 8 11p F

C18 0

0.1 u

Q4 3

2N3 906

1

2 3

R11 1 20K

C81

150 pF

Q1 4

2N3 904

1

2 3

R40 3

7.5 K

R11 6

1K

R40 8

1K

C15 6

0.1 uF

R16 3

NC

C75

160 pF

R41 1

1K

U12

PI5V 330

1

2

3

4

5

6

7

8 9

10

11

12

13

14

15

16

IN

S1A

S2A

DA

S1B

S2B

DB

GND D C

S2C

S1C

DD

S2D

S1D

EN

VCC

C73 11p F

C15 3

1nF

C76 11p F

R12 1

470 R

+

C15 5

47u F/16V

+

-

U10 B

LM4 5585

6

7

84

R12 3

1K

C16 0

160 pF

R16 1 220

Q4 5

2N3 906

1

2 3

R11 5

1K

D9

BAT8 5

2

3

1

R40 5 100

U9

24C 08

1

2

3

4

8

7

6

5

A0

A1

A2

GND

VCC

WP

SCL

SDA

FB45

300 R

C78

150 pF

Q4 4

2N3 906

1

2 3

U29

CS4 344 2 -CH AU DIO D AC

TSSO P10/SMD

1

2

3

4

5 6

7

8

10

9

SDIN

SCL K

LRC K

MCL K

VQ FILT+

AOU TL

GND

AOU TR

VA

R40 6 22K

C15 2

10u F/16V

C14 9

10u F/16V

R11 7

1K

R12 2 20K

C14 1

0.1 uF

C80 11p F

R12 4

10K

C82

160 pF

C14 2

120 pF

Q1 5

2N3 904

1

2

3

R40 1

1K

+

EC4 01

100 U/25V

+

-

U10 A

LM4 558

3

2

1

84

L2 1.1 uH

R12 0

10K

R40 9

1K

+

C18 1

10u F/16V

C74

150 pF

C15 9

150 pF

+

C14 4

47u F/16V

+

C18 7

47u F/16V

C14 3 1 0uF/16 V

L7 1.1 uH

R13 4

75R /1%

U14

L78 L05

1

2

3

OUT

GND

IN

C15 0

120 pF

D41

Z4.3 V(SMT)

FB55

NC( 300R )

D42

1N4 148( SMT)

R12 8

470 R

R11 9

3.9 K

R13 5

75R /1%

C18 8

0.1 uF

R13 3

75R /1%

C14 5

10u F/16V

L4 1.1 uH

R16 5

NC

R12 6

12K

R12 7 3.9K

GDP 3560, GDP 3564

Page 6

A19

NC

NC

RY/BY#

BYTE#

Flash Mem ory Configura tion:

When usin g 16Mbit INTE L FLASH,

R219=0 oh m, R210=NC

When usin g 16Mbit SST FLASH,

R210=0 oh m, R219=NC

Default i s SST mode.

Flash spe ed <= 70 nS

To flash card board

MEMAD14

MEMAD13

MEMAD12

MEMAD11

MEMAD10

MEMAD9

MEMAD8

MEMAD18

MEMAD17

MEMAD7

MEMAD6

MEMAD4

MEMAD3

MEMAD2

MEMAD1

MEMAD16

MEMDA7

MEMDA14

MEMDA6

MEMDA13

MEMDA5

MEMDA12

MEMDA4

MEMDA11

MEMDA3

MEMDA10

MEMDA2

MEMDA9

MEMDA1

MEMDA8

MEMDA0

MEMRD-

MEMAD0

MEMDA15

AMEMAD19

FLASHCS-

RESET-

MEMDA[15:0]

MEMAD15

MEMAD5

MEMWR-

MEMRD-

MEMWR-

MEMAD[19:0]

DSPVCC33

IMEMAD19

MEMCS0-

MEMAD19

FLASHCS-

MEMAD17

MEMAD15

GND

MEMAD18

MEMAD14

MEMAD11

MEMAD16

MEMAD12

MEMAD19

SSRAMCS-

MEMCS1-

SSRAMCS-

RESET-

MEMWR-

MEMRD-

MEMCS0-

MEMAD[19:0]

DSPVCC33

MEMDA[15:0]

MEMCS1-

DSPVCC33

DSPVCC33

DSPVCC33

DSPVCC33

DSPVCC33

R30

OPEN/4.7K

R112

4.7K

U8

SST39VF160

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

A15

A14

A13

A12

A11

A10

A9

A8

NC

A20

WE#

RP#

VPP

WP#

A19

A18

A17

A7

A6

A5

A4

A3

A2

A1

A16

VCCQ

GND

DQ15

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

VCC

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

OE#

GND

CE#

A0

R107 0R

C138

0.1uF

C140

0.1uF

+

C137

47uF/16V

R109 0R

R125 NC

R108 0R N.C.

J12

OPEN/CONNSOCKET10

1

2

3

4

5

6

7

8

9

10

C139

0.1uF

GND

GDP 3560, GDP 3564

Page 7

VR_SEL Logic:

CD=LOW

DVD=HIG H

CD/DVD_SW Logic:

CD=HIGH

DVD=LO W

Sw ap bet ween OPU B

input and OPU D input

LDON pull up to RFA5V:

SW control.

RFINP

RFINN

AAF_PI

DEFECT

MIRR

AAF_CE

AAF_FE

RFA_TE

RFA_PI

FNP

SVREF15

RFA_FE

RFA_SDEN

AAF_TE

FNN

RFA_SDATA

OPU_F

VC25

OPU_E

TACT+

CDLD

FACT+

DVDLD

OPU_A

OPU_C

Lase rMD

AAF_CE

RFA_CE

OPU_B

TACT-

FACT-

AAF_CE

AAF_FE

AAF_TE

AAF_PI

RFINN

RFINP

VR_SEL

DEFECT

MIRR

RFA_SDEN

RFA_SCLK

SVREF15

LINK

RFA5V

RFA_SDATA

RFA5V

RFA5V

RFGNDRFGND

RFGND

RFGND

RFGND

RFA5V

RFGND

RFGND

RFA5V

RFA5V

RFA5V

RFGND

RF33V

RFA5V

T12

1

.

C125

0.1uF

C123

0.1uF

R62

10K

C1

1

9

0

.1uF

C98 470pF

C122

0.1uF N.C.

R

70

4.

7K

R67 1.3K

R9

100

T15

1

.

FB10

FBR(300R)

T181

.

2V1

1

.

T161

.

C103 0.

1

u

F

R66 2.7K

C105

0.1uF

R65 NC

R73 220R

R59

1K

R61 12K/1%

T6

1

.

R76 22R

C109560p

F

C179

47uF/16V

C

113

220pF

C114 0

.

1uF

Q29

2N3904

1

23

C115

2.7nF

C87

1nF

R63

2K

C95 2.2nF

+

C93

100uF/16V

TP10

1

.

R60

1.2K

C101 0.1uF

L6

10uH

C99 2.2nF

U6

ZR36707

1

2

3

4

5

6

7

8

9

10

11

12

13

14

31

20

2

9

2

3

24

2

8

26

1

9

2

5

18

33

2

7

22211

7

44

45

46

37

30

40

42

43

35

48

47

38

41

39

36

32

5

2

53

5

4

61

5

8

6

4

63

51

5049

59

57

6

2

6

0

5

5

5

6

15

16

34

DVDRFP

DVDRFN

A2

B2

C2

D2

CP

CN

D

C

B

A

CD_D

CD_C

M

I

N

V

C

MB

D

VD

P

D

CD

P

D

MPLDO

N

V

P

B

V

NB

CD_

E

LINK

M

I

R

R

C

D

L

D

DVDLDCD_F

LCP

V33

SCLK

V25

ML

P

F

FE

MNTR

LCN

TPH

SDEN

SDATA

PI

CE

TE

V125

M

EV

O

FNN

FNP

DIP

A

T

ON

VP

A

R

FDC

RFS

IN

V

N

A

ME

V

R

X

A

I

P

RF

A

C

ATOP

AI

N

D

I

N

BYP

CD_B

CD_A

DFT

Q31

2N3904

1

2

3

J2

24P-HEAD

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

2

5

26

272

8

GND-LD

DVD-LD

NC

HFM

MD

CD-LD

VR-DVD

VR-CD

NC

E

VCC

VC(VREF)

GND/PD

F

B

A

RF

CD/DVD_SW

D

C

TT+

F+

F-

G

ND

G

ND

GNDGN

D

C126

0.1uF

C11

8

0.

1

u

F

T19

1

.

C8

8

1nF

T17

1

.

C124

0.1uF

T8

1

.

R69 4.7K

R58

4.7K(NC)

TP7

1

.

C1

0

6

5

.

6

n

F

T71

.

T141

.

+

C116 100uF/16V

C1

0

8

5

.

6nF

+

C127 100uF/16V

C110 0.1

u

F

Q30

2N3904

1

2

3

TP51

.

C120 0

.

1uF

T5

1

.

R64 0R

C96 2.2nF

C100 33pF

C83 33nF

T9

1

.

D7

1N4148

12

R74 13K

T10

1

.

C86 1nF

C

911

n

F

C117

0.1uF

N.C.

Q11

8550

1

2 3

C84 1nF

D6

1N4148

1 2

C

1

2

1

0

.

1u

F

C1075

.

6

nF

L5

10uH

C104

0.1uF

C92 1nF

+

C102

4.7uF/16V

T11

1

.

T131

.

TP9

1

.

R71

9.1K

C85

0.1uF

T1

1

.

T2

1

.

C

8

9

1

nF

C94

0.1uF

C11

2

2

2

n

F

T3

1

.

TP6

1

.

T4

1

.

R75 220R

C

901

n

F

R72 22R

R68 1.3K

TP11

1

.

TP18

1

.

Q10

8550

1

23

TP8

1

.

C97 2.2nF

C111

6

.8

n

F

GDP 3560, GDP 3564

Page 8

CD/DVD_SW Logic:

CD=HIGH

DVD=LO W

Sw ap bet ween OPU B

input and OPU D input

LDON pull up to RFA5V:

SW control.

AAF_PI

DEFECT

MIRR

DSPVCC33

AAF_CE

AAF_FE

RFA_TE

RFA_PI

SVREF15

RFA_FE

RFA_SDEN

AAF_TE

RFA_SDATA

OPU_F

VC25

OPU_E

TACT+

CDLD

FACT+

DVDLD

OPU_A

OPU_C

Lase rMD

LOADLOAD+

MOT_SPDL-

AAF_CE

RFA_CE

REGO2

TR_B1

TR_B2

REGO1

TR_B1

REGO2

SLED_PWM1

REGO1

LOADLOAD+

FACTFACT+ TACT+

TACT-

MOT_SPDL+

MOT_SPDL-

FOCUS_DAC2

MONTIN

SPINDLE_PWM1

SPDL_SENS

TR_B2

TRACK_DAC1

DRVSB

VC2

MONTIN

SLEDSLED+

SLED-

MOT_SPDL-

SLED+

MOT_SPDL+

OPU_B

HOMESW

CLOSE

OPEN

TACT-

FACT-

INSW

OUTSW

SPDL_SENS

AAF_CE

AAF_FE

AAF_TE

AAF_PI

DEFECT

MIRR

RFA_SDEN

RFA_SCLK

SVREF15

LINK

RFA_SDATA

DSPVCC33

FOCUS_DAC

SLED_PWM

CLOSE

OPEN

M5V

SPINDLE_PWM

TRACK_DAC

RF33V

VBIASS1

DRVSB

DSPVCC18

HOMESW

5V

RFGNDRFGND

RFGND

RFGND

RFA5V

RFGND

RFGND

RFGND MGND

RFA5V

RFA5V

SGND

RFGND

RF33V

MGND

M5V

RF33V

MGND

DSPVCC18

DSPVCC33

M5V

M5V

RF33V

RF33V

MGND

MGND

MGND

MGND

MGND

MGND

MGND

MGND

DSPVCC18

RF33V

5V

T12

1

.

R100

12k

C125

0.1uF

C123

0.1uF

R199 4.7K

R62

10K

C1

1

9

0

.1uF

C98 470pF

C122

0.1uF N.C.

R

70

4.

7K

R67 1.3K

R9

100

R96 5.6K

T15

1

.

FB10

FBR(300R)

T181

.

C129

0.1uF

R98 11k

2V1

1

.

T161

.

C103 0.

1

u

F

R104

1M

R66 2.7K

C105

0.1uF

R65 NC

R82 5.6K

R73 220R

Q13

2SS8550D

2

1

3

R95

6.8K

C136

0.1uF

T6

1

.

R76 22R

C109560p

F

J4

SLED & SPINDLE

1

2

3

4

5

6

C179

47uF/16V

C

113

220pF

C114 0

.

1uF

J3

5PIN

1

2

3

4

5

C115

2.7nF

R63

2K

C95 2.2nF

R81

10K/1%

+

C93

100uF/16V

TP10

1

.

C133

560pF

R97 0R

R83

4.7K

C101 0.1uF

R94 11k

R102

3.6K

Q12

2SS8550D

2

13

R93 5.6K

L6

10uH

C99 2.2nF

D11

1N4001,DIP

2

1

R77

470R/1%

U6

ZR36707

1

2

3

4

5

6

7

8

9

10

11

12

13

14

31

20

2

9

2

3

24

2

8

26

1

9

2

5

18

33

2

7

22211

7

44

45

46

37

30

40

42

43

35

48

47

38

41

39

36

32

15

16

34

DVDRFP

DVDRFN

A2

B2

C2

D2

CP

CN

D

C

B

A

CD_D

CD_C

M

I

N

V

C

MB

D

VD

P

D

CD

P

D

MPLDO

N

V

P

B

V

NB

CD_

E

LINK

M

I

R

R

C

D

L

D

DVDLDCD_F

LCP

V33

SCLK

V25

ML

P

F

FE

MNTR

LCN

TPH

SDEN

SDATA

PI

CE

TE

V125

M

EV

O

FNN

FNP

DIP

A

T

ON

VP

A

R

FDC

RFS

IN

V

N

A

ME

V

R

X

A

I

P

RF

A

C

ATOP

AI

N

D

I

N

BYP

CD_B

CD_A

DFT

Q31

2N3904

1

2

3

J2

24P-HEAD

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

2

5

26

272

8

GND-LD

DVD-LD

NC

HFM

MD

CD-LD

VR-DVD

VR-CD

NC

E

VCC

VC(VREF)

GND/PD

F

B

A

RF

CD/DVD_SW

D

C

T-

T+

F+

F-

G

ND

G

ND

GNDGN

D

C126

0.1uF

C132

27nF

C11

8

0.

1

u

F

T19

1

.

R87

5.1K

R101

10K

T17

1

.

C124

0.1uF

T8

1

.

R91 22K

R69 4.7K

C1

0

6

5

.

6

n

F

T71

.

C131

27nF

T141

.

+

C116 100uF/16V

C1

0

8

5

.

6nF

+

C127 100uF/16V

R200

1.2R/1W

R79

470R/1%

C110 0.1

u

F

2

R105 3.3K

C120 0

.

1uF

T5

1

.

R64 0R

R86 5.6K

C135

0.1uF

C96 2.2nF

C100 33pF

T9

1

.

D7

1N4148

12

R74 13K

T10

1

.

D10

1N4001,DIP

21

R198 4.7K

C117

0.1uF

N.C.

Q11

8550

1

2 3

D6

1N4148

1 2

T27

1

.

C

1

2

1

0

.

1u

F

C1075

.

6

nF

L5

10uH

C134

47uF/16V

T28

1

.

R103

4.7K

R88 4.7K

C104

0.1uF

T29

1

.

R106

27K

T30

1

.

+

C102

4.7uF/16V

T11

1

.

T31

1

.

T131

.

R78

10K/1%

TP9

1

.

R71

9.1K

T32

1

.

C130 560pF

T1

1

.

C128

0.1uF

T37

1

.

T2

1

.

T36

1

.

C94

0.1uF

C11

2

2

2

n

F

T3

1

.

T35

1

.

T4

1

.

T34

1

.

U7

AM5869 S

1

2

3

4

5

6

7

8

9

10

11

12

13

14 15

16

17

18

19

20

21

22

23

24

25

26

27

28

29 30

VINFC

TRB_1

REGO 2

VINSL+

REGO 1

FWD

REV

Vcc1

VOTRVOTR+

VOSL+

VOSLVOFCVOFC+ VOTK+

VOTK-

VOLD+

VOLD-

Vcc2

OPIN

VCTL

GND

VINLD

OPOUT

TRB_2

VINTK

BIAS

MUTE

G1 G2

R84

4.7K

R75 220R

R89

4.7k

T33

1

.

R180

2.4R/2W

R92 5.6K

R72 22R

R68 1.3K

R85 5.6K

R99

10k

TP11

1

.

TP18

1

.

D8

1N4001,DIP

21

Q10

8550

1

23

1

R90

20k

R80

10K/1%

C97 2.2nF

C111

6

.8

n

F

GND

GDP 3560, GDP 3564

Page 9

JP20,JP21 settings:

1)Play mode: All Jumps off

2)Download mode: JP21's 1-2 short

3)SW Debug mode: JP20's 1-2 short

Download

NMI

AMCLK

P

CLK

VCLKX2

HD_CLK

HD_DAT

I

7

6I

O

-F

C

HOMES W

-

FC

UI

F

3

5

VID2

RAMCKE

MEMAD17

MEMDA13

MEMAD11 PLLCFGP

MEMRD-

M

IR

R-

F

CUIF

30

SPDIF

GCLKA

RAM

DQ

M

MEMWR-

F

PC

_CL

K

INSW

MEMAD3

MEMAD4

RAMDA

T

13

RAMADD8

MEMDA2

MEMDA14

MEMDA0

RAMDAT3

RAMDAT

1

2

RA

M

DAT

8

RAMA

DD

1

1

RA

MADD0

F

C

UIF34

DUPTD0

MEMAD2

RAM

A

DD4

MEMDA9

FCCS-

RFA

S

DATA-

F

CUIF36

RESET-

RAMA

D

D6

MEMAD6

MEMDA10

MEMDA15

MEMAD12 PLLCFGA

MEMAD13

VID5

RAM

W

E-

RA

M

ADD

9

RAM

ADD2

MEMAD9

MEMDA7

OUTSW

MEMCS0-

RAMDA

T

0

RAMADD5

OSCIN

VID0

VID4

HSYNC

R

AM

D

AT7

RA

MR

AS

-

RAMADD7

RAMADD3

IRRC V

RF

AS

D

E

N-F

CU

IF3

2

VID3

VID7

RA

MDAT2

RAMDAT4

RAM

DAT1

0

MEMDA12

MEMAD10

OSCOUT

RAM

DA

T1

5

RAM

D

AT6

RAMDAT9

MEMAD14

FPC

_

STB

VID6

MEMAD1

R

A

MD

AT1

RAMCS-

MEMAD18

RFA_

SC

LK

DEF

E

C

T-

F

C

UI

F37

RAM

D

AT1

4

RA

M

D

A

T

1

1

IP

CLK

R

AM

B

A

0

RAMADD10

DRVSB

FPC_D OU

T

MEMAD5

OSCOUT

VID1

MEMAD16

IAMCLK

R

A

M

CAS-

MEMDA4

MEMDA6

MEMDA8

RAMADD1

MEMAD19

MEMDA11

MEMDA5

MEMAD8

SPD

L

_

SENS

-

FCUI

F

31

VSYNC

DUPRD0

RAM

D

A

T

5

RA

M

BA1

MEMDA1

MEMAD7

MEMDA3

MEMAD15

OSCIN

MEMAD0

MEMCS1-

GND

GND

ABCLK

ALRCLK

AOUT0

FPC

_C

LK

DRVSB

F

P

C_

ST

B

RF

A_

SC

L

K

MEMWR-

MEMRD-

MEMCS0-

MEMAD[19:0]

SPDIF

AOUT0

ALRCLK

ABCLK

AMCLK

VSYNC

HSYNC

VCLKX2

C_B_U

Y_R_V

CVBS_C

CVBS_G_Y

S

LE

D

_

PWM

SPI

NDL

E_

PW

M

V

B

I

ASS1

SV

R

EF15

A

A

F_

PI

A

AF_TE

AAF

_

FE

A

AF

_

CE

LINK

RFI

NN

RF

INP

FOCU

S_DAC

TRA

C

K_D

A

C

INSW

OUTSW

HD_CLK

DUPTD0

DUPRD0

VID4

VID1

VID5

VID2

VID6

VID3

VID0

VID7

IRRC V

D

DCC

L

K

FPC_

D

OUT

OSCOUT

GCLKA

VR_

SEL

DDC

DAT

MEMDA[15:0]

HD_DAT

RESET-

MEMCS1-

DSPVCC33

VGND AFEGND SGND

VGND

DSPVCC33

DSPVCC18

DSPVCC33

DA+5V

C8

0.1uF

R32 33R

FB3 FBR(300R)

R16

4.7K

R1

7

0R

R1

9

7 0RN.C

.

C9

22pF

+

C12

10U16V

C2 22pF

FB2 FBR(300R)

R10

10K

+

C10

100uF/16V

R7

100

FB4

FBR(300R)

JP1

Jumper2.0

N.C.

1

2

R13 33R

R6

10K

C13

0.1U

+

C3

100uF/16V

+

C5

100uF/16V

D1

1N4148(SMT)

R15

4.7K(NC)

C7

0.1uF

Q1

9014

R5 392 ohm/1 %

C1

220pF(NC)

+

C4

100uF/16V

T201

.

Y1

27.000MHz

FB1 FBR(300R)L1 2.7uH(NC)

R11 0R

U1

ZR36778/ZR36770

12

1

2

3

4

5

6

7

8

9

10

11

50

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

51

52

535455

6

2

56575859

606172636

4

65

66676

8

6

9

70

7

1

83

73

74757677

7879808182918485868788

8

9

90

1

0

1

9

29394

95

96979899

1

0

0

102

1

0

3

1

04

105

156

155

154

152

151

145

136

144

143

142

141

140

139

138

127

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

2

0

5

204

2

02

19

2

190

20

0

18

7

195

197

18

6

1

85

18

4

1

7

5

1

74

1

7

3

172

1

7

1

157

1

69

1

60

1

6

7165

164

163

162

16

1

159

1

58

39

40

41

42

43

44

45

46

47

48

49

106

107

108

109

126

128

129

130

131

132

133

134

135

137

146

147

148

149

150

153

1661

68

1

7

0

183

1

82

181

180

179

1

7

8

177

1

7

6

1

88

1

8

9191

1

9

3

194196

19

8

199

2

01203

2

0

6

2

0

7

2

08

GNDP

SSCRXD/GPCIO[17]

MEMCS[1]#/GPCIO[18]

VDDP

MEMAD[15]

MEMAD[16]

MEMAD[14]

MEMAD[13]/FCUIF29

MEMAD[12]/[PLLCFGA]

MEMDA[15]/FCUIF28

MEMAD[11]/[PLLCFGP]

MEMDA[7]/FCUIF9

GNDP

MEMAD[10]/FCUIF20

MEMDA[14]/FCUIF27

MEMAD[9]/FCUIF19

MEMDA[6]/FCUIF8

MEMAD[8]/FCUIF18

MEMDA[13]/FCUIF26

MEMDA[5]/FCUIF7

MEMAD[20]/[GPCIO19]/[MEMCS#2]

VDDP

MEMDA[12]/FCUIF25

MEMWR#/FCUIF0

MEMDA[4]/FCUIF6

VDDC

MEMDA[11]/FCUIF24

MEMDA[3]/FCUIF5

MEMAD[19]/[PLLSE L]

GNDC

MEMDA[10]/FCUIF23

MEMAD[18]

GNDP

MEMDA[2]/FCUIF4

MEMAD[17]

MEMDA[9]/FCUIF22

MEMAD[7]/FCUIF17

MEMDA[1]/FCUIF3

MEMAD[6]/FCUIF16

VDD-IP

VDDP

RAMADD

[

4]

RA

MA

D

D[

3

]

RAM

AD

D[

5

]

G

N

DP

RA

MADD

[2

]

RAM

A

DD[6 ]

VDDP

RA

M

ADD[1

]

RAM

AD

D[

7]

R

A

M

ADD

[

0

]

GND

P

RAMADD [8]

V

DD

C

RA

M

ADD[

1

0

]

GN

D

C

R

A

M

A

DD[

9

]

VD

D

P

RAM

ADD

[

1

1

]

RAMCS[

0

]#/

RAM

B

A[

1]

RAMBA[0 ]

G

NDP

RA

MC

S

[1]#

RA

M

R

AS#

RAMCAS #

VDDP

RA

M

WE#

RAM

DQM

G

N

D

PCLK

PCL

K

VDDPC LK

RAMDA

T[

8]

GN

DP

RAMDAT[ 7]

RAMDA

T

[

9]

RAM

DA

T

[

6]

VDDP

RA

M

DA

T

[10

]

RAMDAT[ 5]

R

A

M

DA

T

[

1

1]

G

N

D

P

RA

MDA

T

[

4]

V

D

DC

R

AMDAT[

12

]

GND

C

R

AM

DAT

[

3

]

VDDP

RA

M

DA

T[1

3

]

RA

MDAT[

2]

RA

M

DAT

[1

4

]

RAMDAT[ 1]

RAM

D

A

T

[1

5

]

RAMD

A

T[

0

]

VDDP

DUPTD1/GPCIO38

DUPRD1/GPCIO37

VDD-IP

DUPRD0/GPCIO35

GNDP

VDDP

VID[1]/DJTDO/GPCIO30

GCLKA/GPCIO31

GCLKP

XO

VDDA

RESET#

GNDA

GNDP

VDDP

GNDP

HSYNC/GPCIO25/[CJTDO]

VDDC

VSYNC/GPCIO24/[CJTDI]

GNDC

AIN/[GPCIO23/CJTCK]

VDDP-A2

AMCLK

GNDP-A2

ABCLK

ALRCLK

GPAIO/[AOUT3]/IDGPCIO[0]

AOUT[0]

AOUT[1]/[GPCIO22]

AOUT[2]/[GPCIO21]

SPDIF

SLEDP U

L

SE/IDG PCIO6/ FCUIF30

VDD

P

GND

P

V

D

D

C

GNDC

DEFECT/ IDGPCIO 5/FC

U

IF3

7

PWMACT [0]

/

GPCI O39

G

NDPW

M

V

DD

PW

M

GNDA FES

VBIASS1VBIA

SS0

V

D

DA

FE

S

GNDA

F

ERF

R

F

INN

RFINP

V

DDAF

ERF

GN

DDACD

DA

C

D

RIVE

[

1]

VDDDA C

D

A

CD

RI

VE[0

]

G

NDDA

CB

S2

GNDD AC

P

RSET

C

/B

/U

Y

/R

/

V

CVBS/C

CV

BS

/

G/

Y

MEMDA[8]/FCUIF21

MEMAD[5]/FCUIF15

VDDP

MEMDA[0]/FCUIF2

MEMAD[4]/FCUIF14

MEMRD#/FCUIF1

MEMAD[3]/FCUIF13

MEMAD[2]/FCUIF12

MEMCS[0]#

MEMAD[1]/FCUIF11/[BOOTSEL2]

MEMAD[0]/FCUIF10/[BOOTSEL1]

GPCIO[20]/CPUNMI

GNDP

ICGPCIO0/AOUT[3]

IDGPCIO0/RAMCLKE

VCLKx2/CJTMS/ICGPCIO[1]

VID[7]/ICETMS/GPCIO26

VID[6]/ICETDI/ICGPCIO2

VID[5]/ICETDO/IDGPCIO1

GNDP

VID[4]/ICETCK/GPCIO27

VID[3]/DJTMS/GPCIO28

VID[2]/DJTDI/GPCIO29

VDDP

VID[0]/DJTCK/ICGPCIO3

ICGPCIO4

GPCIO33/SPDIFOIN

ICGPCIO5

GPCIO34/SPDIFCIN

IDGPCIO3/FCUIF33

DUPTD0/GPCIO36

GND

DACPS

V

D

DD

A

C

S

GND

DA

C

DS

A

D

CI

N0

A

DCIN 1

ADCIN 2

ADCIN 3

A

DC

I

N4

AD

CI

N5

ADCIN

6

ADCIN 7

PW

M

A

CT[1

]/

G

P

CI

O4

0

P

WM

CO

[0

]/

GP

CIO4 1

P

W

M

CO[

1

]

/

GP

CI

O4

2

PW

M

CO[2 ]/

GP

C

I

O43 /FCUIF34

P

WMCO

[3

]

/

ID

GPCI O

44/FC

UI

F35

PWMCO

[

4]/

G

P

CI

O

45

PW

M

CO[5

]

/GPC IO46/FC UIF36

PWMCO [6]

/

I

DG

PC

I

O

4

/F

C

UI

F

32

I

C

G

P

CI

O

6

I

C

GPC

I

O7

SPI

NDLE D

P

U

LSE/I DGPC

IO

7/F

C

UIF3

1

SSC

C

LK/

GPCI O47

SS

CT

XD

/G

PC

IO

1

6

R14 33R

R12 0R

C11

0.1uF

R3 0

R

N.C

.

R2

100K

C6

0.1uF

R25 33R

R1 0R

GND

GDP 3560, GDP 3564

Page 10

IO Arrangement in 4-in-1:

FCUIF30---XWAIT(CF)

FCUIF31---CMD(SD) & BS(MS) &CS1(CF) & CE(SM)

FCUIF32---BSY(SM) & DATA0(MS/SD) & BSY(CF)

FCUIF34---WP(SM) & SCLK(MS/SD)

FCUIF35---DATA1(MS/SD) & CS2(CF)

FCUIF36---DATA2(MS/SD) and Reset(CF)

FCUIF37---DATA3(MS/SD)

I76IO-FC---ADCIN pin;Option for All_CD signal(need SW match).

I77IO-FC1---WP(write protection) in SD/SM

GND

MEMAD4

MEMDA14

FCRST-

GND

MEMDA5

MEMDA1

MEMAD3

MEMAD10

MEMDA4

MEMDA2

FCUIF35

GND

I76IO-FC

MEMDA13

DSPVCC33

HDIO-FC4

MEMAD6

HDIO-FC2

MEMAD5

FCUIF32

MEMDA15

MEMDA6

MEMDA0

MEMAD0

MEMAD7

FCUIF31

DSPVCC33

FCCS-

FCUIF30

MEMWR-

MEMDA7

MEMDA3

MEMDA9

MEMAD2

MEMAD13

MEMAD9

MEMDA12

FCUIF34

MEMDA10

MEMAD1

FCUIF36

GND

MEMDA11

FCUIF37

MEMAD8

MEMRD-

GND

MEMDA8

DSPVCC33

HDIO-FC4

FCRST-

HDIO-FC2

DSPVCC33

J11

OPEN/FFC-50

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

Assembly No te:

In HW verif ication of first s tage,

In stall R8 8, R89, R90, R91, R100, R103, R106, R352, R113, R114.

Not install U1, U3, R112, R11 1, C1, C20.

SPDL_SENS

FCUIF31

FCUIF30

FCUIF37

MIRR

DEFECT

MIRR-FCUIF30

SPDL_SENS-FCUIF31

DEFECT-FCUIF37

HOMESW

RFA_SDEN

RFA_SDATA

MIRR

SPDL_SENS

DEFECT

DA+5V

RFASDEN-FCUIF32

FCUIF32

FCUIF36

RFA_SDEN

RFA_SDATA

FCUIF35

SER_FLSH_ON

RFASDATA-FCUIF36

HOMESW-FCUIF35HOMESW

HOMESW-FCUIF35

RFASDATA-FCUIF36

RFASDEN-FCUIF32

DEFECT-FCUIF37

MIRR-FCUIF30

SPDL_SENS-FCUIF31

SPDL_SENS

HOMESW

MIRR

SER_FLSH_ON

RFA_SDEN

RFA_SDATA

DEFECT

DA+5V

DSPVCC33

R19 0R

R20 0R

R21 0R

R18 4.7K

R22 0R

R23 0R

R24 0R

EN

G1

1

1

MUX

GND

VCC

U2

FST3257 N.C.

16

8

15

1

2

3

5

6

11

10

14

13 12

9

7

4

EN

G1

1

1

MUX

GND

VCC

U3

FST3257 N.C.

16

8

15

1

2

3

5

6

11

10

14

13 12

9

7

4

C14

0.1uF

C15

0.1uF

64Mbit SDRAM

RA

MD

A

T

9

RAM

B

A

1

RA

MADD0

R

A

M

D

A

T

13

RA

MADD

3

RAMBA

0

RAMDAT 7

RAMAD D1

RAMDAT 11

RAMAD D5

RAMD

QM

RAMDAT 4

R

AM

DA

T0

RA

M

A

D

D

7

R

A

M

W

E

-

RAMCKE

RA

MADD

4

RAMCA S

-

RAM

A

DD6

RAM

DA

T3

RAMCS-

R

AM

D

AT1

5

RAMDQ M

PCLK

R

A

MDA

T6

R

A

MA

DD

9

RAMDAT 8

RAMADD1

1

R

AM

DAT

2

RAMDAT 14

R

A

M

DAT

1

2

RAMRAS -

RAM

ADD8

R

AMDAT

1

0

RAMDAT 1

RAMADD2

RA

MADD10

RAMDAT

5

R

A

M

C

KE

DSPVCC33

C51

0.1uF

R4

4.7KC52

0.1uF

U4

IC42S16400

2324252

6

2

9

3031323334

2

2

3

5

37

19

16

457810

1113 4

2

2

4445

47

48

5

0

51

5

3

3817

18

15

3

9

36

40

41

5

4

6

12

46

52

1

4

27

3

9

49

43

1

28

20

21

A0

A

1

A2

A3 A

4

A5

A

6A7

A8

A9

A1

0

A

11

CKE

CS

WE

D

Q1

DQ2DQ3

DQ4

DQ5

DQ

6

DQ7 DQ8

D

Q

0

D

Q9

D

Q1

0

DQ1 1

D

Q

1

2

D

Q1

3

DQ

1

4

DQ

1

5

CLKC A

S

RAS

DQML

D

Q

M

H

N.C

N.C

V

S

S

VS

S

V

S

S

Q

V

SS

Q

VSSQ

VSSQ

VDD

VDD

VDDQ

VDDQ

V

D

D

Q

V

DDQ

V

DD

VSS

BA

0

B

A

1

C53

0.1uF

For VD D pins o f SDRAM

C49

0.1uF

+

C48

47uF/16V

C50

0.1uF

For VD DP pins of I 76

except for SDRA M part

For VD DC pins of I76

Specia lly for V DDP pins of I76(SD RAM port)

DSPVCC18

DSPVCC33

DSPVCC33

DSPVCC33

DSPVCC18

DSPVCC33

DSPVCC18

DSPVCC18

DSPVCC33

DSPVCC33

C23

0.1uF

C22

0.1uF

C43

0.1uF

C27

0.1uF

+

C16

47uF/16V

C44

0.1uF

C28

0.1uF

C31

10nFC47

0.1uF

C33

10nF

C42

0.1uF

C24

0.1uF

C18

0.1uF

C25

0.1uF

C26

0.1uF

C20

0.1uF

C29

10nF

C37

10nF

C17

0.1uF

C36

1nF

C45

0.1uF

C46

0.1uF

C19

0.1uF

GDP 3560, GDP 3564

Page 11

BLANK SIGNAL

HIGH(1~3V)

CVBS

RGB

FUNCTION

LOW(0V)

TV

4:3

~6V

SWITCH VOLTAGE

16:9

~0V TV

FUNCTION

~0V

~11V

J602

SCART I/F

1

2

3

4

5

6

8

7

9

10

R_MAIN

GND

L_MAIN

GND

C-B-U_OUT

ASPECT

Y-R-V_OUT

G-Y_OUT

RGB/CVBS

CVBS_OUT

J601

SCART

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

AOR

AIR

AOL

AGND

BGND

AIL

B

SWITCH

GGND

CLKOUT

G

DATA

RGND

DATAGND

R

BLANK

VGND

BLANKGND

VOUT

VIN

SHIELD

GDP 3560, GDP 3564

Page 12

F1

1

F1

2NP31G42G53G64G7

5G8NC

9

NC

10

NC

11NC12

NC

1

3

P

1

14

P2

15P316

P4

17

P5

18

P

6

1

9

P7

20

P8

21

P

9

22

P10

2

3

P11

24

P12

25

P13

26

P1

4

27

P15

28

P16

29

NC30F

2

31

F2

32

U802

HL-D125G

O

U

T

1

GND2Vs

3

GND

4

GND

5

U801

AT136BT-12DW

SW11SW22SW33S

W

4

4

D

O

U

T

5

DIN6VSS17CLK

8

S

T

B

9

KEY1

10

K

E

Y2

11

KEY3

12

KEY4

13

VDD1

14

SEG1/KS1

15

SEG2/KS2

16

SEG3/KS3

17

SEG4/KS4

18

SEG5/KS5

19

SEG6/KS6

20

SEG7

21

SEG8

22

S

EG9

23

SEG10

24

S

EG11

25

S

E

G12/GR

I

D

1

1

26

VEE

27

SEG13/

G

RI

D

10

28

SEG14

/

GR

I

D9

29

SE

G15

/GRI

D8

30

SEG16/

G

RID7

31

G

RI

D6

3

2

GRID5

3

3

GRID4

34

GRID3

35

GRID2

36

GRID1

37

VDD2

38

LED4

39

LED3

40

LED2

41

LED1

42

VSS2

43

OSC

44

U803

PT6312BLQ

R813

47K

R801

10R

R812

10K

R811

10K

+

E804

10V100uF

+

E801

10V100uF

C803

0.1uF

D802

1N4148

D803

1N4148

R805

10K

R809

10K

R810

10K

SW801

OPEN/CLOSE

SW805

NEXT

SW803

STOP

SW802

PLAY

VCC

F1F2

VEE

VCC

VCC

IR0

STB

C

L

K

Din/out

KS1

KS

2

KS1

KS2

KS3

VCC

R804

10K

R803

10K

R807

OPEN/10K

LED3

DIN/OUT

STB

GND

CLK

VCC

GND

VEE

F1

F2

IR

1

2

3

4

5

6

JP801

6PIN

1

2

3

4

5

6

7

JP802

7PIN

LED3

C805

100PF

C804

100PF

1

1

2

2

3

3

X801

455KHZ

R802

10R

KEY1

PSW

E805

100U/10V

C802

104

LED1

IR0

VCC

1

1

2

2

3

3

445

5

6

6

7

7

8

8

U804

PT8311-GDP

R814

470R

LED801

LED

SW804

PREV

PSW

LED4

K

S

LED1

R806

10K

R808

OPEN/10K

+

E803

22U/35V

IR0 IR

D801

1N4148

LED4

E802

22U/35V

C801

104

KEY1

KEY2

KEY3

R815

100

VC

C

GDP 3560, GDP 3564

Page 13

Ersatzteilliste

Spare Parts List

DVD

2 / 2006

BESTELL-NR. / ORDER NO.: GMK4100

POS. NR. ABB. MATERIAL-NR. ANZ. BEZEICHNUNG DESCRIPTION

POS. NO. FIG. PART NUMBER QTY.

GMK4100 GDP 3560 GDP 3560

TAUSCHGERAET EXCHANGE SET

0010.000 296420660200 TP 81 D FERNBEDIENUNG (GRAU) TP 81 D REMOTE CONTROL (GREY)

720116059500 BEDIENUNGSANLEITUNG D, GB INSTRUCTION MANUAL D,GB

720116059600 BEDIENUNGSANLEITUNG (CD-14SPR.) INST.MAN (CD)

HINWEIS! NOTE!

IM DEFEKTFALL NEHMEN SIE IN THE EVENT OF A DEFECTIVE

KONTAKT MIT UNSERER PLEASE CONTACT YOUR SERVICE

HOTLINE AUF

d ©

GDP 3560

Es gelten die Vorschriften und Sicherheitshinweise gemäß dem Service Manual "Sicherheit", Mat.-Nummer

720108000001, sowie zusätzlich die eventuell abweichenden, landesspezifischen Vorschriften!

ÄNDERUNGEN VORBEHALTEN / SUBJECT TO ALTERATION

The regulations and safety instructions shall be valid

as provided by the "Safety" Service Manual, part

S

number 720108000001, as well as the respective

( ! )

national deviations.

GDP 3560, GDP 3564

Loading...

Loading...