Page 1

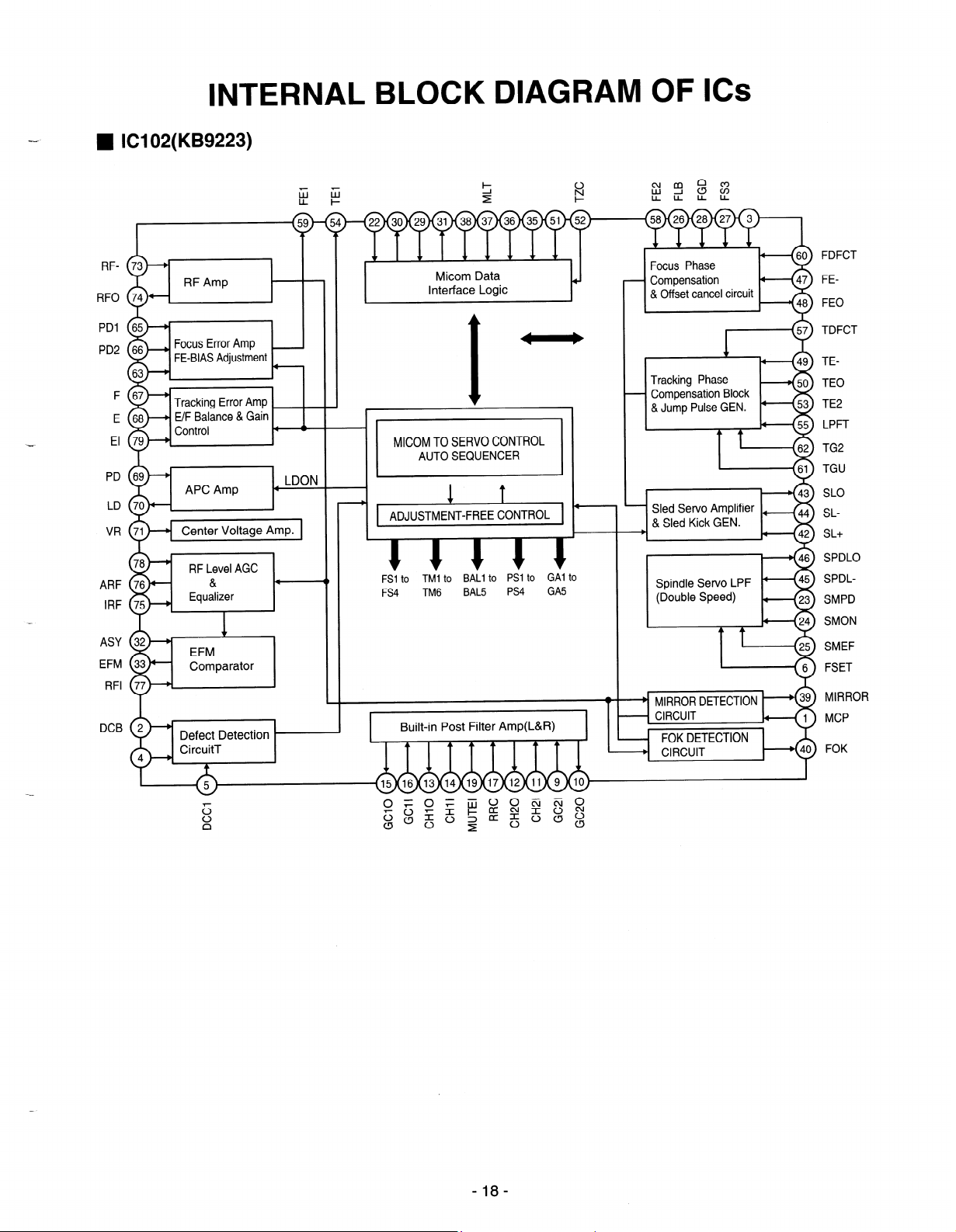

INTERNAL BLOCK DIAGRAM OF ICs

-_

-

-

n IC102(KB9223)

RF-

RF0

PDI

PD2

F

E

El

PD

LD

VR

ARF

IRF

ASY

EFM

RFI

DCB

Focus Error Amp .

FE-BIAS Adjustment

Tracking Error Amp

E/F Balance & Gain

Defect Detection

CircuitT

Interface Logic

I -

MICOM TO SERVO CONTROL

AUTOSEQUENCER

FSI to TM1 to BALl to PSI to GA1 to

TM6

FS4

Built-in Post Filter Amp(L&R)

BAL5

PS4 GA5

Focus Phase

& Offset cancel circuit

Tracking Phase

Compensation Block

& Jump Pulse GEN.

FOK DETECTION

+ CIRCUIT

FDFCT

FEFE0

TDFCT

TETEO

’

TE2

LPFT

TG2

TGU

SLO

SLSL+

SPDLO

SPDLSMPD

SMON

SMEF

FSET

MIRROR

MCP

FOK

-18-

Page 2

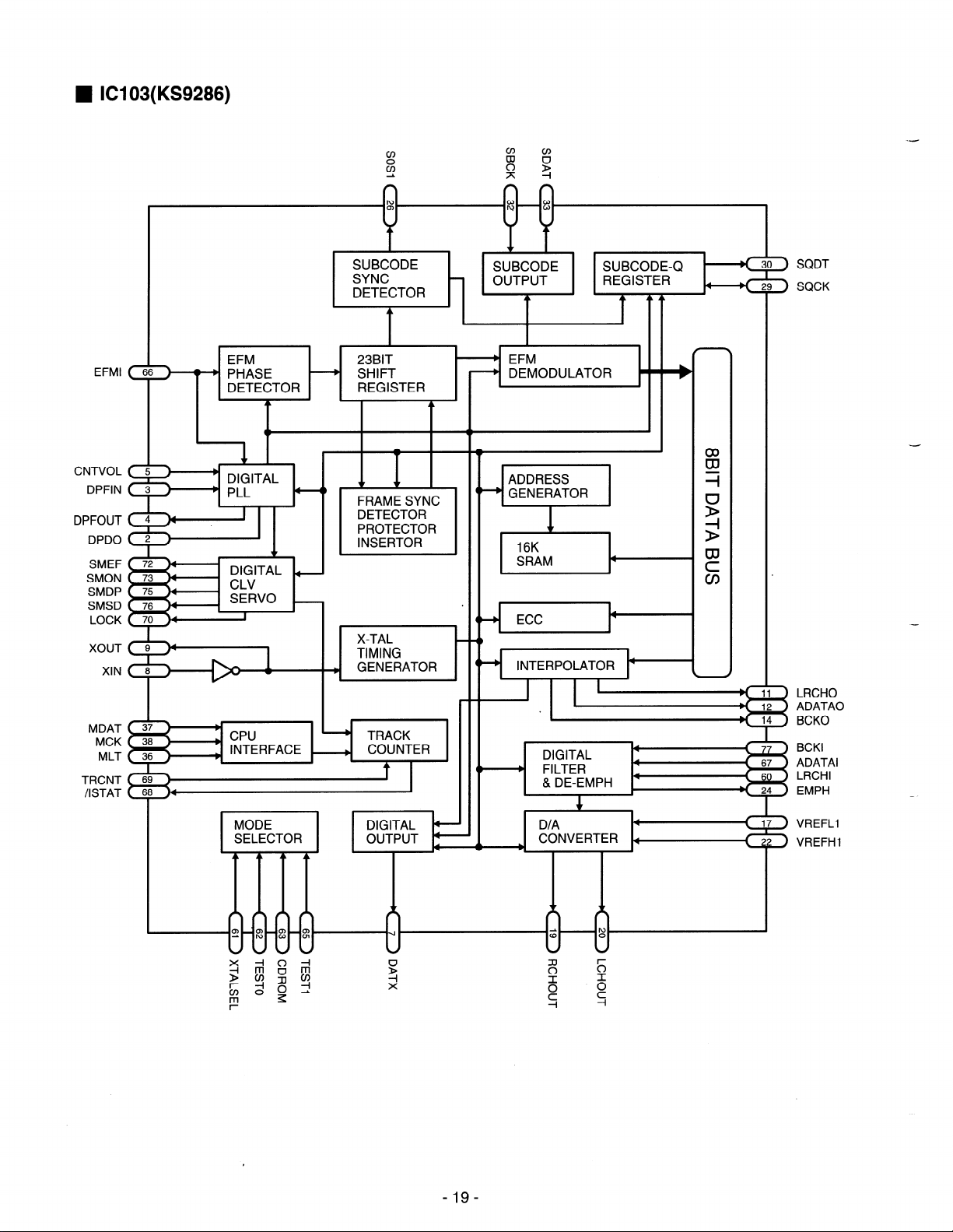

n IC103(KS9286)

EFMI

DETECTOR

A

23BIT

’

EFM

’

DEMODULATOR

REGISTER

.-

SQDT

SQCK

I

--

CNTVOL

DPFIN

DPFOUT

DPDO

SMEF

SMON

SMDP

SMSD

LOCK

XOUT

XIN

MDAT

MCK

MLT

TRCNT

/ISTAT

(9)

( 83-

UlUl I AL

DI I I, - IA

I

I

I

MODE

SELECTOR

FRAME SYNC

DETECTOR

PROTECTOR

INSERTOR

I

X-TAL

TIMING

+ GENERATOR

I )

TRACK

b COUNTER

4 I

16K

SRAM

I

ECC

4

INTERPOLATOR

+I

9 FILTER

4

4

’

DIGITAL

& DE-EMPH

I I

’

LRCHO

ADATAO

BCKO

BCKI

ADATAI

LRCHI

EMPH

VREFLI

VREFHI

-19-

Page 3

04 (358D)

+ -

--

REGULATOR

f MUTE

1 M 4)

+ -

LEVEL

SHIFT

- 20 -

Page 4

INFORMATION OF ICs MI-COM

n IClOl KS57C0108

Pin No.

1

2 P52

3 P51

4 P50

5

6

7 Xin

8 P63/KS3

9 P62/KS2

IO PGl/KSl

11 PGO/KSO

12 P73/KS7

13

14 P71/KS5

15 P70/KS4

16 vss

17 P13/INT4

18

19

20

21 P23/BUZ

22 P22/CLO

23

24 P20/TCLOO

25

26

27 POl/SO

28 POO/SCK29 P83

30

31 P81

32 P80

33 NC

34 NC

35 P33

36

37

38

39

40

41 P43

42 P42

43 P41

44 P40

Port Name.

P53

RESETXout

P72/KS6

P12/INT2

PI l/INTl

PlO/INTO

P21/TCLOl

P03/BTCO

PO2/S I

P82

P32

P31/TCLl

P30/TCLO

VDD

TEST

I/O

0

Unused

Unused

0

I

-

-

0

0

0

0

Unused

Unused

Unused

Unused

-

Unused

I

I

I

I

I

I

I

Unused

I

I

0

Unused

Unused

Unused

Unused

-

I

Unused

l/O

l/O

-

-

Unused

0

0

0

Signal Name

XRST

PLL CTRL

-

RESET-

MCLK

MDATA

MLAT

MUTE

GND

SLEDSW

TRCNT

SCOR

KEY1

KEY0

SENS

FOK

SUBQ

CLSSW

SQCK

GND

GND

GFS

BUSY

SDATA

VDD

GND

KEY-C

KEY-B

KEY-A

Meaning

CDP LSI Reset (L)

CDP LSI Power Control (H-On, L=Off)

Micom Reset (L)

Osci I lator Output

Osci I lato Input

CDP LSI CLK for Command TX

CDP LSI Data for Command TX

CDP LSI Latch for Command TX

Mute

GND

Sled Limit S/W Detect

Track Count Input

SCOR Input

Key Signal Input 1

Key Signal Input 0

SENS Signal

Focus OK Signal

Sub-Q Data

Door Open/Close SW

Sub-Q Clock for Data Read

GND

GND

GFS Signal

Receiver Communication Line - Busy Signal

Receiver Communication Line - Data Signal

VDD

GND

Key Scan Signal C

Key Scan Signal B

Key Scan Signal A

\

\

‘i

--

-

--_

-2l-

Loading...

Loading...