Gigabyte N560B-A2T Schematics Rev.5.0

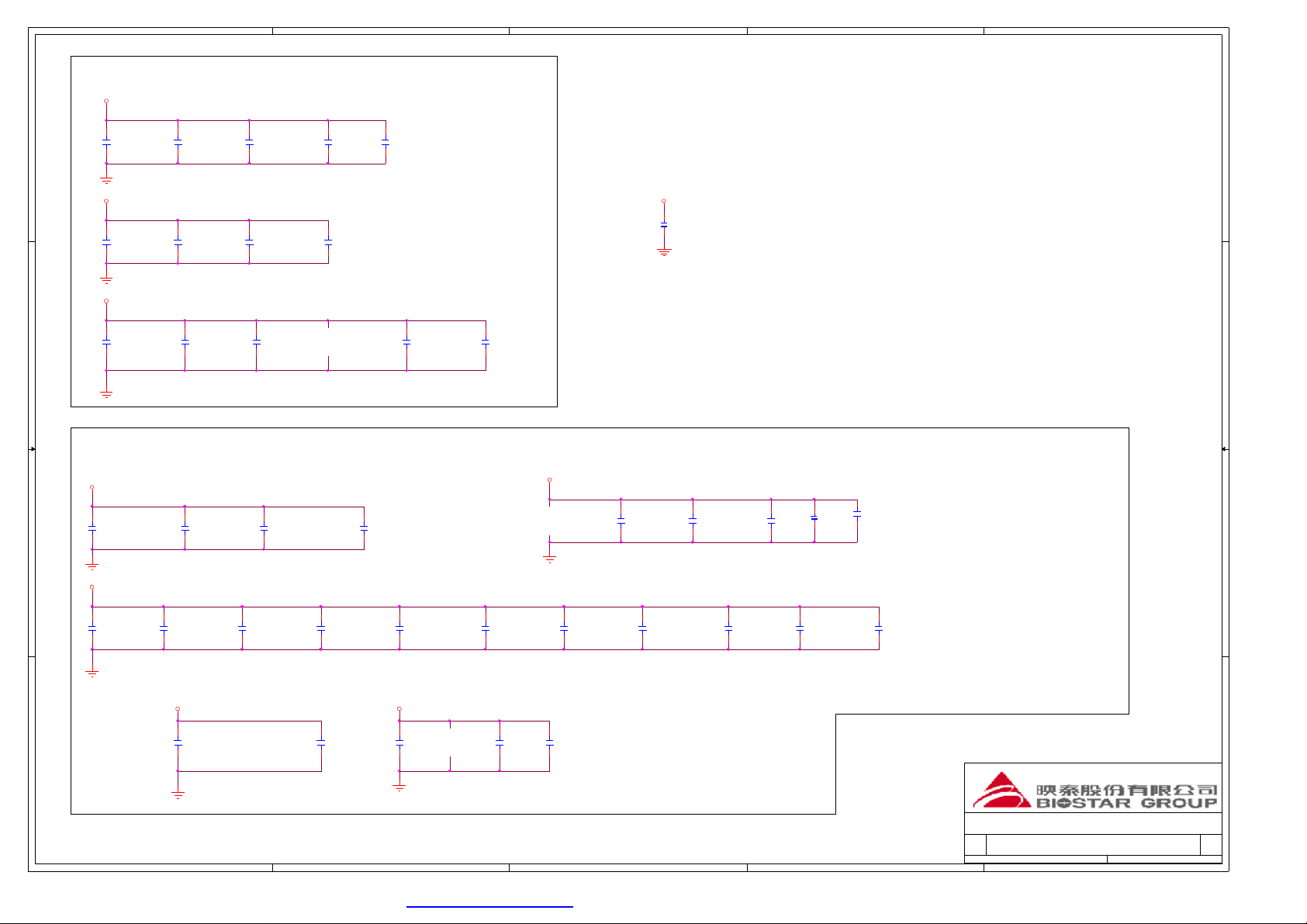

5

TITLE

COVER SHEET

BLOCK DIAGRAM

RESET&CLK MAP

SPEC&CHANGE LIST

D D

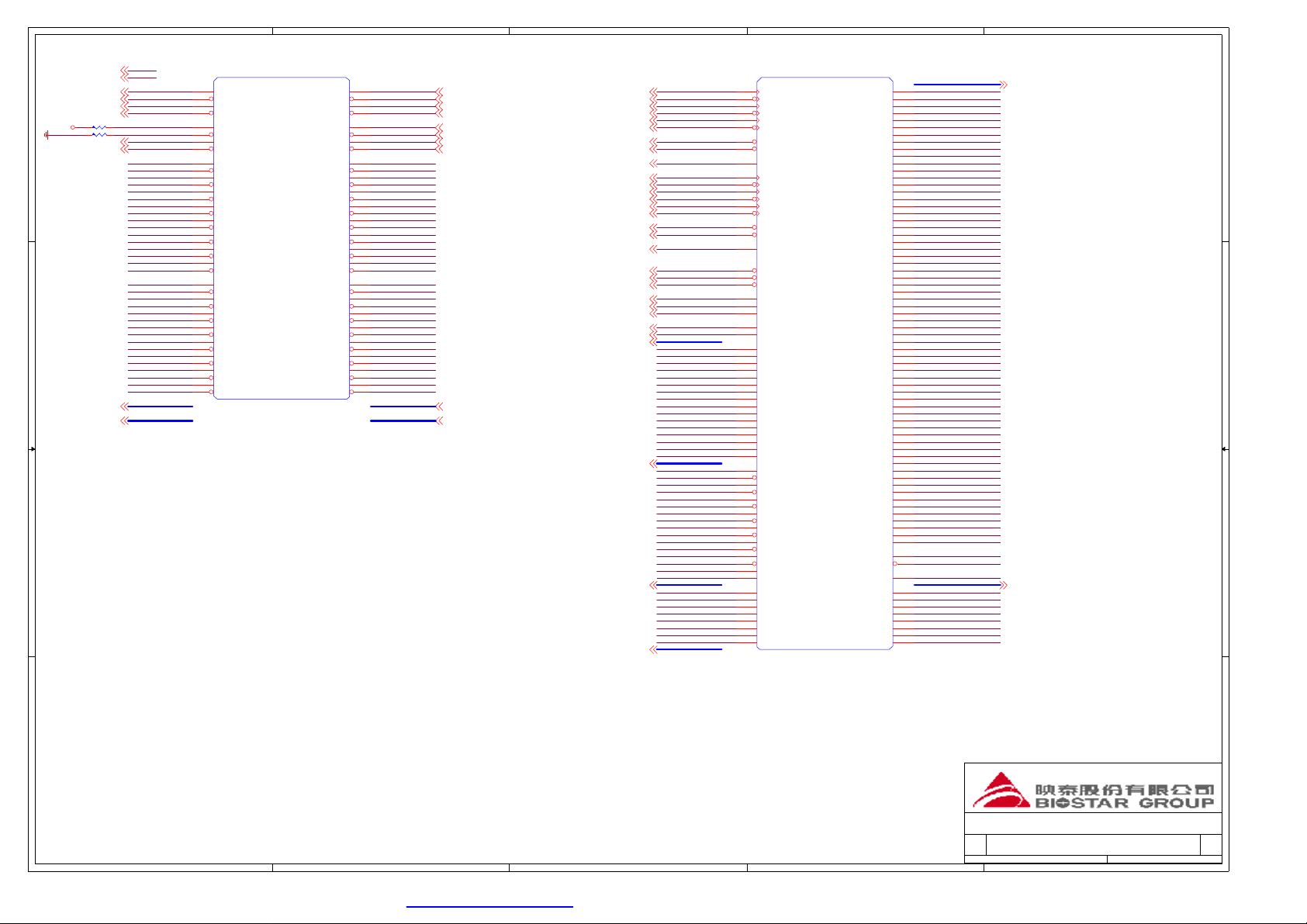

PROCESSOR M2 940

DDR ADD/CTL/VTT TERMINATI

DDR 1

4

3

2

1

SHEET

1

2

3

4

5,6,7,8,9

10

11

N560B-A2T

DDR 2 12

NV CHIPSET(MCP65)

13,14,15

VER:5.0

16,17,18,19

PCI 1&2&3

FRONT PANEL HEADER

PCI EXPRESS X16 & X1

C C

IDE CONN

POWER CONN & FAN CONTROL

FLOOPY / KB / MOUSE / CMOS

Reserved

USB DEVICE

SERIAL & PARALLEL

AUDIO CODEC

AUDIO CONN

VCORE POWER SUPPLY

MEM_VREG/MEM_VTT

B B

LPC SUPER IO(IT8712/8716)

FLASH ROM & H/W MON

POWER SEQUENCING

LAN 10/100

OVER VOLTAGE

MCP65 CORE

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

A A

Title

COVER SHEET

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

N560B-A2T

1

1 39Wednesday, June 13, 2007

5.0

PDF created with pdfFactory Pro trial version www.pdffactory.com

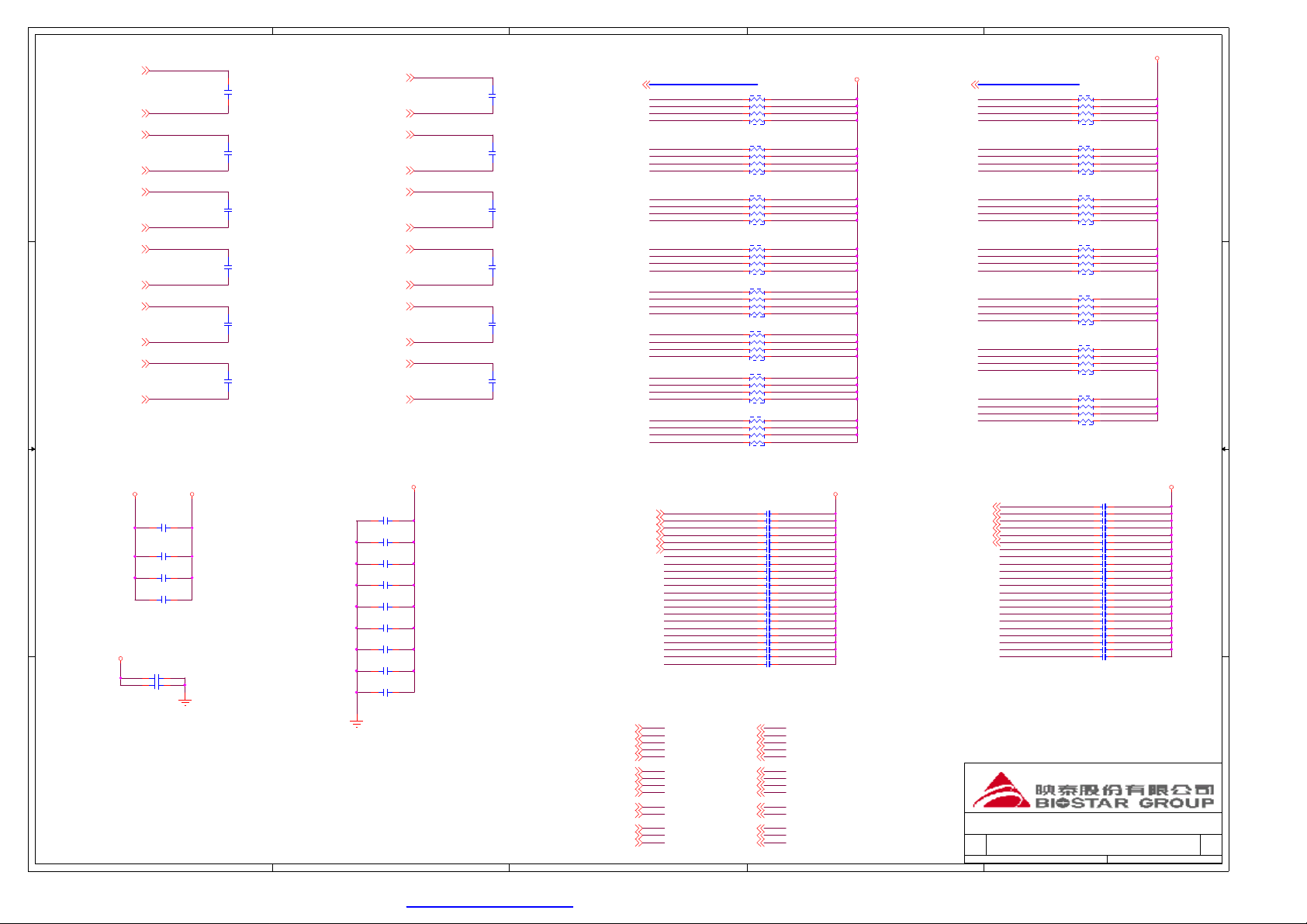

5

4

3

2

1

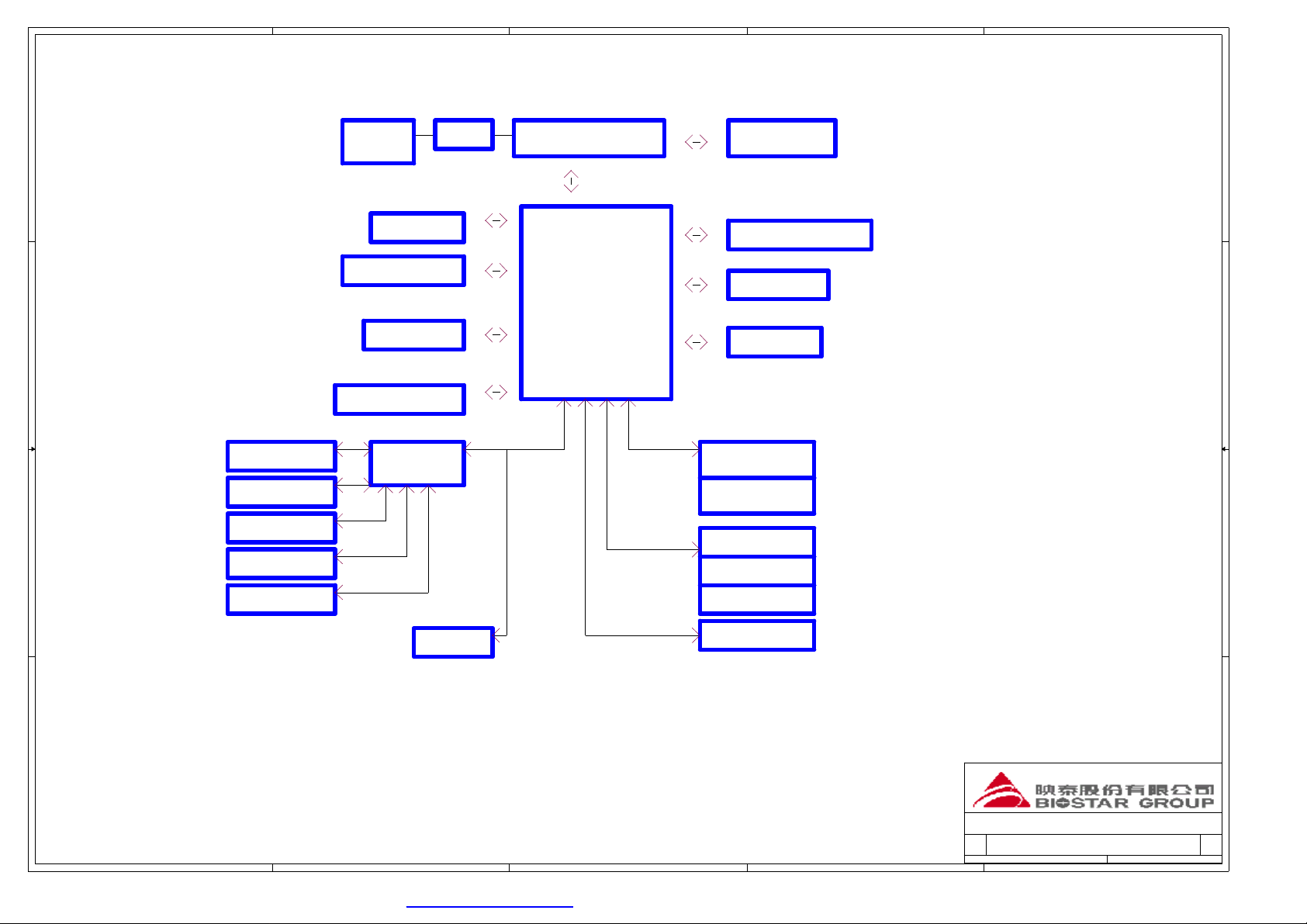

D D

POWER

SUPPLY

VREG

CONN

PEX X16 (1)

PEX X1 (1 OR 2)

AMD M2 SOCKET 940

M2

HT 16X16 1GHZ

NFORCE

MEMORY DDR2

DDR DIMM(4)

128-BIT 400/533/667/800 MHZ

PCI 33MHZ

PCI LAN RTL8110SC

PCI 33MHZ

PCI SLOT (3)

ATA 133

C C

PRIMARY IDE

MCP65 (P/S/V)

692BGA

AC97/HDA

AUDIO CODEC

SATA CONN(X2/X4)

INTEGRATED SATA 1/2

LPC BUS 33MHZ

SIOFLOPPY CONN

ITE8716

PS2/KBRD CONN

USB2.0 (X8/X10)

DOUBLE STACK

USB2 PORTS 3-2

BACK PANEL CONNUSB2 PORTS 1-0

LAN RJ45

PARALLEL CONN

B B

SERIAL CONN

USB2 PORTS 5-4FRONT PANEL HDR

USB2 PORTS 7-6

H/W MON

USB2 PORTS 9-8

RGMII

4MB FLASH

A A

5

4

3

MII/RGMII(/NI)

Title

SYSTEM BLOCK

Size Document Number Rev

Custom

2

Date: Sheet of

N560B-A2T

1

2 39Wednesday, June 13, 2007

5.0

PDF created with pdfFactory Pro trial version www.pdffactory.com

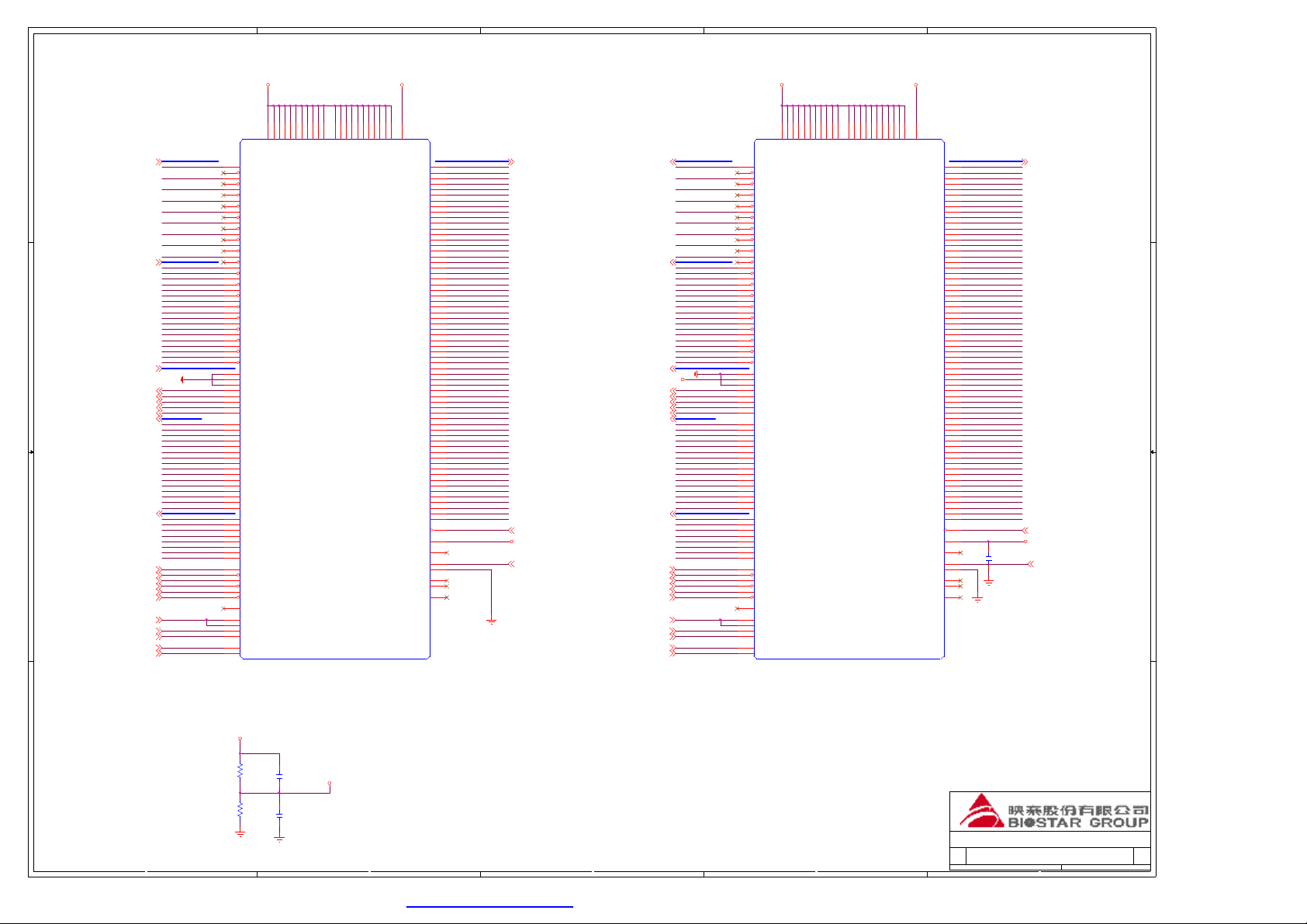

5

4

3

2

1

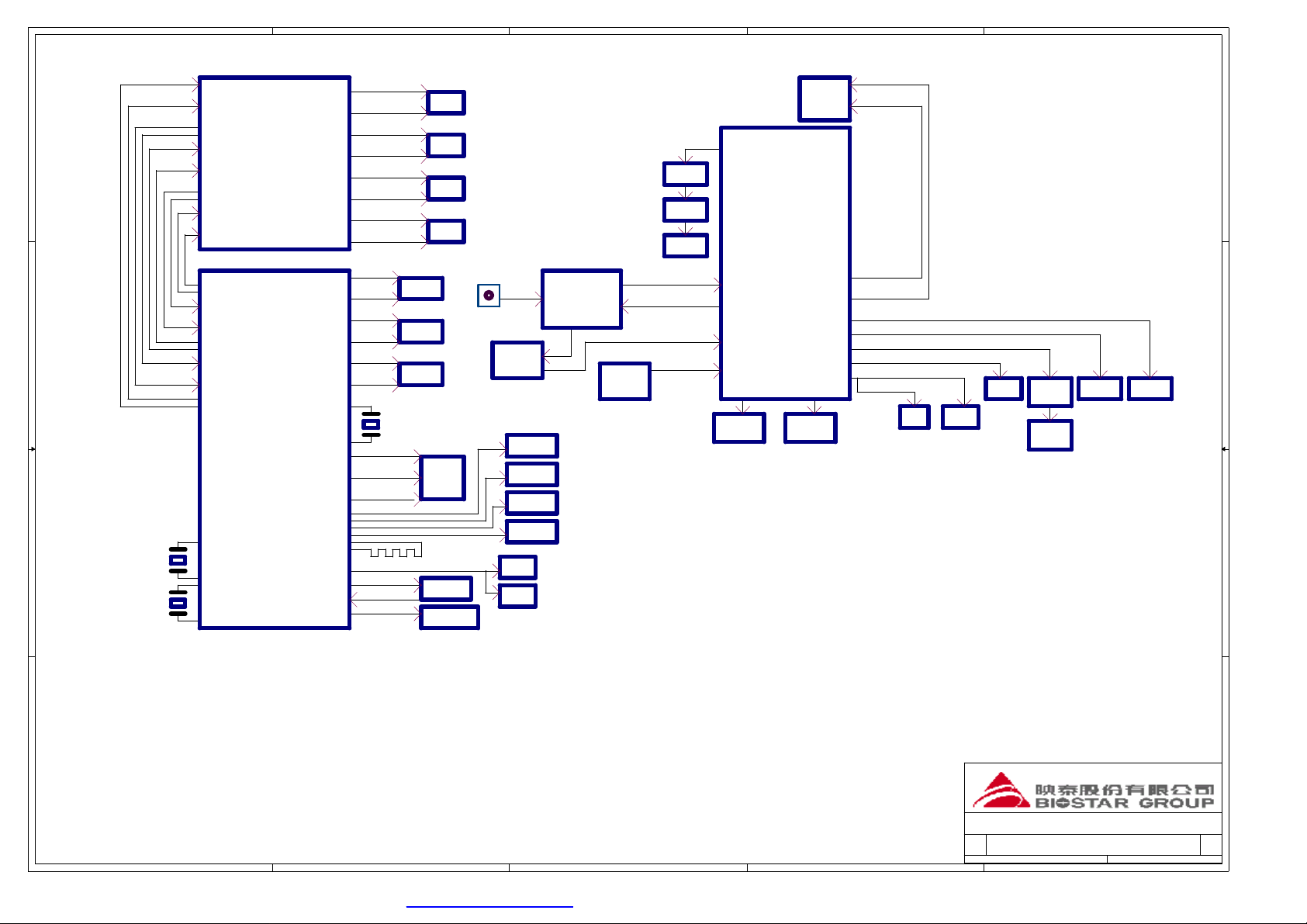

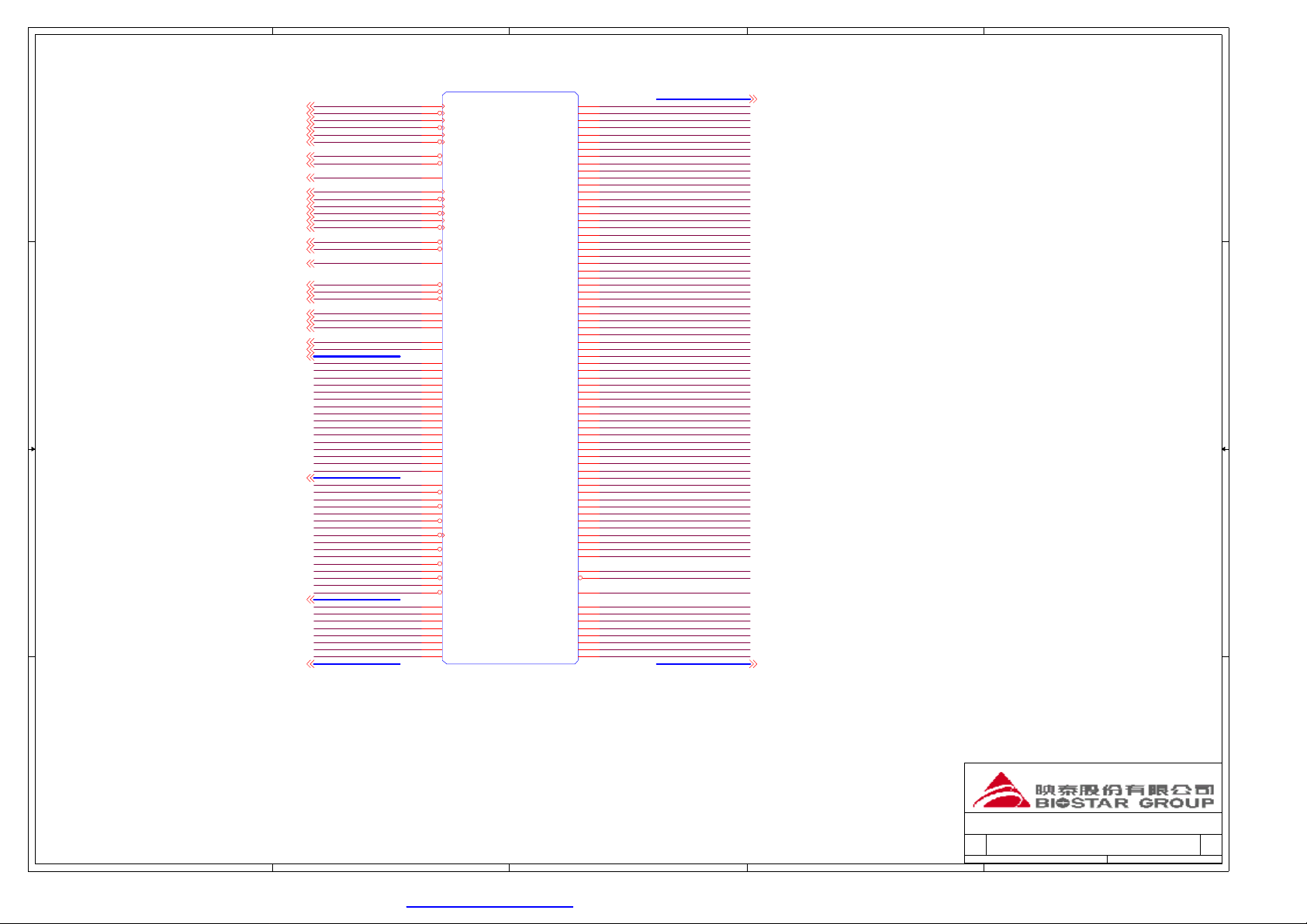

MCP65

M2 SKT 939

CPU RST*

CPU PWRGD

HT MCP RST*

HT MCP PWRGD

PCI RST0*

PCI RST1*

PCI RST2*

PCI RST3*

LPC_RST*PWRGD SB

AC_RESET*

AUDIO_PHY

RESET*

HT_MCP_PWRGD

HT_MCP_RST*

HT_MCP_RST*

HT_MCP_PWRGD

PCIRST_SLOT1*

PCIRST_SLOT2*

PCIRST_SLOT3-4*

PCIRST_IDE*

LPCRST_FLASH*

LPCRST_SIO*

SIO FLASH

PRI IDE

PCI SLOT 3 PCI SLOT2 PCI SLOT1

PCI LAN

M2 940 CPU

HT_CPU_TXCLK0

HT_CPU_TXCLK0*

HT_CPU_RXCLK0

D D

C C

B B

32.768 KHZ

25 MHZ

HT_CPU_RXCLK0*

HT_CPU_TXCLK1

HT_CPU_TXCLK1*

HT_CPU_RXCLK1 DIMM 2

HT_CPU_RXCLK1*

CPUCLK_IN*

CPUCLK_IN

CLKOUT_200MHZ

CLKOUT_200MHZ*

HT_CPU_RXCLK1*

HT_CPU_RXCLK1

HT_CPU_TXCLK1*

HT_CPU_TXCLK1

HT_CPU_RXCLK0*

HT_CPU_RXCLK0

HT_CPU_TXCLK0*

HT_CPU_TXCLK0

RTC_XTAL

XTAL_IN

XTAL_OUT

MEMORY_A1_CLK[2:0]

MEMORY_A1_CLK[2:0]*

MEMORY_B1_CLK[2:0]

MEMORY_B1_CLK[2:0]*

MEMORY_A2_CLK[2:0]

MEMORY_A2_CLK[2:0]*

MEMORY_B2_CLK[2:0]

MEMORY_B2_CLK[2:0]*

MCP65

PE0_REFCLK

PE0_REFCLK*

PE1_REFCLK

PE1_REFCLK*

PE2_REFCLK

PE2_REFCLK*

XTAL_IN

XTAL_OUT

BUF_SIO

SUSCLK

LPC_CLK0

PCI_CLK0

PCI_CLK1

PCI_CLK2

PCI_CLK3

PCI_CLK4

PCI_CLK_FB

LPC_CLK1

AC_97CLK

AC_BITCLK

BUF_25MHZ

CHANNEL A1 0-63

CHANNEL B1 64-127

CHANNEL A2 0-63

CHANNEL B2 64-127

27 MHZ (TV OUT ONLY)

14MHZ OR 24MHZ

32KHZ

33MHZ

33MHZ

33MHZ

AC97/AZALIA LINK

PEX X16

PEX X1

PEX X1

DIMM 0

DIMM 1

DIMM 3

PWR SWTCH

PWR CONN

PS ON

PWR GOOD

CLOCK

DISTRIBUTION

PCI SLOT2

SIO

HDA CODEC

LAN PHY(/NI)

PCI SLOT1

PCI SLOT 3

PCI LAN

FLASH

S-IO

PWR

BUTTON*

PS ON

8712/8716

PWRBT

ON*

SLP_S3*

RESET MAP

PEX X16

PEX X1

PEX X1

PWRBTN*

SLP_S3*

POWER_GOOD

PWRGD_SB

CIRCUIT

PE_RESET*

PWR BUTTON

SLP S3*

PWRGD

PWRGD_SB

GPIO_AUX*

LAN_PHY

RESET*

A A

Title

RESET&CLOCK MAP

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

N560B-A2T

1

3 39Wednesday, June 13, 2007

5.0

PDF created with pdfFactory Pro trial version www.pdffactory.com

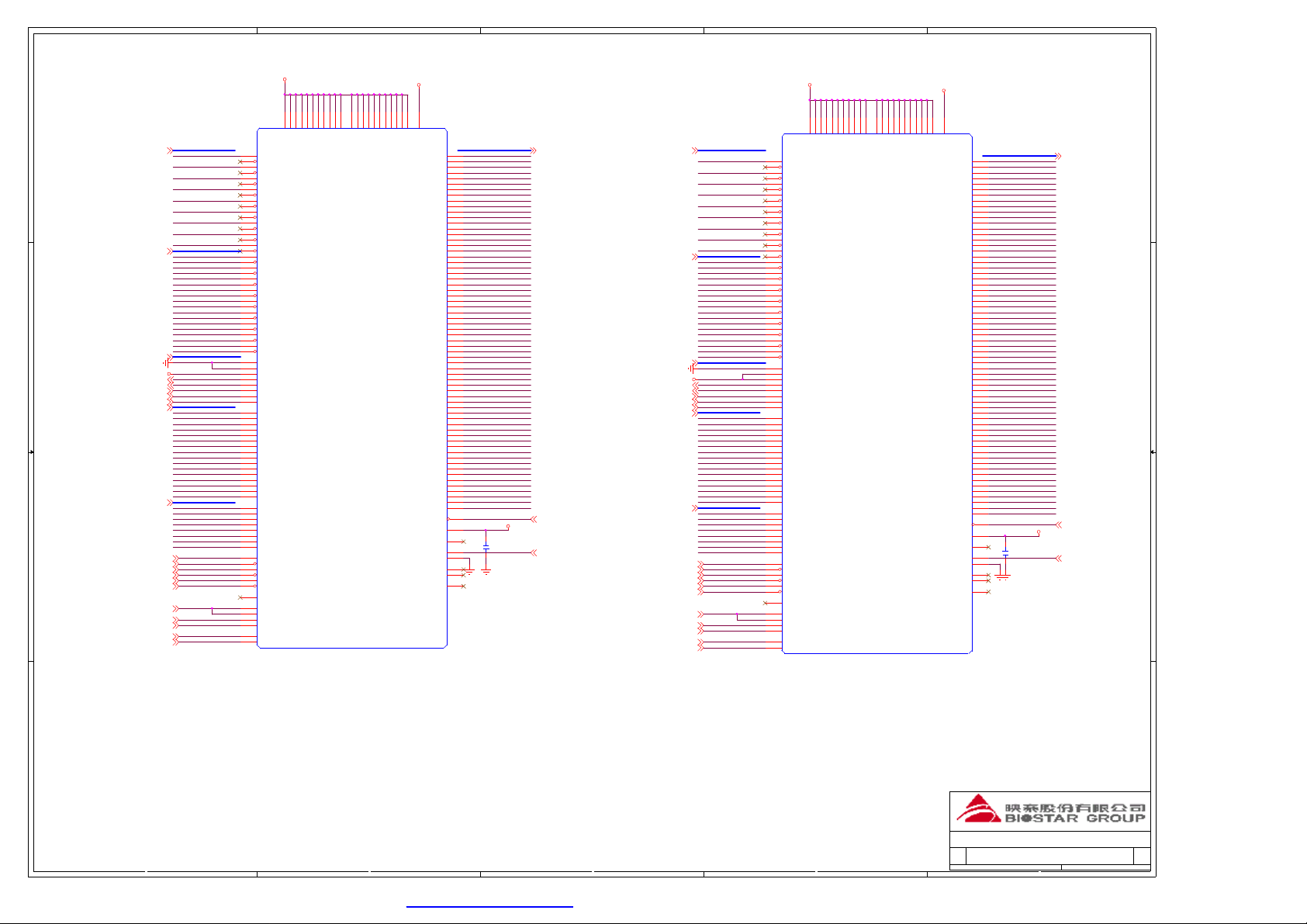

5

4

3

2

1

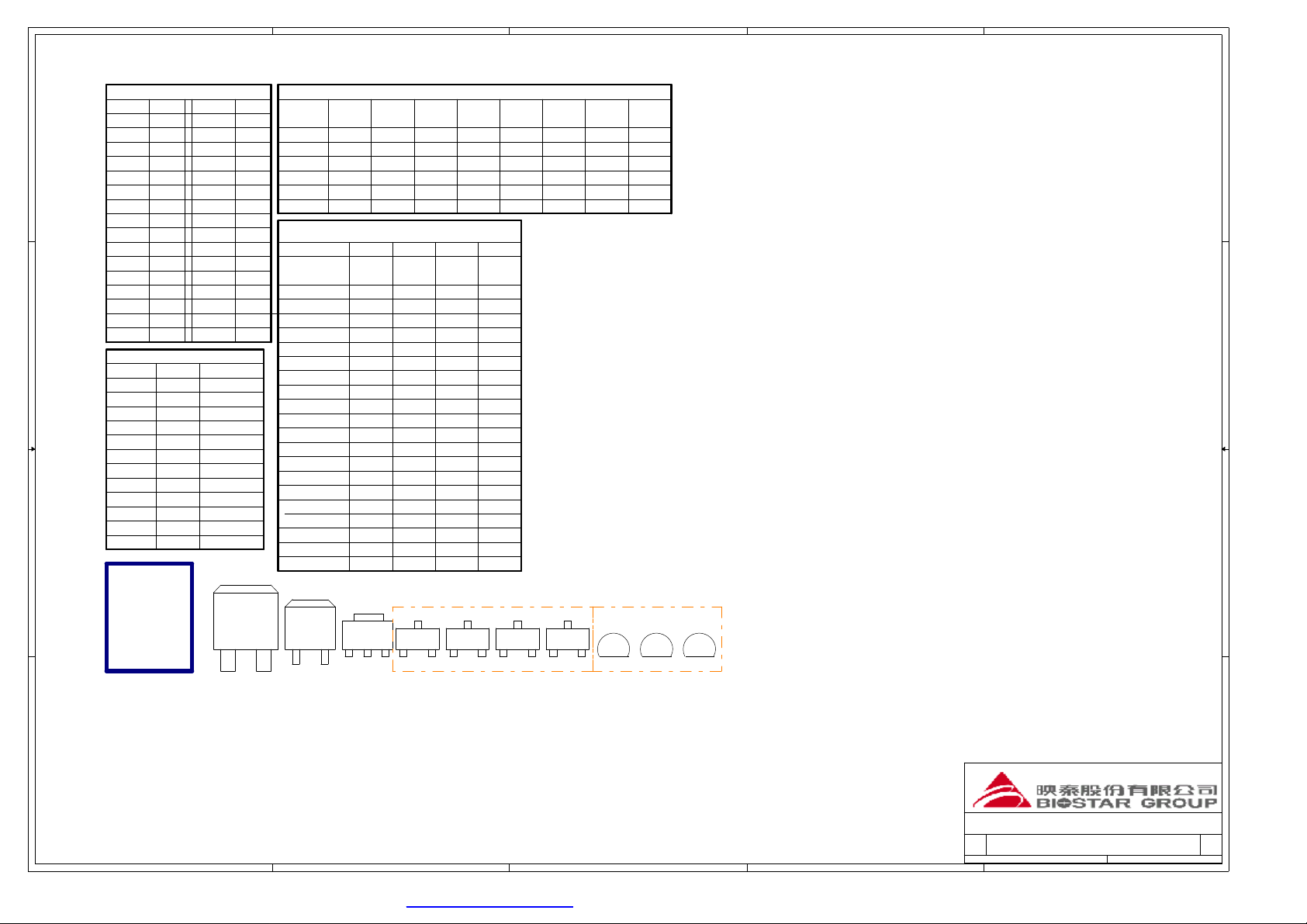

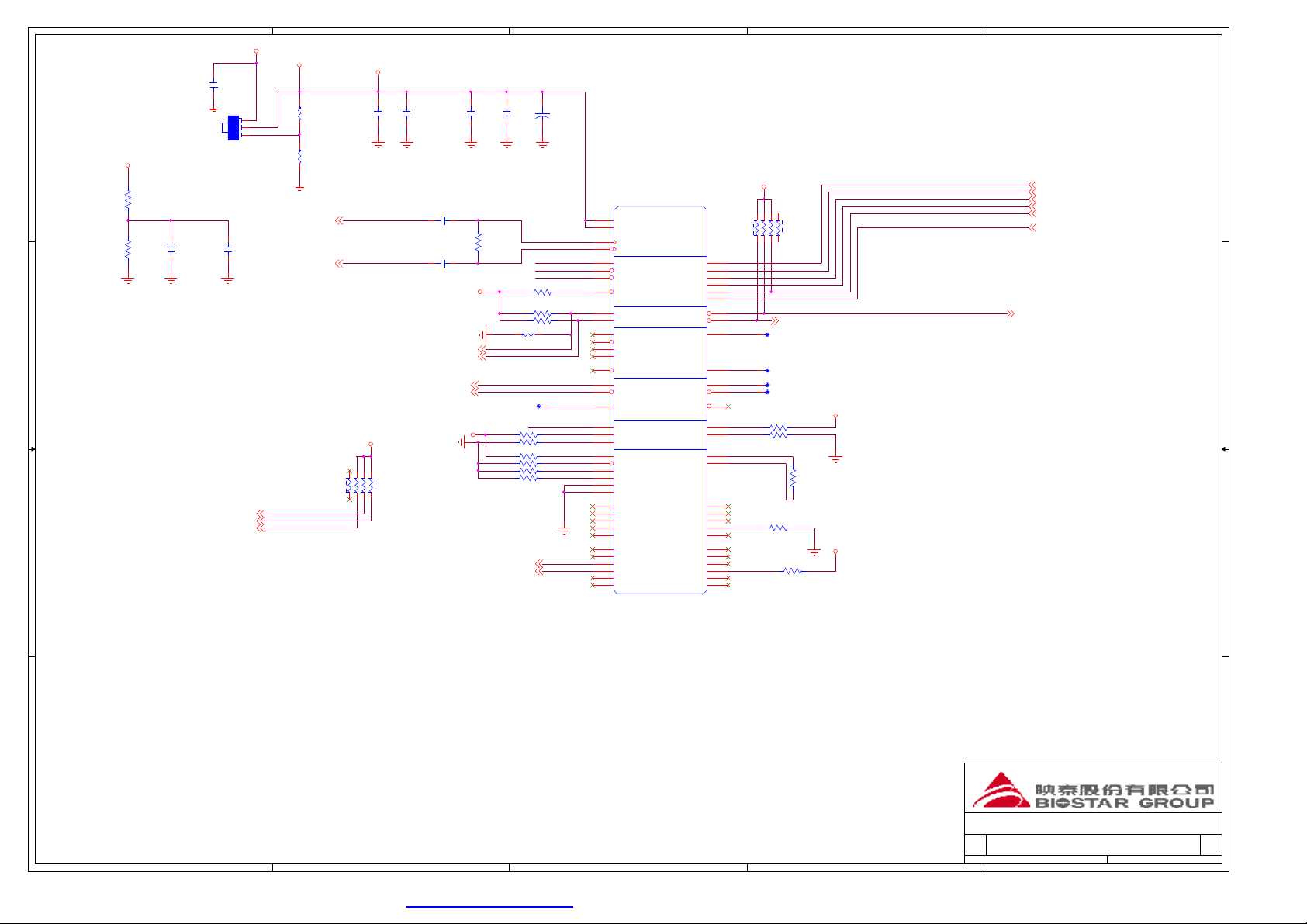

CPU VID TABLE

VID [4..0]

0X10000

0X10001

0X10010

0X10011

0X10100

0X10101

0X10110

0X10111

0X11000

0X11001

0X11010

0X11011

0X11100

0X11110

0X11111

1010 000 = 0X500

1010 001 = 0X51

1010 010 = 0X52

1010 011 = 0X53

0101 101 = 0X2D

ARP

ARP

ARP

ARP

?

?

G

PHB55N03

90N02

VDD

1.150V

1.125V0X00001

1.100V

1.075V

1.050V

1.025V

1.000V

0.975V

0.950V

0.925V

0.900V

0.875V

0.850V

0.825V0X11101

0.800V

OFF

D

VDD

VID [4..0]

0X00000

1.550V

D D

C C

B B

1.525V

1.500V

0X00010

0X00011

1.475V

0X00100

1.450V

1.425V

0X00101

0X00110

1.400V

1.375V

0X00111

1.350V

0X01000

0X01001

1.325V

0X01010 1.300V

1.275V

0X01011

0X01100

1.250V

1.225V

0X01101

1.200V

0X01110

0X01111

1.175V

SMBUS ADDRESS MAP

DEVICE

SLOT

DIMM 0

DIMM 1

DIMM 2

DIMM 3

SIO

PCI SLOT 1 1

PCI SLOT 2

PCI SLOT 3

PCI SLOT 4

22U/25DE 5*7 mm

100U/16DE

220U/10DE

470U/16DE

1000U/10DE

1500U/16DE

3300U/25DE

SMBUS # ADDRESS

0

0

0

1

1

1

1

ADDC BUS

BDDC BUS

6.3*11 mm

6.3*11 mm

8*11 mm

8*14 mm

10*25 mm

10*25 mm

PCI INTERRUPT/IDSEL MAP

BACK PANEL

SLOT

1

2

3

4

5

PCI BUS#

01

01

01

01

01

016

DEVICE#

IDSEL PIN

0X05

22

0X06

24

0X07

23 P_INTX* P_INTY* P_INTZ* P_INTW* 3/3

0X08

0X09

0X0A

PCI DEVICE MAP

A

S

SOT-223

AMS1117

PCI BUS# FUNCTION

MCP51

LOGICAL

0X01-0X0F

PCI BUS 0

XA

0

X9

0

X8

0

X8

0

X6

0

0

X4

0

X4

0

X2

0

X2

0

X1

0

X0

0

X1

0

?

0

X1

1

?

O

O

A

I

C

SOT-23TO-263

R E

DEVICE

MCP65

MAC /MAC

PCI-PCI BRIDGE

SATA1

SATA0

IDE

MODEM CODEC

AUDIO CODEC

USB 2.0

USB 1.1

SHAPE TRIM

LDT

SMBUS2

LEGACY SLAVE

LPC

LOGICAL PCI BUS

PCI SLOT 1

PCI SLOT 2

PCI SLOT 3

PCI SLOT 4

PCI SLOT 5

D

G

TO-252

20N03

TM3055TL-S

PHD55N03

IDSEL PIN

- -

0

0

0

0

0

1

0

1

0

2

0

1

?

0

?

G

SOT-23

2N7002

SI2303S

SI2301S

PCI SLOT

INTA*

P_INTY*

P_INTW*

D

DEVICE ID

- -

0X56/57

0X005C

0X0055

0X0054

0X0053

0X0058

0X0059

0X005B

0X005A

0X005F

0X005E

0X0052

0X00D3

0X0050/51

?

S

PCI SLOT

INTB*

P_INTZ*

P_INTX*

C

B

SOT-23

2N3904

2N3906

MMBT2907A

2N2222A

PCI SLOT

PCI SLOT

INTC*

P_INTW*

P_INTY*

INTD*

P_INTX*

P_INTZ*

REQ/GNT

1/1

2/2

KA

GIO

A

BAT54CKLM431 2N2222ALM431

BAT54S 78L05-DS2N2097A

TO-92SOT-23

LM432

CRU51-M9

1. CPU --- AMD Socket 940(3-Phase Power)

2. CHIPSET --- NF MCP65

3. MEMORY ---Dual Channel DDR SDRAM X 4 (Max. 4GB)

4. SLOTS --- PEX X16 (x1),PEX X1 (x2),PCI (x3)

5. CODEC --- Realtek ALC861VD 5.1 Channel Audio

6. LAN PHY --- RTL8201CN

7. LPC/SIO --- IT8716F

8. SATA -- INTEGRATED(x4)

9. PCB Size --- 20.0cmx30.4cm, 4-Layer

CHANGE LIST

1.Q37 2N7002 CHANGE 2N3904 FOR POWER_SB TIMING

2.ADD C398 10U/10V FOR POWER_SB TIMING

3.PHY RST FOR S3 WAKE CAN WORK R134,C187 /NI, R136 0

4.DEL VID[0..5] TO MCP51.IT8712

5.ADD C45 1U/10V , R16 10K--> 100K FOR +2.6V

6.ADD U5,R83,R82(22) R84,R81(0)/NI FOR ON BOARD VGA PLUG INTO THE MONITOR CAN'T BOOT UP

7.ADD HEATSINK FOR S/B

8.R262.R264 20K --> 56K FOR KBRST,A20GATE BECOMING 3.3V

9.DEL R217,R222 SLEEPBTNJ CHANGE FROM S/B EXSMI PIN. R206 MOVE NEAR S/B

10.ADD OV-->R222,R281,R282,R283 /NI,R217

11.ADD LED-->D14,D15,D16,D17,R64,R66,R67,R74,R108,R149, SW-->PWRSW1,RSTSW2,R62,R63

12.DEL CT31,PWRGD,C3,C4,C6,C7,C13,CT5,CT19,C209,C210,C230,C211,C212,C213,C227,C228,C229,C17(BOM)

13.AR19 0 /NI FOR AUDIO CLK TO 24Mhz

14.ADD FOR EMI BC92,AR23,AL8,FB24

15.FOR EMI C9,C10,C12,C14-->47P

C8,C193,C196,AC32,C331-->104P

C395,C394,C393,C392,C391,C390,C389,C388,C383C387,C382,C386,C381,C385,C378,C384,C380-->100P

C116,C119,C123-->33P

AR22-->0

C343-->103P

C342-->102P

C336-->10P H1,H2-->COMMOM CHOKE

16.DEL BOM FOR EMI FB6 /NI

5.CHANGE HEATSINK FOR N/B TO SHORT

B

EC

B

C

E

TO-92

TO-92

HSD882-D

A A

Title

SPEC&CHANGE LIST

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

N560B-A2T

1

4 39Wednesday, June 13, 2007

5.0

PDF created with pdfFactory Pro trial version www.pdffactory.com

5

4

3

2

1

HTCPU_UPCNTL113

HTCPU_UPCNTL1_13

HTCPU_UPCLK113

HTCPU_UPCLK1_13

HTCPU_UPCLK013

HTCPU_UPCLK0_13

+1.2V_HT

R6449.9 1% 0402

R6349.9 1% 0402

D D

HTCPU_UPCNTL_13

C C

HTCPU_UP[15..0]13

HTCPU_UP_[15..0]13 HTCPU_DWN_[15..0] 13

B B

HTCPU_UPCLK1

HTCPU_UPCLK0

HTCPU_UPCLK0_

HTCPU_UPCNTL1

HTCPU_UPCNTL1_

HTCPU_UPCNTL

HTCPU_UPCNTL_

HTCPU_UP15

HTCPU_UP_15

HTCPU_UP14

HTCPU_UP_14

HTCPU_UP13

HTCPU_UP_13

HTCPU_UP12

HTCPU_UP_12

HTCPU_UP11

HTCPU_UP_11

HTCPU_UP10

HTCPU_UP_10

HTCPU_UP9

HTCPU_UP_9

HTCPU_UP8

HTCPU_UP_8

HTCPU_UP7

HTCPU_UP_7

HTCPU_UP6

HTCPU_UP_6

HTCPU_UP5

HTCPU_UP_5

HTCPU_UP4

HTCPU_UP_4

HTCPU_UP3

HTCPU_UP_3

HTCPU_UP2

HTCPU_UP_2

HTCPU_UP1

HTCPU_UP_1 HTCPU_DWN_1

HTCPU_UP0

HTCPU_UP_0

N6

P6

N3

N2

V4

V5

U1

V1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

HTCPU_UP[15..0]

HTCPU_UP_[15..0] HTCPU_DWN_[15..0]

L0_CLKIN_H(1)

L0_CLKIN_L(1)

L0_CLKIN_H(0)

L0_CLKIN_L(0)

L0_CTLIN_H(1)

L0_CTLIN_L(1)

L0_CTLIN_H(0)

L0_CTLIN_L(0)

L0_CADIN_H(15)

L0_CADIN_L(15)

L0_CADIN_H(14)

L0_CADIN_L(14)

L0_CADIN_H(13)

L0_CADIN_L(13)

L0_CADIN_H(12)

L0_CADIN_L(12)

L0_CADIN_H(11)

L0_CADIN_L(11)

L0_CADIN_H(10)

L0_CADIN_L(10)

L0_CADIN_H(9)

L0_CADIN_L(9)

L0_CADIN_H(8)

L0_CADIN_L(8)

L0_CADIN_H(7)

L0_CADIN_L(7)

L0_CADIN_H(6)

L0_CADIN_L(6)

L0_CADIN_H(5)

L0_CADIN_L(5)

L0_CADIN_H(4)

L0_CADIN_L(4)

L0_CADIN_H(3)

L0_CADIN_L(3)

L0_CADIN_H(2)

L0_CADIN_L(2)

L0_CADIN_H(1)

L0_CADIN_L(1)

L0_CADIN_H(0)

L0_CADIN_L(0)

HYPERTRANSPORT

CPU1A

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

HTCPU_DWNCLK1

AD5

HTCPU_DWNCLK1_HTCPU_UPCLK1_

AD4

HTCPU_DWNCLK0

AD1

HTCPU_DWNCLK0_

AC1

Y6

W6

HTCPU_DWNCNTL

W2

HTCPU_DWNCNTL_

W3

HTCPU_DWN15

Y5

HTCPU_DWN_15

Y4

HTCPU_DWN14

AB6

HTCPU_DWN_14

AA6

HTCPU_DWN13

AB5

HTCPU_DWN_13

AB4

HTCPU_DWN12

AD6

HTCPU_DWN_12

AC6

HTCPU_DWN11

AF6

HTCPU_DWN_11

AE6

HTCPU_DWN10

AF5

HTCPU_DWN_10

AF4

HTCPU_DWN9

AH6

HTCPU_DWN_9

AG6

HTCPU_DWN8

AH5

HTCPU_DWN_8

AH4

HTCPU_DWN7

Y1

HTCPU_DWN_7

W1

HTCPU_DWN6

AA2

HTCPU_DWN_6

AA3

HTCPU_DWN5

AB1

HTCPU_DWN_5

AA1

HTCPU_DWN4

AC2

HTCPU_DWN_4

AC3

HTCPU_DWN3

AE2

HTCPU_DWN_3

AE3

HTCPU_DWN2

AF1

HTCPU_DWN_2

AE1

HTCPU_DWN1

AG2

AG3

HTCPU_DWN0

AH1

HTCPU_DWN_0

AG1

HTCPU_DWN[15..0]

HTCPU_DWNCLK1 13

HTCPU_DWNCLK1_ 13

HTCPU_DWNCLK0 13

HTCPU_DWNCLK0_ 13

HTCPU_DWNCNTL1 13

HTCPU_DWNCNTL1_ 13

HTCPU_DWNCNTL 13HTCPU_UPCNTL13

HTCPU_DWNCNTL_ 13

HTCPU_DWN[15..0] 13

MEM_MA0_CLK_H210,11

MEM_MA0_CLK_L210,11

MEM_MA0_CLK_H110,11

MEM_MA0_CLK_L110,11

MEM_MA0_CLK_H010,11

MEM_MA0_CLK_L010,11

MEM_MA0_CS_L110,11

MEM_MA0_CS_L010,11

MEM_MA0_ODT010,11

MEM_MA1_CLK_H210,11

MEM_MA1_CLK_L210,11

MEM_MA1_CLK_H110,11

MEM_MA1_CLK_L110,11

MEM_MA1_CLK_H010,11

MEM_MA1_CLK_L010,11

MEM_MA1_CS_L110,11

MEM_MA1_CS_L010,11

MEM_MA1_ODT010,11

MEM_MA_CAS_L10,11

MEM_MA_WE_L10,11

MEM_MA_RAS_L10,11

MEM_MA_BANK210,11

MEM_MA_BANK110,11

MEM_MA_BANK010,11

MEM_MA_CKE110,11

MEM_MA_CKE010,11

MEM_MA_ADD[15..0]10,11

MEM_MA_DQS_H[8..0]11

MEM_MA_DQS_L[8..0]11

MEM_MA_DM[8..0]11

MEM_MA_ADD[15..0]

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H[8..0]

MEM_MA_DQS_H7 MEM_MA_DATA10

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0 MEM_MA_DM8

MEM_MA_DQS_L[8..0]

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

MEM_MA_DM[8..0]

AG21

AG20

AC25

AA24

AC28

AE20

AE19

W27

AD27

AA25

AC27

AB25

AB27

AA26

AA27

AC26

W24

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

AF15

AF19

AJ25

AH29

G19

H19

U27

U26

G20

G21

V27

N25

Y27

L27

M25

M27

N24

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

D29

C29

C25

D25

E19

F19

F15

G15

B29

E24

E18

H15

CPU1B

MEMORY INTERFACE A

MA0_CLK_H(2)

MA0_CLK_L(2)

MA0_CLK_H(1)

MA0_CLK_L(1)

MA0_CLK_H(0)

MA0_CLK_L(0)

MA0_CS_L(1)

MA0_CS_L(0)

MA0_ODT(0)

MA1_CLK_H(2)

MA1_CLK_L(2)

MA1_CLK_H(1)

MA1_CLK_L(1)

MA1_CLK_H(0)

MA1_CLK_L(0)

MA1_CS_L(1)

MA1_CS_L(0)

MA1_ODT(0)

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK(2)

MA_BANK(1)

MA_BANK(0)

MA_CKE(1)

MA_CKE(0)

MA_ADD(15)

MA_ADD(14)

MA_ADD(13)

MA_ADD(12)

MA_ADD(11)

MA_ADD(10)

MA_ADD(9)

MA_ADD(8)

MA_ADD(7)

MA_ADD(6)

MA_ADD(5)

MA_ADD(4)

MA_ADD(3)

MA_ADD(2)

MA_ADD(1)

MA_ADD(0)

MA_DQS_H(7)

MA_DQS_L(7)

MA_DQS_H(6)

MA_DQS_L(6)

MA_DQS_H(5)

MA_DQS_L(5)

MA_DQS_H(4)

MA_DQS_L(4)

MA_DQS_H(3)

MA_DQS_L(3)

MA_DQS_H(2)

MA_DQS_L(2)

MA_DQS_H(1)

MA_DQS_L(1)

MA_DQS_H(0)

MA_DQS_L(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

MA_DQS_H(8)

MA_DQS_L(8)

MA_DM(8)

MA_CHECK(7)

MA_CHECK(6)

MA_CHECK(5)

MA_CHECK(4)

MA_CHECK(3)

MA_CHECK(2)

MA_CHECK(1)

MA_CHECK(0)

MEM_MA_DATA[0..63]

MEM_MA_DATA63

AE14

MEM_MA_DATA62

AG14

MEM_MA_DATA61

AG16

MEM_MA_DATA60

AD17

MEM_MA_DATA59

AD13

MEM_MA_DATA58

AE13

MEM_MA_DATA57

AG15

MEM_MA_DATA56

AE16

MEM_MA_DATA55

AG17

MEM_MA_DATA54

AE18

MEM_MA_DATA53

AD21

MEM_MA_DATA52

AG22

MEM_MA_DATA51

AE17

MEM_MA_DATA50

AF17

MEM_MA_DATA49

AF21

MEM_MA_DATA48

AE21

MEM_MA_DATA47

AF23

MEM_MA_DATA46

AE23

MEM_MA_DATA45

AJ26

MEM_MA_DATA44

AG26

MEM_MA_DATA43

AE22

MEM_MA_DATA42

AG23

MEM_MA_DATA41

AH25

MEM_MA_DATA40

AF25

MEM_MA_DATA39

AJ28

MEM_MA_DATA38

AJ29

MEM_MA_DATA37

AF29

MEM_MA_DATA36

AE26

MEM_MA_DATA35

AJ27

MEM_MA_DATA34

AH27

MEM_MA_DATA33

AG29

MEM_MA_DATA32

AF27

MEM_MA_DATA31

E29

MEM_MA_DATA30

E28

MEM_MA_DATA29

D27

MEM_MA_DATA28

C27

MEM_MA_DATA27

G26

MEM_MA_DATA26

F27

MEM_MA_DATA25

C28

MEM_MA_DATA24

E27

MEM_MA_DATA23

F25

MEM_MA_DATA22

E25

MEM_MA_DATA21

E23

MEM_MA_DATA20

D23

MEM_MA_DATA19

E26

MEM_MA_DATA18

C26

MEM_MA_DATA17

G23

MEM_MA_DATA16

F23

MEM_MA_DATA15

E22

MEM_MA_DATA14

E21

MEM_MA_DATA13

F17

MEM_MA_DATA12

G17

MEM_MA_DATA11

G22

F21

MEM_MA_DATA9

G18

MEM_MA_DATA8

E17

MEM_MA_DATA7

G16

MEM_MA_DATA6

E15

MEM_MA_DATA5

G13

MEM_MA_DATA4

H13

MEM_MA_DATA3

H17

MEM_MA_DATA2

E16

MEM_MA_DATA1

E14

MEM_MA_DATA0

G14

MEM_MA_DQS_H8

J28

MEM_MA_DQS_L8

J27

J25

MEM_MA_CHECK[7..0]

MEM_MA_CHECK7

K25

MEM_MA_CHECK6

J26

MEM_MA_CHECK5

G28

MEM_MA_CHECK4

G27

MEM_MA_CHECK3

L24

MEM_MA_CHECK2

K27

MEM_MA_CHECK1

H29

MEM_MA_CHECK0

H27

MEM_MA_DATA[0..63] 11

MEM_MA_CHECK[7..0] 11

A A

Title

M2 HT/DDR 0-63

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

N560B-A2T

1

5 39Wednesday, June 13, 2007

5.0

PDF created with pdfFactory Pro trial version www.pdffactory.com

5

4

3

2

1

CPU1C

MEM_MB0_CLK_H210,12

MEM_MB0_CLK_L210,12

MEM_MB0_CLK_H110,12

MEM_MB0_CLK_L110,12

D D

C C

B B

MEM_MB0_CLK_H010,12

MEM_MB0_CLK_L010,12

MEM_MB0_CS_L110,12

MEM_MB0_CS_L010,12

MEM_MB0_ODT010,12

MEM_MB1_CLK_H210,12

MEM_MB1_CLK_L210,12

MEM_MB1_CLK_H110,12

MEM_MB1_CLK_L110,12

MEM_MB1_CLK_H010,12

MEM_MB1_CLK_L010,12

MEM_MB1_CS_L110,12

MEM_MB1_CS_L010,12

MEM_MB1_ODT010,12

MEM_MB_CAS_L10,12

MEM_MB_WE_L10,12

MEM_MB_RAS_L10,12

MEM_MB_BANK210,12

MEM_MB_BANK110,12

MEM_MB_BANK010,12

MEM_MB_CKE110,12

MEM_MB_CKE010,12

MEM_MB_ADD[15..0]10,12

MEM_MB_DQS_H[8..0]12

MEM_MB_DQS_L[8..0]12

MEM_MB_ADD[15..0]

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13 MEM_MB_DATA25

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H[8..0]

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DQS_L[8..0]

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

AJ19

AK19

AE30

AC31

AD29

AL19

AL18

W29

W28

AE29

AB31

AD31

AC29

AC30

AB29

AA31

AA28

AE31

AA29

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

AJ14

AH17

AJ23

AK29

A18

A19

U31

U30

C19

D19

N31

M31

M29

N28

N29

N30

P29

P31

R29

R28

R31

R30

T31

T29

U29

U28

D31

C31

C24

C23

D17

C17

C14

C13

C30

A23

B17

B13

MEMORY INTERFACE B

MB0_CLK_H(2)

MB0_CLK_L(2)

MB0_CLK_H(1)

MB0_CLK_L(1)

MB0_CLK_H(0)

MB0_CLK_L(0)

MB0_CS_L(1)

MB0_CS_L(0)

MB0_ODT(0)

MB1_CLK_H(2)

MB1_CLK_L(2)

MB1_CLK_H(1)

MB1_CLK_L(1)

MB1_CLK_H(0)

MB1_CLK_L(0)

MB1_CS_L(1)

MB1_CS_L(0)

MB1_ODT(0)

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK(2)

MB_BANK(1)

MB_BANK(0)

MB_CKE(1)

MB_CKE(0)

MB_ADD(15)

MB_ADD(14)

MB_ADD(13)

MB_ADD(12)

MB_ADD(11)

MB_ADD(10)

MB_ADD(9)

MB_ADD(8)

MB_ADD(7)

MB_ADD(6)

MB_ADD(5)

MB_ADD(4)

MB_ADD(3)

MB_ADD(2)

MB_ADD(1)

MB_ADD(0)

MB_DQS_H(7)

MB_DQS_L(7)

MB_DQS_H(6)

MB_DQS_L(6)

MB_DQS_H(5)

MB_DQS_L(5)

MB_DQS_H(4)

MB_DQS_L(4)

MB_DQS_H(3)

MB_DQS_L(3)

MB_DQS_H(2)

MB_DQS_L(2)

MB_DQS_H(1)

MB_DQS_L(1)

MB_DQS_H(0)

MB_DQS_L(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

MB_DQS_H(8)

MB_DQS_L(8)

MB_DM(8)

MB_CHECK(7)

MB_CHECK(6)

MB_CHECK(5)

MB_CHECK(4)

MB_CHECK(3)

MB_CHECK(2)

MB_CHECK(1)

MB_CHECK(0)

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_DQS_H8

MEM_MB_DQS_L8

MEM_MB_DM8

MEM_MB_CHECK7

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

MEM_MB_DATA[0..63]

MEM_MB_CHECK[7..0]MEM_MB_DM[8..0]

MEM_MB_DATA[0..63] 12

MEM_MB_CHECK[7..0] 12MEM_MB_DM[8..0]12

A A

Title

DDR MEM 64-127

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

N560B-A2T

1

6 39Wednesday, June 13, 2007

5.0

PDF created with pdfFactory Pro trial version www.pdffactory.com

5

D D

+1.8V_SUS

BR1

16.9 1% 0402

1 2

12

16.9 1% 0402

C C

B B

CPU_M_VREFF

12

BR2

BC3

1UF 10V Y5V

+5V

I

O

A

BC4

0.1UF 16V Y5V 0402

+2.5V

R1

R2

CPU_CLK_13

12

C16

10UF 10V 0805 Y5V

Q14

AZ1117H-ADJ SOT-223

Vout=Vref (1.25V) X ( 1+R2/R1 )

=2.5V

12

HTCPU_STOP_13

HTCPU_PWRGD13

HTCPU_RST_13

R40

49.9 1% 0402

R39

54.9 1% 0402

CPU_CLK13

ROUTE AS DIFF PAIR

10/5/5/5/10

+1.8V_SUS

1 2

3 4

+2.5V

CPU_CLK

CPU_CLK*

5 6

7 8

12

RN8

330 8P4R

4

12

C4

C48

10UF 10V 0805 Y5V

1UF 16V 0805 Y5V

12

C45

1UF 16V 0805 Y5V

ROUTE AS DIF 5/5/5/20

LAYOUT: PLACE 169 OHM WITHIN

600mils OF CPU

AND TRACE TO AC CAPS LESS

THAN 1250mil

C43

12

3900P 50V X7R 0402

C44

3900P 50V X7R 0402

CPU_CORE_FB31

CPU_CORE_FB_31

+1.8V_SUS

+1.8V_SUS

THERM_SIC18

THERM_SID18

12

R59

169 1% 0402

1 2

TP_VDDIOSENSE1 TP /NI

CPU_THERMDC33,34

CPU_THERMDA33

12

C3

+

CT1

10UF 10V 0805 Y5V

100UF 16V 5X11 2mm

HTCPU_PWRGD

HTCPU_STOP_

HTCPU_RST_ VID3

R87 1K 1% 0402

1 2

R89 300 0402

1 2

R91 300 0402

1 2

R85 300 0402 /NI

CPU_CORE_FB

CPU_CORE_FB_

R92 39.2 1% 0402

CPU_M_VREFF

1 2

R93 39.2 1% 0402

1 2

R53 510 0402

1 2

R54 510 0402

1 2

R55 300 0402

1 2

R56 300 0402

1 2

AL10

AJ10

AH10

AH11

AJ11

C10

D10

A8

B8

C9

D8

C7

AL3

AL6

AK6

AL9

A5

G2

G1

E12

F12

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AG9

AG8

AH7

AJ6

3

CPU1D

MISC

VDDA1

VDDA2

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

SIC

SID

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

THERMDC

THERMDA

TEST3

TEST2

VID(5)

VID(4)

VID(3)

VID(2)

VID(1)

VID(0)

THERMTRIP_L

PROCHOT_L

DBRDY

VDDIO_FB_H

VDDIO_FB_L

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

D2

VID4

D1

C1

VID2

E3

VID1

E2

VID0

E1

AK7

AL7

AK10

TDO

B6

AK11

AL11

F1

R62 44.2 1% 0402

V8

R61 44.2 1% 0402

V7

FBCLKOUT

C11

FBCLKOUT*

D11

AK8

AH8

AJ9

AL8

AJ8

J10

H9

AK9

AK5

G7

D4

+1.8V_SUS

RN26

330 8P4R

1 2

3 4

5 6

7 8

CPU_THERMTRIP

PROCHOT 13

TP_CPU_TDO1

TP /NI

CPU_DBREQ1

TP /NI

TP /NI

TP_VDDIOFB1

TP_VDDIOFB_1

TP /NI

12

12

R57

80.6 1% 0402

1 2

R94 300 0402

1 2

R88 300 0402

1 2

2

+1.2V_HT

LAYOUT: PLACE WITHIN 1 INCH OF CPU

5/10

8/5/8/20

LAYOUT: ROUTE 80 OHM DIFF IMPEDENCE

LAYOUT: PLACE WITHIN 1 INCH OF CPU

+1.8V_SUS

K8_VID5 31

K8_VID4 31

K8_VID3 31

K8_VID2 31

K8_VID1 31

K8_VID0 31

CPU_THERMTRIP_ 13

1

A A

Title

M2 CNTL/STRAPS

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

N560B-A2T

1

7 39Wednesday, June 13, 2007

5.0

PDF created with pdfFactory Pro trial version www.pdffactory.com

5

4

3

2

1

+V_CPU

ADD FOR EMI

PLACE NEAR C80

BC1

D D

1UF 10V Y5V

+1.8V_SUS

PLACE AT CPU SOCKET SOLDER SIDE

+V_CPU +V_CPU

C C

B B

A A

AA8

AA10

AA12

AA14

AA16

AA18

AB7

AB9

AB11

AC4

AC5

AC8

AC10

AD2

AD3

AD7

AD9

AE10

AF7

AF9

AG4

AG5

AG7

AH2

AH3

E10

F11

G10

G12

H11

H23

J12

J14

J16

J18

J20

J22

J24

K11

K13

K15

K17

K19

K21

K23

L10

L12

Y17

Y19

CPU1F

VDD1

A4

VDD1

A6

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

B3

VDD28

B5

VDD29

B7

VDD30

C2

VDD31

C4

VDD32

C6

VDD33

C8

VDD34

D3

VDD35

D5

VDD36

D7

VDD37

D9

VDD38

E4

VDD39

E6

VDD40

E8

VDD41

VDD42

F5

VDD43

F7

VDD44

F9

VDD45

VDD46

G6

VDD47

G8

VDD48

VDD49

VDD50

H7

VDD51

VDD52

VDD53

J8

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

K7

VDD62

K9

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

L4

VDD71

L5

VDD72

L8

VDD73

VDD74

VDD75

VDD150

VDD151

5

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS240

VSS241

A3

A7

A9

A11

AA4

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE9

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

Y14

Y16

L14

L16

L18

M11

M13

M15

M17

M19

N10

N12

N14

N16

N18

P11

P13

P15

P17

P19

R10

R12

R14

R16

R18

R20

T11

T13

T15

T17

T19

T21

U10

U12

U14

U16

U18

U20

V11

V13

V15

V17

V19

V21

W10

W12

W14

W16

W18

W20

Y11

Y13

Y15

Y21

CPU1G

VDD2

VDD1

VDD2

VDD3

M2

VDD4

M3

VDD5

M7

VDD6

M9

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

N8

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

P7

VDD19

P9

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

R4

VDD26

R5

VDD27

R8

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

T2

VDD35

T3

VDD36

T7

VDD37

T9

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

U8

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

V9

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

W4

VDD59

W5

VDD60

W8

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

Y2

VDD68

Y3

VDD69

Y7

VDD70

Y9

VDD71

VDD72

VDD73

VDD74

VDD75

4

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

AK20

AK22

AK24

AK26

AK28

AK30

AL5

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H22

H24

H26

H28

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

Y18

+V_CPU

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AE12

AF11

M21

M23

N20

N22

P21

P23

R22

T23

U22

V23

W22

Y23

CPU1H

VDD3

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

L20

VDD19

L22

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

3

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

N17

N19

N21

N23

P2

P3

P8

P10

P12

P14

P16

P18

P20

P22

R7

R9

R11

R13

R15

R17

R19

R21

R23

T8

T10

T12

T14

T16

T18

T20

T22

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

W7

Y20

Y22

+1.8V_SUS

+1.2V_HT_CPU

+0.9V_SUS

C143

10UF 10V 0805 Y5V

1 2

+1.2V_HT_CPU

2

AB24

AB26

AB28

AB30

AC24

AD26

AD28

AD30

AF30

M24

M26

M28

M30

P24

P26

P28

P30

V25

V26

V28

V30

AJ4

AJ3

AJ2

AJ1

D12

C12

B12

A12

T24

T26

T28

T30

Y24

Y26

Y28

Y29

C147

1UF 16V 0805 Y5V

1 2

CPU1I

VDDIO

VLDT_B1

VLDT_A1

VLDT_B2

VLDT_A2

VLDT_B3

VLDT_A3

VLDT_B4

VLDT_A4

VTT1

VTT2

VTT3

VTT4

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO29

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

Title

Size Document Number Rev

Custom

Date: Sheet of

+1.2V_HT

H6

H5

H2

H1

AK12

VTT5

AJ12

VTT6

AH12

VTT7

AG12

VTT8

AL12

VTT9

K24

VSS1

K26

VSS2

K28

VSS3

K30

VSS4

L7

VSS5

L9

VSS6

L11

VSS7

L13

VSS8

L15

VSS9

L17

L19

L21

L23

M8

M10

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

M2 PWR/GND

1 2

1 2

+0.9V_SUS

N560B-A2T

1UF 16V 0805 Y5VC62

10UF 10V 0805 Y5VC68

8 39Wednesday, June 13, 2007

1

5.0

PDF created with pdfFactory Pro trial version www.pdffactory.com

+1.8V_SUS

5

DECOUPLING BETWEEN PROCESSOR AND DIMMS

PLACE AS CLOSE TO PROCESSOR AS

POSSIBLE

4

3

2

1

12

+V_CPU

BC24

+0.9V_SUS

12

C135

+0.9V_SUS

12

C39

12

BC22

1UF 16V 0805 Y5V

1UF 16V 0805 Y5V

0.1UF 16V Y5V 0402 /NI

1UF 10V Y5V

D D

C C

B B

12

C162

1UF 16V 0805 Y5V /NI

12

C46

1UF 16V 0805 Y5V

12

C153

1UF 10V Y5V

PLACE BOTTOM SIDE DECOUPLING

12

BC6

10UF 10V 0805 Y5V

12

BC14

1UF 16V 0805 Y5V

12

C144

1UF 16V 0805 Y5V

12

C34

0.1UF 16V Y5V 0402

12

BC23

10UF 10V 0805 Y5V

12

BC10

1UF 16V 0805 Y5V

12

C49

1UF 16V 0805 Y5V

12

12

BC15

1UF 16V 0805 Y5V

BC7

1UF 16V 0805 Y5V

12

C150

1UF 10V Y5V

12

C41

1UF 10V Y5V

+1.8V_SUS

12

BC2

1UF 16V 0805 Y5V

+V_CPU

BC12

100UF 2V CD

12

BC17

1UF 16V 0805 Y5V

12

C54

1UF 16V 0805 Y5V

12

C167

0.1UF 16V Y5V 0402

BC20

1UF 16V 0805 Y5V

+V_CPU

12

BC18

1UF 16V 0805 Y5V

A A

12

+1.8V_SUS

5

BC25

10UF 10V 0805 Y5V

12

C164

1UF 10V Y5V

12

BC13

1UF 16V 0805 Y5V

12

BC16

1UF 16V 0805 Y5V

12

C56

1UF 10V Y5V

12

+0.9V_SUS

12

4

BC11

1UF 16V 0805 Y5V

C47

0.1UF 16V Y5V 0402

12

BC21

1UF 16V 0805 Y5V

12

C140

12

12

0.1UF 16V Y5V 0402 /NI

C159

0.1UF 16V Y5V 0402

BC8

10UF 10V 0805 Y5V

3

12

BC19

1UF 16V 0805 Y5V

12

BC26

1UF 10V Y5V

12

BC9

1UF 16V 0805 Y5V

12

BC5

1UF 10V Y5V

Title

M2 DECOUPLING

Size Document Number Rev

Custom

2

Date: Sheet of

N560B-A2T

1

9 39Wednesday, June 13, 2007

5.0

PDF created with pdfFactory Pro trial version www.pdffactory.com

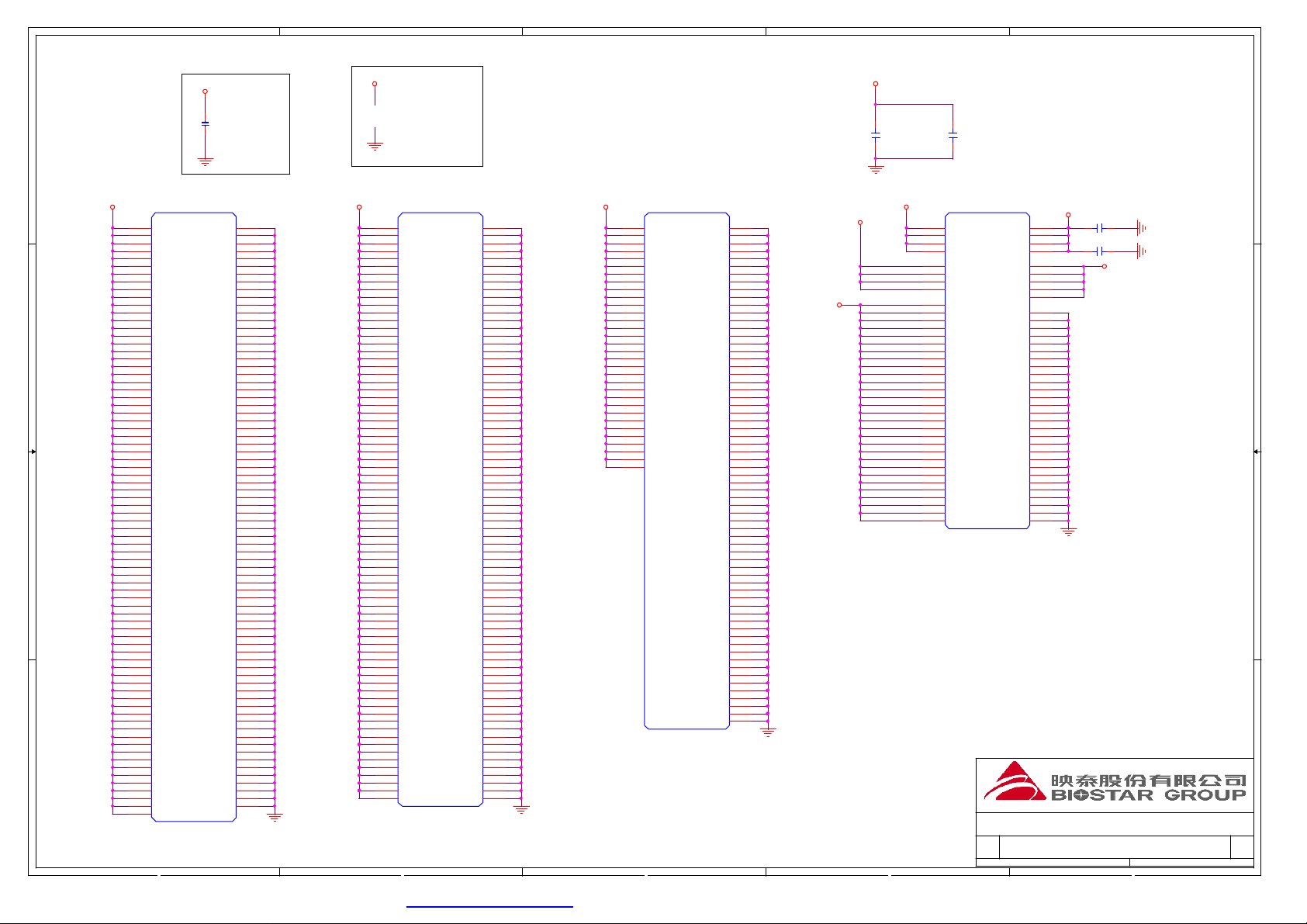

5

MEM_MA0_CLK_H25,11

MEM_MA0_CLK_L25,11

D D

C C

MEM_MA0_CLK_H15,11

MEM_MA0_CLK_L15,11

MEM_MA0_CLK_H05,11

MEM_MA0_CLK_L05,11

MEM_MB0_CLK_H26,12

MEM_MB0_CLK_L26,12

MEM_MB0_CLK_H16,12

MEM_MB0_CLK_L16,12

MEM_MB0_CLK_H06,12

MEM_MB0_CLK_L06,12

LAYOUT: FRONT SIDE PLACE ALTERNATING GND AND 1.8V

ALONG 0.9V VTT FILL

12

C155

1.5P 50V NPO 0402

C35

1.5P 50V NPO 0402

C106

1.5P 50V NPO 0402

C152

1.5P 50V NPO 0402

C40

1.5P 50V NPO 0402

C104

1.5P 50V NPO 0402

MEM_MA1_CLK_H25,11

MEM_MA1_CLK_H15,11

MEM_MA1_CLK_H05,11

MEM_MB1_CLK_H26,12

MEM_MB1_CLK_H16,12

MEM_MB1_CLK_H06,12

4

MEM_MA_ADD[15..0]5,11

MEM_MA1_CLK_L25,11

MEM_MA1_CLK_L15,11

MEM_MA1_CLK_L05,11

MEM_MB1_CLK_L26,12

MEM_MB1_CLK_L16,12

MEM_MB1_CLK_L06,12

C154

1.5P 50V NPO 0402

C38

1.5P 50V NPO 0402

C105

1.5P 50V NPO 0402

C151

1.5P 50V NPO 0402

C42

1.5P 50V NPO 0402

C107

1.5P 50V NPO 0402

3

MEM_MA_ADD[15..0] MEM_MB_ADD[15..0]

MEM_MB_BANK0

MEM_MB_RAS_L

MEM_MB1_CS_L0

MEM_MB0_CS_L0

MEM_MB_ADD1

MEM_MA_ADD3

MEM_MB_ADD3

MEM_MA_ADD4

MEM_MA_RAS_L

MEM_MA_ADD0

MEM_MB_BANK1

MEM_MB_ADD10

MEM_MB_ADD15

MEM_MA_ADD11

MEM_MA_ADD9

MEM_MA_ADD12

MEM_MB1_ODT0

MEM_MA1_ODT0

MEM_MA0_ODT0

MEM_MA_CKE1

MEM_MA_CKE0

MEM_MA_ADD15

MEM_MB_BANK2

MEM_MB0_ODT0

MEM_MB1_CS_L1

MEM_MA0_CS_L1

MEM_MB0_CS_L1

MEM_MA_BANK1

MEM_MB_ADD0

MEM_MA_ADD10

MEM_MA_BANK0

RN24 47 8P4R

78

56

34

12

RN19 47 8P4R

78

56

34

12

RN23 47 8P4R

78

56

34

12

RN12 47 8P4R

78

56

34

12

RN25 47 8P4R

78

56

34

12

RN9 47 8P4R

78

56

34

12

RN29 47 8P4R

78

56

34

12

RN22 47 8P4R

78

56

34

12

+0.9V_SUS

2

MEM_MB_ADD[15..0]6,12

MEM_MB_ADD12

MEM_MB_ADD9

MEM_MB_ADD11

MEM_MB_ADD7

MEM_MA_ADD6

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MB_ADD14

MEM_MA_ADD5

MEM_MB_ADD8

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD4

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MB_ADD2

MEM_MB_WE_L

MEM_MA_WE_L

MEM_MA0_CS_L0MEM_MB_CAS_L

MEM_MA1_CS_L0

MEM_MB_CKE0

MEM_MA_ADD14

MEM_MB_CKE1

MEM_MA_BANK2

MEM_MA_CAS_L

MEM_MA_ADD13

MEM_MB_ADD13

MEM_MA1_CS_L1

1

RN14 47 8P4R

78

56

34

12

RN11 47 8P4R

78

56

34

12

RN17 47 8P4R

78

56

34

12

RN20 47 8P4R

78

56

34

12

RN27 47 8P4R

78

56

34

12

RN10 47 8P4R

78

56

34

12

RN28 47 8P4R

78

56

34

12

+0.9V_SUS

+0.9V_SUS

B B

+1.8V_SUS

C165 1UF 10V Y5V

C55 1UF 16V 0805 Y5V

A A

+1.8V_SUS

C156 0.1UF 16V Y5V 0402

1 2

C95 0.1UF 16V Y5V 0402

1 2

C50 0.1UF 16V Y5V 0402

1 2

C57 0.1UF 16V Y5V 0402

1 2

1 2

1 2

5

C84 0.1UF 16V Y5V 0402

1 2

C67 0.1UF 16V Y5V 0402

1 2

C51 0.1UF 16V Y5V 0402

1 2

C148 1UF 10V Y5V

1 2

C157 0.1UF 16V Y5V 0402

1 2

C53 0.1UF 16V Y5V 0402

1 2

C100 0.1UF 16V Y5V 0402

1 2

C145 0.1UF 16V Y5V 0402

1 2

C37 0.1UF 16V Y5V 0402

1 2

4

MEM_MA_BANK05,11

MEM_MA_BANK15,11

MEM_MA_BANK25,11

MEM_MA_CAS_L5,11

MEM_MA_WE_L5,11

MEM_MA_RAS_L5,11

MEM_MA_BANK05,11

MEM_MA_BANK15,11

MEM_MA_BANK25,11

MEM_MA_CKE05,11

MEM_MA_CKE15,11

MEM_MA0_CS_L05,11

MEM_MA0_CS_L15,11

MEM_MA1_CS_L05,11

MEM_MA1_CS_L15,11

MEM_MA0_ODT05,11

MEM_MA1_ODT05,11

MEM_MA_CAS_L5,11

MEM_MA_WE_L5,11

MEM_MA_RAS_L5,11

3

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MB0_CS_L06,12

MEM_MB0_CS_L16,12

MEM_MB1_CS_L06,12

MEM_MB_BANK06,12

MEM_MB_BANK16,12

MEM_MB_BANK26,12

MEM_MB_CKE06,12

MEM_MB_CKE16,12

MEM_MB1_CS_L16,12

MEM_MB0_ODT06,12

MEM_MB1_ODT06,12

MEM_MB_CAS_L6,12

MEM_MB_WE_L6,12

MEM_MB_RAS_L6,12

22P 50V NPO 0402C119

22P 50V NPO 0402C120

22P 50V NPO 0402C69

22P 50V NPO 0402C130

22P 50V NPO 0402C129

22P 50V NPO 0402C124

22P 50V NPO 0402C111

22P 50V NPO 0402C96

22P 50V NPO 0402C99

22P 50V NPO 0402C98

22P 50V NPO 0402C91

22P 50V NPO 0402C92

22P 50V NPO 0402C87

22P 50V NPO 0402C80

22P 50V NPO 0402C88

22P 50V NPO 0402C75

22P 50V NPO 0402C116

22P 50V NPO 0402C76

22P 50V NPO 0402C134

22P 50V NPO 0402C70

22P 50V NPO 0402C63

+1.8V_SUS

MEM_MB_BANK06,12

MEM_MB_BANK16,12

MEM_MB_BANK26,12

MEM_MB_CAS_L6,12

MEM_MB_WE_L6,12

MEM_MB_RAS_L6,12

2

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

Title

DDR ADD/CTL/VTT TERMINATI

Size Document Number Rev

Custom

Date: Sheet of

22P 50V NPO 0402C115

22P 50V NPO 0402C110

22P 50V NPO 0402C64

22P 50V NPO 0402C125

22P 50V NPO 0402C126

22P 50V NPO 0402C121

22P 50V NPO 0402C112

22P 50V NPO 0402C93

22P 50V NPO 0402C97

22P 50V NPO 0402C94

22P 50V NPO 0402C89

22P 50V NPO 0402C90

22P 50V NPO 0402C82

22P 50V NPO 0402C77

22P 50V NPO 0402C83

22P 50V NPO 0402C71

22P 50V NPO 0402C117

22P 50V NPO 0402C78

22P 50V NPO 0402C7222P 50V NPO 0402C81

22P 50V NPO 0402C131

22P 50V NPO 0402C65

22P 50V NPO 0402C66

N560B-A2T

1

+1.8V_SUS+0.9V_SUS

5.0

10 39Wednesday, June 13, 2007

PDF created with pdfFactory Pro trial version www.pdffactory.com

5

4

3

2

1

191

194515662727578

VDDQ3

VDDQ4

VDDQ5

VDDQ6

+3.3V

DIMMA1

DIMMA2

172

178

184

187

189

1975359646769170

175

238

VDD1

VDD2

VDD3

VDD4

VDD5

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

ERR_OUT_L

VDDSPD

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

WE_L

VREF

TEST

ODT0

ODT1

PAR_IN

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

NC1

MEM_MA_DATA[0..63]

MEM_MA_DATA63

236

MEM_MA_DATA62

235

MEM_MA_DATA61

230

MEM_MA_DATA60

229

MEM_MA_DATA59

117

MEM_MA_DATA58

116

MEM_MA_DATA57

111

MEM_MA_DATA56

110

MEM_MA_DATA55

227

MEM_MA_DATA54

226

MEM_MA_DATA53

218

MEM_MA_DATA52

217

MEM_MA_DATA51

108

MEM_MA_DATA50

107

MEM_MA_DATA49

99

MEM_MA_DATA48

98

MEM_MA_DATA47

215

MEM_MA_DATA46

214

MEM_MA_DATA45

209

MEM_MA_DATA44

208

MEM_MA_DATA43

96

MEM_MA_DATA42

95

MEM_MA_DATA41

90

MEM_MA_DATA40

89

MEM_MA_DATA39

206

MEM_MA_DATA38

205

MEM_MA_DATA37

200

MEM_MA_DATA36

199

MEM_MA_DATA35

87

MEM_MA_DATA34

86

MEM_MA_DATA33

81

MEM_MA_DATA32

80

MEM_MA_DATA31

159

MEM_MA_DATA30

158

MEM_MA_DATA29

153

MEM_MA_DATA28

152

MEM_MA_DATA27

40

MEM_MA_DATA26

39

MEM_MA_DATA25

34

MEM_MA_DATA24

33

MEM_MA_DATA23

150

MEM_MA_DATA22

149

MEM_MA_DATA21

144

MEM_MA_DATA20

143

MEM_MA_DATA19

31

MEM_MA_DATA18

30

MEM_MA_DATA17MEM_MA_ADD15

25

MEM_MA_DATA16

24

MEM_MA_DATA15

141

MEM_MA_DATA14

140

MEM_MA_DATA13

132

MEM_MA_DATA12

131

MEM_MA_DATA11

22

MEM_MA_DATA10

21

MEM_MA_DATA9

13

MEM_MA_DATA8

12

MEM_MA_DATA7

129

MEM_MA_DATA6

128

MEM_MA_DATA5

123

MEM_MA_DATA4

122

MEM_MA_DATA3

10

MEM_MA_DATA2

9

MEM_MA_DATA1

4

MEM_MA_DATA0

3

73

1

102

195

77

55

68

19

MEM_MA_DATA[0..63]5

MEM_MA_WE_L5,10

MEM_M_VREF

MEM_MA0_ODT05,10

MEM_MA_DM[8..0]5

MEM_MA_DQS_H[8..0]5

MEM_MA_DQS_L[8..0]5

SMB_MEM_SCL12,18

SMB_MEM_SDA12,18

MEM_MA_BANK25,10

MEM_MA_BANK15,10

MEM_MA_BANK05,10

MEM_MA_ADD[15..0]5,10

MEM_MA_CHECK[7..0]5

MEM_MA1_CLK_H05,10

MEM_MA1_CLK_L05,10

MEM_MA1_CLK_H15,10

MEM_MA1_CLK_L15,10

MEM_MA1_CLK_H25,10

MEM_MA1_CLK_L25,10

MEM_MA_CKE15,10

MEM_MA_RAS_L5,10

MEM_MA_CAS_L5,10

MEM_MA1_CS_L05,10

MEM_MA1_CS_L15,10

MEM_MA_DM[8..0]

MEM_MA_DM8

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

MEM_MA_DQS_H[8..0]

MEM_MA_DQS_H8

MEM_MA_DQS_L8

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DQS_L[8..0]

+3.3V

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7 MEM_MA_DATA9

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_CHECK[7..0]

MEM_MA_CHECK7

MEM_MA_CHECK6

MEM_MA_CHECK5

MEM_MA_CHECK4

MEM_MA_CHECK3

MEM_MA_CHECK2

MEM_MA_CHECK1

MEM_MA_CHECK0

MEM_MA_CKE1

164

165

232

233

223

224

211

212

202

203

155

156

146

147

134

135

125

126

46

45

114

113

105

104

93

92

84

83

37

36

28

27

16

15

7

6

101

240

239

120

119

54

190

71

173

174

196

176

57

70

177

179

58

180

60

61

182

63

183

188

168

167

162

161

49

48

43

42

185

186

137

138

220

221

18

52

171

192

74

193

76

DDR2-240 pin-G

DQS17_H

DQS17_L

DQS16_H

DQS16_L

DQS15_H

DQS15_L

DQS14_H

DQS14_L

DQS13_H

DQS13_L

DQS12_H

DQS12_L

DQS11_H

DQS11_L

DQS10_H

DQS10_L

DQS9_H

DQS9_L

DQS8_H

DQS8_L

DQS7_H

DQS7_L

DQS6_H

DQS6_L

DQS5_H

DQS5_L

DQS4_H

DQS4_L

DQS3_H

DQS3_L

DQS2_H

DQS2_L

DQS1_H

DQS1_L

DQS0_H

DQS0_L

SA2

SA1

SA0

SCL

SDA

BA2

BA1

BA0

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

CK0_H

CK0_L

CK1_H

CK1_L

CK2_H

CK2_L

RESET_L

CKE0

CKE1

RAS_L

CAS_L

S0_L

S1_L

VDD6

181

VDD7

VDD8

VDD9

VDD10

VDD11

VDDQ1

VDDQ2

191

194515662727578

VDDQ3

VDDQ4

VDDQ5

VDDQ6

+3.3V+1.8V_SUS

DIMMA2

238

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

ERR_OUT_L

VDDSPD

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

WE_L

VREF

TEST

ODT0

ODT1

PAR_IN

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

NC1

MEM_MA_DATA[0..63]

236

235

230

229

117

116

111

110

227

226

218

217

108

107

99

98

215

214

209

208

96

95

90

89

206

205

200

199

87

86

81

80

159

158

153

152

40

39

34

33

150

149

144

143

31

30

25

24

141

140

132

131

22

21

13

12

129

128

123

122

10

9

4

3

73

1

102

195

77

55

68

19

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA30

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA26

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

MEM_MA_DATA[0..63]5

MEM_MA_WE_L5,10

MEM_M_VREF

12

C18

1UF 10V Y5V

MEM_MA1_ODT05,10

PLACE NEAR DIMM SOCKETS

+1.8V_SUS

DIMMA1

172

178

184

187

189

1975359646769170

175

D D

MEM_MA_DM[8..0]5

MEM_MA_DQS_H[8..0]5

C C

MEM_MA_DQS_L[8..0]5

SMB_MEM_SCL12,18

SMB_MEM_SDA12,18

MEM_MA_BANK25,10

MEM_MA_BANK15,10

MEM_MA_BANK05,10

MEM_MA_ADD[15..0]5,10

MEM_MA_CHECK[7..0]5

B B

MEM_MA0_CLK_H05,10

MEM_MA0_CLK_L05,10

MEM_MA0_CLK_H15,10

MEM_MA0_CLK_L15,10

MEM_MA0_CLK_H25,10

MEM_MA0_CLK_L25,10

MEM_MA_CKE05,10

MEM_MA_RAS_L5,10

MEM_MA_CAS_L5,10

MEM_MA0_CS_L05,10

MEM_MA0_CS_L15,10

MEM_MA_DM[8..0]

MEM_MA_DM8

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

MEM_MA_DQS_H[8..0]

MEM_MA_DQS_H8

MEM_MA_DQS_L8

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DQS_L[8..0]

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_CHECK[7..0]

MEM_MA_CHECK7

MEM_MA_CHECK6

MEM_MA_CHECK5

MEM_MA_CHECK4

MEM_MA_CHECK3

MEM_MA_CHECK2

MEM_MA_CHECK1

MEM_MA_CHECK0

MEM_MA_CKE0

164

165

232

233

223

224

211

212

202

203

155

156

146

147

134

135

125

126

46

45

114

113

105

104

93

92

84

83

37

36

28

27

16

15

7

6

101

240

239

120

119

54

190

71

173

174

196

176

57

70

177

179

58

180

60

61

182

63

183

188

168

167

162

161

49

48

43

42

185

186

137

138

220

221

18

52

171

192

74

193

76

DQS17_H

DQS17_L

DQS16_H

DQS16_L

DQS15_H

DQS15_L

DQS14_H

DQS14_L

DQS13_H

DQS13_L

DQS12_H

DQS12_L

DQS11_H

DQS11_L

DQS10_H

DQS10_L

DQS9_H

DQS9_L

DQS8_H

DQS8_L

DQS7_H

DQS7_L

DQS6_H

DQS6_L

DQS5_H

DQS5_L

DQS4_H

DQS4_L

DQS3_H

DQS3_L

DQS2_H

DQS2_L

DQS1_H

DQS1_L

DQS0_H

DQS0_L

SA2

SA1

SA0

SCL

SDA

BA2

BA1

BA0

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

CK0_H

CK0_L

CK1_H

CK1_L

CK2_H

CK2_L

RESET_L

CKE0

CKE1

RAS_L

CAS_L

S0_L

S1_L

DDR2-240 pin-T

VDD1

VDD2

VDD3

VDD4

VDD5

181

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDDQ1

VDDQ2

+1.8V_SUS

R41

A A

5

150 1% 0402

1 2

R42

150 1% 0402

1 2

12

C17

1UF 10V Y5V

MEM_M_VREF

12

C21

0.1UF 16V Y5V 0402 /NI

PLACE NEAR DIMM SOCKETS

Title

DDR DIMM0&1

Size Document Number Rev

C

4

3

2

Date: Sheet of

N560B-A2T

1

11 39Wednesday, June 13, 2007

PDF created with pdfFactory Pro trial version www.pdffactory.com

5.0

5

4

3

2

1

+1.8V_SUS

DIMMB1

172

178

184

187

189

1975359646769170

175

181

D D

C C

B B

MEM_MB_DM[8..0]6

MEM_MB_DQS_H[8..0]6

MEM_MB_DQS_L[8..0]6

SMB_MEM_SCL11,18

SMB_MEM_SDA11,18

MEM_MB_BANK26,10

MEM_MB_BANK16,10

MEM_MB_BANK06,10

MEM_MB_ADD[15..0]6,10

MEM_MB_CHECK[7..0]6

MEM_MB0_CLK_H06,10

MEM_MB0_CLK_L06,10

MEM_MB0_CLK_H16,10

MEM_MB0_CLK_L16,10

MEM_MB0_CLK_H26,10

MEM_MB0_CLK_L26,10

MEM_MB_RAS_L6,10

MEM_MB_CAS_L6,10

MEM_MB0_CS_L06,10

MEM_MB0_CS_L16,10

MEM_MB_DM[8..0]

MEM_MB_DM8

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

MEM_MB_DQS_H[8..0]

MEM_MB_DQS_H8

MEM_MB_DQS_L8

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DQS_L[8..0]

+3.3V

MEM_MB_ADD[15..0]

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10 MEM_MB_DATA12

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_CHECK[7..0]

MEM_MB_CHECK7

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

MEM_MB_CKE06,10

164

165

232

233

223

224

211

212

202

203

155

156

146

147

134

135

125

126

46

45

114

113

105

104

93

92

84

83

37

36

28

27

16

15

7

6

101

240

239

120

119

54

190

71

173

174

196

176

57

70

177

179

58

180

60

61

182

63

183

188

168

167

162

161

49

48

43

42

185

186

137

138

220

221

18

52

171

192

74

193

76

DQS17_H

DQS17_L

DQS16_H

DQS16_L

DQS15_H

DQS15_L

DQS14_H

DQS14_L

DQS13_H

DQS13_L

DQS12_H

DQS12_L

DQS11_H

DQS11_L

DQS10_H

DQS10_L

DQS9_H

DQS9_L

DQS8_H

DQS8_L

DQS7_H

DQS7_L

DQS6_H

DQS6_L

DQS5_H

DQS5_L

DQS4_H

DQS4_L

DQS3_H

DQS3_L

DQS2_H

DQS2_L

DQS1_H

DQS1_L

DQS0_H

DQS0_L

SA2

SA1

SA0

SCL

SDA

BA2

BA1

BA0

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

CK0_H

CK0_L

CK1_H

CK1_L

CK2_H

CK2_L

RESET_L

CKE0

CKE1

RAS_L

CAS_L

S0_L

S1_L

DDR2-240 pin-T

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDDQ1

VDDQ2

191

194515662727578

VDDQ3

VDDQ4

VDDQ5

VDDQ6

+3.3V

DIMMB1

238

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

ERR_OUT_L

VDDSPD

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

WE_L

VREF

TEST

ODT0

ODT1

PAR_IN

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

NC1

MEM_MB_DATA[0..63]

236

235

230

229

117

116

111

110

227

226

218

217

108

107

99

98

215

214

209

208

96

95

90

89

206

205

200

199

87

86

81

80

159

158

153

152

40

39

34

33

150

149

144

143

31

30

25

24

141

140

132

131

22

21

13

12

129

128

123

122

10

9

4

3

73

1

102

195

77

55

68

19

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38MEM_MB_DQS_L5

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA11MEM_MB_ADD9

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

12

C20