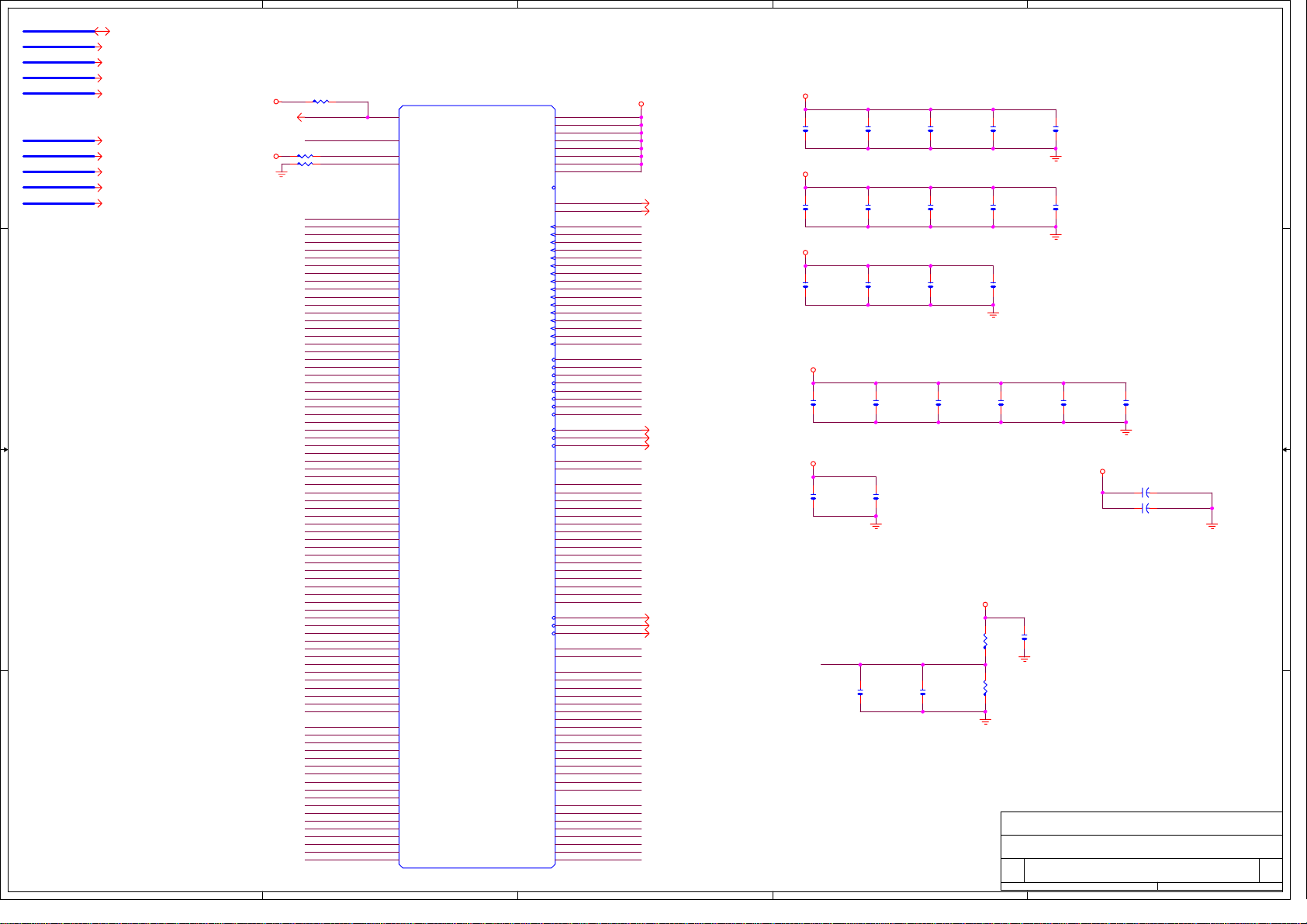

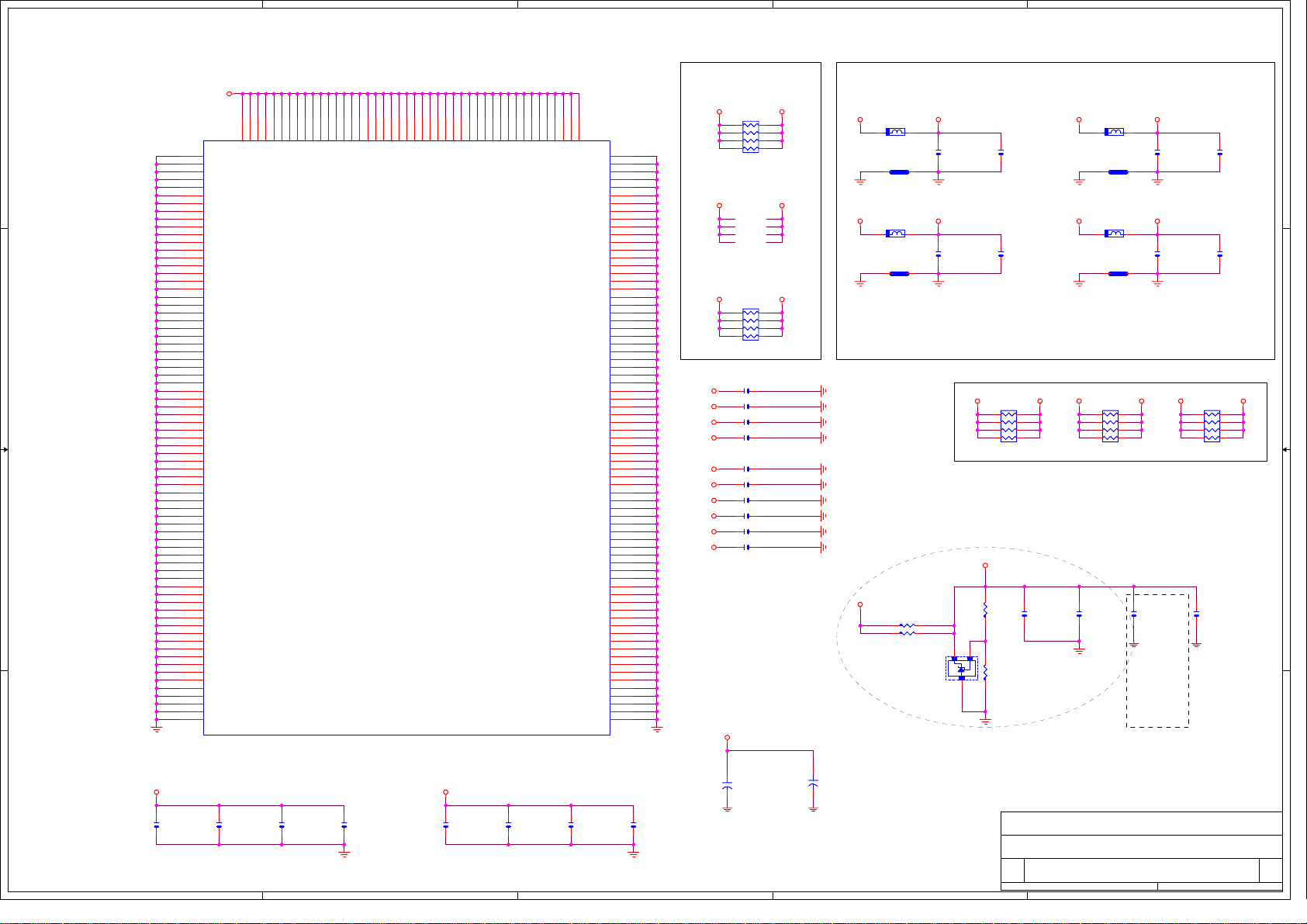

Gigabyte xp-m8vm800 r10a-0728-1 Schematics

5

4

3

2

1

GIGABYTE XP-M8VM800 Schematics

D D

SHEET

1

2

3

4,5,6,7

8,9,10

11,12,13

C C

14

15,17

18

19

21

22

COVER SHEET

BOM & PCB MODIFY HISTORY

BLOCK DIAGRAM

AMD K8 CLAWHAMMER

VIA_K8M800 (NORTH BRIDGE)

VIA_VT8237 (SOUTH BIRDGE)

CLOCK GENERATOR

DDR SDRAM DIMMS 1,2 & DDR Termination

AGP SLOT

PCI SLOT 1,2,3

IDE,FRONT USB

LPC I/O_ITE8705

TITLE

SHEET TITLE

REV:1.0

23

24

B B

25

26

27

BIOS & FDD

AUDIO AC97

AUDIO JACK & GAMEPORT

COM,PRT,KB/MS

RTL8100C & USB CONNECTOR

16,20,28 INFO CON,VGA CON, FRONT PANEL

29

30

31

A A

32

33

34

5

VCORE (PWM ISL6559BC+6602B+6601B)

VCC12,VCC18,VCC25,VDDQ

ATX, DC POWER

DDR POWER(5VDUAL,3VDUAL,25VSTR,VTTDDR)

POWER SEQUENCE

TI TSB43AB23 1394

4

COMPONENT SIDE

(0.5 oz. Copper)

GND SIDE

(1 oz. Copper)

VCC SIDE

(1 oz. Copper)

SOLDER SIDE

(0.5 oz. Copper)

Title

Size Document Number Rev

Custom

3

2

Date: Sheet

AXPER

COVER SHEET

AXPER

1

135Monday, August 01, 2005

of

1.0

5

4

3

2

1

XP-M8VM800

Component value change history

Date Change Item Reason

D D

1/28 -FA-0.2

2/12 -FA-0.3

C C

0.19/25

1. Add C708,709,710,711,707 follow rule

2.

Add Q168,169,RN243

3.

4.

Del R28

follow ruleDel EC63,65,66,86,87

For CPURESET issue

For CPURESET issue

5.6.Add EC19,EC21,EC24,EC25,CI,R1271,Q30,R334 For FA

F_PANEL change to JP2*10/-10,-11,-12 For FA

1.

Add BC61,BC376,R1362,C616,C617,D52,EC43

L11,L12,Q155,R1268,R1270,R1276,R1269

R1278,R1280,R1281,Q149,Q150,Q151,Q154

R1266,R1272,R1273,R1424,U38,U51,U52

For FA

VIA K8M800 + VT8237 CHIPSET FOR AMD K8

Circuit or PCB layout change for next version

Date Change Item Reason

1/28 0.2

1. Add RN243,Q168,Q169,R1425 For CPURESET issue

Remove R28 For CPURESET issue

F_PANEL change to 2*5 pin

Remove EC84,EC85,

EC86,87 change to C708,709 follow rule

EC65,66,63&C710,711,707 COLAY follow rule

3/9 0.4

1. Add PCI test mode

5/12 1.02

From K8VT800M 1.04 change1.

3/18 '05 2.0 Costdown

94.06.21_2.02

Vcore PWM Re-Layout, PWORK

線路修正。

follow rule

follow rule

3/15 -00-1.0

1. change to disty value follow rule

MS/KB change to KB_MS

1. add RN244,245,246 follow rule

5/3

B B

5/21

10A

1.

PCB change to 1.01

2.

R1312 change to 1k/6

3.

L5,6,10 change to 48 type

4.

R230 add 0/6

5.

R1415,1416 change to 1K/6

6.

remove LED,R343

7.

SB heat sink change to12SP2-04E004-01,02,03

10B

1. PCB change to 1.02

for LE

follow rule

follow rule

follow rule

follow rule

follow rule

follow rule

for AMD frequency

94/07/08

XP-M7VM800 R10A

94/07/20

XP-M8VM800 R10A

For AXPER XP-M7VM800 R10A

For AXPER XP-M8VM800 R10A

6/11 10B P-BOM

8/11 10B ECN

A A

U10 10HL4-132004-71 Add second source1.

9/15 10C

AXPER

BOM & PCB MODIFY HISTORY

AXPER

235Monday, August 01, 2005

1

of

1.0

10/08

C86 change to 100K/41. Follow VIA note

10D

Add DL CKD BOM, remove KTS battery, manual,color box

5

4

Title

Size Document Number Rev

Custom

3

2

Date: Sheet

5

4

3

2

1

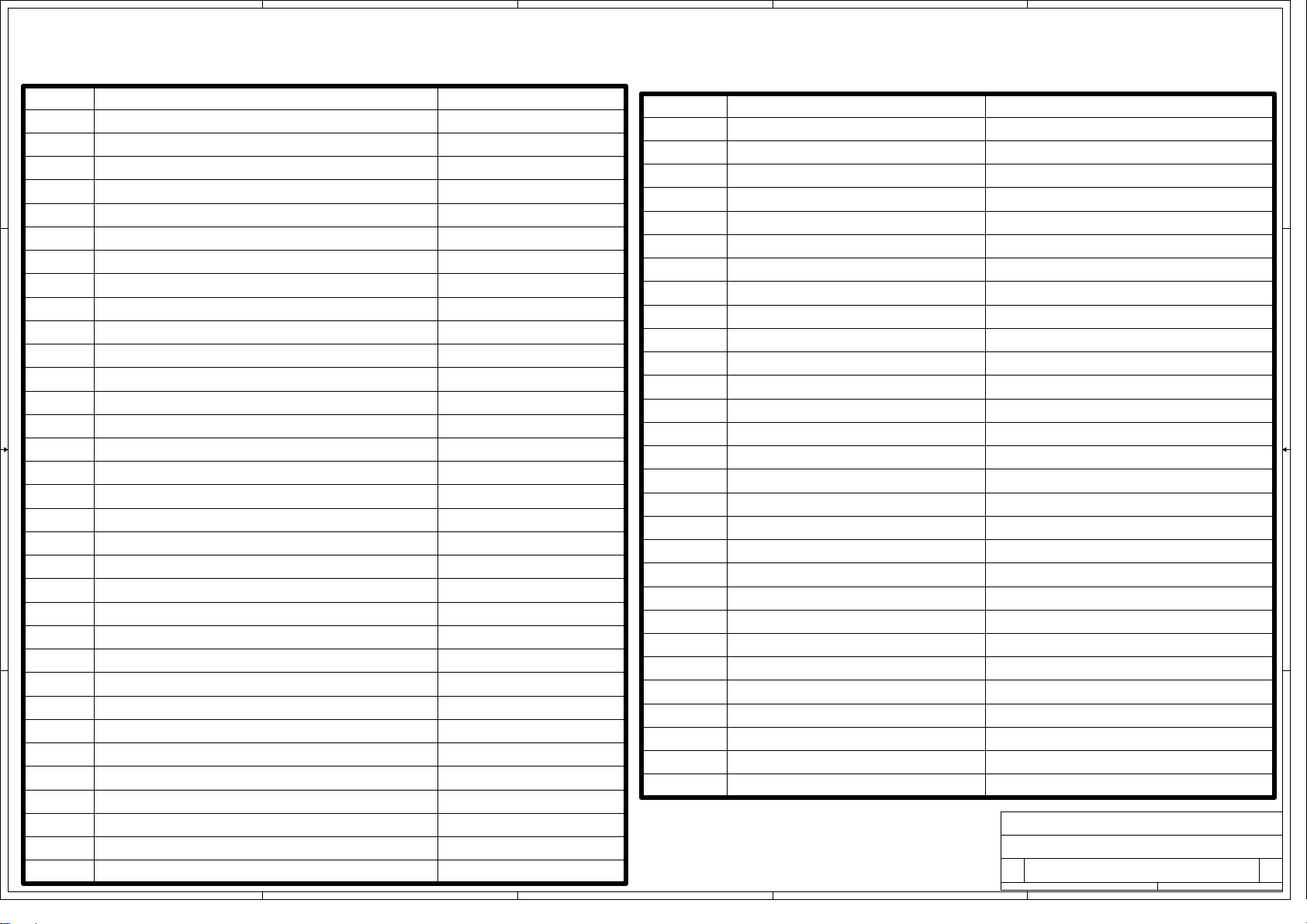

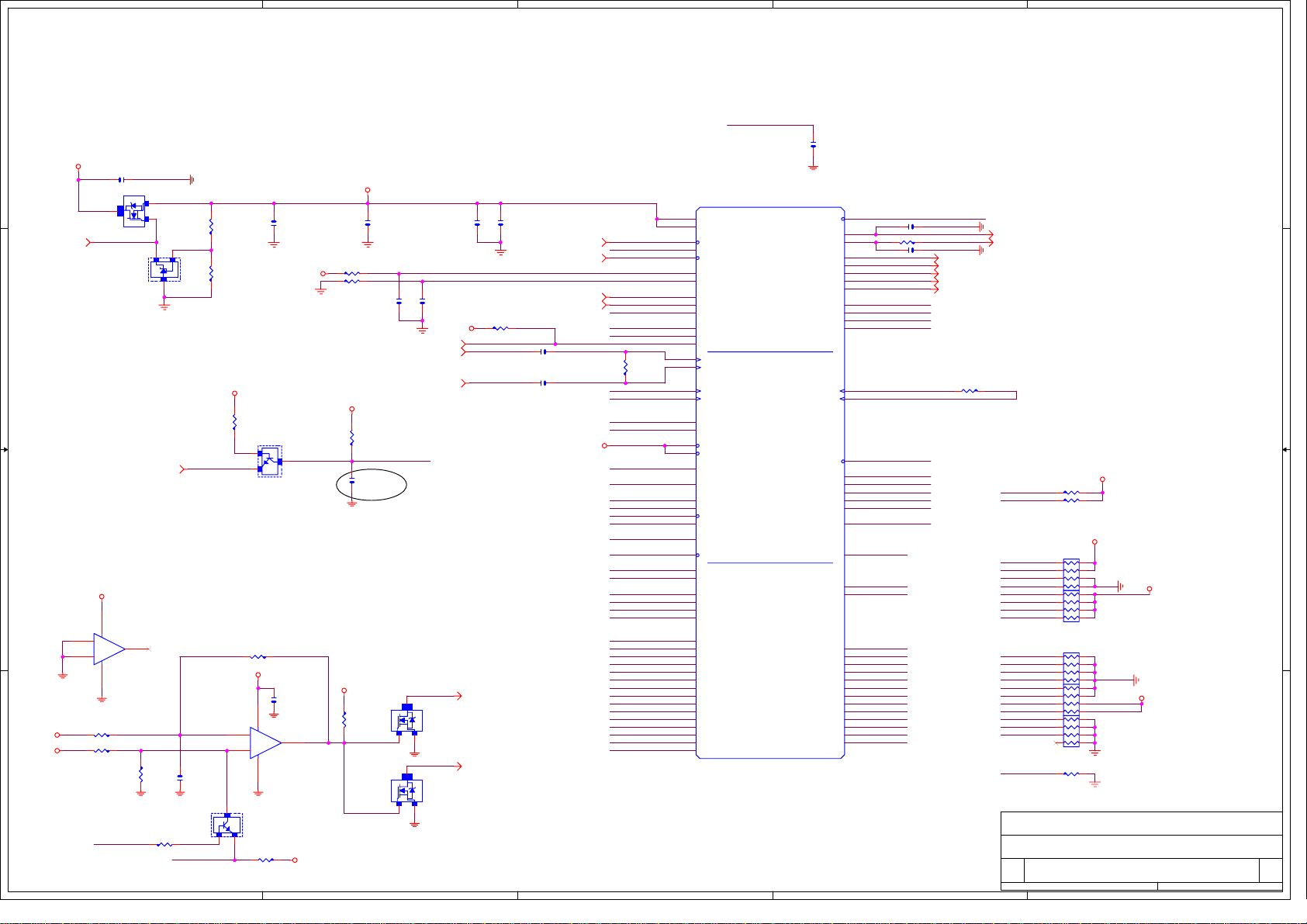

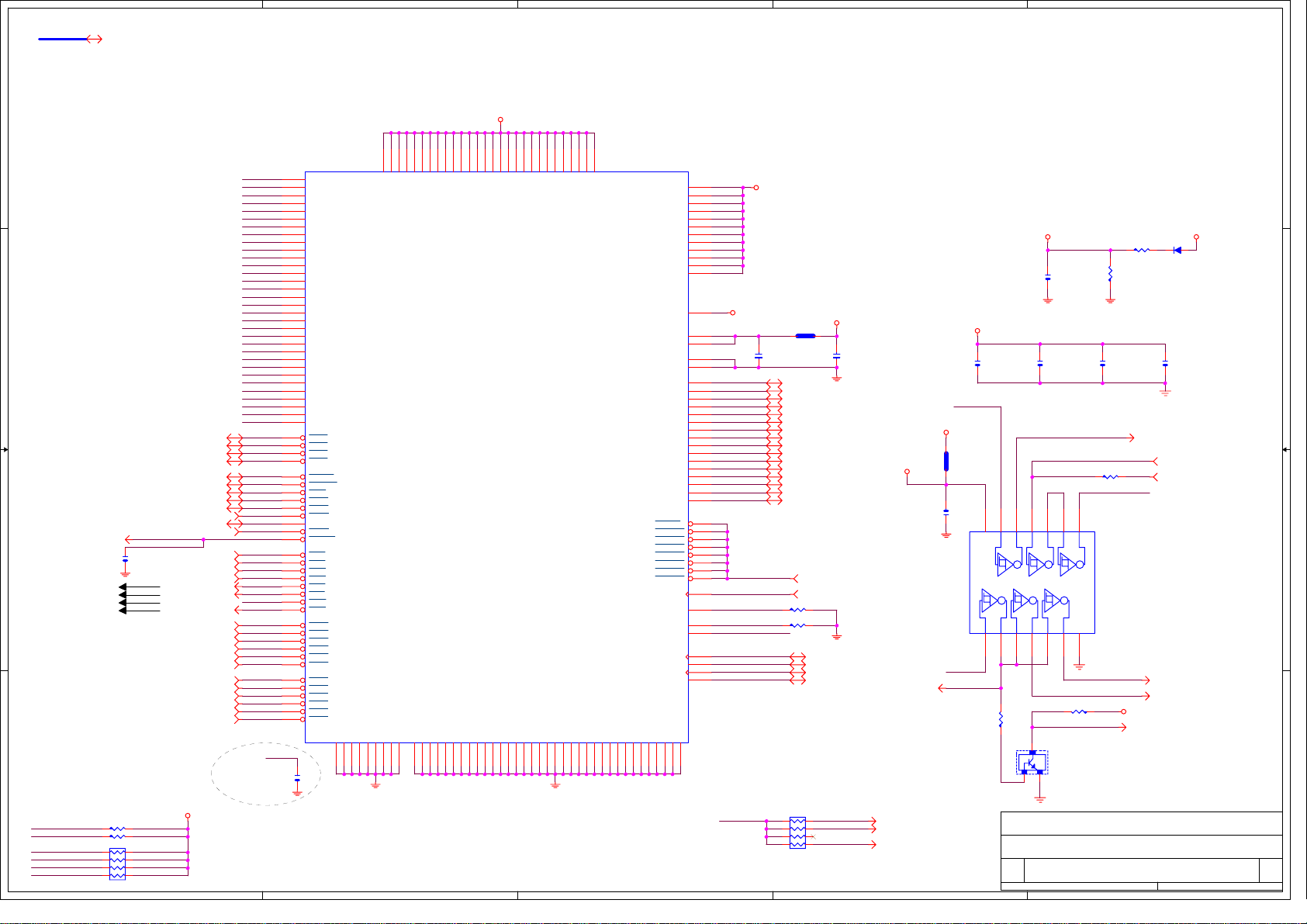

XP-M8VM800 BLOCK DIAGRAM

System Block Diagram

D D

AMD K8 CLAWHAMMER

VCC12=1.2V

VCC25=2.5V

25VSTR=2.5V CPUVREF=1.25V

HT12B=1.2V

P.4,5,6,7

If use K8T800

AGP 8X SLOT

VDDQ=1.5V or 3.3V

C C

GVREF_CG=0.35V or 0.75V

P.18

PCI SLOT 1~3

P.19

VIA K8M800/K8T800

VCC12=1.2V

VCC25=2.5V

P.8,9,10

25VDDA=2.5V

VTTDDR=1.25V

LDT

LINK

VDD=1.5V or 2.5V

VDDQ=1.5V or 3.3V

V-LINK

REAR USB2.0 X4

FUSEPWR=5V

P.21,27

VIA VT8237/VT8235(CE)

DDR SDRAM

DIMM 1

25VSTR=2.5V

DDRVREF=1.25V

P.15

DIMM 2

25VSTR=2.5V

DDRVREF=1.25V

P.15

IDE 1,2 (ATA133)

P.21

KEYBOARD/MOUSE

5VDUAL=5V

FUSEVCC=5V

P.26

Rtt

SSTL-2

Termination

25VSTR=2.5V

VTTDDR=1.25V

P.17

CPUCLKT

CPUCLKC

NBGCLK

GUICLK

VCLK

SBPCLK

SB14CLK

APICCLK

USBCLK

-PCICLK

SMBCLK

SMBDAT

CLOCK

GEN

CYPRESS

28331

P.14

AGPGCLK

PCICLK0

PCICLK1

PCICLK2

SIOPCLK

SIO48CLK

LANCLK

1394CLK

AUDIO14

FRONT USB2.0 X4

FUSEPWR1=5V

P.21

B B

LAN RTL8100C

VDD25=2.5V AVDD33=3.3V

P.27

VCC25=2.5V

3VDUAL=3.3V

25VDUAL=2.5V VSUS=1.5V or 2.5V

P.11,12,13

VLVREF=0.625V

RTCVDD=3.3V

AC'97_ALC650/655/658

AVDD=5V

P.24

TSB43AB23A 1394

1394VDD=3.3V 3VDUAL=3.3V

P.34

LPC

Bus

Analog Out

AVDD=5V

P.25

Analog In

AVDD=5V

P.25

3D Audio Out

AVDD=5V

P.25

FLASH ROM

P.23

A A

5

X_Bus

5VSB=5V

P.22

P.26 P.26 P.26 P.23

SERIAL PARALLEL FLOPPYIR

4

LPC IT8705

3

VOLTAGE MONITOR

P.22

TEMPERATURE MONITOR

P.22

2

Title

Size Document Number Rev

Custom

Date: Sheet

AXPER

BLOCK DIAGRAM

AXPER

1

335Monday, August 01, 2005

of

1.0

5

4

3

2

1

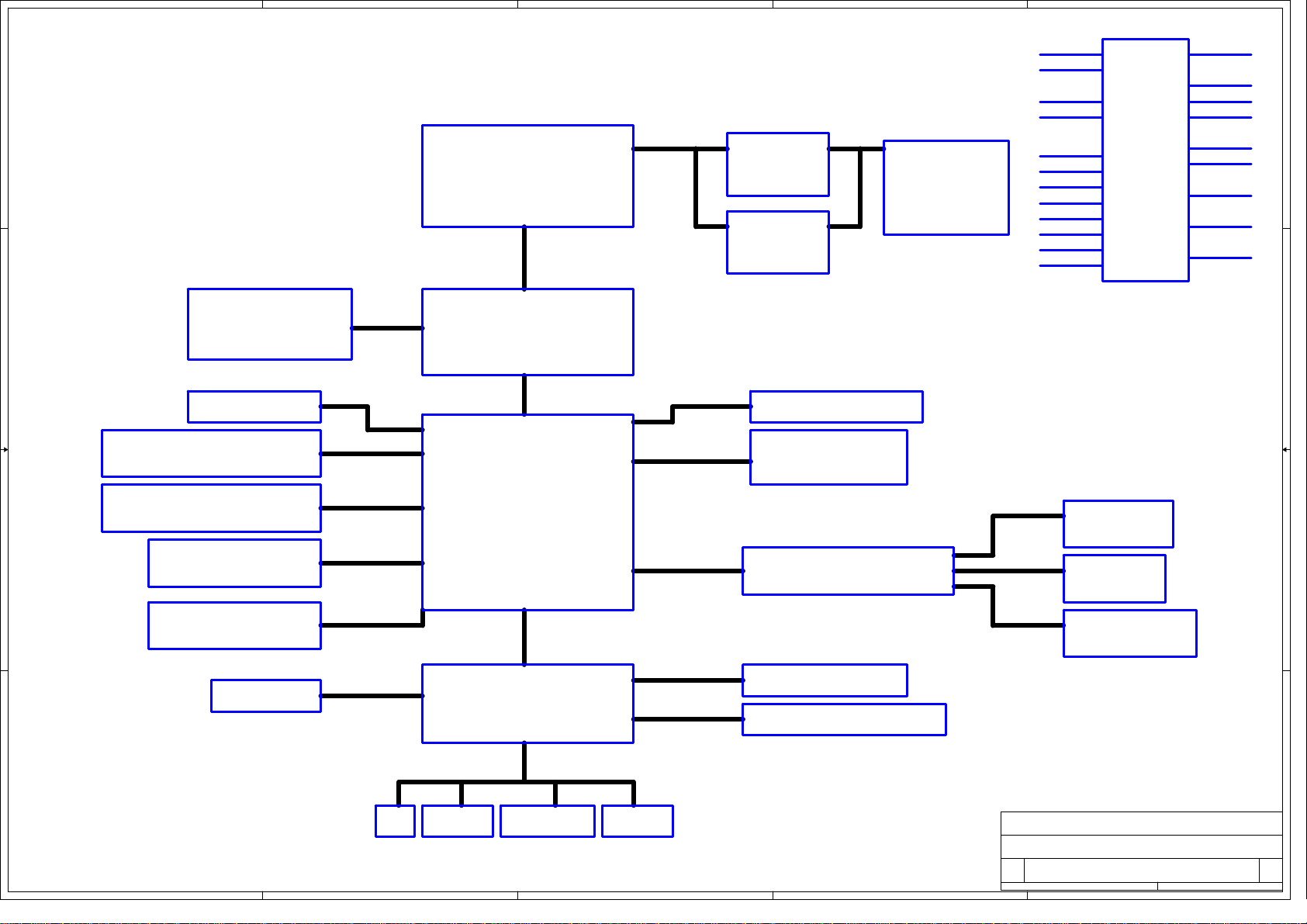

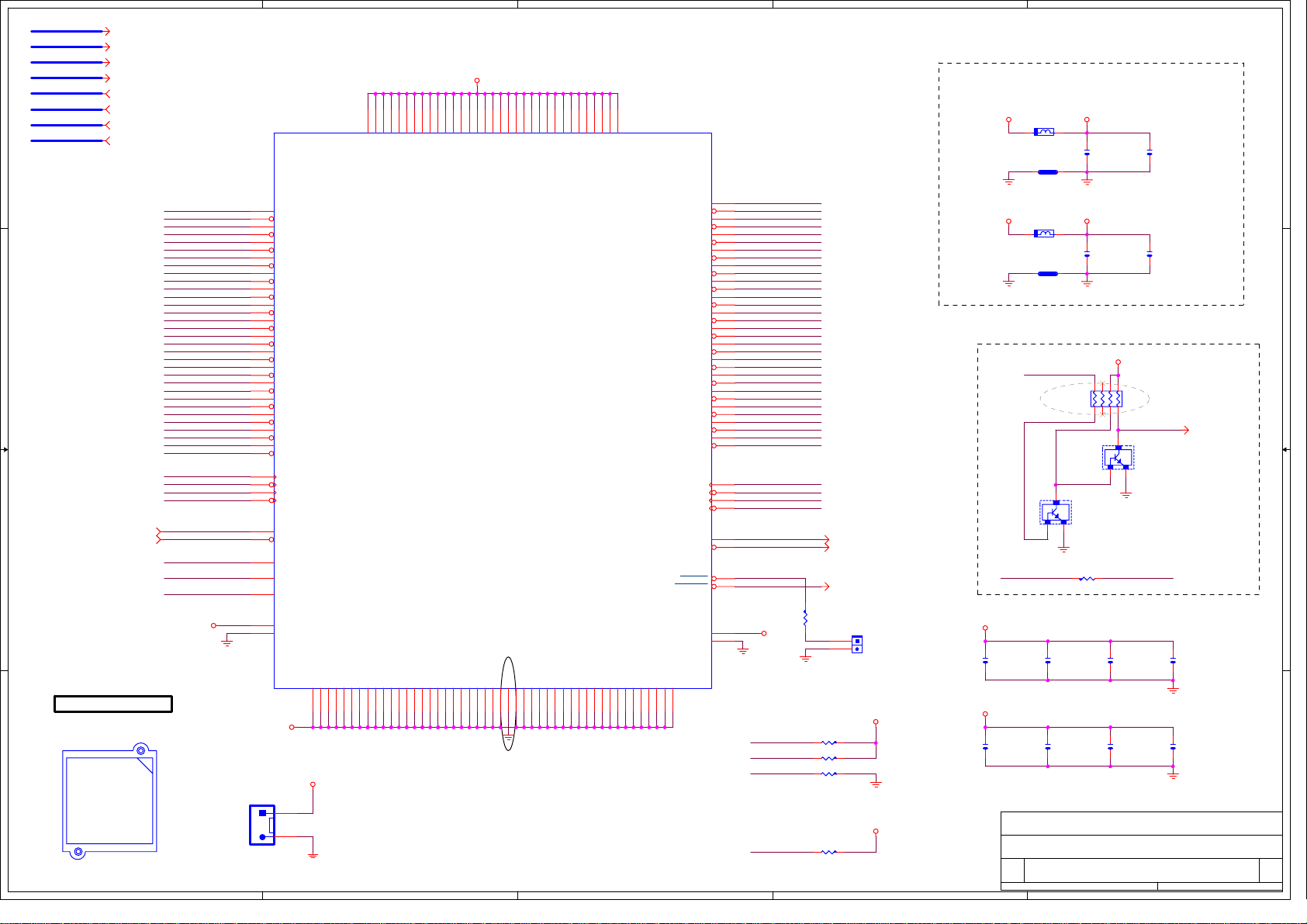

L0_CADIN_L[0..15]

D D

C C

B B

L0_CADIN_H[0..15]

L0_CLKIN_L[0..1]

L0_CLKIN_H[0..1]

L0_CADOUT_L[0..15]

L0_CADOUT_H[0..15]

L0_CLKOUT_L[0..1]

L0_CLKOUT_H[0..1]

L0_CADIN_L[0..15] 8

L0_CADIN_H[0..15] 8

L0_CLKIN_L[0..1] 8

L0_CLKIN_H[0..1] 8

L0_CADOUT_L[0..15] 8

L0_CADOUT_H[0..15] 8

L0_CLKOUT_L[0..1] 8

L0_CLKOUT_H[0..1] 8

HT12B

R1 49.9/6/1

R2 49.9/6/1

L0_CTLIN_H08

L0_CTLIN_L08

VCC12

Clawhammer HT Interface

VCC12 HT12B

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

3/8/2005

D29

VLDT0_A6

D27

VLDT0_A5

D25

VLDT0_A4

C28

VLDT0_A3

C26

VLDT0_A2

B29

VLDT0_A1

B27

VLDT0_A0

T25

L0_CADIN_H15

R25

L0_CADIN_L15

U27

L0_CADIN_H14

U26

L0_CADIN_L14

V25

L0_CADIN_H13

U25

L0_CADIN_L13

W27

L0_CADIN_H12

W26

L0_CADIN_L12

AA27

L0_CADIN_H11

AA26

L0_CADIN_L11

AB25

L0_CADIN_H10

AA25

L0_CADIN_L10

AC27

L0_CADIN_H9

AC26

L0_CADIN_L9

AD25

L0_CADIN_H8

AC25

L0_CADIN_L8

T27

L0_CADIN_H7

T28

L0_CADIN_L7

V29

L0_CADIN_H6

U29

L0_CADIN_L6

V27

L0_CADIN_H5

V28

L0_CADIN_L5

Y29

L0_CADIN_H4

W29

L0_CADIN_L4

AB29

L0_CADIN_H3

AA29

L0_CADIN_L3

AB27

L0_CADIN_H2

AB28

L0_CADIN_L2

AD29

L0_CADIN_H1

AC29

L0_CADIN_L1

AD27

L0_CADIN_H0

AD28

L0_CADIN_L0

Y25

L0_CLKIN_H1

W25

L0_CLKIN_L1

Y27

L0_CLKIN_H0

Y28

L0_CLKIN_L0

R27

L0_CTLIN_H1

R26

L0_CTLIN_L1

T29

L0_CTLIN_H0

R29

L0_CTLIN_L0

HOLE5

HOLE6

1

2

CPU-SK/754/D

SOCKET_754A

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

AH29

VLDT0_B6

AH27

VLDT0_B5

AG28

VLDT0_B4

AG26

VLDT0_B3

AF29

VLDT0_B2

AE28

VLDT0_B1

AF25

VLDT0_B0

N26

N27

L25

M25

L26

L27

J25

K25

G25

H25

G26

G27

E25

F25

E26

E27

N29

P29

M28

M27

L29

M29

K28

K27

H28

H27

G29

H29

F28

F27

E29

F29

J26

J27

J29

K29

N25

P25

P28

P27

HYPER TRANSPORT - LINK0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1L0_CTLIN_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

HT12B

L0_CTLOUT_H0 8

L0_CTLOUT_L0 8

C1

10U/12/Y5V/10V

C2

10U/12/Y5V/10V

DEL EC57

3/25

VCC12

C6

0.22U/4/Y/10V

A A

5

C7

0.22U/4/Y/10VC80.22U/4/Y/10V

4

C9

0.22U/4/Y/10V

Near CPU side

3

Title

Size Document Number Rev

Custom

2

Date: Sheet

AXPER

K8 SOCKET 754-1

AXPER

1

435Monday, August 01, 2005

1.0

of

5

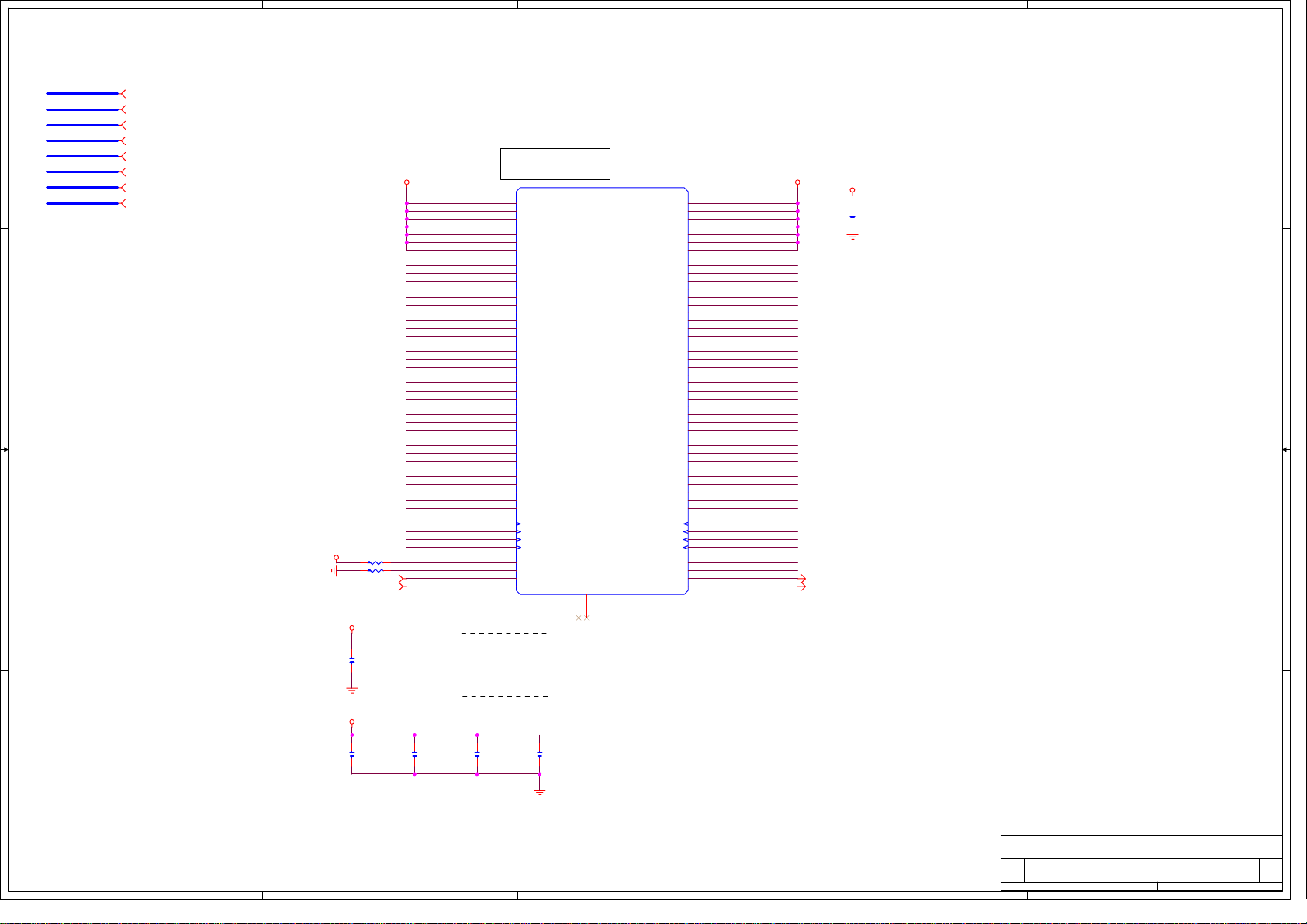

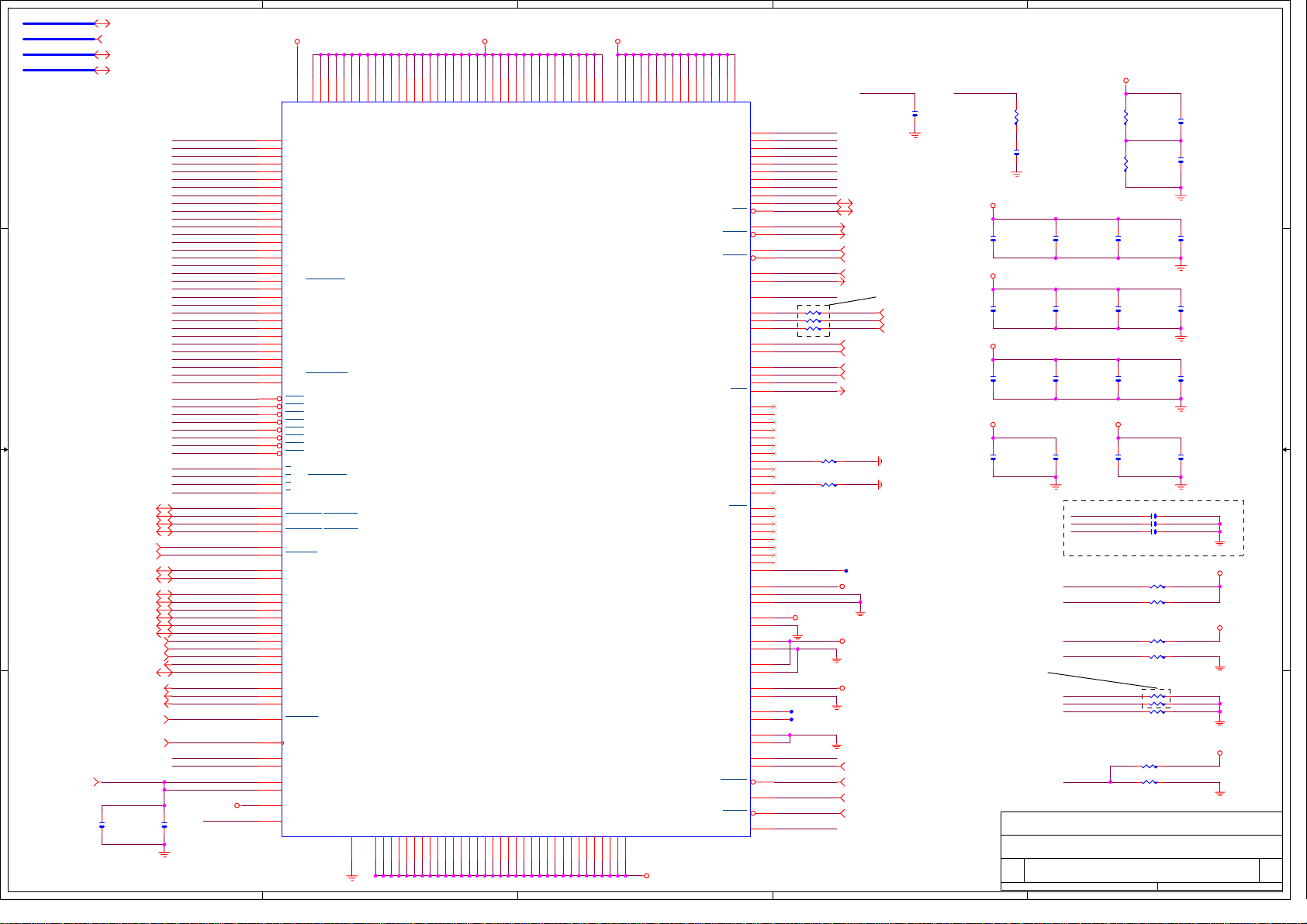

MD[0..63]

MAA[0..13]

-DQS[0..17]

DCLK[0..7]

-DCLK[0..7]

D D

MEMBANKB[0..1]

MAB[0..13]

MEMCHECK[0..7]

MEMBANKA[0..1]

-CS[0..5]

C C

B B

A A

MD[0..63] 17

MAA[0..13] 15,17

-DQS[0..17] 17

DCLK[0..7] 15,17

-DCLK[0..7] 15,17

MEMBANKB[0..1] 15,17

MAB[0..13] 15,17

MEMCHECK[0..7] 17

MEMBANKA[0..1] 15,17

-CS[0..5] 15,17

5

VTTDDR

VTTDDR_SENSE32

25VSTR

R1120 51.1/6/1/X

VTTDDR_SENSE

CPUVREF

R4 15/6/1

R5 15/6/1

MD63

MD62

MD61

MD60

MD59

MD58

MD57

MD56

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

MD47

MD46

MD45

MD44

MD43

MD42

MD41

MD40

MD39

MD38

MD37

MD36

MD35

MD34

MD33

MD32

MD31

MD30

MD29

MD28

MD27

MD26

MD25

MD24

MD23

MD22

MD21

MD20

MD19

MD18

MD17

MD16

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

-DQS17

-DQS16

-DQS15

-DQS14

-DQS13

-DQS12

-DQS11

-DQS10

-DQS9

-DQS8

-DQS7

-DQS6

-DQS5

-DQS4

-DQS3

-DQS2

-DQS1

-DQS0

MEMZN

MEMZP

AE13

AG12

D14

C14

A16

B15

A12

B11

A17

A15

C13

A11

A10

C11

AC1

AC3

AC2

AD1

AE1

AE3

AG3

AJ4

AE2

AF1

AH3

AJ3

AJ5

AJ6

AJ7

AH9

AG5

AH5

AJ9

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

A13

AA1

AG1

AH7

AH13

A14

AB1

AJ2

AJ8

AJ13

4

B9

C7

A6

A9

A5

B5

C5

A4

E2

E1

A3

B3

E3

F1

G2

G1

L3

L1

G3

J2

L2

M1

W1

W3

W2

Y1

R1

A7

C2

H1

T1

A8

D1

J1

4

VTT_SENSE

MEMVREF1

MEMZN

MEMZP

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDQS17

MEMDQS16

MEMDQS15

MEMDQS14

MEMDQS13

MEMDQS12

MEMDQS11

MEMDQS10

MEMDQS9

MEMDQS8

MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0

SOCKET_754B

RSVD_MEMADDA15

RSVD_MEMADDA14

RSVD_MEMADDB15

RSVD_MEMADDB14

MEMORY INTERFACE

VTT_A4

VTT_A1

VTT_A2

VTT_A3

VTT_B1

VTT_B2

VTT_B3

VTT_B4

MEMRESET_L

MEMCKEA

MEMCKEB

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

MEMADDB13

MEMADDB12

MEMADDB11

MEMADDB10

MEMADDB9

MEMADDB8

MEMADDB7

MEMADDB6

MEMADDB5

MEMADDB4

MEMADDB3

MEMADDB2

MEMADDB1

MEMADDB0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

D17

A18

B17

C17

AF16

AG16

AH16

AJ17

AG10

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E14

D12

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

MEMCKEA

MEMCKEB

DCLK7

-DCLK7

DCLK6

-DCLK6

DCLK5

-DCLK5

DCLK4

-DCLK4

DCLK3

-DCLK3

DCLK2

-DCLK2

DCLK1

-DCLK1

DCLK0

-DCLK0

-CS7

-CS6

-CS5

-CS4

-CS3

-CS2

-CS1

-CS0

-SRASA

-SCASA

-SWEA

MEMBANKA1

MEMBANKA0

MAA15

MAA14

MAA13

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

-SRASB

-SCASB

-SWEB

MEMBANKB1

MEMBANKB0

MAB15

MAB14

MAB13

MAB12

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

3

VTTDDR

MEMCKEA 15,17

MEMCKEB 15,17

-SRASA 15,17

-SCASA 15,17

-SWEA 15,17

-SRASB 15,17

-SCASB 15,17

-SWEB 15,17

3

2

1

Place a cap every 0.5 in. on VTTDDR traces between CPU and DDR.

VTTDDR

C16

0.22U/4/Y/10V

VTTDDR

C22

0.22U/4/Y/10V

VTTDDR

C28

100P/4/N/50V

C17

0.22U/4/Y/10V

C23

0.22U/4/Y/10V

C29

100P/4/N/50V

C18

0.22U/4/Y/10V

C24

0.22U/4/Y/10V

C30

1N/4/X/50V

C20

0.22U/4/Y/10V

C26

0.1U/4/Y/16V/X

C31

1N/4/X/50V

C21

0.22U/4/Y/10V

C27

0.1U/4/Y/16V/X

Locate close to CPU socket

VTTDDR

C34

4.7U/12/X5R/10V

VTTDDR

C352

10U/12/Y5V/10V/X

C35

4.7U/12/X5R/10V

C353

10U/12/Y5V/10V/X

C36

4.7U/12/X5R/10V

C19

4.7U/12/X5R/10V

C25

4.7U/12/X5R/10V

VTTDDR

C37

4.7U/12/X5R/10V

+

EC54 100U/D/10V/57

+

EC55 100U/D/10V/57

CPUVREF

25VSTR

C38

R7

0.1U/4/Y/16V

150/6/1

R8

150/6/1

Title

Size Document Number Rev

Custom

Date: Sheet

AXPER

K8 SOCKET 754-2

AXPER

1

535Monday, August 01, 2005

of

CPUVREF

40

MILS

C39

1N/4/X/50V

C40

0.1U/4/Y/16V

2

1.0

5

4

3

2

1

D D

3VDUAL

BC433 0.1U/6/Y/25V/X

Q59 2N7002/SOT23

3

25VDDA_EN33

C C

B B

VCC

5VSB

A A

25VDDA_EN

5VSB

84

5

+

6

-

R18 10K/6

R19 8.2K/6

-CPURST

D

CPU_PWROK11

U17B

7

KA393D/SO8

R22 8.2K/6

5

1

2

GS

Q104

APL431BAI-TR/SOT23/150mA

CAR

SOT23

RAC

R21

C48

8.2K/6

1U/6/Y/16V

-THRMTRIP

R466

22/6

R467

1K/6/1

VCC25

R868

8.2K/6

Q61

2

1

SOT23

R16 4.7K/6

5VSB

84

3

+

2

-

Q3

MMBT2222A/SOT23

SOT23

132

R23

1K/6

BC407

10U/12/Y5V/10V

HT12B

3

MMBT2222A/SOT23

C507

0.1U/4/Y/16V/X

U17A

1

KA393D/SO8

VCC25

Route trace 50 mils wide and 500

to 750 mils long between these

caps.

25VDDA

C41

R9 44.2/6/1

R10 44.2/6/1

1N/4/X/50V

VCC25

R516

8.2K/6

C506

1N/4/X/50V

VCC

R17

1K/6

10U/12/Y5V/10V

C44

K8PWROK

GS

2

GS

2

4

C42

10N/4/X/50V

C45

1N/4/X/50V

25VSTR

25VSTRFB32

CPUCLK0_H14

CPUCLK0_L14

Modify at 11/8

3

Q1

D

2N7002/SOT23

1

3

Q2

D

2N7002/SOT23

1

C43

1N/4/X/50V

R1121 51.1/6/1/X

25VSTRFB

CPUCLK0_H

VCORE_EN 29,33

-PWRBTSW 12,28

Route VDDA25 trace approx.

50 mils wide (use 2x25 mil

traces to exit ball field) and

500 mils long.

-CPURST8

-LDTSTOP8,13

COREFB29

-COREFB29

C46 3.9n/4/X7R/50V

C47 3.9n/4/X7R/50V

VTTDDR

-CPURST

K8PWROK

-LDTSTOP

REF1

REF0

COREFB

-COREFB

VDDIOFB

-VDDIOFB

CLKIN

R12

169/6/1

-CLKINCPUCLK0_L

NC_AJ23

NC_AH23

NC_AE24

NC_AF24

DBRDY

NC_C15

TMS_CPU

TCK_CPU

-TRST_CPU

TDI_CPU

NC_C18

NC_A19

NC_AE23

NC_AF23

NC_AF22

NC_AF21

3

AH25

AJ25

AF20

AE18

AJ27

AF27

AE26

A23

A24

B23

AE12

AF12

AE11

AJ21

AH21

AJ23

AH23

AE24

AF24

C16

AG15

AH17

C15

E20

E17

B21

A21

C18

A19

A28

AJ28

AE23

AF23

AF22

AF21

AA2

AG2

B18

AH1

AE21

C20

AG4

AG6

AE9

AG9

C1

J3

R3

D3

C6

VDDA1

VDDA2

RESET_L

PWROK

LDTSTOP_L

L0_REF1

L0_REF0

COREFB_H

COREFB_L

CORE_SENSE

VDDIOFB_H

VDDIOFB_L

VDDIO_SENSE

CLKIN_H

CLKIN_L

NC_AJ23

NC_AH23

NC_AE24

NC_AF24

VTT_A5

VTT_B5

DBRDY

NC_C15

TMS

TCK

TRST_L

TDI

NC_C18

NC_A19

KEY1

KEY0

NC_AE23

NC_AF23

NC_AF22

NC_AF21

FREE29

FREE31

FREE33

FREE35

FREE1

FREE37

FREE4

FREE38

FREE41

FREE7

FREE11

FREE12

FREE13

FREE14

FREE40

-CPURST

C505

1N/4/X/50V/X

SOCKET_754C

THERMTRIP_L

THERMDA

THERMDC

VID4

VID3

VID2

VID1

VID0

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

G_FBCLKOUT_H

G_FBCLKOUT_L

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

NC_AF18

RSVD_SCL

RSVD_SDA

FREE26

FREE28

FREE30

FREE32

FREE34

FREE36

FREE10

FREE18

FREE19

FREE42

FREE24

FREE25

FREE27

-THRMTRIP

A20

C549 1N/4/X/50V/X

A26

R1142 0/6

A27

C548 0.1U/6/Y/25V/X

VID4

AG13

VID3

AF14

VID2

AG14

VID1

AF15

VID0

AE15

NC_AG18

AG18

NC_AH18CORE_SENSE

AH18

NC_AG17

AG17

NC_AJ18

AJ18

AH19

-FBCLKOUT

AJ19

-DBREQ

AE19

NC_D20

D20

NC_C21

C21

NC_D18

D18

NC_C19

C19

NC_B19

B19

TDO

A22

AF18

D22

C22

B13

B7

C3

K1

R2

AA3

F3

C23

AG7

AE22

C24

A25

C9

FBCLKOUT

2

VID4 29

VID3 29

VID2 29

VID1 29

VID0 29

R13 80.6/6/1

TMPIN3+ 22

TMPIN3- 22

NC_AJ23

TDO

TMS_CPU

TCK_CPU

NC_D18

NC_B19

NC_A19

TDI_CPU

NC_C18

-TRST_CPU

NC_AE23

NC_AF23

NC_AF21

NC_AF22

NC_AJ18

NC_AG17

-DBREQ

DBRDY

NC_C19

NC_D20

NC_C21

NC_AH23

Title

Size Document Number Rev

Custom

Date: Sheet

R1142,C548,C549 MUST NEAR

SOCKET_754

Route FBCLKOUT_H/L differentia lly

with 20/8/5/8/20 spacing and trace

width.

25VSTR

R14 820/6

R15 1K/6

VCC25

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R1067 820/6

RN1

1K/8P4R

RN2

1K/8P4R

RN3

1K/8P4R

RN4

1K/8P4R

RN5

1K/8P4R

VCC25

VCC25

AXPER

K8 SOCKET 754-3

AXPER

635Monday, August 01, 2005

1

of

1.0

5

E4G4J4L4N4U4W4

AA4

AC4

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO7

VDDIO8

D D

SOCKET_754D

VCORE

L28

R28

W28

AC28

AF28

AH28

C29F2H2K2M2P2T2V2Y2

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

C C

VSS1

VSS3

SOCKET_754E

B2

AH20

AB21

VSS4

VSS5

VSS6

VSS7

VSS8

W22

M23

L24

AG25

AG27D2AF2W6Y7

VSS100

VSS101

VSS9

VSS10

VSS102

VSS103

VSS11

VSS12

VSS104

VSS105

VSS13

VSS14

AA8

VSS106

VSS15

AB9

VSS107

VSS16

AA10

AB2

VSS108

VSS17

J12

AD2

VSS109

VSS18

B14

VDDIO9

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

L7

AC15

H18

B20

E21

H22

J23

H24

F26N7L9

AH2B4AH4B6G6J6L6N6R6U6AA6

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

Y15

AE16

J18

G20

R20

U20

W20

AA20

AC20

4

AE4D5AF5F6H6K6M6P6T6V6Y6

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

V10

G13

K14

Y14

AB14

G15

AC6

AH6F7H7K7M7P7T7V7AB7

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

AE20

AG20

AJ20

D21

F21

H21

K21

M21

VDDIO19

VDD18

J15

VSS127

VSS36

P21

VDDIO20

VDD19

AA15

VSS128

VSS37

T21

VDDIO21

VDD20

H16

VSS129

VSS38

V21

AB6

VDDIO22

VDD21

K16

VSS130

VSS39

Y21

AD6D7G7J7AA7

AC7

AF7F8H8

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

Y16

AB16

G17

J17

AA17

AC17

AE17

F18

AD7B8G8J8L8N8R8U8W8

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

AD21

AG21

B22

E22

G22

J22

L22

N22

AB8

AD8D9G9

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDD29

VDD30

VDD31

VDD32

VDD33

K18

Y18

AB18

AD18

AC8

AH8F9H9K9M9P9T9V9Y9

VSS138

VSS139

VSS140

VSS141

VSS142

VSS47

VSS48

VSS49

VSS50

VSS51

R22

U22

AG29

AA22

VDDIO35

VDD34

AG19

VSS143

VSS52

AC22

AC9

VDDIO36

VDD35

E19

VSS144

VSS53

AG22

AF9

VDDIO37

VDD36

G19

VSS145

VSS54

AH22

F10

VDDIO38

VDD39

AC19

VSS146

VSS55

AJ22

AD10

VDDIO39

VDD38

AA19

VSS147

VSS56

D23

D11

VDDIO40

VDD37

J19

VSS148

VSS57

F23

AF11

VDDIO41

VDD40

F20

VSS149

VSS58

H23

F12

VDDIO42

VDD41

H20

AD9

VSS150

VSS59

K23

AD12

VDDIO43

VDD42

K20

B10

VSS151

VSS60

P23

D13

AF13

VDDIO44

VDD43

M20

P20

G10

J10

VSS152

VSS61

T23

V23

F14

VDDIO45

VDDIO46

VDD44

VDD45

T20

L10

VSS153

VSS155

VSS62

VSS63

Y23

AD14

V20

N10

AB23

F16

VDDIO47

VDDIO48

VDD46

VDD47

Y20

R10

VSS156

VSS157

VSS64

VSS65

AD23

AD16

VDDIO49

VDD48

AB20

U10

VSS158

VSS66

AG23

D15R4N28

VDDIO50

VDD49

AD20

G21

W10

AC10

VSS159

VSS67

E24

G24

VCORE25VSTR

VDDIO6

VDD50

VDD51

J21

AH10

VSS160

VSS161

VSS68

VSS69

J24

VDD96

VDD52

L21

F11

VSS162

VSS70

N24

U28

VDD97

VDD53

N21

H11

VSS163

VSS71

R24

AA28

R21

K11

U24

3

AE27R7U7W7K8M8P8T8V8Y8J9N9R9U9W9

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

F22

G12

VSS169

VSS77

AJ24

K22

AA12

VSS170

VSS78

B25

M22

AC12

VSS171

VSS79

C25

P22

AH12

VSS172

VSS80

B26

T22

F13

VSS173

VSS81

D26

V22

H13

VSS174

VSS82

H26

Y22

K13

VSS175

VSS83

M26

VDD66

AB22

Y13

VSS176

VSS84

T26

U21

Y11

VSS164

VSS72

W24

W21

AB11

VSS165

VSS166

VSS73

VSS74

AA24

AA21

AD11

VSS167

VSS75

AC24

AC21

B12

VSS168

VSS76

AG24

VDD111

VDD67

AD22

AB13

VSS177

VSS85

Y26

VDD112

VDD68

E23

AD13

VSS178

VSS86

AD26

VDD113

VDD69

G23

AF17

VSS179

VSS87

AF26

AA9

VDD114

VDD70

L23

G14

VSS180

VSS88

AH26

H10

VDD115

VDD71

N23

J14

VSS181

VSS89

C27

K10

VDD116

VDD72

R23

AA14

VSS182

VSS90

B28

M10

VDD117

VDD73

U23

AC14

VSS183

VSS91

D28

P10

VDD118

VDD74

W23

AE14

VSS184

VSS92

G28

T10

VDD119

VDD75

AA23

D16

VSS185

VSS187

F15

Y10

VDD120

VDD76

AC23

E15

VSS186

VSS188

H15

AB10

VDD121

VDD77

B24

K15

VSS189

VSS206

AB17

G11

VDD122

VDD78

D24

AB15

VSS190

VSS207

AD17

J11

VDD123

VDD79

F24

AD15

VSS191

VSS208

B16

AA11

AC11

VDD124

VDD80

K24

M24

AH14

E16

VSS192

VSS209

G18

AA18

H12

VDD125

VDD126

VDD81

VDD82

P24

G16

VSS194

VSS195

VSS210

VSS211

AC18

K12

VDD127

VDD83

T24

J16

VSS196

VSS212

D19

Y12

AB12

VDD128

VDD84

V24

Y24

AA16

AC16

VSS197

VSS213

F19

H19

J13

VDD129

VDD130

VDD85

VDD86

AB24

AE29

VSS198

VSS199

VSS214

VSS215

K19

AA13

VDD131

VDD87

AD24

AJ26

VSS223

VSS216

Y19

AC13

VDD132

VDD88

AH24

E18

VSS201

VSS217

AB19

H14

VDD133

VDD89

AE25

F17

VSS202

VSS218

AD19

AB26

VDD93

VDD90

K26

H17

VSS203

VSS219

AF19

E28

VDD94

VDD91

P26

K17

VSS204

VSS220

J20

J28

VDD95

VDD92

V26

Y17

VSS205

VSS221

L20

N20

POWER

VSS222

GROUND

2

1

VCORE

C54

0.22U/4/Y/10V

SC20

10U/12/Y5V/10V/X

C72

4.7U/12/X5R/10V/X

SC37

10U/12/Y5V/10V/X

4

C73

4.7U/12/X5R/10V/X

SC38

10U/12/Y5V/10V/X

SC35

0.1U/6/Y5V/25V/X

CPU

背版

C52

0.22U/4/Y/10V

C58

10U/12/Y5V/10V

C70

4.7U/12/X5R/10V/X

C51

0.22U/4/Y/10V

C57

10U/12/Y5V/10V

C69

4.7U/12/X5R/10V

C55

10U/12/Y5V/10V

C529

4.7U/12/X5R/10V/X

5

SC22

0.1U/6/Y5V/25V/X

C56

10U/12/Y5V/10V

C68

4.7U/12/X5R/10V/X

SC34

0.1U/6/Y5V/25V/X

SC21

0.1U/6/Y5V/25V/X

VCORE

B B

VCORE

VCORE

SC33

0.1U/6/Y5V/25V/X

A A

C53

0.22U/4/Y/10V

SC19

10U/12/Y5V/10V/X

C71

4.7U/12/X5R/10V

SC36

0.1U/6/Y5V/25V/X

25VSTR

C59

0.22U/4/Y/10V

25VSTR

SC15

10U/12/Y5V/10V/X

C60

0.22U/4/Y/10V

SC16

10U/12/Y5V/10V/X

3

C61

0.22U/4/Y/10V

SC17

10U/12/Y5V/10V/X

C62

0.22U/4/Y/10V

SC18

10U/12/Y5V/10V/X

10U/12/Y5V/10V

C63

0.22U/4/Y/10V

C350

C64

0.22U/4/Y/10V

C351

10U/12/Y5V/10V

Title

Size Document Number Rev

C

2

Date: Sheet

AXPER

K8 SOCKET 754-4

AXPER

1

1.0

of

735Monday, August 01, 2005

A

L0_CADIN_L[0..15]

L0_CADIN_H[0..15]

L0_CLKIN_L[0..1]

L0_CLKIN_H[0..1]

L0_CADOUT_L[0..15]

L0_CADOUT_H[0..15]

4 4

L0_CLKOUT_L[0..1]

L0_CLKOUT_H[0..1]

L0_CADIN_L[0..15] 4

L0_CADIN_H[0..15] 4

L0_CLKIN_L[0..1] 4

L0_CLKIN_H[0..1] 4

L0_CADOUT_L[0..15] 4

L0_CADOUT_H[0..15] 4

L0_CLKOUT_L[0..1] 4

L0_CLKOUT_H[0..1] 4

D22

B

C

D

E

Modify at 11/8,from VIA ECN()

VCC12

FOR K8M800 ONLY

E22

F22

G22

T22

U22

B23

D23

F23

U23

V23

B24

C24

D24

E24

T24

U24

V24

A25

B25

C25

T25

U25

V25

A26

U26

B26

V22

C23D9E23

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

A24

T23

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

V26

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

U6A

VCC3

FB1 1/6

FB16

0/6/SHT30/X

AVDD2

C79

1N/4/X/50V

C80

1U/6/Y/16V

FB17

0/6/SHT30/X

-CPURST_NB

RN243

680/8P4R

132

R1425 0/6/X

BC2

0.22U/4/Y/10V

SC2

AGND2

AVDD1VCC3

C81

1N/4/X/50V

C82

1U/6/Y/16V

AGND1

VCC25

07/28

1 2

3 4

5 6

7 8

-CPURST

Q168

MMBT2222A/SOT23

SOT23

132

Q169

MMBT2222A/SOT23

SOT23

1/14 modify

BC3

0.22U/4/Y/10V

SC3

0.1U/4/Y/16V/B/X

AXPER

VIA K8T800-LDT LINK

AXPER

E

-CPURST 6

BC4

0.22U/4/Y/10V

SC4

0.1U/4/Y/16V/B/X

835Monday, August 01, 2005

of

1.0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

3 3

L0_CTLOUT_H04

L0_CTLOUT_L04

2 2

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H0

L0_CTLOUT_L0

RPCOMP

RNCOMP

RTCOMP

AVDD1

G24

RCADP15

G23

RCADN15

J22

RCADP14

H22

RCADN14

J24

RCADP13

J23

RCADN13

L22

RCADP12

K22

RCADN12

N22

RCADP11

M22

RCADN11

N24

RCADP10

N23

RCADN10

R22

RCADP9

P22

RCADN9

R24

RCADP8

R23

RCADN8

H26

RCADP7

G26

RCADN7

H24

RCADP6

H25

RCADN6

K26

RCADP5

J26

RCADN5

K24

RCADP4

K25

RCADN4

M24

RCADP3

M25

RCADN3

P26

RCADP2

N26

RCADN2

P24

RCADP1

P25

RCADN1

T26

RCADP0

R26

RCADN0

L24

RCLKP1

L23

RCLKN1

M26

RCLKP0

L26

RCLKN0

F24

RCTLP

F25

RCTLN

D25

RPCOMP

D26

RNCOMP

C26

RTCOMP

E25

AVDD1

E26 C22

AGND1 AVDD2

AGND1

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

B9C9E9

VLDT

D10

E10

F10

A10

J10

C10

B10

B

VLDT

N.B HEATSINK

NB_HEATSINK

VCC12

NB FAN

1 1

NB_FAN

NB_HEATSINK

A

H1X2/NB_FAN/X

A9

+12V

C11

D11

VLDT

E11

F11

J11

J13

J14

F15

J15

J12

VLDT

F16

J16

J17

J18

K18

M18

L18

N18

VLDT

P18

R18

T18

U18

F19

Follow VIA ECN 8/29

VLDT

F20

E21

F21

G21

H21

K21

TCADP15

TCADN15

TCADP14

TCADN14

TCADP13

TCADN13

TCADP12

TCADN12

TCADP11

TCADN11

TCADP10

TCADN10

TCADP9

TCADN9

TCADP8

TCADN8

TCADP7

TCADN7

TCADP6

TCADN6

TCADP5

TCADN5

TCADP4

TCADN4

TCADP3

TCADN3

TCADP2

TCADN2

TCADP1

TCADN1

TCADP0

TCADN0

TCLKP1

TCLKN1

TCLKP0

TCLKN0

TCTLP

TCTLN

LDTRST

LDTSTOP

AGND

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

L21

N21

P21

T21

U21

V21

C

D21

D19

C19

E18

E19

D17

C17

D15

C15

E14

E15

D13

C13

E12

E13

B20

C20

A19

A20

B18

C18

A17

A18

A15

A16

B14

C14

A13

A14

B12

C12

E16

E17

B16

C16

A21

A22

B11

A12

C21

AGND2

K8M800/CE/A0

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H0

L0_CTLIN_L0

-CPURST_NB

-LDTSTOP

AVDD2

RNCOMP

RTCOMP

RPCOMP

-LDTSTOP

L0_CTLIN_H0 4

L0_CTLIN_L0 4

-LDTSTOP 6,13

R1068

100/6/X

HT_RST

1

2

JP1X2/X

R24 49.9/6/1

R25 100/6/1

R26 49.9/6/1

R514 1K/6

VCC12

VCC25

FB2 1/6

K8M800/K8T800 HT Interface

-CPURST_NB -CPURST

VCC12

BC1

0.22U/4/Y/10V

VCC12

SC1

0.1U/4/Y/16V/B/X

D

0.1U/4/Y/16V/B/X

Title

Size Document Number Rev

Custom

Date: Sheet

L0_CADIN_H15

E20

A

GAD[0..31]

SBA[0..7]

-GCBE[0..3]

VAD[0..7]

4 4

3 3

2 2

1 1

GVREF_GC18

GAD[0..31] 18

SBA[0..7] 18

-GCBE[0..3] 18

VAD[0..7] 13

AD_STB018

-AD_STB018

AD_STB118

-AD_STB118

SB_STB18

-SB_STB18

ADBIH18

ADBIL18

-GFRAME18

-GIRDY18

-GTRDY18

-GDEVSEL18

-GSTOP18

GPAR18

-GSERR18

-AGP8XDET18

NBGCLK14

GVREF_GC

C85

0.1U/4/Y/16V

A

VDDQ

T2U2V2W2T3U3V3W3Y3T4U4V4W4Y4AA4T5U5Y5AA5

U1

VCC1

VCC1

VCC1

VCC1

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

-GCBE0

-GCBE1

-GCBE2

-GCBE3

AD_STB0

-AD_STB0

AD_STB1

-AD_STB1

SB_STB

-SB_STB

ADBIH

ADBIL

-GFRAME

-GIRDY

-GTRDY

-GDEVSEL

-GSTOP

GPAR

-RBF18

-WBF18

-GREQ18

-GGNT18

-RBF

-WBF

-GREQ

-GGNT

-GSERR

ST0

ST018

ST1

ST118

ST2

ST218

-AGP8XDET

NBGCLK

GPCOMP

GNCOMP

VSUSNB

C86

100K/4

DEBUG

VCCQQ

AF18

GD0/DVOBHSYNC

AD18

GD1/DVOBVSYNC

AE18

GD2/DVOBD1

AF17

GD3/DVOBD0

AD17

GD4/DVOBD3

AD16

GD5/DVOBD2

AE16

GD6/DVOBD5

AF16

GD7/DVOBD4

AF14

GD8/DVOBD6

AD14

GD9/DVOBD9

AD13

GD10/DVOBD8

AE13

GD11/DVOBD11

AF13

GD12/DVOBD10

AD12

GD13/DVOBCCLKINT

AF12

GD14/DVOBFLDSTL

AE12

GD15/MDDC_DATA

AD10

GD16/DVOCVSYNC

AE10

GD17/DVOCHSYNC

AF10

GD18/DVOCBLANK

AD9

GD19/DVOCD0

AF9

GD20/DVOCD1

AF8

GD21/DVOCD2

AE9

GD22/DVOCD3

AD8

GD23/DVOCD4

AF6

GD24/DVOCD7

AD7

GD25/DVOCD6

AE6

GD26/DVOCD9

AD5

GD27/DVOCD8

AF5

GD28/DVOCD11

AF4

GD29/DVOCD10

AE4

GD30/DVOBCINTR

AD4

GD31/DVOCFLDSTL

AC2

SBA0/ADDID0

AC3

SBA1/ADDID1

AD1

SBA2/ADDID2

AD2

SBA3/ADDID3

AF2

SBA4/ADDID4

AD3

SBA5/ADDID5

AE3

SBA6/ADDID6

AF3

SBA7/ADDID7

AD15

C/BE0/DVOBD7

AF11

C/BE1/DVOBBLANK

AD11

C/BE2

AC7

C/BE3/DVOCD5

AE15

AD_STBF0/DVOBCLK

AF15

AD_STBS0/DVOBCLK

AE7

AD_STBF1/DVOCCLK

AF7

AD_STBS1/DVOCCLK

AF1

SB_STBF

AE1

SB_STBS

AC5

DBIH

AC4

DBIL

AC9

GFRAME/MDVI_DATA

AC10

GIRDY/MI2CCLK

AC14

GTRDY/MDVI_CLK

AC11

GDEVSEL/MI2CDATA

AC12

GSTOP/MDDC_CLK

AC16

GPAR

AD6

RBF

AC1

WBF

Y1

GREQ

AA3

GGNT

AC15

GSERR

AA2

ST0

AA1

ST1

AB1

ST2

Y2

AG8XDET

A11

GCLK

V1

AGPPCOMP/DVOBCRCOMP

W1

AGPNCOMP

AC13

AGPVREF0

AC6

AGPVREF1

AC25

VSUS25

AC17

DEBUG

B

VDDQ

AB7

AB8M8N8T8U8V8T9U9V9W9V10

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VSSQQ

NC/VCC3

NC/VCC3

NC/VCC3

NC/VCC3

NC/VCC3

NC/VCC3

NC/VCC3

NC/VCC3

NC/VCC3

NC/VCC3

NC/VCC3

NC/VCC3

NC/VCC3

NC/VCC3

NC/VCC3

NC/VCC3

NC/VCC3

T1

E1F1E2F2G2E3F3G3H3F5G5H5J5K5L5M5N5F6K8J9K9L9M9N9P9

B

VCC1

NC/VCC3

VCC1

NC/VCC3

C

VDD

V11

AB11

V12

AB12

V13

AB13

AB14

V14

V15

W15

V16

W16

V17

W17

AB17

W18

AB18

AC18

AB19

AC19

AB20

AC20

AC21

U6B

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

NC/VCC3

NC/VCC3

NC/VCC3

NC/VCC3

L8

NC/VCC3

NC/VCC3

NC/VCC3

NC/VCC3

R9

NC/VCC3

NC/VCC3

NC/VCC3

D1

J4E4F4G4H4

NC/VCC3

NC/VCC3

NC/VCC3

VCC3

C

VCC2

VCC2

VCC2

VD0

VD1

VD2

VD3

VD4

VD5

VD6

VD7

LCOMPP

VPAR

VBE

DNSTB

DNSTB

UPSTB

UPSTB

UPCMD

DNCMD

LVREF

NC/AR

NC/AG

NC/AB

NC/HSYNC

NC/VSYNC

NC/SPD2

NC/SPCLK2

NC/RSET

NC/INTA

NC/DVID0/TVD0

NC/DVID1/TVD1

NC/DVID2/TVD2

NC/DVID3/TVD3

NC/DVID4/TVD4

NC/DVID5/TVD5

NC/DVID6/TVD6

NC/DVID7/TVD7

NC/DVID8/TVD8

NC/DVID9/TVD9

NC/DVID10/TVD10

NC/DVID11/TVD11

NC/DVIDE/TVBL

NC/DVIVS/TVVS

NC/DVIHS/TVHS

NC/DVICLK/TVCLK

NC/DVIDET/TVCKI

NC/SPD1

NC/SPCLK1

NC/GOP0

NC/GPOUT

NC/DACVDD

NC/GNDDAC1

NC/GNDDAC2

NC/VCCRGB

NC/GNDRGB

NC/VCCPLL1

NC/GNDPLL1

NC/VCCPLL2

NC/GNDPLL2

NC/VCCPLL3

NC/GNDPLL3

NC/VCCD1

NC/VCCD2

NC/VSSD1

NC/VSSD3

NC/BISTIN

NC/XIN

PCIRST

PWRGD

SUSST

TESTIN

VCC2

AD20

AD21

AF24

AE24

AE19

AF20

AD24

AF25

AD19

AF19

AE21

AF22

AD22

AE23

AF23

AF26

AD23

AF21

B3

A3

A2

A1

B1

C1

C2

C4

E7

J1

K2

K3

L4

K1

L2

L3

M4

L1

M2

M3

M1

N1

N3

N4

P3

P4

P1

P2

N2

D2

B2

C3

D4

A4

B4

D5

C5

A5

B5

A6

B6

A7

D7

B7

C7

D3

C6

AD25

AE26

AD26

AC26

K8M800/CE/A0

VAD0

VAD1

VAD2

VAD3

VAD4

VAD5

VAD6

VAD7

LCOMPP

VPAR

-VBE

VDNSTB

-VDNSTB

VUPSTB

-VUPSTB

VUPCMD

VDNCMD

LVREF_NB

R1000 4.7/6

R1001 4.7/6

R1002 4.7/6

VGAHSYNC

VGAVSYNC

SPD2

SPCLK2

RSET

-PIRQA

R1723 8.2K/6

R1724 8.2K/6

VIA Recommend

+3.3VRGBVDD

GND_RGB

TP99

TP100

BISTIN

GUICLK

-NBRST

-NBPWROK

-SUS_ST

TESTIN

VDNSTB 13

-VDNSTB 13

VUPSTB 13

-VUPSTB 13

VUPCMD 13

VDNCMD 13

VGAHSYNC 20

VGAVSYNC 20

SPD2 20

SPCLK2 20

-PIRQA 11,18,19

+3.3VDACVDD

+1.5VRGBPLL1

GND_RGBPLL1

+1.5VRGBPLL2

GND_RGBPLL2

GUICLK 14

-NBRST 11

-NBPWROK 11

-SUS_ST 12

D

C508

1N/4/X/50V

VPAR 13

-VBE 13

Only for K8M800

AR

AR 20

AG

AG 20

AB

AB 20

TP87

GND_DAC

Reserved pins for test

D

-NBRST-NBPWROK

R468

22/6

C317

33P/4/N/50V

VCC25

BC5

0.1U/4/Y/16V

VDDQ

BC9

0.1U/4/Y/16V

VCC3

BC357

0.1U/4/Y/16V

VCC25 VDDQ

0.1U/4/Y/16V/B/X

SC5

0.1U/4/Y/16V/B/X

Only for K8M800

Title

Size Document Number Rev

Custom

Date: Sheet

E

VCC25

R29

3K/6/1

LVREF_NB

R30

1K/6/1

BC6

0.1U/4/Y/16V

BC10

0.1U/4/Y/16V

BC358

0.1U/4/Y/16V

SC6

AR

AG

AB

BC7

0.1U/4/Y/16V/X

BC11

0.1U/4/Y/16V/X

BC359

0.1U/4/Y/16V/X

SC7

0.1U/4/Y/16V/B/X

C712 10P/4/N/50V/X

C713 10P/4/N/50V/X

C714 10P/4/N/50V/X

For EMI

TESTIN

VPAR

GNCOMP

GPCOMP

BISTIN

RSET

LCOMPP

DEBUG

R31 8.2K/6

R32 8.2K/6/X

R34 60.4/6/1

R35 60.4/6/1

R1420 1K/6

R1004 90.9/6/1

R1003 360/6/1

R1005 8.2K/6/X

R1006 8.2K/6

AXPER

VIA K8T800-AGP/VLINK

AXPER

E

C83

0.1U/4/Y/16V

C84

0.1U/4/Y/16V

BC8

0.1U/4/Y/16V/X

BC12

0.1U/4/Y/16V/X

BC360

0.1U/4/Y/16V/X

SC8

0.1U/4/Y/16V/B/X

VCC25

VDDQ

VCC25

935Monday, August 01, 2005

of

1.0

A

B

C

D

E

Modify at 11/8,from VIA ECN

For K8T800 VDD=2.5V

VDD

4 4

G1

H1

R1

H2

J2

R2

AB2

AE2

J3

R3

AB3

K4

R4

AB4

E5

P5

R5

V5

W5

AB5

AE5

D6

E6

AB6

3 3

2 2

1 1

F7

A8

B8

C8

D8

E8

F8

AC8

AE8

AB9

K10

L10

M10

N10

P10

R10

T10

U10

AB10

K11

L11

M11

N11

P11

R11

T11

U11

AE11

D12

F12

K12

L12

M12

N12

P12

R12

T12

U12

B13

F13

K13

L13

M13

N13

P13

R13

T13

U13

D14 F14

H8J8P8R8H9F9H10

VSS

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS VSS

VDD

H11

W10

W11

H12

W12

W13

W14

H15

H16

V18

K19

L19

M19

R19

T19

U19

V19

W19

Y20

Y21

AA21

Y22

AA22

AB22

Y23

AA23

AB23

Y24

AA24

AB24

Y25

AA25

AB25

Y26

AA26

AB21

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDVDD

VDD

AB26

VDD

VDD

VSS

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U6C

F26

W26

AE25

W25

R25

N25

L25

J25

G25

AC24

W24

AC23

W23

P23

M23

K23

H23

A23

AE22

AC22

W22

B22

W21

R21

M21

J21

B21

AE20

D20

B19

F18

D18

AE17

U17

T17

R17

P17

N17

M17

L17

K17

F17

B17

AB16

U16

T16

R16

P16

N16

M16

L16

K16

D16

AB15

U15

T15

R15

P15

N15

M15

L15

K15

B15

AE14

U14

T14

R14

P14

N14

M14

L14

K14

K8M800/CE/A0

VDD VCC25

RN199

1 2

3 4

5 6

7 8

0/8P4R/X

VDD VCC25

VDD VCC25

RN208

1 2

3 4

5 6

7 8

0/8P4R/X

SC39 0.1U/6/Y/25V/X

VDD

SC40 0.1U/6/Y/25V/X

VDD

SC41 0.1U/6/Y/25V/X

VDD

SC42 0.1U/6/Y/25V/X

VDD

北橋背版電容

SC43 0.1U/6/Y/25V/X

VCC12

SC44 0.1U/6/Y/25V/X

VCC12

SC45 0.1U/6/Y/25V/X

VCC12

SC46 0.1U/6/Y/25V/X

VCC12

SC47 0.1U/6/Y/25V/X

VCC12

SC48 0.1U/6/Y/25V/X

VCC12

K8M800 R1119=499

VSUSNB=1.5V

K8T800 R1119=100

VSUSNB=2.5V

VDD

+

EC80

100U/D/10V/57

Only for K8M800

FB18

1/6

FB19

0/6/SHT30/X

+1.5VRGBPLL1VDD

C560

1N/4/X/50V

C561

1U/6/Y/16V

GND_RGBPLL1

FB25

1/6

FB20

0/6/SHT30/X

+3.3VDACVDDVCC3

C562

1N/4/X/50V

C563

1U/6/Y/16V

GND_DAC

For K8M800 VDD=1.5V

VDD VDD

RN244

1 2

3 4

5 6

7 8

0/8P4R/X

Chipset內部VDDQ與VDD為Short

VSUSNB

3VDUAL

R1116 75/6

R1117 75/6

SOT23

APL431L/SOT23/150mA

1

+

EC33

1000U/D/6.3V/8C/[11CL1-8C1001-13_11CL1-8C1001-14_11CL1-8C1001-15_11CL1-8C1001-11]/X

Q128

CAR

R1118

100/6/1

RAC

R1119

499/6/1

VDD

VCC3

VDDQ VDDQ

BC367

0.1U/4/Y/16V

BC366

0.1U/4/Y/16V

FB21

1/6

FB22

0/6/SHT30/X

FB23

1/6

FB24

0/6/SHT30/X

RN245

1 2

3 4

5 6

7 8

0/8P4R/X

+1.5VRGBPLL2

GND_RGBPLL2

+3.3VRGBVDD

GND_RGB

。

C200

1U/6/Y/16V/X

4/6

C564

1N/4/X/50V

C566

1N/4/X/50V

VDD

RN246

1 2

3 4

5 6

7 8

0/8P4R

C201

1U/6/Y/16V

C565

1U/6/Y/16V

C567

1U/6/Y/16V

VDDQ

Co-Lay

A

BC13

0.1U/4/Y/16V

BC14

0.1U/4/Y/16V

BC15

0.1U/4/Y/16V

BC16

0.1U/4/Y/16V

BC17

0.1U/4/Y/16V/X

B

BC18

0.1U/4/Y/16V/X

BC19

0.1U/4/Y/16V/X

BC20

0.1U/4/Y/16V/X

C

Title

Size Document Number Rev

Custom

D

Date: Sheet

AXPER

VIA K8T800-PWR/GND

AXPER

10 35Monday, August 01, 2005

E

of

1.0

5

4

3

2

1

AD[0..31]

D D

C C

B B

O[DDR26V

O[DDR27V

SMBUS SMI#

PWRLED Disable

A A

GPI9

GPO9

OVDDR26V

OVDDR27V

GPIO14

OFF_PD

AD[0..31] 19

-PCIRST22

C577

22P/4/N/50V/X

R1367 8.2K/6

R1368 8.2K/6

1 2

3 4

5 6

7 8

RN239

8.2K/8P4R

5

VCC3

VCC3

H9

H10

H12J8K8L8M8N8P8R8R19

GND

GND

E8

GND

F25

GND

VCC33

GND

H23

J21

4

H11

VCC33

VCC33

VCC33

GND

GND

J25B2A17

A13

VCC33

USBGND

A15

VCC33

USBGND

AD0

G2

-IRDY

C578

AD0

J4

AD1

J3

AD2

H3

AD3

F1

AD4

G1

AD5

H4

AD6

F2

AD7

E1

AD8

G3

AD9

E3

AD10

D1

AD11

G4

AD12

D2

AD13

D3

AD14

F3

AD15

K3

AD16

L3

AD17

K2

AD18

K1

AD19

M4

AD20

L2

AD21

N4

AD22

L1

AD23

M2

AD24

M1

AD25

P4

AD26

N3

AD27

N2

AD28

N1

AD29

P1

AD30

P2

AD31

E2

CBE0

C1

CBE1

L4

CBE2

M3

CBE3

J1

FRAME

H2

DEVSEL

J2

IRDY

H1

TRDY

K4

STOP

C2

SERR

F4

PAR

C3

PERR

R1

PCIRST

A4

INTA

B4

INTB

B5

INTC

C4

INTD

D4

INTE

E4

INTF

A3

INTG

B3

INTH

A5

REQ0

B6

REQ1

C5

REQ2

D5

REQ3

P3

REQ4

R3

REQ5

A6

GNT0

D6

GNT1

C6

GNT2

E5

GNT3

R4

GNT4

R2

GNT5

GND

GND

A1A2B1

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

-SERR19

PAR19

-PERR19

-CBE0

-CBE1

-CBE2

-CBE3

-FRAME

-DEVSEL

-IRDY

-TRDY

-STOP

-SERR

PAR

-PERR

-PCIRST

-PIRQA

-PIRQB

-PIRQC

-PIRQD

OVDDR26V

OVDDR27V

GPIO14

OFF_PD

-PREQ0

-PREQ1

-PREQ2

-PREQ3

-PREQ4

-PREQ5

-PGNT0

-PGNT1

-PGNT2

-PGNT3

-PGNT4

-PGNT5

15P/6/N/50V/X

-CBE019

-CBE119

-CBE219

-CBE319

-FRAME19

-DEVSEL19

-IRDY19

-TRDY19

-STOP19

-PIRQA9,18,19

-PIRQB18,19

-PIRQC19

-PIRQD19

OVDDR26V32

OVDDR27V32

OFF_PD28

-PREQ019

-PREQ119

-PREQ219

-PREQ319

-PREQ419

-PREQ519

-PGNT019

-PGNT119

-PGNT219

-PGNT319

-PGNT419

-PGNT519

VCC33

USBGND

A19

VCC33

USBGND

A21

VCC33

USBGND

B13

VCC33

USBGND

VCC33

USBGND

B15

B17

T8

VCC33

USBGND

B19

T19

VCC33

USBGND

B21

VCC33

USBGND

U8

VCC33

USBGND

C13

U19V8V19

VCC33

USBGND

C14

VCC33

USBGND

C15

V21W9W10

VCC33

USBGND

C16

C17

VCC33

USBGND

C18

VCC33

USBGND

C19

W11

VCC33

USBGND

C20

W17

VCC33

USBGND

C21

W18

VCC33

USBGND

D13

W19

VCC33

USBGND

D15

W21

VCC33

USBGND

D17

Y21

VCC33

USBGND

D19

W8

VCC33

USBGND

D21

VCC33

USBGND

E13

U42A

A22

USBVDD

B22

USBVDD

C22

USBVDD

D22

USBVDD

E22

USBVDD

F22

USBVDD

J13

USBVDD

J14

USBVDD

J15

USBVDD

J16

USBVDD

J17

USBVDD

J18

USBVDD

C24

USBSUS25

A23

PLLVDDA

B23

PLLVDDA

D23

PLLGNDA

C23

PLLGNDA

E20

USBP0+

D20

USBP0-

A20

USBP1+

B20

USBP1-

E18

USBP2+

D18

USBP2-

A18

USBP3+

B18

USBP3-

D16

USBP4+

E16

USBP4-

A16

USBP5+

B16

USBP5-

D14

USBP6+

E14

USBP6-

A14

USBP7+

B14

USBP7-

C26

USBOC0

D24

USBOC1

B26

USBOC2

C25

USBOC3

B24

USBOC4

A24

USBOC5

A26

USBOC6

A25

USBOC7

E23

USBCLK

B25

USB REXT

D26

UDPWR

D25

UDPWREN

H14

W3

V1

W1

W2

USBGND

USBGND

USBGND

USBGND

USBGND

VT8237

H15

H16

H18

H17

KBCK/KA20G

KBDT/KBRC

MSCK/IRQ1

MSDT/IRQ12

USBGND

USBGND

USBGND

USBGND

USBGND

USBGND

E15

E17

E19

E21

H13

3

SUS_25V

USB0

-USB0

USB1

-USB1

USB2

-USB2

USB3

-USB3

USB4

-USB4

USB5

-USB5

USB6

-USB6

USB7

-USB7

-USBOC

USBCLK

GPI9

GPO9

KBCK

KBDT

MSCK

MSDT

PWROK

Z20

3VDUAL

R1144

0/8/SHT30/X

BC368

0.1U/6/Y/25V

USB0 27

-USB0 27

USB1 27

-USB1 27

USB2 21

-USB2 21

USB3 21

-USB3 21

USB4 21

-USB4 21

USB5 21

-USB5 21

USB6 21

-USB6 21

USB7 21

-USB7 21

-USBOC 21,27

USBCLK 14

R1148 6.04K/6/1

R1149 1K/6/X

KBCK 26

KBDT 26

MSCK 26

MSDT 26

1 2

3 4

5 6

7 8

RN258 33/8P4R

VCC25

BC369

0.1U/6/Y/25V

7414_VCC

BC370

0.1U/6/Y/25V

IDERST12

CPU_PWROK 6

-NBPWROK 9

SBPWROK 12,13

2

VCC3

-PCIRST

IDERST

VCC3

BC364

0.1U/6/Y/25V

IDERST

R1145

0/6/SHE30/X

141312111098

I5O5I4O4I3

VCC

I0O0I1O1I2O2GND

1234567

R1150

8.2K/6

Title

Size Document Number Rev

Custom

Date: Sheet

SUS_25V

BC363

0.1U/6/Y/25V

BC365

0.1U/6/Y/25V

R1151 1K/6

Q135

MMBT2222A/SOT23

SOT23

132

R1146 100/6/X

BC405

0.1U/6/Y/25V

PWROK

O3

U43

74HC14/SO14

R1366

1/6

R1143

220/6

-NBRST 9

VCC

-IDERST 21

AXPER

VIA VT8237-PCI/USB/PS2 1/3

AXPER

3VDUAL

D41

1N4001/S

BC404

0.1U/6/Y/25V

VCC12_OK 28,33

ATXPWROK 16,31,32,33

-AGPRST 18

-PPCIRST 19

11 35Monday, August 01, 2005

1

of

1.0

Loading...

Loading...