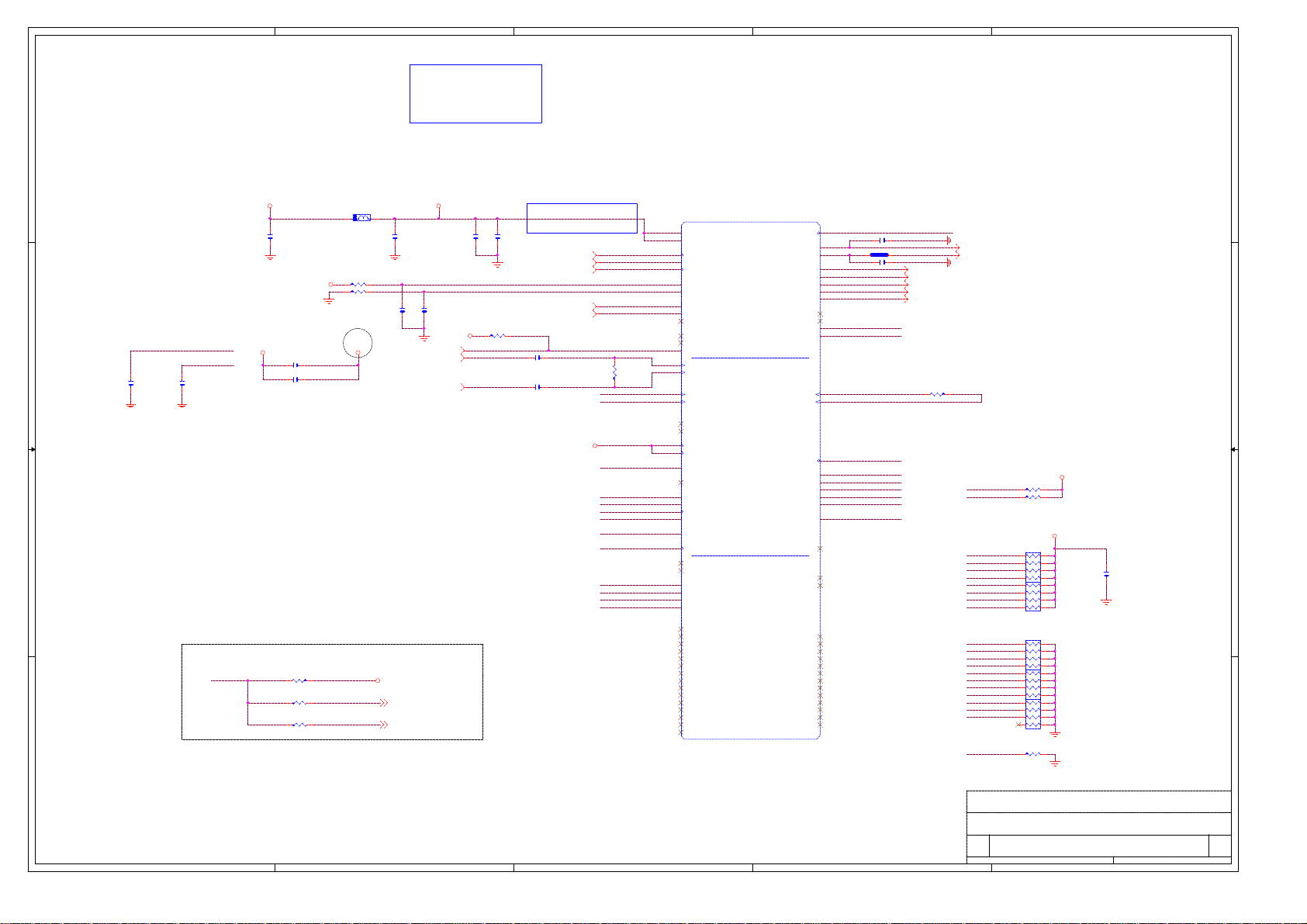

Gigabyte XP-M8S761GX_10A_1019-1 Schematics

5

4

XP-M8S761GX Schematics

3

2

1

Revision 1.0

Date:2005-10-19-1

D D

C C

B B

SHEET

1

2

3

4,5,6,7

8-11

12-15

16

17

18

19

20

21

22

23

24

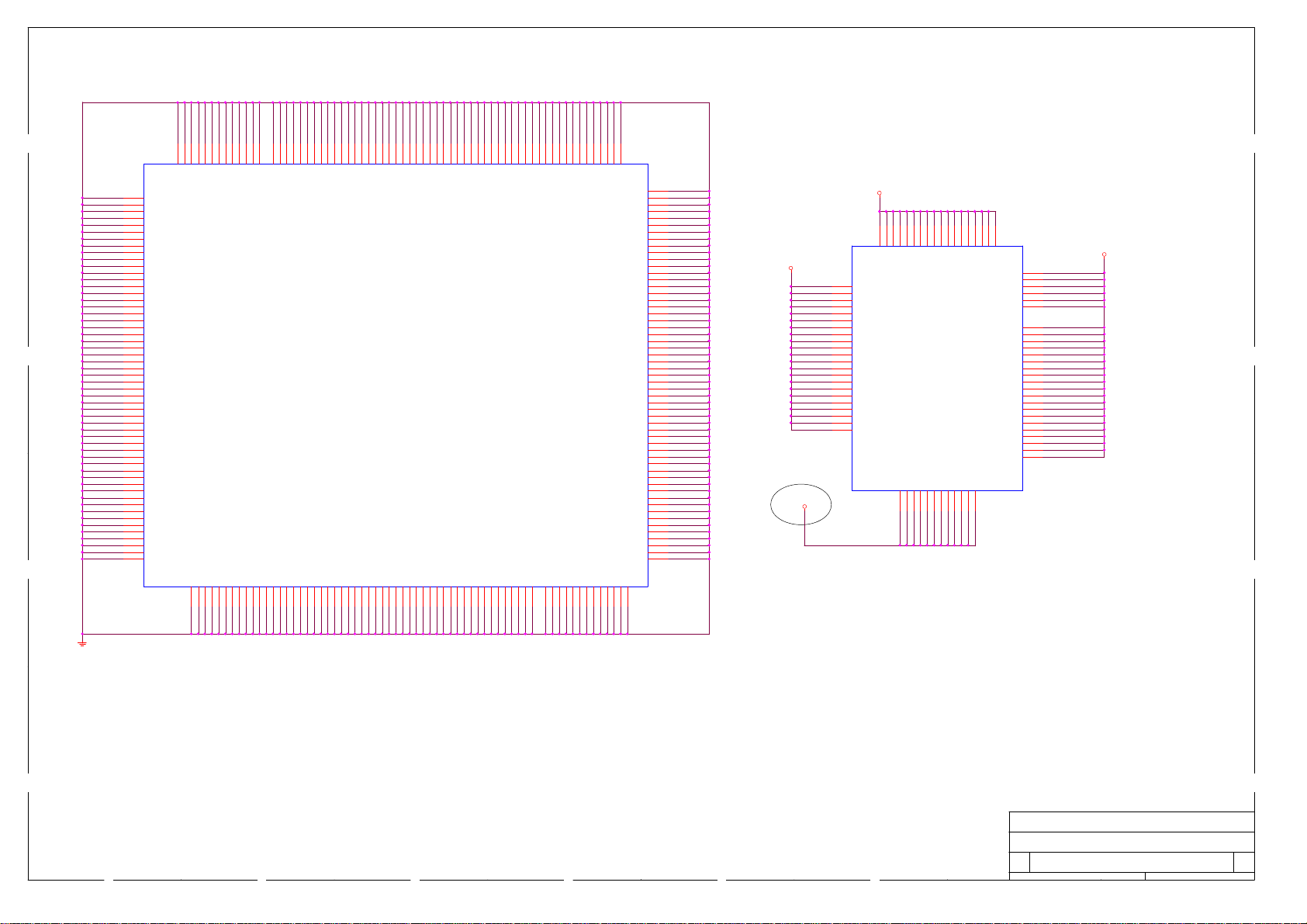

COVER SHEET

BOM & PCB MODIFY HISTORY

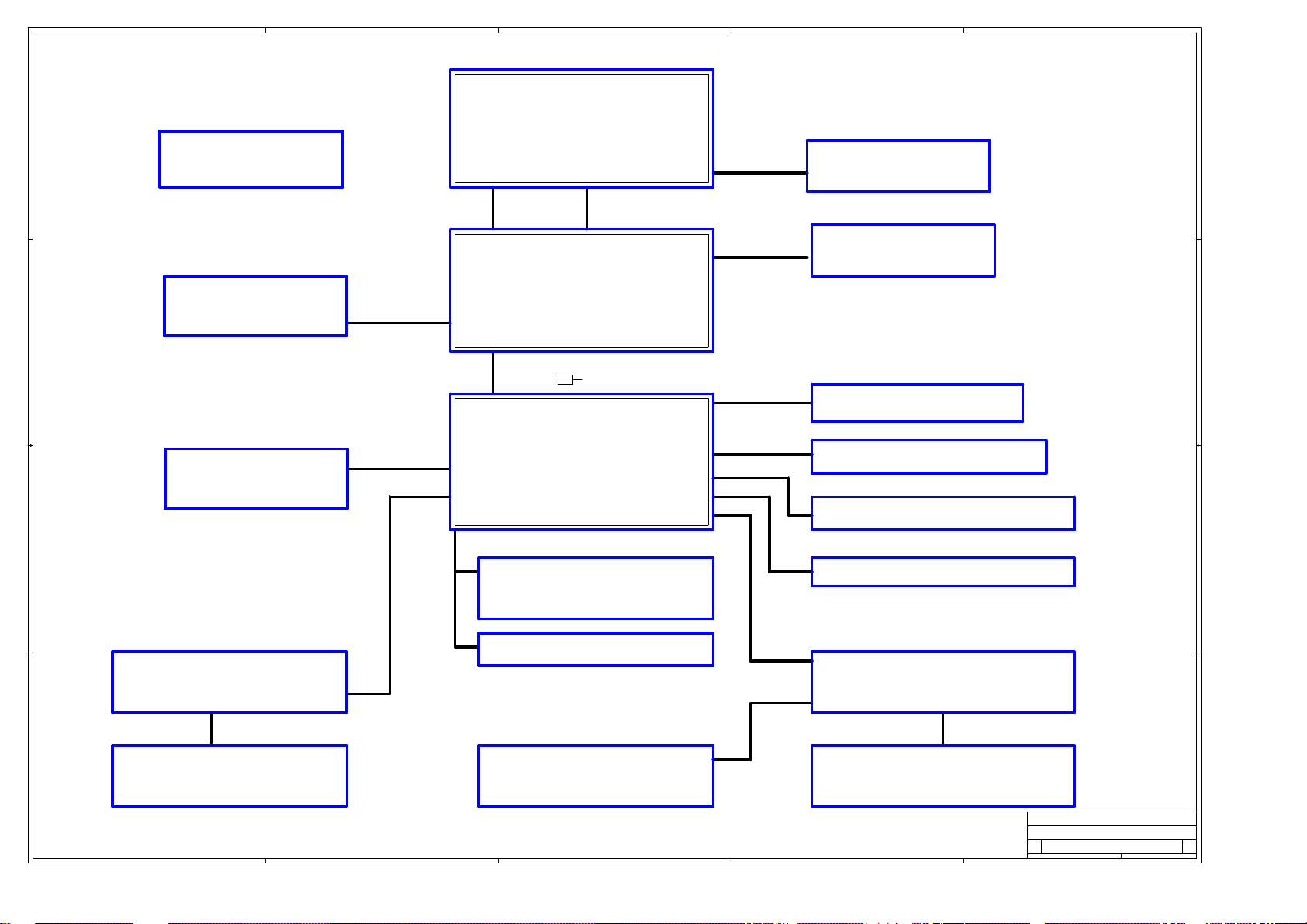

BLOCK DIAGRAM

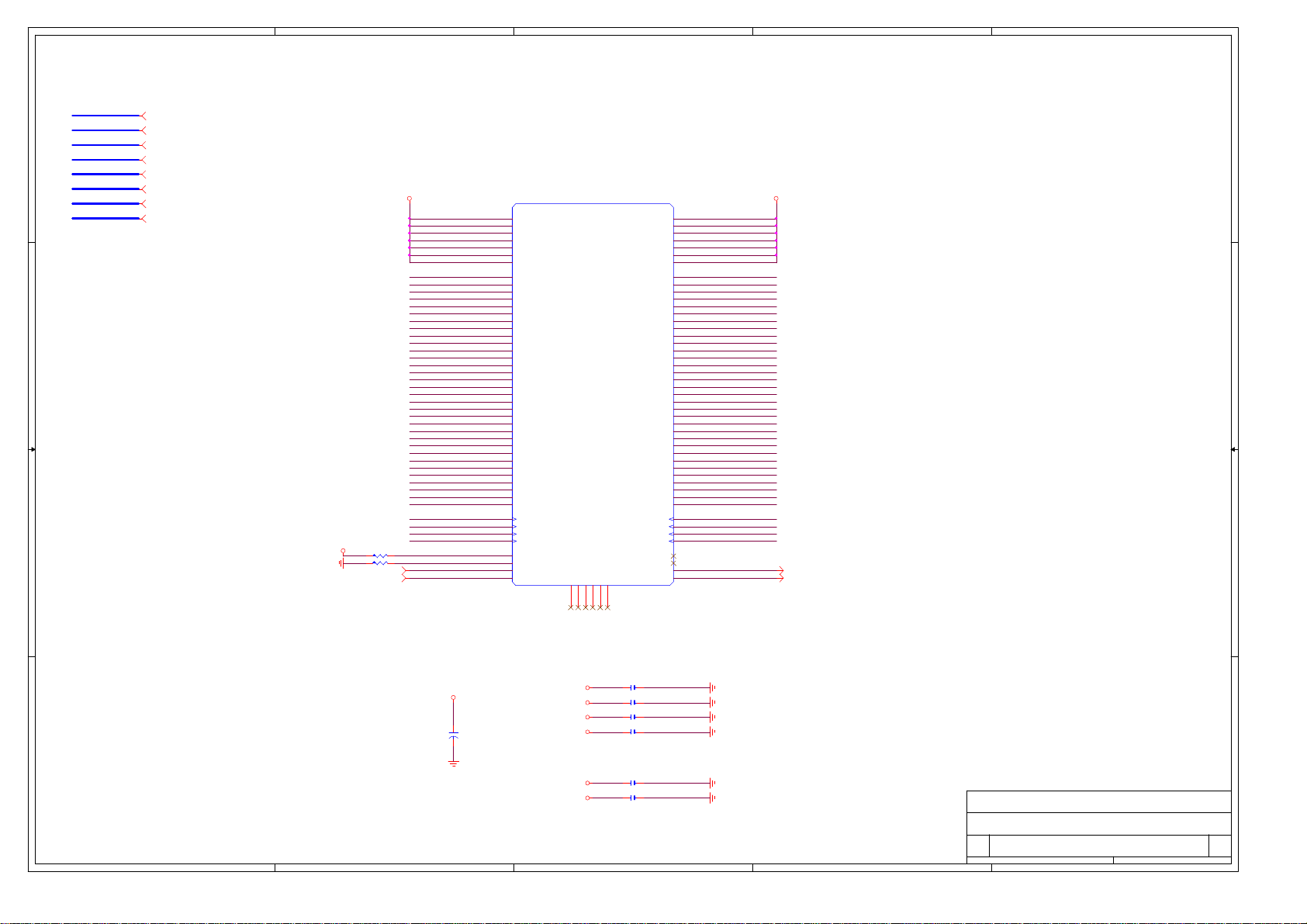

AMD K8 CPU

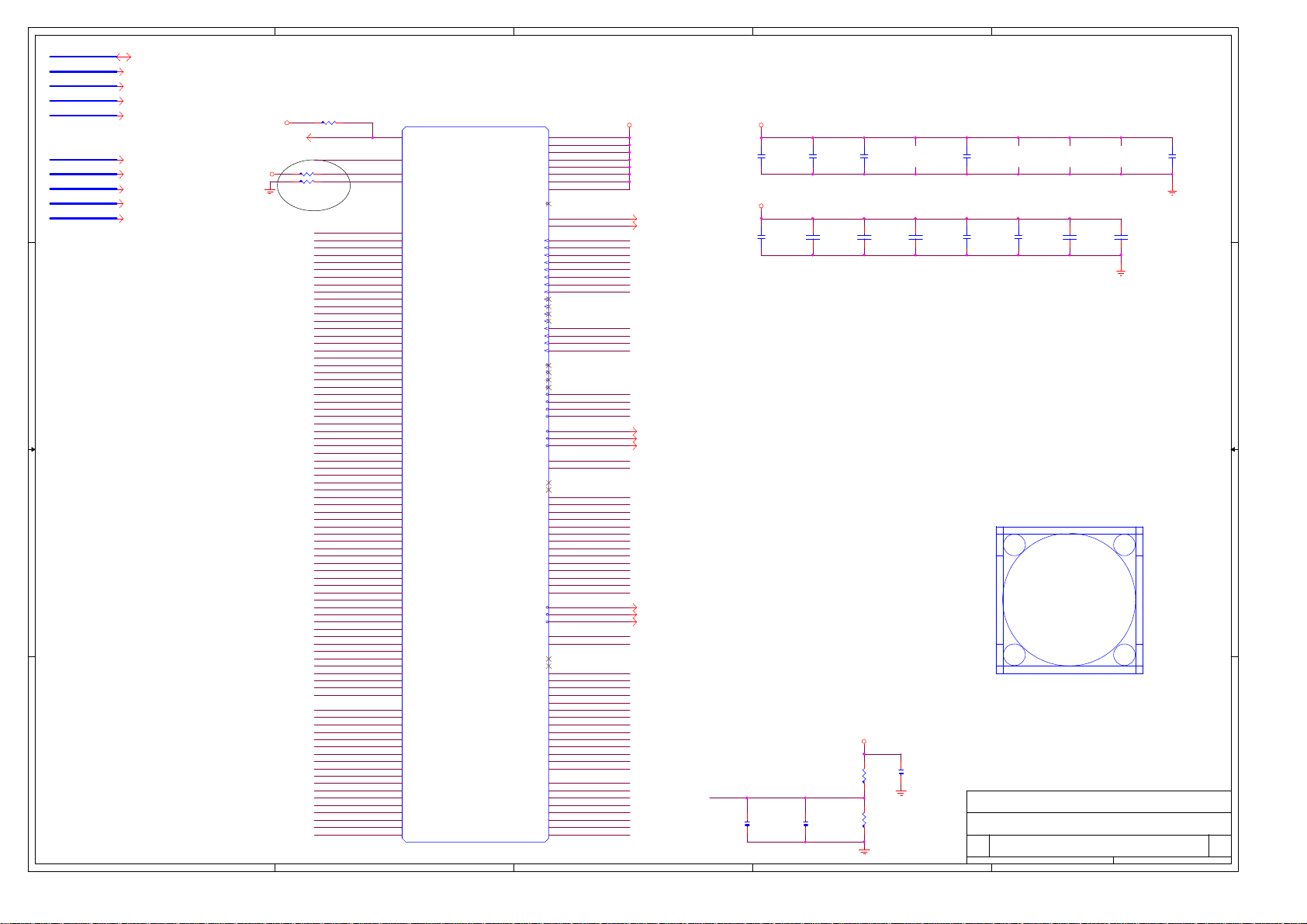

SIS760FX (NORTH BRIDGE) HOST; DDR; AGP,HYPER ZIP

SIS964 (SOUTH BIRDGE)

CLOCK GENERATOR

DDR SDRAMS 1, 2

DDR DAmping & Termination

Local Frame Buffer

Video Connector

AGP 8X SLOT

PCI SLOT 1,2,3

IDE,FRONT USB,PCIRST#

VCORE 3-PHASE PWM POWER

TITLE

SHEET

32

33

34

35

36

37

TITLE

W83301GR DDR POWER

F_PANEL

TI TSB43AB23 1394 (3 PORT)

RTL8100C/8110S 10/100/1G LAN

ATX CONN

K8 Power Sequence

25

26

27

28

29

30

A A

31

LPCIO_IT8705, GAME PORT

BIOS

COM, LPT, FDD, KB/MS

AC 97 ALC650/655/658

AUDIO JACK

VDDQ,VCC18,3VDUAL, 18VDUAL DC POWER

FAN, IR, INFO_LINK

5

4

PCB Vendor:

PCB Size: 243.84*243.84 mm

Title

Size Document Number Rev

Custom

3

2

Date: Sheet of

祥裕,育富

AXPER

COVER SHEET

XP-M8S761GX

1

COMPONENT SIDE

(1 oz. Copper)

VCC LAYER

(1 oz. Copper)

GND LAYER

(1 oz. Copper)

SOLDER SIDE

(1 oz. Copper)

1 34Wednesday, October 19, 2005

1.0

5

4

3

2

1

Model Name: XP-M8S761GX

Version:1.0

Circuit or PCB layout change for next version

Date Change Item Reason

D D

Component value change history

AUTOBOM

94/07/25

Date Change Item Reason

07/27/2005 NEW BOM REV:0.1A

BOM REV:1.0A for PVT10/19/2005

C C

B B

A A

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

BOM & PCB MODIFY HISTORY

AXPER

XP-M8S761GX

1

2 34Wednesday, October 19, 2005

1.0

5

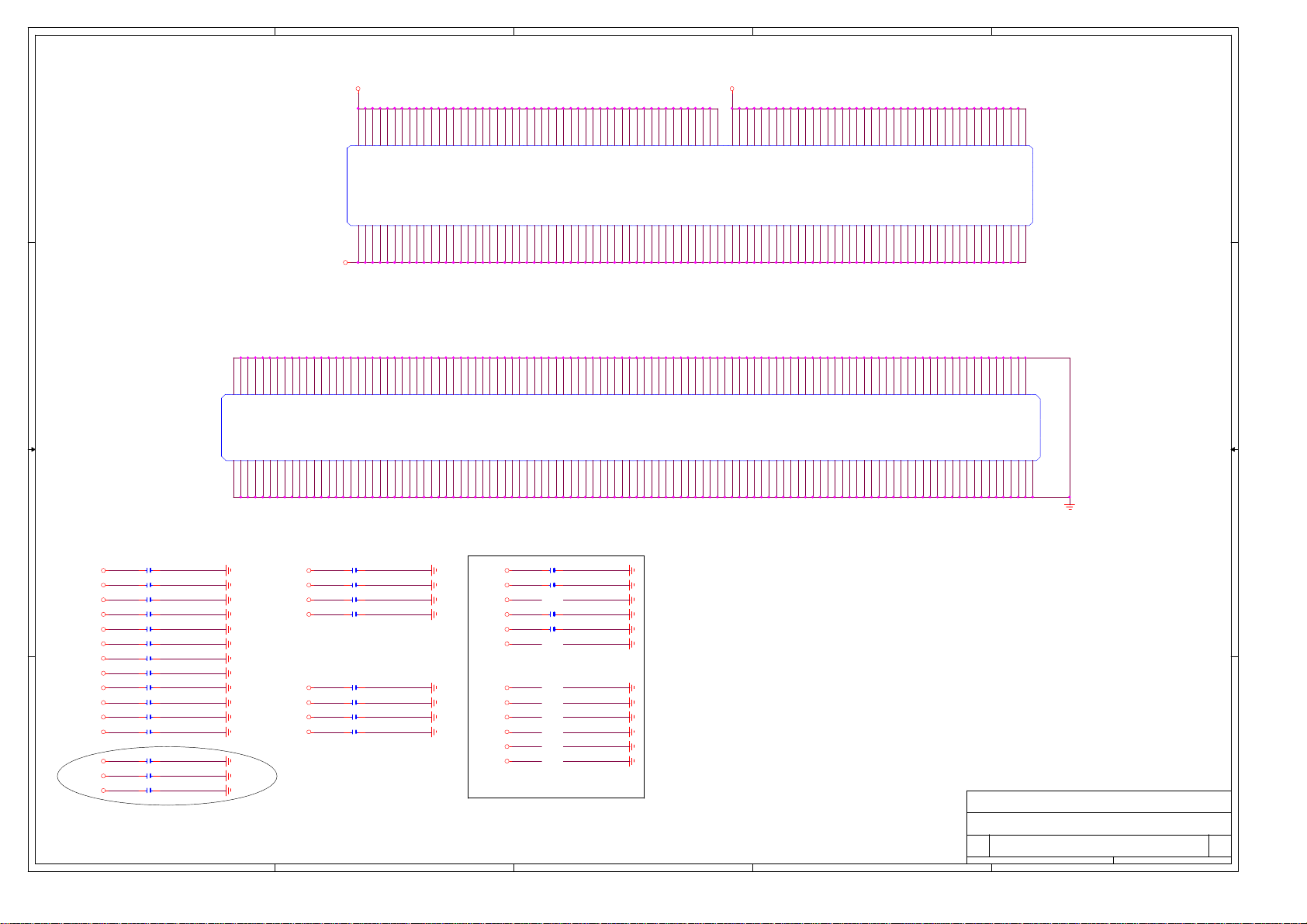

BLOCK DIAGRAM

4

3

2

1

AMD K8 CPU

D D

CLOCK GENERATOR

SIS761GX NORTH BRIDGE

VID0~4

MAA0~14

MDD0~63

-DQSD0~8

PWM/OTHER POWER

VCORE = 1.75V (650-1100MHZ) / SLEEP : 1.3V

5VSB,-12V,+12V,VCC,VCC3,3VDUAL

DDRVTT,DDR25V,3VSTR,VCC25

PAGE 32~34

DDR SDRAM DIMM X 2

PCIE_16

C C

ZAD0~16

CONTROL BUS

Z LINK

USB CONN

SIS964 SOUTH BRIDGE

USB PORTS 0~7

Serial ATA

IDE Primary and Secondary

B B

PCI BUS

PCI SLOT 1,2,3

BIOS SST49LF003A

RTL8201CL

AC97 CODEC

ALC655/658

AC97 LINK

A A

AUDIO PORTS :

LINE_IN

5

FRONT AUDIO

MICLIN_ OUT

CD_IN

FRONT PANEL /FANS

4

3

LPC BUS

LPC I/O IT8705AF

I/O PORTS :

COMA

LPT

PS2

FDD

2

Title

Size Document Number Rev

Custom

Date: Sheet of

AXPER

BLOCK DIAGRAM

XP-M8S761GX

1

3 34Wednesday, October 19, 2005

1.0

5

4

3

2

1

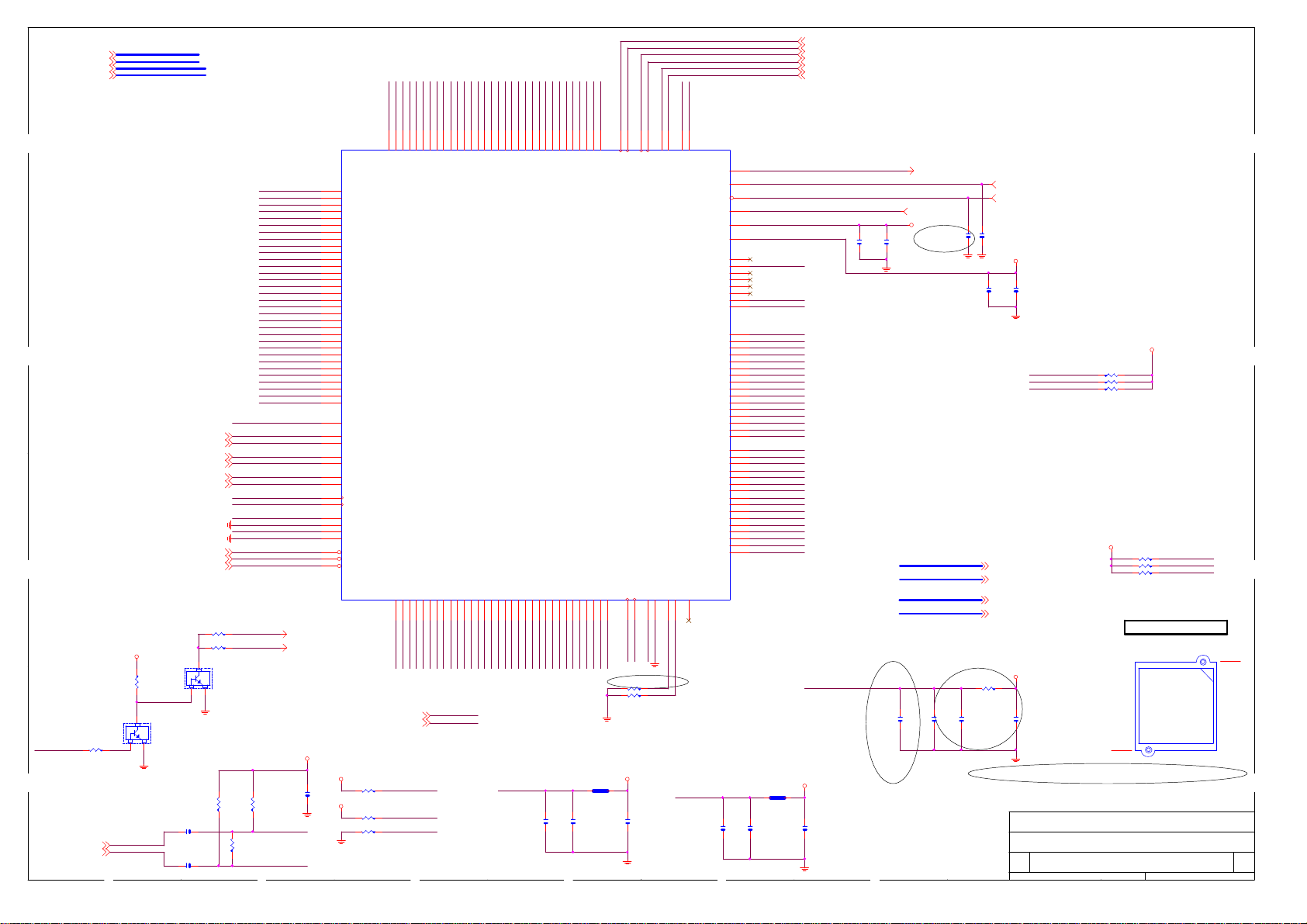

L0_CADIN_L[0..15]

D D

C C

B B

L0_CADIN_H[0..15]

L0_CLKIN_L[0..1]

L0_CLKIN_H[0..1]

L0_CADOUT_L[0..15]

L0_CADOUT_H[0..15]

L0_CLKOUT_L[0..1]

L0_CLKOUT_H[0..1]

L0_CADIN_L[0..15] [8]

L0_CADIN_H[0..15] [8]

L0_CLKIN_L[0..1] [8]

L0_CLKIN_H[0..1] [8]

L0_CADOUT_L[0..15] [8]

L0_CADOUT_H[0..15] [8]

L0_CLKOUT_L[0..1] [8]

L0_CLKOUT_H[0..1] [8]

VCC12

Clawhammer HT Interface

VCC12 HT12B

D29

VLDT0_A6

D27

VLDT0_A5

D25

VLDT0_A4

C28

VLDT0_A3

C26

VLDT0_A2

B29

VLDT0_A1

B27

T25

R25

U27

U26

V25

U25

W27

W26

AA27

AA26

AB25

AA25

AC27

AC26

AD25

AC25

T27

T28

V29

U29

V27

V28

Y29

W29

AB29

AA29

AB27

AB28

AD29

AC29

AD27

AD28

Y25

W25

Y27

Y28

R27

R26

T29

R29

VLDT0_A0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

R1 49.9/6/1

R2 49.9/6/1

L0_CTLIN_H0[8]

L0_CTLIN_L0[8]

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

HOLE5

HOLE6

HOLE1

12171819

SOCKET_754A

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

HOLE2

HOLE3

HOLE4

20

AH29

VLDT0_B6

AH27

VLDT0_B5

AG28

VLDT0_B4

AG26

VLDT0_B3

AF29

VLDT0_B2

AE28

VLDT0_B1

AF25

VLDT0_B0

N26

N27

L25

M25

L26

L27

J25

K25

G25

H25

G26

G27

E25

F25

E26

E27

N29

P29

M28

M27

L29

M29

K28

K27

H28

H27

G29

H29

F28

F27

E29

F29

J26

J27

J29

K29

N25

P25

P28

P27

HYPER TRANSPORT - LINK0

由

CPU內部VCC12 .

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H0

L0_CTLOUT_L0

轉出

L0_CTLOUT_H0 [8]

L0_CTLOUT_L0 [8]

BC1 4.7u/8/Y5V/10V/Z

VCC12

EC1

+

1000U/D/6.3V/8C/30m

A A

Near CPU side

5

4

VCC12

VCC12

VCC12

VCC12

HT12B

HT12B

BC2 4.7u/8/Y5V/10V/Z/X

BC3 0.1u/6/Y5V/25V/Z

BC4 0.1u/6/Y5V/25V/Z/X

BC5 4.7u/8/Y5V/10V/Z

BC6 0.1u/6/Y5V/25V/Z

3

Title

Size Document Number Rev

Custom

2

Date: Sheet of

AXPER

K8 SOCKET 754-1

XP-M8S761GX

1

4 34Wednesday, October 19, 2005

1.0

5

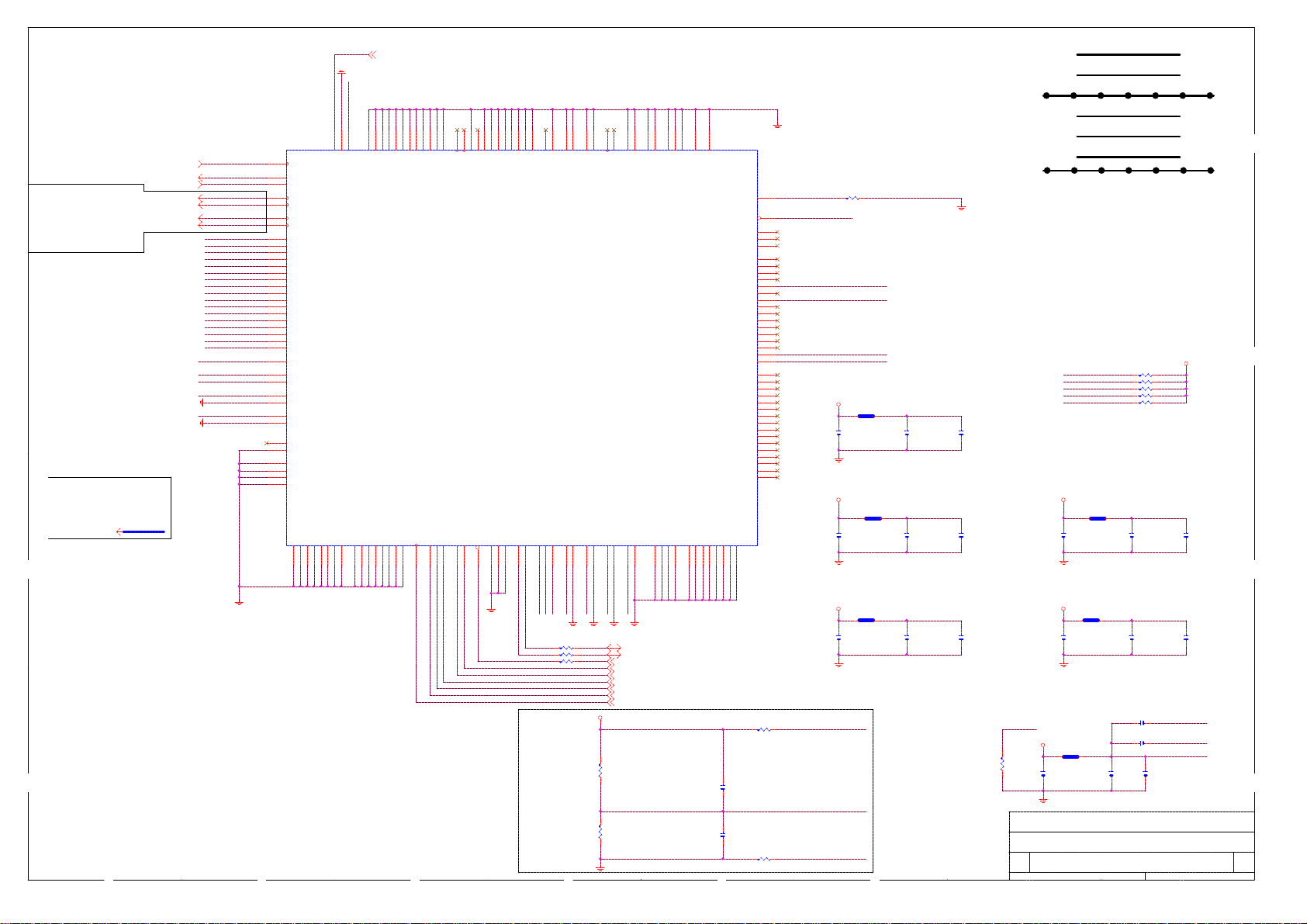

MD[0..63]

MAA[0..13]

-DQS[0..17]

DCLK[0..7]

-DCLK[0..7]

D D

MEMBANKB[0..1]

MAB[0..13]

MEMCHECK[0..7]

MEMBANKA[0..1]

-CS[0..5]

C C

B B

A A

MD[0..63] [18]

MAA[0..13] [17,18]

-DQS[0..17] [18]

DCLK[0..7] [17,18]

-DCLK[0..7] [17,18]

MEMBANKB[0..1] [17,18]

MAB[0..13] [17,18]

MEMCHECK[0..7] [18]

MEMBANKA[0..1] [17,18]

-CS[0..5] [17,18]

5

VTTDDR

VTTDDR_SENSE

25VSTR

R3 49.9/6/1/X

VTTDDR_SENSE

R4 10/6/1

R5 10/6/1

For DDR

compatibility

MD63

MD62

MD61

MD60

MD59

MD58

MD57

MD56

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

MD47

MD46

MD45

MD44

MD43

MD42

MD41

MD40

MD39

MD38

MD37

MD36

MD35

MD34

MD33

MD32

MD31

MD30

MD29

MD28

MD27

MD26

MD25

MD24

MD23

MD22

MD21

MD20

MD19

MD18

MD17

MD16

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

-DQS17

-DQS16

-DQS15

-DQS14

-DQS13

-DQS12

-DQS11

-DQS10

-DQS9

-DQS8

-DQS7

-DQS6

-DQS5

-DQS4

-DQS3

-DQS2

-DQS1

-DQS0

CPUVREF

MEMZN

MEMZP

AE13

AG12

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

AH13

AJ13

D14

C14

A16

B15

A12

B11

A17

A15

C13

A11

A10

C11

AC1

AC3

AC2

AD1

AE1

AE3

AG3

AE2

AF1

AH3

AH9

AG5

AH5

A13

AA1

AG1

AH7

A14

AB1

B9

C7

A6

A9

A5

B5

C5

A4

E2

E1

A3

B3

E3

F1

G2

G1

L3

L1

G3

J2

L2

M1

W1

W3

W2

Y1

AJ4

AJ3

AJ5

AJ6

AJ7

AJ9

R1

A7

C2

H1

T1

A8

D1

J1

AJ2

AJ8

4

VTT_SENSE

MEMVREF1

MEMZN

MEMZP

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDQS17

MEMDQS16

MEMDQS15

MEMDQS14

MEMDQS13

MEMDQS12

MEMDQS11

MEMDQS10

MEMDQS9

MEMDQS8

MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0

4

SOCKET_754B

RSVD_MEMADDA15

RSVD_MEMADDA14

RSVD_MEMADDB15

RSVD_MEMADDB14

MEMORY INTERFACE

VTT_A4

VTT_A1

VTT_A2

VTT_A3

VTT_B1

VTT_B2

VTT_B3

VTT_B4

MEMRESET_L

MEMCKEA

MEMCKEB

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

MEMADDB13

MEMADDB12

MEMADDB11

MEMADDB10

MEMADDB9

MEMADDB8

MEMADDB7

MEMADDB6

MEMADDB5

MEMADDB4

MEMADDB3

MEMADDB2

MEMADDB1

MEMADDB0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

D17

A18

B17

C17

AF16

AG16

AH16

AJ17

AG10

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E14

D12

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

MEMCKEA

MEMCKEB

DCLK7

-DCLK7

DCLK6

-DCLK6

DCLK5

-DCLK5

DCLK4

-DCLK4

DCLK1

-DCLK1

DCLK0

-DCLK0

-CS3

-CS2

-CS1

-CS0

-SRASA

-SCASA

-SWEA

MEMBANKA1

MEMBANKA0

MAA13

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

-SRASB

-SCASB

-SWEB

MEMBANKB1

MEMBANKB0

MAB13

MAB12

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

3

2

Place a cap every 0.5 in. on VTTDDR traces between CPU and DDR.

VTTDDR

MEMCKEA [17,18]

MEMCKEB [17,18]

-SRASA [17,18]

-SCASA [17,18]

-SWEA [17,18]

-SRASB [17,18]

-SCASB [17,18]

-SWEB [17,18]

VTTDDR

BC7

4.7u/8/Y5V/10V/Z

VTTDDR

SC38

4.7u/8/Y5V/10V/Z/X

BC8

4.7u/8/Y5V/10V/Z

BC17

10u/12/X5R/6.3V/M/X

1 2

1 2

BC9

4.7u/8/Y5V/10V/Z

BC18

10u/12/X5R/6.3V/M/X

BC19

10u/12/X5R/6.3V/M/X

1 2

BC11

4.7u/8/Y5V/10V/Z/X

BC15

4.7u/8/Y5V/10V/Z/X

BC16

4.7u/8/Y5V/10V/Z/X

CPU RETAINTION/[12KRC-04K801-01_12KRC-04K801-11]

BC20

10u/12/X5R/6.3V/M

1 2

SOCKET_754

CPUVREF

25VSTR

BC22

0.1u/6/Y5V/25V/Z

R6

CPUVREF

3

40 MILS

BC23

0.01u/4/X7R/16V/K

BC24

0.1u/6/Y5V/25V/Z

150/6/1

R7

150/6/1

2

Title

Size Document Number Rev

Custom

Date: Sheet of

AXPER

K8 SOCKET 754-2

XP-M8S761GX

1

BC21

10u/12/X5R/6.3V/M/X

1 2

GND

1

5 34Wednesday, October 19, 2005

BC14

4.7u/8/Y5V/10V/Z/X

GND

1.0

5

4

3

2

1

D D

BC25

10u/8/Y5V/10V/Z

HT12B

C C

B B

A A

-CPURST

C1

1n/4/X7R/50V/K/X

K8PWROK

C10

1n/4/X7R/50V/K/X

-THRMTRIP

Close to

VCORE VCC

CPUCLK0_H(L)

C7 39p/4/NPO/50V/J/X

C8 39p/4/NPO/50V/J/X

R21 1K/6

SR1 0/6

SR2 0/6

Route trace 50 mils wide and

500 to 750 mils long between

these caps.

FB1 FB30/6/[10LF1-40300A-01_10LF1-07300A-01]

R11 44.2/6/1

R12 44.2/6/1

C4

1n/4/X7R/50V/KC51n/4/X7R/50V/K

VCC25

-THRMTRIP_SB

-THRMTRIP_W

25VDDA25_VDDA

BC303

10u/8/Y5V/10V/Z

0.1u/6/Y5V/25V/Z

25VSTRFB

CPUCLK0_H[16]

CPUCLK0_L[16]

-THRMTRIP_SB [13]

-THRMTRIP_W [31]

25VSTR

BC26

R13 49.9/6/1/X

25VSTRFB

CPUCLK0_H

10/19 REV:1.0A

Route VDDA25 trace approx.

50 mils wide (use 2x25 mil

traces to exit ball field) and

500 mils long.

BC27

1n/4/X7R/50V/K

-CPURST[8]

K8PWROK[34]

-LDTSTOP[8]

COREFB[19]

-COREFB[19]

C6 3.9n/4/X7R/50V/K

C9 3.9n/4/X7R/50V/K

VTTDDR

-CPURST

K8PWROK

-LDTSTOP

REF1

REF0

COREFB

-COREFB

CLKIN

R14

169/6/1

-CLKINCPUCLK0_L

NC_AJ23

NC_AH23

DBRDY

TMS

TCK

-TRST

TDI

NC_C18

NC_A19

NC_AE23

NC_AF23

NC_AF22

NC_AF21

AH25

AJ25

AF20

AE18

AJ27

AF27

AE26

AE12

AF12

AE11

AJ21

AH21

AJ23

AH23

AE24

AF24

AG15

AH17

AJ28

AE23

AF23

AF22

AF21

AG2

AH1

AE21

C20

AG4

AG6

AE9

AG9

A23

A24

B23

C16

C15

E20

E17

B21

A21

C18

A19

A28

C1

R3

AA2

D3

B18

C6

VDDA1

VDDA2

RESET_L

PWROK

LDTSTOP_L

L0_REF1

L0_REF0

COREFB_H

COREFB_L

CORE_SENSE

VDDIOFB_H

VDDIOFB_L

VDDIO_SENSE

CLKIN_H

CLKIN_L

NC_AJ23

NC_AH23

NC_AE24

NC_AF24

VTT_A5

VTT_B5

DBRDY

NC_C15

TMS

TCK

TRST_L

TDI

NC_C18

NC_A19

KEY1

KEY0

NC_AE23

NC_AF23

NC_AF22

NC_AF21

FREE29

J3

FREE31

FREE33

FREE35

FREE1

FREE37

FREE4

FREE38

FREE41

FREE7

FREE11

FREE12

FREE13

FREE14

FREE40

SOCKET_754C

THERMTRIP_L

G_FBCLKOUT_H

G_FBCLKOUT_L

THERMDA

THERMDC

VID4

VID3

VID2

VID1

VID0

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

NC_AF18

RSVD_SCL

RSVD_SDA

FREE26

FREE28

FREE30

FREE32

FREE34

FREE36

FREE10

FREE18

FREE19

FREE42

FREE24

FREE25

FREE27

-THRMTRIP

A20

C2 1n/4/X7R/50V/K/X

A26

R9 0/6/SHT/X

A27

C3 0.1u/6/Y5V/25V/Z/X

VID4

AG13

VID3

AF14

VID2

AG14

VID1

AF15

VID0

AE15

AG18

AH18

NC_AG17

AG17

NC_AJ18

AJ18

FBCLKOUT

AH19

-FBCLKOUT

AJ19

-DBREQ

AE19

NC_D20

D20

NC_C21

C21

NC_D18

D18

NC_C19

C19

NC_B19

B19

TDO

A22

AF18

D22

C22

B13

B7

C3

K1

R2

AA3

F3

C23

AG7

AE22

C24

A25

C9

VID4 [19]

VID3 [19]

VID2 [19]

VID1 [19]

VID0 [19]

R15 80.6/6/1

TMPIN3+ [25]

TMPIN3- [25]

NC_AJ23

TDO

TMS

-DBREQ

DBRDY

TCK

NC_C18

NC_A19

TDI

-TRST

NC_AE23

NC_AF23

NC_AF22

NC_AF21

NC_B19

NC_D18

NC_AJ18

NC_AG17

NC_C19

NC_D20

NC_C21

NC_AH23

R1142,C548,C549 MUST NEAR

SOCKET_754

Route FBCLKOUT_H/L differentially

with 20/8/5/8/20 spacing and trace

width.

25VSTR

R18 820/6

R19 1K/6

VCC25

1 2

RN1

3 4

1K/8P4R/6

5 6

7 8

1 2

RN2

3 4

1K/8P4R/6

5 6

7 8

1 2

RN3

3 4

1K/8P4R/6

5 6

7 8

1 2

RN4

3 4

1K/8P4R/6

5 6

7 8

1 2

RN5

3 4

1K/8P4R/6

5 6

7 8

R20 820/6

BC12

0.1u/6/Y5V/25V/Z

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

AXPER

K8 SOCKET 754-3

XP-M8S761GX

1

6 34Wednesday, October 19, 2005

1.0

5

4

3

VCORE25VSTR

2

1

D D

C C

L28

R28

W28

AC28

AF28

AH28

C29F2H2K2M2P2T2V2Y2

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS1

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

SOCKET_754E

B2

AH20

AB21

W22

M23

B B

VCORE

VCORE

VCORE

VCORE

VCORE

VCORE

VCORE

VCORE

VCORE

VCORE

VCORE

VCORE

VCORE

A A

VCORE

VCORE

BC28 10u/8/X5R/6.3V/K

BC30 10u/8/X5R/6.3V/K

BC32 10u/8/X5R/6.3V/K/X

BC34 10u/8/X5R/6.3V/K

BC36 10u/8/X5R/6.3V/K/X

BC37 10u/8/X5R/6.3V/K

BC38 10u/8/X5R/6.3V/K

BC39 10u/8/X5R/6.3V/K/X

BC40 0.1u/6/Y5V/25V/Z

BC42 0.1u/6/Y5V/25V/Z

BC44 0.1u/6/Y5V/25V/Z BC45 0.1u/6/Y5V/25V/Z/X

BC46 0.1u/6/Y5V/25V/Z

BC731 10u/8/X5R/6.3V/K

BC732 0.1u/6/Y5V/25V/Z

BC733 0.01u/4/X7R/25V/K

FOR PH1

5

L24

AG25

25VSTR

25VSTR

25VSTR

25VSTR

VSS12

AG27D2AF2W6Y7

25VSTR

25VSTR

25VSTR

25VSTR

E4G4J4L4N4U4W4

VDDIO1

VDD1

SOCKET_754D

L7

VCORE

AB2

AD2

AH2B4AH4B6G6J6L6N6R6U6AA6

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

AA8

AB9

AA10

J12

B14

Y15

BC29 4.7u/8/Y5V/10V/Z

BC31 4.7u/8/Y5V/10V/Z

BC33 10u/8/X5R/6.3V/K/X

BC35 10u/8/X5R/6.3V/K

BC41 0.1u/6/Y5V/25V/Z/X

BC43 0.1u/6/Y5V/25V/Z

BC47 0.1u/6/Y5V/25V/Z

VDDIO2

VDD2

AC15

H18

VSS111

VSS20

AE16

J18

VDDIO3

VDDIO4

VDD3

VDD4

B20

E21

VSS112

VSS113

VSS21

VSS22

G20

R20

AA4

AC4

AE4D5AF5F6H6K6M6P6T6V6Y6

VDDIO5

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDD5

VDD6

VDD7

VDD8

VDD9

H22

J23

H24

F26N7L9

VSS114

VSS115

VSS116

VSS117

VSS118

VSS23

VSS24

VSS25

VSS26

VSS27

U20

W20

AA20

AC20

AE20

4

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

V10

G13

K14

Y14

AC6

AH6F7H7K7M7P7T7V7AB7

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

AG20

AJ20

D21

F21

H21

AB6

AD6D7G7J7AA7

AC7

AF7F8H8

AB8

AD8D9G9

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

AB14

G15

J15

AA15

H16

K16

Y16

AB16

G17

J17

AA17

AC17

AE17

F18

K18

Y18

AB18

AD18

AG19

VSS125

VSS34

K21

M21

VSS126

VSS35

VCORE

VCORE

VCORE

VCORE

VCORE

VCORE

25VSTR

25VSTR

25VSTR

25VSTR

25VSTR

25VSTR

VSS127

VSS36

P21

T21

VSS128

VSS129

VSS37

VSS38

V21

Y21

VSS130

VSS39

AD7B8G8J8L8N8R8U8W8

VSS131

VSS40

AD21

AG21

VSS132

VSS133

VSS41

VSS42

B22

SC3 10u/8/X5R/6.3V/K/X

SC4 10u/8/X5R/6.3V/K/X

SC6 0.1u/6/Y5V/25V/Z/X

SC7 0.1u/6/Y5V/25V/Z/X

VSS134

VSS43

E22

G22

VSS135

VSS136

VSS44

VSS45

J22

L22

AC8

AH8F9H9K9M9P9T9V9Y9

VSS137

VSS138

VSS139

VSS140

VSS46

VSS47

VSS48

VSS49

N22

R22

U22

AG29

VSS141

VSS142

VSS50

VSS51

AA22

AC22

VSS143

VSS52

Place on K8 CPU solder side

AC9

AF9

VDDIO36

VDDIO37

VDD35

VDD36

E19

G19

VSS144

VSS145

VSS53

VSS54

AG22

AH22

F10

AD10

VDDIO38

VDDIO39

VDD39

VDD38

AC19

AA19

VSS146

VSS147

VSS55

VSS56

AJ22

D23

3

D11

AF11

VDDIO40

VDDIO41

VDD37

VDD40

J19

F20

VSS148

VSS149

VSS57

VSS58

F23

H23

F12

AD12

VDDIO42

VDDIO43

VDD41

VDD42

H20

K20

AD9

B10

VSS150

VSS151

VSS59

VSS60

K23

P23

D13

AF13

VDDIO44

VDDIO45

VDD43

VDD44

M20

P20

G10

J10

VSS152

VSS153

VSS61

VSS62

T23

V23

F14

AD14

VDDIO46

VDDIO47

VDD45

VDD46

T20

V20

L10

N10

VSS155

VSS156

VSS63

VSS64

Y23

AB23

F16

AD16

VDDIO48

VDDIO49

VDD47

VDD48

Y20

AB20

R10

U10

VSS157

VSS158

VSS65

VSS66

AD23

AG23

D15R4N28

U28

AA28

AE27R7U7W7K8M8P8T8V8Y8J9N9R9U9W9

VDD96

VDD97

VDD98

VDD99

VDDIO6

VDD50

G21

J21

AC10

AH10

VSS160

VSS68

G24

J24

VDD51

VDD52

L21

N21

F11

H11

VSS161

VSS162

VSS69

VSS70

N24

R24

VDD53

VDD54

R21

U21

K11

Y11

VSS163

VSS164

VSS71

VSS72

U24

W24

VDD100

VDD55

VDD56

W21

AB11

VSS165

VSS166

VSS73

VSS74

AA24

VDDIO50

VDD49

AD20

W10

VSS159

VSS67

E24

VDD101

VDD57

AA21

AC21

AD11

B12

VSS167

VSS75

AC24

AG24

VDD102

VDD103

VDD58

VDD59

F22

K22

G12

AA12

VSS168

VSS169

VSS76

VSS77

AJ24

B25

VDD104

VDD105

VDD60

VDD61

M22

P22

AC12

AH12

VSS170

VSS171

VSS78

VSS79

C25

B26

VDD106

VDD107

VDD62

VDD63

T22

V22

F13

H13

VSS172

VSS173

VSS80

VSS81

D26

H26

VDD108

VDD109

VDD64

VDD65

Y22

AB22

K13

Y13

VSS174

VSS175

VSS82

VSS83

M26

T26

VDD110

VDD111

VDD66

VDD67

AD22

E23

AB13

AD13

VSS176

VSS177

VSS84

VSS85

Y26

AD26

AA9

VDD112

VDD113

VDD68

VDD69

G23

L23

AF17

G14

VSS178

VSS179

VSS86

VSS87

AF26

AH26

H10

K10

VDD114

VDD115

VDD70

VDD71

N23

R23

J14

AA14

VSS180

VSS181

VSS88

VSS89

C27

B28

2

M10

P10

VDD116

VDD117

VDD72

VDD73

U23

W23

AC14

AE14

VSS182

VSS183

VSS90

VSS91

D28

G28

T10

Y10

VDD118

VDD119

VDD74

VDD75

AA23

AC23

D16

E15

VSS184

VSS185

VSS92

VSS187

F15

H15

AB10

G11

VDD120

VDD121

VDD76

VDD77

B24

D24

K15

AB15

VSS186

VSS189

VSS188

VSS206

AB17

AD17

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

VDD93

VDD94

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD78

VDD79

VDD80

VDD81

VDD82

VDD83

VDD84

VDD85

F24

K24

M24

P24

T24

V24

Y24

AB24

AD15

AH14

E16

G16

J16

AA16

AC16

AE29

VSS190

VSS191

VSS192

VSS194

VSS195

VSS196

VSS197

VSS198

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

B16

G18

AA18

AC18

D19

F19

H19

K19

Title

Size Document Number Rev

Custom

Date: Sheet of

VDD130

VDD131

VDD86

VDD87

AD24

AH24

AJ26

E18

VSS199

VSS223

VSS215

VSS216

Y19

AB19

VDD132

VDD133

VDD88

VDD89

AE25

K26

F17

H17

VSS201

VSS202

VSS217

VSS218

AD19

AF19

VDD95

POWER

VDD90

VDD91

VDD92

P26

V26

K17

Y17

VSS203

VSS204

VSS205

GROUND

VSS219

VSS220

VSS221

VSS222

J20

L20

N20

K8 SOCKET 754-4

AXPER

XP-M8S761GX

1

7 34Wednesday, October 19, 2005

1.0

8

877665544332211

R1827

8.2K/6

L0_CADIN_L[0..15]

L0_CADIN_H[0..15]

L0_CADOUT_H[0..15]

L0_CADOUT_L[0..15]

VCC3

R1826

8.2K/6

Q153

MMBT2222A/SOT23/600mA/40

132

CPUCLK1_L

CPUCLK1_H

L0_CLKOUT_L0[4]

L0_CLKOUT_H0[4]

L0_CLKOUT_L1[4]

L0_CLKOUT_H1[4]

L0_CTLOUT_L0[4]

L0_CTLOUT_H0[4]

-LDTSTOP[6]

LDTREQ#[13]

-CPURST[6]

R1838 0/6

R1839 0/6/X

Q154

MMBT2222A/SOT23/600mA/40

132

R25

49.9/6/1

C12 3.9n/4/X7R/50V/K

C13 3.9n/4/X7R/50V/K

GLEDOVAGP16V

R29

169/6/1

LRCOMP

761CLK761CLK+

HTAVDD

HTPHYAVDD

-LDTSTOP

LDTREQ#

-CPURST

L0_CADOUT_H0

L0_CADOUT_H1

L0_CADOUT_H2

L0_CADOUT_H3

L0_CADOUT_H4

L0_CADOUT_H5

L0_CADOUT_H6

L0_CADOUT_H7

L0_CADOUT_H8

L0_CADOUT_H9

L0_CADOUT_H10

L0_CADOUT_H11

L0_CADOUT_H12

L0_CADOUT_H13

L0_CADOUT_H14

L0_CADOUT_H15

L0_CADOUT_L0

L0_CADOUT_L1

L0_CADOUT_L2

L0_CADOUT_L3

L0_CADOUT_L4

L0_CADOUT_L5

L0_CADOUT_L6

L0_CADOUT_L7

L0_CADOUT_L8

L0_CADOUT_L9

L0_CADOUT_L10

L0_CADOUT_L11

L0_CADOUT_L12

L0_CADOUT_L13

L0_CADOUT_L14

L0_CADOUT_L15

GLED- [13,32]

OVAGP16V [13]

BC55

0.1u/6/Y5V/25V/Z

R26

49.9/6/1

761CLK-

761CLK+

VCC12

AE32

AD34

AB32

AA34

AC30

AB29

AD32

AC34

AA32

AC31

AA29

V34

T32

R34

N32

Y30

U30

T29

P30

N29

L30

Y34

U34

R32

P34

M32

Y31

U31

R29

P31

M29

L31

J34

V32

W32

V29

W29

L34

M34

C18

B18

C17

A18

A17

B17

F18

D18

E18

LRCAD_P0

LRCAD_P1

LRCAD_P2

LRCAD_P3

LRCAD_P4

LRCAD_P5

LRCAD_P6

LRCAD_P7

LRCAD_P8

LRCAD_P9

LRCAD_P10

LRCAD_P11

LRCAD_P12

LRCAD_P13

LRCAD_P14

LRCAD_P15

LRCAD_N0

LRCAD_N1

LRCAD_N2

LRCAD_N3

LRCAD_N4

LRCAD_N5

LRCAD_N6

LRCAD_N7

LRCAD_N8

LRCAD_N9

LRCAD_N10

LRCAD_N11

LRCAD_N12

LRCAD_N13

LRCAD_N14

LRCAD_N15

LRCOMP

LRCLK_N0

LRCLK_P0

LRCLK_N1

LRCLK_P1

LRCTL_N

LRCTL_P

HTCLKN

HTCLKP

HTAVDD

HTAVSS

HTPHYAVDD

HTPHYAVSS

LDTSTOP#

LDTREQ#

LDTRESET#

VCC12

R24 100/6/1

VCC12

R27 49.9/6/1

R28 49.9/6/1

L0_CADIN_L1

L0_CADIN_L4

L0_CADIN_L2

L0_CADIN_L3

L0_CADIN_L5

L0_CADIN_L6

L0_CADIN_L0

A23

C24

A26

C27

C30

A32

C33

LTCAD_N0

LTCAD_N1

LTCAD_N2

LTCAD_N3

LTCAD_N4

LTCAD_N5

LTCAD_N6

HOST_RX

PETp0

PETp1

PETp2

PETp3

PETp4

PETp5

J1K3M1N3R1T3V1W3AA1

EXP_A_TXP5

EXP_A_TXP2

EXP_A_TXP4

EXP_A_TXP1

EXP_A_TXP3

EXP_A_TXP0

PECLK0[16]

-PECLK0[16]

LRCOMP

LTCOMPN

LTCOMPP

L0_CADIN_L9

L0_CADIN_L7

L0_CADIN_L8

L0_CADIN_L10

E34

E22

F24

E25

LTCAD_N7

LTCAD_N8

LTCAD_N9

L0_CADIN_L11

L0_CADIN_L12

L0_CADIN_L14

L0_CADIN_L13

F27

F30

F33

J29

LTCAD_N10

LTCAD_N11

LTCAD_N12

LTCAD_N13

LTCAD_N14

L0_CADIN_L15

L0_CADIN_H1

L0_CADIN_H0

L0_CADIN_H2

J31

A22

C23

A25

LTCAD_P0

LTCAD_P1

LTCAD_N15

L0_CADIN_H6

L0_CADIN_H5

L0_CADIN_H4

L0_CADIN_H3

C26

C29

A31

LTCAD_P2

LTCAD_P3

LTCAD_P4

LTCAD_P5

L0_CADIN_H7

L0_CADIN_H8

C32

D34

D22

LTCAD_P6

LTCAD_P7

HOST_TX

761-1

PCIE_TX

PETp6

PETp7

PETp8

PETp9

PETp10/SVB_BLUE+

PETp11/SVB_GREEN+

PETp12/SVB_RED+

PETp13/SVA_BLUE+

PETp14/SVA_GREEN+

PETp15/SVA_RED+

PETn0

PETn1

PETn2

PETn3

PETn4

PETn5

EXP_A_TXN5

EXP_A_TXN4

EXP_A_TXN3

EXP_A_TXN1

EXP_A_TXN2

EXP_A_TXN0

BC56

0.01u/4/X7R/16V/K

PETn6

EXP_A_TXN7

EXP_A_TXN6

AB3

EXP_A_TXP6

EXP_A_TXP9

EXP_A_TXP8

EXP_A_TXP7

PECLK0

-PECLK0

AD1

AE3

AG1

AH3

AK1

EXP_A_TXP11

EXP_A_TXP10

EXP_A_TXP14

EXP_A_TXP12

EXP_A_TXP13

AL3K1L3N1P3T1U3W1Y3

EXP_A_TXP15

HTAVDD

L0_CADIN_H9

L0_CADIN_H10

L0_CADIN_H11

L0_CADIN_H12

F23

D25

F26

F29

LTCAD_P8

LTCAD_P9

LTCAD_P10

LTCAD_P11

PETn7

PETn8

PETn9

PETn10/SVB_BLUE-

AB1

AC3

AE1

AF3

EXP_A_TXN9

EXP_A_TXN8

EXP_A_TXN11

EXP_A_TXN10

FB4

BC57

0.1u/6/Y5V/25V/Z

L0_CADIN_H13

L0_CADIN_H14

L0_CADIN_H15

F32

H29

H31

A29

A28

LTCLK_N0

LTCAD_P13

LTCAD_P14

LTCAD_P15

PETn12/SVB_RED-

PETn13/SVA_BLUE-

PETn14/SVA_GREEN-

PETn15/SVA_RED-

AH1

AJ3

AL1

AM3

EXP_A_TXN14

EXP_A_TXN13

EXP_A_TXN12

EXP_A_TXN15

R1796 390/6/1

R1797 124/6/1

VCC18

0/6/SHT/X

LTCLK_P0

REFCLKN

H2H1Y2Y1AA3

-PECLK0

LTCAD_P12

PETn11/SVB_GREEN-

E28

D28

H34

LTCTL_N

LTCLK_N1

LTCLK_P1

REFCLKP

PCIEAVDD

PCIEAVSS

PCIEAVDD

PECLK0

BC58

0.1u/6/Y5V/25V/Z

LTCOMPP

LTCOMPN

J33

J32

LTCTL_P

LTCOMP_N

LTCOMP_P

PCIE_RSET0

PCIE_RSET1

PMEN

AA4

E14

PCIERSET1

PWROK

PCIRST#

AUXOK

AUX3.3

AUX_IVDD

TRAPA0

TRAPA1

TRAPA2

TRAPA3

TRAPA4

TRAPA5

TRAPA6

TRAPA7

PERp0

PERp1

PERp2

PERp3

PERp4

PERp5

PERp6

PERp7

PERp8

PERp9

PERp10

PERp11

PERp12

PERp13

PERp14

PERp15

PERn0

PERn1

PERn2

PERn3

PERn4

PERn5

PERn6

PERn7

PERn8

PERn9

PERn10

PERn11

PERn12

PERn13

PERn14

PERn15

U25A

INTXN

SIS761GX/A1/[10HB1-04761-10]

G34

PCIE_RX

PCIERSET0

08/18 sis E-Mail

HTPHYAVDD

BC59

0.01u/4/X7R/16V/K

F17

A15

F14

F15

E15

C15

E17

F16

E16

D16

C16

B16

A16

B15

J5

K6

M5

N6

R5

T6

V5

W6

AB6

AD5

AE6

AG5

AH6

AK5

AL6

AN5

J4

L6

M4

P6

R4

U6

V4

Y6

AC6

AD4

AF6

AG4

AJ6

AK4

AM6

AN4

EXP_A_RXP0

EXP_A_RXP1

EXP_A_RXP2

EXP_A_RXP3

EXP_A_RXP4

EXP_A_RXP5

EXP_A_RXP6

EXP_A_RXP7

EXP_A_RXP8

EXP_A_RXP9

EXP_A_RXP10

EXP_A_RXP11

EXP_A_RXP12

EXP_A_RXP13

EXP_A_RXP14

EXP_A_RXP15

EXP_A_RXN0

EXP_A_RXN1

EXP_A_RXN2

EXP_A_RXN3

EXP_A_RXN4

EXP_A_RXN5

EXP_A_RXN6

EXP_A_RXN7

EXP_A_RXN8

EXP_A_RXN9

EXP_A_RXN10

EXP_A_RXN11

EXP_A_RXN12

EXP_A_RXN13

EXP_A_RXN14

EXP_A_RXN15

FB5

BC60

0.1u/6/Y5V/25V/Z

L0_CADIN_L[0..15][4]

L0_CADIN_H[0..15][4]

L0_CADOUT_H[0..15][4]

L0_CADOUT_L[0..15][4]

D D

C C

B B

LDTREQ#

A A

CPUCLK1_L[16]

CPUCLK1_H[16]

TRAPA1

TRAPA6

TRAPA7

0/6/SHT/X

L0_CLKIN_L0 [4]

L0_CLKIN_H0 [4]

L0_CLKIN_L1 [4]

L0_CLKIN_H1 [4]

L0_CTLIN_L0 [4]

L0_CTLIN_H0 [4]

0.01u/4/X7R/16V/K/X

PCIEAVDD

VCC18

BC61

0.1u/6/Y5V/25V/Z/X

BC48

BC49

0.1u/6/Y5V/25V/Z

SC39

2.2u/6/Y5V/6.3V/Z

-INTA [9,12,22]

AUXOK [13,31]

3VDUAL

C16

120p/4/NPO/50V/J

0.01u/4/X7R/16V/K/X

EXP_A_TXP[0..15]

EXP_A_TXN[0..15]

EXP_A_RXP[0..15]

EXP_A_RXN[0..15]

10/19 REV:1.0A

BC694

0.01u/4/X7R/16V/K

PWROK [13,34]

-PCIRST [12,25,26,34]

08/17 REV:0.2

C17

100p/4/NPO/50V/J/X

18VDUAL

BC51

BC52

0.1u/6/Y5V/25V/Z

VCC18

Internal pull-down

TRAPA1

R1790 8.2K/6/X

TRAPA6

R1791 8.2K/6/X

TRAPA7

R1792 8.2K/6/X

VCC25

R1793 680/6

EXP_A_TXP[0..15] [21]

EXP_A_TXN[0..15] [21]

EXP_A_RXP[0..15] [21]

EXP_A_RXN[0..15] [21]

R1794 1K/6

R1795 680/6

N.B HEATSINK

VCC18

FB15 0/6

BC695

10u/8/Y5V/10V/Z

BC696

0.1u/6/Y5V/25V/Z

FANSINK/[12SP2-04E004-A1_12SP2-04E004-A2_12SP2-04E004-A3_12SP2-04E004-A4]

08/11 REV:0.2

Title

Size Document Number Rev

Custom

Date: Sheet of

SIS761GX-1(HOST/APCIE)

NB_HEATSINK1

2

2

對邊

HEATSINK:

12SP2-04E004-C1,C2C3,C4

AXPER

XP-M8S761GX

-LDTSTOP

LDTREQ#

-CPURST

FANSINK

8 34Wednesday, October 19, 2005

1

1

1.0

8

877665544332211

VOSCIE [16]

ECLKAVDD

C3B3B4A4D4C5D5E5C6B6D6F6G6F2F1F4F5E3E4D2D3C1C2

AD29

AF34

VSSP

AM11

VSSP

AP12

VSSP

AP8

VSSP

AM9

VSSP

AM12

AF33

VOSCIE

ECLKAVSS

VSSP

VSSP

AP13

ECLKAVDD

VSSP

VSSP

AJ8

AK10

AJ11

VSS

VSSP

AK13

VSS

VSSP

AJ9

VSS

VSSP

AL10

VSS

VSSP

AJ12

VSS

VSSP

AL13

VSS

VSSP

VSS

VSS

VSS

VSS

VSS

VSS

VSSP

VACLK

VBHCLK

VBHSYNC

761GX-2

VOSCI

BOUT

GOUT

VSYNC

ROUT

A13

A11

INTA#

HSYNC

A12

B12

C12

F11

B11

D D

ZCLK_NB[16]

ZREQ_UP[12]

The differences

between the traces of

MuTIOL Strobes and

Data in each group

should be smaller than

0.05",and strobes need

guide GND trace

ZREQ_DN[12]

C C

The differences between

the traces of MuTIOL

Strobes and Data should

be smaller than 0.05"

ZAD[0..16][12]

ZAD[0..16]

ZCLK_NB

ZREQ_UP

ZREQ_DN

-ZSTB0

-ZSTB0[12]

ZSTB0

ZSTB0[12]

-ZSTB1

-ZSTB1[12]

ZSTB1

ZSTB1[12]

ZVREF

ZCMP_N

ZCMP_P

Z1XAVDD

Z4XAVDD

ZAD2

ZAD0

ZAD5

ZAD3

ZAD10

ZAD8

ZAD13

ZAD11

ZAD4

ZAD1

ZAD7

ZAD6

ZAD12

ZAD9

ZAD15

ZAD14

ZAD16

AM16

AL24

AP23

AL20

AM20

AN19

AP19

AJ23

AK23

AJ21

AK21

AJ19

AK19

AJ17

AK17

AL22

AM22

AN21

AP21

AL18

AM18

AN17

AP17

AN23

AP24

AN24

AM24

AK16

AL16

AP16

AN16

AP11

AN11

AP10

AN10

ZCLK

ZUREQ

ZDREQ

ZSTB#0

ZSTB0

ZSTB#1

ZSTB1

ZAD2

ZAD0

ZAD5

ZAD3

ZAD10

ZAD8

ZAD13

ZAD11

ZAD4

ZAD1

ZAD7

ZAD6

ZAD12

ZAD9

ZAD15

ZAD14

ZAD16

ZVREF

ZCMP_N

ZCMP_P

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

AN9

NC

AP9

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

AP7

AM8

B2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSP

VBCAD

VRSET

VGPIO0

VCOMP

VVBWN

VGPIO1

VSS

VSS

VSS

F10

E11

F13

D12

E12

F12

C11

D11

E7

VSS

VSS

DACAVSS1

DACAVDD1

C13

E13

VGPIO0 : DDC1CLK

VGPIO1 : DDC1DATA

VSS

VSS

VBCLK

DCLKAVDD

DACAVSS2

DACAVDD2

A14

B13

D13

Fix @ 2003/08/22

G1

G4G5A7E1E2B7A5D7B5

VSS

VSS

VSSP

VSSP

VBVSYNC

DCLKAVSS

MCLKAVDD

MCLKAVSS

VSS

B14

C14

D14

E10

R, G, B do

not change

layer.

BC71

0.1u/6/Y5V/25V/Z

BC80

0.01u/4/X7R/16V/K/X

Internal pull-down

VSS

VSS

H3

VSSP

TESTMODE2

TESTMODE1

TESTMODE0

VSS

VSS

VSS

ENTEST

DLLEN#

TRAP15

TRAP14

TRAP13

TRAP12

TRAP11

TRAP10

VSS

VSS

TRAP9

TRAP8

TRAP7

TRAP6

TRAP5

TRAP4

TRAP3

TRAP2

TRAP1

TRAP0

F9D9B9C9F8E8D8

U25B

AK31

CPUDLLENN

AK29

AL34

AL33

AL32

AM33

AM34

AN33

AM32

AN32

AP32

AL31

AM31

AN31

AP31

AK30

AL30

AM30

AN30

AP30

AJ29

AP27

DB15

AN27

DB14

AM27

DB13

AL27

DB12

AK27

DB11

AJ27

DB10

AP28

DB9

AN28

DB8

AM28

DB7

AL28

DB6

AK28

DB5

AJ28

DB4

AP29

DB3

AN29

DB2

AM29

DB1

AL29

DB0

VSS

SIS761GX/A1/[10HB1-04761-10]

R56 0/6

TRAP11

TRAP9

TRAP1

TRAP0

VCC3

R1819 0/6/SHT/X

BC69

0.1u/6/Y5V/25V/Z

VCC18 VCC18

R1820 0/6/SHT/X

BC78

0.1u/6/Y5V/25V/Z/X

ECLKAVDD

BC70

0.01u/4/X7R/16V/K/X

Z1XAVDD

BC79

0.1u/6/Y5V/25V/Z

F3F7B8H6C8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

A8

D10

B10

A10

HSYNC_A

VSYNC_A

GND Trace & GND VIA

RED_A

GREEN_A

BLUE_A

GND Trace & GND VIA

TRAP0

R63 8.2K/6/X

TRAP1

R64 8.2K/6/X

TRAP9

R65 8.2K/6/X

TRAP11

R66 8.2K/6/X

CPUDLLENN

R67 8.2K/6/X

R1821 0/6/SHT/X

BC81

0.1u/6/Y5V/25V/Z

Z4XAVDD

BC82

0.1u/6/Y5V/25V/Z

5mil

5mil

20mil

12mil

12mil

12mil

20mil

VCC18

BC83

0.01u/4/X7R/16V/K/X

B B

VCOMP

VVBWN

DACAVDD

DACAVDD

VRSET

R1798 33/6

R1800 0/6

VOSCI

A A

DCLKAVDD

-INTA [8,12,22]

VSYNC_A [20]

HSYNC_A [20]

BLUE_A [20]

GREEN_A [20]

RED_A [20]

VOSCI [16]

VCC18

R77

150/6/1

R79

49.9/6/1

MCLKAVDD

DDC_SDA_A [20]

DDC_SCL_A [20]

Place near 755/760 chip.

R75 56/6

MuTIOL 1.0

Vref=0.5

*VCC1.8

MuTIOL 2.0

Vref=0.25

BC84

*VCC1.8

0.01u/4/X7R/16V/K

BC86

0.1u/6/Y5V/25V/Z

R80 56/6

下一版改

VCC3 VCC3

R1822 0/6/SHT/X

BC691

0.1u/6/Y5V/25V/Z

ZCMP_N

Use R807

open

Use R807

0_R

0.1U/6

ZVREF

ZCMP_P

DCLKAVDD

BC692

0.01u/4/X7R/16V/K/X

BC693

0.1u/6/Y5V/25V/Z

VRSET

R68

130/6/1

Title

Size Document Number Rev

Custom

Date: Sheet of

VCC18

FB7

BC75

0.1u/6/Y5V/25V/Z

R1823 0/6/SHT/X

BC72

0.1u/6/Y5V/25V/Z/X

0/6/SHT/X

MCLKAVDD

BC73

0.01u/4/X7R/16V/K/XR1799 33/6

VVBWN

C14

0.1u/6/Y5V/25V/Z

VCOMP

C15

0.1u/6/Y5V/25V/Z

DACAVDD

BC77

BC76

0.1u/6/Y5V/25V/Z

0.01u/4/X7R/16V/K/X

AXPER

SIS761GX

XP-M8S761GX

BC74

0.1u/6/Y5V/25V/Z

9 34Wednesday, October 19, 2005

1.0

8

877665544332211

D D

AA5

AA6

M2

M3

M6

C C

W2

W4

W5

AA2

AB2

AB4

AB5

AC1

AC2

AC4

AC5

AD2

AD3

AD6

AE2

AE4

AE5

B B

A3A6A9C4C7

C10D1E6E9G3G2H4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSP

VSSP

J2

VSSP

J3

VSSP

J6

VSSP

K2

VSSP

K4

VSSP

K5

VSSP

L1

VSSP

L2

VSSP

L4

VSSP

L5

VSSP

VSSP

VSSP

VSSP

N2

VSSP

N4

VSSP

N5

VSSP

P1

VSSP

P2

VSSP

P4

VSSP

P5

VSSP

R2

VSSP

R3

VSSP

R6

VSSP

T2

VSSP

T4

VSSP

T5

VSSP

U1

VSSP

U2

VSSP

U4

VSSP

U5

VSSP

V2

VSSP

V3

VSSP

V6

VSSP

VSSP

VSSP

VSSP

Y4

VSSP

Y5

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

AF1

AF2

AF4

AF5

AG2

AG3

VSS

VSSP

AG6

VSS

VSSP

AH2

VSS

VSSP

AH4

VSSP

VSSP

AH5

H5

VSSP

VSSP

AJ1

VSSP

VSSP

AJ2

A24

VSSP

AJ4

A27

A30

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

761GX-4

Ground

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

VSSP

AJ5

AJ7

AJ10

AJ13

VSSP

AK2

AK3

AK6

AK7

AK8

AK9

AK11

AK12

B32

VSS

VSSP

AL2

B33

VSS

VSSP

AL4

C22

VSS

VSSP

AL5

C25

VSS

VSSP

AL7

C28

VSS

VSSP

AL8

C31

VSS

VSSP

AL9

C34

VSS

VSSP

AL11

D23

VSS

VSSP

AL12

D24

VSS

VSSP

AM1

D26

VSS

VSSP

AM2

D27

VSS

VSSP

AM4

D29

VSS

VSSP

AM5

VSS

VSSP

D30

AM7

D31

VSS

VSSP

AM10

D32

VSS

VSSP

AM13

D33

VSS

VSSP

AN2

VSS

VSSP

E23

AN3

E24

VSS

VSSP

AN6

E26

VSS

VSSP

AN7

E27

VSS

VSSP

AN8

E29

VSS

VSSP

AN12

E30

VSS

VSSP

AN13

E31

VSS

VSSP

AP3

E32

VSS

VSSP

AP4

E33

VSS

VSSP

AP5

F22

VSS

VSSP

AP6

VSS

VSSP

F25

F28

F31

F34

G29

G30

G31

G32

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ16

AJ18

AK18

AL19

AM19

AJ20

AK20

G33

H30

H32

H33

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL21

AM21

AJ22

AK22

U25D

J30

VSS

K29

VSS

K30

VSS

K31

VSS

K32

VSS

K33

VSS

K34

VSS

L29

VSS

L32

VSS

L33

VSS

M30

VSS

M31

VSS

M33

VSS

N30

VSS

N31

VSS

N33

VSS

N34

VSS

P29

VSS

P32

VSS

P33

VSS

R30

VSS

R31

VSS

R33

VSS

T30

VSS

T31

VSS

T33

VSS

T34

VSS

U29

VSS

U32

VSS

U33

VSS

V30

VSS

V31

VSS

V33

VSS

W30

VSS

W31

VSS

W33

VSS

W34

VSS

Y29

VSS

Y32

VSS

Y33

VSS

AA30

VSS

AA31

VSS

AA33

VSS

AB30

VSS

AB31

VSS

AB33

VSS

AB34

VSS

AC29

VSS

AC32

VSS

AC33

VSS

AD30

VSS

AD31

VSS

AD33

VSS

AE31

VSS

AE33

VSS

AE34

VSS

VSS

VSS

AJ24

AK24

SIS761GX/A1/[10HB1-04761-10]

VCC18

08/11 REV:0.2

VCC18

AL17

AM17

AN18

AP18

AN20

AP20

AN22

AP22

AL23

AM23

AJ25

AJ26

AK25

AK26

AL25

AL26

AM25

AM26

AN25

AN26

AP25

AP26

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VCC12

A19

A20

A21

VLDT

VLDT

VLDT

B19

B20

B21

C19

C20

C21

D19

D20

D21

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

761GX-3

Power

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

AK14

AK15

AL14

AL15

AM14

AM15

VDDPEX

AN14

AJ14

AJ15

E19

E20

VLDT

VDDPEX

AN15

AP14

E21

F19

VLDT

VLDT

VDDPEX

VDDPEX

AP15

VLDT

F20

VLDT

U25C

F21

VLDT

AE29

IVDD

AE30

IVDD

AF29

IVDD

AF30

IVDD

AF31

IVDD

AF32

IVDD

AG29

IVDD

AG30

IVDD

AG31

IVDD

AG32

IVDD

AG33

IVDD

AG34

IVDD

AH29

IVDD

AH30

IVDD

AH31

IVDD

AH32

IVDD

AH33

IVDD

AH34

IVDD

AJ30

IVDD

AJ31

IVDD

AJ32

IVDD

AJ33

IVDD

AJ34

IVDD

AK32

IVDD

AK33

IVDD

AK34

IVDD

SIS761GX/A1/[10HB1-04761-10]

VCC18

A A

Title

Size Document Number Rev

Custom

Date: Sheet of

AXPER

SIS761GX

XP-M8S761GX

10 34Wednesday, October 19, 2005

1.0

8

877665544332211

Close to SIS760 chipset

Top side Cap. Solder side Cap.

BC685 0.1u/6/Y5V/25V/Z/X

BC88 0.1u/6/Y5V/25V/Z

VCC12

BC89 0.1u/6/Y5V/25V/Z

BC686 0.1u/6/Y5V/25V/Z/X

BC687 4.7u/8/Y5V/10V/Z/X

BC93 0.1u/6/Y5V/25V/Z

BC95 0.1u/6/Y5V/25V/Z/X

BC96 0.1u/6/Y5V/25V/Z

BC688 4.7u/8/Y5V/10V/Z/X

BC697 1u/6/Y5V/10V/Z/X

BC103 4.7u/8/Y5V/10V/Z/X

BC104 1u/6/Y5V/10V/Z/X

BC105 0.1u/6/Y5V/25V/Z

BC106 0.1u/6/Y5V/25V/Z

BC107 4.7u/8/Y5V/10V/Z/X

BC108 1u/6/Y5V/10V/Z/X

VCC18

VCC18

08/11 REV:0.2

VCC18 VCC18

D D

N15

N16

N17

N18

P15

P16

P17

P18

P12

P13

P14

R12

R13

R14

T12

T13

T14

U12

U13

U14

V12

V13

V14

W12

W13

W14

Y12

Y13

Y14

AA12

AA13

AA14

AA15

AB12

AB13

AB14

AB15

AC12

AC13

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

AC14

VDDPEX

P19

P20

P21

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

LDTTXPVDD

LDTTXPVDD

LDTTXPVDD

LDTTXPVDD

LDTTXPVDD

LDTTXPVDD

LDTTXPVDD

LDTTXPVDD

LDTTXPVDD

LDTTXPVDD

R21

LDTRXPVDD

T21

LDTRXPVDD

U21

LDTRXPVDD

V21

VCC18

VCC18

C C

VCC12

W21

W22

AC17

AC18

AC20

AC21

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AC19

AC16

W24

V22

N13

N14

L12

L13

L14

M12

M13

M14

N12

L19

L20

L21

L22

L23

L24

M24

N24

P24

R24

T24

U24

V24

LDTRXPVDD

LDTRXPVDD

LDTRXPVDD

LDTRXPVDD

PVDDQ

PVDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

VDDZ

PVDDZ

PVDDZ

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

LDTTXPVDD

761GX-5

Power

VDDPEX

AC15

AD12

VDDPEX

VDDPEX

AD13

AD14

VDDPEX

VDDPEX

AD15

VDDPEX

VDDPEX

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

U25E

M19

M20

M21

M22

M23

N19

N20

N21

N22

N23

P22

P23

R22

R23

T22

T23

U22

U23

V23

W23

Y21

Y22

Y23

Y24

AA16

AA17

AA18

AA19

AA20

AA21

AA22

AA23

AA24

AB16

AB17

AB18

AB19

AB20

AB21

AB22

AB23

AB24

AC22

AC23

AC24

AD23

AD24

VCC18

VCC18

08/11 REV:0.2

VCC3

VCC18VCC18

VCC18

08/11 REV:0.2

VCC18

08/11 REV:0.2

SC15 1u/6/Y5V/10V/Z

SC16 0.1u/6/Y5V/25V/Z

SC17 10u/8/Y5V/10V/Z

08/15 for PCIE issue

SC18 10u/8/Y5V/10V/Z

SC19 0.1u/6/Y5V/25V/ZBC92 1u/6/Y5V/10V/Z

SC20 0.1u/6/Y5V/25V/Z

SC21 0.1u/6/Y5V/25V/Z

SC22 0.1u/6/Y5V/25V/Z

SC23 0.1u/6/Y5V/25V/Z

SC24 0.1u/6/Y5V/25V/Z/X

SC25 10u/8/Y5V/10V/Z

SC26 10u/8/Y5V/10V/Z

SC27 0.1u/6/Y5V/25V/Z

VCC12

SC28 1u/6/Y5V/10V/Z

SC29 0.1u/6/Y5V/25V/Z

08/15 for PCIE issue

B B

VCC3.3

VCC3.3

VCC3.3

VCC3.3

VCC3.3

VCC3.3

VCC3.3

VCC3.3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSP

VSSP

VSSP

VSSP

VSSP

VCC3

L15

L16

L17

L18

M15

M16

M17

M18

R16

R17

R18

R19

R20

T16

T17

T18

T19

T20

U16

U17

U18

U19

U20

V16

V17

V18

V19

V20

W16

W17

W18

W19

W20

Y16

Y17

Y18

Y19

Y20

R15

T15

U15

V15

W15

Y15

VSSP

SIS761GX/A1/[10HB1-04761-10]

A A

Title

Size Document Number Rev

Custom

Date: Sheet of

AXPER

SIS761GX

XP-M8S761GX

11 34Wednesday, October 19, 2005

1.0

Loading...

Loading...