Gigabyte NF44X-A7 rev.12 Schematics

5

4

3

2

1

PAGE

D D

C C

B B

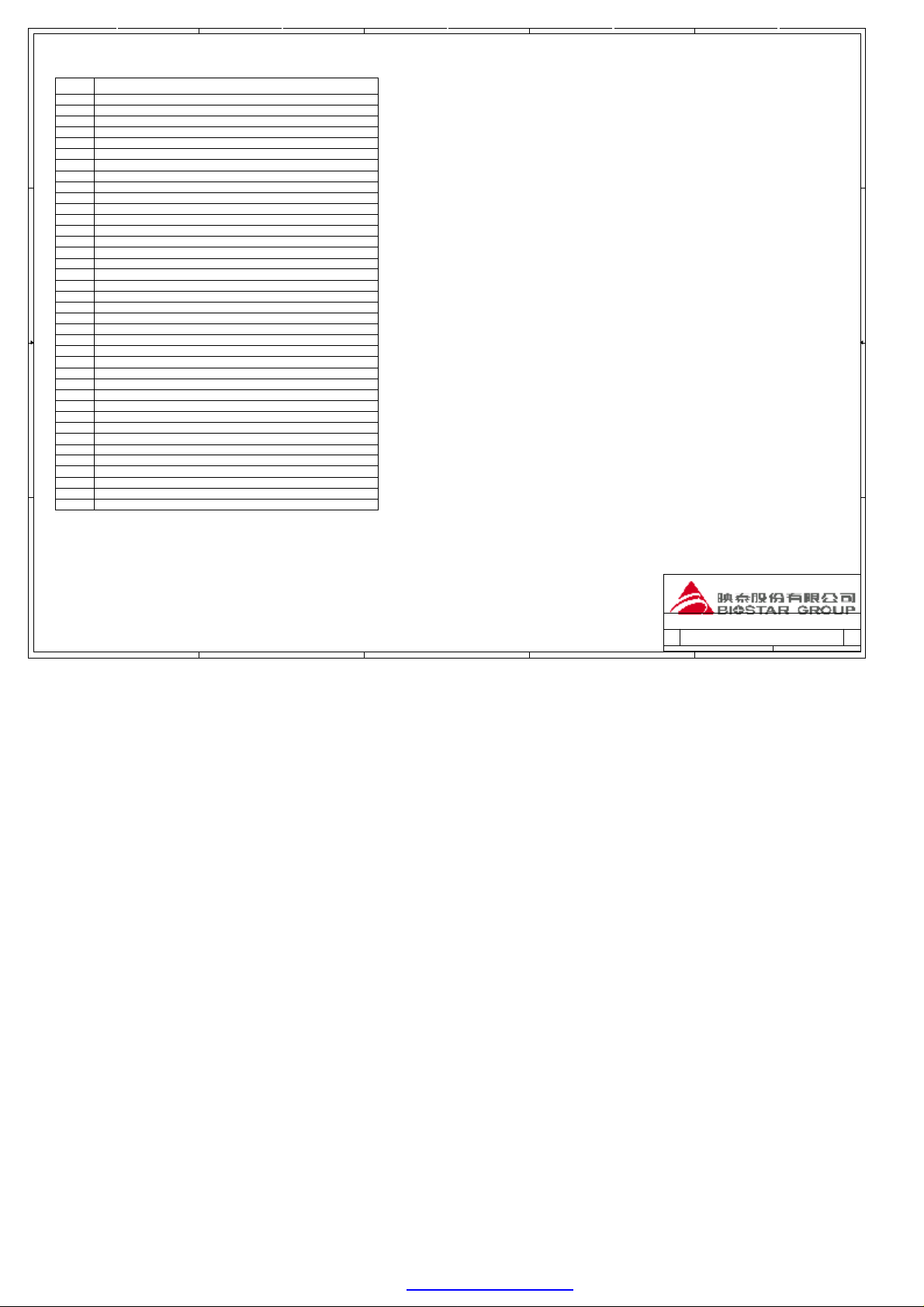

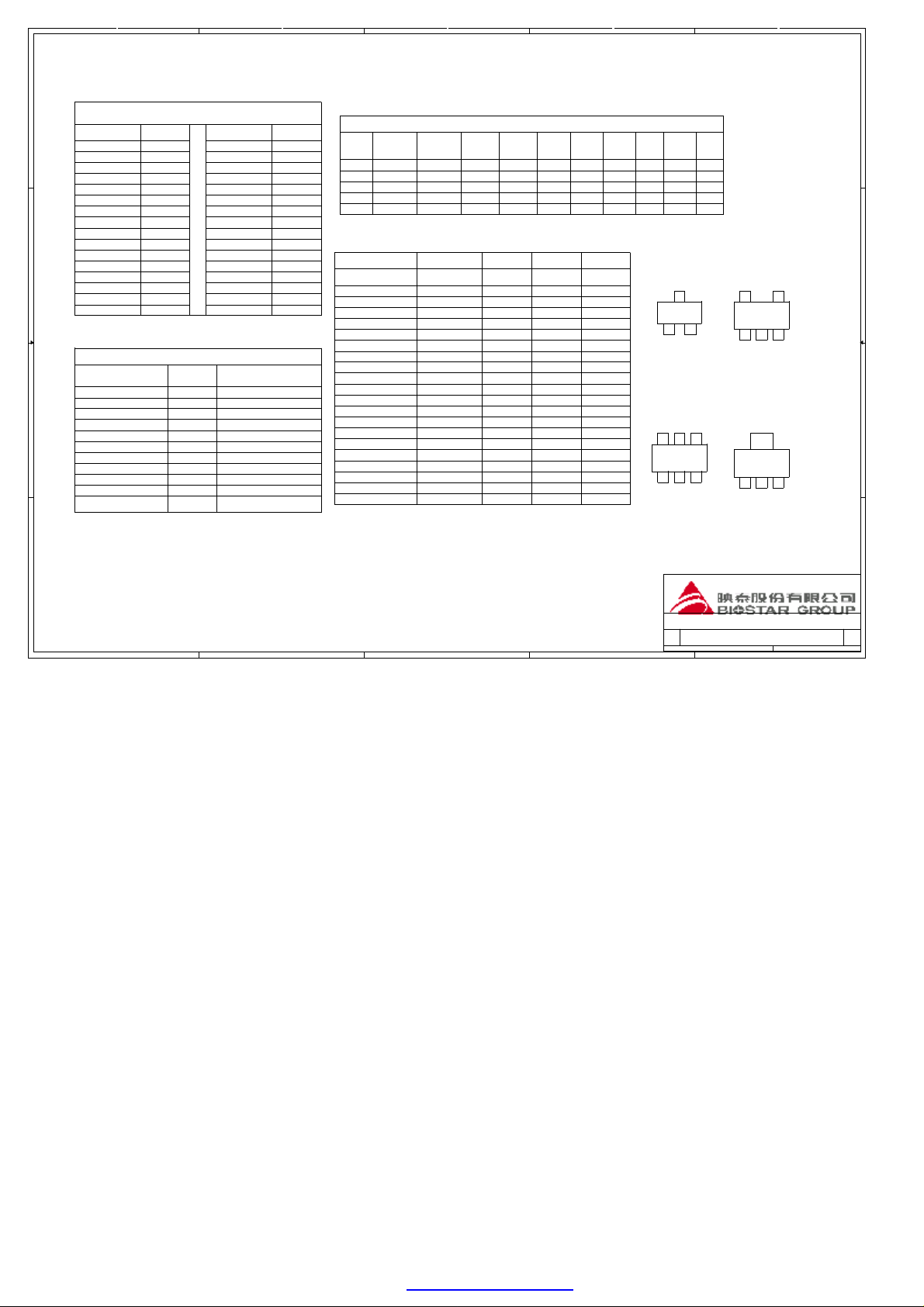

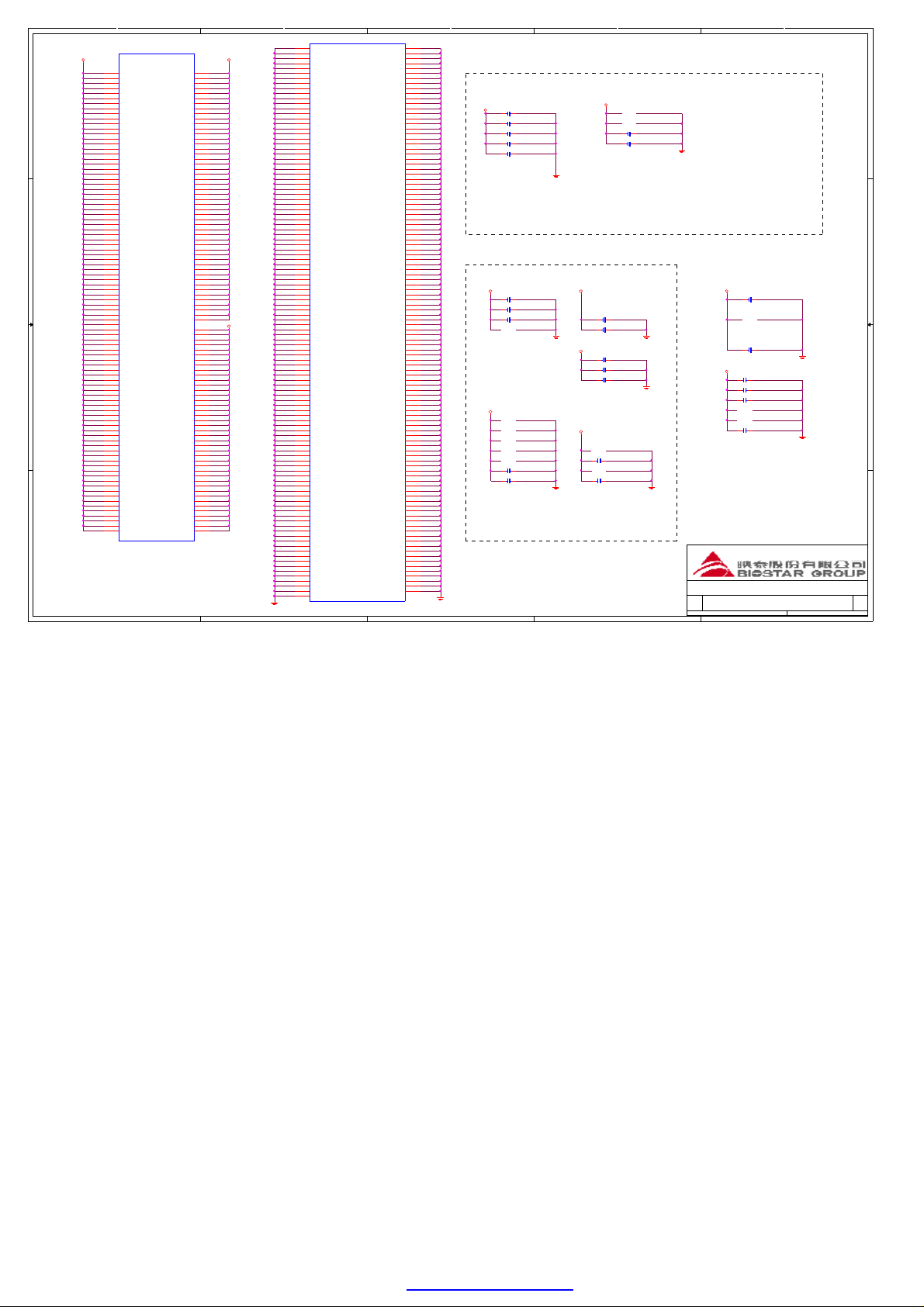

CONTENTS

COVER & COMPONENT SIZE

1-2

BLOCK DIAGRAM

3

RESET MAP

4

CLOCK DISTRIBUTION

5

6

PCI DEVICE TABLE / VID TABLE

7-11

SKT 754 K8CPU

12

CPU DECOUPLING

DDR DIMM 0

13

DDR DIMM 1

14

15

16

CK804 HT

17

CK804 PCI EXPRESS

CK804 PCI

18

19

CK804 SATA / IDE

CK804 G/MII / AC97 / USB

20

CK804 POWER & DECOUPLING

21

PCI EXPRESS X1 CONNECTOR'S

22

23

PCI EXPRESS X16 CONNECTOR

24

PCI CONNECTOR 1/2

25

PCI CONNECTOR 3/4

26

PCI TERMINATION

AUDIO ALC655 CODEC

27

28

AUDIO PORT

SIO ITE 8712

29

30

H/W MON,FAN CONTROL

31

IDE CONNECTORS

32

FLOPPY / PS2 / FLASH ROM

SERIAL PORT& PARALLEL PORT

33

USB CONNECTORS

34

35

POWER SEQUENCING

10/100 LAN PHY RTL8201BL/CL

36

PWR CON / FNT PNL/ VBAT

37

OVER VOLTAGE CKT

38

39

VCC_CORE DC-DC CONVER

40

PLL DELAY / PWRGD / MEM VREG

41

CK804 CORE / LAN / HT - VREGS

FRONT USB

42

43

BOM

NF44X-A7 ( CK804-4X )

REV 1.2

DDR DECOUPLINGDDR ADD/CTL TERMINATION

DDR X 2 , PCI-Ex16 X 1 , PCI-Ex1 X 2 , PCI X 4 ,

Realtek 10/100 Lan PHY , AMD K8-754

A A

Title

COVER SHEET

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

NF44X-A7

1 43Wednesday, April 19, 2006

1

1.2

PDF created with pdfFactory Pro trial version www.pdffactory.com

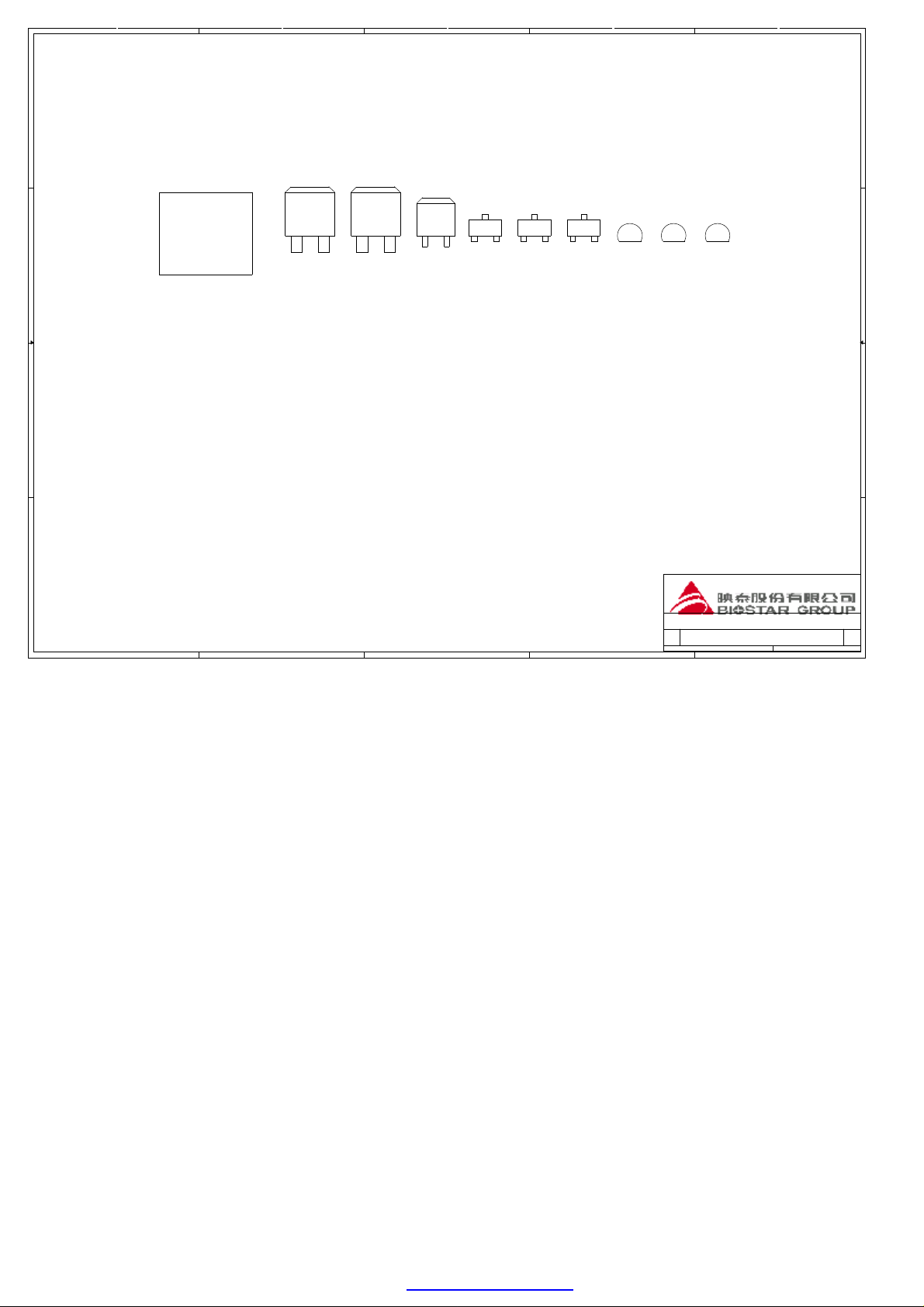

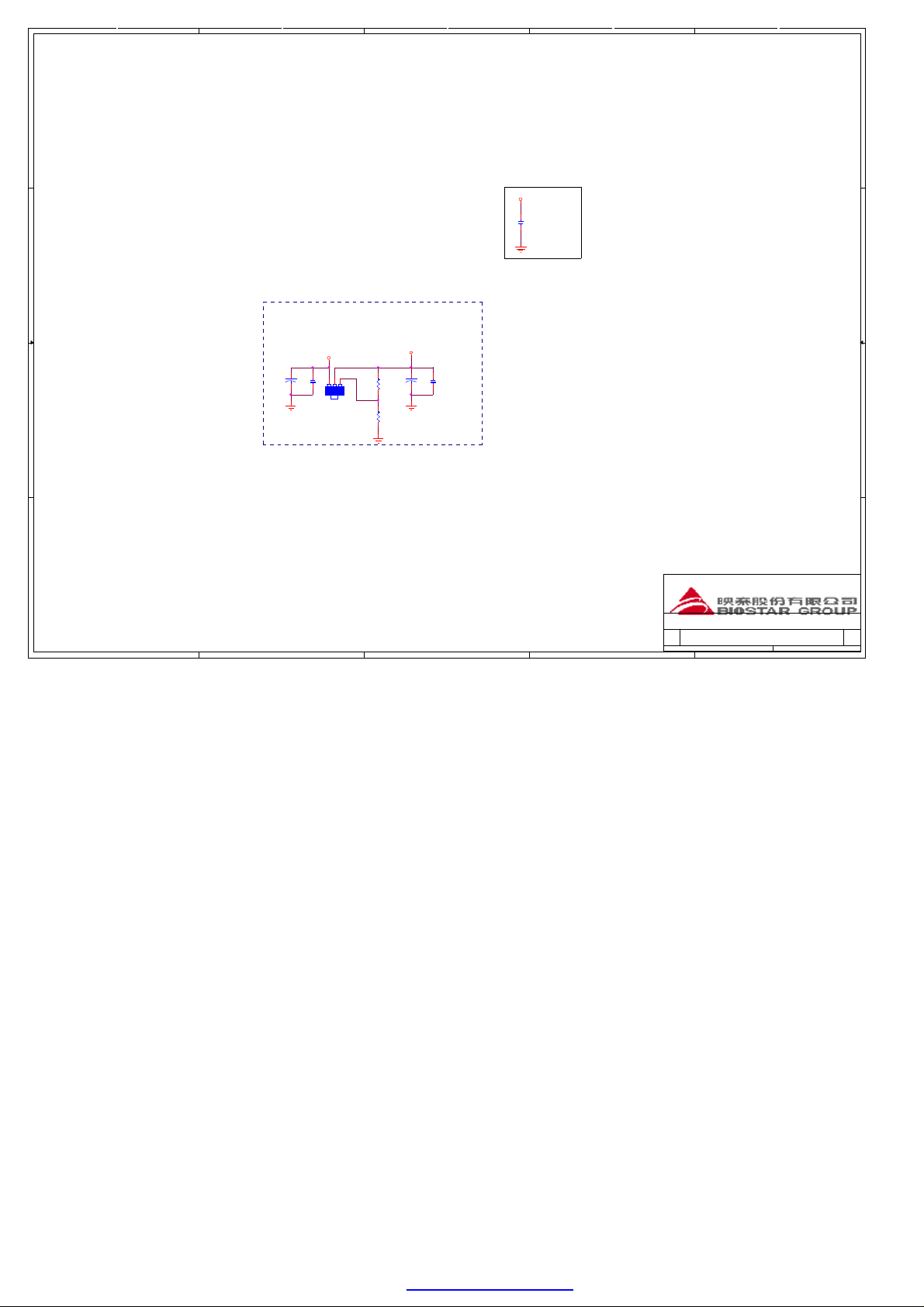

5

D D

22U/25DE

5*7 mm

100U/16DE

6.3*11 mm

220U/10DE

6.3*11 mm

8*11 mm

470U/16DE

1000U/10DE

8*14 mm

1500U/16DE

C C

B B

3300U/25DE

10*25 mm

10*25 mm

4

D

S

G

TO-263

2SK3296 HSD882-D

1

TO-263

B55QS03

2

3

3

D

G

TO-252 SOT-23

20N03

TM3055TL-S

45N03

FDD6030L

D

G

S

SOT-23

2N7002 LM431

SI2303S

SI2301S

C

S

B

2N3904

2N3906

MMBT2907A

2

1

3

C

E

B C

E

2

3

1

E

SOT-23

BAT54C

BAT54S

1

2

T0-92

T0-92

2N2222A

78L05-D

2N2097A

LM432

B

T0-92

A A

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

Custom

Component Size

NF44X-A7

1

2 43Wednesday, April 19, 2006

1.2

PDF created with pdfFactory Pro trial version www.pdffactory.com

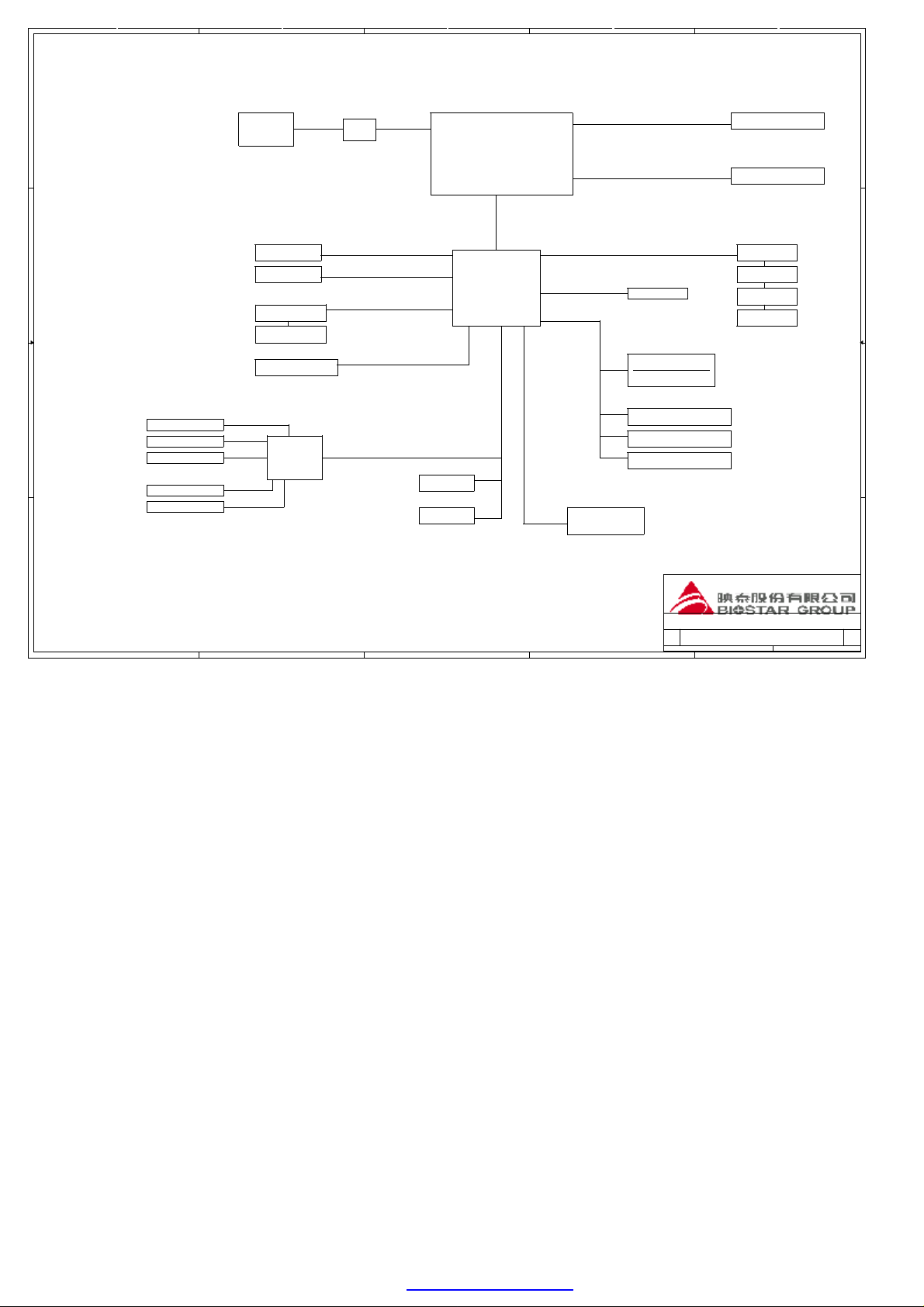

5

4

3

2

1

D D

C C

B B

FLOPPY CONN

PS2/KBRD CONN

PARALLEL CONN

SERIAL CONN

SERIAL HDR

POWER

SUPPLY

CONNECTOR

PEX X16

PEX X1 (2)

PRIMARY IDE

SECONDARY IDE

X4 - SATA CONN

SIO

ITE 8712

VREG

PCI EXPRESS

PCI EXPRESS

ATA 133

INTEGRATED SATA

LPC BUS 33MHZ

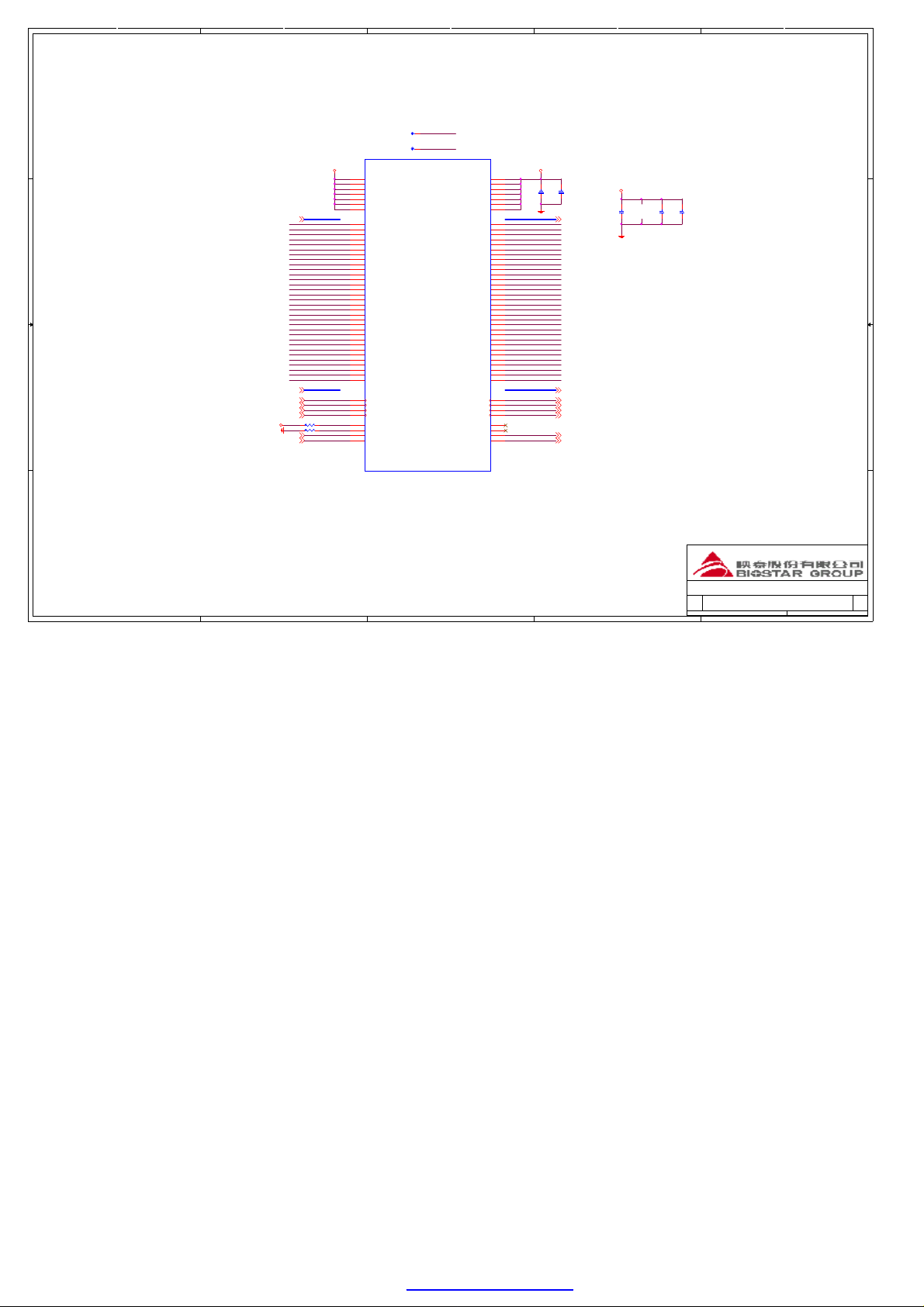

BLOCK DIAGRAM

SOCKET 754

K8

HT 16X16 1GHZ

NFORCE

CRUSH K804 Ultra

740BGA

LPC HDR

4MB FLASH

RGMII

PCI 33MHZ

AC97

X10 USB2

MII/RGMII

AC97

BACK PANEL CONN

USB2 PORTS 5-4

DOUBLE STACK

USB2 PORTS 3-2

X2/GBIT LAN

FRONT PANEL HDR

USB2 PORTS 1-0

USB2 PORTS 7-6

USB2 PORTS 9-8

DDR SDRAM CONN 1

DDR SDRAM CONN 2

PCI SLOT 1

PCI SLOT 2

PCI SLOT 3

PCI SLOT 4

A A

Title

BLOCK DIAGRAM

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

NF44X-A7

3 43Wednesday, April 19, 2006

1

1.2

PDF created with pdfFactory Pro trial version www.pdffactory.com

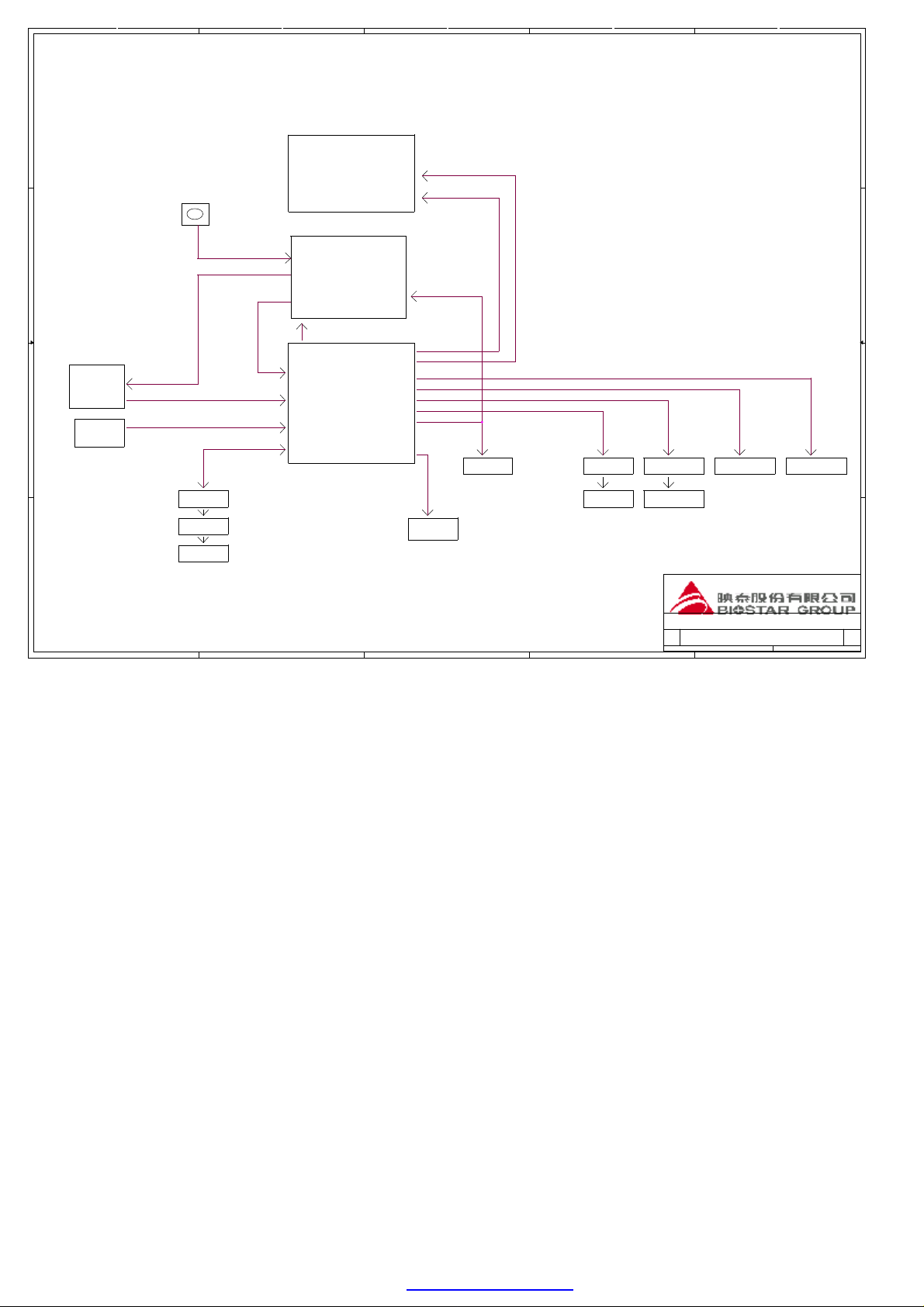

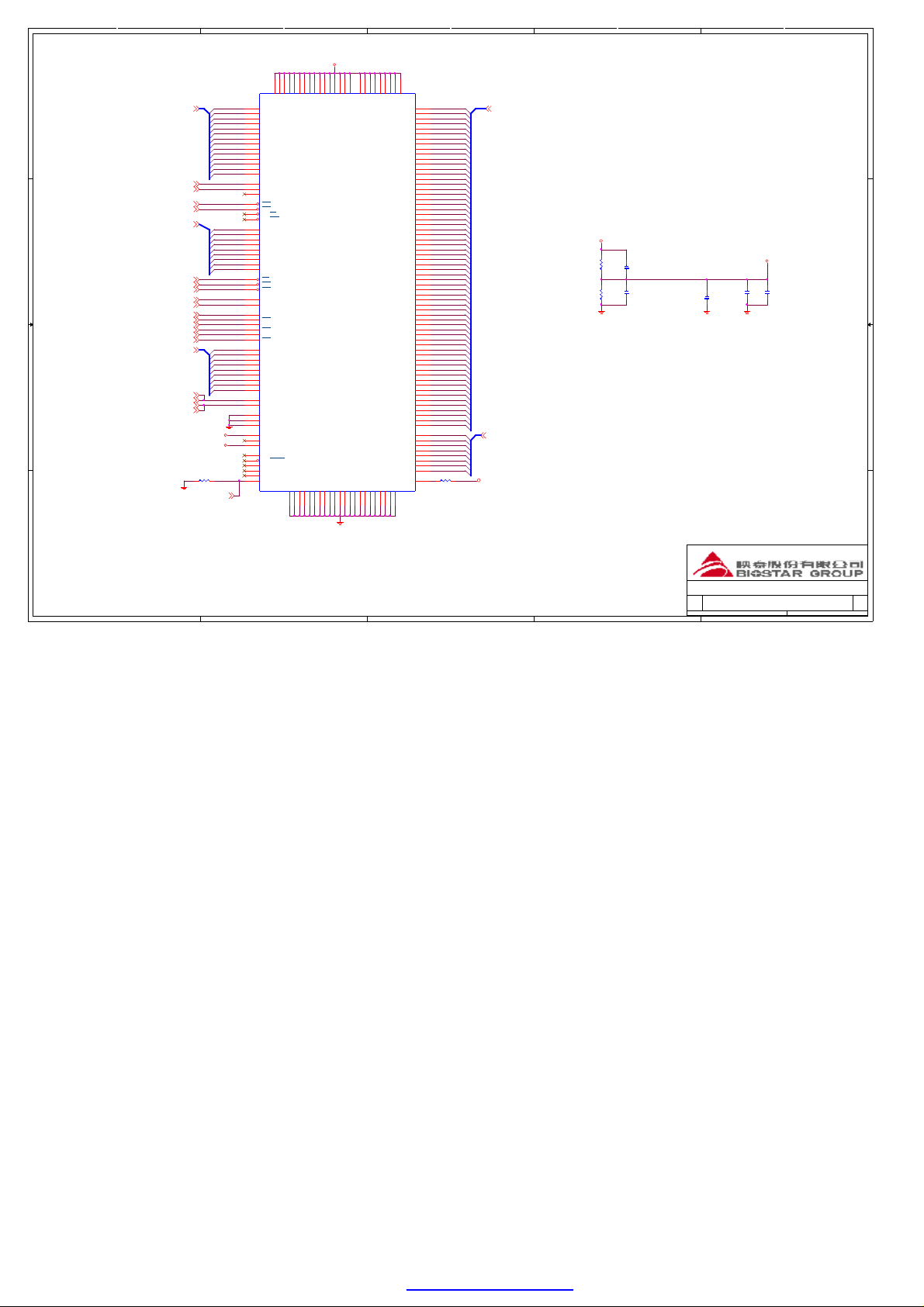

5

4

3

2

1

D D

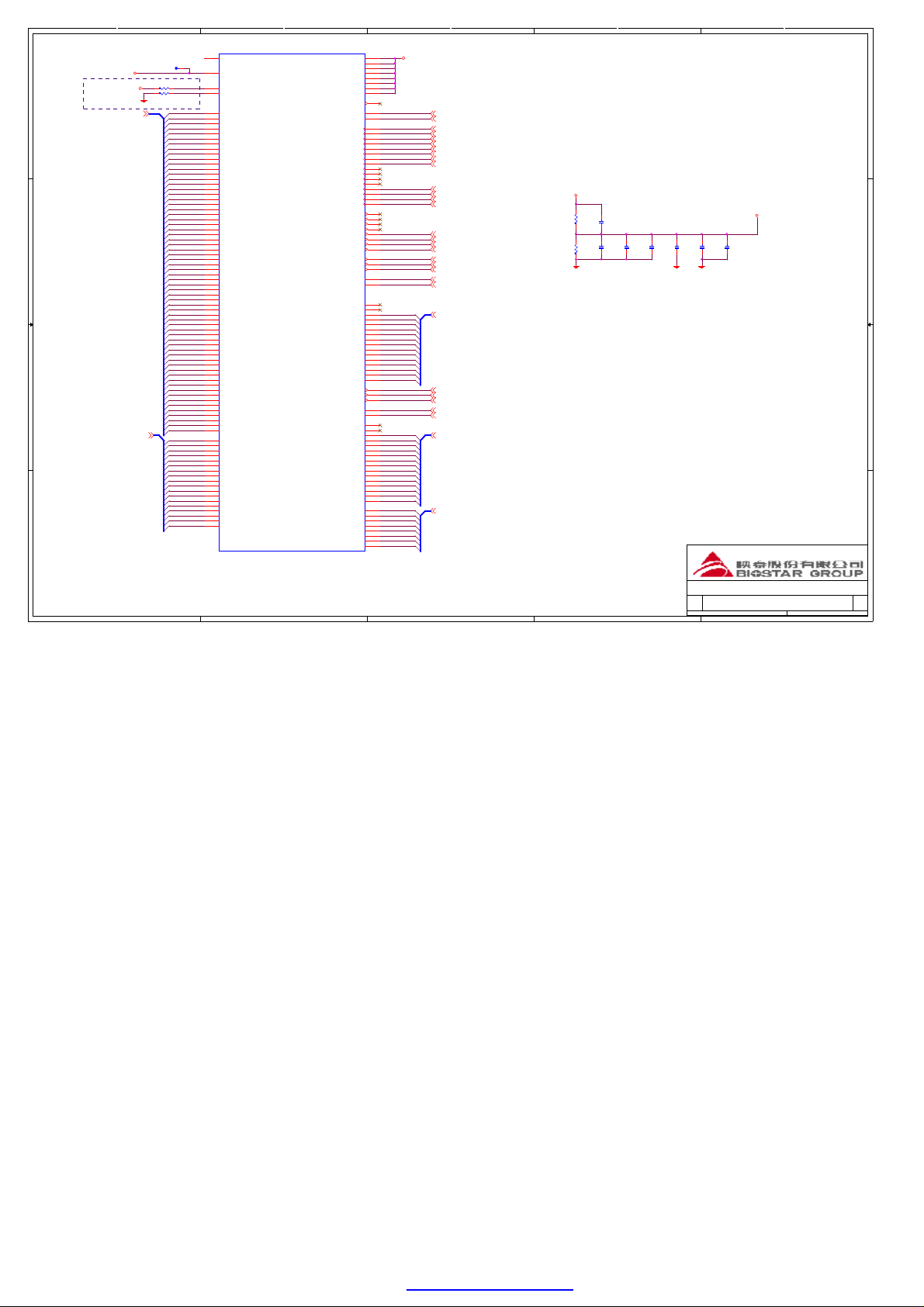

RESET MAP

K8 SKT 754

RESET*

CPU_RST*

CPU_PWRGD

LPCRST_SIO*

CPU_PWRGD

CPU_RST*

PCIRST_SLOT1*

PCIRST_SLOT2*

PCIRST_SLOT3-4*

PCIRST_IDE*

LPCRST_FLASH*

PRI IDEFLASH

SEC IDE

PCI SLOT 3

PCI SLOT 2

PCI SLOT 1

CPU RST*

PWR SWTCH

PWRBTN*

C C

PANSWH# (75)

PSON# (76)

CPU PWRGD

SIO

ITE 8712

PWRON# (75)

PSIN (71)

PWR CONN

PS ON

PWR GOOD

B B

PWRGD SB

CIRCUIT

SLP_S3*

POWER_GOOD

PWRGD_SB

SLP S3*

PWR BUTTON

PWRGD

PWRGD_SB

PE_RESET*

CPU PWRGD

CPU RST*

PCI RST0*

PCI RST1*

PCI RST2*

PCI RST3*

LPC_RST*

GPIO_AUX*

CK804 Ultra

PEX X16 PCI SLOT 4

PEX X1(2) LAN_PHY

PEX X1NC

A A

Title

RESET MAP

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

NF44X-A7

4 43Wednesday, April 19, 2006

1

1.2

PDF created with pdfFactory Pro trial version www.pdffactory.com

5

4

3

2

1

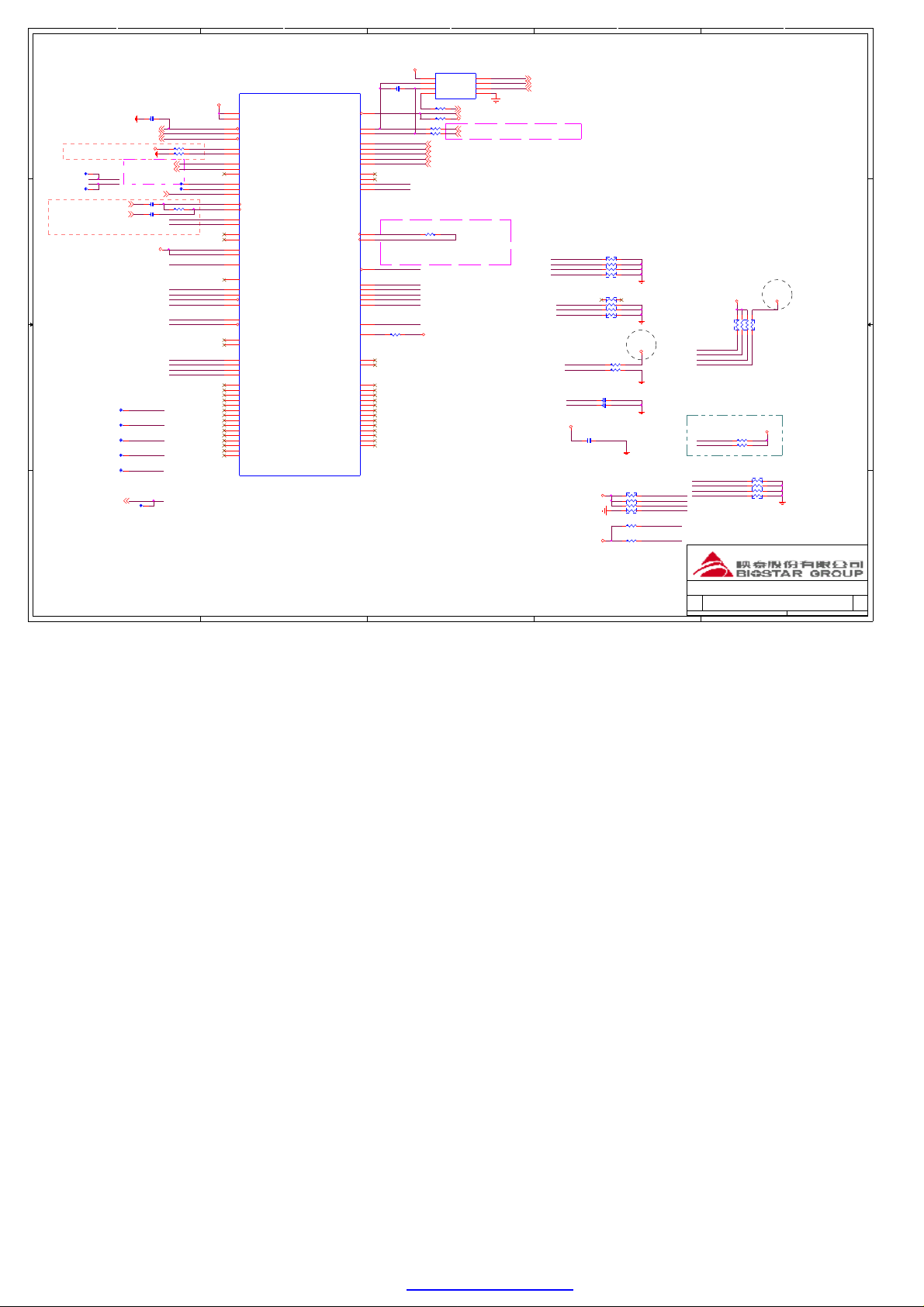

HT_TXCLK0

HT_TXCLK0*

HT_RXCLK0

D D

HT_RXCLK0*

HT_TXCLK1

HT_TXCLK1*

HT_RXCLK1

HT_RXCLK1*

CPU_CLK_IN*

CPU_CLK_IN

MEMORY_A1_CLK[2:0]

MEMORY_A1_CLK[2:0]*

MEMORY_B1_CLK[2:0]

MEMORY_B1_CLK[2:0]*

DIMM 1

DIMM 2

CK804 Ultra

CPU_CLK_IN

K8 754 CPU

CPU_CLK_IN*

HT_RXCLK1*

HT_RXCLK1

HT_TXCLK1*

HT_TXCLK1

HT_RXCLK0*

HT_RXCLK0

HT_TXCLK0*

C C

32.0 KHZ

25 MHZ

B B

HT_TXCLK0

XTAL_IN

XTAL_OUT

XTAL_IN

XTAL_OUT

PE0_REFCLK

PE0_REFCLK*

PE1_REFCLK

PE1_REFCLK*

PE2_REFCLK

PE2_REFCLK*

PE3_REFCLK

PE3_REFCLK*

PCI_CLK_FB

AC_BITCLK

BUF_25MHZ

BUF_SIO

SUSCLK

LPC_CLK0

PCI_CLK0

PCI_CLK1

PCI_CLK2

PCI_CLK3

PCI_CLK4

PCI_CLK5

LPC_CLK1

AC_97CLK

14MHZ OR 24MHZ

TP_N/A

24MHZ

AC '97 LINK

PEX X16

PEX X1

PEX X1

ZDB

SIO

AC97

CODEC

FLASH

LPC

HEADER

PCI SLOT 2

PCI SLOT 1

PCI SLOT 3

PCI SLOT 4

LAN

PHY

A A

Title

CLOCK DISTRIBUTION

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

NF44X-A7

5 43Wednesday, April 19, 2006

1

1.2

PDF created with pdfFactory Pro trial version www.pdffactory.com

5

4

3

2

1

D D

0X00000

0X00001

0X00010

0X00011

0X00100

0X00101

0X00110

0X00111

0X01000

0X01001

0X01010

C C

B B

0X01011

0X01100

0X01101

0X01110

0X01111

CPU VID TABLE

VDDVID [4..0]

1.550V

1.525V

1.500V

1.475V

1.450V

1.425V

1.400V

1.375V

1.350V

1.300V

1.275V

1.250V

1.225V

1.200V

1.175V

SMBUS ADDRESS MAP

DEVICE

DIMM 0

DIMM 1

DIMM 2

DIMM 3

SIO

PCI SLOT 1

PCI SLOT 2

PCI SLOT 3

PCI SLOT 4

DDC BUS

DDC BUS

SMBUS #

VID [4..0]

0X10000

0X10001

0X10010

0X10011

0X10100

0X10101

0X10110

0X10111

0X11000

0X110011.325V

0X11010

0X11011

0X11100

0X11101

0X11110

0X11111

ADDRESS

1010 000 = 0X50

0

0

1010 001 = 0X51

1010 010 = 0X52

0

1010 011 = 0X53

0

1

0101 101 = 0X2D

1

ARP

1

ARP

ARP

1

1

ARP

A

?

?

B

VDD

1.150V

1.125V

1.100V

1.075V

1.050V

1.025V

1.000V

0.975V

0.950V

0.925V

0.900V

0.875V

0.850V

0.825V

0.800V

OFF

BACK PANEL

PCI BUS#

SLOT

none

PCI SLOT 4

PCI SLOT 3

PCI SLOT 2

PCI SLOT 1

01

01

01

01

01

PCI DEVICE MAP

CK804

MAC /MAC

PCI-PCI BRIDGE

SATA1

SATA0

IDE

MODEM CODEC

AUDIO CODEC

USB 2.0

USB 1.1

SHAPE TRIM

LDT

SMBUS2

LEGACY SLAVE

LPC

LOGICAL PCI BUS

PCI SLOT 1

PCI SLOT 2

PCI SLOT 3

PCI SLOT 4

PCI SLOT 5

PCI INTERRUPT/IDSEL MAP

IDSEL PIN

DEVICE#

23 0/0

0X0A

25

0X09

24

0X08

23 P_INTY*

0X07

22

0X06

PCI BUS#DEVICE

CK804 LOGICAL

PCI BUS 0

DEVICE#

0X01-0X0F

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

XA

X9

X8

X8

X6

X4

X4

X2

X2

X1

X0

X1

?

X1

?

PCI SLOT

INTA*

P_INTY*

P_INTX*

P_INTW*

P_INTZ*

P_INTY*

PCI SLOT

P_INTZ*

P_INTY*

P_INTX*

P_INTW*

P_INTZ*

FUNCTION

INTB*

-0

0

0

0

0

1

0

1

0

2

0

1

?

0

?

PCI SLOT

PCI SLOT

INTC*

P_INTW*

P_INTX*

P_INTZ*

P_INTW*

P_INTY*

P_INTZ*

P_INTX*

P_INTW* P_INTX*

DEVICE ID

-0X56/57

0X005C

0X0055

0X0054

0X0053

0X0058

0X0059

0X005B

0X005A

0X005F

0X005E

0X0052

0X00D3

0X0050/51

?

REQ/GNT

RESET

INTD*

3/3

2/2

1/1

0/0

SOT23-6

2

1

1

0

0

SOT23

1

6

1

CLOCK

0

3

2

1

0

SOT23-5/SC70

SOT89-5

5

3

2

4

2

1

3

SOT223

5

4

2

3

4

2

1

3

A A

Title

PCI DEVICE MAP

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

NF44X-A7

6 43Wednesday, April 19, 2006

1

1.2

PDF created with pdfFactory Pro trial version www.pdffactory.com

5

D D

C C

B B

+1.2V_HT_CPU

4

TP9 TP /NI

TP13 TP /NI

CPU1A

+1.2V_HT +1.2V_HT_CPU

D29

VLDT_A6

D27

VLDT_A5

D25

VLDT_A4

C28

VLDT_A3

C26

VLDT_A2

B29

VLDT_A1

B27

CTLIP1

CTLIN1

R25

U27

U26

U25

W27

W26

AA27

AA26

AB25

AA25

AC27

AC26

AD25

AC25

U29

W29

AB29

AA29

AB27

AB28

AD29

AC29

AD27

AD28

W25

R27

R26

R29

T25

V25

T27

T28

V29

V27

V28

Y29

Y25

Y27

Y28

T29

VLDT_A0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

HT_UP[15..0]

HT_UP[15..0]16

HT_UP15

HT_UP*15

HT_UP14

HT_UP*14

HT_UP13

HT_UP*13

HT_UP12

HT_UP*12

HT_UP11

HT_UP*11

HT_UP10

HT_UP*10

HT_UP9

HT_UP*9

HT_UP8

HT_UP*8

HT_UP7

HT_UP*7

HT_UP6

HT_UP*6

HT_UP5

HT_UP*5

HT_UP4

HT_UP*4

HT_UP3

HT_UP*3

HT_UP2

HT_UP*2

HT_UP1

HT_UP*1

HT_UP0

HT_UP*0

HT_UP*[15..0]

HT_UP*[15..0]16

HT_UPCLK1

HT_UPCLK116

HT_UPCLK1*

HT_UPCLK1*16

HT_UPCLK0

HT_UPCLK016

HT_UPCLK0*

HT_UPCLK0*16

R362 49.9 1%

R363 49.9 1%

HT_UPCNTL

HT_UPCNTL16

HT_UPCNTL*

HT_UPCNTL*16

+1.2V_HT

+1.2V_HT_CPU

3

A

B

VLDT0_B6

VLDT0_B5

VLDT0_B4

VLDT0_B3

VLDT0_B2

VLDT0_B1

VLDT0_B0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

AH29

AH27

AG28

AG26

AF29

AE28

AF25

N26

N27

L25

M25

L26

L27

J25

K25

G25

H25

G26

G27

E25

F25

E26

E27

N29

P29

M28

M27

L29

M29

K28

K27

H28

H27

G29

H29

F28

F27

E29

F29

J26

J27

J29

K29

N25

P25

P28

P27

BGA754S-DIP

+1.2V_HT_CPU

HT_DWN[15..0]

HT_DWN15

HT_DWN*15

HT_DWN14

HT_DWN*14

HT_DWN13

HT_DWN*13

HT_DWN12

HT_DWN*12

HT_DWN11

HT_DWN*11

HT_DWN10

HT_DWN*10

HT_DWN9

HT_DWN*9

HT_DWN8

HT_DWN*8

HT_DWN7

HT_DWN*7

HT_DWN6

HT_DWN*6

HT_DWN5

HT_DWN*5

HT_DWN4

HT_DWN*4

HT_DWN3

HT_DWN*3

HT_DWN2

HT_DWN*2

HT_DWN1

HT_DWN*1

HT_DWN0

HT_DWN*0

HT_DWN*[15..0]

HT_DWNCLK1

HT_DWNCLK1*

HT_DWNCLK0

HT_DWNCLK0*

HT_DWNCNTL

HT_DWNCNTL*

C443

C442

1UF 16V 0805 Y5V

1UF 10V Y5V

HT_DWN[15..0] 16

HT_DWN*[15..0] 16

HT_DWNCLK1 16

HT_DWNCLK1* 16

HT_DWNCLK0 16

HT_DWNCLK0* 16

HT_DWNCNTL 16

HT_DWNCNTL* 16

2

LAYOUT: Place HT bypass caps on topside

near unconnected Clawhammer HT Link

+1.2V_HT

C444

C446

1UF 16V 0805 Y5V

C447

0.1UF 25V Y5V /NI

1UF 10V Y5V

1

A A

Title

K8 HT

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

NF44X-A7

1

1.2

7 43Wednesday, April 19, 2006

PDF created with pdfFactory Pro trial version www.pdffactory.com

5

CPU1B

AE13

DQS17

DQS16

DQS15

DQS14

DQS13

DQS12

DQS11

DQS10

DQS9

DQS8

DQS7

DQS6

DQS5

DQS4

DQS3

DQS2

DQS1

DQS0

MEMZN

MEMZP

MD63

MD62

MD61

MD60

MD59

MD58

MD57

MD56

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

MD47

MD46

MD45

MD44

MD43

MD42

MD41

MD40

MD39

MD38

MD37

MD36

MD35

MD34

MD33

MD32

MD31

MD30

MD29

MD28

MD27

MD26

MD25

MD24

MD23

MD22

MD21

MD20

MD19

MD18

MD17

MD16

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

VTT_SENSE

AG12

MEMVREF1

D14

MEMZN

C14

MEMZP

A16

MEMDATA63

B15

MEMDATA62

A12

MEMDATA61

B11

MEMDATA60

A17

MEMDATA59

A15

MEMDATA58

C13

MEMDATA57

A11

MEMDATA56

A10

MEMDATA55

B9

MEMDATA54

C7

MEMDATA53

A6

MEMDATA52

C11

MEMDATA51

A9

MEMDATA50

A5

MEMDATA49

B5

MEMDATA48

C5

MEMDATA47

A4

MEMDATA46

E2

MEMDATA45

E1

MEMDATA44

A3

MEMDATA43

B3

MEMDATA42

E3

MEMDATA41

F1

MEMDATA40

G2

MEMDATA39

G1

MEMDATA38

L3

MEMDATA37

L1

MEMDATA36

G3

MEMDATA35

J2

MEMDATA34

L2

MEMDATA33

M1

MEMDATA32

W1

MEMDATA31

W3

MEMDATA30

AC1

MEMDATA29

AC3

MEMDATA28

W2

MEMDATA27

Y1

MEMDATA26

AC2

MEMDATA25

AD1

MEMDATA24

AE1

MEMDATA23

AE3

MEMDATA22

AG3

MEMDATA21

AJ4

MEMDATA20

AE2

MEMDATA19

AF1

MEMDATA18

AH3

MEMDATA17

AJ3

MEMDATA16

AJ5

MEMDATA15

AJ6

MEMDATA14

AJ7

MEMDATA13

AH9

MEMDATA12

AG5

MEMDATA11

AH5

MEMDATA10

AJ9

MEMDATA9

AJ10

MEMDATA8

AH11

MEMDATA7

AJ11

MEMDATA6

AH15

MEMDATA5

AJ15

MEMDATA4

AG11

MEMDATA3

AJ12

MEMDATA2

AJ14

MEMDATA1

AJ16

MEMDATA0

R1

MEMDQS17

A13

MEMDQS16

A7

MEMDQS15

C2

MEMDQS14

H1

MEMDQS13

AA1

MEMDQS12

AG1

MEMDQS11

AH7

MEMDQS10

AH13

MEMDQS9

T1

MEMDQS8

A14

MEMDQS7

A8

MEMDQS6

D1

MEMDQS5

J1

MEMDQS4

AB1

MEMDQS3

AJ2

MEMDQS2

AJ8

MEMDQS1

AJ13

MEMDQS0

+2.5VDIMM

MD[63:0]15

TP2TP /NI

R364 33 1%

R365 33 1%

DQS[17:0]13,14,15

+1.25VREF_CLAW

D D

C C

B B

A A

LAYOUT: 10/5/10

LAYOUT: PLACE WITHIN 1 INCH OF CPU

4

VTT_A4

VTT_A1

VTT_A2

VTT_A3

VTT_B1

VTT_B2

VTT_B3

VTT_B4

MEMRESET_L

MEMCKEA

MEMCKEB

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

RSVD_MEMADDA15

RSVD_MEMADDA14

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

RSVD_MEMADDB_B15

RSVD_MEMADDB_B14

MEMADDB_B13

MEMADDB_B12

MEMADDB_B11

MEMADDB_B10

MEMADDB_B9

MEMADDB_B8

MEMADDB_B7

MEMADDB_B6

MEMADDB_B5

MEMADDB_B4

MEMADDB_B3

MEMADDB_B2

MEMADDB_B1

MEMADDB_B0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

BGA754S-DIP

3

D17

+1.25VTT

A18

B17

C17

AF16

AG16

AH16

AJ17

AG10

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

-CS3

D6

-CS2

E6

-CS1

C4

-CS0

E5

H5

D4

G5

K3

H3

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E14

D12

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

MAA13

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

MAB13

MAB12

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

MECC7

MECC6

MECC5

MECC4

MECC3

MECC2

MECC1

MECC0

DCLK7+

DCLK7DCLK6+

DCLK6DCLK5+

DCLK5DCLK4+

DCLK4-

DCLK1+

DCLK1DCLK0+

DCLK0-

CKE0 13,14,15

CKE1 13,14,15

DCLK7+ 13,15

DCLK7- 13,15

DCLK6+ 14,15

DCLK6- 14,15

DCLK5+ 13,15

DCLK5- 13,15

DCLK4+ 14,15

DCLK4- 14,15

DCLK1+ 14,15

DCLK1- 14,15

DCLK0+ 13,15

DCLK0- 13,15

-CS3 14,15

-CS2 14,15

-CS1 13,15

-CS0 13,15

-SRASA 13,15

-SCASA 13,15

-SWEA 13,15

MEMBAA1 13,15

MEMBAA0 13,15

MAA[13:0] 13,15

-SRASB 14,15

-SCASB 14,15

-SWEB 14,15

MEMBAB1 14,15

MEMBAB0 14,15

MAB[13:0] 14,15

MECC[7:0] 15

Clawhammer DDR Interface

+1.25VREF_CLAW

+2.5VDIMM

Change

to 1%

LAYOUT: Place on the bottom of the

board.

R366

110 1%

110 1%

2

C448

0.01UF 50V X7R

C449

0.01UF 50V X7R

C450

0.1UF 25V Y5V

C452

C451R367

33P 50V NPO

0.1UF 25V Y5V /NI

LAYOUT: Place 39pF

EMI cap near output

C453

0.1UF 25V Y5V

+1.25VREF_CLAW

C454

1000P 50V X7R /NI

LAYOUT: Locate caps

close to socket.

1

Title

K8 CNTL/STRAPS

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

NF44X-A7

1

1.2

8 43Wednesday, April 19, 2006

PDF created with pdfFactory Pro trial version www.pdffactory.com

5

CPU_RST*

CPU_PWRGD

HT_STOP*

R372 44.2 1%

R373 44.2 1%

CPU_CORE_FB

CPU_CORE_FB-

R374 169 1%

BPSCLK+

BPSCLK-

DBRDY

TMS

TCK

-TRST

TDI

SINCHN

-BRN

CLAW_ANALOG3

CLAW_ANALOG2

CLAW_ANALOG1

CLAW_ANALOG0

LVREF1

LVREF0

VDDIOFB_HCPUCKVDDIOFB_L

CPUCK+

CPUCK-

+2.5VDDA

AH25

AJ25

AF20

AE18

AJ27

AF27

AE26

A23

A24

B23

AE12

AF12

AE11

AJ21

AH21

AJ23

AH23

AE24

AF24

C16

AG15

AH17

C15

E20

E17

B21

A21

C18

A19

A28

AJ28

AE23

AF23

AF22

AF21

C1

J3

R3

AA2

D3

AG2

B18

AH1

AE21

C20

AG4

C6

AG6

AE9

AG9

D D

PLACE WITHIN 1 INCH

10/5/10

TP3TP /NI

TP1TP /NI

ROUTE AS DIF 20/5/5/5/20

LAYOUT: PLACE 169 OHM WITHIN 0.5INCH OF CPU

C C

B B

VDDIO_SENSE40

A A

CPUCK+

CPU_CLK*16

TP /NI

TP /NI

TP /NI

TP /NI

TP /NI

+1.2V_HT_CPU

CPU_CLK16

TP6

TP4

TP8

TP7

TP5

C456

47P 50V NPO /NI

CPU_RST*16

CPU_PWRGD16

HT_STOP*16

CPU_CORE_FB39

CPU_CORE_FB-39

ROUTE AS DIFF PAIR

TP10 TP /NI

10/5/10 10

TP11 TP /NI

VDDIO_SENSE40

3900P 50V X7RC457

3900P 50V X7RC458

+1.25VTT

CPU_RST*

CPU_PWRGD

HT_STOP*

CPU_CORE_FB

CPU_CORE_FB-

VDDIO_SENSE

TP12 TP /NI

4

LAYOUT: Route +2.5VDDA approx. 50mil wide

and 500mils long.(Reference to ground)

CPU1C

A20

VDDA1

VDDA2

RESET_L

PWROK

LDTSTOP_L

L0_REF1

L0_REF0

COREFB_H

COREFB_L

CORE_SENSE

VDDIOFB_H

VDDIOFB_L

VDDIO_SENSE

CLKIN_H

CLKIN_L

NC

NC

NC

NC

VTT_A5

VTT_B5

DBRDY

NC

TMS

TCK

TRST_L

TDI

NC

NC

KEY1

KEY0

NC

NC

NC

NC

FREE29

FREE31

FREE33

FREE35

FREE1

FREE37

FREE4

FREE38

FREE41

FREE7

FREE11

FREE12

FREE13

FREE14

FREE40

BGA754S-DIP

THERMTRIP_L

THERMDA

THERMDC

G_FBCLKOUT_H

G_FBCLKOUT_L

DBREQ_L

RSVD_SCL

RSVD_SDA

FREE26

FREE28

FREE30

FREE32

FREE34

FREE36

FREE10

FREE18

FREE19

FREE42

FREE24

FREE25

FREE27

A26

A27

AG13

VID4

AF14

VID3

AG14

VID2

AF15

VID1

AE15

VID0

AG18

NC

AH18

NC

AG17

NC

AJ18

NC

AH19

AJ19

AE19

D20

NC

C21

NC

D18

NC

C19

NC

B19

NC

A22

TDO

AF18

NC

D22

C22

B13

B7

C3

K1

R2

AA3

F3

C23

AG7

AE22

C24

A25

C9

3

+3.3V_STBY

U16

1

VDD

2

C455

2200P 50V X7R /NI

VID4

VID3

VID2

VID1

VID0

FBCLKOUT+

FBCLKOUT-

-DBREQ

SCANCLK1

SCANCLK2

SCANEN

SCANSHENB

SCANSHENA

TDO

R376 0 /NI

D+

3

D-

4 5

T_CRIT_A#VSS

LM90 MSOP8 /NI

R368 0 /NI

R369 680

R370 0

R371 0

K8_VID4 38

K8_VID3 38

K8_VID2 38

K8_VID1 38

K8_VID0 38

BP1

BP0

80.6 1%-->82 1%

R375 80.6 1%

LAYOUT: Route differentially

with 20/8/5/8/20

LAYOUT: PLACE WITHIN 0.5 INCH OF CPU

+2.5VDIMM

8

SMB_CL

7

SMB_DA

6

ALERT#

CHIP_THERM* 20,29

CPU_THERMTRIP* 16

+2.5VDDA

CPU_THERMDA 29

CPU_THERMDC 29,30

SMB_SCL

SMB_SDA

SMB_ALLERT-

ROUTING : 10/10/10

SMB_SCL 20,22,23,24,25,38

SMB_SDA 20,22,23,24,25,38

SMB_ALLERT* 29

SCANSHENA

SCANSHENB

SCANCLK1

SCANCLK2

SCANEN

BP1

BP0

BPSCLK+

BPSCLK-

LVREF0

LVREF1

+2.5VDDA

+2.5VDDA

+2.5VDDA

1UF 10V Y5VC461

RN106

1 2

3 4

5 6

7 8

680 8P4R

RN107

680 8P4R

R377 820

R378 820

1000P 50V X7RC459

1000P 50V X7RC460

2

78

56

34

12

+2.5VDIMM

RN110

680 8P4R

1 2

3 4

5 6

7 8

R416 680

R417 680

CPU_PWRGD

-DBREQ

DBRDY

TCK

HT_STOP*

CPU_RST*

RN108

680 8P4R

TDI

-TRST

TMS

TDO

Modify circuit

SINCHN

-BRN

CLAW_ANALOG3

CLAW_ANALOG2

CLAW_ANALOG1

CLAW_ANALOG0

+2.5VDDA

78

R379 680

R380 680

123456

+2.5VDDA

RN109

680 8P4R

+2.5VDIMM

78

56

34

12

1

Title

K8 DDR MEM 0-63

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

NF44X-A7

1

1.2

9 43Wednesday, April 19, 2006

PDF created with pdfFactory Pro trial version www.pdffactory.com

5

CPU1D

+V_CPU +2.5VDIMM

L7

VDD1

AC15

VDD2

H18

VDD3

B20

VDD4

E21

VDD5

H22

VDD6

J23

VDD7

AB14

AA15

AB16

AA17

AC17

AE17

AB18

AD18

AG19

AC19

AA19

AB20

AD20

AA21

AC21

AB22

AD22

AA23

AC23

AB24

AD24

AH24

AE25

H24

F26

V10

G13

K14

Y14

G15

J15

H16

K16

Y16

G17

J17

F18

K18

Y18

E19

G19

J19

F20

H20

K20

M20

P20

T20

V20

Y20

G21

J21

L21

N21

R21

U21

W21

F22

K22

M22

P22

T22

V22

Y22

E23

G23

L23

N23

R23

U23

W23

B24

D24

F24

K24

M24

P24

T24

V24

Y24

K26

P26

V26

N7

L9

5

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

VDD77

VDD78

VDD79

VDD80

VDD81

VDD82

VDD83

VDD84

VDD85

VDD86

VDD87

VDD88

VDD89

VDD90

VDD91

VDD92

BGA754S-DIP

D D

C C

B B

A A

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VDDIO46

VDDIO47

VDDIO48

VDDIO49

VDDIO50

VDDIO6

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

VDD133

VDD93

VDD94

VDD95

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

+V_CPU

N28

U28

AA28

AE27

R7

U7

W7

K8

M8

P8

T8

V8

Y8

J9

N9

R9

U9

W9

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

4

CPU1E

B2

VSS1

AH20

VSS3

AB21

VSS4

W22

VSS5

M23

VSS6

L24

VSS7

AG25

VSS8

AG27

VSS9

D2

VSS10

AF2

VSS11

W6

VSS12

Y7

VSS13

AA8

VSS14

AB9

VSS15

AA10

VSS16

J12

VSS17

B14

VSS18

Y15

VSS19

AE16

VSS20

J18

VSS21

G20

VSS22

R20

VSS23

U20

VSS24

W20

VSS25

AA20

VSS26

AC20

VSS27

AE20

VSS28

AG20

VSS29

AJ20

VSS30

D21

VSS31

F21

VSS32

H21

VSS33

K21

VSS34

M21

VSS35

P21

VSS36

T21

VSS37

V21

VSS38

Y21

VSS39

AD21

VSS40

AG21

VSS41

B22

VSS42

E22

VSS43

G22

VSS44

J22

VSS45

L22

VSS46

N22

VSS47

R22

VSS48

U22

VSS49

AG29

VSS50

AA22

VSS51

AC22

VSS52

AG22

VSS53

AH22

VSS54

AJ22

VSS55

D23

VSS56

F23

VSS57

H23

VSS58

K23

VSS59

P23

VSS60

T23

VSS61

V23

VSS62

Y23

VSS63

AB23

VSS64

AD23

VSS65

AG23

VSS66

E24

VSS67

G24

VSS68

J24

VSS69

N24

VSS70

R24

VSS71

U24

VSS72

W24

VSS73

AA24

VSS74

AC24

VSS75

AG24

VSS76

AJ24

VSS77

B25

VSS78

C25

VSS79

B26

VSS80

D26

VSS81

H26

VSS82

M26

VSS83

T26

VSS84

Y26

VSS85

AD26

VSS86

AF26

VSS87

AH26

VSS88

C27

VSS89

B28

VSS90

D28

VSS91

G28

VSS92

F15

VSS187

H15

VSS188

AB17

VSS206

AD17

VSS207

B16

VSS208

G18

VSS209

AA18

VSS210

AC18

VSS211

D19

VSS212

F19

VSS213

H19

VSS214

K19

VSS215

Y19

VSS216

AB19

VSS217

AD19

VSS218

AF19

VSS219

J20

VSS220

L20

VSS221

N20

VSS222

BGA754S-DIP

4

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS189

VSS190

VSS191

VSS192

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS223

VSS201

VSS202

VSS203

VSS204

VSS205

3

L28

R28

W28

AC28

AF28

AH28

C29

F2

H2

K2

M2

P2

T2

V2

Y2

AB2

AD2

AH2

B4

AH4

B6

G6

J6

L6

N6

R6

U6

AA6

AC6

AH6

F7

H7

K7

M7

P7

T7

V7

AB7

AD7

B8

G8

J8

L8

N8

R8

U8

W8

AC8

AH8

F9

H9

K9

M9

P9

T9

V9

Y9

AD9

B10

G10

J10

L10

N10

R10

U10

W10

AC10

AH10

F11

H11

K11

Y11

AB11

AD11

B12

G12

AA12

AC12

AH12

F13

H13

K13

Y13

AB13

AD13

AF17

G14

J14

AA14

AC14

AE14

D16

E15

K15

AB15

AD15

AH14

E16

G16

J16

AA16

AC16

AE29

AJ26

E18

F17

H17

K17

Y17

Clawhammer Power and Ground Connections

+V_CPU

0.1UF 25V Y5V /NIC462

1UF 16V 0805 Y5VC463

1UF 16V 0805 Y5V /NIC464

1UF 16V 0805 Y5V /NIC465

1UF 16V 0805 Y5VC467

LAYOUT: Place 6 EMI

caps along bottom right

side of CPU,2 in middle

of HT link,and 12 along

bottom left side of CPU.

0.1UF 25V Y5VC585

0.1UF 25V Y5VC586

1UF 16V 0805 Y5V /NIC469

+V_CPU

+2.5VDIMM

1UF 16V 0805 Y5VC488

1UF 16V 0805 Y5V /NIC490

3

2

+V_CPU

C56 1UF 16V 0805 Y5V

C466 0.1UF 25V Y5V

LAYOUT: Place in uPGA

socket cavity.

LAYOUT: Place 1 cap every 1~1.5" along VCORE perimiter.

0.1UF 25V Y5V /NIC470

0.1UF 25V Y5VC472

+V_CPU

0.1UF 25V Y5VC584

0.1UF 25V Y5VC583

0.1UF 25V Y5VC474

1UF 16V 0805 Y5V /NIC487

1UF 16V 0805 Y5V /NIC491

Title

Size Document Number Rev

Custom

2

Date: Sheet of

1

LAYOUT: Place

1000p caps

between VRM &

CPU..

+2.5VDIMM+2.5VDIMM+V_CPU

0.1UF 25V Y5VC468

0.1UF 25V Y5VC473

+2.5VDIMM

C475 10UF 10V 0805 Y5V /NI

C476 1UF 16V 0805 Y5V /NI

C477 1UF 16V 0805 Y5V /NI

C482 1UF 16V 0805 Y5V /NI

LAYOUT: Located close to socket

K8 DDR MEM 64-127

NF44X-A7

1

1.2

10 43Wednesday, April 19, 2006

PDF created with pdfFactory Pro trial version www.pdffactory.com

5

D D

C C

100UF 16V 5X11 2mm /NI

B B

4

C51 2.5V

2.5V @ 500MA AMPS MAX

C494

CT41

1UF 16V 0805 Y5V /NI

AZ1117H-ADJ SOT-223

Vout=Vref (1.25V) X ( 1+R2/R1 )

=2.5V

3

+V_CPU

ADD FOR EMI

PLACE NEAR C80

C103

0.1UF 25V Y5V /NI

+5V

OIA

Q62

+2.5VDDA

C495R381

49.9 1%

R382

54.9 1%

CT42

100UF 16V 5X11 2mm /NI

1UF 16V 0805 Y5V

R1

R2

2

1

A A

Title

AMD-K8-POWER

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

NF44X-A7

11 43Wednesday, April 19, 2006

1

1.2

PDF created with pdfFactory Pro trial version www.pdffactory.com

5

D D

4

3

2

1

+V_CPU

12

C122

C C

10UF 10V 0805 Y5V /NI

+V_CPU

12

BC19

1UF 16V 0805 Y5V /NI

12

BC16

1UF 16V 0805 Y5V /NI

12

BC1

0.1UF 25V Y5V

PLACE TOP SIDE UNDER CPU HEATSINK

12

C581

10UF 10V 0805 Y5V /NI

12

BC20

1UF 16V 0805 Y5V /NI

+2.5VDIMM

PLACE TOP SIDE UNDER CPU HEATSINK NEXT TO MEM CLKS

12

12

C167

0.1UF 25V Y5V /NI

C112

0.1UF 25V Y5V /NI

PLACE NEAR CPU ON EITHER SIDE

+1.25VTT

12

12

C9

C75

0.1UF 25V Y5V /NI

10UF 10V 0805 Y5V /NI

+2.5VDIMM

+1.2V_HT

12

C191

0.1UF 25V Y5V /NI

B B

A A

Title

CPU DECOUPLING

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

NF44X-A7

12 43Wednesday, April 19, 2006

1

1.2

PDF created with pdfFactory Pro trial version www.pdffactory.com

5

DIMM1

-CS08,15

-CS18,15

-SWEA8,15

-SCASA8,15

-SRASA8,15

CKE08,14,15

CKE18,14,15

DCLK5+8,15

DCLK5-8,15

DCLK0+8,15

DCLK0-8,15

DCLK7+8,15

DCLK7-8,15

SMBDT14,20

SMBCK14,20

+1.25VREF_MEM

MEMBAA0

MEMBAA1

+2.5VDIMM

R385 0 /NI

FETEN14

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

-SWEA

-SCASA

-SRASA

CKE0

CKE1

DCLK5+

DCLK5DCLK0+

DCLK0DCLK7+

DCLK7-

SMBDT

SMBCK

DQS_9

DQS_10

DQS_11

DQS_12

DQS_13

DQS_14

DQS_15

DQS_16

DQS_17

DQS_0

DQS_1

DQS_2

DQS_3

DQS_4

DQS_5

DQS_6

DQS_7

DQS_8

FETEN

D D

C C

B B

MAA[13:0]8,15

MEMBAA08,15

MEMBAA18,15

DQS_[17:0]8,14,15

DQS_[17:0]8,14,15

SMB_MEM_SDA14,20

SMB_MEM_SCL14,20

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

157

158

71

163

97

107

119

129

149

159

169

177

140

63

65

154

21

111

16

17

137

138

76

75

5

14

25

36

56

67

78

86

47

91

92

181

182

183

1

82

184

9

10

101

102

173

103

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

CS0

CS1

NC/CS2

NC/CS3

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

WE

CAS

RAS

CKE0

CKE1

CK0/DNU

CK0/DNU

CK1

CK1

CK2/DNU

CK2/DNU

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

SDA

SCL

SA0

SA1

SA2

VREF

VDDID

VDDSPD

NC

NC/RESET

NC

NC

NC

NC/FETEN

4

15223054627796

VDDQ

VDDQ

VDDQ

+2.5VDIMM

104

112

128

136

143

156

164

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

GND

GND

GND

3111826344250586674818993

GND

172

180738467085108

VDD

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

100

116

VDD

VDD

GND

GND

124

132

139

120

148

168

VDD

VDD

VDD

VDD

VDD

GND

GND

GND

GND

GND

DDRAM184 NYLON LOTES B

145

152

160

176

3

DIMM1

VDD

MD_0

2

D0

MD_1

4

D1

MD_2

6

D2

MD_3

8

D3

MD_4

94

D4

MD_5

95

D5

MD_6

98

D6

MD_7

99

D7

MD_8

12

D8

MD_9

13

D9

MD_10

19

D10

MD_11

20

D11

MD_12

105

D12

MD_13

106

D13

MD_14

109

D14

MD_15

110

D15

MD_16

23

D16

MD_17

24

D17

MD_18

28

D18

MD_19

31

D19

MD_20

114

D20

MD_21

117

D21

MD_22

121

D22

MD_23

123

D23

MD_24

33

D24

MD_25

35

D25

MD_26

39

D26

MD_27

40

D27

MD_28

126

D28

MD_29

127

D29

MD_30

131

D30

MD_31

133

D31

MD_32

53

D32

MD_33

55

D33

MD_34

57

D34

MD_35

60

D35

MD_36

146

D36

MD_37

147

D37

MD_38

150

D38

MD_39

151

D39

MD_40

61

D40

MD_41

64

D41

MD_42

68

D42

MD_43

69

D43

MD_44

153

D44

MD_45

155

D45

MD_46

161

D46

MD_47

162

D47

MD_48

72

D48

MD_49

73

D49

MD_50

79

D50

MD_51

80

D51

MD_52

165

D52

MD_53

166

D53

MD_54

170

D54

MD_55

171

D55

MD_56

83

D56

MD_57

84

D57

MD_58

87

D58

MD_59

88

D59

MD_60

174

D60

MD_61

175

D61

MD_62

178

D62

MD_63

179

D63

MECC_0

44

CB0

MECC_1

45

CB1

MECC_2

49

CB2

MECC_3

51

CB3

MECC_4

134

CB4

MECC_5

135

CB5

MECC_6

142

CB6

MECC_7

144

CB7

R386 4.7K

90

WP

MD_[63:0] 14,15

+1.25VREF_MEM

MECC_[7:0] 14,15

+2.5VDIMM

Change

to 1%

Change

to 1%

+2.5VDIMM

R383

100 1%

R384

100 1%

2

C496

0.01UF 50V X7R

C497

0.1UF 25V Y5V

LAYOUT: Place 39pf

EMI cap near output

C500

33P 50V NPO

1

+1.25VREF_MEM

LAYOUT: Locate caps

close to DIMMs.

C498

C499

1000P 50V X7R /NI

0.1UF 25V Y5V /NI

A A

Title

DDR DIMM1

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

NF44X-A7

1

1.2

13 43Wednesday, April 19, 2006

PDF created with pdfFactory Pro trial version www.pdffactory.com

Loading...

Loading...