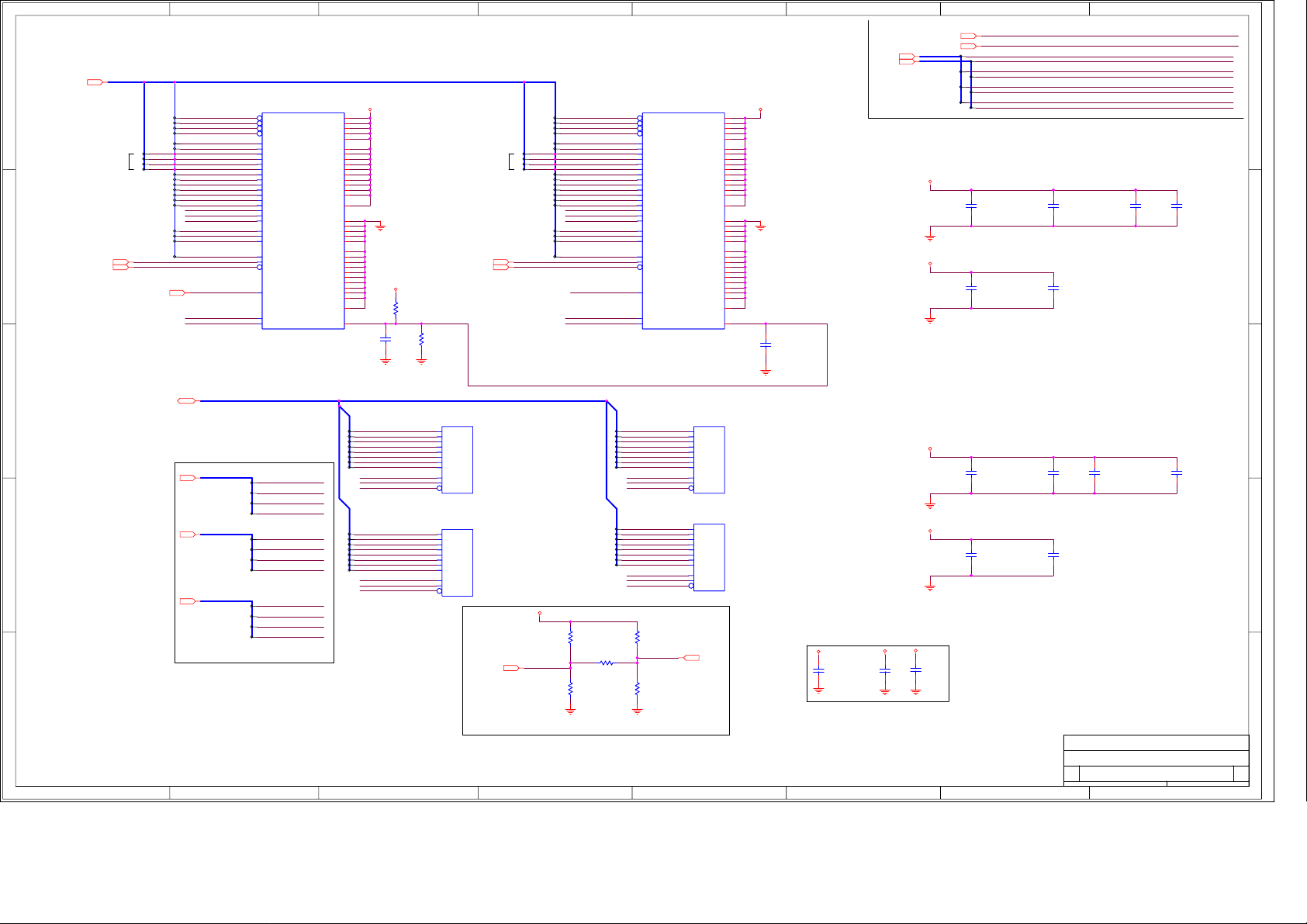

Gigabyte gv-nx73l128t-rh-le_pvt_10 Schematics

P381: G72, DDR2 MEMORY 16Mx16

HGFEDCBA

1

1

Page1: P381 Overview

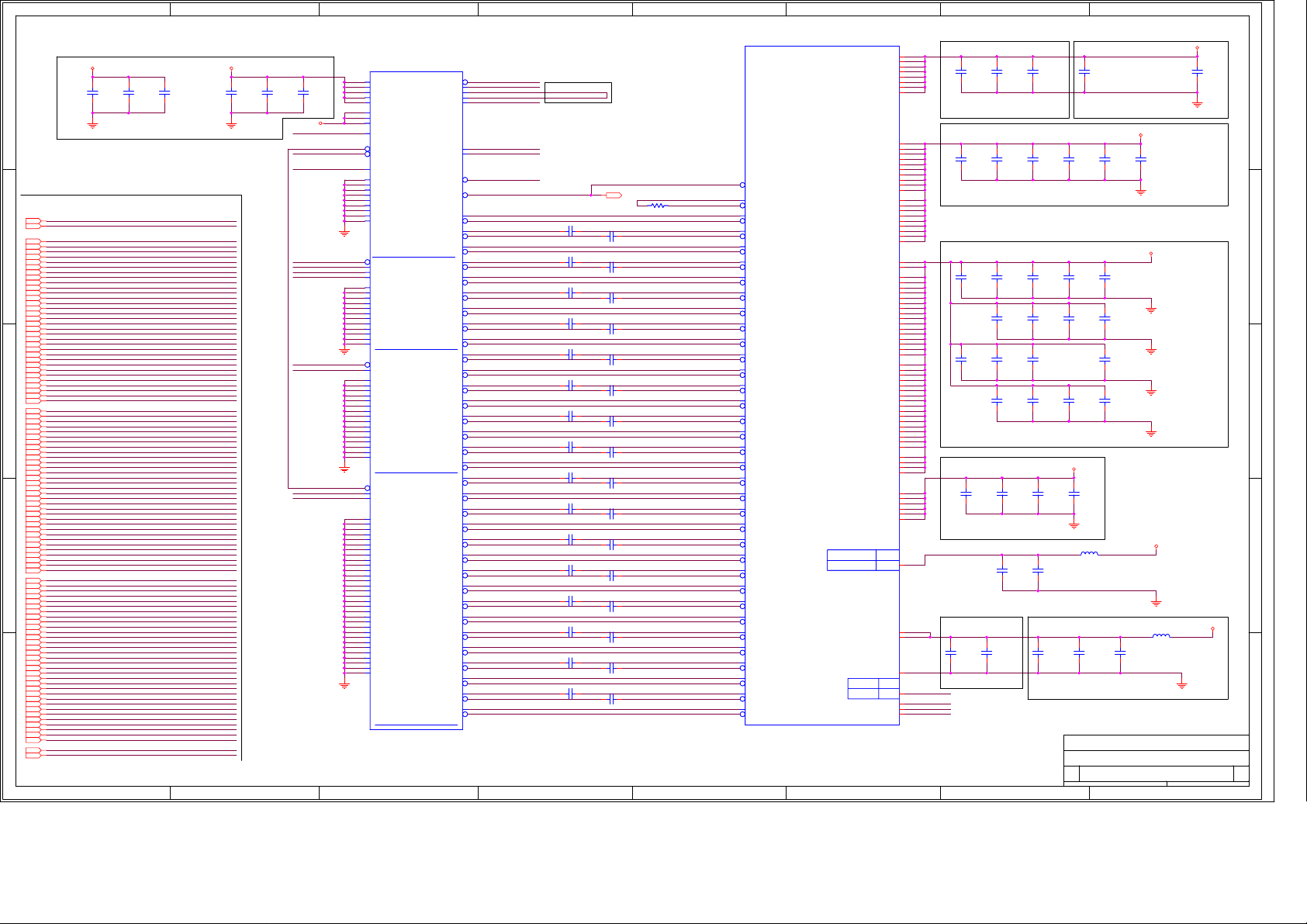

Page2: PCI Express Interface

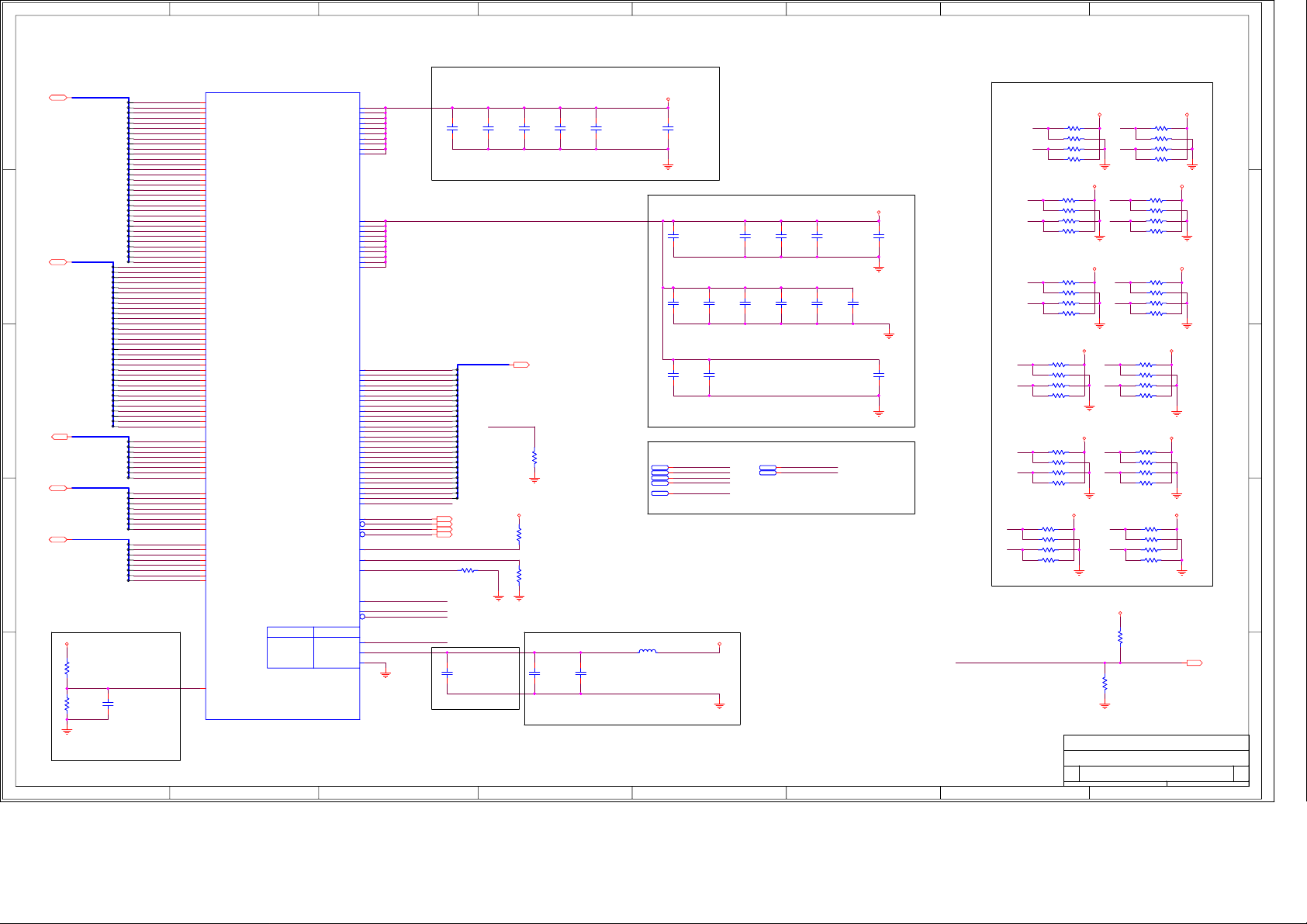

Page3: Frame Buffer Interface

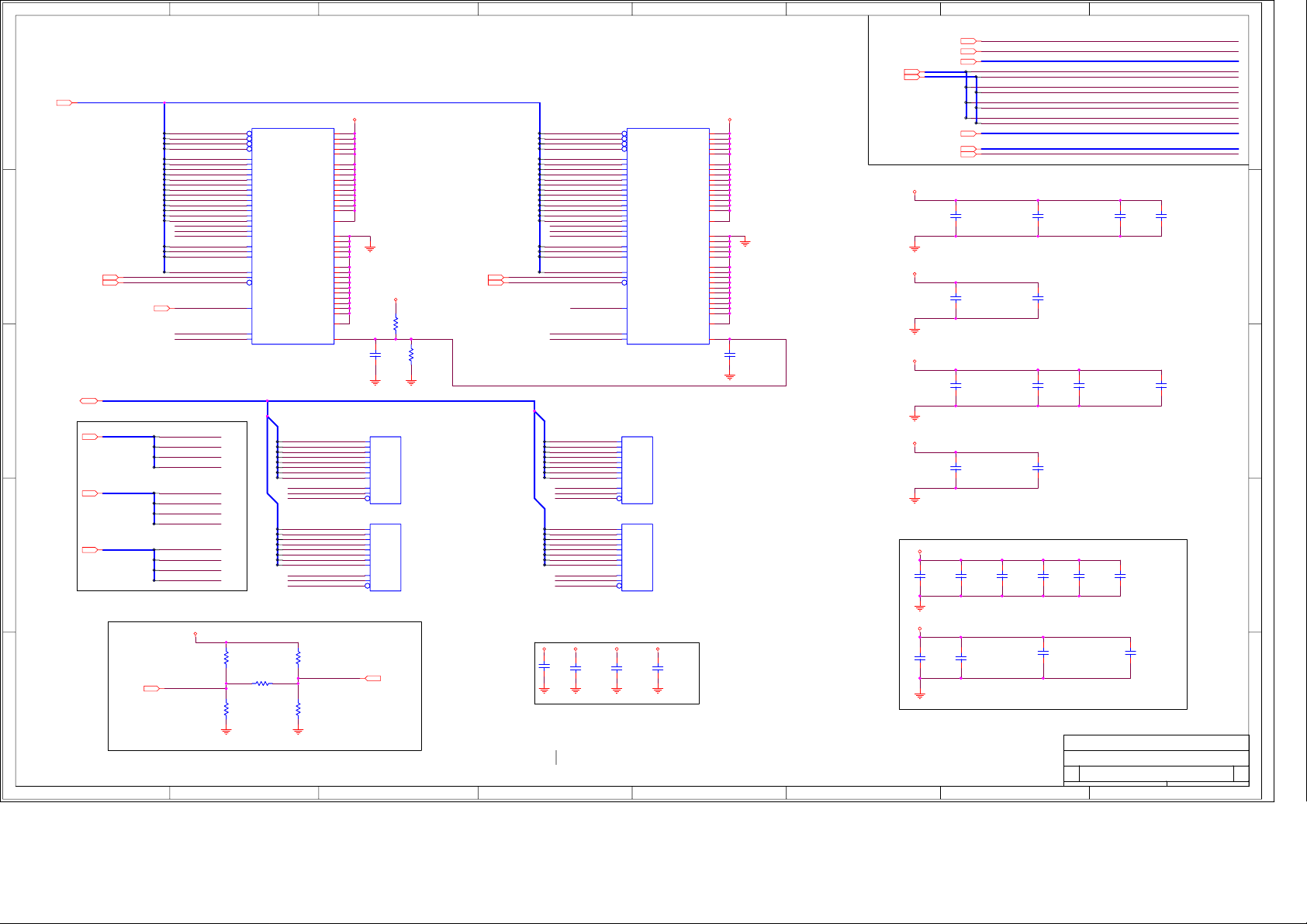

Page4: Memory 1st bank 0..31

Page5: Memory 1st bank 32..63

Page6: DACA

Page7: DACB, VGA Output/ TV Out

2

Page8: S-Video Minidin Connector

Page9: TMDS Interface

2

Page10: MIOA, MIOB Interface, LPC-ROM

Page11: STRAPS, Mechanical Parts

Page12: XTAL, GPIO, BIOS, FAN, JTAG, THERMAL

Page13: PowerSupplyI: NVVDD, FBVDDQ

Page14: PowerSupplyII: 5V, DDC5V, F3V3, TMDS_PLLVDD

3

VARIANT ASSEMBLY

SKU

BASE

B

SKU00

1

2

SKU01

3

SKU02

4

SKU03

SKU04

5

<UNDEFINED>

6

7

<UNDEFINED>

8

<UNDEFINED>

9

<UNDEFINED>

10

<UNDEFINED>

11

4

12

13

14

15

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

NVPN

600-10381-xxxx-000

600-10381-0000-100

600-10381-0001-100

600-10381-0002-100

600-10381-0003-100

600-10381-0004-100

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

P381: G72/G3-64, 32 BIT DDR2 MEMORY, VGA+SDTV

P381: G72/G3-64, 64 BIT DDR2 MEMORY, VGA+SDTV

P381: G72/G3-64, 32 BIT DDR2 MEMORY, DVI+SDTV

P381: G72/G3-64, 64 BIT DDR2 MEMORY, DVI+SDTV

P381: G72/G3-64, 64 BIT DDR2 MEMORY, VGA+DVI+SDTV

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A B D F H

5

GIGABYTE

GIGABYTE

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

E GC

Date: Sheet

P381 : G72

P381 : G72

P381 : G72

GV-NX73L128T-RH-LE

GV-NX73L128T-RH-LE

GV-NX73L128T-RH-LE

Thursday, August 03, 2006

Thursday, August 03, 2006

Thursday, August 03, 2006

GIGABYTE

1.0

1.0

1.0

of

115

of

115

of

115

PEX-Interface

PLACE NEAR FINGERS

3V3

C21

C21

C22

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C22

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C23

C23

1UF

1UF

10V

1

10V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

GND

Net Name

PEX_TSTCLK

IN

PEX_TSTCLK*

IN

PEX_TX0

IN

2

3

4

5

PEX_TX0*

IN

PEX_TX1

IN

PEX_TX1*

IN

PEX_TX2

IN

PEX_TX2*

IN

PEX_TX3

IN

PEX_TX3*

IN

PEX_TX4

IN

PEX_TX4*

IN

PEX_TX5

IN

PEX_TX5*

IN

PEX_TX6

IN

PEX_TX6*

IN

PEX_TX7

IN

PEX_TX7*

IN

PEX_TX8

IN

PEX_TX8*

IN

PEX_TX9

IN

PEX_TX9*

IN

PEX_TX10

IN

PEX_TX10*

IN

PEX_TX11

IN

PEX_TX11*

IN

PEX_TX12

IN

PEX_TX12*

IN

PEX_TX13

IN

PEX_TX13*

IN

PEX_TX14

IN

PEX_TX14*

IN

PEX_TX15

IN

PEX_TX15*

IN

PEX_TXX0

IN

PEX_TXX0*

IN

PEX_TXX1

IN

PEX_TXX1*

IN

PEX_TXX2

IN

PEX_TXX2*

IN

PEX_TXX3

IN

PEX_TXX3*

IN

PEX_TXX4

IN

PEX_TXX4*

IN

PEX_TXX5

IN

PEX_TXX5*

IN

PEX_TXX6

IN

PEX_TXX6*

IN

PEX_TXX7

IN

PEX_TXX7*

IN

PEX_TXX8

IN

PEX_TXX8*

IN

PEX_TXX9

IN

IN

PEX_TXX10

IN

PEX_TXX10*

IN

PEX_TXX11

IN

PEX_TXX11*

IN

PEX_TXX12

IN

PEX_TXX12*

IN

PEX_TXX13

IN

PEX_TXX13*

IN

PEX_TXX14

IN

PEX_TXX14*

IN

PEX_TXX15

IN

PEX_TXX15*

IN

PEX_RX0

IN

PEX_RX0*

IN

PEX_RX1

IN

PEX_RX1*

IN

PEX_RX2

IN

PEX_RX2*

IN

PEX_RX3

IN

PEX_RX3*

IN

PEX_RX4

IN

PEX_RX4*

IN

PEX_RX5

IN

PEX_RX5*

IN

PEX_RX6

IN

PEX_RX6*

IN

PEX_RX7

IN

PEX_RX7*

IN

PEX_RX8

IN

PEX_RX8*

IN

PEX_RX9

IN

PEX_RX9*

IN

PEX_RX10

IN

PEX_RX10*

IN

PEX_RX11

IN

PEX_RX11*

IN

PEX_RX12

IN

PEX_RX12*

IN

PEX_RX13

IN

PEX_RX13*

IN

PEX_RX14

IN

PEX_RX14*

IN

PEX_RX15

IN

PEX_RX15*

IN

PEX_REFCLK

IN

PEX_REFCLK*

IN

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

PEX_TX0 1 100DIFF

PEX_TX0 1 100DIFF

PEX_TX1 1 100DIFF

PEX_TX1 1 100DIFF

PEX_TX2 1 100DIFF

PEX_TX2 1 100DIFF

PEX_TX3 1 100DIFF

PEX_TX3 1 100DIFF

PEX_TX4 1 100DIFF

PEX_TX4 1 100DIFF

PEX_TX5 1 100DIFF

PEX_TX6 1 100DIFF

PEX_TX6 1 100DIFF

PEX_TX7 1 100DIFF

PEX_TX7 1 100DIFF

PEX_TX8 1 100DIFF

PEX_TX8 1 100DIFF

PEX_TX9 1 100DIFF

PEX_TX9 1 100DIFF

PEX_TX10 1 100DIFF

PEX_TX10 1 100DIFF

PEX_TX11 1 100DIFF

PEX_TX11 1 100DIFF

PEX_TX12 1 100DIFF

PEX_TX12 1 100DIFF

PEX_TX13 1 100DIFF

PEX_TX13 1 100DIFF

PEX_TX14 1 100DIFF

PEX_TX14 1 100DIFF

PEX_TX15 1 100DIFF

PEX_TX15 1 100DIFF

PEX_TXX0 1 100DIFF

PEX_TXX0 1 100DIFF

PEX_TXX1 1 100DIFF

PEX_TXX1 1 100DIFF

PEX_TXX2 1 100DIFF

PEX_TXX2 1 100DIFF

PEX_TXX3 1 100DIFF

PEX_TXX3 1 100DIFF

PEX_TXX4 1 100DIFF

PEX_TXX4 1 100DIFF

PEX_TXX5 1 100DIFF

PEX_TXX5 1 100DIFF

PEX_TXX6 1 100DIFF

PEX_TXX7 1 100DIFF

PEX_TXX7 1 100DIFF

PEX_TXX8 1 100DIFF

PEX_TXX8 1 100DIFF

PEX_TXX9 1 100DIFF

PEX_TXX10 1 100DIFF

PEX_TXX10 1 100DIFF

PEX_TXX11 1 100DIFF

PEX_TXX11 1 100DIFF

PEX_TXX12 1 100DIFF

PEX_TXX12 1 100DIFF

PEX_TXX13 1 100DIFF

PEX_TXX13 1 100DIFF

PEX_TXX14 1 100DIFF

PEX_TXX14 1 100DIFF

PEX_TXX15 1 100DIFF

PEX_RX0 1 100DIFF

PEX_RX0 1 100DIFF

PEX_RX1 1 100DIFF

PEX_RX2 1 100DIFF

PEX_RX2 1 100DIFF

PEX_RX3 1 100DIFF

PEX_RX3 1 100DIFF

PEX_RX4 1 100DIFF

PEX_RX4 1 100DIFF

PEX_RX5 1 100DIFF

PEX_RX5 1 100DIFF

PEX_RX6 1 100DIFF

PEX_RX6 1 100DIFF

PEX_RX7 1 100DIFF

PEX_RX7 1 100DIFF

PEX_RX8 1 100DIFF

PEX_RX8 1 100DIFF

PEX_RX9 1 100DIFF

PEX_RX9 1 100DIFF

PEX_RX10 1 100DIFF

PEX_RX11 1 100DIFF

PEX_RX11 1 100DIFF

PEX_RX12 1 100DIFF

PEX_RX12 1 100DIFF

PEX_RX13 1 100DIFF

PEX_RX13 1 100DIFF

PEX_RX14 1 100DIFF

PEX_RX14 1 100DIFF

PEX_RX15 1 100DIFF

PEX_RX15 1 100DIFF

PEX_REFCLK 1 100DIFF

PEX_REFCLK 1 100DIFF

A B D F H

CRITICALDIFF_PAIR

1PEX_TST 100DIFF

1PEX_TST 100DIFF

1PEX_TXX6 100DIFF

1PEX_TXX9 100DIFF

1PEX_RX10 100DIFF

IMPEDANCE

100DIFFPEX_TX5 1

100DIFFPEX_TXX15 1

100DIFFPEX_RX1 1

12V

C15

C15

C647

C647

C644

4.7UF

4.7UF

16V

16V

20%

20%

X7R

X7R

1206

1206

COMMON

COMMON

C644

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

3V3

SNN_3V3AUX

PRSNT

SNN_PE_PRSNT2_A

SNN_PE_RSVD2

SNN_PE_PRSNT2_B

SNN_PE_RSVD3

SNN_PE_RSVD4

SNN_PE_RSVD5

SNN_PE_PRSNT2_C

SNN_PE_RSVD6

SNN_PE_RSVD7

SNN_PE_RSVD8

4.7UF

4.7UF

16V

16V

20%

20%

X7R

X7R

1206

1206

COMMON

COMMON

GND

CN1

CN1

NONPHY-X16

NONPHY-X16

CON_X16

CON_X16

COMMON

COMMON

B1

+12V

B2

+12V

A2

+12V

A3

+12V

B3

+12V/RSVD

B8

+3V3

A9

+3V3

A10

+3V3

B10

+3V3AUX

A1

PRSNT1

B17

PRSNT2

B12

RSVD

B4

GND

A4

GND

B7

GND

A12

GND

B13

GND

A15

GND

B16

GND

B18

GND

A18

GND

TRST* JTAG1

TCLK JTAG2

TDI JTAG3

TDO JTAG4

TMS JTAG5

GND

END OF X1

END OF X1

B31

PRSNT2

A19

RSVD

B30

RSVD

A32

RSVD

A20

GND

B21

GND

B22

GND

A23

GND

A24

GND

B25

GND

B26

GND

A27

GND

A28

GND

B29

GND

A31

GND

B32

GND

END OF X4

GND

GND

END OF X4

B48

PRSNT2

A33

RSVD

A34

GND

B35

GND

B36

GND

A37

GND

A38

GND

B39

GND

B40

GND

A41

GND

A42

GND

B43

GND

B44

GND

A45

GND

A46

GND

B47

GND

B49

GND

A49

GND

END OF X8

END OF X8

B81

PRSNT2

A50

RSVD

B82

RSVD

A51

GND

B52

GND

B53

GND

A54

GND

A55

GND

B56

GND

B57

GND

A58

GND

A59

GND

B60

GND

B61

GND

A62

GND

A63

GND

B64

GND

B65

GND

A66

GND

A67

GND

B68

GND

B69

GND

A70

GND

A71

GND

B72

GND

B73

GND

A74

GND

A75

GND

B76

GND

B77

GND

A78

GND

A79

GND

B80

GND

A82

GND

GND

END OF X16

END OF X16

SMCLK

SMDAT

WAKE

PERST

REFCLK

REFCLK

PERP0

PERN0

PETP0

PETN0

PERP1

PERN1

PETP1

PETN1

PERP2

PERN2

PETP2

PETN2

PERP3

PERN3

PETP3

PETN3

PERP4

PERN4

PETP4

PETN4

PERP5

PERN5

PETP5

PETN5

PERP6

PERN6

PETP6

PETN6

PERP7

PERN7

PETP7

PETN7

PERP8

PERN8

PETP8

PETN8

PERP9

PERN9

PETP9

PETN9

PERP10

PERN10

PETP10

PETN10

PERP11

PERN11

PETP11

PETN11

PERP12

PERN12

PETP12

PETN12

PERP13

PERN13

PETP13

PETN13

PERP14

PERN14

PETP14

PETN14

PERP15

PERN15

PETP15

PETN15

SNN_JTAGE_TRST*

B9

SNN_JTAGE_TCLK

A5

JTAGE_TDI/O

A6

A7

SNN_JTAGE_TMS

A8

SNN_PEX_SMCLK

B5

SNN_PEX_SMDAT

B6

SNN_PEX_WAKE*

B11

PEX_PWRGD*

A11

PEX_REFCLK

A13

PEX_REFCLK*

A14

PEX_TXX0

A16

PEX_TXX0*

A17

PEX_RX0

B14

PEX_RX0*

B15

PEX_TXX1

A21

PEX_TXX1*

A22

PEX_RX1

B19

PEX_RX1*

B20

PEX_TXX2

A25

PEX_TXX2*

A26

PEX_RX2

B23

PEX_RX2*

B24

PEX_TXX3

A29

PEX_TXX3*

A30

PEX_RX3

B27

PEX_RX3*

B28

PEX_TXX4

A35

PEX_TXX4*

A36

PEX_RX4

B33

PEX_RX4*

B34

PEX_TXX5

A39

PEX_TXX5*

A40

PEX_RX5

B37

PEX_RX5*

B38

PEX_TXX6

A43

PEX_TXX6*

A44

PEX_RX6

B41

PEX_RX6*

B42

PEX_TXX7

A47

PEX_TXX7*

A48

PEX_RX7

B45

PEX_RX7*

B46

PEX_TXX8

A52

PEX_TXX8*

A53

PEX_RX8

B50

PEX_RX8*

B51

PEX_TXX9PEX_TXX9*

A56

PEX_TXX9*

A57

PEX_RX9

B54

PEX_RX9*

B55

PEX_TXX10

A60

PEX_TXX10*

A61

PEX_RX10

B58

PEX_RX10*

B59

PEX_TXX11

A64

PEX_TXX11*

A65

PEX_RX11

B62

PEX_RX11*

B63

PEX_TXX12

A68

PEX_TXX12*

A69

PEX_RX12

B66

PEX_RX12*

B67

PEX_TXX13

A72

PEX_TXX13*

A73

PEX_RX13

B70

PEX_RX13*

B71

PEX_TXX14

A76

PEX_TXX14*

A77

PEX_RX14

B74

PEX_RX14*

B75

PEX_TXX15

A80

PEX_TXX15*

A81

PEX_RX15

B78

PEX_RX15*

B79

COMMON 10%

COMMON 10%

COMMON X5R 10%

COMMON X5R 10%

X5R

X5R

COMMON X5R 10% 10V 0402

COMMON X5R 10% 10V 0402

COMMON X5R 10% 10V 0402

COMMON X5R 10% 10V 0402

COMMON 10% 10V 0402

X5R

COMMON 10% 10V 0402

X5R

X5R 10%

X5R 10%

COMMON X5R 10% 10V 0402

COMMON X5R 10% 10V 0402

COMMON 10V 040210%X5R

COMMON 10V 040210%X5R

COMMON 10V

COMMON 10V

MAKE CUTTABLE TRACE

C639

.1UF

C639

.1UF

10VX5R 0402

10VX5R 0402

X5R 10% 0402

X5R 10% 0402

C637

.1UF

C637

.1UF

10%X5R

040210VCOMMON

10%X5R

040210VCOMMON

COMMON 0402

COMMON 0402

C634

.1UF

C634

.1UF

040210V

040210V

C629

.1UF

C629

.1UF

10VCOMMON 10% 0402

10VCOMMON 10% 0402

COMMON

COMMON

C625 .1UF

C625 .1UF

10V10%X5R 0402COMMON

10V10%X5R 0402COMMON

10% 10V

10% 10V

C618

.1UFC618

.1UF

COMMON X5R 10% 10V 0402

COMMON X5R 10% 10V 0402

C612

.1UFC612

.1UF

COMMON X5R 10% 10V 0402

COMMON X5R 10% 10V 0402

C600

.1UF

C600

.1UF

COMMON X5R 10% 10V

COMMON X5R 10% 10V

C593

.1UF

C593

.1UF

040210VCOMMON

040210VCOMMON

COMMON

COMMON

C584

.1UFC584

.1UF

X5R 10% 10V 0402

COMMON

X5R 10% 10V 0402

COMMON

C573

.1UFC573

.1UF

X5RCOMMON 10%

X5RCOMMON 10%

C557

.1UF

C557

.1UF

0402X5R 10%

0402X5R 10%

COMMON X5R

COMMON X5R

C545

.1UF

C545

.1UF

10%COMMON

10V 0402X5R

10%COMMON

10V 0402X5R

COMMON X5R 10V

COMMON X5R 10V

C531 .1UF

C531 .1UF

040210V10%X5RCOMMON

040210V10%X5RCOMMON

X5R 040210V10%COMMON

X5R 040210V10%COMMON

C522 .1UF

C522 .1UF

040210VX5RCOMMON 10%

040210VX5RCOMMON 10%

C520 .1UF

C520 .1UF

040210VCOMMON X5R 10%

040210VCOMMON X5R 10%

OUT

C638

.1UF

C638

.1UF

10VCOMMON

10VCOMMON

C636

.1UF

C636

.1UF

10V10%X5R

10V10%X5R

C631

.1UF

C631

.1UF

10VCOMMON

10VCOMMON

C628

.1UF

C628

.1UF

C624

.1UF

C624

.1UF

C617

.1UFC617

.1UF

C608

.1UFC608

.1UF

C596

.1UF

C596

.1UF

C591

.1UF

C591

.1UF

C579

.1UF

C579

.1UF

C566

.1UF

C566

.1UF

10V 0402

10V 0402

C553

.1UF

C553

.1UF

C539

.1UF

C539

.1UF

C529 .1UF

C529 .1UF

C521 .1UF

C521 .1UF

C519 .1UF

C519 .1UF

HGFEDCBA

U3A

U3A

BGA533

BGA533

COMMON

COMMON

1/12 PCI_EXPRESS

1/12 PCI_EXPRESS

AC6

AF13

AF14

AE3

AE4

AD5

AD6

AF1

AG2

AE6

AE7

AG3

AG4

AD7

AC7

AF4

AF5

AE9

AE10

AG6

AG7

AD10

AC10

AF7

AF8

AE12

AE13

AG9

AG10

AD13

AC13

AF10

AF11

AC15

AD15

AG12

AG13

AE15

AE16

AG15

AG16

AC18

AD18

AF16

AF17

AE18

AE19

AG18

AG19

AC21

AD21

AF19

AF20

AE21

AE22

AG21

AG22

AD22

AD23

AF22

AF23

AF25

AE25

AG24

AG25

AE24

AD24

AG26

AF27

PEX_RST

PEX_TSTCLK_OUT

PEX_TSTCLK_OUT

PEX_REFCLK

PEX_REFCLK

PEX_TX0

PEX_TX0

PEX_RX0

PEX_RX0

PEX_TX1

PEX_TX1

PEX_RX1

PEX_RX1

PEX_TX2

PEX_TX2

PEX_RX2

PEX_RX2

PEX_TX3

PEX_TX3

PEX_RX3

PEX_RX3

PEX_TX4

PEX_TX4

PEX_RX4

PEX_RX4

PEX_TX5

PEX_TX5

PEX_RX5

PEX_RX5

PEX_TX6

PEX_TX6

PEX_RX6

PEX_RX6

PEX_TX7

PEX_TX7

PEX_RX7

PEX_RX7

PEX_TX8

PEX_TX8

PEX_RX8

PEX_RX8

PEX_TX9

PEX_TX9

PEX_RX9

PEX_RX9

PEX_TX10

PEX_TX10

PEX_RX10

PEX_RX10

PEX_TX11

PEX_TX11

PEX_RX11

PEX_RX11

PEX_TX12

PEX_TX12

PEX_RX12

PEX_RX12

PEX_TX13

PEX_TX13

PEX_RX13

PEX_RX13

PEX_TX14

PEX_TX14

PEX_RX14

PEX_RX14

PEX_TX15

PEX_TX15

PEX_RX15

PEX_RX15

NV46

NV46

NV_PLLAVDD

NV_PLLAVDD

G72/73 NV4x

G72/73 NV4x

PEX_TSTCLK

R531 200

R531 200

040210%X5R

040210%X5R

040210V10%X5R

040210V10%X5R

0402COMMON X5R

0402COMMON X5R

0402

0402

040210V10%X5R

040210V10%X5R

040210V10%

040210V10%

040210%

040210%

040210V10%X5RCOMMON

040210V10%X5RCOMMON

040210V10%X5RCOMMON

040210V10%X5RCOMMON

PEX_TSTCLK*

COMMON0402

COMMON0402

5%

5%

PEX_TX0

PEX_TX0*

PEX_TX1

PEX_TX1*

PEX_TX2

PEX_TX2*

PEX_TX3

PEX_TX3*

PEX_TX4

PEX_TX4*

PEX_TX5

PEX_TX5*

PEX_TX6

PEX_TX6*

PEX_TX7

PEX_TX7*

PEX_TX8

PEX_TX8*

PEX_TX9

PEX_TX9*

PEX_TX10

PEX_TX10*

PEX_TX11

PEX_TX11*

PEX_TX12

PEX_TX12*

PEX_TX13

PEX_TX13*

PEX_TX14

PEX_TX14*

PEX_TX15

PEX_TX15*

E GC

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

VDD_LP

VDD_LP

VDD_LP

VDD_LP

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33

NV44

NV44

PEX_PLLAVDD

PEX_PLLDVDD

PEX_PLLGND

SPDIF NC

AB10

AB11

AB14

AB15

W17

W18

AB20

AB21

C571

C571

.022UF

.022UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

PLACE NEAR BALLS

AA4

AB5

AB6

AB7

AB8

AB9

AC9

AC11

AB12

AC12

AB13

AB16

AC16

AB17

AC17

AB18

AB19

AC19

AC20

J9

VDD

M9

VDD

R9

VDD

T9

VDD

J10

VDD

J11

VDD

M11

VDD

N11

VDD

R11

VDD

T11

VDD

L12

VDD

M12

VDD

T12

VDD

U12

VDD

L13

VDD

M13

VDD

T13

VDD

U13

VDD

W13

VDD

M14

VDD

T14

VDD

L15

VDD

M15

VDD

T15

VDD

U15

VDD

W15

VDD

L16

VDD

M16

VDD

T16

VDD

U16

VDD

W16

VDD

M17

VDD

N17

VDD

R17

VDD

T17

VDD

W9

W10

W11

W12

J12

F13

J13

F14

J15

J16

N9

VDD

Y6

AA5

AA6

D12

E12

NC

F12

NC

C13

NC

PLACE NEAR BALLS

PLACE NEAR BALLS

PLACE NEAR BALLS

NV_PLLAVDD

PEX_PLL_DVDD

PLACE NEAR BALLS

SNN_NC1

SNN_NC2

SNN_NC3

SNN_NC4

C594

C594

4700PF

4700PF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C546

C546

.022UF

.022UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C541

C541

100PF

100PF

50V

50V

5%

5%

C0G

C0G

0402

0402

COMMON

COMMON

C551

C551

220PF

220PF

50V

50V

5%

5%

C0G

C0G

0402

0402

COMMON

COMMON

C558

C558

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C580

C580

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C554

C554

.022UF

.022UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C581

C581

.022UF

.022UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C582

C582

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C552

C552

100PF

100PF

50V

50V

5%

5%

C0G

C0G

0402

0402

COMMON

COMMON

C577

C577

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C570

C570

220PF

220PF

50V

50V

5%

5%

C0G

C0G

0402

0402

COMMON

COMMON

C559

C559

4700PF

4700PF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C31

C31

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C548

C548

.022UF

.022UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C562

C562

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

PLACE NEAR GPU

PEX1V2

C572

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C574

C574

C555

C555

C572

GND

C575

C575

C547

C547

C565

C565

100PF

100PF

.01UF

50V

50V

5%

5%

C0G

C0G

0402

0402

COMMON

COMMON

C564

C564

100PF

100PF

50V

50V

5%

5%

C0G

C0G

0402

0402

COMMON

COMMON

C619

C619

10UF

10UF

6.3V

6.3V

20%

20%

X5R

X5R

0805

0805

COMMON

COMMON

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C540

C540

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C640

C640

10UF

10UF

6.3V

6.3V

20%

20%

X5R

X5R

0805

0805

COMMON

COMMON

C622

C622

10UF

10UF

6.3V

6.3V

20%

20%

X5R

X5R

0805

0805

COMMON

COMMON

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C578

C578

220PF

220PF

50V

50V

5%

5%

C0G

C0G

0402

0402

COMMON

COMMON

C576

C576

220PF

220PF

50V

50V

5%

5%

C0G

C0G

0402

0402

COMMON

COMMON

C569

C569

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

F3V3

C563

C563

C568

C568

1UF

1UF

.022UF

.022UF

10V

10V

16V

16V

10%

10%

10%

10%

X5R

X5R

X7R

X7R

0402

0402

0603

0603

COMMON

COMMON

COMMON

COMMON

GND

LB1

120R@100MHz

LB1

120R@100MHz

Bead_0402

COMMON

Bead_0402

COMMON

C32

C32

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

LB505 30R@100MHz

LB505 30R@100MHz

BEAD_0603 COMMON

C611

C611

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C615

C615

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C613

C613

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

BEAD_0603 COMMON

PLACE NEAR GPU

GIGABYTE

GIGABYTE

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

PEX-Interface

PEX-Interface

PEX-Interface

GV-NX73L128T-RH-LE

GV-NX73L128T-RH-LE

GV-NX73L128T-RH-LE

Thursday, August 03, 2006

Thursday, August 03, 2006

Thursday, August 03, 2006

GIGABYTE

C626

C626

10UF/8/X5R/6.3V

10UF/8/X5R/6.3V

6.3V

6.3V

20%

20%

X5R

X5R

0805

0805

COMMON

COMMON

NVVDD

GND

GND

GND

GND

NVVDD

GND

PEX1V2

C623

C623

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0805

0805

COMMON

COMMON

GND

PEX1V2

GND

of

215

of

215

of

215

1

2

3

4

5

1.0

1.0

1.0

GPU: FB-Interface

HGFEDCBA

U3B

U3B

BGA533

BGA533

COMMON

1

2

3

4

FBAD[31..0]

BI

FBAD[63..32]

BI

FBADQM[7..0]

OUT

FBADQS[7..0]

BI

FBADQSN[7..0]

BI

FBAD0

0

FBAD1

1

FBAD2

2

FBAD3

3

FBAD4

4

FBAD5

5

FBAD6

6

FBAD7

7

FBAD8

8

FBAD9

9

FBAD10

10

FBAD11

11

FBAD12

12

FBAD13

13

FBAD14

14

FBAD15

15

FBAD16

16

FBAD17

17

FBAD18

18

FBAD19

19

FBAD20

20

FBAD21

21

FBAD22

22

FBAD23

23

FBAD24

24

FBAD25

25

FBAD26

26

FBAD27

27

FBAD28

28

FBAD29

29

FBAD30

30

FBAD31

31

FBAD32

32

FBAD33

33

FBAD34

34

FBAD35

35

FBAD36

36

FBAD37

37

FBAD38

38

FBAD39

39

FBAD40

40

FBAD41

41

FBAD42

42

FBAD43

43

FBAD44

44

FBAD45

45

FBAD46

46

FBAD47

47

FBAD48

48

FBAD49

49

FBAD50

50

FBAD51

51

FBAD52

52

FBAD53

53

FBAD54

54

FBAD55

55

FBAD56

56

FBAD57

57

FBAD58

58

FBAD59

59

FBAD60

60

FBAD61

61

FBAD62

62

FBAD63

63

FBADQM0

0

FBADQM1

1

FBADQM2

2

FBADQM3

3

FBADQM4

4

FBADQM5

5

FBADQM6

6

FBADQM7

7

FBADQS0

0

FBADQS1

1

FBADQS2

2

FBADQS3

3

FBADQS4

4

FBADQS5

5

FBADQS6

6

FBADQS7

7

FBADQSN0

0

FBADQSN1

1

FBADQSN2

2

FBADQSN3

3

FBADQSN4

4

FBADQSN5

5

FBADQSN6

6

FBADQSN7

7

FBVDDQ

R516

R516

1K

1K

Rt

1%

1%

0402

0402

COMMON

COMMON

R518

R518

1K

1K

Rb

1%

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

1%

0402

0402

COMMON

COMMON

GND

FBVREF = FBVDDQ * Rb/(Rt + Rb)

VREF = 0.5 * FBVDDQ

DDR2: 1.00V = 2.0V * 1K/(1K + 1K)

A B D F H

C556

C556

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

FBVREF

A26

C24

B24

A24

C22

A25

B25

D23

G22

J23

E24

F23

J24

F24

G23

H24

D16

E16

D17

F18

E19

E18

D20

D19

A18

B18

A19

B19

D18

C19

C16

C18

N26

N25

R25

R26

R27

T25

T27

T26

AB23

Y24

AB24

AB22

AC24

AC22

AA23

AA22

T24

T23

R24

R23

R22

T22

N23

P24

AA24

AA27

AA26

AB25

AB26

AB27

AA25

W25

D21

F22

F20

A21

V27

W22

V22

V24

B22

D22

E21

C21

V25

W24

U24

W26

A22

E22

F21

B21

V26

W23

V23

W27

A16

COMMON

2/12 FRAME_BUFFER

2/12 FRAME_BUFFER

FB_DQ0

FB_DQ1

FB_DQ2

FB_DQ3

FB_DQ4

FB_DQ5

FB_DQ6

FB_DQ7

FB_DQ8

FB_DQ9

FB_DQ10

FB_DQ11

FB_DQ12

FB_DQ13

FB_DQ14

FB_DQ15

FB_DQ16

FB_DQ17

FB_DQ18

FB_DQ19

FB_DQ20

FB_DQ21

FB_DQ22

FB_DQ23

FB_DQ24

FB_DQ25

FB_DQ26

FB_DQ27

FB_DQ28

FB_DQ29

FB_DQ30

FB_DQ31

FB_DQ32

FB_DQ33

FB_DQ34

FB_DQ35

FB_DQ36

FB_DQ37

FB_DQ38

FB_DQ39

FB_DQ40

FB_DQ41

FB_DQ42

FB_DQ43

FB_DQ44

FB_DQ45

FB_DQ46

FB_DQ47

FB_DQ48

FB_DQ49

FB_DQ50

FB_DQ51

FB_DQ52

FB_DQ53

FB_DQ54

FB_DQ55

FB_DQ56

FB_DQ57

FB_DQ58

FB_DQ59

FB_DQ60

FB_DQ61

FB_DQ62

FB_DQ63

FB_DQM0

FB_DQM1

FB_DQM2

FB_DQM3

FB_DQM4

FB_DQM5

FB_DQM6

FB_DQM7

FB_DQS_WP0

FB_DQS_WP1

FB_DQS_WP2

FB_DQS_WP3

FB_DQS_WP4

FB_DQS_WP5

FB_DQS_WP6

FB_DQS_WP7

FB_DQS_RN0

FB_DQS_RN1

FB_DQS_RN2

FB_DQS_RN3

FB_DQS_RN4

FB_DQS_RN5

FB_DQS_RN6

FB_DQS_RN7

FB_VREF

NV46

NV46

FB_PLLAVDD

FB_PLLAVDD

FB_PLLGND

FB_PLLGND

NC

NC

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_CMD0

FB_CMD1

FB_CMD2

FB_CMD3

FB_CMD4

FB_CMD5

FB_CMD6

FB_CMD7

FB_CMD8

FB_CMD9

FB_CMD10

FB_CMD11

FB_CMD12

FB_CMD13

FB_CMD14

FB_CMD15

FB_CMD16

FB_CMD17

FB_CMD18

FB_CMD19

FB_CMD20

FB_CMD21

FB_CMD22

FB_CMD23

FB_CMD24

FB_CMD25

FB_CMD26

FB_CLK0

FB_CLK0

FB_CLK1

FB_CLK1

FB_CAL_PD_VDDQ

FB_CAL_PU_GND

FB_CAL_TERM_GND

FB_DEBUG

FB_REFCLK

FB_REFCLK

NV44

NV44

FB_PLLVDD

FB_PLLAVDD

FB_PLLGND

E15

F15

F16

J17

J18

L19

N19

R19

U19

W19

F17

F19

J19

M19

T19

J22

L22

P22

U22

Y22

G27

D25

F26

F25

G25

J25

J27

M26

C27

C25

D24

N27

G24

J26

M27

C26

M25

D26

D27

K26

K25

K24

F27

K27

G26

B27

N24

L24

K23

M22

N22

D15

E13

H22

K22

M23

M24

D14

D13

C15

GND

PLACE NEAR BGA

C537

C537

C550

C550

.1UF

.1UF

.1UF

.1UF

10V

10V

10V

10V

10%

10%

10%

10%

X5R

X5R

X5R

X5R

0402

0402

0402

0402

COMMON

COMMON

COMMON

COMMON

FBVTT connected for DDR2 ram

FBACMD0

FBACMD1

FBACMD2

FBACMD3

FBACMD4

FBACMD5

FBACMD6

FBACMD7

FBACMD8

FBACMD9

FBACMD10

FBACMD11 FBACMD11

FBACMD12

FBACMD13

FBACMD14

FBACMD15

FBACMD16

FBACMD17

FBACMD18

FBACMD19

FBACMD20

FBACMD21

FBACMD22

FBACMD23

FBACMD24

FBACMD25

SNN_FBA_CMD26

FBACLK0

FBACLK0*

FBACLK1

FBACLK1*

FBCAL_PD_VDDQ

FBCAL_PU_GND

FBCAL_TERM_GND

FBA_DEBUG_ODT

SNN_FBA_REFCLK

SNN_FBA_REFCLK*

SNN_FBA_PLLVDD

FBA_PLLAVDD

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

OUT

OUT

OUT

OUT

R513

R513

0402

0402

1%

1%

C561

C561

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

PLACE NEAR BALLS

FBACMD[25..0]

PD REQUIRED FOR INITIALIZATION

CKE

40.2

40.2

COMMON

COMMON

GND GND

C535

C535

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

OUT

R38

R38

10K

10K

5%

5%

0402

0402

COMMON

COMMON

GND

FBVDDQ

R517

R517

40.2

40.2

1%

1%

0402

0402

COMMON

COMMON

R519

R519

30.1/4/1

30.1/4/1

1%

1%

0402

0402

COMMON

COMMON

PLACE NEAR GPU

C560

C560

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C536

C536

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C34

C34

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0805

0805

COMMON

COMMON

C35

C35

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

TP502TP502

TP501TP501

LB501

COMMONBEAD_0402

COMMONBEAD_0402

FBVDDQ

C567

C567

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

GND

PLACE BELOW GPU

C532

C532

4700PF

4700PF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C528

C528

C549

C549

.022UF

.022UF

4700PF

4700PF

16V

16V

25V

25V

10%

10%

10%

10%

X7R

X7R

X7R

X7R

0402

0402

0402

0402

COMMON

COMMON

COMMON

COMMON

C534

C534

C524

C524

4700PF

4700PF

.022UF

.022UF

25V

25V

16V

16V

10%

10%

10%

10%

X7R

X7R

X7R

X7R

0402

0402

0402

0402

COMMON

COMMON

COMMON

COMMON

LABTESTPOINTS

FBACLK0

FBACLK0*

FBACLK1

TP7TP7

FBACLK1*

TP8TP8

FBA_DEBUG_ODT

TP4TP4

220R@100MHzLB501

220R@100MHz

NVVDD

GND

E GC

C526

C526

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C523

C523

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

TP5TP5

TP6TP6

C542

C542

4700PF

4700PF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C543

C543

4700PF

4700PF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

Rmoved two 0.022uf, and two 0.1uf

FBADQS1

FBADQSN1

C538

C538

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C527

C527

.022UF

.022UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C525

C525

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

FBVDDQ

GND

GND

FBA CMD/ADDR TERMINATIONS:

FBVDDQ

150

150

150RP501B

150

COMMON

COMMON

COMMON0402X4

COMMON0402X4

150

150

COMMON0402X4

COMMON0402X4

150

150

COMMON

COMMON

150

150

COMMON0402X4

COMMON0402X4

150

150

FBVDDQ

150

150

150RP3B

150

COMMON

COMMON

FBVDDQ

FBVDDQ

GND

GND

GND

FBACMD17

FBACMD18

FBACMD2

FBACMD3

GND

FBACMD6

FBACMD8

FBACMD13

FBACMD14

1 8

2 7

0402X4 COMMON

0402X4 COMMON

3 6

0402X4 COMMON

0402X4 COMMON

4 5

0402X4

0402X4

FBACMD0

RP7D 150

RP7D 150

4 5

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

RP7C

RP7C

3 6

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

FBACMD1

RP3B

2 7

0402X4

0402X4

+/-5%

+/-5%

RP3A 150

RP3A 150

1 8

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

FBACMD4

RP501A

RP501A

1 8

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

RP501B

2 7

0402X4

0402X4

+/-5%

+/-5%

FBACMD5

RP10C 150

RP10C 150

3 6

+/-5%

FBACMD9

+/-5%

RP10D

RP10D

4 5

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

RP6A 150

RP6A 150

1 8

+/-5%

+/-5%

RP6B

RP6B

2 7

0402X4

0402X4

+/-5%

+/-5%

RP5B

RP5B

2 7

+/-5%

+/-5%

RP5A

RP5A

1 8

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

C533

C533

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

FBACMD10

GND

FBACMD15

RP6D

150

RP6D

150

FBACMD16

4 5

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

RP6C

150

RP6C

150

3 6

COMMON

COMMON

0402X4

0402X4

+/-5%

+/-5%

RP10B 150

RP10B 150

2 7

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

RP10A

150RP10A

150

1 8

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

C544

C544

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

FBVDDQ

FBACMD23

FBACMD24

FBACMD19

FBACMD20

4 5

0402X4

0402X4

RP3C 150

RP3C 150

3 6

RP11C

RP11C

3 6

0402X4

0402X4

RP11D

4 5

0402X4

0402X4

RP1D

RP1D

4 5

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

RP1C 150

RP1C 150

3 6

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

RP2B

RP2B

2 7

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

RP2A

RP2A

1 8

+/-5%

+/-5%

RP3D 150

RP3D 150

+/-5%

+/-5%

+/-5%

+/-5%

+/-5%

+/-5%

+/-5%

+/-5%

150

150

150

150

150

150

COMMON0402X4

COMMON0402X4

150

150

150RP11D

150

COMMON

COMMON

COMMON0402X4

COMMON0402X4

COMMON

COMMON

COMMON

COMMON

FBVDDQ

FBACMD21

4 5

3 6

0402X4

0402X4

FBACMD22

3 6

0402X4 COMMON

0402X4 COMMON

4 5

0402X4 COMMON

0402X4 COMMON

GND

FBACMD25

FBACMD7

GND

RP8D

RP8D

4 5

RP8C 150

RP8C 150

3 6

0402X4

0402X4

RP8B 150

RP8B 150

2 7

0402X4

0402X4

RP8A 150

RP8A 150

1 8

0402X4 COMMON

0402X4 COMMON

RP11A

RP11A

1 8

0402X4

0402X4

+/-5%

+/-5%

RP11B

RP11B

2 7

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

RP7B

RP7B

2 7

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

RP7A

1 8

+/-5%

+/-5%

RP4A

RP4A

1 8

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

RP4B 150

RP4B 150

2 7

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

RP501C 150

RP501C 150

3 6

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

RP501D 150

RP501D 150

4 5

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

RP1A 150

RP1A 150

COMMON0402X4

COMMON0402X4

+/-5%

+/-5%

RP1B 150

RP1B 150

+/-5%

+/-5%

RP9C 150

RP9C 150

+/-5%

+/-5%

RP9D 150

RP9D 150

COMMON

COMMON

+/-5%

+/-5%

RP4D

150

RP4D

150

COMMON0402X4

COMMON0402X4

+/-5%

+/-5%

RP4C 150

RP4C 150

COMMON

COMMON

+/-5%

+/-5%

RP2C

150

RP2C

150

+/-5%

+/-5%

RP2D 150

RP2D 150

+/-5%

+/-5%

RP9A

RP9A

1 8

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

RP9B

RP9B

2 7

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

RP5D

RP5D

4 5

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

RP5C

3 6

0402X4 COMMON

0402X4 COMMON

+/-5%

+/-5%

FBVDDQ

150

150

COMMON0402X4

COMMON0402X4

+/-5%

+/-5%

COMMON

COMMON

+/-5%

+/-5%

COMMON

COMMON

+/-5%

+/-5%

+/-5%

+/-5%

GND

FBVDDQ

150

150

COMMON

COMMON

150

150

150

150

150RP7A

150

COMMON0402X4

COMMON0402X4

GND

FBVDDQ

150

150

GND

FBVDDQ

GND

FBVDDQ

GND

FBVDDQ

150

150

150

150

150

150

150RP5C

150

GND

1

2

3

4

FBVDDQ

R40

R40

10K/X

10K/X

5%

5%

0402

0402

NS

RESET

FBACMD12

NS

OUT

COMMON

COMMON

R39

R39

10K

10K

5%

5%

0402

0402

PD REQUIRED FOR INITIALIZATION OF DDR2

GND

GIGABYTE

GIGABYTE

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

GPU: FB-Interface

GPU: FB-Interface

GPU: FB-Interface

GV-NX73L128T-RH-LE

GV-NX73L128T-RH-LE

GV-NX73L128T-RH-LE

Thursday, August 03, 2006

Thursday, August 03, 2006

Thursday, August 03, 2006

GIGABYTE

of

315

of

315

of

315

5

1.0

1.0

1.0

Memory Bit 0..31

PLACE ALL DISCRETE COMPONENTS AS NEAR AS POSSIBLE TO MEMORY

1

2

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

FBACMD[25..0]

IN

USED ONLY FOR 1GB DEVICES ---->

BI

IN

IN

IN

IN

IN

FBADQM[7..0]

FBADQS[7..0]

FBADQSN[7..0]

FBAD[63..0]

FBACLK0

FBACLK0*

FBACMD15 FBACMD15

15

FBACMD25 FBACMD25

25

FBACMD9 FBACMD9

9

FBACMD8 FBACMD8

8

FBACMD1 FBACMD1

1

FBACMD3 FBACMD3

3

FBACMD2 FBACMD2

2

FBACMD0 FBACMD0

0

FBACMD24 FBACMD24

24

FBACMD22 FBACMD22

22

FBACMD21 FBACMD21

21

FBACMD23 FBACMD23

23

FBACMD19 FBACMD19

19

FBACMD20 FBACMD20

20

FBACMD17 FBACMD17

17

FBACMD16 FBACMD16

16

FBACMD14 FBACMD14

14

SNN_FBA1_NC_R8

SNN_FBA1_NC_R3

SNN_FBA1_NC_R7

FBACMD10 FBACMD10

10

FBACMD18 FBACMD18

18

FBACMD7 FBACMD7

7

FBACMD11 FBACMD11

11

FBACMD12 FBACMD12

IN

SNN_FBA1_NC_A2

SNN_FBA1_NC_E2

FBADQM0

0

FBADQM1

1

FBADQM2

2

FBADQM3

3

FBADQS0 FBADQS0

0

FBADQS1

1

FBADQS2

2

FBADQS3

3

FBADQSN0

0

FBADQSN1

1

FBADQSN2

2

FBADQSN3

3

FBVDDQ

FBACLK0

IN

U4C

U4C

BGA84

BGA84

COMMON

COMMON

1/2

1/2

K7

RAS

L7

CAS

K3

WE

L8

CS

M8

A<0>

M3

A<1>

M7

A<2>

N2

A<3>

N8

A<4>

N3

A<5>

N7

A<6>

P2

A<7>

P8

A<8>

P3

A<9>

M2

A<10>

P7

A<11>

R2

A<12>

R8

NC/A<13>

R3

NC/A<14>

R7

NC/A<15>

L2

BA<0>

L3

BA<1>

L1

NC/BA<2>

K2

CKE

J8

CLK

K8

CLK

K9

ODT

A2

NC

E2

NC

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

R33

R33

120

120

5%

5%

0402

0402

DNP

DNP

R351%100

R351%100

COMMON0603

COMMON0603

R34

R34

120

120

5%

5%

0402

0402

DNP

DNP

GND GND

FBAD0

FBAD1

FBAD2

FBAD3

FBAD4

FBAD5

FBAD6

FBAD7

FBADQM0

FBADQSN0

FBAD8

FBAD9

FBAD10

FBAD11

FBAD12

FBAD13

FBAD14

FBAD15

FBADQM1

FBADQS1

FBADQSN1

FBVDDQ

A1

VDD

E1

VDD

J9

VDD

M9

VDD

R1

VDD

A9

VDDQ

C1

VDDQ

C3

VDDQ

C7

VDDQ

C9

VDDQ

E9

VDDQ

G1

VDDQ

G3

VDDQ

G7

VDDQ

G9

VDDQ

J1

VDDL

A3

VSS

E3

VSS

J3

VSS

N1

VSS

GND

P9

VSS

A7

VSSQ

B2

VSSQ

B8

VSSQ

D2

VSSQ

D8

VSSQ

E7

VSSQ

F2

VSSQ

F8

VSSQ

H2

VSSQ

H8

VSSQ

J7

VSSL

VREF_B

J2

Vref

C507

C507

.047UF

.047UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

GND

U4A

U4A

BGA84

BGA84

COMMON

COMMON

D1

DQ<0>

D3

DQ<1>

C8

DQ<2>

D7

DQ<3>

D9

DQ<4>

B1

DQ<5>

C2

DQ<6>

B9

DQ<7>

B3

DQM

B7

DQS

A8

DQS

U501C

U501C

BGA84

BGA84

COMMON

COMMON

G8

DQ<0>

H9

DQ<1>

F1

DQ<2>

H3

DQ<3>

H7

DQ<4>

G2

DQ<5>

H1

DQ<6>

F9

DQ<7>

F3

DQM

F7

DQS

E8

DQS

FBVDDQ

USED ONLY FOR 1GB DEVICES ---->

FBACLK0

IN

FBACLK0*

IN

R505

R505

1K

1K

1%

1%

0402

0402

COMMON

COMMON

R503

R503

1K

1K

1%

1%

0402

0402

COMMON

COMMON

GND

2/2

2/2

2/2

2/2

Place these caps next to plane transitions

R36

R36

120

120

5%

5%

0402

0402

DNP

DNP

FBACLK0*

R37

R37

120

120

5%

5%

0402

0402

DNP

DNP

IN

A B D F H

FBVDDQ

GND

15

25

9

8

1

3

2

0

24

22

21

23

19

20

17

16

14

10

18

7

11

SNN_FBA2_NC_R8

SNN_FBA2_NC_R3

SNN_FBA2_NC_R7

SNN_FBA2_NC_A2

SNN_FBA2_NC_E2

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

C55

C55

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

FBAD16

FBAD17

FBAD18

FBAD19

FBAD20

FBAD21

FBAD22

FBAD23

FBADQM2

FBADQS2

FBADQSN2

FBAD24

FBAD25

FBAD26

FBAD27

FBAD28

FBAD29

FBAD30

FBAD31

FBADQM3

FBADQS3

FBADQSN3

FBVDDQ

HGFEDCBA

C52

C52

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C47

C47

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C56

C56

C61

C61

.01UF

.01UF

.01UF

.01UF

25V

25V

25V

25V

10%

10%

10%

10%

X7R

X7R

X7R

X7R

0402

0402

0402

0402

COMMON

COMMON

COMMON

COMMON

Memory Bit 0..31

Memory Bit 0..31

Memory Bit 0..31

GV-NX73L128T-RH-LE

GV-NX73L128T-RH-LE

GV-NX73L128T-RH-LE

Thursday, August 03, 2006

Thursday, August 03, 2006

Thursday, August 03, 2006

NV_IMPEDANCE NV_CRITICAL_NET

100DIFF 1FBACLK0

100DIFFFBACLK0 1

50OHM 1

100DIFF 1FBADQS0

100DIFF 1FBADQS1

100DIFFFBADQS3 1

50OHM 1

50OHM 1

C503

C503

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

GIGABYTE

GIGABYTE

GIGABYTE

1FBADQS1 100DIFF

1100DIFFFBADQS2

150OHM

C57

C57

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

C58

C58

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

415

415

415

1

2

3

4

5

1.0

1.0

1.0

of

of

of

DIFFPAIRNET

FBACLK0

IN

FBACLK0*

IN

FBAD[63..0]

IN

FBADQS0

0

FBADQS[7..0]

IN

FBADQSN[7..0]

IN

U501B

U501B

BGA84

BGA84

COMMON

COMMON

1/2

1/2

K7

RAS

L7

CAS

K3

WE

L8

CS

M8

A<0>

M3

A<1>

M7

A<2>

N2

A<3>

N8

A<4>

N3

A<5>

N7

A<6>

P2

A<7>

P8

A<8>

P3

A<9>

M2

A<10>

P7

A<11>

R2

A<12>

R8

NC/A<13>

R3

NC/A<14>

R7

NC/A<15>

L2

BA<0>

L3

BA<1>

L1

NC/BA<2>

K2

CKE

J8

CLK

K8

CLK

K9

ODT

A2

NC

E2

NC

U501A

U501A

BGA84

BGA84

COMMON

COMMON

2/2

2/2

D1

DQ<0>

D3

DQ<1>

C2

DQ<2>

D7

DQ<3>

B9

DQ<4>

B1

DQ<5>

D9

DQ<6>

C8

DQ<7>

B3

DQM

B7

DQS

A8

DQS

U4B

U4B

BGA84

BGA84

COMMON

COMMON

2/2

2/2

F9

DQ<0>

G8

DQ<1>

H3

DQ<2>

G2

DQ<3>

H1

DQ<4>

F1

DQ<5>

H9

DQ<6>

H7

DQ<7>

F3

DQM

F7

DQS

E8

DQS

FBVDDQ

FBVDDQ

C40

C50

C50

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C40

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

GND

C37

C37

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

GND

GND

FBVDDQ

A1

VDD

E1

VDD

J9

VDD

M9

VDD

R1

VDD

A9

VDDQ

C1

VDDQ

C3

VDDQ

C7

VDDQ

C9

VDDQ

E9

VDDQ

G1

VDDQ

G3

VDDQ

G7

VDDQ

G9

VDDQ

J1

VDDL

A3

VSS

E3

VSS

J3

VSS

GND

N1

VSS

P9

VSS

A7

VSSQ

B2

VSSQ

B8

VSSQ

D2

VSSQ

D8

VSSQ

E7

VSSQ

F2

VSSQ

F8

VSSQ

H2

VSSQ

H8

VSSQ

J7

VSSL

J2

Vref

C506

C506

.047UF

.047UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

GND

FBVDDQ

GND

FBVDDQ

GND

FBVDDQ

GND

FBVDDQ

GND

X-cap for CMD

FBVDDQ

C62

C62

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

GND

FBVDDQ

C60

C60

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

GND

E GC

IN

IN

IN

C513

C513

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C512

C512

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C508

C508

.1UF/X

.1UF/X

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C514

C514

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

1

2

3

C505

C505

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C502

C502

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

0

1

2

3

FBADQM[7..0]

FBACMD[25..0]

FBADQSN0

FBADQS0 100DIFF 1

FBADQS1

FBADQSN1

FBADQS2

FBADQSN2

FBADQS2 100DIFF 1

FBADQS3

FBADQSN3

FBADQS3 100DIFF 1

FBA_ODT

C46

C46

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C44

C44

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C41

C41

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C515

C515

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C64

C64

C63

C63

.01UF

.01UF

.01UF

.01UF

25V

25V

25V

25V

10%

10%

10%

10%

X7R

X7R

X7R

X7R

0402

0402

0402

0402

COMMON

COMMON

COMMON

COMMON

C501

C501

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Memory Bit 32..63

PLACE ALL DISCRETE COMPONENTS AS NEAR AS POSSIBLE TO MEMORY

FBACMD[25..0]

1

IN

FBACMD15 FBACMD15

15

FBACMD25 FBACMD25

25

FBACMD9 FBACMD9

9

FBACMD8 FBACMD8

8

FBACMD1 FBACMD1

1

FBACMD3 FBACMD3

3

FBACMD13 FBACMD13

13

FBACMD4 FBACMD4

4

FBACMD5 FBACMD5

SUBPARTITION BITS ---->

2

USED ONLY FOR 1GB DEVICES ---->

3

5

FBACMD6 FBACMD6

6

FBACLK1 FBACLK1

IN

FBACLK1* FBACLK1*

IN

FBACMD21 FBACMD21

21

FBACMD23 FBACMD23

23

FBACMD19 FBACMD19

19

FBACMD20 FBACMD20

20

FBACMD17 FBACMD17

17

FBACMD16 FBACMD16

16

FBACMD14 FBACMD14

14

SNN_FBA3_NC_R8

SNN_FBA3_NC_R3

SNN_FBA3_NC_R7

FBACMD10 FBACMD10

10

FBACMD18 FBACMD18

18

FBACMD7 FBACMD7

7

FBACMD11 FBACMD11

11

FBACMD12 FBACMD12

IN

SNN_FBA3_NC_A2

SNN_FBA3_NC_E2

FBAD[63..0]

BI

FBADQM[7..0]

IN

FBADQS[7..0]

IN

4

FBADQSN[7..0]

IN

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A B D F H

U5C

U5C

BGA84

BGA84

COMMON

COMMON

1/2

1/2

K7

RAS

L7

CAS

K3

WE

L8

CS

M8

A<0>

M3

A<1>

M7

A<2>

N2

A<3>

N8

A<4>

N3

A<5>

N7

A<6>

P2

A<7>

P8

A<8>

P3

A<9>

M2

A<10>

P7

A<11>

R2

A<12>

R8

NC/A<13>

R3

NC/A<14>

R7

NC/A<15>

L2

BA<0>

L3

BA<1>

L1

NC/BA<2>

K2

CKE

J8

CLK

K8

CLK

K9

ODT

A2

NC

E2

NC

FBADQM4

4

FBADQM5

5

FBADQM6

6

FBADQM7

7

FBADQS4

4

FBADQS5

5

FBADQS6

6

FBADQS7

7

FBADQSN4

4

FBADQSN5

5

FBADQSN6

6

FBADQSN7

7

FBVDDQ

A1

VDD

E1

VDD

J9

VDD

M9

VDD

R1

VDD

A9

VDDQ

C1

VDDQ

C3

VDDQ

C7

VDDQ

C9

VDDQ

E9

VDDQ

G1

VDDQ

G3

VDDQ

G7

VDDQ

G9

VDDQ

J1

VDDL

A3

VSS

E3

VSS

J3

VSS

GND

N1

VSS

P9

VSS

A7

VSSQ

B2

VSSQ

B8

VSSQ

D2

VSSQ

D8

VSSQ

E7

VSSQ

F2

VSSQ

F8

VSSQ

H2

VSSQ

H8

VSSQ

J7

VSSL

VREF_A

J2

Vref

GND

FBAD32

32

FBAD33

33

FBAD34

34

FBAD35

35

FBAD36

36

FBAD37

37

FBAD38

38

FBAD39

39

FBADQM4

FBADQS4

FBADQSN4

FBAD40

40

FBAD41

41

FBAD42

42

FBAD43

43

FBAD44

44

FBAD45

45

FBAD46

46

FBAD47

47

FBADQM5

FBADQS5

FBADQSN5

FBVDDQ

C51

C51

.047UF

.047UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

R31

R31

1K

1K

1%

1%

0402

0402

COMMON

COMMON

GND

SUBPARTITION BITS ---->

R32

R32

1K

1K

1%

1%

0402

0402

COMMON

COMMON

D9

D7

C8

B9

B1

C2

D3

D1

B3

B7

A8

C8

D1

B9

B1

D7

D9

D3

C2

B3

B7

A8

U5A

U5A

BGA84

BGA84

COMMON

COMMON

U502C

U502C

BGA84

BGA84

COMMON

COMMON

USED ONLY FOR 1GB DEVICES ---->

2/2

2/2

DQ<0>

DQ<1>

DQ<2>

DQ<3>

DQ<4>

DQ<5>

DQ<6>

DQ<7>

DQM

DQS

DQS

2/2

2/2

DQ<0>

DQ<1>

DQ<2>

DQ<3>

DQ<4>

DQ<5>

DQ<6>

DQ<7>

DQM

DQS

DQS

Place the differential termination resistor at the end of the transmission line.

13

4

5

6

IN

IN

FBVDDQ

FBACLK1

IN

15

25

9

8

1

3

21

23

19

20

17

16

14

SNN_FBA4_NC_R8

SNN_FBA4_NC_R3

SNN_FBA4_NC_R7

10

18

7

11

SNN_FBA4_NC_A2

SNN_FBA4_NC_E2

R507

R507

120/X

120/X

5%

5%

0402

0402

DNP

DNP

R504 100

R504 100

1%

1%

R506

R506

120/X

120/X

5%

5%

0402

0402

DNP

DNP

GND GND

HGFEDCBA

DIFFPAIR

NET

FBACLK1

IN

IN

FBADQSN[7..0]

IN

U502A

U502A

BGA84

BGA84

COMMON

COMMON

1/2

1/2

K7

RAS

L7

CAS

K3

WE

L8

CS

M8

A<0>

M3

A<1>

M7

A<2>

N2

A<3>

N8

A<4>

N3

A<5>

N7

A<6>

P2

A<7>

P8

A<8>

P3

A<9>

M2

A<10>

P7

A<11>

R2

A<12>

R8

NC/A<13>

R3

NC/A<14>

R7

NC/A<15>

L2

BA<0>

L3

BA<1>

L1

NC/BA<2>

K2

CKE

J8

CLK

K8

CLK

K9

ODT

A2

NC

E2

NC

FBVDDQ

A1

VDD

E1

VDD

J9

VDD

M9

VDD

R1

VDD

A9

VDDQ

C1

VDDQ

C3

VDDQ

C7

VDDQ

C9

VDDQ

E9

VDDQ

G1

VDDQ

G3

VDDQ

G7

VDDQ

G9

VDDQ

J1

VDDL

A3

VSS

E3

VSS

J3

VSS

GND

N1

VSS

P9

VSS

A7

VSSQ

B2

VSSQ

B8

VSSQ

D2

VSSQ

D8

VSSQ

E7

VSSQ

F2

VSSQ

F8

VSSQ

H2

VSSQ

H8

VSSQ

J7

VSSL

J2

Vref

C54

C54

.047UF

.047UF

16V

16V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

GND

FBVDDQ

GND

FBVDDQ

GND

FBADQSN4

4

FBADQS5

5

FBADQSN5

5

FBADQS6

6

FBADQSN6

6

FBADQS7

7

FBADQSN7

7

C516

C516

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C511

C511

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

FBACLK1*

IN

FBADQS4

4

FBADQS[7..0]

FBACLK1 1100DIFF

FBADQS4 100DIFF 1

FBADQS4 100DIFF 1

FBADQS5 100DIFF 1

FBADQS5 100DIFF 1

FBADQS6 100DIFF 1

FBADQS6 100DIFF 1

FBADQS7 100DIFF 1

C43

C43

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C517

C517

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

NV_IMPEDANCE

100DIFF 1FBADQS7

C49

C49

1UF

1UF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

1100DIFFFBACLK1

C59

C59

4.7UF

4.7UF

6.3V

6.3V

10%

10%

X5R

X5R

0603

0603

COMMON

COMMON

NV_CRITICAL_NET

1

2

3

U502B

U502B

BGA84

BGA84

COMMON

COMMON

2/2

FBAD48

48

FBAD49

49

FBAD50

50

FBAD51

51

FBAD52

52

FBAD53

53

FBAD54

54

FBAD55

55

FBADQM6

FBADQS6

FBADQSN6

FBAD56

56

FBAD57

57

FBAD58

58

FBAD59

59

FBAD60

60

FBAD61

61

FBAD62

62

FBAD63

63

FBADQM7

FBADQS7

FBADQSN7

R502

R502

120/X

120/X

5%

5%

0402

0402

DNP

DNP

FBACLK1*

COMMON0603

COMMON0603

R501

R501

120/X

120/X

5%

5%

0402

0402

DNP

DNP

2/2

G8

DQ<0>

F9

DQ<1>

G2

DQ<2>

F1

DQ<3>

H7

DQ<4>

H9

DQ<5>

H1

DQ<6>

H3

DQ<7>

F3

DQM

F7

DQS

E8

DQS

U5B

U5B

BGA84

BGA84

COMMON

COMMON

2/2

2/2

F1

DQ<0>

H7

DQ<1>

H9

DQ<2>

H3

DQ<3>

H1

DQ<4>

G2

DQ<5>

G8

DQ<6>

F9

DQ<7>

F3

DQM

F7

DQS

E8

DQS

Place near signal transition area

IN

FBVDDQ

C39

C39

.01UF

.01UF

25V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

GND

E GC

FBVDDQ

FBVDDQ

C48

C510

C510

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

GND

FBVDDQ

C42

C42

.1UF

.1UF

10V

10V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

GND

FBVDDQ

C38

C38

C36

C36

.01UF

.01UF

.01UF