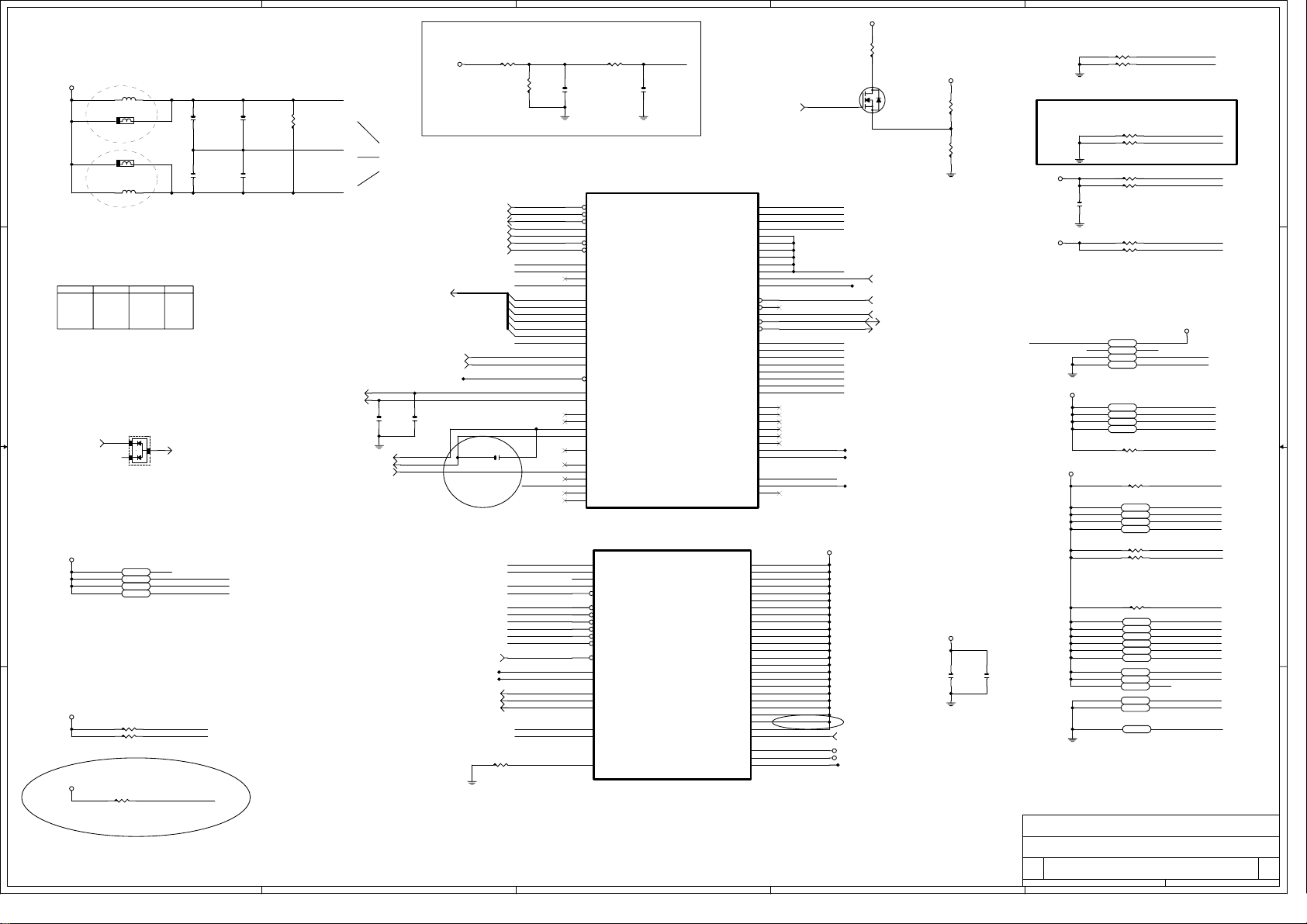

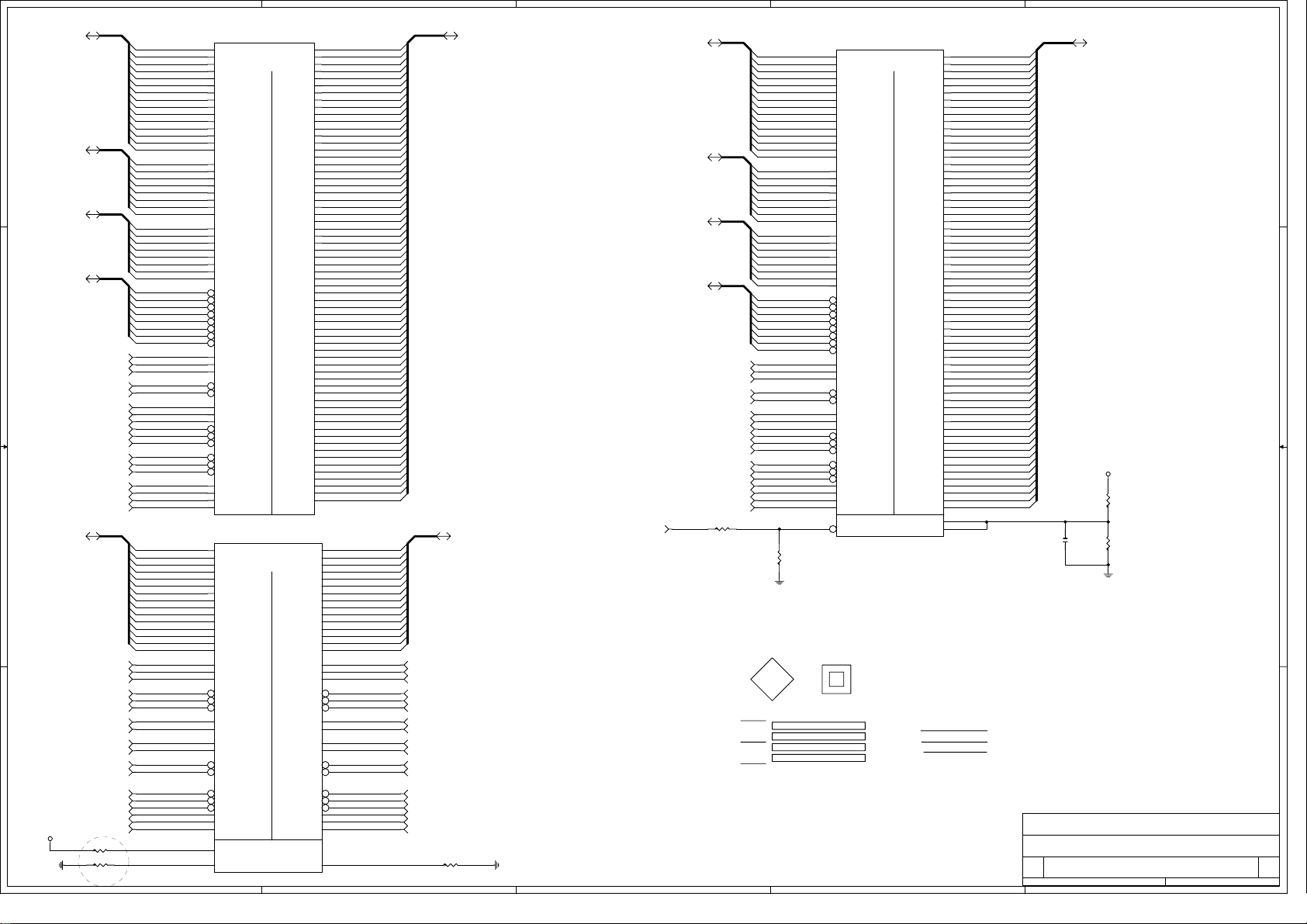

Gigabyte GA-8n-sli quad royal Schematic REV.1.1

5

4

3

Model Name:GA-8N-SLI QUAD ROYAL (NVIDIA)

2

1

SHEET TITLE

D D

01

02

03

04~06

07

08

C C

09

10

11

12

13

14

15

COVER SHEET

BLOCK DIAGRAM

BOM & PCB MODIFY HISTORY

INTEL LGA775

C19 HOST

C19 PCIE, HT

C19 POWER

CK804 HOST, PCIE

CK804 PCI, LPC, IDE, SATA

CK804 USB, AC97, MII

CK804 POWER

DDRII CHANNEL A

Revision 1.1

16 DDRII CHANNEL B

B B

17

DDRII TERMINATOR

SHEET TITLE

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

DUAL LPC BIOS

ITE 8712HX_GB LPC IO

HARDWARE MONITOR

IDE, FDD

KB & PS2 MOUSE & FUSE

FRONT PANNEL

PROCHOT# & FAN CONTROLC19 DIMM

COM & LPT PORT

F_USB & R_USB & 1394 CONNECTOR

AC97 ALC850

AUDIO JACK

TI TSB43AB23PDT

VRM 10.1/ISL6556

MISC. & DISCRETE POWER

DISCRETE POWER(ISL6537)

18

19

20

21

22

23

A A

24

0.2 PCB Vendor:

C19 PCI EXPRESS * 16 SLOT

C19 PCI EXPRESS * 16 SLI

CK804 PCI EXPRESS * 16 SLOT

CK804 PCI EXPRESS * 16 SLI

WINBOND W83L951F

GBIT LAN PHY 88E1111

PCI SLOT

育富,祥裕

5

4

40

ATX POWER CONNECTOR

AGERE ET1310 LOM41

42 GPIO/RESET TABLE

COMPONENT SIDE

(1 oz. Copper)

VCC SIDE

(1 oz. Copper)

GND SIDE

(1 oz. Copper)

SOLDER SIDE

(1 oz. Copper)

3

2

Title

Size Document Number Rev

Custom

Date: Sheet

Gigabyte Technology

Cover Sheet

GA-8N-SLI QUAD ROYAL

142Monday, October 17, 2005

1

of

1.1

5

4

3

2

1

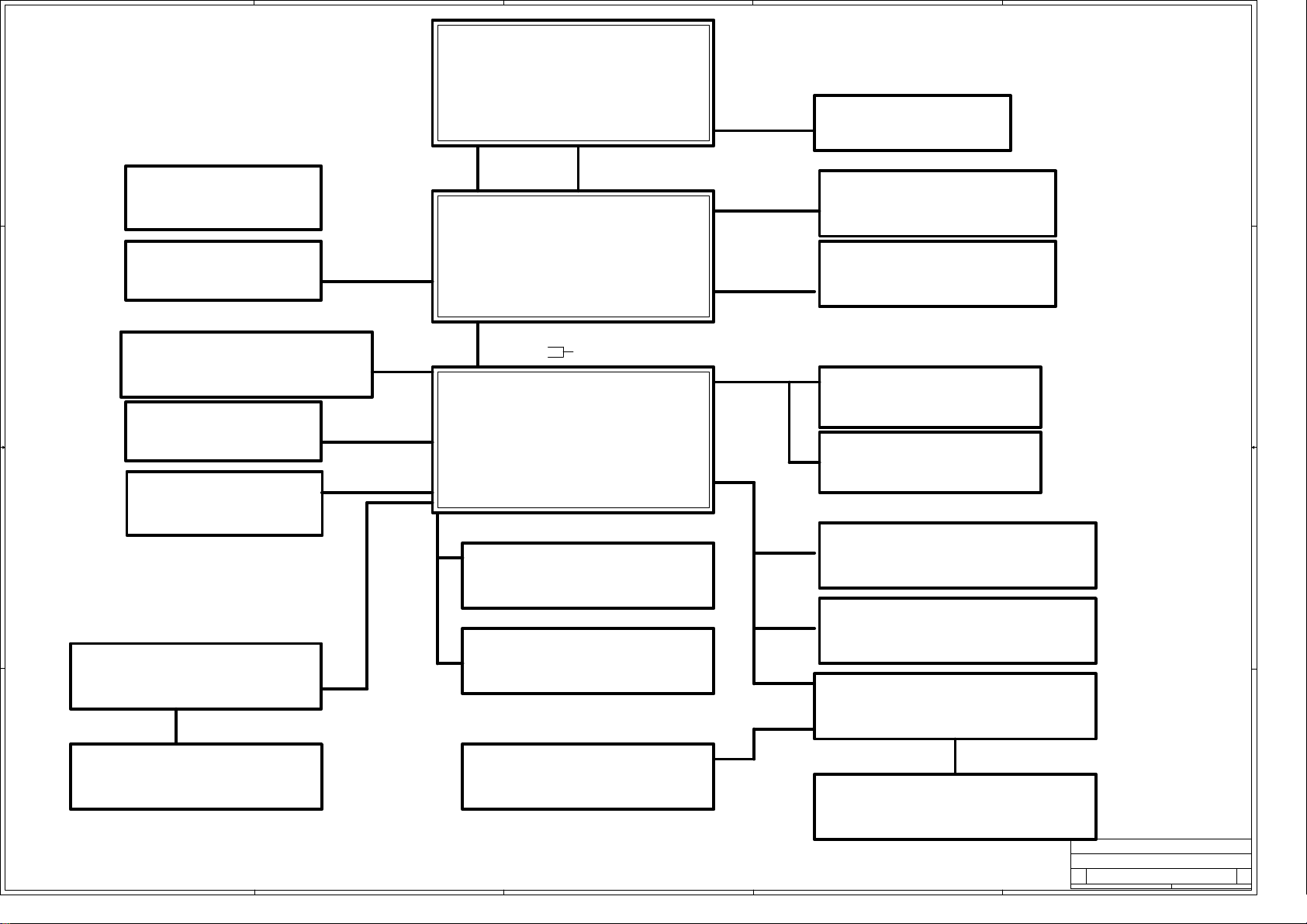

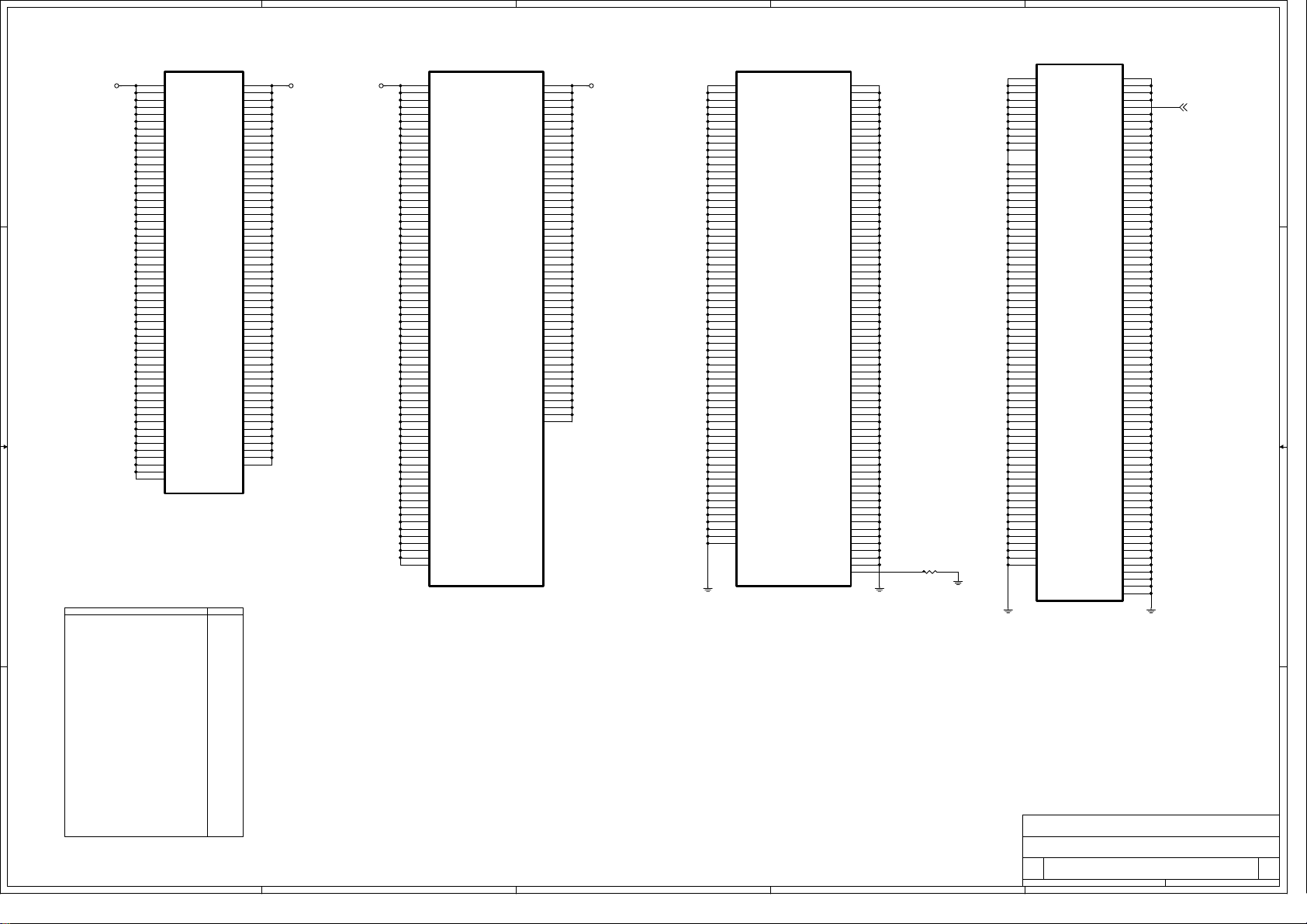

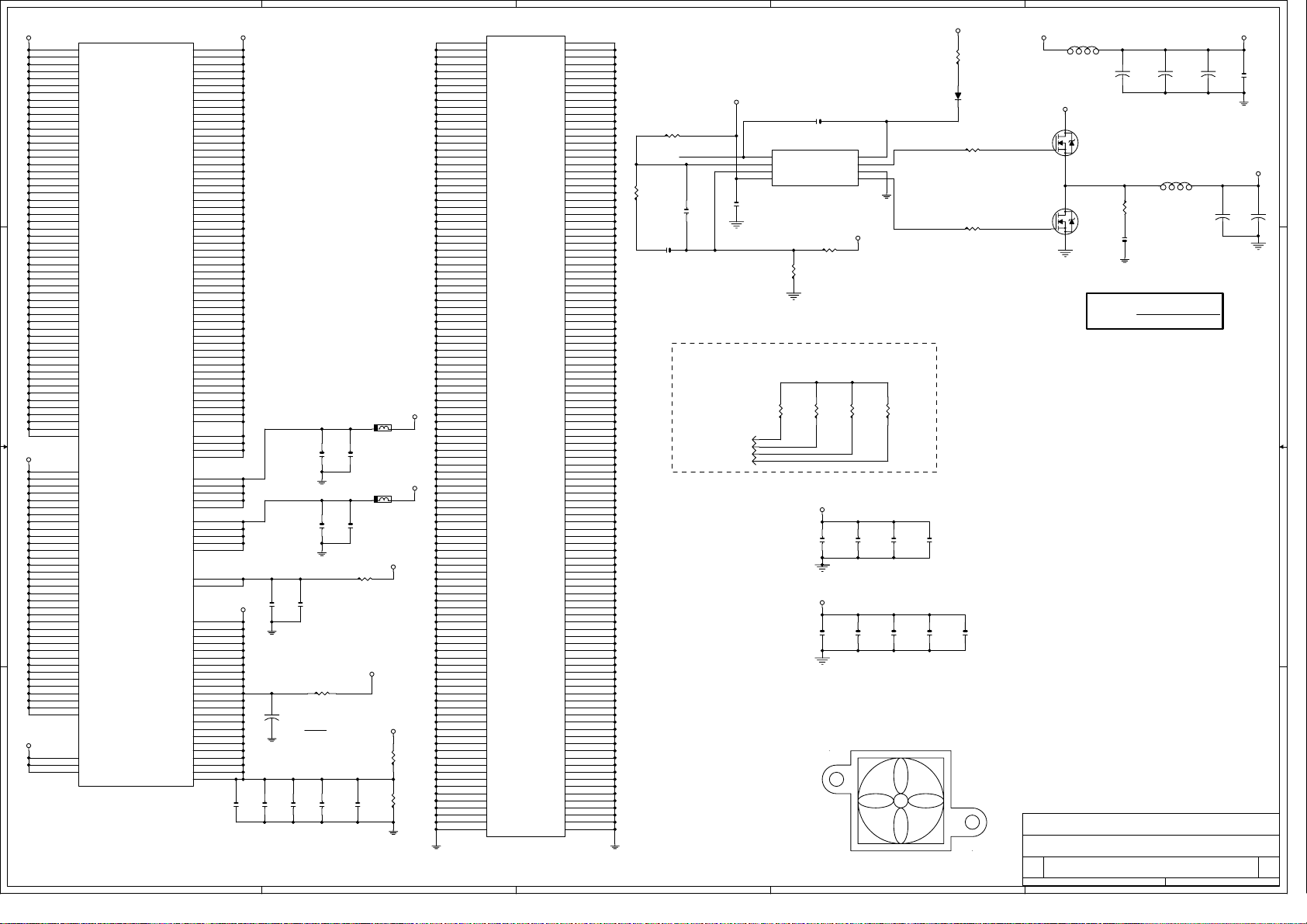

BLOCK DIAGRAM

INTEL Pentium4

LGA775

D D

VCORE = 1.75V / SLEEP : 1.3V

VCC3

PAGE 4, 5, 6

VID0~4

AGERE ET1310 LOM

VDDQ = 1.5V (AGP POWER 4X)

VCC3 = 3.3V

+12V = 12V

3VDUAL = 3.3V

VCC = 5V

PAGE 41

PCI EXPRESS

VDDQ = 1.5V (AGP POWER 4X)

VCC3 = 3.3V

+12V = 12V

3VDUAL = 3.3V

VCC = 5V

C C

GBIT PHY

PAGE 18,19

MARVELL

88E1111

PCI EXPRESS

VDDQ = 1.5V (AGP POWER 4X)

VCC3 = 3.3V

+12V = 12V

3VDUAL = 3.3V

VCC = 5V

PAGE 20,21

USB PORTS 0~9

VCC = 5V

5VSB = 5V

5VUSB = 5V

B B

PAGE 27

GAD0~31

ADSTB0,ADSTB0ADSTB1,ADSTB1SBA0~7

SBSTB,SBSTB-

GCBE0~3ST0~2

PAGE 23

USB

GMII

3GIO

3GIO

CRUSH 19

SPP

37.5mmX37.5mm,

1mm ball pitch PBGA1040

VCORE = 1.75V / SLEEP : 1.3V

2_5VSTR = 2.5V(MEMORY)

VDDQ = 1.5V (AGP POWER 4X, HUBLINK)

8 up, 8 down

CONTROL BUS

PAGE 7 ,8 ,9,10

HT LINK

NFORCE4

CK8 04

BGA740

VCC25 = 2.5V(I/O,MEMORY/I,VLINK/I)

3VDUAL = 3.3V(SUSPEND POWER)

VCC3 = 3.3V

RTCVDD = 3.3V

PAGE 11,12,13,14

PCI BUS

PCI SLOT 1

+12 = 12V

-12 = -12V

VCC = 5V

VCC3 = 3V

3VDUAL = 3V

PAGE 24

MAA0~14

MAA_CPC1~5

MAB_CPC1~5

MDD0~63

-DQSD0~7

DM0~7

LPC BUS

TI TSB43AB23PDT

AC97 ALC850

+12V = 12V

VCC3 = 3.3V

VCC = 5V

AVDD = 5V

PAGE 29

AC97 LINK

PAGE 36

LPC BUS

PWM/OTHER POWER

VCORE = 1.75V (650-1100MHZ) / SLEEP : 1.3V

5VSB,-12V,+12V,VCC,VCC3,3VDUAL

VTT_DDR,2_5VSTR

PAGE 37,38,39,40

CHANNEL A

DDRII SDRAM DIMM X 2

2_5VSTR = 2.5V(MEMORY,SUSPEND POWER)

VTT_DDR = 1.25V

PAGE 15,17

CHANNEL B

DDRII SDRAM DIMM X 2

2_5VSTR = 2.5V(MEMORY,SUSPEND POWER)

VTT_DDR = 1.25V

PAGE 16,17

IDE Primary

VCC = 5V

PAGE 28

SERIAL ATA

VCC = 5V

PAGE 12

DUAL BIOS/HWMO/FAN CONTRL

VCC = 5V

VCC3 = 3V

PAGE 25,27,31

WINBOND W83L951F

PAGE 22

LPC I/O ITE8712G

VCC = 5V

5VSB = 5V

VBAT = 3V

PAGE 6

AUDIO PORTS :

CD_IN

LINE_IN

AUX_IN

A A

LIN_ OUT

TELE

FRONT AUDIO

MIC

PAGE 30, 31

FRONT PANEL /CPU FAN

VCC = 5V

5VSB = 5V

+12 = 12V

PVCC = 5V

PAGE 28

I/O PORTS :

COMB

LPT

COMA

PS2

IR

FDD

PAGE 26,28,29

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet

Gigabyte Technology

Block Diagram

GA-8N-SLI QUAD ROYAL

1

242Monday, October 17, 2005

1.1

of

5

4

3

2

1

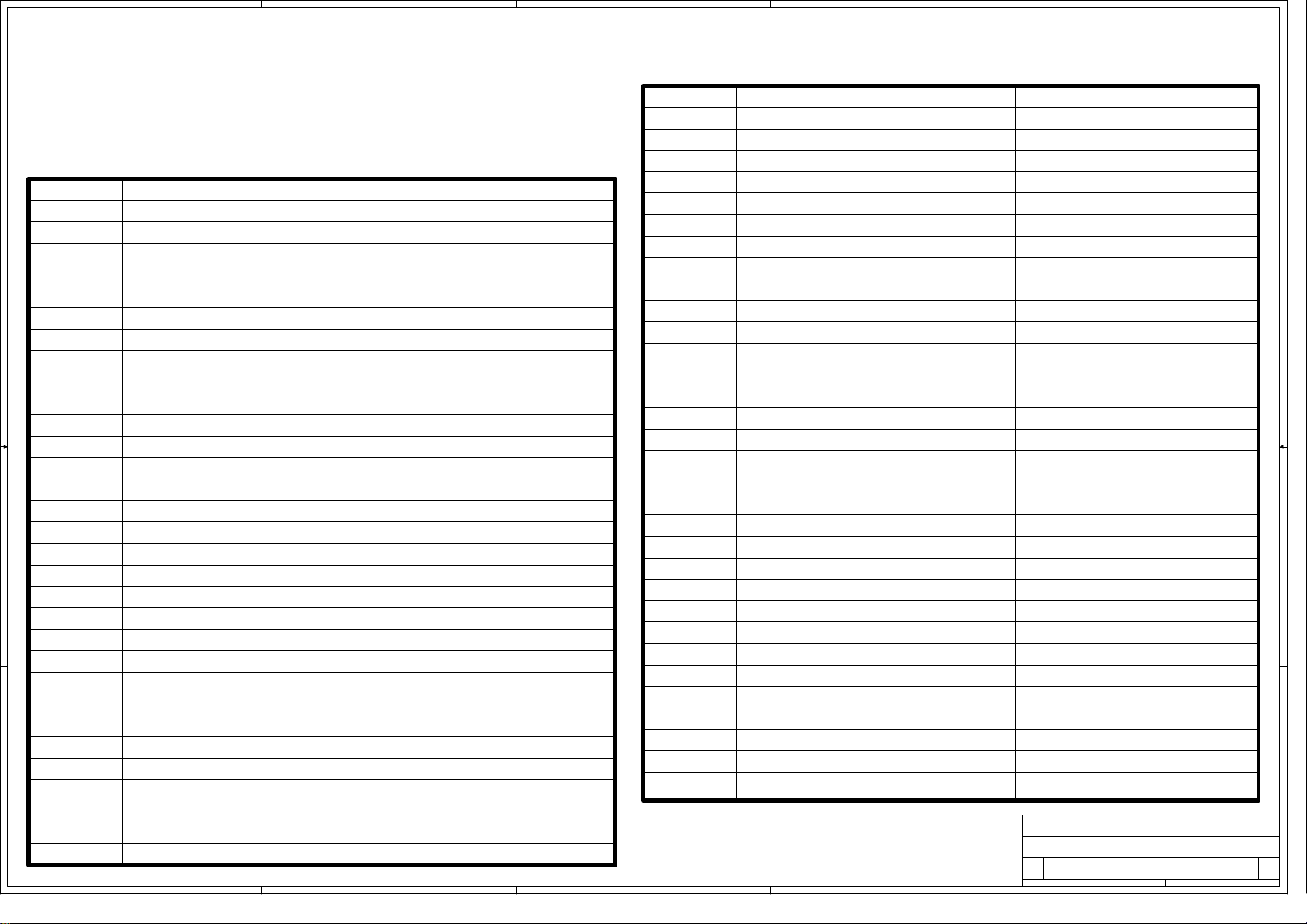

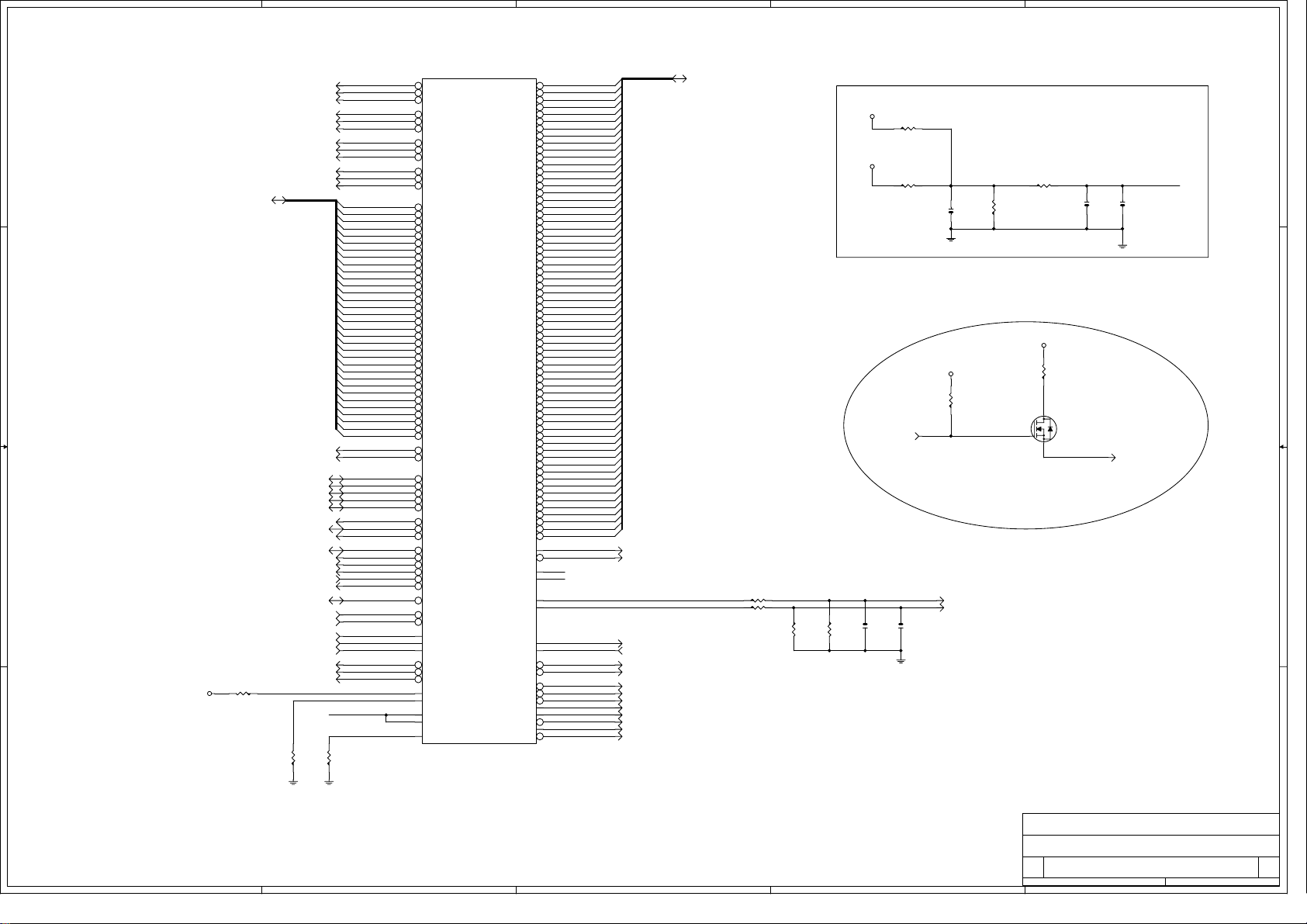

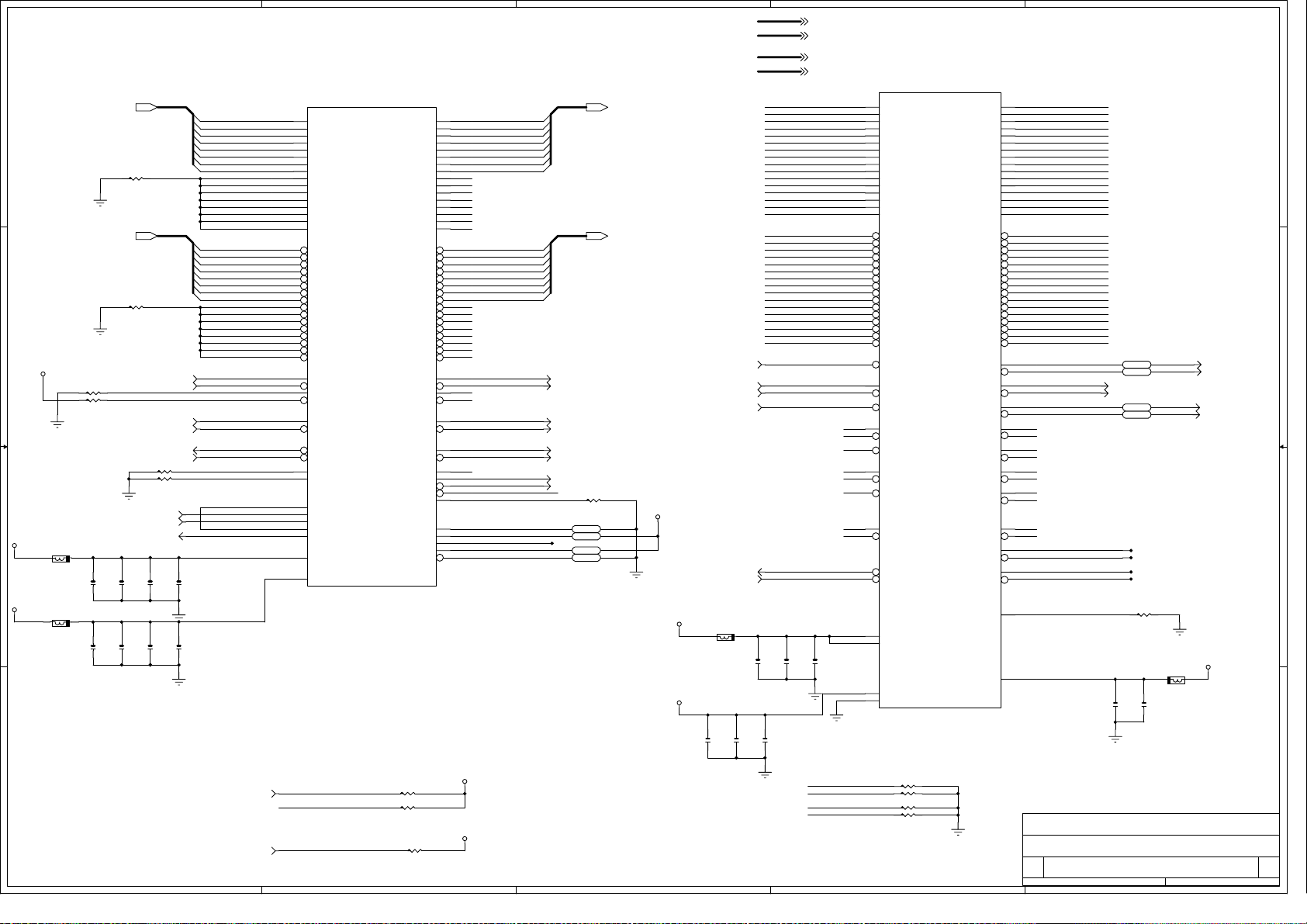

Model Name: GA-8N-SLI QUAD ROYAL

Circuit or PCB layout change

for next version

Version: 0.3

PAGE Change Item Reason

D D

Component value change history

Data Reason

94.5.22_0.1 1'st pilot run BOM

94.5.30_0.1 ITE8712A VIN3/ATXPG should be high.

C C

94.7.05_0.2 2'st pilot run BOM

B B

Change Item

PI2PCIE412ZHE symbol is wrong.

W83L951F Global Reset connect to RSMRST

ET1310 LAN disable connect to RSMRST

Power: R258, C538

W83L951F: ADC control is only for GPI, when

ADC enable.

Add RF_ID94.7.07_0.2

EC14 change to 1000uF

C19_MEM_VTT connect to DDRVTT by 0 ohm

C10, C11, C49 must be installed

C53 change from 0.1u to 4.7u

CENTER and LFE miss connect

C32, C37, C39 change to 2.2u to pass Freq. Resp

BAT54A to qualify CPUVDD_EN for 3.46G

Function: force 200 CPU to use 266 strapping

A A

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet

Gigabyte Technology

BOM & PCB MODIFY HISTORY

GA-8N-SLI QUAD ROYAL

1

of

342Monday, October 17, 2005

1.1

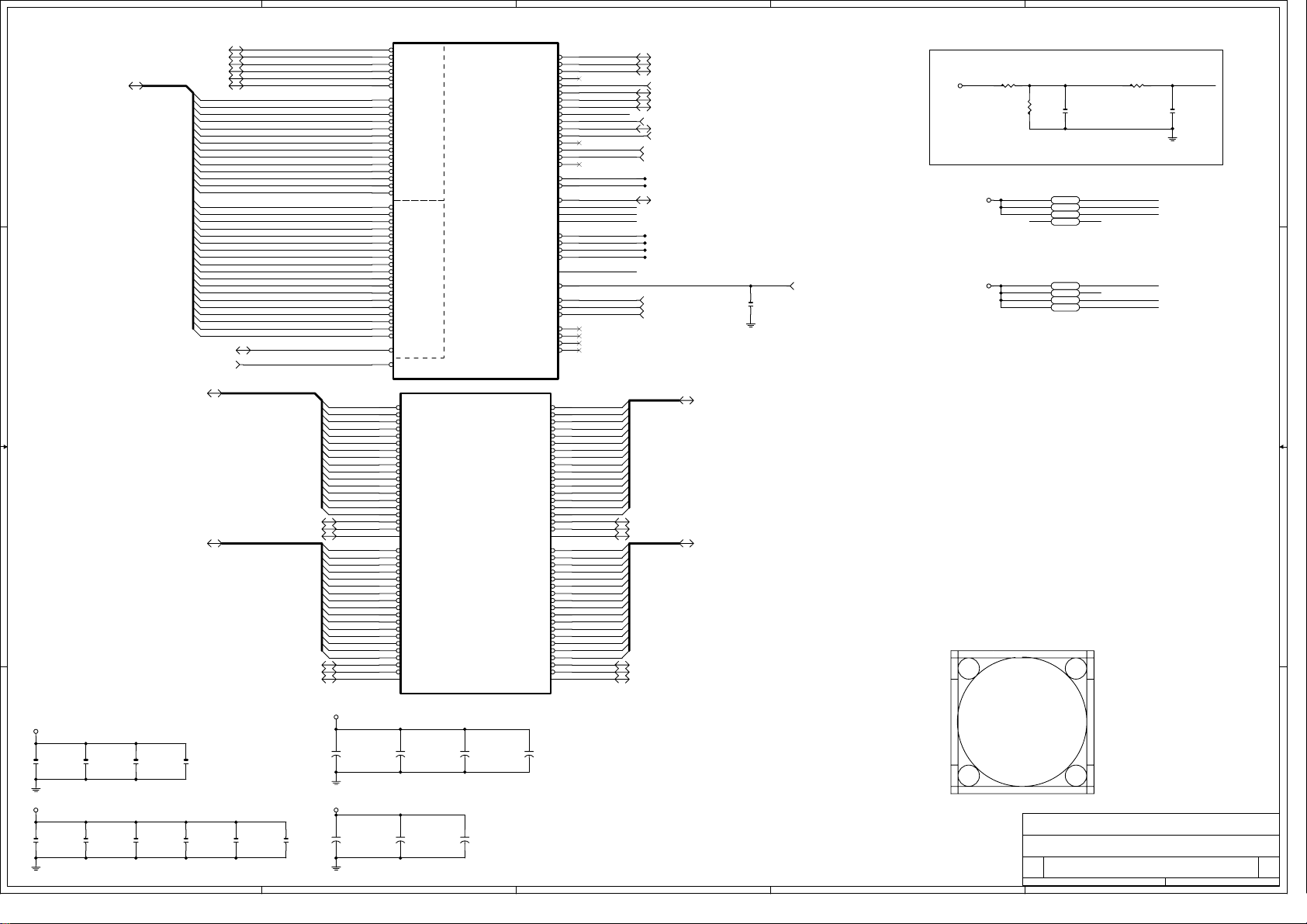

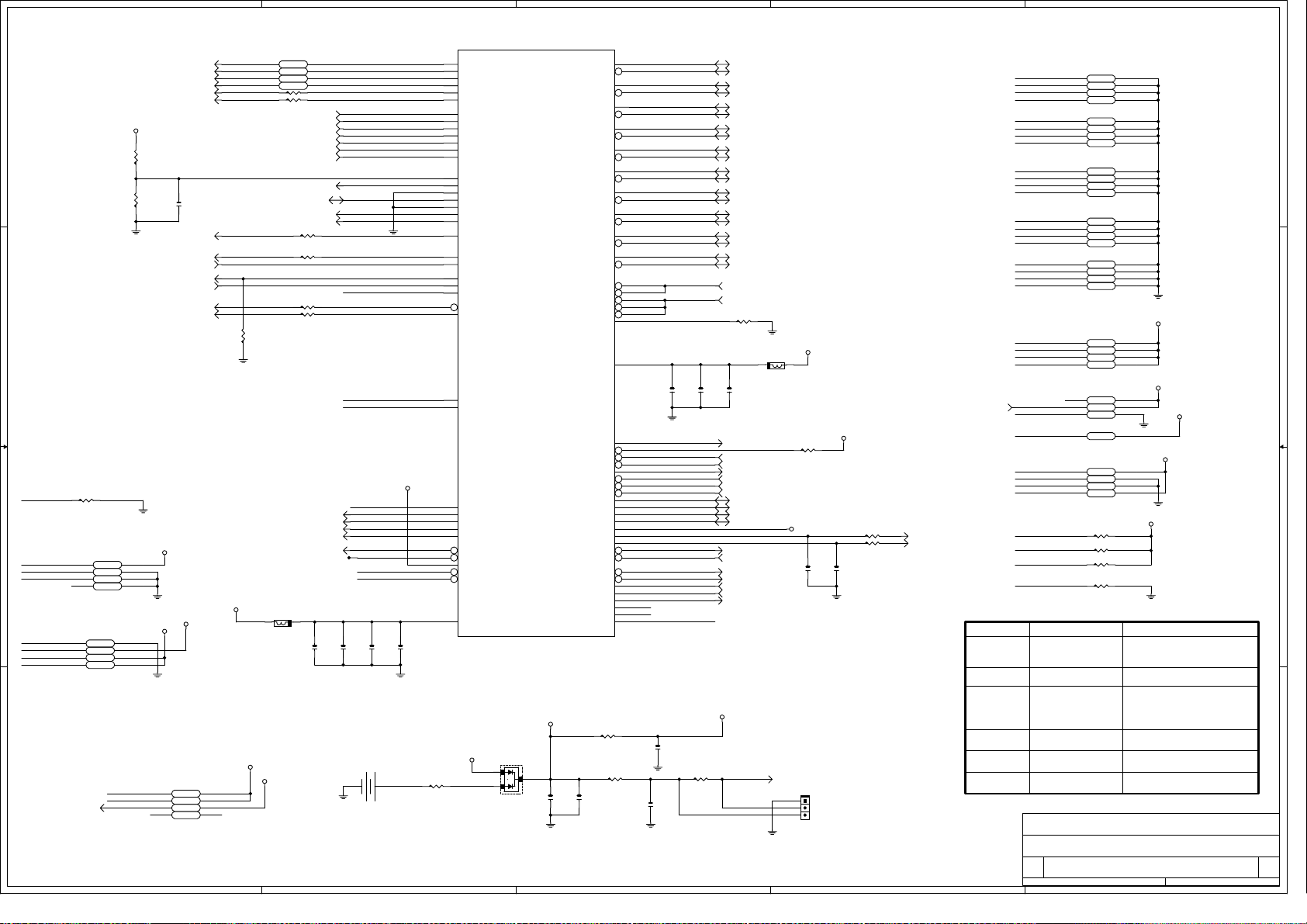

5

-HADSTB0{7}

-HREQ0{7}

-HREQ1{7}

-HREQ2{7}

HA[3..35]{7}

D D

C C

B B

SP-CAP 4pcs與10U 10 pcs Co-Layout

VCORE

C220

10u/X5R/X

A A

VCORE

C343

10u/X5R

C218

10u/X5R/X

C345

10u/X5R

C356

10u/X5R

C327

10u/X5R

5

-HREQ3{7}

-HREQ4{7}

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA17

HA18

HA19

HA20

HA21

HA22

HA23

HA24

HA25

HA26

HA27

HA28

HA29

HA30

HA31

HA32

HA33

HA34

HA35

-HADSTB1{7}

-HPCREQ{7}

HD[0..15]{7}

-DBI0{7}

STBN0{7}

HD[16..31]{7}

C347

10u/X5R

C316

10u/X5R

C328

10u/X5R

STBP0{7}

-DBI1{7}

STBN1{7}

STBP1{7}

C330

10u/X5R

VCORE

+

VCORE

+

4

U19A

R6

ADSTB0#

K4

REQ0#

J5

REQ1#

M6

REQ2#

K6

REQ3#

J6

REQ4#

L5

A03#

P6

A04#

M5

A05#

L4

A06#

M4

A07#

R4

A08#

T5

A09#

U6

A10#

T4

A11#

U5

A12#

U4

A13#

V5

A14#

V4

A15#

W5

A16#

AB6

A17#

W6

A18#

Y6

A19#

Y4

A20#

AA4

A21#

AD6

A22#

AA5

A23#

AB5

A24#

AC5

A25#

AB4

A26#

AF5

A27#

AF4

A28#

AG6

A29#

AG4

A30#

AG5

A31#

AH4

A32#

AH5

A33#

AJ5

A34#

AJ6 AC4

A35# RSVD

AD5

ADSTB1#

G5

PCREQ#/FC7

U19B

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

C321

100U/9mohm/X

LGA775

B4

D00#

C5

D01#

A4

D02#

C6

D03#

A5

D04#

B6

D05#

B7

D06#

A7

D07#

A10

D08#

A11

D09#

B10

D10#

C11

D11#

D8

D12#

B12

D13#

C12

D14#

D11

D15#

A8

DBI0#

C8

DSTBN0#

B9

DSTBP0

G9

D16#

F8

D17#

F9

D18#

E9

D19#

D7

D20#

E10

D21#

D10

D22#

F11

D23#

F12

D24#

D13

D25#

E13

D26#

G13

D27#

F14

D28#

G14

D29#

F15

D30#

G15

D31#

G11

DBI1#

G12

DSTBN1#

E12

DSTBP1

LGA775

+

C649

100U/9mohm/X

+

C219

100U/9mohm/X

SP-CAP X 3PCS (Solder Side)

C353

100U/9mohm/X

4

+

C344

100U/9mohm/X

+

C329

100U/9mohm/X

DBSY#

DRDY#

LOCK#

TRDY#

BINIT#

DEFER#

EDRDY#

MCERR#

TESTHI08

TESTHI09

TESTHI10

GTLREF

RESET#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DBI2#

DSTBN2#

DSTBP2

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBI3#

DSTBN3#

DSTBP3

+

ADS#

BNR#

HIT#

RSP#

BPRI#

HITM#

IERR#

INIT#

AP0#

AP1#

BR0#

DP0#

DP1#

DP2#

DP3#

RS0#

RS1#

RS2#

RSVD

RSVD

RSVD

G16

E15

E16

G18

G17

F17

F18

E18

E19

F20

E21

F21

G21

E22

D22

G22

D19

G20

G19

D20

D17

A14

C15

C14

B15

C18

B16

A17

B18

C21

B21

B19

A19

A22

B22

C20

A16

C17

C648

100U/9mohm/X

D2

C2

D4

H4

G8

B2

C1

E4

AB2

P3

C3

E3

AD3

G7

F2

AB3

U2

U3

F3

G3

G4

H5

J16

H15

H16

J17

H1

G23

B3

F5

A3

AE4

P5

N4

-IERR

TP_CPU_U2

TP_CPU_U3

TESTHI8

TESTHI9

TESTHI10

TP_CPU_J16

TP_CPU_H15

TP_CPU_H16

TP_CPU_J17

GTLREF

-CPURST

-RS0

-RS1

-RS2

HD32

HD33

HD34

HD35

HD36

HD37

HD38

HD39

HD40

HD41

HD42

HD43

HD44

HD45

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

3

-HADS {7}

-BNR {7}

-HIT {7}

-BPRI {7}

-DBSY {7}

-DRDY {7}

-HITM {7}

*

-HINIT {7}

-HLOCK {7}

-HTRDY {7}

-DEFER {7}

-EDRDY {7}

TP13

TP12

-BR0 {7}

TP4

TP5

TP2

TP3

-RS0 {7}

-RS1 {7}

-RS2 {7}

-DBI2 {7}

STBN2 {7}

STBP2 {7 }

-DBI3 {7}

STBN3 {7}

STBP3 {7 }

3

HD[32..47] {7}

HD[48..63] {7}

C274

22P/X

-CPURST {7}

2

Closed to Pin-H1

VTT_OR

2

R223

124 1%

GTLREF VOLTAGE SHOULD BE 0.63XVTT= 0.76V (FOR THIS DESIGN)

VTT_OL

VTT_OL

GTLREF_R

R221

210 1%

CR1

CPU RETAINTION/X

Title

Size Document Number Rev

Custom

Date: Sheet

C413

1u

1 2

62

3 4

62

5 6

62

7 8

62

1 2

62

3 4

62

5 6

62

7 8

62

0.63*VTT

R202

RN34A

RN34B

RN34C

RN34D

RN33A

RN33B

RN33C

RN33D

GA-8N-SLI QUAD ROYAL

1

GTLREF

10

C408

220P

TESTHI8

TESTHI9

TESTHI10

-IERR

-CPURST

-BR0

Gigabyte Technology

P4_LGA775-A,B

of

1

442Monday, October 17, 2005

1.1

5

AC low-pass:

1. < 0.2dB in pass band

2. < 0.5dB below 1Hz

3. 34dB attenuation from 1MHz to 66MHz

4. 28dB over 66MHz

VTT_GMCH

L9

10uH 100mA/X

D D

C C

B B

A A

FB5

220/0.2A

FB4

220/0.2A

L8

10uH 100mA/X

下一版加

10U between

VSSA & VCOREPLL

BSEL2 BSEL1 BSEL0

000266

110 100

00 10

01 -> 01

10 10

11 01 , no 166 CPU

BSEL1_GPO{26}

VTT_GMCH

RN18D

RN18C

RN18B

RN18A

C19

Remove Pull-up requirement on the following FSB

async signals: CPU_A20M#, CPU_FERR#, CPU_IGNNE#,

CPU_SMI#, CPU_STPCLK#, CPU_INIT#, CPU_SLP#.

VTT_OR

VTT_OR

R207 62

Q68

BAT54A-7 30V 0.2A

680

680

680

680

R209 150

R208 150

1 13300

00 2001

10 1661

BSEL1 {7}

78

56

34

12

-THRMTRIP

INTR

NMI

C265

1u

C261

1u

BSEL2

BSEL1

BSEL0

Note:

VCCA & VCOREPLL

define doesn't same as

old P4 design kit

C272

10u/X5R

C254

10u/X5R

VCCA

R161

0

VSSA

VCOREPLL

As close as possible to

CPU socket

CPU_TEMP{26,27}

THERMDC{26,27}

VCC_SENSE{27,37}

VSS_SENSE{37}

C19_GTLREF{7}

4

VTT_OR

Trace width doesn't

less than 12 Mil

VID[0..5]{37}

CPUCLK{7}

-CPUCLK{7}

C410

C409

1n/X

1n/X

Place inner

CPUsocket

由內層拉兩條

3

Closed to Pin-H2

R224

124 1%

GTLREF VOLTAGE SHOULD BE 0.63XVTT= 0.76V (FOR THIS DESIGN)

-STPCLK{7}

TP6

C372 10u/X

GTLREF1_R GTLREF1

R215

210 1%

-SMI{7}

-A20M{7}

-FERR{7}

INTR{7}

NMI{7}

-IGNNE{7}

VCCA

VSSA

VCOREPLL

VID0

VID1

VID2

VID3

VID4

VID5

VID_SEL

NC_SKTOCC

GTLREF1

Trace

TCK

TDI

TMS

-TRST

-BPM0

-BPM1

-BPM2

-BPM3

-BPM4

-BPM5

-RST_BTN{13,22,30}

TP10

TP14

BSEL0{7}

BSEL1{7}

BSEL2{7}

R244

H_ITPCLK

-H_ITPCLK

MSID0

MSID1

IMPSEL

62/X

GND : 50 OHM

NC: 60 OHM

0.63*VTT

R201 10

C417

1u

P2

K3

R3

K1

L1

N2

M3

A23

B23

D23

C23

AM2

AL5

AM3

AL6

AK4

AL4

AN7

F28

G28

AE8

AL1

AK1

AN3

AN4

AN5

AN6

F29

J3

E24

F23

H2

E23

AM5

AE1

AD1

AF1

AC1

AG1

AJ2

AJ1

AD2

AG2

AF2

AG3

AC2

AK3

AJ3

G29

H30

G30

W1

V1

E6

U19C

SMI#

A20M#

FERR#/PBE#

LINT0

LINT1

IGNNE#

STPCLK#

VCCA

VSSA

RSVD

VCCIOPLL

VID0

VID1

VID2

VID3

VID4

VID5

VID_SELECT

BCLK0

BCLK1

SKTOCC#

THERMDA

THERMDC

VCC_SENSE

VSS_SENSE

RSVD

RSVD

VTT_PKGSENSE

N/C

F10

N/C

GTLREF1

N/C

RSVD

LGA775

U19D

TCK

TDI

TDO

TMS

TRST#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

DBR#

ITPCLK0

ITPCLK1

BSEL0

BSEL1

BSEL2

MSID0

MSID1

IMPSEL

C407

220P

LGA775

TESTHI00

TESTHI01

TESTHI11

TESTHI12

TESTHI02

TESTHI03

TESTHI04

TESTHI05

TESTHII06

TESTHI07

RSVD

RSVD

SLP#

RSVD

PWRGOOD

PROCHOT#

THERMTRIP#

COMP0

COMP1

COMP2

COMP3

COMP4

COMP5

COMP6

COMP7

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

BOOTSELECT

LL_ID0

LL_ID1

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTTPWRGD

VTT_OUT

VTT_OUT

VTT_SEL

GTL_DET pull-up

8.2K at NB page

GTL_DET{6,7}

F26

W3

P1

W2

F25

G25

G27

G26

G24

F24

AK6

G6

L2

AH2

N1

AL2

M2

A13

T1

G2

R1

J2

T2

Y3

AE3

N5

AE6

C9

G10

D16

A20

E7

N/C

F6

N/C

Y1

V2

AA2

A29

B25

B29

B30

C29

A26

B27

C28

A25

A28

A27

C30

A30

C25

C26

C27

B26

D27

D28

D25

D26

B28

D29

D30

AM6

AA1

J1

VTT_SEL

F27

VCC3

2

G

For Exterme CPU

P4 Extreme: 1.5V

Other: 1.2V

TESTHI0

TESTHI1

TESTHI11

TESTHI12

TESTHI2_7

RSVD_G6

COMP0

COMP1

COMP2

COMP3

COMP4

COMP5

COMP6

COMP7

TP_CPU_E7

TP_CPU_F6

NC_BOOTSEL

LL_ID0

VTT SELECT CONTROL OUTPUT

VTT_GMCH

TP1

TP8

TP7

TP9

internal P-U

TP15

LLID[1:0]=00

VTT_SEL=1

GTLREF_SEL=0

D29, D30 short

to VTT_GMCH

VTT_PWRGD {37,39}

VTT_OR

VTT_OL

2

R165

249 1%

-GTL_DET

31

D

Q21

2N7002

S

TESTHI0

-FORCEPR {31}

-CPUSLP {7}

CPUPWROK {7}

-PROCHOT {7,31}

-THRMTRIP {7,22}

VCC3

VTT_OR

R162

110 1%

R163

61.9 1%

C420

0.1u

1

Place outside of CPU socket

R182 60.4 1%

R206 60.4 1%

COMP0

COMP1

Reserved for SMITHFIELD CPU

RN62A

RN62B

RN62C

RN62D

RN31B

RN31A

RN31C

RN31D

VTT_OR

CPUPWROK

RN28A

RN28B

RN28C

RN28D

RN29B

RN29A

RN29C

RN29D

RN30A

RN30B

RN30C

RN30D

RN32A

RN32B

RN32C

RN32D

COMP2

COMP3

COMP4

COMP5

COMP6

COMP7

MSID0

MSID1

TESTHI2_7

TESTHI11

TESTHI12

TESTHI1

VTT_PWRGD

-PROCHOT

VID_SEL

R211 60.4 1%

R210 60.4 1%

VTT_OL

VTT_OR

-FORCEPR

C421

0.1u

VTT_OUT_RIGH: VTT_PWRGD,VID[5:0],GTLREF,TMS,TDI,TDO,BPM[50]

VTT_OUT_LEFT: RESET#,BR0#,PWRGOOD,TESTHI1,8,9,10,11,12

R229 60.4 1%

R227 60.4 1%

C411

0.1u

R204 60.4 1%

R203 60.4 1%

1 2

62

3 4

62

5 6

62

7 8

62

VTT_OL

3 4

62

1 2

62

5 6

62

7 8

62

R228 100

VTT_OR

R234 680

1 2

680

3 4

680

5 6

680

7 8

680

R557 680

R558 680

Smithfield PRB=1 will only boot if MSID is low.

R225 150

3 4

51

1 2

51

5 6

51

7 8

51

1 2

51

3 4

51

5 6

51

7 8

51

1 2

51

3 4

51

5 6

51

7 8

51

-BPM5

-BPM4

-BPM0

-BPM1

-BPM2

-BPM3

-TRST

VID2

VID5

VID0

VID4

VID1

VID3

TMS

TDI

TCK

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet

Gigabyte Technology

P4_LGA775-B

GA-8N-SLI QUAD ROYAL

1

of

542Monday, October 17, 2005

1.1

5

4

3

2

1

U19E

VID1

VID2

0

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

00

0

1

1

1

1

1

1

1

1

0

0

1

1

5

AC23

AC24

AC25

AC26

AC27

AC28

AC29

AC30

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AE11

AE12

AE14

AE15

AE18

AE19

AE21

AE22

AE23

AF11

AF12

AF14

AF15

AF18

AF19

AF21

AF22

AG11

AG12

AG14

AG15

AG18

AG19

AG21

AG22

AG25

AG26

AG27

AG28

AG29

AG30

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

1

1

1

1

0

0

0

1

1

1

1

AA8

AB8

AC8

AD8

AE9

AF8

AF9

AG8

AG9

VID0

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

0

0

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

10

0

0

1

1

0

1

1

LGA775

VID12.5

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

VCORE VCOREVCORE VCORE

D D

C C

B B

VID4

VID3

1

1

1

1

1

0

0

1

0

1

0

1

0

1

0

1

1

0

1

0

1

0

1

0

0

1

0

1

0

0

1

0

1

1

0

1

0

0

1

0

1

1

0

0

A A

1

1

0

1

0

0

1

1

0

0

1

1

0

1

1 OFF

11

1

VDAC

1.2500

1.2625

1.2750

1.28751

1.3000

1.3125

1.3250

1.3375

1.3500

1.3625

1.3750

1.3875

1.4000

1.41251

1.4250

1.4375

1.4500

1.4625

1.4750

1.4875

1.5000

1.5125

1.5250

1.5375

1.5500

1.5625

1.5750

1.58750

1.6000

OFF

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AH11

AH12

AH14

AH15

AH18

AH19

AH21

AH22

AH25

AH26

AH27

AH28

AH29

AH30

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

U19F

AM11

VCC

AM12

VCC

AM14

VCC

AM15

VCC

AM18

VCC

AM19

VCC

AM21

VCC

AM22

VCC

AM25

VCC

AM26

VCC

AM29

VCC

AM30

VCC

AM8

VCC

AM9

VCC

AN11

VCC

AN12

VCC

AN14

VCC

AN15

VCC

AN18

VCC

AN19

VCC

AN21

VCC

AN22

VCC

AN25

VCC

AN26

VCC

AN29

VCC

AN30

VCC

AN8

VCC

AN9

VCC

J10

VCC

J11

VCC

J12

VCC

J13

VCC

J14

VCC

J15

VCC

J18

VCC

J19

VCC

J20

VCC

J21

VCC

J22

VCC

J23

VCC

J24

VCC

J25

VCC

J26

VCC

J27

VCC

J28

VCC

J29

VCC

J30

VCC

J8

VCC

J9

VCC

K23

VCC

K24

VCC

K25

VCC

K26

VCC

K27

VCC

K28

VCC

K29

VCC

K30

VCC

K8

VCC

L8

VCC

M23

VCC

M24

VCC

M25

VCC

M26

VCC

M27

VCC

M28

VCC

M29

VCC

M30

VCC

M8

VCC

LGA775

4

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

N23

N24

N25

N26

N27

N28

N29

N30

N8

P8

R8

T23

T24

T25

T26

T27

T28

T29

T30

T8

U23

U24

U25

U26

U27

U28

U29

U30

U8

V8

W23

W24

W25

W26

W27

W28

W29

W30

W8

Y23

Y24

Y25

Y26

Y27

Y28

Y29

Y30

Y8

3

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA30

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE20

AE24

AE25

AE26

AE27

AE28

AE29

AE30

AF10

AF13

AF16

AF17

AF20

AF23

AF24

AF25

AF26

AF27

AF28

AF29

AF30

U19G

A12

VSS

A15

VSS

A18

VSS

A2

VSS

A21

VSS

A24

VSS

A6

VSS

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AA3

VSS

VSS

AA6

VSS

AA7

VSS

AB1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE5

VSS

AE7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF3

VSS

VSS

AF6

VSS

AF7

VSS

LGA775

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AG10

AG13

AG16

AG17

AG20

AG23

AG24

AG7

AH1

AH10

AH13

AH16

AH17

AH20

AH23

AH24

AH3

AH6

AH7

AJ10

AJ13

AJ16

AJ17

AJ20

AJ23

AJ24

AJ27

AJ28

AJ29

AJ30

AJ4

AJ7

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

AK30

AK5

AK7

AL10

AL13

AL16

AL17

AL20

AL23

AL24

AL27

AL28

AL3

AL7

AM1

AM10

AM13

AM16

AM17

AM20

AM23

AM24

AM27

AM28

AM4

AM7

CPU_AM7

2

R205

0/X

U19H

AN1

VSS

AN10

VSS

AN13

VSS

AN16

VSS

AN17

VSS

AN2

VSS

AN20

VSS

AN23

VSS

AN24

VSS

AN27

VSS

AN28

VSS

B1

VSS

B11

VSS

B14

VSS

B17

VSS

B20

VSS

B24

VSS

B5

VSS

B8

VSS

C10

VSS

C13

VSS

C16

VSS

C19

VSS

C22

VSS

C24

VSS

C4

VSS

C7

VSS

D12

VSS

D15

VSS

D18

VSS

D21

VSS

D24

VSS

D3

VSS

D5

VSS

D6

VSS

D9

VSS

E11

VSS

E14

VSS

E17

VSS

E2

VSS

E20

VSS

E25

VSS

E26

VSS

E27

VSS

E28

VSS

E29

VSS

E8

VSS

F10

VSS

F13

VSS

F16

VSS

F19

VSS

F22

VSS

F4

VSS

F7

VSS

G1

VSS

H10

VSS

H11

VSS

H12

VSS

H13

VSS

H14

VSS

H17

VSS

H18

VSS

H19

VSS

H20

VSS

H21

VSS

H22

VSS

H23

VSS

H24

VSS

LGA775

Title

Size Document Number Rev

Custom

Date: Sheet

Gigabyte Technology

GA- 8N-SLI QUAD ROYAL

H25

VSS

H26

VSS

H27

VSS

H28

VSS

H29

VSS

H3

VSS

H6

VSS

H7

VSS

H8

VSS

H9

VSS

J4

VSS

J7

VSS

K2

VSS

K5

VSS

K7

VSS

L23

VSS

L24

VSS

L25

VSS

L26

VSS

L27

VSS

L28

VSS

L29

VSS

L3

VSS

L30

VSS

L6

VSS

L7

VSS

M1

VSS

M7

VSS

N3

VSS

N6

VSS

N7

VSS

P23

VSS

P24

VSS

P25

VSS

P26

VSS

P27

VSS

P28

VSS

P29

VSS

P30

VSS

P4

VSS

P7

VSS

R2

VSS

R23

VSS

R24

VSS

R25

VSS

R26

VSS

R27

VSS

R28

VSS

R29

VSS

R30

VSS

R5

VSS

R7

VSS

T3

VSS

T6

VSS

T7

VSS

U1

VSS

U7

VSS

V23

VSS

V24

VSS

V25

VSS

V26

VSS

V27

VSS

V28

VSS

V29

VSS

V3

VSS

V30

VSS

V6

VSS

V7

VSS

W4

VSS

W7

VSS

Y2

VSS

Y5

VSS

Y7

VSS

P4_LGA775-D

1

GTL_DET {5,7}

of

642Monday, October 17, 2005

1.1

5

4

3

2

1

U24A

CPU I/F

C19

SEC

1 OF 8

CPU_D10*

CPU_D11*

CPU_D12*

CPU_D13*

CPU_D14*

CPU_D15*

CPU_D16*

CPU_D17*

CPU_D18*

CPU_D19*

CPU_D20*

CPU_D21*

CPU_D22*

CPU_D23*

CPU_D24*

CPU_D25*

CPU_D26*

CPU_D27*

CPU_D28*

CPU_D29*

CPU_D30*

CPU_D31*

CPU_D32*

CPU_D33*

CPU_D34*

CPU_D35*

CPU_D36*

CPU_D37*

CPU_D38*

CPU_D39*

CPU_D40*

CPU_D41*

CPU_D42*

CPU_D43*

CPU_D44*

CPU_D45*

CPU_D46*

CPU_D47*

CPU_D48*

CPU_D49*

CPU_D50*

CPU_D51*

CPU_D52*

CPU_D53*

CPU_D54*

CPU_D55*

CPU_D56*

CPU_D57*

CPU_D58*

CPU_D59*

CPU_D60*

CPU_D61*

CPU_D62*

CPU_D63*

CPU_PWRGOOD

CPU_RESET*

CPU_ITP_CLK0

CPU_ITP_CLK1

CPU_BCLK0

CPU_BCLK1

CPU_BPRI*

CPU_DEFER*

CPU_A20M*

CPU_IGNNE*

CPU_INIT*

CPU_INTR

CPU_SMI*

CPU_STPCLK*

CPU_D0*

CPU_D1*

CPU_D2*

CPU_D3*

CPU_D4*

CPU_D5*

CPU_D6*

CPU_D7*

CPU_D8*

CPU_D9*

CPU_FC5

CPU_FC7

CPU_NMI

CPU_SLP

P4

AG4

AG3

AD5

AE7

AC9

AA5

AC3

M10

AF3

P2

N3

W5

W7

T10

Y3

N8

L7

L10

N7

N6

L5

J4

J8

L9

J7

H8

J6

H7

H5

E5

H6

G6

G5

F5

F8

F6

G8

F7

E6

E8

D8

A3

C4

B3

A5

A4

C5

B4

L6

E7

N4

R5

L8

N9

H3

J5

F3

H1

H2

R6

G3

K2

H4

A8

D3

D4

J3

M3

J2

C6

B6

E4

F2

D5

CPU_DSTBP0*

CPU_DSTBN0*

CPU_DBI0*

CPU_DSTBP1*

CPU_DSTBN1*

CPU_DBI1*

CPU_DSTBP2*

CPU_DSTBN2*

CPU_DBI2*

CPU_DSTBP3*

CPU_DSTBN3*

CPU_DBI3*

CPU_A3*

CPU_A4*

CPU_A5*

CPU_A6*

CPU_A7*

CPU_A8*

CPU_A9*

CPU_A10*

CPU_A11*

CPU_A12*

CPU_A13*

CPU_A14*

CPU_A15*

CPU_A16*

CPU_A17*

CPU_A18*

CPU_A19*

CPU_A20*

CPU_A21*

CPU_A22*

CPU_A23*

CPU_A24*

CPU_A25*

CPU_A26*

CPU_A27*

CPU_A28*

CPU_A29*

CPU_A30*

CPU_A31*

CPU_A32*

CPU_A33*

CPU_A34*

CPU_A35*

CPU_ADSTB0*

CPU_ADSTB1*

CPU_REQ0*

CPU_REQ1*

CPU_REQ2*

CPU_REQ3*

CPU_REQ4*

CPU_ADS*

CPU_BNR*

CPU_BR0*

CPU_DBSY*

CPU_DRDY*

CPU_HIT*

CPU_HITM*

CPU_LOCK*

CPU_TRDY*

CPU_PROCHOT*

CPU_THERMTRIP*

CPU_FERR*

CPU_BSEL2

CPU_BSEL1

CPU_BSEL0

CPU_RS0*

CPU_RS1*

CPU_RS2*

CPU_DRV0_VTT

CPU_DRV1_GND

CPU_GTL_VREF

CPU_GTL_VREF

CPU_CTERM_GND

STBP0{4}

STBN0{4}

-DBI0{4}

-PROCHOT{5,31}

-THRMTRIP{5,22}

-HADSTB0{4}

-HADSTB1{4}

-HREQ0{4}

-HREQ1{4}

-HREQ2{4}

-HREQ3{4}

-HREQ4{4}

-HADS{4}

-BNR{4}

-DBSY{4}

-HLOCK{4}

-HTRDY{4}

-FERR{5}

BSEL2{5}

BSEL1{5}

BSEL0{5}

R188

60.4 1%

STBP1{4}

STBN1{4}

STBP2{4}

STBN2{4}

STBP3{4}

STBN3{4}

-BR0{4}

-DRDY{4}

-HITM{4}

-DBI1{4}

-DBI2{4}

-DBI3{4}

-HIT{4}

-RS0{4}

-RS1{4}

-RS2{4}

CPU_DRV0_VTT

CPU_DRV1_GND

C19_GTLREF

CPU_CTERM_GND

R190

511 1%

CPU Clock BIAS Control

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA17

HA18

HA19

HA20

HA21

HA22

HA23

HA24

HA25

HA26

HA27

HA28

HA29

HA30

HA31

HA32

HA33

HA34

HA35

D D

HA[3..35]{4}

C C

B B

R189 60.4 1%

VTT_OR

A A

K4

M4

K3

M1

L3

M2

N2

N5

T4

T2

T3

T1

P3

U2

U3

U5

U8

P10

U7

U6

R8

U9

R3

U4

W6

W8

W9

V10

Y5

AA6

AA7

AA8

AA4

V4

AA9

AC8

AC5

Y10

AC7

AC6

AB10

AE6

AE8

AE4

AF5

AE9

AE2

AD10

AD4

AA2

V2

Y4

V3

W3

AB2

Y2

Y1

AA3

AD2

AD3

AB4

AB3

AD1

AE5

C2

AE10

B8

C7

AE3

AF2

F4

R7

T5

R9

E3

C1

C3

E1

D1

B2

D2

M5

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

HD32

HD33

HD34

HD35

HD36

HD37

HD38

HD39

HD40

HD41

HD42

HD43

HD44

HD45

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

CPU_BCLK0

CPU_BCLK1

CPUPWROK {5}

-CPURST {4}

-EDRDY {4}

-HPCREQ {4}

-BPRI {4}

-DEFER {4}

-A20M {5}

-IGNNE {5}

-HINIT {4}

INTR {5}

NMI {5}

-SMI {5}

-CPUSLP {5}

-STPCLK {5}

HD[0..63] {4}

R177 33

R178 33

R174

60.4 1%

R173

60.4 1%

VTT_OL

VTT_OR

C308

10P/X

R187

R186

100 1%

C19_GTLREF_R

100 1%

C358

0.1u

+12V

R181

8.2K

GTL_DET{5,6}

For Exterme CPU

Extreme: 0.63*VTT+0.1V (Hi)

Other: 0.63*VTT (Low)

CPUCLK {5}

-CPUCLK {5}

C309

10P/X

For extreme edition:

northwood core - VTT_OL != VTT_OR.

R184 35.7 1%

R185

82.5 1%

VCORE

2

G

C19_GTLREF_D

31

D

S

C357

0.1u

R183

619 1%

Q24

2N7002

C19_GTLREF

C19_GTLREF

C361

220P

C19_GTLREF {5}

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet

Gigabyte Technology

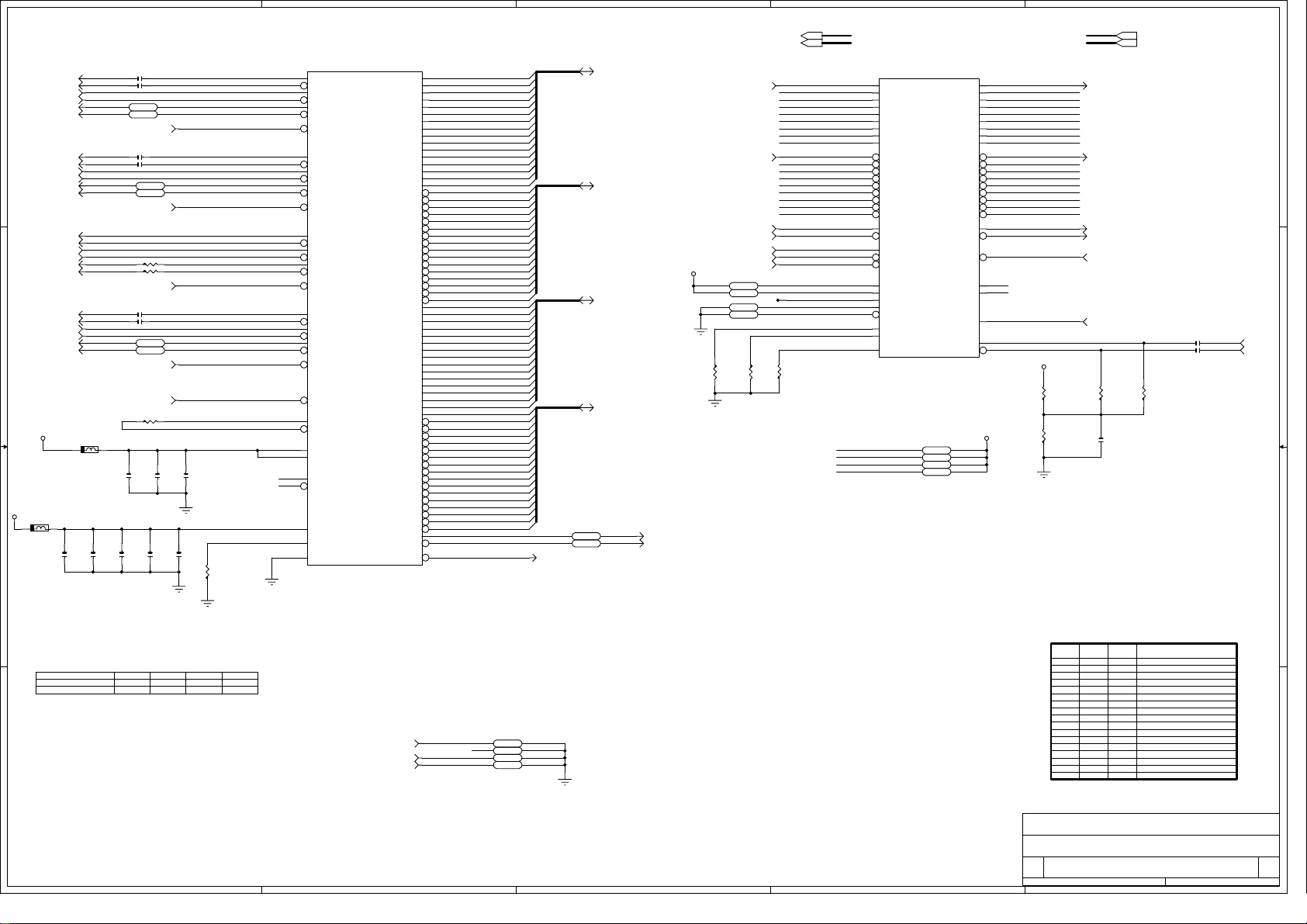

C19 HOST

GA- 8N-SLI QUAD ROYAL

1

of

742Monday, October 17, 2005

1.1

5

4

3

2

1

-HT_UP[7:0]

HT_UP[7:0] -HT_DWN[7:0]

AP29

AT29

AP6

AN6

AP5

AR6

AR5

AT5

AN1

AR4

AT4

AR3

AT3

AP2

AR2

AN2

AM8

AN7

AK8

AL8

AN4

AP4

AM1

AM6

AL6

AM7

AL7

AP8

AR8

AM2

AN3

AM5

AL5

AK2

AK5

AK3

AJ8

AJ7

U24B

C19

PE1_TX0

PE1_TX0*

PE1_RX0

PE1_RX0*

PE1_REFCLK

PE1_REFCLK*

PE1_PRSNT*

PE2_TX0

PE2_TX0*

PE2_RX0

PE2_RX0*

PE2_REFCLK

PE2_REFCLK*

PE2_PRSNT*

PE3_TX0

PE3_TX0*

PE3_RX0

PE3_RX0*

PE3_REFCLK

PE3_REFCLK*

PE3_PRSNT*

PE4_TX0

PE4_TX0*

PE4_RX0

PE4_RX0*

PE4_REFCLK

PE4_REFCLK*

PE4_PRSNT*

PE0_PRSNT*

PE_CLK_TEST

PE_CLK_TEST*

+3.3V_PLL1

+3.3V_PLL2

PE_CLKIN

PE_CLKIN*

VDD_PE_PLL_CORE

PE_CTERM_GND

GND_PE_PLL

SEC

2 OF 8

PCI EXP I/F

PE0_TX15

PE0_TX14

PE0_TX13

PE0_TX12

PE0_TX11

PE0_TX10

PE0_TX9

PE0_TX8

PE0_TX7

PE0_TX6

PE0_TX5

PE0_TX4

PE0_TX3

PE0_TX2

PE0_TX1

PE0_TX0

PE0_TX15*

PE0_TX14*

PE0_TX13*

PE0_TX12*

PE0_TX11*

PE0_TX10*

PE0_TX9*

PE0_TX8*

PE0_TX7*

PE0_TX6*

PE0_TX5*

PE0_TX4*

PE0_TX3*

PE0_TX2*

PE0_TX1*

PE0_TX0*

PE0_RX15

PE0_RX14

PE0_RX13

PE0_RX12

PE0_RX11

PE0_RX10

PE0_RX9

PE0_RX8

PE0_RX7

PE0_RX6

PE0_RX5

PE0_RX4

PE0_RX3

PE0_RX2

PE0_RX1

PE0_RX0

PE0_RX15*

PE0_RX14*

PE0_RX13*

PE0_RX12*

PE0_RX11*

PE0_RX10*

PE0_RX9*

PE0_RX8*

PE0_RX7*

PE0_RX6*

PE0_RX5*

PE0_RX4*

PE0_RX3*

PE0_RX2*

PE0_RX1*

PE0_RX0*

PE0_REFCLK

PE0_REFCLK*

PE_RESET*

AN20

AN18

AR18

AR17

AT16

AP16

AP15

AP14

AP13

AT13

AT12

AN12

AN10

AR10

AR9

AT8

AP20

AP19

AP18

AP17

AT17

AR16

AN16

AN14

AR14

AR13

AR12

AP12

AP11

AP10

AP9

AT9

AM19

AN17

AK17

AJ17

AK16

AM15

AJ15

AM13

AK13

AJ13

AK12

AN11

AJ11

AN9

AK9

AJ9

AN19

AM17

AL17

AH17

AM16

AN15

AH15

AM14

AL13

AH13

AM12

AM11

AH11

AM9

AL9

AH9

AP7

AN8

AP1

PE0_TXC15

PE0_TXC14

PE0_TXC13

PE0_TXC12

PE0_TXC11

PE0_TXC10

PE0_TXC9

PE0_TXC8

PE0_TXC7

PE0_TXC6

PE0_TXC5

PE0_TXC4

PE0_TXC3

PE0_TXC2

PE0_TXC1

PE0_TXC0

-PE0_TXC15

-PE0_TXC14

-PE0_TXC13

-PE0_TXC12

-PE0_TXC11

-PE0_TXC10

-PE0_TXC9

-PE0_TXC8

-PE0_TXC7

-PE0_TXC6

-PE0_TXC5

-PE0_TXC4

-PE0_TXC3

-PE0_TXC2

-PE0_TXC1

-PE0_TXC0

PE0_RX15

PE0_RX14

PE0_RX13

PE0_RX12

PE0_RX11

PE0_RX10

PE0_RX9

PE0_RX8

PE0_RX7

PE0_RX6

PE0_RX5

PE0_RX4

PE0_RX3

PE0_RX2

PE0_RX1

PE0_RX0

-PE0_RX15

-PE0_RX14

-PE0_RX13

-PE0_RX12

-PE0_RX11

-PE0_RX10

-PE0_RX9

-PE0_RX8

-PE0_RX7

-PE0_RX6

-PE0_RX5

-PE0_RX4

-PE0_RX3

-PE0_RX2

-PE0_RX1

-PE0_RX0

C19_PCIE_CLK0

-C19_PCIE_CLK0

-NB_PE_RESET {18,19,21,41}

RN25C

RN25D

33

100 1%

C447

0.1u

RN24A

RN24B

RN24C

RN24D

C450

0.01u

C342

0.01u

PE1_TX0

-PE1_TX0

C19_PE1_CLK

-C19_PE1_CLK

PE2_TX0

-PE2_TX0

C19_PE2_CLK

-C19_PE2_CLK

C19_PE3_CLK

-C19_PE3_CLK

PE4_TX0

-PE4_TX0

C19_PE4_CLK

-C19_PE4_CLK

C19_PE_CLK_TEST

-C19_PE_CLK_TEST

C19_PE_PLL

PE_CLK_COMP

C19_VCC3_PLL

If external PCIE Clock

R170

3.09K 1%

FB15

30/4A

2A

C366 0.1u

C375 0.1u

5 6

7 8

-NB_PE1_PRSNT{21}

C225 0.1u

C230 0.1u

-NB_PE2_PRSNT{21}

R179 33

R180

-NB_PE3_PRSNT{19}

C112 0.1u

C108 0.1u

-NB_PE4_PRSNT{41}

-NB_PE0_PRSNT{18,24}

R176

C682

4.7u

33

33

1 2

33

3 4

33

5 6

33

7 8

33

C461

4.7u

C333

C320

0.1u

4.7u

PCIE_OP1{21}

PCIE_ON1{21}

PCIE_IP1{21}

PCIE_IN1{21}

PCIE_CLK1{21}

-PCIE_CLK1{21}

D D

PCIE_OP2{21}

PCIE_ON2{21}

PCIE_IP2{21}

PCIE_IN2{21}

PCIE_CLK2{21}

-PCIE_CLK2{21}

PCIE_OP3{19}

PCIE_ON3{19}

PCIE_IP3{19}

PCIE_IN3{19}

PCIE_SLI_CLK{19}

-PCIE_SLI_CLK{19}

PCIE_OP4{41}

PCIE_ON4{41}

PCIE_IP4{41}

PCIE_IN4{41}

C C

PCIE_CLK4{41}

-PCIE_CLK4{41}

VCC3

VCC1_4

FB8

DC 0.08/220/2A

C704

B B

10u/X5R

Shape, 10u*2 is better?

Critical : FB8 change to 0805

PE0_TXC[15:0] {18}

-PE0_TXC[15:0] {18}

PE0_RX[15:0] {18}

-PE0_RX[15:0] {18}

1 2

33

3 4

33

RN25A

RN25B

VCC1_4

PCIE_CLK0 {18}

-PCIE_CLK0 {18}

HT_UPCNTL{11}

-HT_UPCNTL{11}

HT_UPCLK0{11}

-HT_UPCLK0{11}

HT_PWRGD{11}

-HT_RESET{11}

-HT_STOP{11}

7 8

8.2K

5 6

8.2K

1 2

8.2K

3 4

8.2K

R199

49.9 1%

U24C

HT_UP7

HT_UP6

HT_UP5

HT_UP4

HT_UP3

HT_UP2

HT_UP1

HT_UP0 HT_DWN0

-HT_UP7

-HT_UP6

-HT_UP5

-HT_UP4

-HT_UP3

-HT_UP2

-HT_UP1

-HT_UP0

C19_TMS

RN20D

C19_TDI

RN20C

NC_C19_TDO

TP11

C19_TCK

RN20A

C19_TRST

RN20B

HT_RXCOMP

HT_TXCOMP

C19_TEST

R213

R171

150 1%

8.2K

AH25

AM25

AK25

AK24

AJ23

AM23

AN21

AJ21

AM20

AG25

AN25

AL25

AM24

AH23

AN23

AM21

AK21

AL21

AL23

AK23

AG19

AH19

AJ19

AG10

AJ5

AJ6

AJ3

AJ4

AH26

AG26

AM4

-HT_REQ

-HT_STOP

-HT_RESET

HT_PWRGD

C19

HT_RXCTL

HT_RXD7

SEC 3 OF 8

HT_RXD6

HT_RXD5

HT_RXD4

HT_RXD3

HT_RXD2

HT_RXD1

HT_RXD0

HT I/F

HT_RXCTL*

HT_RXD7*

HT_RXD6*

HT_RXD5*

HT_RXD4*

HT_RXD3*

HT_RXD2*

HT_RXD1*

HT_RXD0*

HT_RX_CLK

HT_RX_CLK*

HT_PWRGD

HT_RESET*

HT_STOP*

TMS

TDI

TDO

TCK

TRST*

HT_RX_COMP_GND

HT_TX_COMP_GND

TEST

1 2

4.7K

3 4

4.7K

5 6

4.7K

7 8

4.7K

HT_TXCTL

HT_TXD7

HT_TXD6

HT_TXD5

HT_TXD4

HT_TXD3

HT_TXD2

HT_TXD1

HT_TXD0

HT_TXCTL*

HT_TXD7*

HT_TXD6*

HT_TXD5*

HT_TXD4*

HT_TXD3*

HT_TXD2*

HT_TXD1*

HT_TXD0*

HT_TX_CLK

HT_TX_CLK*

HT_REQ*

NC1

NC2

25MHZ_IN

CLKIN

CLKIN*

RN26A

RN26B

RN26C

RN26D

VCC3

AR20

AT21

AP21

AP22

AP23

AT24

AR25

AR26

AN26

AT20

AR21

AR22

AN22

AN24

AT25

AP25

AP26

AP27

AP24

AR24

AK19

AL3

D7

AL4

AR30

AP30

HT_DWN7

HT_DWN6

HT_DWN5

HT_DWN4

HT_DWN3

HT_DWN2

HT_DWN1

-HT_DWN7

-HT_DWN6

-HT_DWN5

-HT_DWN4

-HT_DWN3

-HT_DWN2

-HT_DWN1

-HT_DWN0

C19_CLKIN

-C19_CLKIN

VCC3

R217

1.54K 1%

CLK_ACTERM

R216

511 1%

HT_DWNCNTL {11}

-HT_DWNCNTL {11}

HT_DWNCLK0 {11}

-HT_DWNCLK0 {11}

-HT_REQ {11}

C19_25MHZ_IN {13,23,41}

R198

49.9 1%

C414

0.01u

HT_DWN[7:0]

R212

49.9 1%

C412 3.9n

C406 3.9n

C19_CLK {11}

-C19_CLK {11}

Bus

Dev

Func

No.

No.

POSSIBLE PCIE Configuration

X16,X1,X1,X1,X1

X8,X8,X1,X1,X1 X

A A

PE2/2# PE3/3#

X

XXX

X

5

PE4/4#PE1/1#

NC X

C19: CLOCK can be set individually,

PRSNT# should be checked. P-L for always enable

1 2

-NB_PE1_PRSNT{21}

-NB_PE2_PRSNT{21}

-NB_PE3_PRSNT{19}

4

8.2K

3 4

8.2K

5 6

8.2K

7 8

8.2K

RN21A

RN21B

RN21C

RN21D

3

2

0 Host Bridge00

00 1 HT Contrl Reg

00 2 PLL and Misc Contrl 1

003

00 4 Clock trim contrl Reg

100

101

102

103

104

105

10 6 Memory Contrl Reg 7

200

400

500

600

70 0 PCIE Contrl 5

Title

Size Document Number Rev

Custom

Date: Sheet

Gigabyte Technology

GA- 8N-SLI QUAD ROYAL

Device

No.

PLL and Misc Contrl 2

Memory Contrl Reg 1

Memory Contrl Reg 2

Memory Contrl Reg 3

Memory Contrl Reg 4

Memory Contrl Reg 5

Memory Contrl Reg 6

PCIE Contrl 1

PCIE Contrl 2

PCIE Contrl 3

PCIE Contrl 4

C19 PCIE, HT

1

1.1

of

842Monday, October 17, 2005

5

4

3

2

1

MA1A[14..0]{16,17}

D D

DMB[0..7]{16}

DQSB[0..7]{16}

-DQSB[0..7]{16}

C C

SBA1A0{16,17}

SBA1A1{16,17}

SBA1A2{16,17}

-CS1A0{16,17}

-CS1A1{16,17}

DCLK1A0{16}

DCLK1A1{16}

DCLK1A2{16}

-DCLK1A0{16}

-DCLK1A1{16}

-DCLK1A2{16}

-SRAS1A{16,17}

-SCAS1A{16,17}

-SWE1A{16,17}

CKE1A0{16,17}

CKE1A1{16,17}

MODT1_A0{16,17}

MODT1_A1{16,17}

MA0A[14..0]{15,17} MA1B[14..0] {16,17}

B B

SBA0A0{15,17}

SBA0A1{15,17}

SBA0A2{15,17}

-SRAS0A{15,17}

-SCAS0A{15,17}

-SWE0A{15,17}

CKE0A0{15,17}

CKE0A1{15,17}

MODT0_A0{15,17}

MODT0_A1{15,17}

-CS0A0{15,17}

R195

R193

-CS0A1{15,17}

-DCLK0A0{15}

-DCLK0A1{15}

-DCLK0A2{15}

DCLK0A0{15}

DCLK0A1{15}

DCLK0A2{15}

A A

DDR18V

MA1A0

MA1A1

MA1A2

MA1A3

MA1A4

MA1A5

MA1A6

MA1A7

MA1A8

MA1A9

MA1A10

MA1A11

MA1A12

MA1A13

MA1A14

DMB0

DMB1

DMB2

DMB3

DMB4

DMB5

DMB6

DMB7

DQSB0

DQSB1

DQSB2

DQSB3

DQSB4

DQSB5

DQSB6

DQSB7

-DQSB0

-DQSB1

-DQSB2

-DQSB3

-DQSB4

-DQSB5

-DQSB6

-DQSB7

MA0A0

MA0A1

MA0A2

MA0A3

MA0A4

MA0A5

MA0A6

MA0A7

MA0A8

MA0A9

MA0A10

MA0A11

MA0A12

MA0A13

MA0A14

MEM_COMP_18V

35.7 1%

MEM_COMP_GN D MEM_COMP_VTT

35.7 1%

Change to 27 % for 1100MHz DDR

5

M27

W29

AC31

AG30

AM32

AC29

AG29

AL30

G17

G25

W28

AC30

AF28

AM31

AF30

AG31

AM33

AL34

N29

A34

B34

D33

E33

E31

E32

F30

F31

E28

F29

E29

U30

D29

H13

F17

H21

F25

K12

H17

K20

H25

V27

J13

J21

N33

N28

J27

R30

U31

L29

J17

L28

K16

R32

R28

R29

H27

G27

T32

U28

T34

A33

B33

B32

A32

D32

C32

D31

C31

B30

T36

C30

E30

Y34

B29

U32

T35

C29

U35

V33

V34

B28

C28

Y33

Y36

V35

Y35

P33

A16

P34

B16

E10

E11

U24D

C19

MA1A_0

MA1A_1

SEC

MA1A_2

4 OF 8

MA1A_3

MA1A_4

MA1A_5

MA1A_6

MA1A_7

MA1A_8

MA1A_9

MA1A_10

MA1A_11

MA1A_12

MA1A_13

MA1A_14

MDQM1_0

MDQM1_1

MDQM1_2

MDQM1_3

MDQM1_4

MDQM1_5

MDQM1_6

MDQM1_7

MDQS1_0

MDQS1_1

MDQS1_2

MDQS1_3

MDQS1_4

MDQS1_5

MDQS1_6

MDQS1_7

MDQS1_0*

MDQS1_1*

MDQS1_2*

MDQS1_3*

MDQS1_4*

MDQS1_5*

MDQS1_6*

MDQS1_7*

MBA1A_0

MBA1A_1

MBA1A_2

MCS1A_0*

MCS1A_1*

MCLK1A_0

MCLK1A_1

MCLK1A_2

MCLK1A_0*

MCLK1A_1*

MCLK1A_2*

MRAS_1A*

MCAS_1A*

MWE_1A*

MCKE1A_0

MCKE1A_1

MODT1A_0

MODT1A_1

U24F

MA0A_0

C19

MA0A_1

SEC

MA0A_2

6 OF 8

MA0A_3

MA0A_4

MA0A_5

MA0A_6

MA0A_7

MA0A_8

MA0A_9

MA0A_10

MA0A_11

MA0A_12

MA0A_13

MA0A_14

MBA0A_0

MBA0A_1

MBA0A_2

MRAS_0A*

MCAS_0A*

MWE_0A*

MCKE0A_0

MCKE0A_1

MODT0A_0

MODT0A_1

MCS0A_0*

MCS0A_1*

MCLK0A_0*

MCLK0A_1*

MCLK0A_2*

MCLK0A_0

MCLK0A_1

MCLK0A_2

MEM_DRV0_1P8V

MEM_DRV1_GND

MD1_0

MD1_1

MD1_2

MD1_3

MD1_4

MD1_5

MD1_6

MD1_7

MD1_8

MD1_9

MD1_10

MD1_11

MD1_12

MD1_13

MD1_14

MD1_15

MD1_16

MD1_17

MD1_18

MD1_19

MD1_20

MD1_21

MD1_22

MD1_23

MD1_24

MD1_25

MD1_26

MD1_27

MD1_28

MD1_29

MD1_30

MD1_31

DIMM 1

MD1_32

MD1_33

MD1_34

MD1_35

MD1_36

MD1_37

MD1_38

MD1_39

MD1_40

MD1_41

MD1_42

MD1_43

MD1_44

MD1_45

MD1_46

MD1_47

MD1_48

MD1_49

MD1_50

MD1_51

MD1_52

MD1_53

MD1_54

MD1_55

MD1_56

MD1_57

MD1_58

MD1_59

MD1_60

MD1_61

MD1_62

MD1_63

MA1B_0

MA1B_1

MA1B_2

MA1B_3

MA1B_4

MA1B_5

MA1B_6

MA1B_7

MA1B_8

MA1B_9

MA1B_10

MA1B_11

MA1B_12

MA1B_13

MA1B_14

MBA1B_0

MBA1B_1

MBA1B_2

DIMM 0

DIMM 3

MRAS_1B*

MCAS_1B*

MWE_1B*

MCKE1B_0

MCKE1B_1

MODT1B_0

MODT1B_1

MCS1B_0*

MCS1B_1*

MCLK1B_0*

MCLK1B_1*

MCLK1B_2*

MCLK1B_0

MCLK1B_1

MCLK1B_2

MEM_TERM_GND

F13

G13

F15

G15

J11

E12

D13

E15

K14

E16

H19

J19

H15

J15

D18

G19

F21

G21

F23

G23

K18

E20

D21

E23

K22

E24

J25

E27

H23

J23

D25

K24

W32

W30

AA30

AA29

T27

W31

Y32

AA31

Y27

AC32

AD32

AE31

AA28

AA33

AC28

AB27

AE33

AD27

AJ32

AJ31

AE29

AE28

AG28

AJ30

AL32

AK30

AK29

AN30

AK32

AK31

AJ29

AL29

F35

G31

E36

G32

F32

E34

F34

D35

D36

D34

H32

C36

C35

H29

B35

G34

F33

C34

H31

G29

H30

K26

F27

P27

U33

R31

U29

N30

F19

AH32

N31

E19

AG32

F11

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

MDB40

MDB41

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

MDB48

MDB49

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

MDB56

MDB57

MDB58

MDB59

MDB60

MDB61

MDB62

MDB63

MA1B0

MA1B1

MA1B2

MA1B3

MA1B4

MA1B5

MA1B6

MA1B7

MA1B8

MA1B9

MA1B10

MA1B11

MA1B12

MA1B13

MA1B14

SBA1B0 {16}

SBA1B1 {16}

SBA1B2 {16}

-SRAS1B {16,17}

-SCAS1B {16,17}

-SWE1B {16,17}

CKE1B0 {16,17}

CKE1B1 {16,17}

MODT1_B0 {16,17}

MODT1_B1 {16,17}

-CS1B0 {16,17}

-CS1B1 {16,17}

-DCLK1B0 {16}

-DCLK1B1 {16}

-DCLK1B2 {16}

DCLK1B0 {16}

DCLK1B1 {16}

DCLK1B2 {16}

4

R194

MDB[63:0] {16}

150 1%

MA0B[14..0]{15,17}

DMA[0..7]{15}

DQSA[0..7]{15}

-DQSA[0..7]{15}

SBA0B0{15,17}

SBA0B1{15,17}

SBA0B2{15,17}

-CS0B0{15,17}

-CS0B1{15,17}

DCLK0B0{15}

DCLK0B1{15}

DCLK0B2{15}

-DCLK0B0{15}

-DCLK0B1{15}

-DCLK0B2{15}

-SRAS0B{15,17}

-SCAS0B{15,17}

-SWE0B{15,17}

CKE0B0{15,17}

CKE0B1{15,17}

MODT0_B0{15,17}

MODT0_B1{15,17}

-P_RST_STR{12}

R219

CHANNEL A

CHANNEL B

3

6.8K

MA0B0

MA0B1

MA0B2

MA0B3

MA0B4

MA0B5

MA0B6

MA0B7

MA0B8

MA0B9

MA0B10

MA0B11

MA0B12

MA0B13

MA0B14

DMA0

DMA1

DMA2

DMA3

DMA4

DMA5

DMA6

DMA7

DQSA0

DQSA1

DQSA2

DQSA3

DQSA4

DQSA5

DQSA6

DQSA7

-DQSA0

-DQSA1

-DQSA2

-DQSA3

-DQSA4

-DQSA5

-DQSA6

-DQSA7

-STR_EN

C19

R222

8.2K

CHANNEL A, COPY A

CHANNEL A, COPY B

CHANNEL B, COPY A

CHANNEL B, COPY B

M34

M35

M33

M32

AC34

AG34

AM36

AT33

AD34

AH34

AN35

AT32

AD33

AH33

AN36

AR33

AA32

AM34

AM35

M36

W34

AA35

AN31

L31

L34

K33

L32

K34

K32

K35

J33

J34

P35

J35

D12

E17

E21

E25

B12

C16

C21

C25

C12

D16

B21

B25

N32

L30

H36

U34

R34

B17

T33

C17

N34

N35

A28

D28

CPU SKT

U24E

MA0B_0

MA0B_1

MA0B_2

MA0B_3

MA0B_4

MA0B_5

MA0B_6

MA0B_7

MA0B_8

MA0B_9

MA0B_10

MA0B_11

MA0B_12

MA0B_13

MA0B_14

MDQM0_0

MDQM0_1

MDQM0_2

MDQM0_3

MDQM0_4

MDQM0_5

MDQM0_6

MDQM0_7

MDQS0_0

MDQS0_1

MDQS0_2

MDQS0_3

MDQS0_4

MDQS0_5

MDQS0_6

MDQS0_7

MDQS0_0*

MDQS0_1*

MDQS0_2*

MDQS0_3*

MDQS0_4*

MDQS0_5*

MDQS0_6*

MDQS0_7*

MBA0B_0

MBA0B_1

MBA0B_2

MCS0B_0*

MCS0B_1*

MCLK0B_0

MCLK0B_1

MCLK0B_2

MCLK0B_0*

MCLK0B_1*

MCLK0B_2*

MRAS_0B*

MCAS_0B*

MWE_0B*

MCKE0B_0

MCKE0B_1

MODT0B_0

MODT0B_1

STR_EN*

DDRII1

DDRII2

DDRII3

DDRII4

SEC

5 OF 8

DIMM 2

2

C19

MD0_0

MD0_1

MD0_2

MD0_3

MD0_4

MD0_5

MD0_6

MD0_7

MD0_8

MD0_9

MD0_10

MD0_11

MD0_12

MD0_13

MD0_14

MD0_15

MD0_16

MD0_17

MD0_18

MD0_19

MD0_20

MD0_21

MD0_22

MD0_23

MD0_24

MD0_25

MD0_26

MD0_27

MD0_28

MD0_29

MD0_30

MD0_31

MD0_32

MD0_33

MD0_34

MD0_35

MD0_36

MD0_37

MD0_38

MD0_39

MD0_40

MD0_41

MD0_42

MD0_43

MD0_44

MD0_45

MD0_46

MD0_47

MD0_48

MD0_49

MD0_50

MD0_51

MD0_52

MD0_53

MD0_54

MD0_55

MD0_56

MD0_57

MD0_58

MD0_59

MD0_60

MD0_61

MD0_62

MD0_63

MEM_VREF

MEM_VREF2

NB

DIMM0

DIMM2

DIMM1

DIMM3

D10

C11

B13

C13

B10

C10

A12

E13

D14

C15

C18

C19

B14

C14

B18

D17

B20

A20

D22

C23

D20

C20

B22

C22

B24

A24

C26

C27

D24

C24

B26

D26

AB35

AB33

AE32

AE35

AA34

AB34

AD35

AD36

AF34

AF33

AJ33

AJ35

AE34

AF35

AH35

AH36

AK34

AL33

AN34

AR35

AJ34

AK35

AP36

AP35

AT34

AP33

AN32

AP31

AP34

AR34

AR32

AP32

H11

G11

ADDR/CNTL 0A

ADDR/CNTL 0B

ADDR/CNTL 1A

ADDR/CNTL 1B

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

C19_MEM_VREF

Title

Size Document Number Rev

Custom

Date: Sheet

MDA[63:0] {15}

DDR18V

R191

121 1%

R192

C376

0.1u

121 1%

Gigabyte Technology

C19 DIMM

GA- 8N-SLI QUAD ROYAL

1

942Monday, October 17, 2005

1.1

of

5

DDR18V

D D

C C

VTT_GMCH

B B

VCC3

A A

M22

M23

M24

M25

M14

M15

M16

M17

M18

M19

M20

M21

AA13

AD13

AB13

AC13

AF10

W12

AH5

AG5

AG6

AG7

AG8

AG9

AH2

AH3

W13

W14

AA12

AB12

AC12

AD12

AE12

AH1

AH4

AN29

AM29

AM28

U24G

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

+1.8V_MEM

POWER

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

VTT_CPU

+3.3V

+3.3V

+3.3V

C19

VDD_NVCORE

VDD_NVCORE

SEC

VDD_NVCORE

7 OF 8

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_NVCORE

VDD_HT_CORE

VDD_HT_CORE

VDD_HT_CORE

VDD_HT_CORE

VDD_PE_CORE

VDD_PE_CORE

VDD_PE_CORE

VDD_PE_CORE

VDD_PE_CORE

VDD_PEIO_CORE

VDD_PEIO_CORE

VDD_PEIO_CORE

VDD_PEIO_CORE

VDD_PEIO_CORE

VDD_PLL_CORE

VDD_PLL_CORE

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

+0.9V_VTT

Internal Chip Termination Voltage Regulation

(CTT)

5

L27

K27

K28

J28

J29

J30

J31

T24

J32

R23

H33

H34

H35

R24

N14

N15

N16

N17

N18

N19

N20

N21

P14

P15

P16

P17

P18

P19

P20

P21

R14

N22

T14

N23

R25

T23

N24

N25

P22

P23

P24

P25

T25

V13

U12

U14

U13

V12

AF9

Y12

Y13

Y14

V14

AJ2

AJ1

VCC1_4

AA23

AA24

AB23

AB24

AD16

AD17

AC17

AC18

AC19

AC20

AC21

AC22

AC23

AC24

AD20

AD21

AD22

AD23

AD24

AF27

AK27

AG27

AH27

AK28

AM27

AP28

AL27

AN27

AR28

AT28

AD18

AD19

AE16

V25

U23

U24

V23

V24

W24

Y24

AA25

AB25

AC25

AD25

W25

Y25

AJ27

AE23

AE24

AE25

AE17

AE18

U25

AE19

AE20

AE21

AE22

AD15

AC15

AE15

AC16

AE14

AE13

AB14

AC14

AA14

AD14

W23

Y23

C19_MEM_VTT

K9

K10

K11

J9

J10

A9

B9

C9

D9

E9

M12

M13

N12

N13

P12

P13

R13

R12

T12

T13

F9

G9

H9

C19_VDD_PLL

C677

4.7u

C19_VDD_PEX_D

C19_VDD_PEX_A

C319

C332

4.7u

0.1u

Choose VTT mode

R555

VTT mode (1.5A)

EC60

0.925

330uF

47

C679

C678

0.1u

4.7u/X

C317

0.1u

C331

0.1u

FB7

0

* 108 + 1.5 > 3A

C680

0.1u

FB9

FB6

C326

4.7u

C318

4.7u

DDRVTT

C681

0.1u

0

4

30/4A

30/4A

VCC1_4

DDR18V

4

VCC1_4

VCC1_4

R519

100 1%

R520

121 1%

AA1

AA10

AA16

AA17

AA18

AA19

AA20

AA21

AA27

AA36

AB28

AB30

AB32

AB5

AB7

AB9

AC10

AC27

AC33

AC4

AD28

AD30

AD9

AE1

AN28

AE27

AE36

AE30

AF32

AF7

AK20

AG13

AG15

AG17

AG11

AG21

AG23

AG12

AG33

AH10

AH12

AH14

AH16

AH18

AH20

AH22

AH24

AN5

AH28

AH30

D30

AJ36

AG14

AK10

AK14

AK18

AK22

AK33

AK6

AM10

AG16

AM18

AL31

AM22

AM26

AM30

AG18

AN13

AG20

AG22

AG24

AH21

AN33

AK7

AP3

AR1

AR29

AR36

AL11

AL15

AT2

AH7

AJ25

AT35

AK11

AL19

AM3

3

U24H

C19

SEC 8 OF 8

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

A13

GND

A17

GND

A2

GND

A21

GND

A25

GND

A29

GND

A35

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

D6

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

B1

GND

B36

GND

B5

GND

C33

GND

D11

GND

D15

GND

D19

GND

D23

GND

D27

GND

GND

E14

GND

E18

GND

E2

GND

E22

GND

E26

GND

AK4

GND

E35

GND

CHIPSET CORE AND PCIE 23 AMPS@1.525V

G10

G12

G14

G16

G18

G20

G22

G24

G26

G28

G30

G33

G4

J1

J12

J14

J16

J18

J20

J22

J24

J26

J36

K13

K15

K17

K19

K21

K23

K25

Y9

K30

K5

K7

C8

AK15

L33

L4

M28

M30

M9

N1

N10

N27

N36

P28

P30

P32

P5

P7

P9

R10

R27

R33

R4

T16

T17

T18

T19

T20

T21

T28

T30

T9

U1

U10

U16

U17

U18

U19

U20

U21

U27

U36

V16

V17

V18

V19

V20

V21

V28

V30

V32

V5

V7

V9

W10

W16

W17

W18

W19

W20

W21

W27

W33

W4

Y16

Y17

Y18

Y19

Y20

Y21

Y28

Y30

AK26

G7

AD7

Y7

M7

T7

AF4

R391

30K 1%

R394

20K 1%

C558

FB_VCC1_4_NT

3

VCC14_COMP

4.7N

VCC14_PHASE

C538

100P

ATXGPO12{22,26}

ATXGPO13{22,26}

ATXGPO14{22,26}

ATXGPO15{22,26}

SW+VCC

U34

8

7

6

5

ISL6520A

C676

1u

FB_VCC1_4

Range: 1.4~1.95V

0.1u