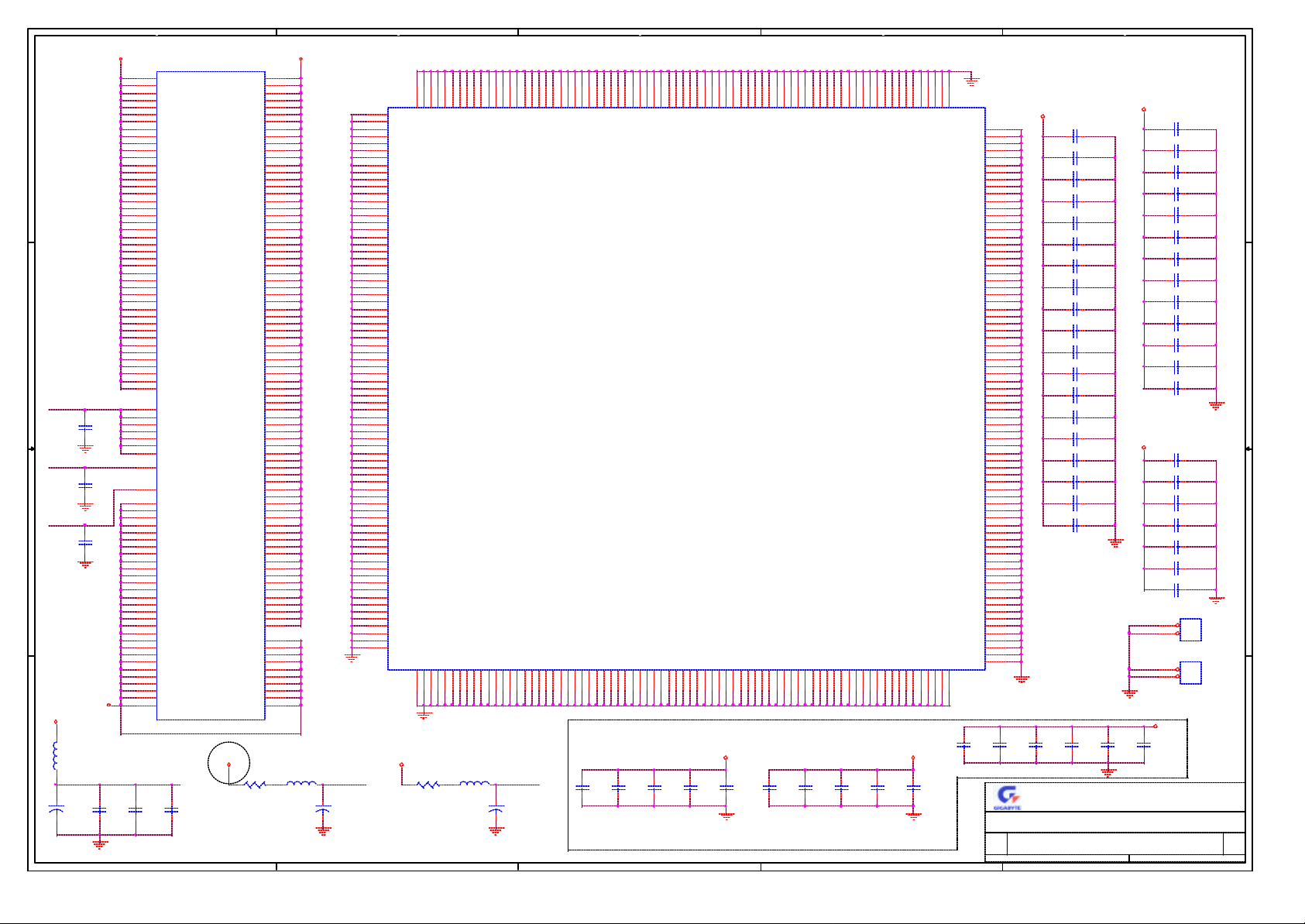

Gigabyte GA-8IP533A Schematics rev.1.0

5

4

3

2

1

REV:1.0

GA-8IP533A

D D

FSC

TITLE

COVER SHEET

BLOCK DIAGRAM

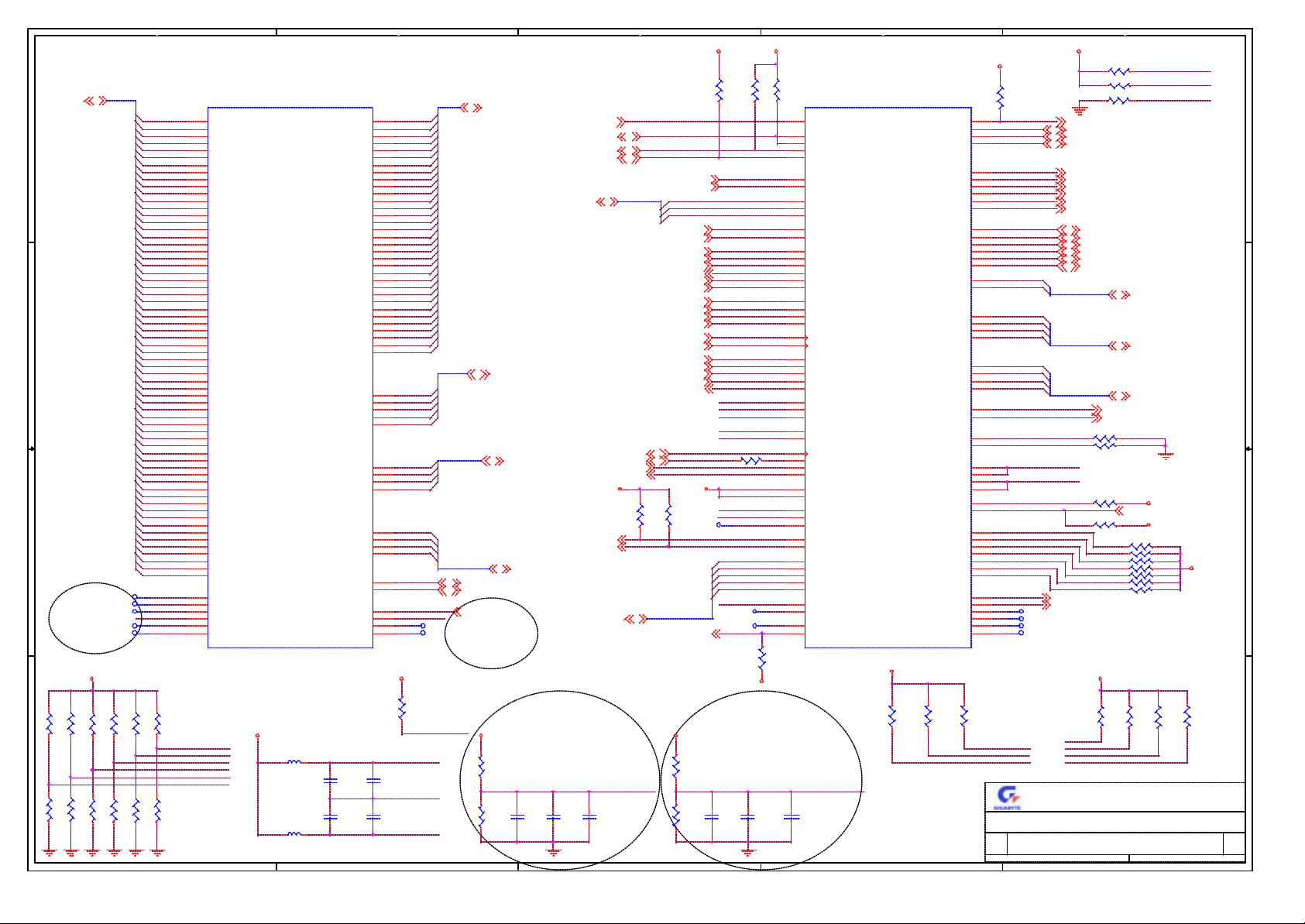

CPU 0

CPU 1

LEVEL SHIFT

CPU DECOUPLING

C C

MCH

DDR DIMM CHANNEL A

DDR DIMM CHANNEL B

P64H2

PCIX SLOT1

PCIX SLOT2

BRIDGE BOARD CONNECTOR

GIGABIT LAN CONTROLLER

GIGABIT LAN POWERGOD/POWER

I2C MULTIPLEXER & 32BIT PCI CONNECTOR

B B

ICH3

SUPER IO

PAGE

1

2,3

5,6

7,8

9

10

11,12,13

14,15,16,17

18,19,20,21

22,23,24,25,26

27

28

29,30

31,32

33,34

35

36,37,38

39

4.5 mil

4 mil

4.5 mil

4 mil

14 mil

4 mil

4.5 mil

4 mil

4.5 mil

9/22/2003

BOARD STACK-UP

PP 2116

FR4

PP 2116

FR4

PP 7628 X 2

FR4

PP 2116

FR4

PP 2116

COMPONENT SIDE

INT 5

INT 1

GND

INT 2

GND

INT 4

INT 6

SOLDER SIDE

0.5OZ

1OZ

1OZ

1OZ

1OZ

1OZINT 3

1OZ

1OZ

1OZ

0.5OZ

ADM1026 HARDWARE MONITOR 40

SERIAL PORT

FRONT PANEL & KB/MS

ATI RAGE XL

VGA CONNECTOR

CLOCK GENERATOR

USB CONNECTOR

A A

VRM ENABLE AND POWER OK LOGIC

POWER CONNECTOR

VOLTAGE REGULATORS

PCI IDSEL AND ROUTING

IPMI GPIO AND I2C ADDRESS

5

4

41

42

43,44

45

46

47

48

49

50,51,52,53,54

55

56

Title

Size Document Number Rev

3

2

Date: Sheet of

GIGA-BYTE TECHNOLOGY CO., LTD.

COVER SHEET

GA-8IP533A

1 57T uesday, September 23, 2003

1

1.0

5

4

3

2

1

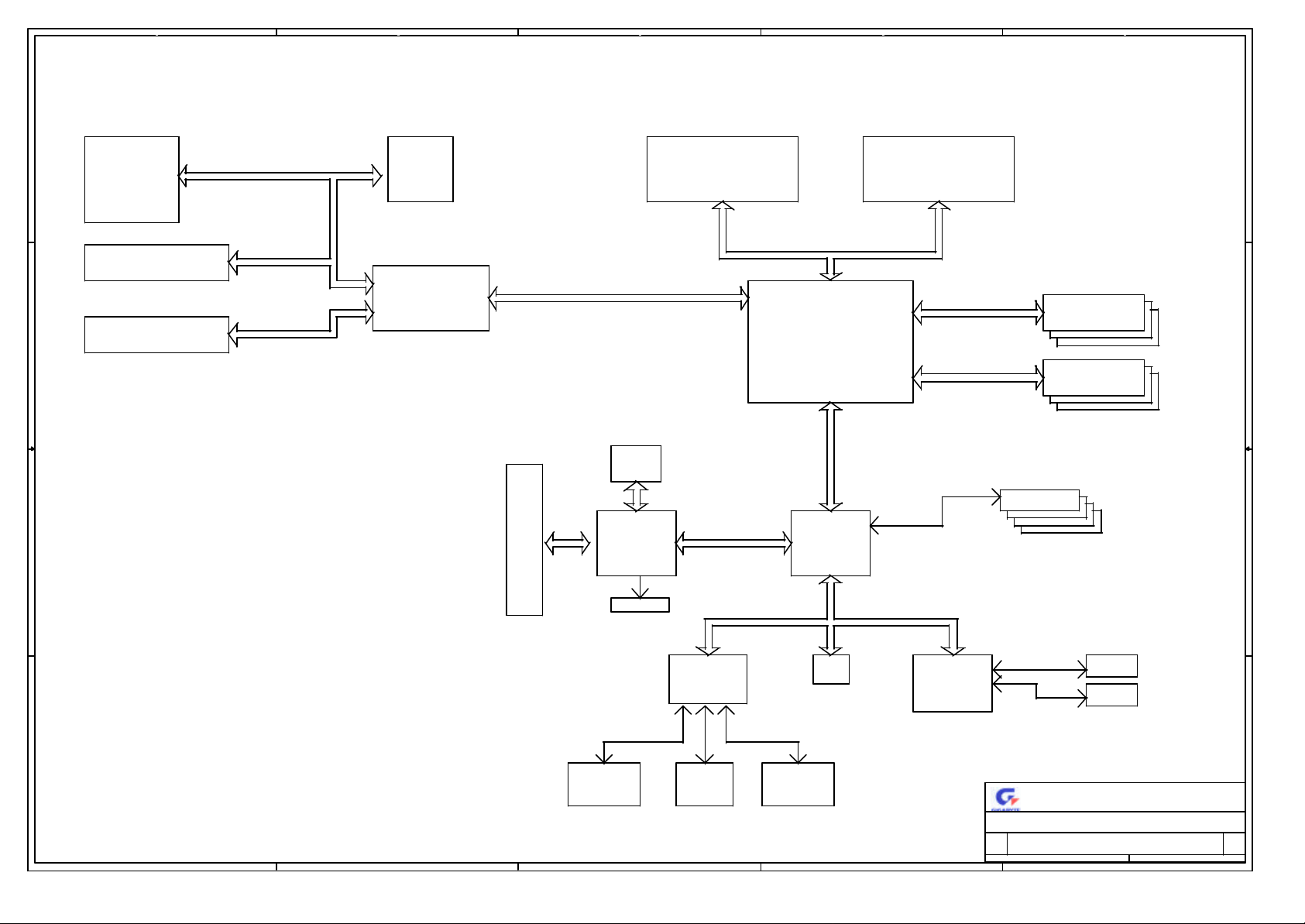

8IP533A SYSTEM BLOCK DIAGRAM

D D

Ultra 320

PCI-X_66MHz

SCSI

64-Bit PCI-X SLOT3

ZCR

C C

B B

64-Bit PCI-X SLOT 2

PCI-X_66MHz

PCI-X_133MHz

BUS A

BUS B

Gigabit

LAN

82546EB

P64H2

#1

PCI_33MHz

HI 2.0_16Bit

Frame

Buffer

ATI

Rage 128XL

Processor 1

PCI_33MHz

400/533

E7501

MCH

ICH3-S

Prestonia/NoconaPrestonia/Nocona

Processor 2

DDR Channel A

DDR DIMM

DDR Channel B

DDR DIMM

HI 1.5_8Bit

USB Ports

VGA Con.

32 BIT PCI RISER

CONNECTOR

I/O NS

PC87366

A A

PS2 KB

/ Mouse

5

4

Floppy

3

SERIAL

A/B

LPC

FWHSUPER

2

IPMI

QLOGIC

ZIRCON_UL

Title

Size Document Number Rev

Date: Sheet of

GIGA-BYTE TECHNOLOGY CO., LTD.

SYSTEM BLOCK DIAGRAM

SM BUS

IPMB

GA-8IP533A

1

2 57T uesday, September 23, 2003

1.0

AIC7899

5

4

3

2

1

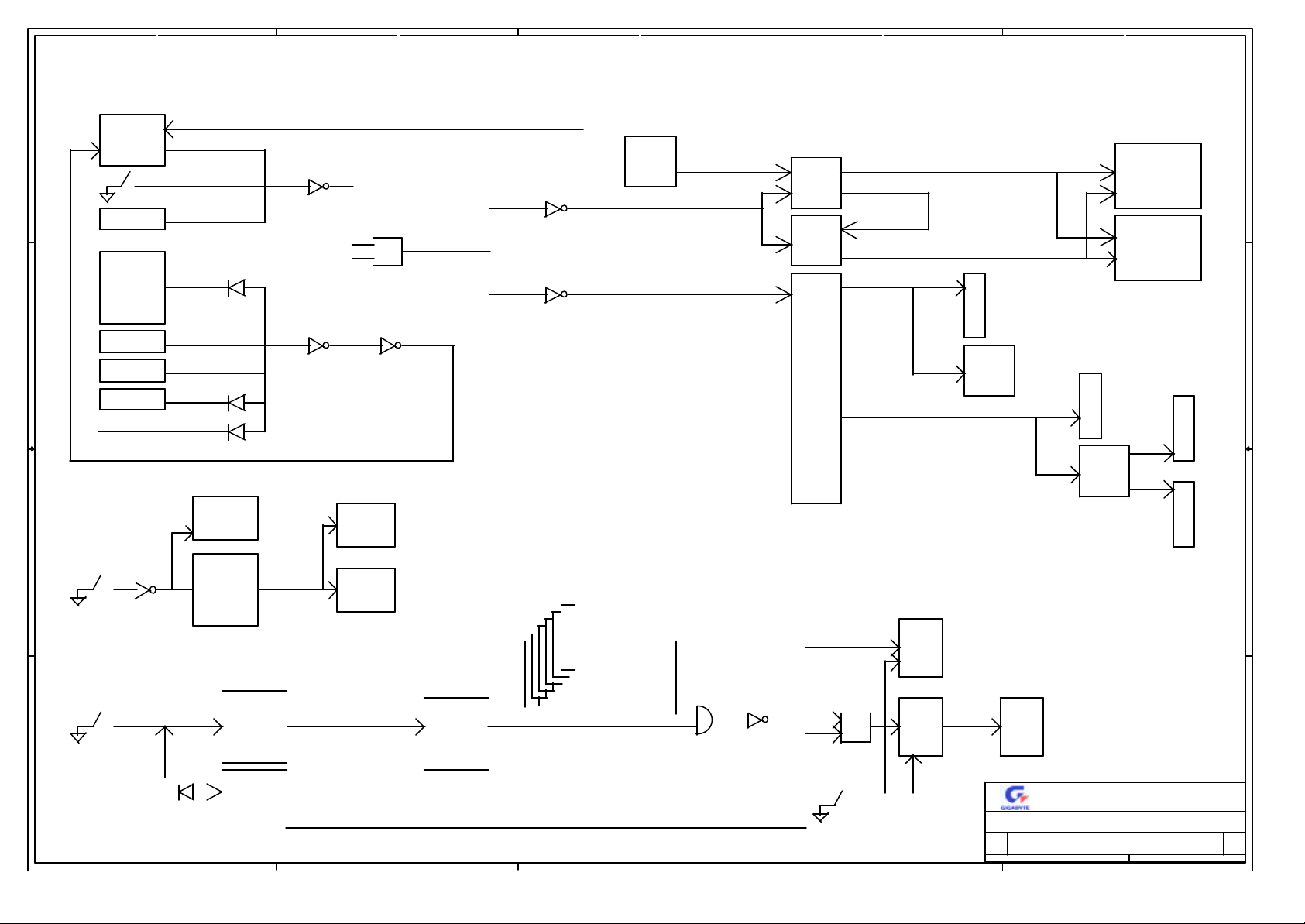

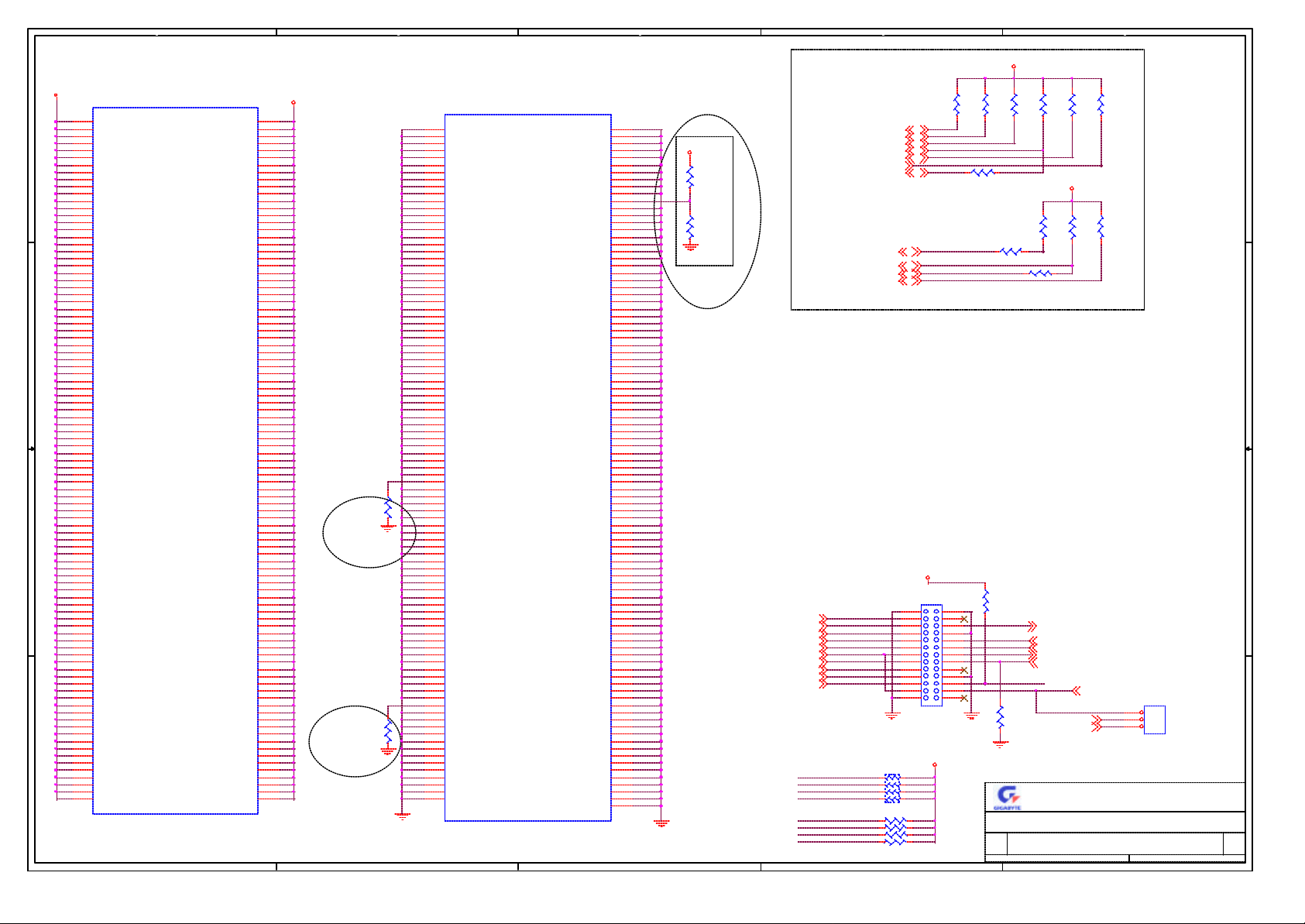

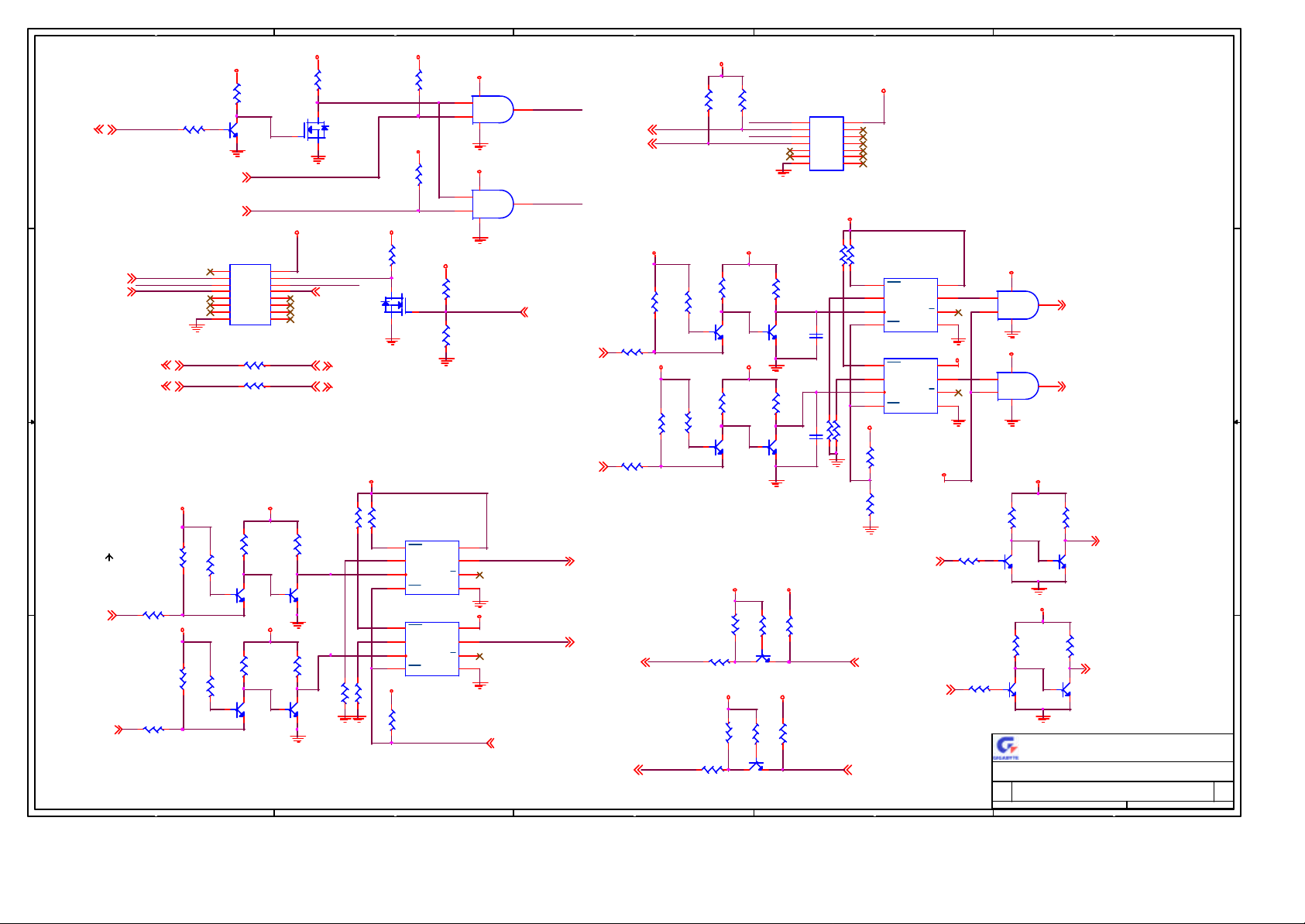

SYSTEM RESET AND POWER OK BLOCK DIAGRAM

OR

INVERTER

IPMI_RST_IN_N

BMC_PWROK_IN

INVERTER

INVERTER

HIP6301

ICH3_VRMPWRGD

ICH3_PWROK

P64H2_PWROK

ICH3

MCH

P64H2

ICH3_PCIRST_N

PA_PCIRST_N

PB_PCIRST_N

ICH3_CPUPWRGD

CPU_RESET_N

PCIX

SLOT1

AIC7899

/AIC7902

82546

PCIX

SLOT2

CPU0

CPU1

RJ45-1

RJ45-1

RESET I/O

D D

C C

ZIRCON UL

PWROK

RESET OUT

ITP CONN

ATX

POWER

SUPPLY

CONN.

LTC1709-7

LTC1735

LTC1735

IPMI_RST_N

RESET SWITCH

INVERTER

ITP_RESET

PS_PWRGD

PGOOD_2D5

INVERTER

PGOOD_1D25

PGOOD_1D2

ICH3_VRMPWRGD

NMI CIRCUIT

ZIRCON UL

NMI_IN

B B

ICH3

GPIO8

NMI

NMI_ SW

INVERTER

CPU0

CPU1

DDR DIMM 1 - 6

ADM1026

VDD_ID

GPIO11

POWER CONN

PWRBTN SW

A A

PWRBTN

SIO

PWRBTN IN

PWRBTN OUT

PWRBTN OUT

PWRBTN IN

ZIRCON UL

POWER 0N EN

5

ICH3_PWRBNIB_S_N

EN_PSON_N

4

ICH3

PWRBTN IN

PWRBTN OUT

ICH3_SLP_S5_N

AND

3

INVERTER

PSON

OR

CASE_OPEN

OR

2

PS_ON

Title

Size Document Number Rev

Date: Sheet of

GIGA-BYTE TECHNOLOGY CO., LTD.

SYSTEM RESET AND POWER ON DIAGRAM

GA-8IP533A

3 57T uesday, September 23, 2003

1

1.0

5

4

3

2

1

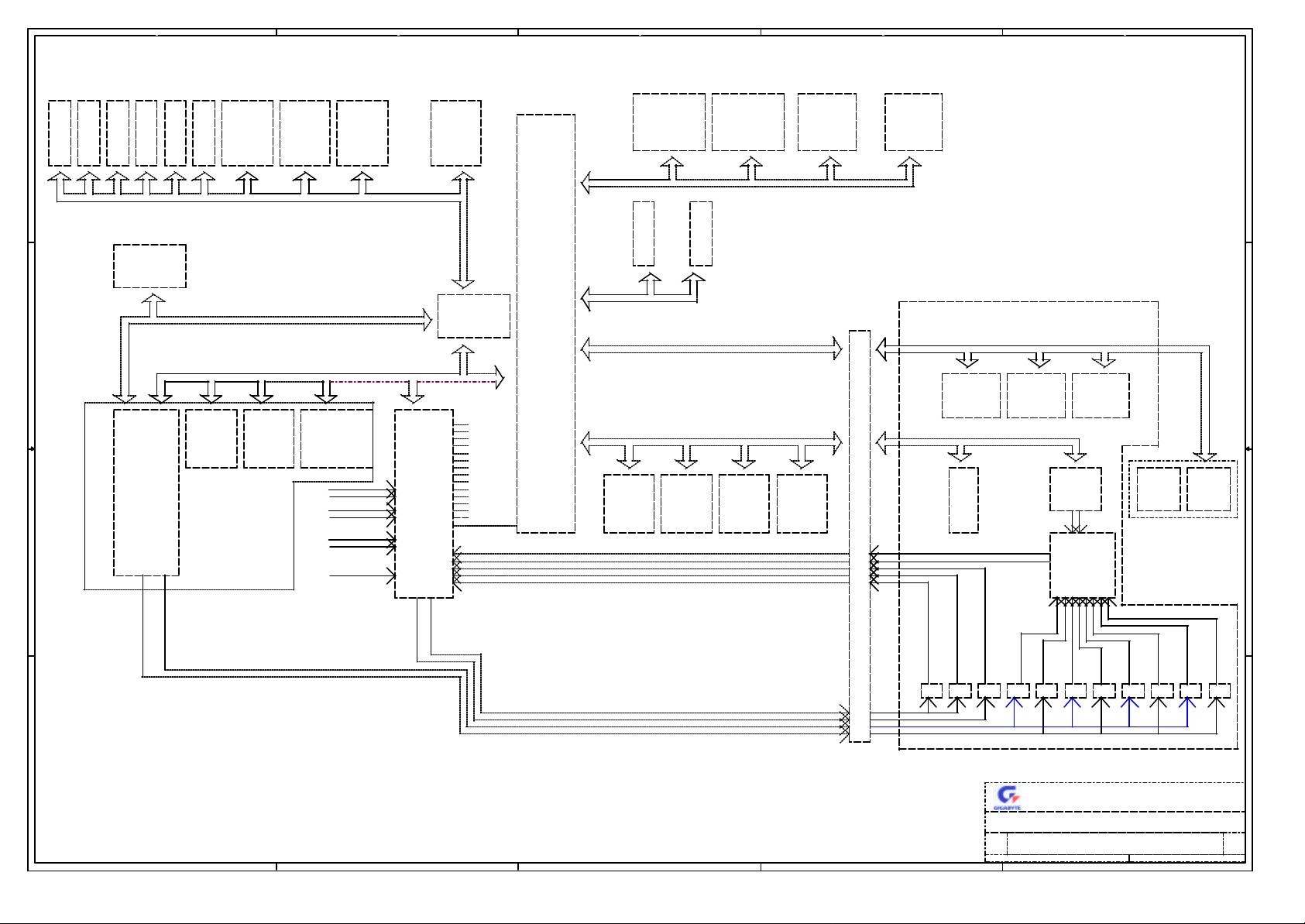

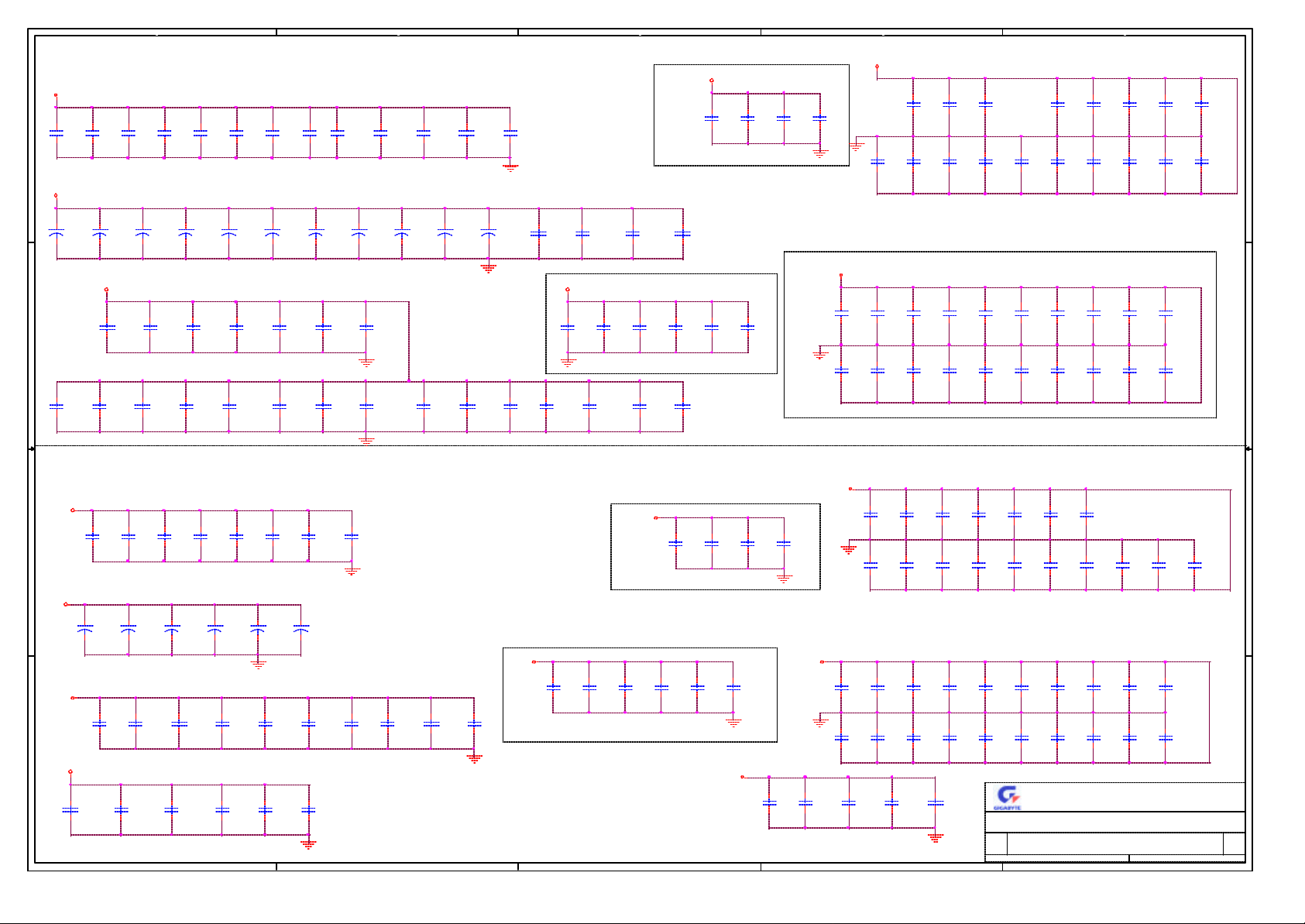

DDR

DIMMA2

DIMMA1

D D

DIMMA3

DDR

DIMMB1

A8H

DDR

DDR

DDR

DIMMB2

AAH

DDR

DIMMB3

ACHA0H A4HA2H

ADDR:

60H

ADDR:

C2H

CY28329P64H2MCH

ADDR:

D2H

SMBUS AND HARDWARE MONITOR BLOCK DIAGRAM

CPU0

EEPROM

ADDR:

AEH

(OPTION)

ICH3

ADDR:

44H

SMBUS0

(NOT USE)

3.3VSB

SIO

POWER

SUPPLY

(OPTION)

CPU1

EEPROM

ADDR:

A8H

(OPTION)

PCIX_SLOT1 PCIX_SLOT2

ICH3 SMBUS

ICH3 SMBUS

3.3VSB3.3V

82546EB

SMBUS2

BMC LAN BUS

C C

BMC SMBUS

3.3VSB

3.3VSB

CONTROL CIRCUIT

PCA9544

ADDR:

E2H

SMBUS33VSB

3.3VSB

BLACKPLANE

3VSBSMBUS3

W83791

W83791

W83791

ADDR:5AH ADDR:5CH ADDR:5EH

(OPTION) (OPTION) (OPTION)

5VSBSMBUS1

PCA9554A

ADDR:

DA/DB

LCD CONNECTOR

ADDR:

70H

74HCT4052

Z2

Z1

Y2_0

Y1_0

Y1_1

I/O 1I/O 0

Y2_1

Y1_2

Y2_2

Y1_3

Y2_3

ID

EEPROM FF

ADDR:

AEH

LM75

ADDR:

91H

FRONT

PANEL

DAC

VCC1_2

VTT_DDR

VCC1_5DUAL

VCC1_8

VCC2_5G

VCC2_5

VCC1_8SB

VCC2_5DUAL

V_CORE

+12V

-12V

VCC

VBAT_ADM

VCC3

ADM1026_INT_N

FAN_SENSE3

5

FAN_SENSE4

6

FAN_SENSE5

9

FAN_SENSE1

3

FAN_SENSE2

4

SMBUS1

5VSB

LM75 LM75

ADDR:

94H/95H

CPU1CPU0 DDR

ADDR:

90H/91H

(OPTION) (OPTION)

LM75LM75

ADDR:

92H/93H

SCSI

ADDR:

96H/97H

FAN_SENSE3

FAN_SENSE4

FAN_SENSE5

FAN_SENSE1

FAN_SENSE2

ZIRCON_UL

RTC

PCF8563

ADDR:

A2/A3

EEPROM

24C128

ADDR:A6H

IPMI

B B

1920

IPMB CONNECTOR

ADDR:28HADDR:24H

CPU0_THERMDA

CPU0_THERMDC

CPU1_THERMDA

CPU1_THERMDC

CPU0_HOT_N

CPU1_HOT_N

PS_ON_N

ADM1026

ADDR:

5CH

PWM

FAN_PWM1

FAN_PWM2

ADM1026 DAC

ADM1026 PWM

BMC PWM1

BMC PWM2

A A

PS

FAN1

PS

FAN2

Housing

FAN

CPU

FAN1

CPU

FAN2

CPU

FAN3

CPU

FAN4

CPU

FAN5

CPU

FAN6

CPU

FAN7

CPU

FAN8

BRIDGE BOARD

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

GIGA-BYTE TECHNOLOGY CO., LTD.

SMBUS BLOCK DIAGRAM

GA-8IP533A

4 57T uesday, September 23, 2003

1

1.0

5

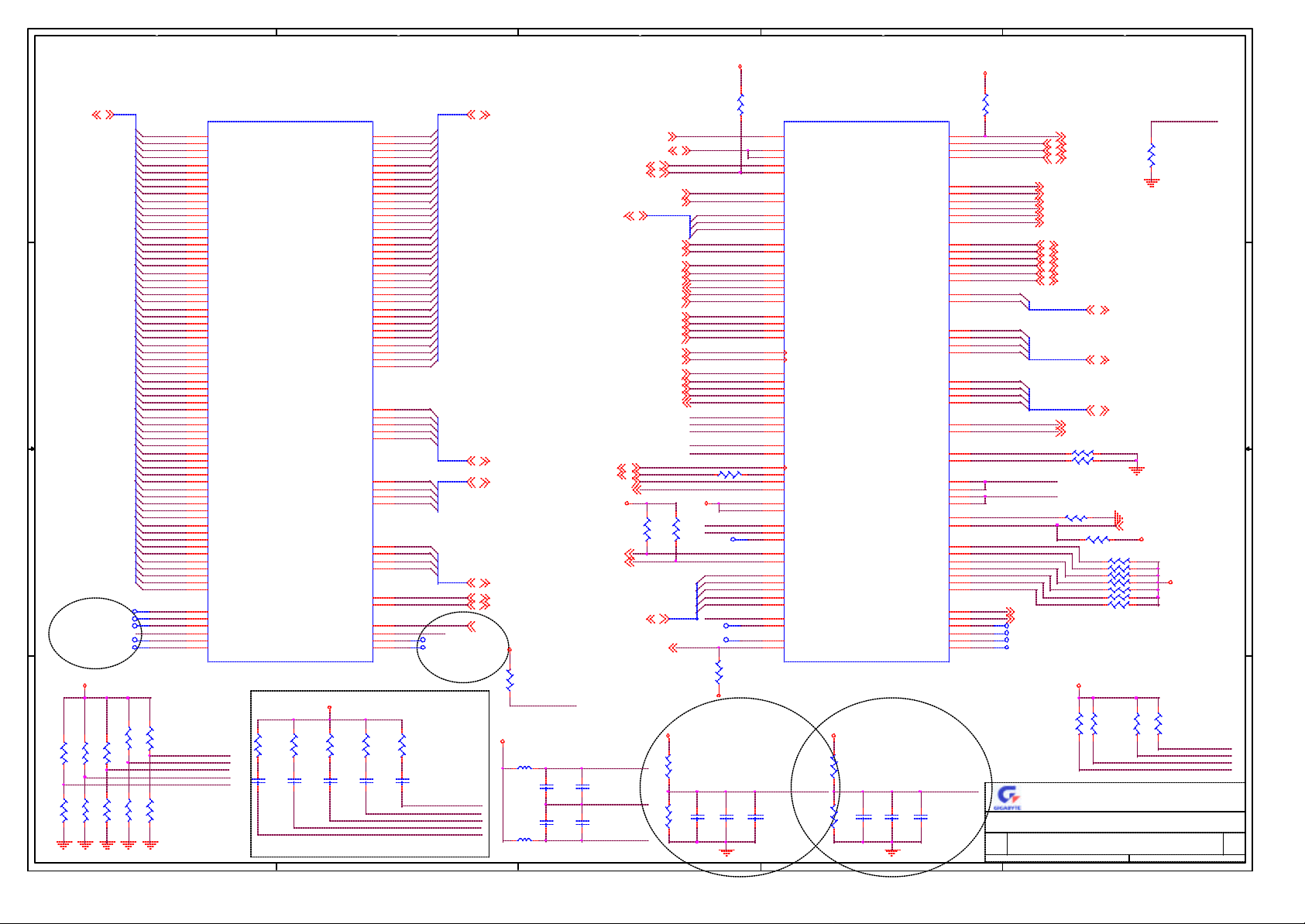

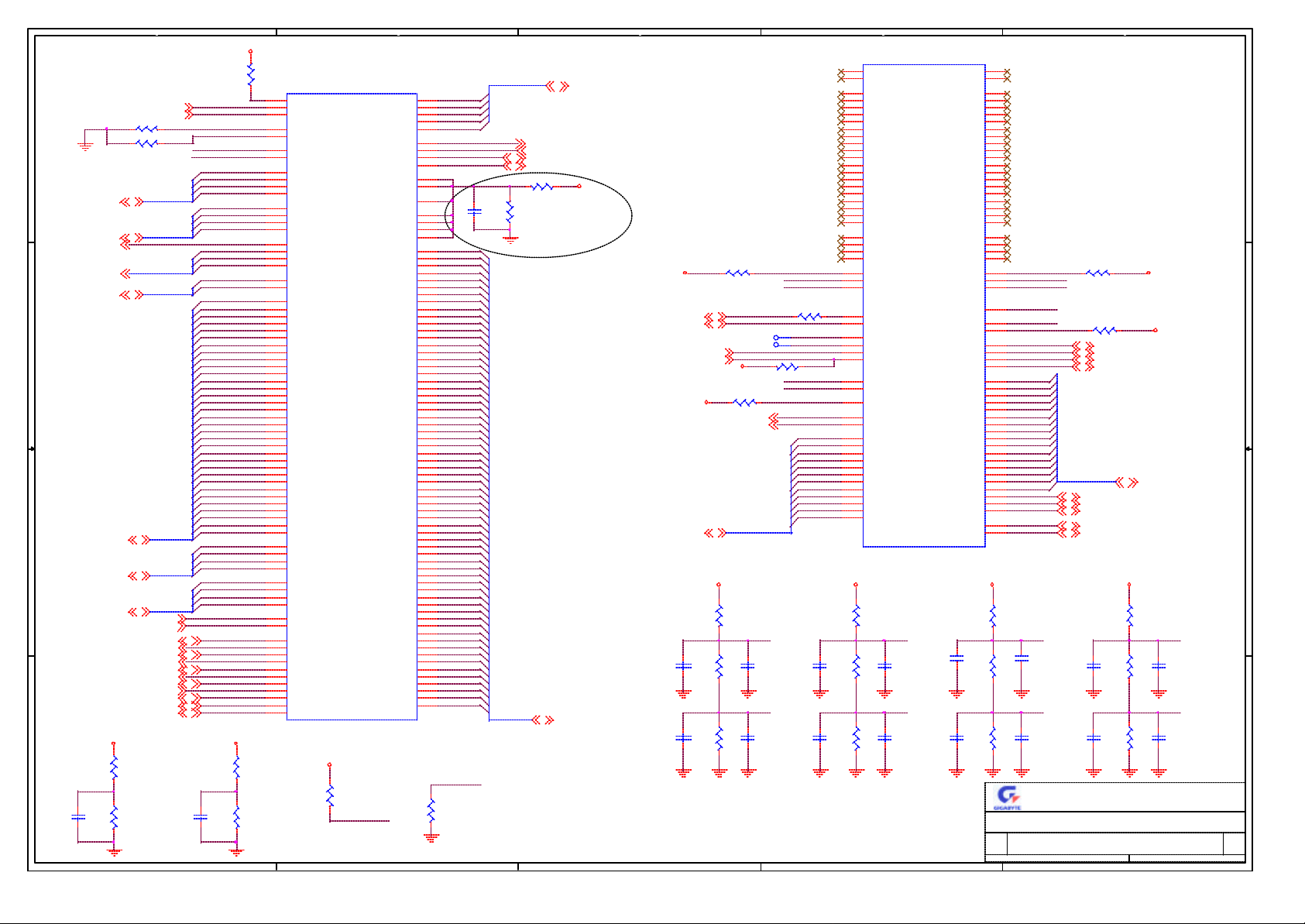

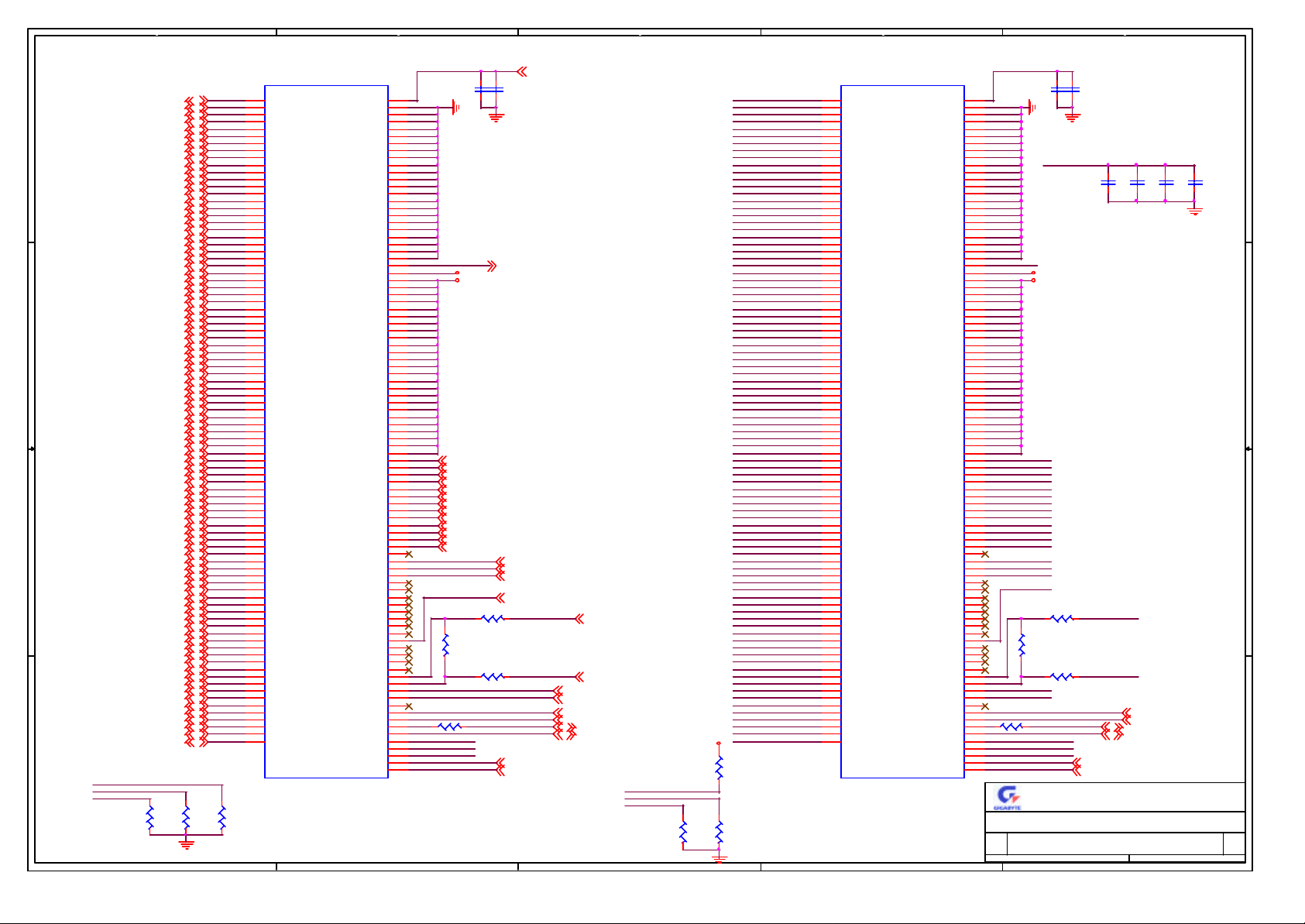

PROCESSOR1 FC-mPGA604

(END

HD[0..63][7,11]

HD63

AB6 C8

HD62

Y9

HD61

AA8

HD60

D D

C C

B B

THE PIN

C5 IS

VCCVIDLB

FOR

NOCONA

CPU.

R7 1K/6/X

A A

R13 1K/6

VCC3

R8 1K/6/X

R14 1K/6

R15 1K/6 R9 1K/6/X

TP3

TP5

TP7

TP11

TP13

R10 1K/6/X

R16 1K/6/X

CPU0_VCCVID

R11 1K/6/X

R17 1K/6/X

HD59

HD58

HD57

HD56

HD55

HD54

HD53

HD52

HD51

HD50

HD49

HD48

HD47

HD46

HD45

HD44

HD43

HD42

HD41

HD40

HD39

HD38

HD37

HD36

HD35

HD34

HD33

HD32

HD31

HD30

HD29

HD28

HD27

HD26

HD25

HD24

HD23

HD22

HD21

HD20

HD19

HD18

HD17

HD16

HD15

HD14

HD13

HD12

HD11

HD10

HD9

HD8

HD7

HD6

HD5

HD4

HD3

HD2

HD1

HD0

CPU0-SM_EP_A2

R12 1K/6/X

CPU0-SM_EP_A1

CPU0-SM_EP_A0

CPU0-SM_TS_A1

CPU0-SM_TS_A0

CPU_SMBUS_WP

1K/6/X

R18

5

AC5

AC6

AE7

AD7

AC8

AB10

AA10

AA11

AB13

AB12

AC14

AA14

AA13

AC9

AD8

AD10

AE9

AC11

AE10

AC12

AD11

AD14

AD13

AB15

AD18

AE13

AC17

AA16

AB16

AB17

AD19

AD21

AE20

AE22

AC21

AC20

AA18

AC23

AE23

AD24

AC24

AE25

AD25

AC26

AE26

AA19

AB19

AB22

AB20

AA21

AA22

AB23

AB25

AB26

AA24

Y23

AD27

AA25

Y24

AA27

Y26

AC1

W3

D25

A26

A16

C5

processor)

U1A

D63 A35

D62

D61

D60

Socket 604

D59

D58

D57

D56

D55

D54

D53

D52

D51

D50

D49

D48

D47

D46

D45

D44

D43

D42

D41

D40

D39

D38

D37

D36

D35

D34

D33

D32

D31

D30

D29

D28

D27

D26

D25

D24

D23

D22

D21

D20

D19

D18

D17

D16

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

SOCKET-604

V_CORE

Part 1

L1

4.7U/8

L2

4.7U/8

BREQ4#

BREQ3#

BREQ2#

BREQ1#

BREQ0#

RSVD10

21

C1

10U/12

C8

10U/12

21

4

HA35

HA34

C9

A34

HA33

A7

A33

HA32

A6

A32

HA31

B7

A31

HA30

C11

A30

HA29

D12

A29

HA28

E13

A28

HA27

B8

A27

HA26

A9

A26

HA25

D13

A25

HA24

E14

A24

HA23

C12

A23

HA22

B11

A22

HA21

B10

A21

HA20

A10

A20

HA19

F15

A19

HA18

D15

A18

HA17

D16

A17

HA16

C14

A16

HA15

C15

A15

HA14

A12

A14

HA13

B13

A13

HA12

B14

A12

HA11

B16

A11

HA10

A13

A10

HA9

D17

A9

HA8

C17

A8

HA7

A19

A7

HA6

C18

A6

HA5

B18

A5

HA4

A20

A4

HA3

A22

A3

-HREQ4

B22

-HREQ3

C20

-HREQ2

C21

-HREQ1

B21

-HREQ0

B19

DBI[0..3]

DBI3

AB9

DBI3#

DBI2#

DBI1#

DBI0#

DP3#

DP2#

DP1#

DP0#

AP1#

AP0#

RSVD7

RSVD8

RSVD9

DBI2

AE12

DBI1

AD22

DBI0

AC27

DP3

AE17

DP2

AC15

DP1

AE19

DP0

AC18

D9

E10

P0_FORCEPR_N

A15

CPU0_VCCVID

A4

A1

AE16

THE PIN A15 IS FORCEPR# FOR NOCONA CPU.

T HE PIN A4 IS VCCVID FOR NOCONA CPU.

V_CORE

CPU0_VCCA

C1586

22U/12

CPU0_VSSA

C1587

22U/12

CPU0_VCCIOPLL

4

AP1_N

AP0_N

TP19

TP4

CLOSE TO CPU0

R1734

49.9/6/1

P0_FORCEPR_N

DP[0..3]

HA[3..35] [7,11]

-HREQ[0..4] [7,11]

DBI[0..3] [7,11]

R32

51/6/1

R38

86.6/6/1

DP[0..3] [7,11]

AP1_N [7,11]

AP0_N [7,11]

P0_FORCEPR_N [9]

R37

R38

C5

1U/6

BREQ2_3_N[7]

CPU1_BREQ0_N[9]

CPU0_BREQ0_N[9]

RS[0..2][7,11]

CPU0_BSEL1[48]

CPU0_BSEL0[46,48]

CPU0_VID[0..4][48,49]

NOCONA

86.6 ohn 1%

C6

220P/6

BPRI_N[7,11]

I2C_BUS0_CLK[7,35,39]

I2C_BUS0_DAT[7,35,39]

CPU_SMBUS_WP[7]

CPU_SMBALERT_N[7,35,37]

VCC3

PRESTONIA

100 ohn 1%86.6 ohn 1%

100 ohn 1%

C7

220P/6

3

BPRI_N

BREQ2_3_N

CPU1_BREQ0_N

CPU0_BREQ0_N

RS[0..2]

ICH3_A20M_N[6,7,36]

ICH3_IGNNE_N[6,7,36]

CPU_LINT1_NMI[6,7]

ICH3_LINT0_INTR[6,7,36]

I CH3_CPUPWRGD[7,36]

ICH3_CPUSLP_N[6,7,36]

R1384

1K/6

3

R1

49.9/6/1

DEFER_N[7,11]

CPURST_N[6,7,11]

RSP_N[7,11]

HTRDY_N[7,11]

ICH3_INIT_N[6,7,36,37]

FERR_N[7,36]

CPU0_SMI_N[9]

STPCLK_N[6,7]

CPU0_BCLK0[46]

CPU0_BCLK1[46]

ITP_TCK_P[6,7]

ITP_TDI_P0[6]

ITP_TMS_P[6,7]

ITP_TRST_N[6,7]

ITP_TDO_P0[6]

I2C_BUS0_CLK

I2C_BUS0_DAT

CPU_SMBUS_WP

CPU_SMBALERT_N

3VSB

R1385

1K/6

CPU0_VID[0..4]

CPU0_604_PRT#[37]

V_COREV_CORE

R31

51/6/1

R37

86.6/6/1

V_CORE

R1306

49.9/6/1

DEFER_N

CPURST_N

RS2

RS1

RS0

RSP_N

HTRDY_N

ICH3_A20M_N

ICH3_IGNNE_N

ICH3_INIT_N

FERR_N

CPU_LINT1_NMI

ICH3_LINT0_INTR

I CH3_CPUPWRGD

CPU0_SMI_N

ICH3_CPUSLP_N

STPCLK_N

CPU0_BCLK0

CPU0_BCLK1

ITP_TCK_P

ITP_TDI_P0

ITP_TMS_P

ITP_TRST_N

ITP_TDO_P0

CPU0-SM_EP_A2

CPU0-SM_EP_A1

CPU0-SM_EP_A0

CPU0-SM_TS_A1

CPU0-SM_TS_A0

R1772 47/6

CPU0_VCCA

CPU0_VCCIOPLL

TP1

CPU0_VID4

CPU0_VID3

CPU0_VID2

CPU0_VID1

CPU0_VID0

CPU0_VSSA

C2

1U/6

V_CORE

R6

49.9/6/1

U1B

D23

BPRI#

D10

BR3#

E11

BR2#

F12

BR1#

D20

BR0#

C23

DEFER#

Y8

RESET#

F21

RS2#

D22

RS1#

E21

RS0#

C6

RSP#

E19

TRDY#

F27

A20M#

C26

IGNNE

D6

INIT

E27

FERR#

G23

LINT1

B24

LINT0

AB7

PWRGOOD

C27

SMI#

AE6

SLP#

D4

STPCLK#

Y4

BCLK0

W5

BCLK1

E24

TCK

C24

TDI

A25

TMS

F24

TRST#

E25

TDO

AB28

SM_EP_A2

AB29

SM_EP_A1

AA29

SM_EP_A0

Y29

SM_TS_A1

AA28

SM_TS_A0

AC28

SM_CLK

AC29

SM_DAT

AD29

SM_WP

AD28

SM_ALERT#

AE28

SM_VCC0

AE29

SM_VCC1

AB4

VCCA

AD4

VCCIOPLL

B27

VCC_SENSE

AB3

BSEL1

AA3

BSEL0

B3

VID4

C3

VID3

D3

VID2

E3

VID1

F3

VID0

AA5

VSSA

VCC3

C3

220P/6

R1386

10K/6

D26

AE15

AE4

CPU0_GTL_VREF1CPU0_GTL_VREF2

C4

220P/6

VSS_SENSE

RSVD11

SMB_PRT

SOCKET-604

TP2

TP6

2

Socket 604

Part 2

3VSB

R1354

4.7K/6

2

IERR#

ADS#

BINIT#

BNR#

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

DBSY#

DRDY#

HIT#

HITM#

LOCK#

MCERR#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

THERMTRIP#

PROCHOT#

COMP1

COMP0

GTLREF3

GTLREF2

GTLREF1

GTLREF0

ODTEN

SKTOCC#

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

R26

4.7K/6

CPU_SMBALERT_N

V_CORE

R1305

470/6

CPU0_IERR_N

E5

ADS_N

D19

BINIT_N

F11

BNR_N

F20

CPU_BPM5_N

E4

CPU_BPM4_N

E8

CPU_BPM3_N

F5

CPU_BPM2_N

E7

CPU_BPM1_N

F8

CPU_BPM0_N

F6

DBSY_N

F18

HDRDY_N

E18

HIT_N

E22

HITM_N

A23

HLOCK_N

A17

BERR_N

D7

ADSTB1

F14

ADSTB0

F17

DSTBP3

Y11

DSTBP2

Y14

DSTBP1

Y17

DSTBP0

Y20

DSTBN3

Y12

DSTBN2

Y15

DSTBN1

Y18

DSTBN0

Y21

CPU0_THRMTRIP_N

F26

PROC0_HOT_N

B25

CPU0_COMP1

E16

CPU0_COMP0

AD16

CPU0_GTL_VREF2

F9

F23

CPU0_GTL_VREF1

W9

W23

CPU0_ODTEN

B5

CPU0_SKTOCC_N

A3

CPU0_TESTHI6

AE5

CPU0_TESTHI5

AD5

CPU0_TESTHI4

AA7

CPU0_TESTHI3

Y6

CPU0_TESTHI2

W8

CPU0_TESTHI1

W7

CPU0_TESTHI0

W6

Y28

Y27

Y3

AD1

B1

AE30

R27

4.7K/6

I2C_BUS0_CLK

I2C_BUS0_DAT

Title

Size Document Number Rev

Date: Sheet of

V_CORE

CPU0_IERR_N [6,9]

ADS_N [7,11]

BINIT_N [7,11]

BNR_N [7,11]

CPU_BPM5_N [6,7]

CPU_BPM4_N [6,7]

CPU_BPM3_N [6,7]

CPU_BPM2_N [6,7]

CPU_BPM1_N [6,7]

CPU_BPM0_N [6,7]

ADSTB[0..1]

DSTBP[0..3]

DSTBN[0..3]

R19 49.9/6/1

R20 49.9/6/1

R21 51/6

R89 4.7K/6

CPU0_THERM_DC1 [40]

CPU0_THERM_DA1 [40]

TP18

TP20

TP21

TP372

FERR_N

PROC0_HOT_N

I CH3_CPUPWRGD

CPURST_N

GIGA-BYTE TECHNOLOGY CO., LTD.

CPU1 SIGNAL

1

R35 150/6/X

R36 150/6

R39 150/6/X

DBSY_N [7,11]

HDRDY_N [7,11]

HIT_N [7,11]

HITM_N [7,11]

HLOCK_N [7,11]

BERR_N [7,11]

ADSTB[0..1] [7,11]

DSTBP[0..3] [7,11]

DSTBN[0..3] [7,11]

CPU0_THRMTRIP_N [9]

PROC0_HOT_N [9]

CPU0_SKTOCC_N [48,51]

R22 49.9/6/1

R23 49.9/6/1

R24 49.9/6/1

R25 49.9/6/1

R28 49.9/6/1

R29 49.9/6/1

R30 49.9/6/1

V_CORE

R2

R3

200/6

56/6

GA-8IP533A

1

ITP_TDO_P0

ITP_TDI_P0

ITP_TRST_N

V_CORE

3VSB

R4

200/6

5 57T uesday, September 23, 2003

V_CORE

R5

51/6

1.0

5

4

3

2

V_CORE

1

V_CORE

U1C

AD30

VCC1

AC31

VCC2

AC3

VCC3

AB30

D D

C C

B B

A A

AB2

AA31

AA1

M3

M1

L30

L28

L26

L24

K31

K29

K27

K25

K23

J30

J28

J26

J24

H31

H29

H27

H25

H23

G30

G28

G26

G24

G8

G6

G4

G2

F31

F29

F22

F16

F10

E30

E28

E26

E20

E12

D31

D29

D24

D18

D14

C30

C28

C22

C16

C10

B31

B29

B26

B20

B12

A30

A28

A24

A18

A14

L8

L6

L4

L2

K9

K7

K5

K3

K1

J8

J6

J4

J2

H9

H7

H5

H3

H1

F4

F1

E6

E2

D8

D1

C4

C2

B6

B4

A8

A2

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

SOCKET-604

Socket 604

Part 3

5

VCC96

VCC97

VCC98

VCC99

VCC100

VCC101

VCC102

VCC103

VCC104

VCC105

VCC106

VCC107

VCC108

VCC109

VCC110

VCC111

VCC112

VCC113

VCC114

VCC115

VCC116

VCC117

VCC118

VCC119

VCC120

VCC121

VCC122

VCC123

VCC124

VCC125

VCC126

VCC127

VCC128

VCC129

VCC130

VCC131

VCC132

VCC133

VCC134

VCC135

VCC136

VCC137

VCC138

VCC139

VCC140

VCC141

VCC142

VCC143

VCC144

VCC145

VCC146

VCC147

VCC148

VCC149

VCC150

VCC151

VCC152

VCC153

VCC154

VCC155

VCC156

VCC157

VCC158

VCC159

VCC160

VCC161

VCC162

VCC163

VCC164

VCC165

VCC166

VCC167

VCC168

VCC169

VCC170

VCC171

VCC172

VCC173

VCC174

VCC175

VCC176

VCC177

VCC178

VCC179

VCC180

VCC181

VCC182

VCC183

VCC184

VCC185

VCC186

VCC187

VCC188

VCC189

VCC190

AE3

Y2

AD2

AE24

AE18

AE14

AE8

AD26

AD20

AD12

AD6

AC22

AC16

AC10

AC4

AB24

AB18

AB14

AB8

AA26

AA20

AA12

AA6

AA4

Y30

Y22

Y16

Y10

W31

W29

W27

W25

W1

V30

V28

V26

V24

V8

V6

V4

V2

U31

U29

U27

U25

U23

U9

U7

U5

U3

U1

T30

T28

T26

T24

T8

T6

T4

T2

R31

R29

R27

R25

R23

R9

R7

R5

R3

R1

P30

P28

P26

P24

P8

P6

P4

P2

N31

N29

N27

N25

N23

N9

N7

N5

N3

N1

M31

M29

M27

M25

M23

M9

M7

M5

V_CORE

R1684

0/6/X

NC FOR NOCONA

49.9 ohm

FOR

NOCONA

R1685

49.9/6/1

R42

U1D

M30

VSS1

M28

VSS2

M26

VSS3

M24

VSS4

M8

M6

M4

M2

L31

L29

L27

L25

L23

L9

L7

L5

L3

L1

K30

K28

K26

K24

K8

K6

K4

K2

J31

J29

J27

J25

J23

J9

J7

J5

J3

J1

H30

H28

H26

H24

H8

H6

H4

H2

G31

G29

G27

G25

G9

G7

G5

G3

G1

F30

F28

F25

F19

F13

F7

F2

E31

E29

E23

E17

E15

E9

E1

D30

D28

D27

D21

D11

D5

D2

C31

C29

C25

C19

C13

C7

C1

B30

B28

B23

B17

B15

B9

B2

A31

A29

A27

A21

A11

A5

4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

SOCKET-604

Socket 604

Part 4

G7 : BOOT_SELECT

C1 : TESTLOW

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

AE2

AD3

AE27

AE21

AE11

AD31

AD23

AD17

AD15

AD9

AC30

AC25

AC19

AC13

AC7

AC2

AB31

AB27

AB21

AB11

AB5

AB1

AA30

AA23

AA17

AA15

AA9

AA2

Y31

Y25

Y19

Y13

Y7

Y5

Y1

W30

W28

W26

W24

W4

W2

V31

V29

V27

V25

V23

V9

V7

V5

V3

V1

U30

U28

U26

U24

U8

U6

U4

U2

T31

T29

T27

T25

T23

T9

T7

T5

T3

T1

R30

R28

R26

R24

R8

R6

R4

R2

P31

P29

P27

P25

P23

P9

P7

P5

P3

P1

N30

N28

N26

N24

N8

N6

N4

N2

3

V_CORE

R1682

0/6/X

R1683

0/6

AC30 : SLEW_CTRL

FOR NOCONA

ICH3_A20M_N[5,7,36]

ICH3_IGNNE_N[5,7,36]

ICH3_LINT0_INTR[5,7,36]

CPU_LINT1_NMI[5,7]

ICH3_CPUSLP_N[5,7,36]

CPU0_IERR_N[5,9]

ICH3_LINT1_NMI[36]

ICH3_SMI_N[9,36]

STPCLK_N[5,7]

ICH3_STPCLK_N[36]

ICH3_INIT_N[5,7,36,37]

RP1

7

5

3

1

8P4R-51

2

1

3

5

7

9

11

13

15

17

19

21

23

25 26

H2X13/PTH2.0/X

8

6

4

2

CPU_BPM0_N[5,7]

CPU_BPM1_N[5,7]

CPU_BPM2_N[5,7]

CPU_BPM3_N[5,7]

CPU_BPM5_N[5,7]

CPURST_N[5,7,11] ITP_TCK_P [5,7]

ITP_TCK_P[5,7]

ITP_BCLK0[46]

ITP_BCLK1[46]

CPU_BPM0_N

CPU_BPM1_N

CPU_BPM2_N

CPU_BPM3_N

CPU_BPM4_N

CPU_BPM5_N

CPU_BPM5_N

CPU_BPM4_N

CPU_BPM3_N

CPU_BPM2_N

CPU_BPM1_N

CPU_BPM0_N

ITP_TDO_P1

ITP_TMS_P

R1307 51/6

R1308 51/6

R87 75/6

R33 51/6

R41

200/6

R1286 0/6

ICH3_SMI_N

STPCLK_N

ICH3_STPCLK_N

ICH3_INIT_N

Should be close to CPU1

V_CORE

ITP

2

4

6

8

10

12

14

16

18

20

22

24

V_CORE

R43

200/6

200/6

R50 0/6

R51 0/6

R1296

1.5K/6/1

ITP_TMS_P

STPPWR

R1297

27.4/6/1

Title

Size Document Number Rev

Date: Sheet of

R45

200/6

V_CORE

R48

200/6

ITP_TDO_P1 [7]

ITP_TDO_P1

R46

470/6/X

R49

200/6

JP11

1

2

3

H1X3/X

1-2 = P1 Only

2-3 = P1+P2

R44

200/6

R47

200/6

DRB_RESET_N [48]

ITP_TDI_P0 [5]

ITP_TMS_P [5,7]CPU_BPM4_N[5,7]

ITP_TRST_N [5,7]

ITP_TDO_P0[5]

ITP_TDI_P1[7]

GIGA-BYTE TECHNOLOGY CO., LTD.

CPU1 POWER AND GND

GA-8IP533A

6 57T uesday, September 23, 2003

1

1.0

5

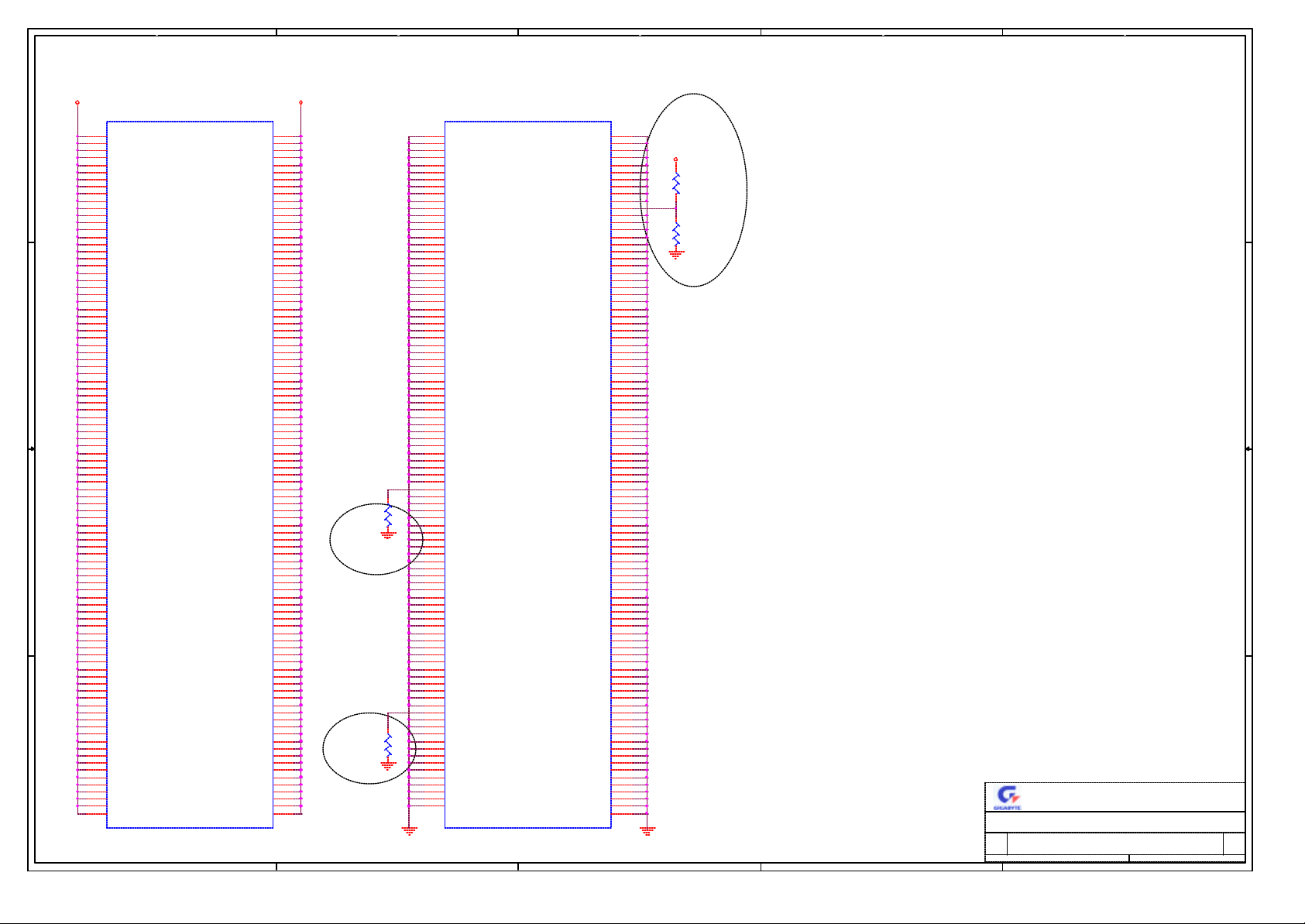

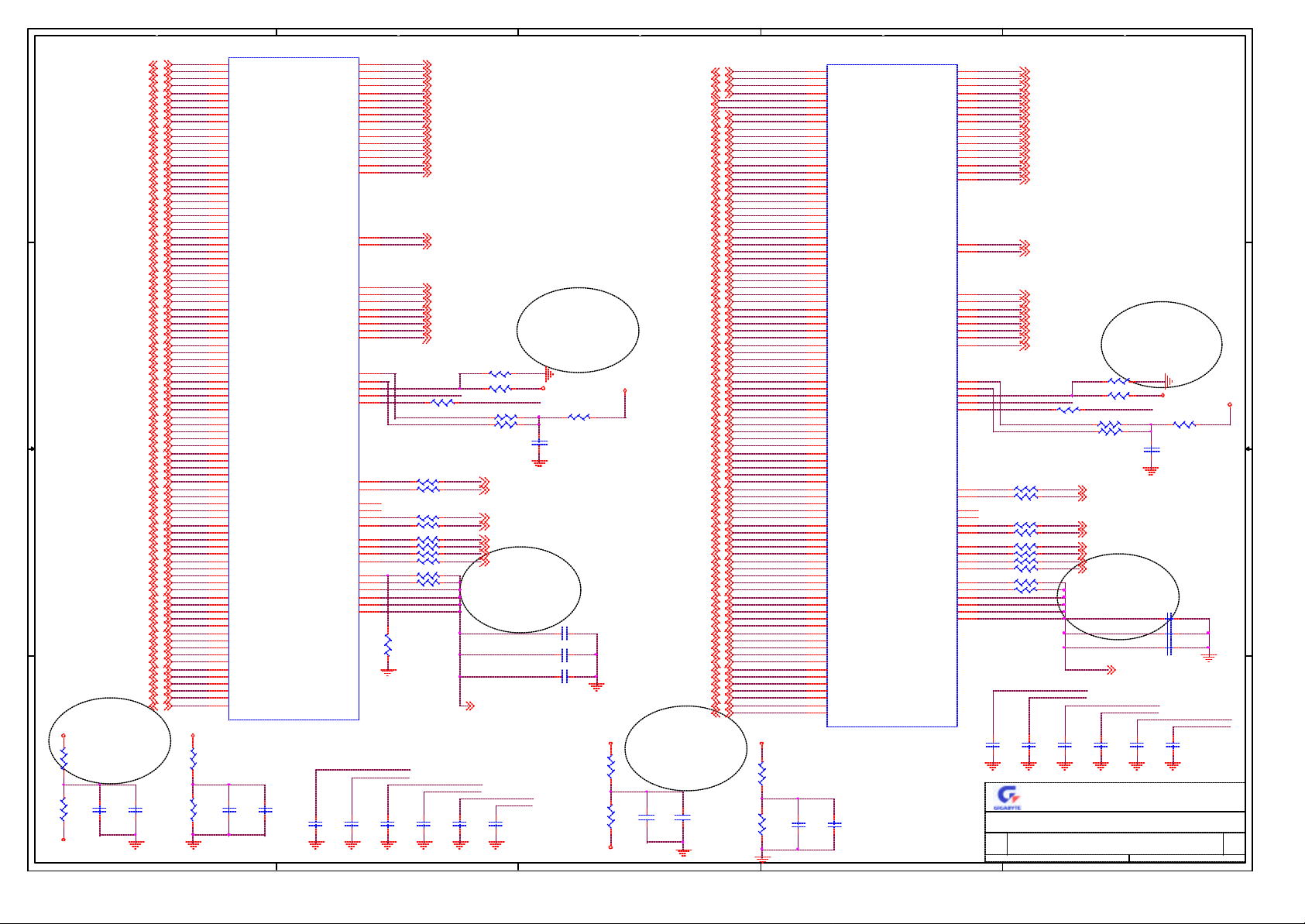

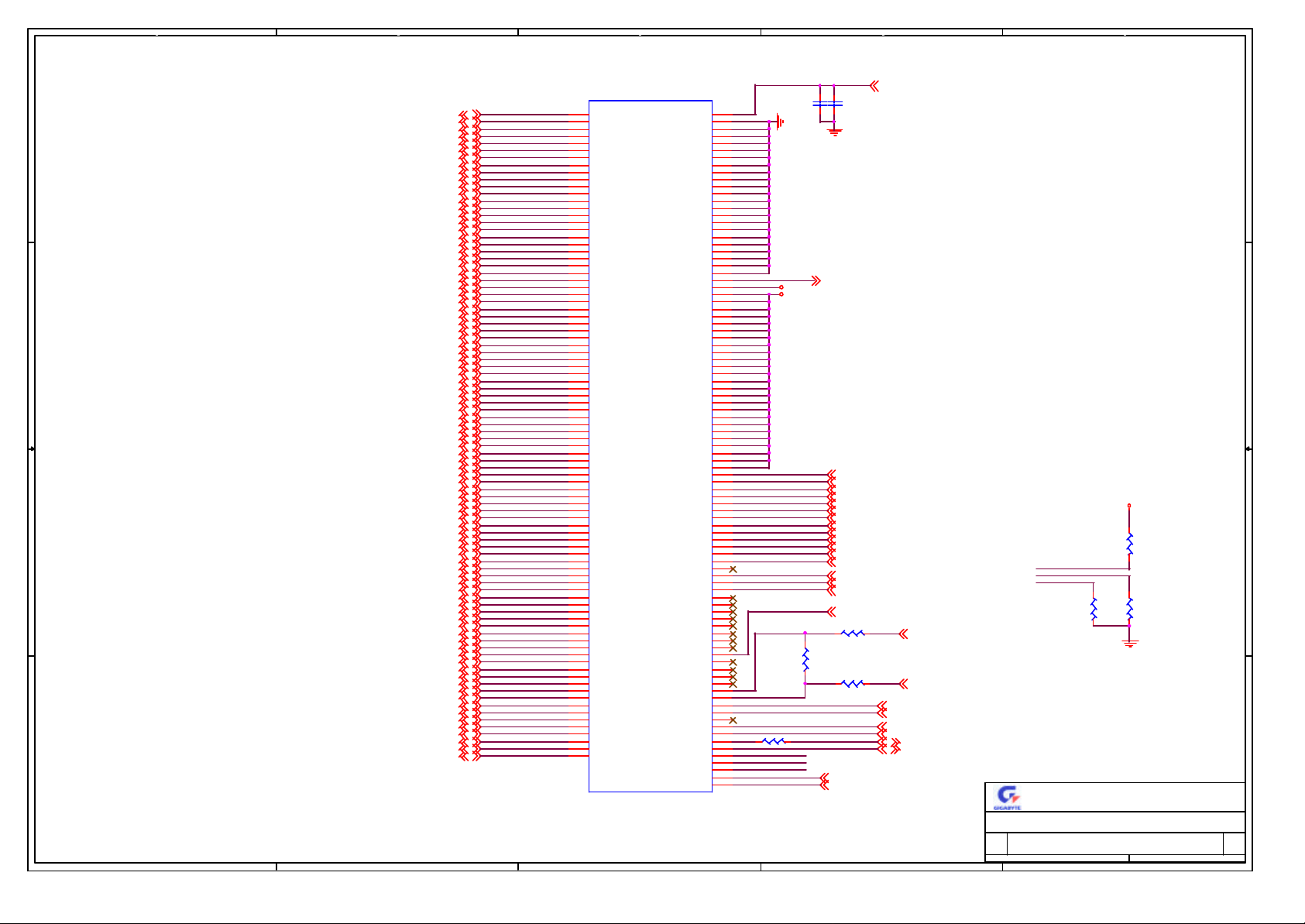

PROCESSOR2 FC-mPGA604

4

3

V_CORE

2

V_CORE

1

("Middle"

Processor)

BINIT_N

BNR_N

BERR_N

HITM_N

HIT_N

HA[3..35] [5,11]

-HREQ[0..4] [5,11]

DBI[0..3] [5,11]

DP[0..3] [5,11]

AP1_N [5,11]

AP0_N [5,11]

P1_FORCEPR_N [9]

V_CORE

CLOSE TO CPU0

R1735

49.9/6/1

P1_FORCEPR_N

V_CORE

L3

4.7U/8

L4

4.7U/8

BPRI_N[5,11]

BREQ2_3_N[5]

CPU0_BREQ0[9]

CPU1_BREQ0[9]

DEFER_N[5,11]

VCC3

CPU1_604_PRT#[37]

CPURST_N[5,6,11]

RSP_N[5,11]

HTRDY_N[5,11]

ICH3_A20M_N[5,6,36]

ICH3_IGNNE_N[5,6,36]

ICH3_INIT_N[5,6,36,37]

CPU_LINT1_NMI[5,6]

ICH3_LINT0_INTR[5,6,36]

I CH3_CPUPWRGD[5,36]

CPU1_SMI_N[9]

ICH3_CPUSLP_N[5,6,36]

STPCLK_N[5,6]

CPU1_BCLK0[46]

CPU1_BCLK1[46]

ITP_TCK_P[5,6]

ITP_TDI_P1[6]

ITP_TMS_P[5,6]

ITP_TRST_N[5,6]

ITP_TDO_P1[6]

I2C_BUS0_CLK

I2C_BUS0_DAT

CPU_SMBUS_WP

CPU_SMBALERT_N

3

FERR_N[5,36]

R1392

1K/6

V_CORE

RS[0..2][5,11]

I2C_BUS0_CLK[5,35,39]

I2C_BUS0_DAT[5,35,39]

CPU_SMBUS_WP[5]

CPU_SMBALERT_N[5,35,37]

CPU1_BSEL1[48]

CPU1_BSEL0[48]

CPU1_VID[0..4][48,49]

C9

10U/12

C10

10U/12

CPU1_VCCA

C1588

22U/12

CPU1_VSSA

C1589

22U/12

CPU1_VCCIOPLL

21

21

HD[0..63][5,11]

HD63

TP24

TP26

TP28

TP32

TP34

1K/6/X

R62

R67 1K/6/X

1K/6/X

R63

R68 1K/6/X

5

HD62

HD61

HD60

HD59

HD58

HD57

HD56

HD55

HD54

HD53

HD52

HD51

HD50

HD49

HD48

HD47

HD46

HD45

HD44

HD43

HD42

HD41

HD40

HD39

HD38

HD37

HD36

HD35

HD34

HD33

HD32

HD31

HD30

HD29

HD28

HD27

HD26

HD25

HD24

HD23

HD22

HD21

HD20

HD19

HD18

HD17

HD16

HD15

HD14

HD13

HD12

HD11

HD10

HD9

HD8

HD7

HD6

HD5

HD4

HD3

HD2

HD1

HD0

D D

C C

B B

THE PIN

C5 IS

VCCVIDLB

FOR

NOCONA

CPU.

VCC3

1K/6

1K/6/X

1K/6/X

R60

R61

R59

A A

R65 1K/6/X

R64 1K/6

R66 1K/6/X

U2A

AB6 C8

D63 A35

Y9

D62

AA8

D61

AC5

D60

D59

D58

D57

D56

D55

D54

D53

D52

D51

D50

D49

D48

D47

D46

D45

D44

D43

D42

D41

D40

D39

D38

D37

D36

D35

D34

D33

D32

D31

D30

D29

D28

D27

D26

D25

D24

D23

D22

D21

D20

D19

D18

D17

D16

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

SOCKET-604

Socket 604

Part 1

V_CORE

R1687

R1688

40.2/6/1

40.2/6/1

C1591

C1590

47P/6

47P/6

40.2/6/1

AC6

AE7

AD7

AC8

AB10

AA10

AA11

AB13

AB12

AC14

AA14

AA13

AC9

AD8

AD10

AE9

AC11

AE10

AC12

AD11

AD14

AD13

AB15

AD18

AE13

AC17

AA16

AB16

AB17

AD19

AD21

AE20

AE22

AC21

AC20

AA18

AC23

AE23

AD24

AC24

AE25

AD25

AC26

AE26

AA19

AB19

AB22

AB20

AA21

AA22

AB23

AB25

AB26

AA24

Y23

AD27

AA25

Y24

AA27

Y26

AC1

W3

D25

C5

A26

A16

CPU1-SM_EP_A2

CPU1-SM_EP_A1

CPU1-SM_EP_A0

CPU1-SM_TS_A1

CPU1-SM_TS_A0

HA35

HA34

C9

A34

HA33

A7

A33

HA32

A6

A32

HA31

B7

A31

HA30

C11

A30

HA29

D12

A29

HA28

E13

A28

HA27

B8

A27

HA26

A9

A26

HA25

D13

A25

HA24

E14

A24

HA23

C12

A23

HA22

B11

A22

HA21

B10

A21

HA20

A10

A20

HA19

F15

A19

HA18

D15

A18

HA17

D16

A17

HA16

C14

A16

HA15

C15

A15

HA14

A12

A14

HA13

B13

A13

HA12

B14

A12

HA11

B16

A11

HA10

A13

A10

HA9

D17

A9

HA8

C17

A8

HA7

A19

A7

HA6

C18

A6

HA5

B18

A5

HA4

A20

A4

HA3

A22

A3

-HREQ4

B22

BREQ4#

BREQ3#

BREQ2#

BREQ1#

BREQ0#

DBI3#

DBI2#

DBI1#

DBI0#

RSVD7

RSVD8

RSVD9

RSVD10

-HREQ3

C20

-HREQ2

C21

-HREQ1

B21

-HREQ0

B19

DBI3

AB9

DBI2

AE12

DBI1

AD22

DBI0

AC27

DP3

AE17

DP3#

DP2#

DP1#

DP0#

AP1#

AP0#

DP2

AC15

DP1

AE19

DP0

AC18

AP1_N

D9

AP0_N

E10

P1_FORCEPR_N

A15

CPU1_VCCVIDCPU1_VCCVID

A4

A1

AE16

THE PIN A15 IS FORCEPR# FOR NOCONA CPU.

THE PIN A4 IS VCCVID FOR NOCONA CPU.

TP40

TP25

FOR NOCONA

R1689

R1690

R1691

40.2/6/1

40.2/6/1

C1592

C1593

47P/6

C1594

47P/6

4

47P/6

CPU0_BREQ0

CPU1_BREQ0

3VSB

R1393

1K/6

R80

51/6/1

R82

86.6/6/1

R52

49.9/6/1

BPRI_N

BREQ2_3_N

DEFER_N

CPURST_N

RS2RS[0..2]

RS1

RS0

RSP_N

HTRDY_N

ICH3_A20M_N

ICH3_IGNNE_N

ICH3_INIT_N

FERR_N

CPU_LINT1_NMI

ICH3_LINT0_INTR

I CH3_CPUPWRGD

CPU1_SMI_N

ICH3_CPUSLP_N

STPCLK_N

CPU1_BCLK0

CPU1_BCLK1

ITP_TCK_P

ITP_TDI_P1

ITP_TMS_P

ITP_TRST_N

ITP_TDO_P1

CPU1-SM_EP_A2

CPU1-SM_EP_A1

CPU1-SM_EP_A0

CPU1-SM_TS_A1

CPU1-SM_TS_A0

R1773 47/6

CPU1_VCCA

CPU1_VCCIOPLL

TP22

CPU1_VID4

CPU1_VID3

CPU1_VID2

CPU1_VID1

CPU1_VID0

CPU1_VSSA

TP23

TP27

R1394

10K/6

VCC3

C15

C14

220P/6

1U/6

U2B

D23

BPRI#

D10

BR3#

E11

BR2#

F12

BR1#

D20

BR0#

C23

DEFER#

Y8

RESET#

F21

RS2#

D22

RS1#

E21

RS0#

C6

RSP#

E19

TRDY#

F27

A20M#

C26

IGNNE

D6

INIT

E27

FERR#

G23

LINT1

B24

LINT0

AB7

PWRGOOD

C27

SMI#

AE6

SLP#

D4

STPCLK#

Y4

BCLK0

W5

BCLK1

E24

TCK

C24

TDI

A25

TMS

F24

TRST#

E25

TDO

AB28

SM_EP_A2

AB29

SM_EP_A1

AA29

SM_EP_A0

Y29

SM_TS_A1

AA28

SM_TS_A0

AC28

SM_CLK

AC29

SM_DAT

AD29

SM_WP

AD28

SM_ALERT#

AE28

SM_VCC0

AE29

SM_VCC1

AB4

VCCA

AD4

VCCIOPLL

B27

VCC_SENSE

AB3

BSEL1

AA3

BSEL0

B3

VID4

C3

VID3

D3

VID2

E3

VID1

F3

VID0

AA5

VSSA

D26

VSS_SENSE

AE15

RSVD11

AE4

SMB_PRT

SOCKET-604

CPU1_GTL_VREF2

C16

220P/6

Socket 604

Part 2

V_CORE

R79

51/6/1

C11

R81

1U/6

86.6/6/1

2

IERR#

ADS#

BINIT#

BNR#

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

DBSY#

DRDY#

HIT#

HITM#

LOCK#

MCERR#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

THERMTRIP#

PROCHOT#

COMP1

COMP0

GTLREF3

GTLREF2

GTLREF1

GTLREF0

ODTEN

SKTOCC#

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

NOCONA

86.6 ohn 1%

R81 100 ohn 1%

86.6 ohn 1%

R82 100 ohn 1%

CPU1_GTL_VREF1

C12

C13

220P/6

220P/6

R53

470/6

CPU1_IERR_N

E5

ADS_N

D19

BINIT_N

F11

BNR_N

F20

CPU_BPM5_N

E4

CPU_BPM4_N

E8

CPU_BPM3_N

F5

CPU_BPM2_N

E7

CPU_BPM1_N

F8

CPU_BPM0_N

F6

DBSY_N

F18

HDRDY_N

E18

HIT_N

E22

HITM_N

A23

HLOCK_N

A17

BERR_N

D7

ADSTB1

F14

ADSTB0

F17

DSTBP3

Y11

DSTBP2

Y14

DSTBP1

Y17

DSTBP0

Y20

DSTBN3

Y12

DSTBN2

Y15

DSTBN1

Y18

DSTBN0

Y21

CPU1_THRMTRIP_N

F26

PROC1_HOT_N

B25

CPU1_COMP1

E16

CPU1_COMP0

AD16

CPU1_GTL_VREF2

F9

F23

CPU1_GTL_VREF1

W9

W23

CPU1_ODTEN

B5

CPU1_SKTOCC_N

A3

CPU1_TESTHI6

AE5

CPU1_TESTHI5

AD5

CPU1_TESTHI4

AA7

CPU1_TESTHI3

Y6

CPU1_TESTHI2

W8

CPU1_TESTHI1

W7

CPU1_TESTHI0

W6

Y28

Y27

Y3

AD1

B1

AE30

CPU1_THERM_DC1 [40]

CPU1_THERM_DA1 [40]

TP39

TP41

TP42

TP373

PRESTONIA

Title

Size Document Number Rev

Date: Sheet of

CPU1_IERR_N [9]

ADS_N [5,11]

BINIT_N [5,11]

BNR_N [5,11]

CPU_BPM5_N [5,6]

CPU_BPM4_N [5,6]

CPU_BPM3_N [5,6]

CPU_BPM2_N [5,6]

CPU_BPM1_N [5,6]

CPU_BPM0_N [5,6]

DBSY_N [5,11]

HDRDY_N [5,11]

HIT_N [5,11]

HITM_N [5,11]

HLOCK_N [5,11]

BERR_N [5,11]

ADSTB[0..1]

DSTBP[0..3]

DSTBN[0..3]

CPU1_THRMTRIP_N [9]

PROC1_HOT_N [9]

R69 49.9/6/1

R70 49.9/6/1

R71 49.9/6/1

R90 4.7K/6

R72 49.9/6/1

R73 49.9/6/1

R74 49.9/6/1

R75 49.9/6/1

R76 49.9/6/1

R77 49.9/6/1

R78 49.9/6/1

V_CORE

R83

40.2/6/1/X

ADSTB[0..1] [5,11]

DSTBP[0..3] [5,11]

DSTBN[0..3] [5,11]

R84

40.2/6/1/X

R86

680/6

CPU1_SKTOCC_N [48,51]

3VSB

R85

75/6

GIGA-BYTE TECHNOLOGY CO., LTD.

CUP2 SIGNAL

GA-8IP533A

1

ITP_TRST_N

V_CORE

R1914

56/6

PROC1_HOT_N

ITP_TDI_P1

ITP_TCK_P

ITP_TMS_P

7 57T uesday, September 23, 2003

1.0

5

V_COREV_CORE

U2C

AD30

VCC1

D D

C C

B B

A A

AC31

AC3

AB30

AB2

AA31

AA1

M3

M1

L30

L28

L26

L24

K31

K29

K27

K25

K23

J30

J28

J26

J24

H31

H29

H27

H25

H23

G30

G28

G26

G24

G8

G6

G4

G2

F31

F29

F22

F16

F10

E30

E28

E26

E20

E12

D31

D29

D24

D18

D14

C30

C28

C22

C16

C10

B31

B29

B26

B20

B12

A30

A28

A24

A18

A14

L8

L6

L4

L2

K9

K7

K5

K3

K1

J8

J6

J4

J2

H9

H7

H5

H3

H1

F4

F1

E6

E2

D8

D1

C4

C2

B6

B4

A8

A2

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

SOCKET-604

Socket 604

Part 3

5

VCC96

VCC97

VCC98

VCC99

VCC100

VCC101

VCC102

VCC103

VCC104

VCC105

VCC106

VCC107

VCC108

VCC109

VCC110

VCC111

VCC112

VCC113

VCC114

VCC115

VCC116

VCC117

VCC118

VCC119

VCC120

VCC121

VCC122

VCC123

VCC124

VCC125

VCC126

VCC127

VCC128

VCC129

VCC130

VCC131

VCC132

VCC133

VCC134

VCC135

VCC136

VCC137

VCC138

VCC139

VCC140

VCC141

VCC142

VCC143

VCC144

VCC145

VCC146

VCC147

VCC148

VCC149

VCC150

VCC151

VCC152

VCC153

VCC154

VCC155

VCC156

VCC157

VCC158

VCC159

VCC160

VCC161

VCC162

VCC163

VCC164

VCC165

VCC166

VCC167

VCC168

VCC169

VCC170

VCC171

VCC172

VCC173

VCC174

VCC175

VCC176

VCC177

VCC178

VCC179

VCC180

VCC181

VCC182

VCC183

VCC184

VCC185

VCC186

VCC187

VCC188

VCC189

VCC190

AE3

Y2

AD2

AE24

AE18

AE14

AE8

AD26

AD20

AD12

AD6

AC22

AC16

AC10

AC4

AB24

AB18

AB14

AB8

AA26

AA20

AA12

AA6

AA4

Y30

Y22

Y16

Y10

W31

W29

W27

W25

W1

V30

V28

V26

V24

V8

V6

V4

V2

U31

U29

U27

U25

U23

U9

U7

U5

U3

U1

T30

T28

T26

T24

T8

T6

T4

T2

R31

R29

R27

R25

R23

R9

R7

R5

R3

R1

P30

P28

P26

P24

P8

P6

P4

P2

N31

N29

N27

N25

N23

N9

N7

N5

N3

N1

M31

M29

M27

M25

M23

M9

M7

M5

NC FOR NOCONA

49.9 ohm

FOR

NOCONA

R1693

0/6/X

R1694

49.9/6/1

4

U2D

M30

VSS1

M28

VSS2

M26

VSS3

M24

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

SOCKET-604

Socket 604

Part 4

G7 : BOOT_SELECT

C1 : TESTLOW

M8

M6

M4

M2

L31

L29

L27

L25

L23

L9

L7

L5

L3

L1

K30

K28

K26

K24

K8

K6

K4

K2

J31

J29

J27

J25

J23

J9

J7

J5

J3

J1

H30

H28

H26

H24

H8

H6

H4

H2

G31

G29

G27

G25

G9

G7

G5

G3

G1

F30

F28

F25

F19

F13

F7

F2

E31

E29

E23

E17

E15

E9

E1

D30

D28

D27

D21

D11

D5

D2

C31

C29

C25

C19

C13

C7

C1

B30

B28

B23

B17

B15

B9

B2

A31

A29

A27

A21

A11

A5

4

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

AE2

AD3

AE27

AE21

AE11

AD31

AD23

AD17

AD15

AD9

AC30

AC25

AC19

AC13

AC7

AC2

AB31

AB27

AB21

AB11

AB5

AB1

AA30

AA23

AA17

AA15

AA9

AA2

Y31

Y25

Y19

Y13

Y7

Y5

Y1

W30

W28

W26

W24

W4

W2

V31

V29

V27

V25

V23

V9

V7

V5

V3

V1

U30

U28

U26

U24

U8

U6

U4

U2

T31

T29

T27

T25

T23

T9

T7

T5

T3

T1

R30

R28

R26

R24

R8

R6

R4

R2

P31

P29

P27

P25

P23

P9

P7

P5

P3

P1

N30

N28

N26

N24

N8

N6

N4

N2

3

AC30 : SLEW_CTRL

FOR NOCONA

V_CORE

3

R1686

0/6/X

R1692

0/6

2

Title

Size Document Number Rev

2

Date: Sheet of

GIGA-BYTE TECHNOLOGY CO., LTD.

CPU2 POWER AND GND

1

GA-8IP533A

1

8 57T uesday, September 23, 2003

1.0

5

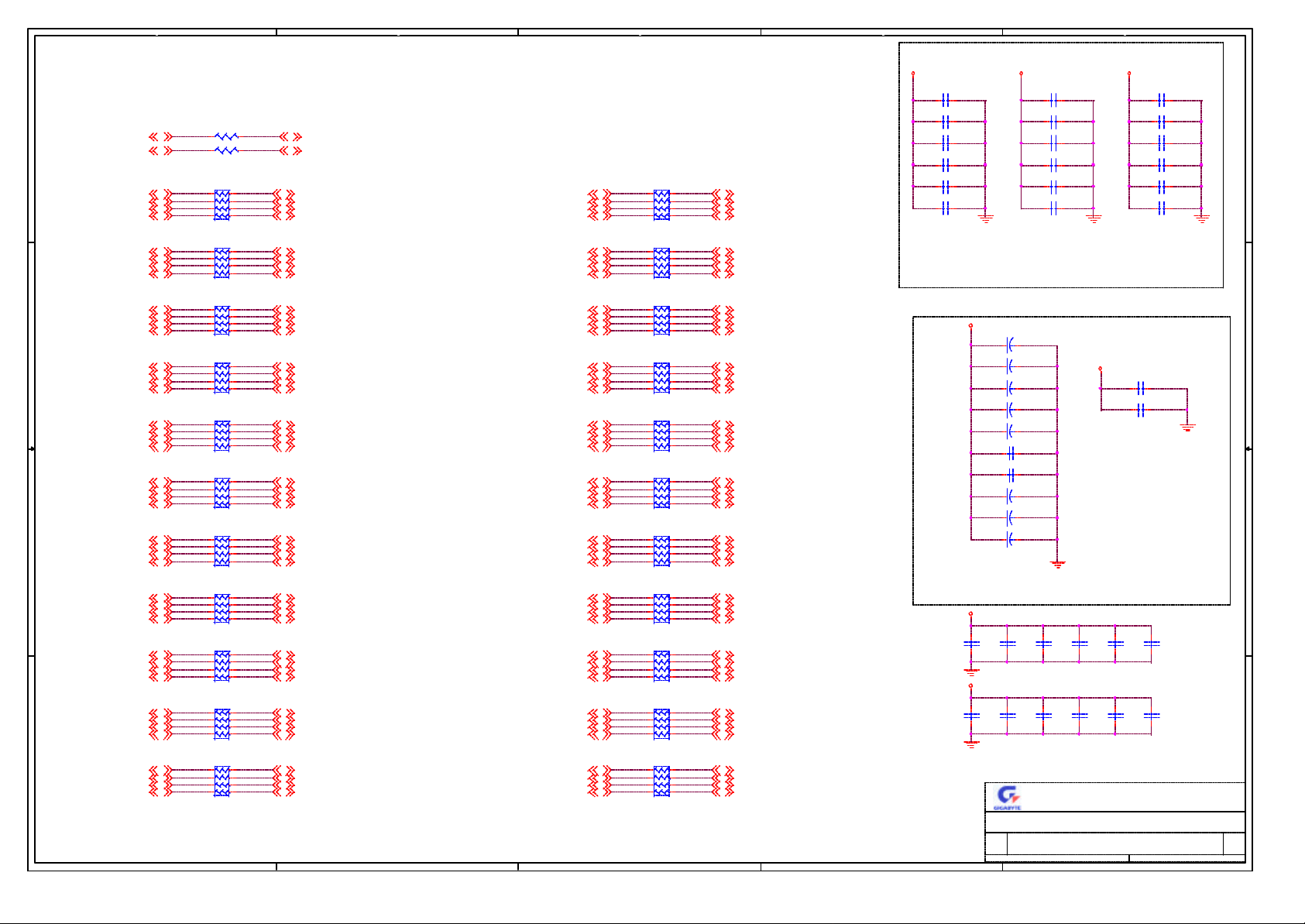

15

14

13

12

11

10

VCC3

R1567

4.7K/6

2

VCC

CPU1_BOOT_N

CPU1_BREQ0_N

3

Q142

2N7002

1

MCH_BREQ0_N [11]MCH_BREQ0_N[11]

CPU0_BREQ0 [7]

CPU1_BREQ0 [7]

CPU REDUCTION

ICH3_SMI_N[6,36]

D D

C C

CPU1 BRQ0

CPU1 BRQ1

ICH3_SMI_N

CPU DISABLE BY ICH3

GPO20,GPO21(MAIN

POWER)

CPU0_BOOT_N[51]

CPU0_BREQ0_N[5]

CPU1_BREQ0_N[5]

CPU0_BREQ0_N

R1651

4.7K/6

CPU0_DISABLE_N[37]

CPU1_DISABLE_N[37]

VCC3

R1566

100/6

3

2

Q141

2N3904

1

CPU0_DISABLE_N

CPU1_DISABLE_N

U150

1 16

NC VCC

2

BE0#

BE3#

3

A0

4

B0

5

BE1#

BE2#

6

A1

7

B1

8 9

GND NC

PI5C3125Q (BUS SWITCH)

R1656 0/6

R1657 0/6

A3

B3

A2

B2

4

VCC3

3VSB

VCC

1

2

VCC

1

2

R1592

4.7K/6/X

CPU0_BOOT_N

R1723

10K/6

53

53

SN74AHC1G08/SOT23-5

SN74AHC1G08/SOT23-5

R1589

4.7K/6

VCC3

R1590

4.7K/6

VCC

R1591

4.7K/6

Q152

3

2N7002

2

CPU0_BOOT_N IS LOW,THEN BOOT FROM

CPU1,OTHERWISE BOOT FROM CPU2

1

CPU2 BRQ1

CPU2 BRQ0

3VSB

U135

U136

CPU0_SMI

4

CPU1_SMI

4

CPU0_BOOT_N [51]

CPU1_THRMTRIP_N[7]

CPU0_THRMTRIP_N[5]

3

V_CORE

R1571

R1568

4.7K/6

4.7K/6

3

1

3

1

R1179

1K/6

Q119

2N2222

R98

1K/6

Q5

2N2222

VCC3V_CORE

Q120

2N2222

Q6

2N2222

CPU1_SMI

CPU0_SMI

2

2

CPU1_SMI_N[7]

CPU0_SMI_N[5]

CPU1_SMI_N

CPU0_SMI_N

R1181

470/6

R1182

V_CORE VCC3

0/6

R91

470/6

R1184

0/6

R1183

470/6

R100

470/6

2

2

3

1

3

1

1

2

3

4

5

6

7 8

R1180

10K/6

C1652

1U/6

R99

10K/6

C1653

1U/6

U149

1A

1Y

2A

2Y

3A

3Y

GND 4Y

7407

R1300

1K/6

R1355

1K/6

VCC

R1302

1K/6

2

VCC

14

13

6A

12

6Y

11

5A

10

5Y

9

4A

3VSB

R1301

1K/6

U126A

VCC3

13

12

11

10

1

2

3

4

R1303

100/6

CLR

D

CLK

PRE

SN74AHC74

U126B

CLR

D

CLK

PRE

SN74AHC74

VDD

GND

VDD

GND

14

5

Q

6

Q

7

3VSB

14

9

Q

8

Q

7

3VSB

3VSB

14

U67B

4

5

1

2

3VSB

7

14

74LVC08/SO

7

6

74LVC08/SO

U67A

3

VCC3

1

IPMI_CPU1_THRMTRIP_N [42,48,51]

IPMI_CPU0_THRMTRIP_N [42,48,51]

R105

470/6

R1192

470/6

VCC3

R103

1K/6

3

2

2

2

Q7

2N2222

1

VCC3

R1188

R1189

1K/6

10K/6

3

2

Q121

2N2222

1

3

1

3

1

R104

10K/6

Q8

2N2222

Q122

2N2222

R1729

1K/6

R1731

1K/6

R1732

1K/6

R1730

1K/6

U155A

1

CLR

2

D

3

CLK

4

PRE

SN74AHC74

U155B

13

CLR

12

D

11

CLK

10

PRE

SN74AHC74

3VSB

R1733

1K/6

RESET CPU HOT CIRCUIT FROM

BMC (OD OUTPUT)

4

14

VDD

5

Q

6

Q

7

GND

14

VDD

9

Q

8

Q

7

GND

RESET_CPU_HOT_N

IPMI_PROC0_HOT_N

3VSB

IPMI_PROC1_HOT_N

RESET_CPU_HOT_N [51]

IPMI_PROC0_HOT_N [40]

3VSBV_CORE

R1737

R1736

IPMI_PROC1_HOT_N [40]

P0_FORCEPR_N[5] BMC_FORCEPR0_N [51]

P1_FORCEPR_N[7] BMC_FORCEPR1_N [51]

P1_FORCEPR_N BMC_FORCEPR1_N

3

470/6

R1739

0/6/X

V_CORE 3VSB

R1740

470/6

R1743

321

0/6/X

321

Q170

2N2222

Q171

2N2222

470/6

R1741

470/6

R1738

1K/6

BMC_FORCEPR0_NP0_FORCEPR_N

R1742

1K/6

R1304

10K/6

2

R1193

470/6

3

R1195

2

CPU0_IERR_N[5,6]

CPU1_IERR_N[7]

470/6

Q123

2N2222

1

R1196

470/6

3

R1198

2

Q125

2N2222

1

470/6

Title

Size Document Number Rev

Date: Sheet of

R1194

300/6

IPMI_IERR0_N [51]

3

2

Q124

2N2222

1

VCC3

R1197

300/6

IPMI_IERR1_N [51]

3

2

Q126

2N2222

1

GIGA-BYTE TECHNOLOGY CO., LTD.

LEVEL SHIFT

GA-8IP533A

1

9 57Tuesday, September 23, 2003

1.0

D

X

LQ0L

X

Q

R1186

0/6

R1191

0/6

5

V_CORE

V_CORE

R1673

470/6

R1190

470/6

74AHC74 FUNCTION TABLE

B B

PROC0_HOT_N[5]

A A

CLK

CLR#

PRE#

H

L

H

H

H

L H

X

H

PROC1_HOT_N[7]

5

V_CORE

C17

C18

100U/1210

D D

V_CORE

100U/1210

C19

100U/1210

C20

1U/8

C21

1U/8

C22

1U/8

C23

1U/8

C24

1U/8

C1535

100U/1210

4

PROCESSOR 1

C1536

C1537

100U/1210

100U/1210

C1538

100U/1210

C1541

100U/1210

3

Place on CPU0 Address Side

V_CORE

C51

1U/6

C52

1U/6

C53

1U/6

C54

1U/6

V_CORE

2

C35

0.1U/6

C26

22U/12

C36

0.1U/6

C27

22U/12

C37

0.1U/6

C28

22U/12

C38

0.1U/6

C39

0.1U/6

C30

100U/1210

C40

0.1U/6

1

C31

100U/1210

C41

0.1U/6

C32

100U/1210

C42

0.1U/6

C33

100U/1210

C43

0.1U/6

C34

100U/1210

C44

0.1U/6

EC7

EC2

1500U/2.5V

SBC1

100U/1210

EC3

1500U/2.5V

SBC2

100U/1210

EC1

1500U/2.5V

V_CORE

C C

EC4

1500U/2.5V

SBC3

100U/1210

EC5

1500U/2.5V

SBC4

100U/1210

EC6

1500U/2.5V

SBC5

100U/1210

1500U/2.5V

SBC6

100U/1210

EC101

1500U/2.5V

SBC7

100U/1210

EC102

1500U/2.5V

EC103

1500U/2.5V

EC104

1500U/2.5V

100U/1210

C1420

V_CORE

C1421

100U/1210

C45

1U/6

C46

1U/6

C1423

100U/1210

Place on CPU0 Data Side

C1497

100U/1210

100U/1210

V_CORE

C75

V_CORE

100U/1210

C1504

1U/8

EC11

1500U/2.5V

B B

V_CORE

V_CORE

A A

C1501

SBC9

100U/1210

C1505

100U/1210

C1502

C1503

100U/1210

100U/1210

C1417

100U/1210

PROCESSOR 2

C78

C77

C76

1U/8

EC12

1500U/2.5V

SBC10

100U/1210

1U/8

EC14

1500U/2.5V

SBC11

100U/1210

C1453

100U/1210

100U/1210

EC16

1500U/2.5V

SBC12

100U/1210

C1457

100U/1210

C79

100U/1210

EC17

1500U/2.5V

100U/1210

SBC8

100U/1210

C80

100U/1210

SBC13

100U/1210

C1458

SBC52

22U/12

C81

100U/1210

EC105

1500U/2.5V

SBC14

100U/1210

C1462

100U/1210

SBC53

22U/12

C82

1U/8

SBC15

100U/1210

SBC16

100U/1210

SBC99

100U/1210

SBC74

22U/1206

SBC100

100U/1210

SBC75

22U/1206

SBC101

100U/1210

V_CORE

SBC102

SBC103

100U/1210

100U/1210

Place on CPU1 Address Side

V_CORE

Place on CPU1 Data Side

C103

C104

1U/6

C105

1U/6

1U/6

GALLATIN/PRESTONIA PROCESSOR 0/1 DECOUPLING

5

4

3

C47

1U/6

SBC104

100U/1210

C106

1U/6

C1424

100U/1210

C48

1U/6

C1419

100U/1210

C109

1U/6

C107

1U/6

C49

1U/6

C110

1U/6

V_CORE

C108

1U/6

C50

1U/6

C111

1U/6

C112

1U/6

V_CORE

SBC92

100U/1210

V_CORE

V_CORE

SBC93

100U/1210

SBC32

0.1U/6

SBC42

0.1U/6

SBC54

0.1U/6

SBC64

0.1U/6

SBC94

100U/1210

SBC33

0.1U/6

SBC43

0.1U/6

C83

22U/12

C93

0.1U/6

SBC55

0.1U/6

SBC65

0.1U/6

2

BACKSIDE CAPS

SBC34

0.1U/6

SBC44

0.1U/6

C84

22U/12

C94

0.1U/6

SBC56

0.1U/6

SBC66

0.1U/6

SBC95

SBC96

100U/1210

100U/1210

SBC36

SBC35

0.1U/6

SBC45

0.1U/6

C85

22U/12

C95

0.1U/6

SBC57

0.1U/6

SBC67

0.1U/6

SBC37

0.1U/6

0.1U/6

SBC46

SBC47

0.1U/6

0.1U/6

C87

C86

22U/12

22U/12

C97

C96

0.1U/6

0.1U/6

SBC59

SBC58

0.1U/6

0.1U/6

SBC68

SBC69

0.1U/6

0.1U/6

Title

Size Document Number Rev

Date: Sheet of

GIGA-BYTE TECHNOLOGY CO., LTD.

CPU DECOUPLING

SBC38

0.1U/6

SBC48

0.1U/6

C88

22U/12

C98

0.1U/6

SBC60

0.1U/6

SBC70

0.1U/6

SBC39

0.1U/6

SBC49

0.1U/6

C89

22U/12

C100

C99

0.1U/6

0.1U/6

SBC61

0.1U/6

SBC71

0.1U/6

GA-8IP533A

1

SBC40

0.1U/6

SBC50

0.1U/6

SBC62

0.1U/6

SBC72

0.1U/6

C101

0.1U/6

10 57T uesday, September 23, 2003

SBC41

0.1U/6

SBC51

0.1U/6

SBC63

0.1U/6

SBC73

0.1U/6

C102

0.1U/6

1.0

5

H_CLKINN[46]

H_CLKINP[46]

R110 24.9/6/1

DSTBP[0..3][5,7]

DSTBN[0..3][5,7]

RSP_N[5,7]

RS[0..2][5,7]

ADSTB[0..1][5,7]

HYSWING

C150

0.01U/6

HA[3..35][5,7]

DBI[0..3][5,7]

DP[0..3][5,7]

R111 24.9/6/1

DSTBP[0..3]

DSTBN[0..3]

RS[0..2]

ADSTB[0..1]

HA[3..35]

DBI[0..3]

DP[0..3]

BINIT_N[5,7]

ICH3_PWROK[31,38,48]

HDRDY_N[5,7]

DEFER_N[5,7]

DBSY_N[5,7]

CPURST_N[5,6,7]

MCH_BREQ0_N[9]

BPRI_N[5,7]

BNR_N[5,7]

BERR_N[5,7]

AP0_N[5,7]

AP1_N[5,7]

ADS_N[5,7]

R131

301/6/1

R133

150/6/1

5

D D

C C

B B

A A

H_CLKINN

H_CLKINP

HYCOMP

HXCOMP

HYSWING

HXSWING

DSTBP0

DSTBP1

DSTBP2

DSTBP3

DSTBN0

DSTBN1

DSTBN2

DSTBN3

RSP_N

RS0

RS1

RS2

ADSTB0

ADSTB1

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA17

HA18

HA19

HA20

HA21

HA22

HA23

HA24

HA25

HA26

HA27

HA28

HA29

HA30

HA31

HA32

HA33

HA34

HA35

DBI0

DBI1

DBI2

DBI3

DP0

DP1

DP2

DP3

BINIT_N

ICH3_PWROK

HDRDY_N

DEFER_N

DBSY_N

CPURST_N

BPRI_N

BNR_N

BERR_N

AP0_N

AP1_N

ADS_N

HXSWING

C151

0.01U/6

R108

4.7K/6/1

V_COREV_CORE

VCC3

U3A

C29 AB2

XORMODE_N HREQ0_N

U3

H_CLKINN

T2

H_CLKINP

G5

HYRCOMP

V4

HXRCOMP

K5

HYSWING

V8

HXSWING

B8

HDSTBP0_N

H6

HDSTBP1_N

J4

HDSTBP2_N

P3

HDSTBP3_N

B6

HDSTBN0_N

K6

HDSTBN1_N

J2

HDSTBN2_N

R4

HDSTBN3_N

AK4

RSP_N

V2

RS0_N

V5

RS1_N

U4

RS2_N

AE1

HADSTB0_N

AD7

HADSTB1_N

AA8

HA3_N

AB1

HA4_N

AC3

HA5_N

AD2

HA6_N

AB6

HA7_N

AC4

HA8_N

AD4

HA9_N

AE5

HA10_N

AE2

HA11_N

AC6

HA12_N

AB9

HA13_N

AE6

HA14_N

AE3

HA15_N

AD5

HA16_N

AB8

HA17_N

AC7

HA18_N

AC9

HA19_N

AH2

HA20_N

AH3

HA21_N

AG2

HA22_N

AF6

HA23_N

AD8

HA24_N

AF1

HA25_N

AG4

HA26_N

AJ4

HA27_N

AE8

HA28_N

AF3

HA29_N

AF7

HA30_N

AH5

HA31_N

AG7

HA32_N

AH6

HA33_N

AJ1

HA34_N

AG5

HA35_N

F8

DBI0_N

D2

DBI1_N

L4

DBI2_N

P1

DBI3_N

Y4

DP0_N

AA2

DP1_N

AA5

DP2_N

AA4

DP3_N

AG8

BINIT_N

A28

PWRGOOD

Y3

DRDY_N

W8

DEFER_N

W6

DBSY_N

W9

CPURST_N

AF9

BREQ0_N

U6

BPRI_N

V1

BNR_N

AK2

XERR_N

AJ6

AP0_N

AK5

AP1_N

Y7

ADS_N

U3

R1298

4.7K/6

VCC3

MCH_RSVD_02

R132

301/6/1

R134

150/6/1

4

HTRDY_N

HLOCK_N

HITM_N

HIT_N

C133

1U/8

-HREQ[0..4]

R113

86.6/6/1

HD[0..63]

HREQ1_N

HREQ2_N

HREQ3_N

HREQ4_N

HTRDY_N

HLOCK_N

HITM_N

HIT_N

HAVREF0

HAVREF1

HCCVREF

HDVREF0

HDVREF1

HDVREF2

HDVREF3

HD63_N

HD62_N

HD61_N

HD60_N

HD59_N

HD58_N

HD57_N

HD56_N

HD55_N

HD54_N

HD53_N

HD52_N

HD51_N

HD50_N

HD49_N

HD48_N

HD47_N

HD46_N

HD45_N

HD44_N

HD43_N

HD42_N

HD41_N

HD40_N

HD39_N

HD38_N

HD37_N

HD36_N

HD35_N

HD34_N

HD33_N

HD32_N

HD31_N

HD30_N

HD29_N

HD28_N

HD27_N

HD26_N

HD25_N

HD24_N

HD23_N

HD22_N

HD21_N

HD20_N

HD19_N

HD18_N

Plumas MCH System Bus I/F

HD17_N

HD16_N

HD15_N

HD14_N

HD13_N

HD12_N

HD11_N

HD10_N

HD9_N

HD8_N

HD7_N

HD6_N

HD5_N

HD4_N

HD3_N

HD2_N

HD1_N

HD0_N

4

-HREQ2

AA7

-HREQ3

AB3

-HREQ4

Y9

W3

V7

W5

U1

AF4

AJ3

Y6

C5

N8

P6

T7

HD63

T8

HD62

R5

HD61

T5

HD60

T9

HD59

U7

HD58

T3

HD57

T6

HD56

R2

HD55

N1

HD54

N3

HD53

N2

HD52

L2

HD51

M2

HD50

P4

HD49

N4

HD48

L3

HD47

R8

HD46

R7

HD45

N7

HD44

P7

HD43

M4

HD42

P9

HD41

J5

HD40

N6

HD39

K1

HD38

K2

HD37

J1

HD36

G3

HD35

K3

HD34

G2

HD33

H3

HD32

H4

HD31

M7

HD30

F1

HD29

E3

HD28

F2

HD27

D3

HD26

F4

HD25

E1

HD24

M8

HD23

E4

HD22

F5

HD21

D6

HD20

G6

HD19

E6

HD18

L6

HD17

L7

HD16

F7

HD15

J7

HD14

J8

HD13

C2

HD12

H7

HD11

D7

HD10

C7

HD9

C4

HD8

A8

HD7

C8

HD6

A5

HD5

B3

HD4

E8

HD3

B5

HD2

A4

HD1

A9

HD0

B9

MCH_RSVD_01

R1299

1K/6

-HREQ0

-HREQ1

AA1

-HREQ[0..4] [5,7]

HTRDY_N [5,7]

HLOCK_N [5,7]

HITM_N [5,7]

HIT_N [5,7]

R112

51/6/1

V_CORE

NOCONA

R113 100 ohm 1%

86.6 ohm 1%

HD[0..63] [5,7]

3

PROSTENIA

3

VCC1_2

ICH3_SMBDATA[15,16,19,20,24,37,46]

ICH3_SMBCLK[15,16,19,20,24,37,46]

ICH3_HI[0..11][36]

C134

0.1U/6

C142

0.1U/6

2

U3B

G13

HI21_B

F14

HI20_B

E14

HI18_B

B17

HI17_B

H14

HI16_B

J14

HI15_B

C11

HI14_B

E12

HI13_B

D12

HI12_B

C13

HI11_B

A13

HI10_B

F13

HI9_B

C14

HI8_B

D15

HI7_B

B14

HI6_B

A16

HI5_B

A17

HI4_B

C16

HI3_B

C17

HI2_B

G16

HI1_B

D16

HI0_B

G15

PSTRBF_B

H15

PSTRBS_B

A12

PUSTRBF_B

B12

47/6

G10

G12

R120

453/6/1/X

R124

499/6/1/X

R128

392/6/1

PUSTRBS_B

E15

HI_RCONP_B

B15

HISWNG_B

D13

HIVREF_B

B31

SMB_DATA

J25

SMB_CLK

B30

RESERVED02

D29

RESERVED01

J16

CLK66

E28

RSTIN_N

H12

HISWNG_A

G9

HI_VREF_A

H11

HI_RCOMP_A

D10

PSTRBS_A

C10

PSTRBF_A

E11

HI0_A

B11

HI1_A

HI2_A

F10

HI3_A

D9

HI4_A

E9

HI5_A

J11

HI6_A

H9

HI7_N

J13

HI8_A

J10

HI9_N

F11

HI10_A

HI11_N

HI_VSWING_B

HI_VREF_B

Plumas MCH Hub Interfaces

U3

C138

C137

0.1U/6/X

0.01U/6/X

C145

C146

0.01U/6/X

0.1U/6/X

2

R114 24.9/6/1/X

ICH3_SMBDATA

ICH3_SMBCLK

MCH_CLK66[46]

PCIRST2_5_N[15,16,19,20,36]

VCC2_5

VCC1_2

R118 24.9/6/1

ICH3_PSTRBS[36]

ICH3_PSTRBF[36]

ICH3_HI[0..11]

VCC1_2 VCC1_2 VCC1_2 VCC1_2

R119

453/6/1

HI_VSWING_A

R123

499/6/1

HI_VREF_A

R127

392/6/1

HI_RCOMP_B

HI_VSWING_B

HI_VREF_B

R1774

MCH_RSVD_02

TP43

MCH_RSVD_01

TP44

R117 100/6

HI_VSWING_A

HI_VREF_A

HI_RCOMP_A

ICH3_PSTRBS

ICH3_PSTRBF

ICH3_HI0

ICH3_HI1

ICH3_HI2

ICH3_HI3

ICH3_HI4

ICH3_HI5

ICH3_HI6

ICH3_HI7

ICH3_HI8

ICH3_HI9

ICH3_HI10

ICH3_HI11

C136

C135

0.1U/6/X

0.01U/6

C144

C143

0.1U/6/X

0.01U/6

F16

HI21_C

H18

HI20_C

F20

HI18_C

C24

HI17_C

B21

HI16_C

F17

HI15_C

E18

HI14_C

C18

HI13_C

B18

HI12_C

C19

HI11_C

B20

HI10_C

A20

HI9_C

D19

HI8_C

E21

HI7_C

D21

HI6_C

F19

HI5_C

E20

HI4_C

C22

HI3_C

G18

HI2_C

B24

HI1_C

D22

HI0_C

C23

PSTRBF_C

B23

PSTRBS_C

D18

PUSTRBF_C

E17

PUSTRBS_C

HI_RCONP_C

HISWWG_C

HIVREF_C

HIVREF_D

HISWNG_D

HI_RCOMP_D

PUSTRBS_D

PUSTRBF_D

PSTRBS_D

PSTRBF_D

HI0_D

HI1_D

HI2_D

HI3_D

HI4_D

HI5_D

HI6_D

HI7_D

HI8_D

HI9_D

HI10_D

HI11_D

HI12_D

HI13_D

HI14_D

HI15_D

HI16_D

HI17_D

HI18_D

HI20_D

HI21_D

453/6/1/X

499/6/1/X

392/6/1

HI_RCOMP_C

C20

HI_VSWING_C

H17

HI_VREF_C

A21

HI_VREF_D

J22

HI_VSWING_D

F24

HI_RCOMP_D

G21

P1_PUSTRBS

C25

P1_PUSTRBF

B25

P1_PSTRBS

D26

P1_PSTRBF

D27

P1_HI0

D28

P1_HI1

G25

P1_HI2

G26

P1_HI3

F26

P1_HI4

G24

P1_HI5

A27

P1_HI6

H24

P1_HI7

C26

P1_HI8

G22

P1_HI9

E24

P1_HI10

A25

P1_HI11

D24

P1_HI12

A24

P1_HI13

E23

P1_HI14

F23

P1_HI15

F22

P1_HI16

H23

P1_HI17

H25

P1_HI18

F25

P1_HI20

E27

P1_HI21

H21

R121

HI_VSWING_C

R125

HI_VREF_C

R129

Title

Size Document Number Rev

Date: Sheet of

R115 24.9/6/1/X

C139

0.01U/6/X

C140

0.1U/6

C147

C148

0.01U/6/X

0.1U/6

GIGA-BYTE TECHNOLOGY CO., LTD.

MCH-CPU AND HUB INTERFACE

1

R116 24.9/6/1

P1_PUSTRBS [24]

P1_PUSTRBF [24]

P1_PSTRBS [24]

P1_PSTRBF [24]

P1_HI[0..15]

P1_HI16 [24]

P1_HI17 [24]

P1_HI18 [24]

P1_HI20 [24]

P1_HI21 [24]

R122

453/6/1

R126

499/6/1

R130

392/6/1

GA-8IP533A

1

VCC1_2

VCC1_2

P1_HI[0..15] [24]

HI_VSWING_D

C141

0.01U/6

HI_VREF_D

C149

0.01U/6

11 57T uesday, September 23, 2003

1.0

5

U3C

VTT_DDR

AF22

AN28

AE21

AH22

AM27

AF21

AN29

AM28

AL26

AL25

AN25

AM24

AG21

AE20

AL23

AK23

AM25

AK24

AL22

AJ22

AK19

AL19

AN17

AF18

AG18

AK18

AN20

AM19

AL17

AJ18

AF19

AH19

AM21

AL20

AE18

AK20

AH20

AJ21

AN21

AJ19

AL14

AM13

AJ15

AF15

AL13

AJ13

AK14

AN13

AH14

AG14

AE14

AH13

AN12

AL11

AM12

AK12

AE15

AF13

AJ12

AM10

AE12

AH11

AG11

AN5

AL8

AM7

AG12

AF12

AM9

AM6