Page 1

www.kythuatvitinh.com

5

Digitally signed by dd

DN: cn=dd, o=dd,

ou=dd,

email=dddd@yahoo.

com, c=US

Date: 2009.10.23

06:48:26 +07'00'

4

3

2

1

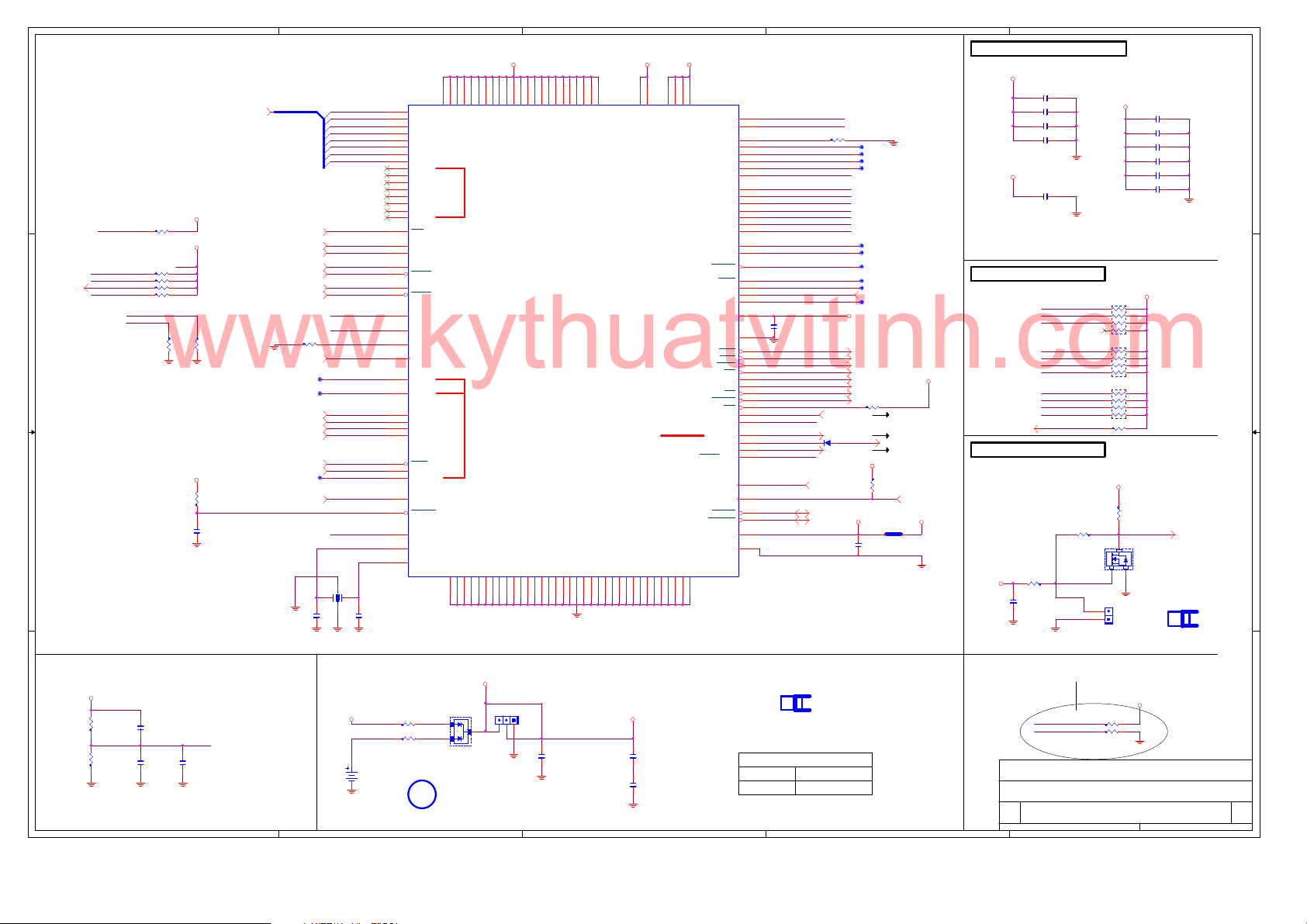

Model Name: GA-7VM400AMF

Revision 1.0

D D

C C

B B

SHEET

1

2

3

4,5

6,7,8

9

10,11,12

13,14

15

16

17

18

19

20

21

BOM & PCB MODIFY HISTORY

COVER SHEET

BLOCK DIAGRAM

AMD CPU SOCKET A

KM400 HOST; DDR; AGP,VLINK,POWER/GOUND

CLOCK GENERATOR (ICS950913CF)

VT8237 (SOUTH BIRDGE)

DDR SDRAM DIMMS 1,2 DDR TERMINATION

AGP SLOT

PCI SLOT 1,2,3

IDE,USB

LPCIO_IT8705

BIOS

COM,PRT,FDD,KB/MS,IR

AC 97 CODEC

TITLE

22

23

24

25

26

A A

27

28

5

4

AUDIO JACK,GAME PORT

RTL8110S & USB CONNECTOR

PANEL,STR LED,FANS

DDR POWER

ATX CONN,3VDUAL,VDDQ DC POWER

VCORE PHASE PWM FAIRCHILD FAN5091M

VID,FID CONTROL

TI TSB43AB2329

3

COMPONENT SIDE

(1 oz. Copper)

GND SIDE

(1 oz. Copper)

VCC SIDE

(1 oz. Copper)

SOLDER SIDE

(1 oz. Copper)

Title

Size Document Number Rev

Custom

2

Date: Sheet of

GIGABYTE

COVER SHEET

GA-7VM400AMF

1

1 29Wednesday, December 17, 2003

1.0

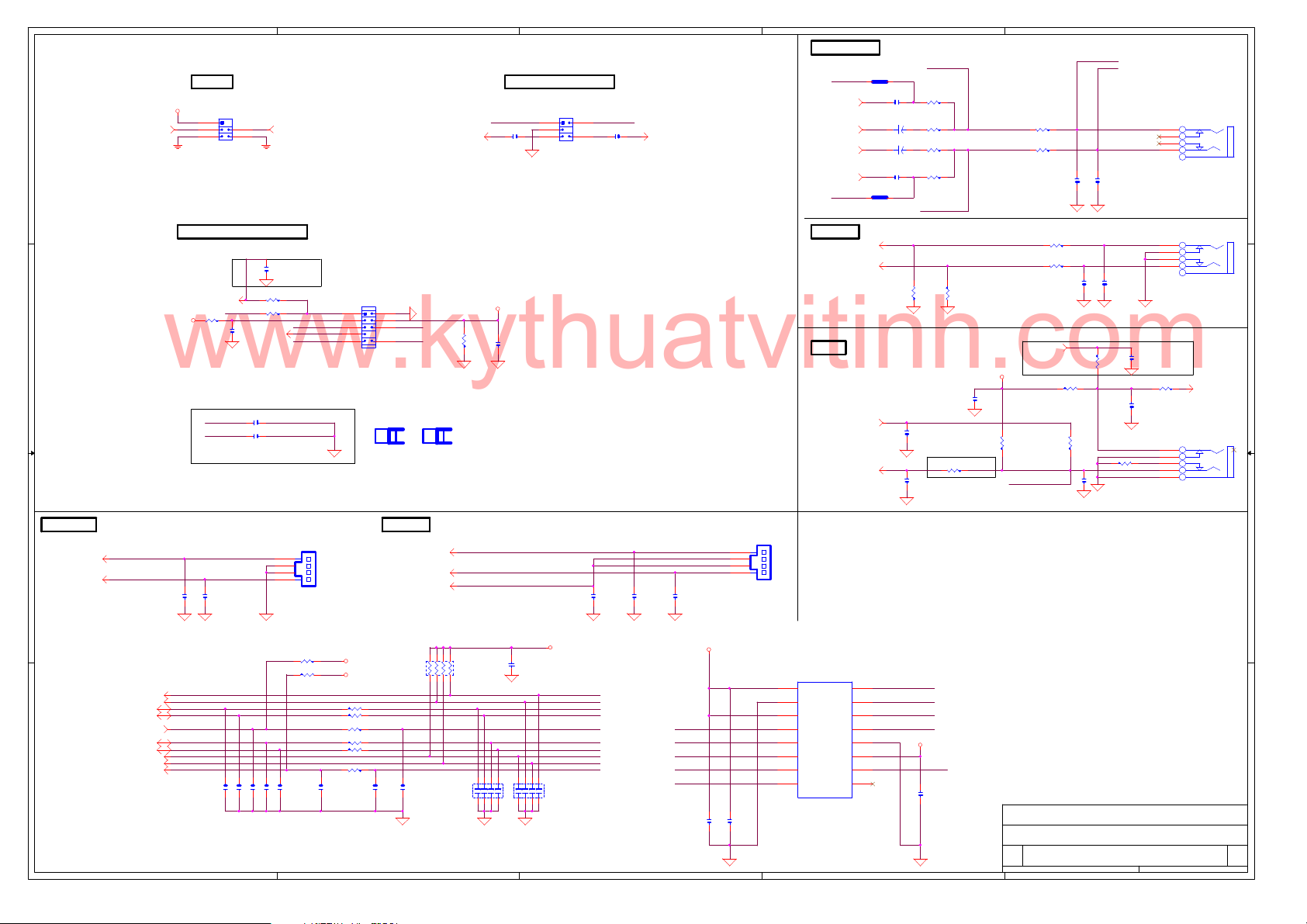

Page 2

www.kythuatvitinh.com

5

4

3

2

1

Model Name: GA-7VM400AMF

Circuit or PCB layout change for next version

Version:1.0

D D

Component value change history

2003.09.22

Date Change Item Reason

2003/10/28 Modify from 7VM400AMFP 0.1. Change model name.

2003/11/24 1.0A BOM RELEASE SOLVE DDR COMPATIBILITY

2003/12/09 1.0B BOM RELEASE COST DOWN

2003/12/17 Add VT8237/CD China Version. 1.0B BOM ECN

C C

0.1 BOM ISSUED.

Change NB form KKM400A/A1 to KM400A/A2.

Date Change Item Reason

2003/10/01 VER: 0.1 PCB 0.1 GERBER OUT

2003/11/20

VER: 1.0 PCB 1.0 GERBER OUT

B B

A A

Title

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

GIGABYTE

BOM & PCB MODIFY HISTORY

GA-7VM400AMF

1

2 29Wednesday, December 17, 2003

1.0

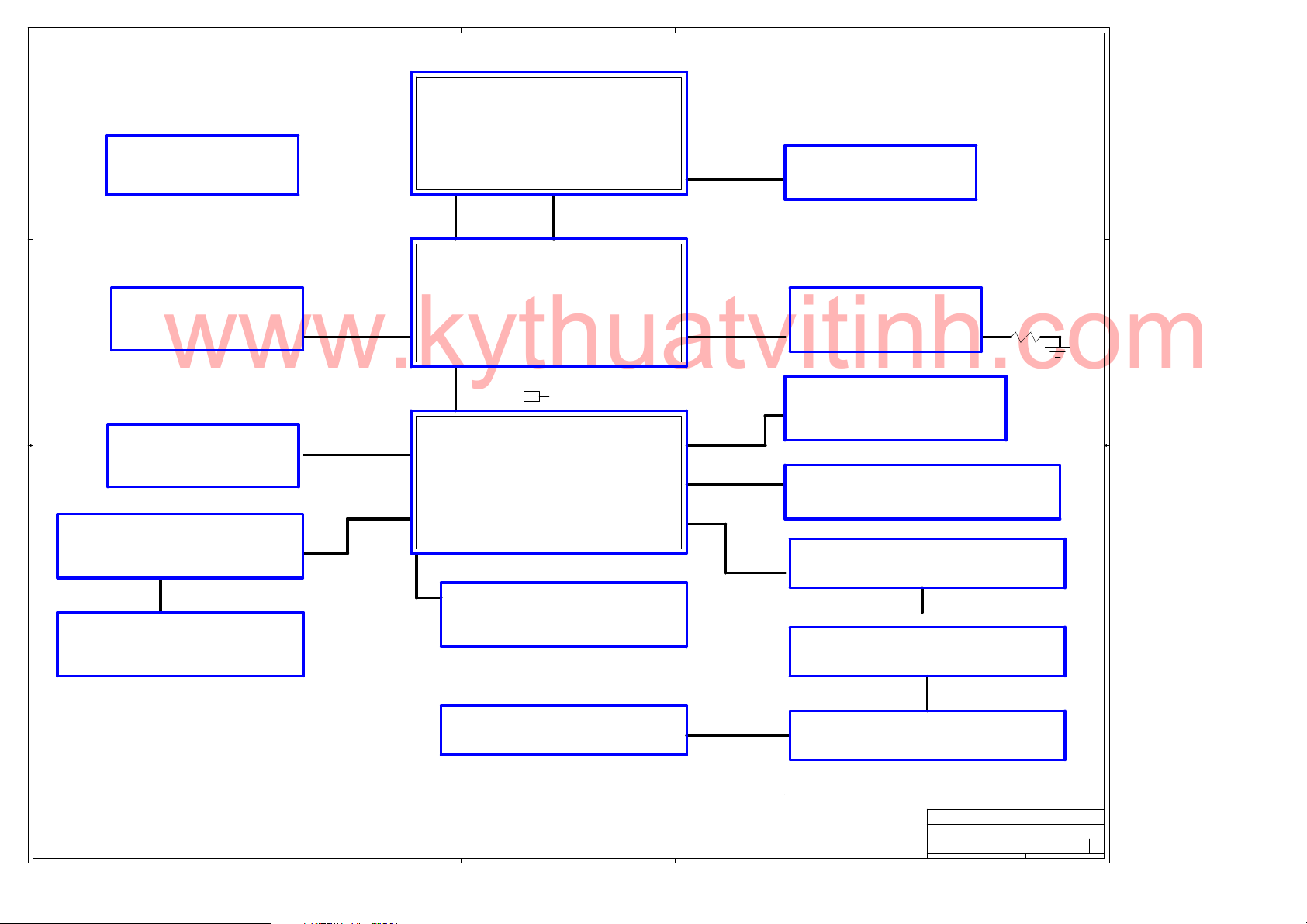

Page 3

www.kythuatvitinh.com

5

4

3

2

1

GA-7VM400AMF BLOCK DIAGRAM

AMD K7

D D

CLOCK

VCC25 = 2.5V(I/O,MEMORY/I,VLINK/I)

VCC3 = 3.3V

PAGE 09

VCORE = 1.75V (650-1100MHZ) / SLEEP : 1.3V

VCCA = 2.5V ; 2_5V = 2.5V

PAGE 4, 5

VID0~4

PWM/OTHER POWER

VCORE = 1.75V (650-1100MHZ) / SLEEP : 1.3V

5VSB,-12V,+12V,VCC,VCC3,3VDUAL

DDRVTT,DDR25V,3VSTR,VCC25

PAGE 25,26,27

GAD0~31

AD_STB0,-AD_STB0

AD_STB1,-AD_STB1

AGP SLOT 4X/8X

VDDQ = 1.5V (AGP POWER 4X)

VCC3 = 3.3V

+12V = 12V

C C

3VDUAL = 3.3V

VCC = 5V

PAGE 15

SBA0~7

SB_STB,-SB_STB

-GBE0~3

ST0~2

AGP BUS

USB PORTS 0~7

VCC = 5V

5VSB = 5V

5VUSB = 5V

PAGE 19

AC97 CODEC ALC655/D

B B

+12V = 12V

VCC3 = 3.3V

VCC = 5V

AVDD = 5V

PAGE 21

VIA KM400A NORTH BRIDGE

VCORE = 1.75V (650-1100MHZ) / SLEEP : 1.3V

DDR25V = 2.5V(SUSPEND POWER)

VDDQ = 1.5V (AGP POWER 4X)

VCC25 = 2.5V(I/O,MEMORY/I,VLINK/I)

VLAD0~7

CONTROL BUS

V LINK

VIA VT8237/CD A2 SOUTH

BRIDGE

VCC25 = 2.5V(I/O,MEMORY/I,VLINK/I)

3VDUAL = 3.3V(SUSPEND POWER)

VCC3 = 3.3V

RTCVDD = 3.3V

PCI BUS

PAGE 10,11,12

PAGE 6,7,8

MAA0~15

MDD0~63

-DQSD0~7

PCI LAN

LPC BUS

DDR SDRAM DIMM X 2

DDR25V = 2.5V(SUSPEND POWER)

DDRVTT = 1.25V

PAGE 13,14

DQM0~7

RTL8100C & USB CONN

PAGE 23

IDE Primary and Secondary

VCC = 5V

PAGE 17

BIOS

VCC = 5V

VCC3 = 3V

PAGE 19

PCI SLOT 1,2,3

+12 = 12V

AUDIO PORTS :

LIN_ OUT

TELE

CD_IN

LINE_IN

AUX_IN

FRONT AUDIO

MIC

GAME PORT

PAGE 22

-12 = -12V

VCC = 5V

VCC3 = 3V

3VDUAL = 3V

PAGE 16

LPC I/O IT8705

VCC = 5V

5VSB = 5V

VBAT = 3V

PAGE 18

FRONT PANEL/FANS

VCC = 5V

5VSB = 5V

+12 = 12V

A A

5

4

PVCC = 5V

3

PAGE 24

I/O PORTS :

COMA COMB LPT IR FDD

2

PAGE 20

Title

Size Document Number Rev

Custom

Date: Sheet of

GIGABYTE

BLOCK DIAGRAM

GA-7VM400AMF

1

1.0

3 29Wednesday, December 17, 2003

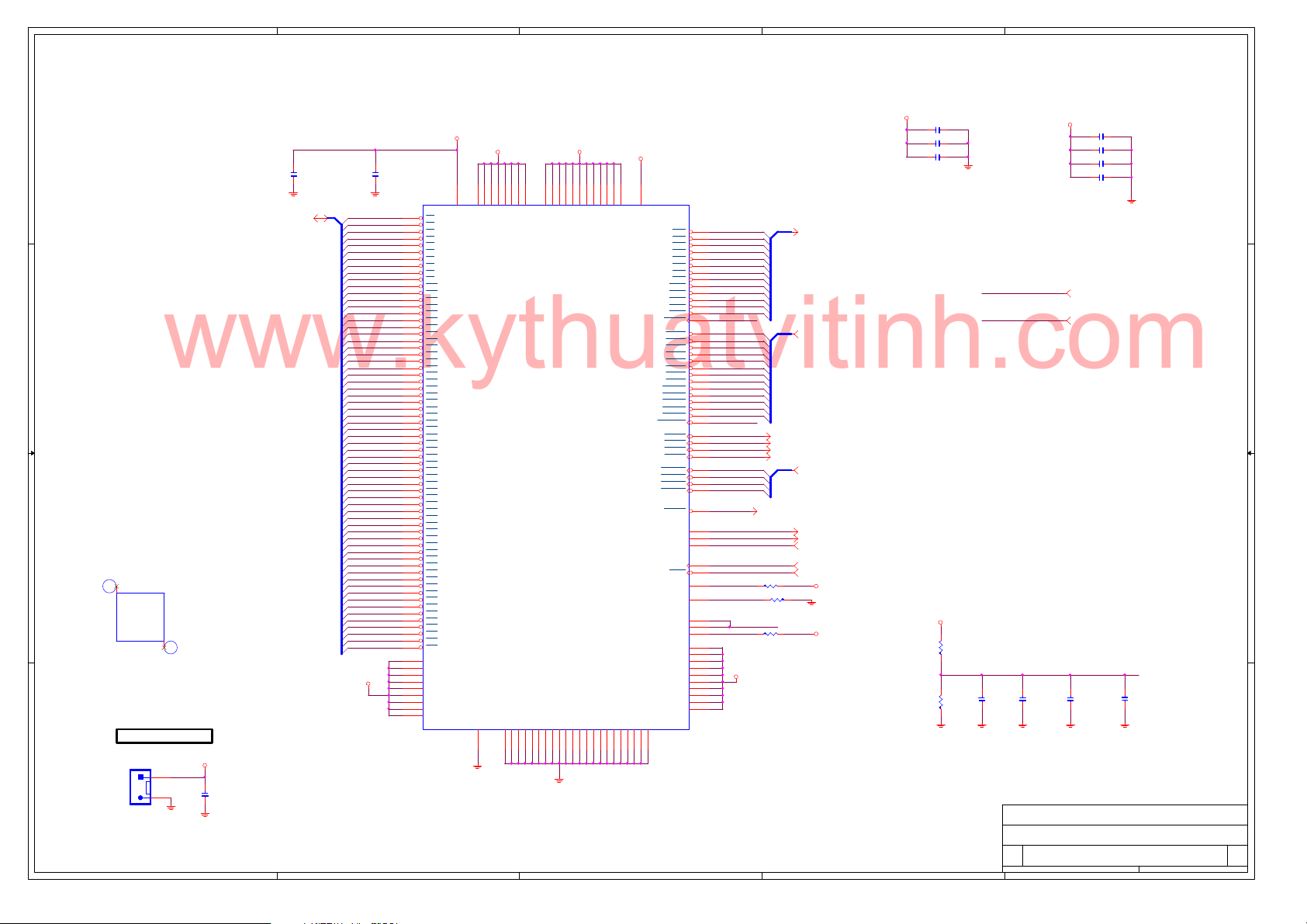

Page 4

www.kythuatvitinh.com

5

4

3

2

1

-CPURST

-SDATA[0..63]<6>

D D

C C

B B

A A

VCORE

-DIVAL<6>

-DOCLK[0:3]<6>

-AI[2:14]<6>

CLKFWDRST<6>

CONNECT<6>

PROCRDY<6>

-SDATA[0..63]

R13 330/6

R16 680/6

R18 680/6

-AI[2:14]

-CAICLK

CLKFWDRST

CONNECT

PROCRDY

R28 330/6

5

AIN0

AIN1

-SDATA0

-SDATA1

-SDATA2

-SDATA3

-SDATA4

-SDATA5

-SDATA6

-SDATA7

-SDATA8

-SDATA9

-SDATA10

-SDATA11

-SDATA12

-SDATA13

-SDATA14

-SDATA15

-SDATA16

-SDATA17

-SDATA18

-SDATA19

-SDATA20

-SDATA21

-SDATA22

-SDATA23

-SDATA24

-SDATA25

-SDATA26

-SDATA27

-SDATA28

-SDATA29

-SDATA30

-SDATA31

-SDATA32

-SDATA33

-SDATA34

-SDATA35

-SDATA36

-SDATA37

-SDATA38

-SDATA39

-SDATA40

-SDATA41

-SDATA42

-SDATA43

-SDATA44

-SDATA45

-SDATA46

-SDATA47

-SDATA48

-SDATA49

-SDATA50

-SDATA51

-SDATA52

-SDATA53

-SDATA54

-SDATA55

-SDATA56

-SDATA57

-SDATA58

-SDATA59

-SDATA60

-SDATA61

-SDATA62

-SDATA63

-CDICLK0

-CDICLK1

-CDICLK2

-CDICLK3

-DIVAL

-DOCLK0

-DOCLK1

-DOCLK2

-DOCLK3

-DOVAL

-AI2

-AI3

-AI4

-AI5

-AI6

-AI7

-AI8

-AI9

-AI10

-AI11

-AI12

-AI13

-AI14

-FILVAL

AA35

W37

W35

AA33

AE37

AC33

AC37

AA37

AC35

W33

AN33

AE35

AL31

AJ29

AL29

AG33

AJ37

AL35

AE33

AJ35

AG37

AL33

AN37

AL37

AG35

AN29

AN35

AN31

AJ33

AJ21

AL23

AN23

AJ31

Y35

U35

U33

S37

S33

Y37

S35

Q37

Q35

N37

J33

G33

G37

E37

G35

Q33

N33

L33

N35

L37

J37

A37

E35

E31

E29

A27

A25

E21

C23

C27

A23

A35

C35

C33

C31

A29

C29

E23

C25

E17

E13

E11

C15

E9

A13

C9

A9

C21

A21

E19

C19

C17

A11

A17

A15

J35

E27

E15

C37

A33

C11

SOCKET_AA

SDATA0

SDATA1

SDATA2

SDATA3

SDATA4

SDATA5

SDATA6

SDATA7

SDATA8

SDATA9

SDATA10

SDATA11

SDATA12

SDATA13

SDATA14

SDATA15

SDATA16

SDATA17

SDATA18

SDATA19

SDATA20

SDATA21

SDATA22

SDATA23

SDATA24

SDATA25

SDATA26

SDATA27

SDATA28

SDATA29

SDATA30

SDATA31

SDATA32

SDATA33

SDATA34

SDATA35

SDATA36

SDATA37

SDATA38

SDATA39

SDATA40

SDATA41

SDATA42

SDATA43

SDATA44

SDATA45

SDATA46

SDATA47

SDATA48

SDATA49

SDATA50

SDATA51

SDATA52

SDATA53

SDATA54

SDATA55

SDATA56

SDATA57

SDATA58

SDATA59

SDATA60

SDATA61

SDATA62

SDATA63

SDATAINCLK0

SDATAINCLK1

SDATAINCLK2

SDATAINCLK3

SDATAINVAL

SDATAOUTCLK0

SDATAOUTCLK1

SDATAOUTCLK2

SDATAOUTCLK3

SDTATOUTVAL

SADDIN0

SADDIN1

SADDIN2

SADDIN3

SADDIN4

SADDIN5

SADDIN6

SADDIN7

SADDIN8

SADDIN9

SADDIN10

SADDIN11

SADDIN12

SADDIN13

SADDIN14

SADDINCLK

CLKFWDRST

CONNECT

PROCRDY

SFILLVAL

0

1

2

3

SOCKETA

4

A20M

FERR

INTR

IGNNE

RESET

STPCLK

PWROK

PICCLK

PICD0/BYPASSCLK

PICD1/BYPASSCLK

COREFB-

COREFB+

CLKIN

CLKIN

RSTCLK

RSTCLK

K7CLKOUT

K7CLKOUT

ANALOG

SYSVREFMODE

VREF_SYS

PLLBYPASS

PLLBYPASSCLK

PLLBYPASSCLK

PLLMON1

PLLMON2

PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

DBRDY

DBREQ

FLUSH

TCK

TDO

TMS

TRST

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

SCHECK0

SCHECK1

SCHECK2

SCHECK3

SCHECK4

SCHECK5

SCHECK6

SCHECK7

SADDOUT0

SADDOUT1

SADDOUT2

SADDOUT3

SADDOUT4

SADDOUT5

SADDOUT6

SADDOUT7

SADDOUT8

SADDOUT9

SADDOUT10

SADDOUT11

SADDOUT12

SADDOUT13

SADDOUT14

SADDOUTCLK

Socket_A/Yellow

-A20M

AE1

FERR

AG1

-CPUINIT

AJ3

INIT

NMI

SMI

ZN

ZP

TDI

AL1

AJ1

AN3

AG3

AN5

AC1

AE3

N1

N3

N5

AG13

AG11

AN17

AL17

AN19

AL19

AL21

AN21

AJ13

AA5

W5

AC5

AE5

AJ25

AN15

AL15

AN13

AL13

AC3

S1

S5

S3

Q5

AA1

AA3

AL3

Q1

U1

U5

Q3

U3

L1

L3

L5

L7

J7

W1

W3

Y1

Y3

U37

Y33

L35

E33

E25

A31

C13

A19

J1

J3

C7

A7

E5

A5

E7

C1

C5

C3

G1

E1

A3

G5

G3

E3

INTR

-IGNNE

NMI

-CPURST

-SMI

-STPCLK

PWK

PICCLK0

-PICD0

-PICD1

-COREFB

COREFB

K7CLKOUT

-K7CLKOUT

SYSVREFMODE

VREFSYS

ZN

ZP

-PLLBYPASS

PLLBYPASSCLK

-PLLBYPASSCLK

PLLMON1

PLLMON2

-PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

-DBREQ

-FLUSH

P_TCK

P_TDI

P_TMS

-P_TRST

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

-AO2

-AO3

-AO4

-AO5

-AO6

-AO7

-AO8

-AO9

-AO10

-AO11

-AO12

-AO13

-AO14

-A20M <10>

-CPUINIT <10>

INTR <10>

-IGNNE <10>

-CPURST <26>

-SMI <10>

-STPCLK <10>

PWK <26>

PICCLK0 <9>

-PICD0 <10>

-PICD1 <10>

C1 680P/4/X/50V

C2 680P/4/X/50V

VID[4..0]

R20 1K/6/X

R22 1K/6/X

VID[4..0] <28>

-AO[2..14]

-AOCLK

CPUCLK

-CPUCLK

-CDICLK0

-CDICLK1

-CDICLK2

-CDICLK3

-CAICLK

VCORE

VCORE

-AO[2..14] <6>

-AOCLK <6>

3

VCORE

R3

60.4/6/1

R6

301/6/1

L17

10nH/6/10

L1

10nH/6/10

L38

10nH/6/10

L5

10nH/6/10

L19

10nH/6/10

FID[0..3]

SC110

10U/8/X/10V/B/X

SC113

10U/8/X/10V/B/X

R4

60.4/6/1

DIC0

C147

5P/4/N/50V

DIC1

C4

5P/4/N/50V

DIC2

C356

5P/4/N/50V

DIC3

C6

5P/4/N/50V

AIC

C148

5P/4/N/50V

FID[0..3] <28>

SC111

10U/8/X/10V/B/X

SC114

10U/8/X/10V/B/X

R31

8.2K/6/X

NMI_SB<10>

CPUCLK <9>

-CPUCLK <9>

L18

10nH/6/10

L2

10nH/6/10

L39

10nH/6/10

L6

10nH/6/10

L20

10nH/6/10

-DICLK0 <6>

-DICLK1 <6>

-DICLK2 <6>

close to cpu socket.

-DICLK3 <6>

-AICLK <6>

Put them inside socket462

SC112

10U/8/X/10V/B/X

SC115

10U/8/X/10V/B/X

VCORE

VCC3

R29

1K/6/X

MMBT2222A/SOT23/X

PWK

To CPU

Q4

C3

10P/4/X

10P/4/X

-P_TRST

P_TDI

P_TMS

P_TCK

-PLLTEST

-DBREQ

SCANINTEVAL

SCANCLK1

SCANCLK2

SCANSHIFTEN

132

2

C146

PLLBYPASSCLK

-PLLBYPASSCLK

RN3

470/8P4R

R19 470/6

R21 470/6

RN6

330/8P4R

NMI

R500

0/6/SHT/X

K7CLKOUT

-K7CLKOUT

78

56

34

12

78

56

34

12

VCORE

R5

680/6

FERR

R7 1K/6

RN1

1 2

3 4

5 6

7 8

100/8P4R

RN2

1 2

3 4

5 6

7 8

100/8P4R

COREFB

SC2

10U/8/X/10V/B/X

-COREFB

至少

10 mil.

GIGABYTE

Title

Size Document Number Rev

Custom

Date: Sheet of

SC3

10U/8/X/10V/B/X

0629 ADD APIC

-PICD0

-PICD1

PICCLK0

PLLMON1

PLLMON2

-PLLBYPASS

ZN

-CPUINIT

INTR

-FLUSH

NMI

-IGNNE

-A20M

-STPCLK

-SMI

COREFB

-COREFB

ZP

SYSVREFMODE

VCC3

R2

220/6

3

Q2

C

MMBT2222A/SOT23

B E

FERR+

2

1

VCORE

VCORE

VCORE

VCORE

VCORE

VREFSYS

R9

100/6/1

1003

R10 330/6

R11 330/6

FOR PC2001

10P/4/B/XSC18

R12 56/6

R14 56/6

R15 680/6

R17 40.2/6/1

RN4 680/8P4R

RN5 680/8P4R

R24 8.2K/6

R25 8.2K/6

R26 56/6/1

R27 330/6

SOCKETA-1

GA-7VM400AMF

1

-FERR <10>

R8

100/6/1

VCC25

12

34

56

78

12

34

56

78

4 29Wednesday, December 17, 2003

VCOREVCORE

BC1

1U/6/Y/10V

1.0

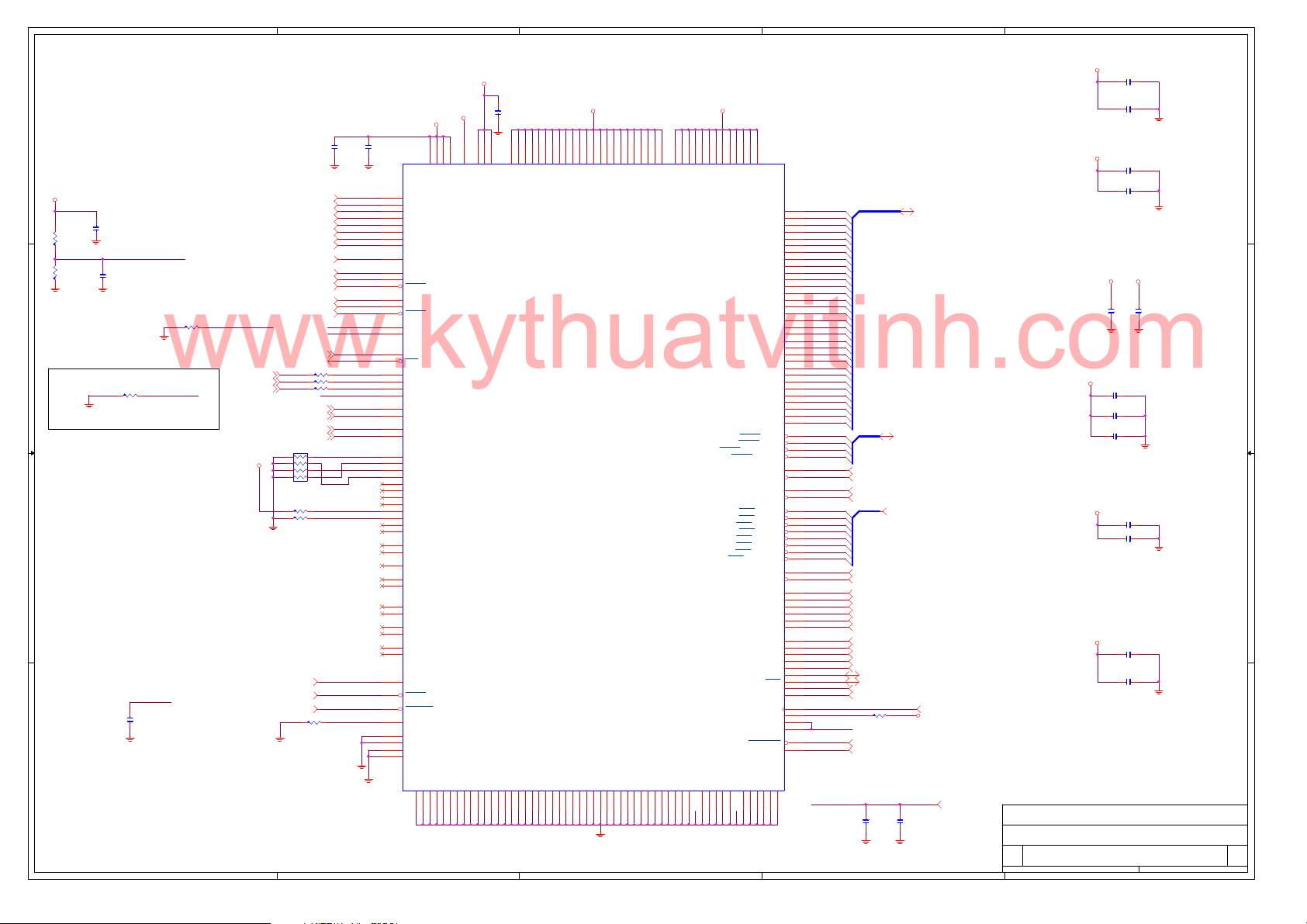

Page 5

www.kythuatvitinh.com

5

VCORE

SOCKET_AB

H12

VCC_CORE1

H16

VCC_CORE2

H20

VCC_CORE3

H24

VCC_CORE4

M8

VCC_CORE5

P30

VCC_CORE6

R8

VCC_CORE7

T30

VCC_CORE8

V8

VCC_CORE9

D D

C C

B B

A A

VCORE

PLL25V

AMD ATHLON PROCESSORS MODEL 6

(OR GREATER) THERMAL DIODE

X30

AB30

AF14

AF18

AF22

AF26

AM34

AK36

AK34

AK30

AK26

AK22

AK18

AK14

AK10

AL5

AH26

AM30

AH22

AH18

AH14

AH10

AH4

AH2

AF36

AF34

AD6

AM26

AD4

AD2

AB36

AB34

AB32

X36

X34

AM22

X32

AM18

P36

P34

P32

K36

K34

K32

AM14

D32

D28

AM10

D24

D20

D16

D12

B36

B32

AM2

B28

B24

B20

B16

B12

AC7

AJ23

Z8

Z6

Z4

Z2

V6

V4

V2

T36

T34

T32

R6

R4

R2

M4

M6

M2

H4

H2

F36

F34

F32

F28

F24

F20

F16

F12

D8

D4

D2

B8

B4

AJ5

5

VCC_CORE10

VCC_CORE11

VCC_CORE12

VCC_CORE13

VCC_CORE14

VCC_CORE15

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

VCC_CORE20

VCC_CORE21

VCC_CORE22

VCC_CORE23

VCC_CORE24

VCC_CORE25

VCC_CORE26

VCC_CORE27

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

VCC_CORE32

VCC_CORE33

VCC_CORE34

VCC_CORE35

VCC_CORE36

VCC_CORE37

VCC_CORE38

VCC_CORE39

VCC_CORE40

VCC_CORE41

VCC_CORE42

VCC_CORE43

VCC_CORE44

VCC_CORE45

VCC_CORE46

VCC_CORE47

VCC_CORE48

VCC_CORE49

VCC_CORE50

VCC_CORE51

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

VCC_CORE56

VCC_CORE57

VCC_CORE58

VCC_CORE59

VCC_CORE60

VCC_CORE61

VCC_CORE62

VCC_CORE63

VCC_CORE64

VCC_CORE65

VCC_CORE66

VCC_CORE67

VCC_CORE68

VCC_CORE69

VCC_CORE70

VCC_CORE71

VCC_CORE72

VCC_CORE73

VCC_CORE74

VCC_CORE75

VCC_CORE76

VCC_CORE77

VCC_CORE78

VCC_CORE79

VCC_CORE80

VCC_CORE81

VCC_CORE82

VCC_CORE83

VCC_CORE84

VCC_CORE85

VCC_CORE86

VCC_CORE87

VCC_CORE88

VCC_CORE89

VCC_CORE90

VCC_CORE91

VCC_CORE92

VCC_CORE93

VCC_CORE94

VCC_CORE95

VCC_CORE96

VCC_CORE97

VCC_CORE98

VCC_CORE99

VCC_CORE100

VCC_CORE101

VCC_Z

VCC_A

REV2.0

AD30

AD8

AF10

AF28

VCC_SRAM1

VCC_SRAM2

VCC_SRAM3

NC1

NC2

NC3

AA31

AC31

AE31

AG23

AF30

AF32

AF6

AF8

VCC_SRAM4

VCC_SRAM5

VCC_SRAM6

VCC_SRAM7

NC6

NC7

NC8

NC9

AG25

AG31

AG5

AJ11

AH30

AH8

AJ9

AK8

VCC_SRAM8

VCC_SRAM9

VCC_SRAM11

VCC_SRAM13

NC10

NC11

NC12

NC13

AJ15

AJ17

AJ19

AJ27

C_FS_0 <9>

C_FS_1 <9>

AL9

AM8

F30F8H10

H28

H30

H32H6H8

VCC_SRAM14

VCC_SRAM16

VCC_SRAM17

VCC_SRAM19

VCC_SRAM20

VCC_SRAM21

VCC_SRAM22

VCC_SRAM23

VCC_SRAM24

SOCKETA

POWER & GND

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

AN11

AN9

THERMDA

NC23

G11

G13

G27

G29

G31

AL11

4

K30K8AJ7

AL7

AN7

G25

G17G9N7Y7AG7

AG15

AG29G7Q7

AA7

AG9

AG17

AG27

G15

G23

AH6

H14

VSS1

KEY

AMD

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS_Z

Socket_A/Yellow

H18

H22

H26

M30

P8

R30

T8

V30

X8

Z30

AB8

AF12

AF16

AF20

AF24

AM36

AK32

AK28

AK24

AK20

AK16

AK12

AK4

AK2

AH36

AM32

AH34

AH32

AH28

AH24

AH20

AH16

AH12

AF4

AF2

AD36

AD34

AD32

AB6

AB4

AB2

Z36

Z34

Z32

X6

AM28

X4

X2

V36

V34

V32

T6

T4

T2

R36

R34

AM24

R32

P6

P4

P2

M36

M34

M32

K6

K4

K2

AM20

H36

H34

F26

F22

F18

F14

F10

F6

F4

F2

AM16

D36

D34

D30

D26

D22

D18

D14

D10

D6

B34

AM12

B30

B26

B22

B18

B14

B10

B6

B2

AM4

AK6

AM6

AE7

KEY

KEY

KEY

KEY

KEY

KEY

BP0_CUT

BP1_CUT

AN27

AL27

KEY

BP2_CUT

BP3_CUT

AN25

AL25

KEY4

KEY6

KEY8

KEY10

KEY12

KEY14

KEY16

KEY18

VCC_SRAM25

VCC_SRAM26

VCC_SRAM27

VCC_SRAM28

VCC_SRAM29

VCC_SRAM30

VCC_SRAM31

NC24

NC25

NC27

NC28

NC29

NC30

NC31

NC32

NC33

NC34

NC35

NC36

NC37

NC42

NC43

NC44

J31J5L31

N31

Q31

S31S7U31U7W31W7Y31Y5AG19

C11

3300P/X/6/X C8

4

G21

AG21

G19

THERMDC

NC45

3

BC2 10U/8/X/6.3V

BC7 10U/8/X/6.3V

BC13 10U/8/X/6.3V

BC18 10U/8/X/6.3V SC7 1U/6/Y/10V/B

BC23 10U/8/X/6.3V

3

D

G S

GPO1 THERMDA

GPO1<12>

2

- Reserve ckt for AMD temp testing -

1. 0.18u CPU:GPIO_T low (Default)

1. 0.13u CPU:GPIO_T high

(b)

THERMDA<18>

5VSB

SC105 1U/6/Y/25V/B/X

84

U2B

5

+

6

-

KA393D/SO8/X

K7_THERMAL

SHUTDOWN

CIRCCUIT

AS CLOSE AS TO THE PIN OF LM90

THERMDA

THERMDC

3

2

VCOREVCORE

BC3 10U/8/X/6.3V

BC8 10U/8/X/6.3V

BC14 10U/8/X/6.3V

BC19 10U/8/X/6.3V

BC24 10U/8/X/6.3V

R1021

1K/6/X

TEMP_A

Q112

2N7002/SOT23/X

1

5VDUAL

R1013

8.2K/6/X

PSON_IN

PSON_IN<26> PSON_OUT <26>

THERMDA

(CPU H/W

MONITOR)

FROM CPU

THERMAL DIODE

PIN

THERMDC

(a)

R1015

0/6/SHT/X

PLL25V

R949

0/6/SHT/X

VCC25

0/6/SHT/X

SPKR<12,24>

單點接地

FOR EMI

3VDUAL

THERMTRIP-

VCC

5VSB

R37 8.2K/6/X

R38 8.2K/6/X

THERMTRIP-

BC51

0.1U/4/Y/16V/X

U1

1

VDD

2

D+

SMBDATA

3

D-

4

T_CRIT_A#

LM90/MSOP8/X

SMBCLK

ALERT#

GND

R39

8.2K/6/X

8

7

6

5

7

2.2n/4/X/50V/X

BC4 0.1U/6/Y/25V

BC9 0.1U/6/Y/25V

BC15 0.1U/6/Y/25V

BC28 0.1U/6/Y/25V

BC32 10U/8/X/6.3V

PLL25V

VCC3

CPU AMD K7 2.5V ONLY

D1

R33

1N4148/S/X

R34 10/6

BC52

4.7U/8/Y/10V

R1012 0/6/X

U53 ATTP 1

1 8

SIREN# 5VSB

2 7

GND VREF

3

PSON_IN#

PSON_OUT#

BC451

0.1U/6/Y/25V/X

R1016

6.98K/6/1

RT

10K/1/0603

t

CPU

THEMISTOR

BUT ADD VREF

NO SUPPORT

R35 1K/6/X

5VSB

U2A

Z11

Z12

C10

0.1U/6/Y/25V/X

SMBCLK <9,12,13,23>

SMBDATA <9,12,13,23>

2

84

3

+

2

-

VCORE VCOREVCORE

BC12 0.1U/6/Y/25V

BC17 0.1U/6/Y/25V

BC22 0.1U/6/Y/25V

BC50 0.1U/6/Y/25V

K7_P_VG <26>

BC53

33P/4/X

6

54

TXRTXD

BC452

0.1U/6/Y/25V/X

TEMP_A

R1017 10K/6/1

BC454

0.1U/6/Y/25V

PUT INSIDE THE CPU SOCKET,

DETECT CPU TEMP

C9

0.1U/4/Y/16V/X

1

KA393D/SO8/X

TMPIN2

PSON_OUT

Title

Size Document Number Rev

Custom

Date: Sheet of

VCC

5VDUAL

R1119

0/6/SHT/X

BC453

0.1U/6/Y/25V

TMPIN2 <18>

VCC

R36

1K/6

GIGABYTE

1

BC6 0.1U/6/Y/25V

BC11 0.1U/6/Y/25V

BC16 0.1U/6/Y/25V

BC44 0.1U/6/Y/25V

(2)

R1014

8.2K/6/X

PSON_OUT

(1)

(RT H/W

MONITOR)

DISABLE PWM

3

Q5

D

2N7002/SOT23

G S

2

1

3

Q6

D

2N7002/SOT23

G S

2

1

SOCKET-2

GA-7VM400AMF

1

FS <27>

PW+ <12,24>

5 29Wednesday, December 17, 2003

1.0

Page 6

www.kythuatvitinh.com

5

VT-KM400A (S2K BUS)

4

3

2

1

VCORE

D D

C C

B B

HEATSINK

2

FANSINK/GOLD

1

FOR EMI

-SDATA[0:63]<4>

SC106

1U/6/Y/10V/B

-SDATA0

-SDATA1

-SDATA2

-SDATA3

-SDATA4

-SDATA5

-SDATA6

-SDATA8

-SDATA10

-SDATA11

-SDATA12

-SDATA13

-SDATA14

-SDATA15

-SDATA16

-SDATA17

-SDATA18

-SDATA19

-SDATA20

-SDATA21

-SDATA22

-SDATA23

-SDATA24

-SDATA25

-SDATA26

-SDATA27

-SDATA28

-SDATA29

-SDATA30

-SDATA31

-SDATA32

-SDATA33

-SDATA34

-SDATA35

-SDATA36

-SDATA37

-SDATA38

-SDATA39

-SDATA40

-SDATA41

-SDATA42

-SDATA43

-SDATA44

-SDATA45

-SDATA46

-SDATA47

-SDATA48

-SDATA49

-SDATA50

-SDATA51

-SDATA52

-SDATA53

-SDATA54

-SDATA55

-SDATA56

-SDATA57

-SDATA58

-SDATA59

-SDATA60

-SDATA61

-SDATA62

-SDATA63

VCC25

BC497

0.1U/6/Y/25V

NB HEAT SINK FAN

A A

NB_FAN

H1X2/NB_FAN/WHITE/X

+12V

C114

0.1U/6/Y/25V/X

5

4

VCC25

VCC25

G22

W21

B17

D0

D20

B20

C20

A20

C21

E19

B21

B18

E18

A17

C18

A18

D18

C17

E20

A21

D21

C22

A26

C25

C23

D24

B26

E21

A23

B23

A22

D23

A25

C26

C24

E26

F26

G25

G26

J26

H26

G24

H24

E22

E24

D25

D26

F25

F24

J25

H22

L26

M26

M25

M23

M24

K23

N22

M22

J24

K22

K25

K26

J23

N23

J22

K24

C11

D11

E11

A12

B12

C12

D12

E12

W22

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

AVDD1

F21

V21

VDD

VDD

AGND1

F10

F15

F19

F20

P21

R21

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

P23

P25

U23

U25

VCORE

J18

L18

R18

K18

P18

N18

M18

VTT

VTT

VTT

VTT

VTT

VTT

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L23

L25

B22

D22

B25

E23

E25

H23

H25

VCC25

J14

J13

J15

J17

J16

VTT

VTT

VTT

VTT

VTT

VSS

VSS

VSS

VSS

VSS

T21

B16

D16

B19

D19

U54A

M21

VTT

VDS2K

AINCLK

AOUT2

AOUT3

AOUT4

AOUT5

AOUT6

AOUT7

AOUT8

AOUT9

AOUT10

AOUT11

AOUT12

AOUT13

AOUT14

AOUTCLK

DICLK0

DICLK1

DICLK2

DICLK3

DOCLK0

DOCLK1

DOCLK2

DOCLK3

DINVAL

CFWDRST

CONNECT

PROCRDY

TESTIN1

S2KCOMP

S2KVREF0

S2KVREF1

TESTIN0

VSS2K

VSS

VSS

VSS

VSS

KM400A/A2

K21

B13

D13

F14

3

AIN2

AIN3

AIN4

AIN5

AIN6

AIN7

AIN8

AIN9

AIN10

AIN11

AIN12

AIN13

AIN14

HCLK

HCLK

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

E17

C16

A14

D17

A15

E16

B14

C15

E15

A16

D15

A13

C13

B15

N26

P22

N24

P26

N25

T22

P24

R22

T24

T23

R23

R26

R24

R25

A19

A24

G23

L24

C19

B24

F23

L22

E13

D14

C14

E14

G21

F22

E10

L21

F17

N21

F12

T26

U26

V26

T25

V25

U24

V24

V23

U22

V22

-AI2

-AI3

-AI4

-AI5

-AI6

-AI7-SDATA7

-AI8

-AI9-SDATA9

-AI10

-AI11

-AI12

-AI13

-AI14

-AICLK

-AO2

-AO3

-AO4

-AO5

-AO6

-AO7

-AO8

-AO9

-AO10

-AO11

-AO12

-AO13

-AO14

-AOCLK

-DICLK0

-DICLK1

-DICLK2

-DICLK3

-DOCLK0

-DOCLK1

-DOCLK2

-DOCLK3

-VID

R1125 1K/6

S2KCOMP

FOR KM400A

S2K_VREF

-TESTIN

R1124 1K/6

VCC25

-DICLK0 <4>

-DICLK1 <4>

-DICLK2 <4>

-DICLK3 <4>

-DIVAL <4>

R1123 49.9/6/1

-AI[2:14] <4>

-AO[2:14] <4>

-DOCLK[0:3] <4>

CLKFWDRST <4>

CONNECT <4>

PROCRDY <4>

HCLK <9>

-HCLK <9>

VCC25

VCC25

2

1U/6/Y/10V/BSC9

1U/6/Y/10V/BSC10

1U/6/Y/10V/BSC11

PLACE THESE CAPS IN

SOLDER SIDE ,CLOSE

TO NB BALL

VCORE

R1126

121/6/1

S2K_VREF is set at 50% of VCC_CORE to NB

R1127

100/6/1

-AOCLK

-AICLK

BC498

1U/6/Y/10V

Title

Size Document Number Rev

Custom

Date: Sheet of

VCORE

PLACE CAPS AROUND NB

-AOCLK <4>

-AICLK <4>

S2K_VREF

BC499

0.1U/6/Y/25V

SC116

0.1U/4/Y/16V/B

0.1U/4/Y/25VBC56

0.1U/4/Y/25VBC57

1U/6/Y/10VBC58

1U/6/Y/10V/BSC117

SC86

1U/6/Y/10V/B

GIGABYTE

KM400A (S2K BUS)

GA-7VM400AMF

1

6 29Wednesday, December 17, 2003

1.0

Page 7

www.kythuatvitinh.com

5

4

3

2

1

VT-KM400A (DDR BUS)

AE22

DDR25V

AA7V9V10

V11

V12

V13

V14

V15

V16

V17

V18

AA15

AA21

T18

U18

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AC22

AE19

AC19

AE13

Y23

AC16

AE16

Y25

AC13

VCC3

VSS

AE10

VCC3

VSS

AC10

VCC3

VSS

VCC3

VCC3

VCC3

VCC3

MAA0

AC11

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

CS0

CS1

CS2

CS3

CS4

CS5

SRASA

SCASA

SWEA

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

MVREF1

MVREF0

VSS

VSS

VSS

VSS

VSS

VSS

KM400A/A2

AC3

AE2

AC4

AE4

AC7

AE7

AB12

AC12

AB14

AB16

AB17

AB15

AC18

AE17

AC17

AB10

AC9

AF17

AB18

AB19

AC21

AD24

AB22

AC24

AB20

AF24

AD6

AC5

AC6

AB6

AB7

AD5

AB11

AD7

AB9

Y26

AD25

AD22

AF19

AE15

AF12

AB8

AF4

Y24

AD26

AF22

AD19

AF15

AE12

AC8

AD4

AA10

AA18

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

MAA14

CKE0

CKE1

CKE2

CKE3

-CS0

-CS1

-CS2

-CS3

-CS4

-CS5

-SRASA

-SCASA

-SWEA

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

-DQS0

-DQS1

-DQS2

-DQS3

-DQS4

-DQS5

-DQS6

-DQS7

1U/6/Y/10V/B

SC14

MAA[0:14] <13,14>

CKE0 <13>

CKE1 <13>

CKE2 <13>

CKE3 <13>

-CS0 <13,14>

-CS1 <13,14>

-CS2 <13,14>

-CS3 <13,14>

-CS4 <14>

-CS5 <14>

-SRASA <13,14>

-SCASA <13,14>

-SWEA <13,14>

MVREF_NB

BC513

1U/6/Y/10V

DQM[0:7] <13,14>

DDR25V VCC25

R1151

100/6/1

R1152

100/6/1

SC87

1U/6/Y/10V/B

VCC25

DDR25V

1U/6/Y/10V/B

0.1U/6/Y/25VBC64

0.1U/6/Y/25VBC66

10U/8/X/6.3V/BSC13

1U/6/Y/10V/BSC15

0.1U/4/Y/25VBC65

0.1U/6/Y/25VBC67

1U/6/Y/10V/BSC16

10U/8/X/6.3V/BSC17

CAPS SCxx PLACE

TO SOLDER SIDE

,CLOSE TO NB

BALL

SC89

SC88

1U/6/Y/10V/B

+

EC45

1000U/D/6.3V/8E

VCC25

AA13

AA22Y21

AVDD2AGND2

VSS

VSS

AE25

VSS

AC25

W23

W24

AA25

AB26

W26

W25

AA26

AA24

AB25

AB24

AF25

AE24

AB23

AC26

AE26

AF26

AD23

AE23

AD21

AF21

AC23

AF23

AE21

AB21

AC20

AF20

AF18

AD18

AD20

AE20

AE18

AD17

AF16

AC15

AC14

AE14

AD16

AD15

AD14

AF14

AF13

AD12

AD11

AF11

AD13

AB13

AE11

AD10

AF10

AE9

AE8

AD9

AD8

AE6

AE3

AE5

AA23

U54B

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

AF7

MD51

AF9

MD52

MD53

AF8

MD54

MD55

MD56

AF5

MD57

MD58

AF1

MD59

AF6

MD60

MD61

AF3

MD62

AF2

MD63

Y22

DCLKO

DCLKIN

D D

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

C C

B B

DCLKO<9>

DCLKI<9>

SR2 10/6/B

BC511

5P/4/N/50V/B/X

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DCLKO_1

DCLKI

BC512

5P/4/N/50V/X

DDR MD DAMPPING

Near DIMM 1

MD0

MD4 MDD4

MD5

MD1

RN7 22/8P4R

MD2

MD6

MD7

MD3

RN8 22/8P4R

MD15

MD14

MD10

MD11

RN9 22/8P4R

MD8

MD9

MD13 MDD13

MD12

RN10 22/8P4R

MD20

MD16

MD17

MD21

RN11 22/8P4R

MD18

MD23

MD19

MD22

RN12 22/8P4R

MD24

MD25

MD29

MD28

RN13 22/8P4R

MD27

MD30

MD26 MDD26

MD31

RN14 22/8P4R

MD34

MD38

MD35

MD39

RN15 22/8P4R

MD36

MD33 MDD33

MD32

MD37

RN16 22/8P4R

MD40

MD44

MD45

MD41

RN17 22/8P4R

MD42

MD43

MD46

MD47

RN18 22/8P4R

MD61

MD57

MD60

MD56

RN19 22/8P4R

MD48

MD53

MD49

MD52

RN20 22/8P4R

MD62

MD58

MD63

MD59

RN21 22/8P4R

MD54

MD50

MD51

MD55

RN22 22/8P4R

-DQS0

R49 22/6

-DQS1

R51 22/6

-DQS2

R52 22/6

-DQS3

R54 22/6

-DQS4

R55 22/6

-DQS5

R56 22/6

-DQS6

R57 22/6

-DQS7

R58 22/6

MDD0

1

1

2

3

4

MDD5

5

6

MDD1

7

8

MDD2

1

2

1

MDD6

3

4

MDD7

5

6

MDD3

7

8

MDD15

1

1

2

MDD14

3

4

MDD10

5

6

MDD11

7

8

MDD8

1

2

1

MDD9

3

4

5

6

MDD12

7

8

MDD20

1

1

2

MDD16

3

4

MDD17

5

6

MDD21

7

8

MDD18

1

2

1

MDD23

3

4

MDD19

5

6

MDD22

7

8

MDD24

1

1

2

MDD25

3

4

MDD29

5

6

MDD28

7

8

MDD27

7

8

MDD30

5

6

3

4

MDD31

1

2

1

MDD34

1

1

2

MDD38

3

4

MDD35

5

6

MDD39

7

8

MDD36

1

2

1

3

4

MDD32

5

6

MDD37

7

8

MDD40

1

1

2

MDD44

3

4

MDD45

5

6

MDD41

7

8

MDD42

1

2

1

MDD43

3

4

MDD46

5

6

MDD47

7

8

MDD61

1

1

2

MDD57

3

4

MDD60

5

6

MDD56

7

8

MDD48

1

2

1

MDD53

3

4

MDD49

5

6

MDD52

7

8

MDD62

1

1

2

MDD58

3

4

MDD63

5

6

MDD59

7

8

MDD54

1

2

1

MDD50

3

4

MDD51

5

6

MDD55

7

8

-DQSD0

-DQSD1

-DQSD2

-DQSD3

-DQSD4

-DQSD5

-DQSD6

-DQSD7

MDD[0:63] <13,14>

0 ~ 7

8 ~ 15

16 ~ 23

24 ~ 31

32 ~ 39

40 ~ 47

48 ~ 55

56 ~ 63

-DQSD[0:7] <13,14>

A A

COUPON2

COUPON1

5

COUPON1 COUPON/X

COUPON2 COUPON/X

21

21

VCC

Title

Size Document Number Rev

Custom

4

3

2

Date: Sheet of

GIGABYTE

KM400A (DDR bus)

GA-7VM400AMF

1

7 29Wednesday, December 17, 2003

1.0

Page 8

www.kythuatvitinh.com

5

4

3

2

1

KM400A (AGP bus, 8 bit V_Link bus)

VCC3

SUS25V

VCC25

D D

VCC25

SC96

1U/6/Y/10V/B

SR5

3K/6/1/B

SR6

1K/6/1/B

The voltage level of

LVREF_NB is 0.625V

C C

VLREF_NB

SC99

1U/6/Y/10V/B

R1134 160/6/1

R1131 360/6/1

VIARESET

VLCOMP_NB

Near N.B.

VCC3

PIN NAME

B B

FP/TVD0

FP/TVD1

FP/TVD2

FP/TVD3

A A

DESCRIPTION

INTERNAL GRAPHIC INTERRUPT

( 0: ENABLE 1:DISABLE)

GRAPHIC I/O

( 0: ENABLE 1:DISABLE)

PCI BASE ADDRESS MAPPING

( 0: NORMAL 1:SPECIFIED)

EXTERNAL/INTERNAL GRAPHIC CLOCK

( 0: INTERNAL 1:EXTERNAL)

-RESET_NB

C314

1000P/6/X/50V

5

AR<19>

AG<19>

AB<19>

-PWROK_NB<12>

-RESET_NB<26>

BC502

0.1U/6/Y/25V

VLAD0<10>

VLAD1<10>

VLAD2<10>

VLAD3<10>

VLAD4<10>

VLAD5<10>

VLAD6<10>

VLAD7<10>

UPCMD<10>

UPSTB<10>

-UPSTB<10>

DNCMD<10>

DNSTB<10>

-DNSTB<10>

GUICLK<9>

-INTA<11,15,16>

R1128 4.7/6

R1129 4.7/6

R1130 4.7/6

VGAHSYNC<19>

VGAVSYNC<19>

SPCLK2<19>

SPD2<19>

RN205

12

34

56

78

10K/8P4R

R1132 10K/6

R1133 10K/6

-SUSST<12>

R1135 1K/6

BC503

1U/6/Y/10V

U54C

VLAD0

W4

VLAD1

W5

VLAD2

AA4

VLAD3

Y1

VLAD4

AC2

VLAD5

Y2

VLAD6

AB4

VLAD7

AC1

VBE0

UPCMD

UPSTB

-UPSTB

DNCMD

DNSTB

-DNSTB

GUICLK

-INTA

VGAHSYNC

VGAVSYNC

SPCLK2

SPD2

TVD0

TVD1

TVD2

TVD3

TVD8

TVD9

BISTIN

Y3

Y4

AA1

AA2

AB3

AB1

AB2

AB5

Y5

E6

F6

A3

A2

B3

B5

B6

A6

C6

D6

D9

C9

B9

A9

E9

E8

B8

A8

C8

C7

B7

A7

B11

B10

D8

A10

A11

C5

D5

D10

E7

F7

D7

AD1

AE1

AD2

A5

B2

A1

E5

D4

4

VBE0<10>

VLCOMP_NB

VLREF_NB

VIARESET

-SUSST

C3

B4

A4

VCCRGB

PLLVDD1

PLLVDD2

VD0

VD1

VD2

VD3

VD4

VD5

VD6

VD7

VBE

UPCMD

UPSTB

UPSTB

DNCMD

DNSTB

DNSTB

LCOMPP

LVREF

XIN

INTA

AR

AG

AB

RSET

HSYNC

VSYNC

SPCLK2

SPD2

TVD00/DVP0D00

TVD01/DVP0D01

TVD02/DVP0D02

TVD03/DVP0D03

TVD04/DVP0D04

TVD05/DVP0D05

TVD06/DVP0D06

TVD07/DVP0D07

TVD08/DVP0D08

TVD09/DVP0D09

TVD10/DVP0D10

TVD11/DVP0D11

TVVS/DVP0VS

TVHS/DVP0HS

TVCLK/DVP0DCLK

TVCLKIN/DVP0DET

TVDE/DVP0DE

DISPCLKO

DISPCLKI

GPO0

GPOUT

SPCLK1

SPD1

PWROK

RESET

SUSSTAT

BISTIN

GNDDAC

GNDRGB

PLLGND1

PLLGND2

VSS

VSS

VSS

VSS

VSS

T16

U21

F11

F13

C10

C4

VCCDAC

VSS

T14

T15

VSS

AD3

VSUS25

VSS

T12

T13

BC514

1U/6/Y/10V/X

J11

J10

J12

VCC5

VSS

VSS

R16

T11

VCC5

VSS

J21

AA16

AA17

AA14

VDD

VDD

VDD

VDD

VCC5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

P15

P16

R11

R12

R13

R14

R15

VCC25

AA6Y6T9

U9

K6L6V6W6AA11

AA12

AA19

AA20F8F9

F16

F18

H21

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N13

N14

N15

N16

P11

P12

P13

P14

AA8

AA9

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

N12

VCC2

VCC2

VCC2

VCC2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

M14

M15

M16

N11

L13

L14

L15

L16

M11

M12

M13

3

VSS

B1C2R9

VCCQQ

VSS

L12

L11

VCC1

VSS

AA5

VCC1

VSS

VCC1

VDDQ

J6N6P6R6T6U6K9L9M9N9P9

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

GD0/FPD10

GD1/FPD11

GD2/FPDVICLK

GD3/FPD09

GD4/FPD08

GD5/FPD07

GD6/FPD06

GD7/FPD05

GD8/FPDVIDET

GD9/FPDVIHS

GD10/FPD01

GD11/FPD23/TVD11

GD12/FPD00

GD13/FPD22/TVD10

GD14/FPD21/TVD09

GD15/FPD20/TVD08

GD16/FPD18/TVD06

GD17/FPD17/TVD05

GD18/FPD16/TVD04

GD19/FPDE/TVDE

GD20/FPD14/TVD02

GD21/FPCLK/TVCLK

GD22/FPD13/TVD01

GD23/FPD15/TVD03

GD24/DVP1D09

GD26/DVP1D10

GD28/DVP1D07

GD29/DVP1D06

GD30/DVP1D08

GD31/DVP1D04

GCBE0/FPD03

GCBE1/SB_DA

GCBE2/FPD19/TVD07

GCBE3/DVP1D11

ADSTB0F/FPD04

ADSTB0S/FPD02

ADSTB1F/FPD12/TVD00

ADSTB1S/FPDET/TVCLKIN

SBA0/DVP1VS

SBA1/DVP1DE

SBA2/DVP1D00

SBA3/DVP1HS

SBA4/DVP1D05

SBA5/DVP1D03

SBA6/DVP1CLK

SBA7/DVP1CLK_N

SBSTBF/DVP1D01

SBSTBS/DVP1D02

GFRAME/FPHS/TVHS

GIRDY/SB_CK

GSTOP/FPDVICLK_N

GDEVSEL/FPVS/TVVS

GPAR/FPDVIVS

GGNT/DVI_DDCDA

GREQ/DVI_DDCCK

ST1/DVP1DET

DBIH/PIPE

WBF/FPCLK_N

AGPCOMP

AGPVREF0

AGPVREF1

AGP8XDET

GSERR/FPDVIDE

VSS

AA3

VSS

VSSQQ

VSS

VSS

VSS

VSS

VCC1

GD25

GD27

GTRDY

GCLK

VSS

VSS

ST0

ST2

DBIL

RBF

VSS

KM400A/A2

F2J2M2R2V2F4M4V4J9

GD0

W2

GD1

W1

GD2

V3

GD3

W3

GD4

V1

GD5

U2

GD6

U1

GD7

U3

GD8

T4

GD9

T5

GD10

R3

GD11

P2

GD12

R1

GD13

P1

GD14

P3

GD15

N3

GD16

N2

GD17

M1

GD18

M3

GD19

M5

GD20

L1

GD21

L4

GD22

L2

GD23

L3

GD24

J1

GD25

H5

GD26

J3

GD27

H4

GD28

H1

GD29

H3

GD30

H2

GD31

G4

-GBE0

T1

-GBE1

P4

-GBE2

N1

-GBE3

K3

AD_STB0

T3

-AD_STB0

T2

AD_STB1

K2

-AD_STB1

K1

SBA0

D2

SBA1

D3

SBA2

E3

SBA3

D1

SBA4

G3

SBA5

F1

SBA6

G1

SBA7

G2

SB_STB

E1

-SB_STB

E2

N5

P5

R5

U5

N4

U4

E4

F5

ST0

G5

ST1

F3

ST2

J5

DBIL

J4

DBIH_PIPE

K5

L5

K4

GCLKNB

V5

AGPCOMP

C1

M6

AGPVREF

H6

G6

R4

VSS

1U/6/Y/10V/B

AGPVREF

SC103

GD[0:31]

-GBE[0:3] <15>

AD_STB0 <15>

-AD_STB0 <15>

AD_STB1 <15>

-AD_STB1 <15>

SBA[0:7] <15>

SB_STB <15>

-SB_STB <15>

-GFRAME <15>

-GIRDY <15>

-GTRDY <15>

-GSTOP <15>

-GDEVSEL <15>

GPAR <15>

-GGNT <15>

-GREQ <15>

ST0 <15>

ST1 <15>

ST2 <15>

DBIL <15>

DBIH_PIPE <15>

-WBF <15>

-RBF <15>

R1136 60.4/6/1

-AGP8XDET <15>

-GSERR <15>

2

GD[0:31] <15>

GCLKNB <9>

VDDQ

SC104

10U/8/X/6.3V/B

AGPVREF <15>

Title

Size Document Number Rev

Custom

Date: Sheet of

VDDQ

0.1U/6/Y/25VBC501

1U/6/Y/10V/BSC93

VDDQ

0.1U/6/Y/25V/XBC504

1U/6/Y/10V/XSC95

SUS25V

VCC3

SC101

1U/6/Y/10V/B

VCC25

SC102

1U/6/Y/10V/B

10U/8/X/6.3V/BSC97

1U/6/Y/10V/BSC98

10U/8/X/6.3V/BSC100

Decoupling capacitors

VDDQ

BC71 1U/6/Y/10V

0.1U/4/Y/25VBC72

PLACE CAPS AROUND NB

VDDQ

1U/6/Y/10V/BSC41

1U/6/Y/10V/BSC44

CAPS SCxx PLACE TO SOLDER

SIDE,CLOSE TO NB BALL

GIGABYTE

KM400A (AGP bus, 8 bit V_Link bus)

GA-7VM400AMF

1

8 29Wednesday, December 17, 2003

1.0

Page 9

www.kythuatvitinh.com

5

CLOCK GENERATOR

L7 FB30/8

VCC25

BC77

PWROK<10,13,24,25,27>

BC81

1U/6/Y/10V

BC96

0.1U/4/Y/16V

VCC3

1U/6/Y/10V

R103 0/6S/X

R104 4.7K/6/X

C353

100P/4/N/50V/X

VCC25

D D

L9 FB30/8

VCC3

-PCI_STP

-CPU_STP

MODE

SEL_CPU

SEL_DDR

IREF

R100

200/6

R102

200/6/X

BC93

1U/6/Y/10V

PICCLK1

BC99

0.1U/4/Y/16V

R1138 8.2K/6

VCC3

R1139 8.2K/6

VCC3

C C

VCC3

APICCLK PICCLK0

B B

R81 8.2K/6

R82 8.2K/6

R84 8.2K/6/X

R86 8.2K/6/X

R1150 10/6

R97 47/6

R101 33/6

L8 FB30/8

VCC3_CLK

BC94

0.1U/4/Y/16V

AUDIO14

0629 ADD APIC

CLK 3.3V--->2.5V

BC95

0.1U/4/Y/16V

SMBCLK<5,12,13,23>

SMBDATA<5,12,13,23>

AUDIO14 <21>

PICCLK0 <4>

PICCLK1 <10>

BC82

0.1U/4/Y/16V

BC97

0.1U/4/Y/16V

4

VCC25_CLK_1

BC85

0.1U/4/Y/16V

BC98

0.1U/4/Y/16V

C354

100P/4/N/50V/X

IREF

-CKGRST

SMBCLK

SMBDATA

U4

50

VCC25_CPU

47

GNDCPU

40

VCC3/ VCC25_DDR

34

VCC3/ VCC25_DDR

39

GNDDDR

33

GNDDDR

51

VCC3_HCLK

5

VCC3_AGP

16

VCC3_PCI

23

VCC3_AVDD

22

VCC3_48M

55

VCC3_REF

19

GND48M

13

GNDPCI

9

GNDAGP

24

AGND

54

GNDHCLK

2

GND

56

VTTPWG/ REF1

25

IREF

26

RST /(PD)

27

SCLK

28

SDATA

HCLK_T+

HCLK_C-

CPUCLK_T+

CPUCLK_C-

AGPCLK0/ MODE

AGPCLK1/ SEL_CPU

AGPCLK2/ PCI_STOP

BUFFER_IN

FBOUT

DDR_T0/ SDRAM0

DDR_C0/ SDRAM1

DDR_T1/ SDRAM2

DDR_C1/ SDRAM3

DDR_T2/ SDRAM4

DDR_C2/ SDRAM5

DDR_T3/ SDRAM6

DDR_C3/ SDRAM7

DDR_T4/ SDRAM8

DDR_C4/ SDRAM9

DDR_T5/ SDRAM10

DDR_C5/ SDRAM11

PCICLK_F/ FS1

PCICLK_0/SEL_SD_DDR

PCICLK_1/MULT_SEL0

PCICLK_2

PCICLK_3

PCICLK_4

PCICLK_5

REF0/ FS0

24_48MHZ/ FS2

48MHZ/ FS3

ICS950913CF/ SSOP56

3

R_HCLK

48

-R_HCLK

49

R_CPUCLK

53

-R_CPUCLK

52

MODE

6

SEL_CPU

7

-PCI_STP

8

DCLKO

45

DCLKIN

46

CKOUT2

44

-CKOUT2

43

CKOUT5

42

-CKOUT5

41

CKOUT1

38

-CKOUT1

37

CKOUT4

36

-CKOUT4

35

CKOUT3

32

-CKOUT3

31

CKOUT0

30

-CKOUT0

29

FS1

10

SEL_DDR

11

MULT_SEL

12

R_PCICLK0

14

R_PCICLK1APICCLK

15

R_PCICLK2

17

-CPU_STP

18

FS0

1

FS2

21

FS3

20

U4_X1

3

X1

4

X2

U4_X2

X1

14.31818MHZ

BC90

10P/4/N/50V

12

R1137 15/6

CKOUT2 <13>

-CKOUT2 <13>

CKOUT5 <13>

-CKOUT5 <13>

CKOUT1 <13>

-CKOUT1 <13>

CKOUT4 <13>

-CKOUT4 <13>

CKOUT3 <13>

-CKOUT3 <13>

CKOUT0 <13>

-CKOUT0 <13>

RN23

33/8P4R

BC91

10P/4/N/50V

R75 33/6

R76 33/6

R73 10/6

R74 10/6

R77 22/6

R78 22/6

R79 22/6

R83 22/6

R85 22/6

R1177 33/6

7

8

5

6

3

4

1

2

1

R88 22/6

R89 22/6

R91 22/6

R93 22/6

DCLKI

HCLK

-HCLK

CPUCLK

-CPUCLK

GCLKNB

VCLK

AGPCLK

PCICLK_F

PCICLKL

1394CLK

PCICLK0

PCICLK1

PCICLK2

LPC33

DCLKO <7>

DCLKI <7>

SIO_OSC

GUICLK

LPC24

USBCLK

2

HCLK <6>

-HCLK <6>

CPUCLK <4>

-CPUCLK <4>

GCLKNB <8>

VCLK <10>

AGPCLK <15>

PCICLK_F <10>

PCICLKL <23>

1394CLK <29>

PCICLK0 <16>

PCICLK1 <16>

PCICLK2 <16>

LPC33 <18>

SIO_OSC <12>

GUICLK <8>

LPC24 <18>

USBCLK <11>

CPUCLK

-CPUCLK

HCLK

-HCLK

GCLKNB

AGPCLK

VCLK

PCICLK_F

PCICLK0

PCICLK1

PCICLK2

LPC33

DCLKO

DCLKIN

SIO_OSC

USBCLK

LPC24

PCICLKL

FS1

0629 ADD APIC

1394CLK

CKOUT2

-CKOUT2

CKOUT5

-CKOUT5

CKOUT1

-CKOUT1

CKOUT4

-CKOUT4

-CKOUT0

CKOUT0

-CKOUT3

CKOUT3

1

C13 10P/4/N/50V/X

C14 10P/4/N/50V/X

C15 22P/4/N/50V

C16 22P/4/N/50V

C17 10P/4/N/50V

C18 10P/4/N/50V

C19 10P/4/N/50V/X

C20 10P/4/50V/X

7

8

5

6

3

4

1

2

CN1 10P/8P4C/X

C22 10P/4/X

C23 10P/4

C24 10P/4/X

C25 10P/4/X

C26 10P/4/X

C27 10P/4/X

C28 10P/4/X

C351 10P/4/X

1

3

5

7

1

3

5

7

7

5

3

1

2

CN2

4

15P/8P4C/X

6

8

2

CN3

4

15P/8P4C/X

6

8

8

CN4

6

15P/8P4C/X

4

2

VCC3

RN28

1

2

1

3

4

5

6

7

8

1K/8P4R

FS2

FS3

FS1

KM400A/CD STRAPPING FSB100/133/166/200MHZ

A A

100MHZ

133MHZ

166MHZ 1

200MHZ

RN29

1

1

3

5

7

1K/8P4R

CPU/CLK GEN.

FS0

FS1

1

0

1

1

0

0

2

4

6

8

8235CD/CE

SDA2

0

0

1

1

5

FS_2

FS_1

FS_0FS0

8237 CD

SDA0 PDA2

0

0

0

1 1

1

11

1

0

FS_1 <12>

PDA0

C_FS_1 C_FS_0 FSB FREQ

0

00

CPU CLOCK

SW1

1

100MHZ

ON OFF

AUTO

AMD CPU FSB SENSE TABLE

1

1

0

0

0

1

1

0

RESERVE

133MHZ

166MHZ

200MHZ

4

FS100M

ON

SW1

1 2

DIP-SW_ESD101E/10N/1P/ON

Default ON

CLK H/W TRAP FREQ TABLE

H/W AUTO TRAP (100/133/166/200MHZ)

CPU AGP PCI FS3 FS2 FS1 FS0

100.00

133.33

166.66

200.00

66.66 33.33

66.66

66.66

66.66

33.33

33.33

33.33

0

0

0 0

0

3

FS100M

1

1

1

1

3

1 0

1 1

0 0

D67

1

2

BAT54C/SOT23

1

3VDUAL

R1212

100K/6

U64

1

2

NC7SZ125/SOT23

SDA0 => CPU Clock Frequency

VCC3

0 - 100/200MHz (Default)

1 - 133/166MHz

5

43

R1214 1K/6

3VDUAL 3VDUAL

R1213

R961

1K/6

8.2K/6

Q119

IDEDA0 <12>

C_FS_0 <5>

2

FS100M

Title

Size Document Number Rev

Custom

Date: Sheet of

2N7002/SOT23

SOT23

132

CLOCK GENERATOR

R960

100K/6

U63

1

2

NC7SZ125/SOT23

GIGABYTE

GA-7VM400AMF

1

5

FS_1FS_0

43

C_FS_1 <5>

9 29Wednesday, December 17, 2003

VCC3VCC3

1.0

Page 10

www.kythuatvitinh.com

5

SB VT8237(Vlink, CPU, LPC,

LAN, LAN EEPROM, I2C BUS)

VLAD[7..0]<8>

D D

R1121

0/6/X

VCC25

VCC3

3VDUAL

R1122

0/6/X

R119

8.2K/6

BC459

1U/6/Y/10V

VPAR

R1198 8.2K/6

AGPBZ

R1185 1K/6

GPIO22

R1186 1K/6

-THERM

GPIO23

R1187 1K/6

R1188 1K/6

GPIO22

GPIO23

-THERM<12>

C C

B B

VLAD[7..0]

DNCMD<8>

R1102 360/6/1

-LFRAME<18>

PWROK<9,13,24,25,27>

C34

10P/6/N/50V

UPCMD<8>

UPSTB<8>

-UPSTB<8>

DNSTB<8>

-DNSTB<8>

TP23

TP24

-LDRQ<18>

TP21

VLAD0

VLAD1

VLAD2

VLAD3

VLAD4

VLAD5

VLAD6

VLAD7

VBE0

VBE0<8>

UPCMD

DNCMD

UPSTB

-UPSTB

DNSTB

-DNSTB

VPAR

VLREF_SB

VLCOMP_SB

VCLK

VCLK<9>

VIOUT

VIIN

LAD0

LAD0<18>

LAD1

LAD1<18>

LAD2

LAD2<18>

LAD3

LAD3<18>

-LFRAME

-LDRQ

LREQ1

-RSMRST

RTCVDD

34

12

Z18

PWROK

Z19

X2

32.768KHz

C35

10P/6/N/50V

4

N21

N22

N23

N24

N25

N26

P22

L21

K21

VD0

VD1

VD2

VD3

VD4

VD5

VD6

VD7

VD8

VD9

VD10

VD11

VD12

VD13

VD14

VD15

VBE

UPCMD

DNCMD

UPSTB

UPSTB

DNSTB

DNSTB

VPAR

VLREF

VCOMPP

VCLK

VIOUT

VIIN

LAD0

LAD1

LAD2

LAD3

LFRM

LREQ0

LREQ1

PWRGD

RSMRST

VBAT

RTCX1

RTCX2

L23

VCCVK

VCCVK

GND

P11

VCCVK

GND

P12

P13

H25

G26

K26

J23

F26

G25

K22

K24

E24

G23

L26

L25

E26

E25

L24

M26

G24

K23

K25

J26

J24

H26

H24

F24

H22

J22

L22

F23

G22

AD8

AF7

AE7

AD7

AF6

AE6

AE8

AC5

AD4

AF4

AE4

AF3

P23

VCCVK

VCCVK

VCCVK

VCCVK

VCCVK

VCCVK

VCCVK

VCCVK

8235/CE(NC)

8235/CE(NC) 8235/CE(NC)

GND

GND

GND

GND

GND

GND

GND

GND

P14

P15

P16

R11

R14

R13

R12

P24

VCCVK

GND

R15

P25

VCCVK

GND

R16

P26

VCCVK

GND

R21

M21

VCCVK

GND

T11

M22

VCCVK

GND

T12

M23

VCCVK

GND

T13

M24

VCCVK

GND

T14

M25

VCCVK

GND

T15

L19

VCCVK

GND

T16

M19

VCCVK

GND

W22

N19

VCCVK

GND

W25

P19AA21

VCCVKGND

AB19

GND

AB22

GND

AB25

GND

GND

AC18

GND

AE17

3

D12

E12

MIISUS25

MIISUS25

GND

GND

AE19

AE22

AE25

GND

GND

AA9

3VDUALVCC25 SUS_25V

D9

MIIVCC

MIIVCC

MIIVCC

APICD1/APICACK

GND

GND

GND

T21

AA10

AB18

E11E9E10

MCRS

MCOL

MIIVCC

MTXENA

MTXD0

MTXD1

MTXD2

MTXD3

MTXCLK

MRXER

MRXCLK

MRXDV

MRXD0

MRXD1

MRXD2

MRXD3

MDCK

MDIO

PHYRST

EECS

EEDO

EEDI

EECK

RAMVCC

RAMGND

FERR

A20M

IGNNE

STPCLK

DPSLP

VGATE

VIDSEL

VRDSLP

AGPBZ/GPI6

PCICLK

APICCLK

APICD0/APICCS

PLLVCC

PLLGND

GND

K19

INTR

INIT

NMI

SMI

SLP

GHI

U6C

A11

B11

C11

A10

B10

B9

A9

C10

D10

C9

D8

C8

B8

A8

C7

A7

B7

D7

D11

B12

A12

C12

E7

E6

U24

U26

T24

R26

T25

T26

U25

R24

V26

R22

P21

AC9

AC8

AB9

AD10

R23

U23

R25

T23

T22

U22

VT8237/CD/A2

MCRS

MCOL

TXEN

MTXD0

MTXD1

MTXD2

MTXD3

MTXCLK

MRXER

MRXCLK

MRXDV

MRXD0

MRXD1

MRXD2

MRXD3

MDC

MDIO

-PHYRST

SEECS

SEEDO

SEEDI

SEECLK

BC388

0.1U/6/Y/25V

-FERR

-A20M

-IGNNE

-CPUINIT

INTR

NMI

-SMI

-STPCLK

-SLP

GPIO22

GPIO23

GPIO8

GPIO28

GPIO29

AGPBZ

FOR SATA

PCICLK_F

PICCLK1

-PICD0

-PICD1

R1101 8.2K/6/X

SEEDI <12>

VCC25

-FERR <4>

-A20M <4>

-IGNNE <4>

-CPUINIT <4>

INTR <4>

NMI_SB <4>

-SMI <4>

-STPCLK <4>

R1103 1K/6

GPIO22 <18>

GPIO8 <12,19>

GPIO29 <27>

D23

1N4148/S

PCICLK_F <9>

-PICD0 <4>

VDDPLL

-PICD1 <4>

BC460

1U/6/Y/25V

2

TP6

TP7

TP8

TP9

TP10

TP11

TP22

TP12

8237/CD

TP13

TP14

ID SETTING

ID SETTING/BIOS WP

HDLED- <17,24>

VCORE GPIO

VCC3

R98

1K/6/X

PICCLK1 <9>

R937

0/SHT/X

VCC3

VCC25

Decoupling capacitors

VCC3

SC81 1U/6/Y/10V/B

BC455 0.1U/6/Y/25V

BC456 0.1U/6/Y/25V

SC107 1U/6/Y/10V/B

3VDUAL

SC108 1U/6/Y/10V/B

CLOSE VT8235 SOLDER

Internal MAC P.U

MCRS

MTXCLK

MCOL

MRXDV

MRXD3

MRXD0

MRXER

MRXD2

MDIO

MRXCLK

MRXD1

R1215

GPO27<12,27>

GPO27

Case Open Circuits

R802

12

0/6/X

R803

RTCVDD

1M/6

C33

0.1U/6/Y/25V/X

2 1

12

2

1

3

1

5

7

1

1

3

1

7

5

5

1

1

7

3

RTCVDD

CI

H1X2/X

VCC25

1K/6

12

R99

1M/6

INTRUDER

SDG

132

1

BC117 1U/6/Y/10V

BC118 1U/6/Y/10V

BC119 0.1U/6/Y/25V

BC457 0.1U/6/Y/25V

BC458 0.1U/6/Y/25V

SC19 1U/6/Y/10V/B

3VDUAL

4

RN33

6

1K/8P4R/X

8

2

4

RN34

2

1K/8P4R/X

8

6

6

RN35

2

1K/8P4R/X

8

4

INTRUDER <12>

Q86

2N7002/SOT23

CI

JU1x2/B/[1-2]CLOSE/X

請遠離

S/B 2MM

VCC3

GPIO28

GPIO29

R812 8.2K/6

R813 8.2K/6

GIGABYTE

VT8237CD/A2(Vlink, CPU, LPC, LAN, I2C)

GA-7VM400AMF

10 29Wednesday, December 17, 2003

1

D37

2

1

BAT54C/SOT23

RTCVDD

3

CLR_CMOS

JP1X2/H(1-2Pin)

123

BC461

0.1U/6/Y/25V

RTCVDD

C177

1U/6/Y/10V

BC519

1U/6/Y/10V

3

VCC25

R1104

A A

3K/6/1 0.1U/6/Y/25V/X

R1106

1K/6/1

C36

C37

1U/6/Y/10V

5

VLREF_SB

SC109

1U/6/Y/10V/B

3VDUAL

VBAT_2

BAT

BAT

R805 1K/6

R1105 1K/6

BATTERY

CR2032

+

CR2032

4

CLR_CMOS_S1

JU1x2/R/[2-3]/X

CLR_CMOS 1-2

SHORT

OPEN

CLEAR CMOS

NORMAL

Title

Size Document Number Rev

Custom

2

Date: Sheet of

1.0

Page 11

www.kythuatvitinh.com

5

4

3

2

1

SB VT8237 (PCI, USB BUS, KB/MS)

VCC3

USBGND

USBGND

E17

E19

KBCK/KA20G

KBDT/KBRC

MSDT/IRQ12

USBGND

USBGND

USBGND

E21

H13

U6A

USBVDD

USBVDD

USBVDD

USBVDD

USBVDD

USBVDD

USBVDD

USBVDD

USBVDD

USBVDD

USBVDD

USBVDD

USBSUS25

PLLVDDA

PLLVDDA

PLLGNDA

PLLGNDA

USBP0+

USBP0-

USBP1+

USBP1-

USBP2+

USBP2-

USBP3+

USBP3-

USBP4+

USBP4-

USBP5+

USBP5-

USBP6+

USBP6-

USBP7+

USBP7-

USBOC0

USBOC1

USBOC2

USBOC3

USBOC4

USBOC5

USBOC6

USBOC7

USBCLK

USB REXT

UDPWR

UDPWREN

MSCK/IRQ1

USBGND

USBGND

USBGND

H15

H16

H14

USBGND

H18

H17

USBGND

A22

B22

C22

D22

E22

F22

J13

J14

J15

J16

J17

J18

C24

A23

B23

D23

C23

E20

D20

A20

B20

E18

D18

A18

B18

D16

E16

A16

B16

D14

E14

A14

B14

C26

D24

B26

C25

B24

A24

A26

A25

E23

B25

D26

D25

W3

V1

W1

W2

VT8237/CD/A2

D D

C C

-PCIRST<18,23,26>

C40

22P/6/N/50V/X

OVDDR26V

OVDDR27V

CLR_PWD

PWRLED

B B

AD[0:31]

AD[0:31]<16,23,29>

-C_BE0<16,23,29>

-C_BE1<16,23,29>

-C_BE2<16,23,29>

-C_BE3<16,23,29>

-FRAME<16,23,29>

-DEVSEL<16,23,29>

-IRDY<16,23,29>

-TRDY<16,23,29>

-STOP<16,23,29>

OVDDR26V<12,25>

OVDDR27V<12,25>

AD0

G2

AD0

AD1

J4

AD1

AD2

J3

AD2

AD3

H3

AD3

AD4

F1

AD4

AD5

G1

AD5

AD6

H4

AD6

AD7

F2

AD7

AD8

E1

AD8

AD9

G3

AD9

AD10

E3

AD10

AD11

D1

AD11

AD12

G4

AD12

AD13

D2

AD13

AD14

D3

AD14

AD15

F3

AD15

AD16

K3

AD16

AD17

L3

AD17

AD18

K2

AD18

AD19

K1

AD19

AD20

M4

AD20

AD21

L2

AD21

AD22

N4

AD22

AD23

L1

AD23

AD24

M2

AD24

AD25

M1

AD25

AD26

P4

AD26

AD27

N3

AD27

AD28

N2

AD28

AD29

N1

AD29

AD30

P1

AD30

AD31

P2

PAR

-PERR

AD31

E2

CBE0

C1

CBE1

L4

CBE2

M3

CBE3

J1

FRAME

H2

DEVSEL

J2

IRDY

H1

TRDY

K4

STOP

C2

SERR

F4

PAR

C3

PERR

R1

PCIRST

A4

INTA

B4

INTB

B5

INTC

C4

INTD

D4

INTE

E4

INTF

A3

INTG

B3

INTH

A5

REQ0

B6

REQ1

C5

REQ2

D5

REQ3

P3

REQ4

R3

REQ5

A6

GNT0

D6

GNT1

C6

GNT2

E5

GNT3

R4

GNT4

R2

GNT5

-C_BE0

-C_BE1

-C_BE2

-C_BE3

-FRAME

-DEVSEL

-IRDY

-TRDY

-STOP

-SERR

-SERR<16,23,29>

PAR<16,23,29>

-PERR<16,23,29>

-PCIRST

-INTA

-INTA<8,15,16>

-INTB

-INTB<15,16,29>

-INTC

-INTC<16,23>

-INTD

-INTD<16>

OVDDR26V

OVDDR27V

GPI12

GPI12<12>

GPO13

GPO13<12,24>

-REQ0

-REQ0<16>

-REQ1

-REQ1<16>

-REQ2

-REQ2<16>

-REQ3

-REQ3<16>

-REQ4

-REQ4<16,29>

-REQ5 KBDT

-REQ5<16,23>

-GNT0

-GNT0<16>

-GNT1

-GNT1<16>

-GNT2

-GNT2<16>

-GNT3

-GNT3<16>

-GNT4

-GNT4<16,29>

-GNT5

-GNT5<16,23>

GPIO12

GPIO13

GPIO14

GPIO15

GND

GND

A1A2B1

H9

H10

H11

VCC33

VCC33

8235/CE CHANGED

GND

GND

GND

GND

GND

GND

E8

F25

H23

J21

J25B2A17

H12J8K8L8M8N8P8R8R19

VCC33

VCC33

VCC33

VCC33

VCC33

VCC33

USBGND

USBGND

A15

A13

USBGND

USBGND

A19

A21

VCC33

USBGND

USBGND

B13

VCC33

GND

VCC33

USBGND

B15

B17

T8

T19

VCC33

VCC33

USBGND

USBGND

B19

B21

U19V8V19

U8

VCC33

VCC33

USBGND

USBGND

C13

C14

VCC33

VCC33

USBGND

USBGND

C15

C16

V21W9W10

VCC33

VCC33

USBGND

USBGND

C17

W11

W17

W18

W19

W21

VCC33

VCC33

VCC33

VCC33

VCC33

VCC33

VCC33

8235/CE(NC)

USBGND

USBGND

USBGND

USBGND

USBGND

USBGND

USBGND

C18

C19

C20

C21

D13

D15

D17

Y21

W8

VCC33

USBGND

D19

D21

VCC33

USBGND

USBGND

E13

E15

SUS_25V

USBDT0+

USBDT0USBDT1+

USBDT1USBDT2+

USBDT2USBDT3+

USBDT3USBDT4+

USBDT4USBDT5+

USBDT5USBDT6+

USBDT6USBDT7+

USBDT7-

USBCLK

GPI9

GPO9

KBCK

MSCK

MSDT

1U/6/Y/25V/B

Z20

-USBOC

SC82

3VDUAL

R1107

0/SHT/X

BC462

1U/6/Y/25V

-USBOC <17,23>

USBCLK <9>

R730 6.04K/6/1

GPI9 <12>

GPO9 <12>

KBCK <20>

KBDT <20>

MSCK <20>

MSDT <20>

3VDUALSUS_25V

D29

1N4001/S

SC62

220/6/B

CLOSE TO SB

VCC25

BC463

1U/6/Y/25V

For USB Driving

8235/CE (N/A)

USBDT0USBDT0+

USBDT1USBDT1+

USBDT2+

USBDT2USBDT3USBDT3+

USBDT4+

USBDT4USBDT5USBDT5+

USBDT6+

USBDT6USBDT7USBDT7+

RN38

15K/8P4R

1 2

3 4

5 6

7 8

RN40

15K/8P4R

1 2

3 4

5 6

7 8

RN173

15K/8P4R

1 2

3 4

5 6

7 8

RN193

15K/8P4R

1 2

3 4

5 6

7 8

USBDT0- <23>

USBDT0+ <23>

USBDT1- <23>

USBDT1+ <23>

USBDT2+ <17>

USBDT2- <17>

USBDT3- <17>

USBDT3+ <17>

USBDT4+ <17>

USBDT4- <17>

USBDT5- <17>

USBDT5+ <17>

USBDT6+ <17>

USBDT6- <17>

USBDT7- <17>

USBDT7+ <17>

IF USB UDPWR/UDPWREN DON'T USE,UDPWR MUST PULL-DOWN

VCC3 VCC3

BC466 1U/6/Y/10V

BC468 1U/6/Y/10V/X BC469 0.1U/6/Y/25V

BC465 0.1U/6/Y/25VBC464 1U/6/Y/10V

BC467 0.1U/6/Y/25V

BC470 0.1U/6/Y/25V/X

-IRDY

A A

15P/6/N/50V/X

C192

Title

VT8237CD/A2 (PCI, USB BUS, KB/MS)

Size Document Number Rev

Custom

5

4

3

2

Date: Sheet of

GIGABYTE

GA-7VM400AMF

1

11 29Wednesday, December 17, 2003

1.0

Page 12

www.kythuatvitinh.com

5

SB VT8237 (SATA,IDE, AC97, POWER MANAGEMENT, PGIO)

J9

J10

J11

K9L9J12

L18

AA22

AA26

AA25

AB26

AC26

AC23

AD25

AD26

AC24

AC25

AB24

AB23

AA24

AA23

W26

W23

W24

AD24

AC20

AB20

AC21

AE18

AF18

AD18

AD19

AF19

AE20

AF20

AD20

AE21

AF21

AD21

AD22

AF22

AD17

AD23

AF23

AE23

AF17

AF25

AF26

AF24

AC22

AE24

AE26

AC19

AB21

AB13

AC13

AF13

AE13

AB15

AC15

AF15

AE15

W12

W13

W14

W15

W16

AC17

AC11

AB17

AB11

R791

8.2K/6

Y24

Y26

Y23

V24

Y25

Y22

V22

V23

V25

U6B

PDD0