FUJITSU SEMICONDUCTOR

DATA SHEET

DS07-16503-4E

32-bit Microcontroller

CMOS

FR60 MB91350A Series

MB91F355A/F353A/F356B/F357B/355A/354A/

MB91353A/352A/351A/V350A

■ DESCRIPTION

The FR family* is a series of standard single-chip microcontrollers that feature a variety of built-in I/O resources

and bus control functions, and that employ a high-performance 32-bit RISC CPU for embedded control applications

that demand powerful and fast CPU processing capabilities.

This product is one of the FR60 family based on the FR30/40 family CPU with enhanced bus access. The FR60

family is a line of single-chip oriented microcontrollers that incorporate a wealth of peripheral resources.

The FR60 family is optimized for embedded control applications that require high CPU processing power, such

as DVD players, navigation equipment, high performance fax machines, and printer controllers.

* : FR, the abbreviation of FUJITSU RISC controller, is a line of products of FUJITSU Limited.

■ FEATURES

1. FR CPU

• 32-bit RISC, load/store architecture with a five-stage pipeline

• Maximum operating frequency : 50 MHz (using the PLL at an oscillation frequency of 12.5 MHz)

• 16-bit fixed length instructions (basic instructions), 1 instruction per cycle

• Instruction set optimized for embedded applications : Memory-to-memory transfer, bit manipulation, barrel shift

etc.

• Instructions adapted for high-level languages : Function entry/exit instructions, multiple-register load/store

instructions

• Register interlock functions : Facilitate coding in assemblers

(Continued)

Be sure to refer to the “Check Sheet” for the latest cautions on development.

“Check Sheet” is seen at the following support page

URL : http://www.fujitsu.com/global/services/microelectronics/product/micom/support/index.html

“Check Sheet” lists the minimal requirement items to be checked to prevent problems beforehand in system

development.

Copyright©2003-2007 FUJITSU LIMITED All rights reserved

MB91350A Series

• On-chip multiplier supported at the instruction level.

Signed 32-bit multiplication : 5 cycles

Signed 16-bit multiplication : 3 cycles

• Interrupt (PC, PS save) : 6 cycles, 16 priority levels

• Harvard architecture allowing program access and data access to be executed simultaneously

• Instructions compatible with the FR family

2. Bus interface

• Maximum operating frequency : 25 MHz

• 24-bit address full output (16 Mbyte address space) capability

(21-bit address full output (2 Mbyte address space) capability : MB91F353A/353A/352A/351A)

• 8,16-bit data output

• Built-in prefetch buffer

• Unused data and address pins can be used as general I/O ports.

• Able to output chip-select for 4 completely independent areas that can be configured in units of 64 Kbytes

• Support for various memory interfaces :

SRAM, ROM/Flash

page mode Flash ROM, page mode ROM interface

• Basic bus cycle : 2 cycles

• Programmable automatic wait cycle generator capable of inserting wait cycles for each area

• RDY input for external wait cycles

• DMA support of fly-by transfer capable of wait control for independent I/O

(The MB91F353A/353A/352A/351A does not support fly-by transfer.)

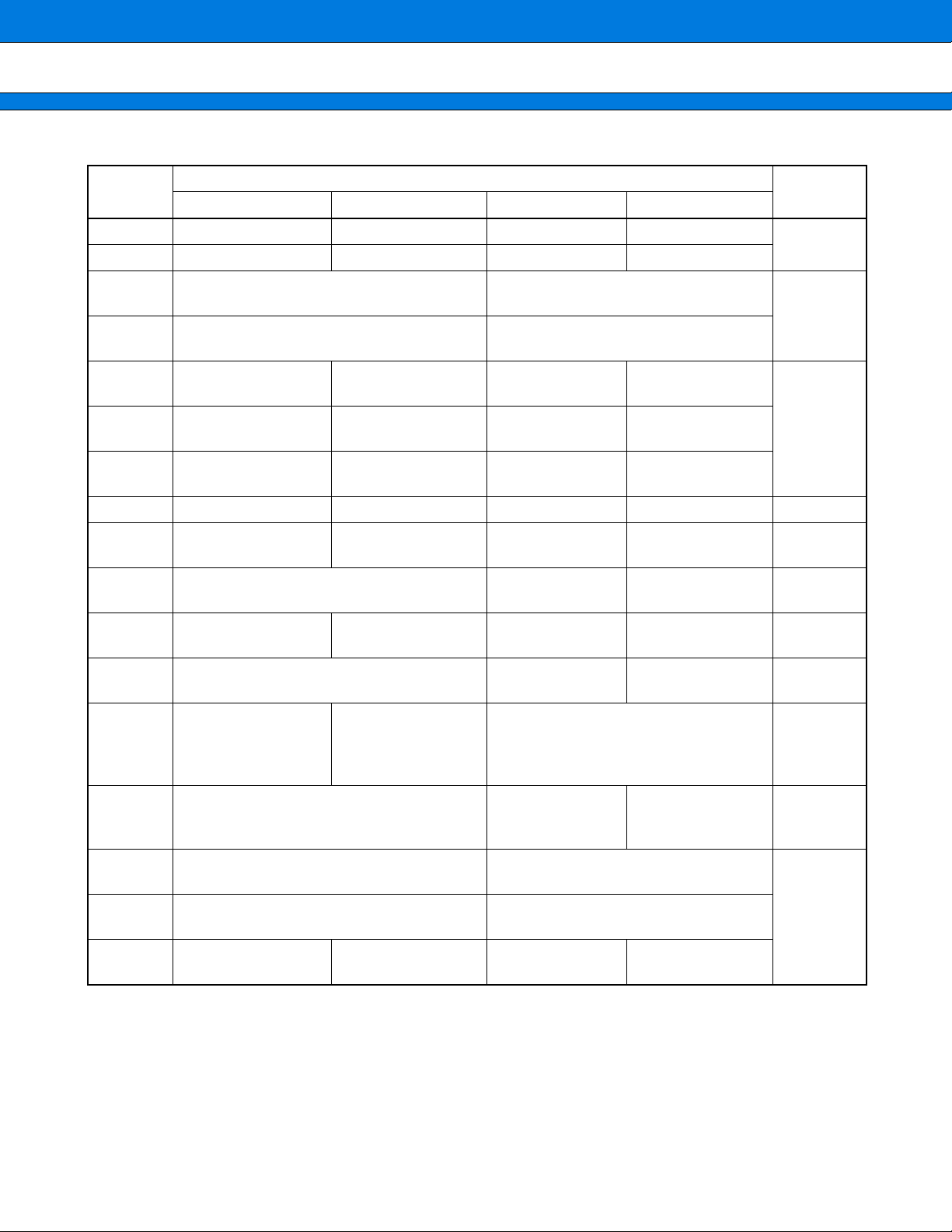

3. Built-in memory

MB91F353A

D-bus memory MB91V350A

ROM No 512 Kbytes 256 Kbytes 512 Kbytes 384 Kbytes 384 Kbytes

RAM (Stack) 16 Kbytes 16 Kbytes 16 Kbytes 16 Kbytes 8 Kbytes 16 Kbytes

RAM (Execute instruction) 16 Kbytes 8 Kbytes 8 Kbytes 8 Kbytes 8 Kbytes 8 Kbytes

MB91F355A

MB91F357B

MB91F356B

MB91353A

MB91355A

MB91352A

MB91354A

MB91351A

4. DMAC (DMA Controller)

• Capable of simultaneous operation of up to 5 channels (external → external : 3 channels)

• 3 transfer sources (external pin, internal peripheral or software) :

Activation sources are software-selectable (transfer can be activated by UART0/1/2).

• Addressing using 32-bit full addressing mode (increment, decrement, fixed)

• Transfer modes (demand transfer, burst transfer, step transfer, block transfer)

• Fly-by transfer support (between external I/O and memory)

• Selectable transfer data size : 8, 16, or 32-bit

• Multi-byte transfer capability (selected by software)

• DMAC descriptor in IO areas (200

(The MB91F353A/353A/352A/351A does not have an external interface.)

External pin transfer is not supported. Demand transfer and fly-by transfer cannot be used.

H to 240H, 1000H to 1024H)

5. Bit search module (for REALOS)

• Search a single word starting from the MSB for the position of the first bit changed from 1 to 0.

(Continued)

2

MB91350A Series

6. Various timers

• 4 channels of 16-bit reload timer (including 1 channel for REALOS) :

Internal clock frequency divider selectable from 2/8/32 (division by 64/128 selectable only for ch.3)

• 16-bit free-run timer : 1 channel

Output compare : 8 channels (MB91F353A/353A/352A/351A : 2 channels)

Input capture : 4 channels

• 16-bit PPG timer : 6 channels (MB91F353A/353A/352A/351A : 3 channels)

7. UART

• UART full duplex double buffer : 5 channels (MB91F353A/353A/352A/351A : 4 channels)

• Selectable parity on/off

• Asynchronous (start-stop synchronized) or CLK-synchronous communications selectable

• Built-in dedicated baud rate timer

• External clock can be used as transfer clock

• Assorted error detection functions (for parity, frame, and overrun errors)

• Support for 115 kbps

8. SIO

• 8-bit data serial transfer : 3 channels (MB91F353A/353A/352A/351A : 2 channels)

• Shift clock selectable from among three internal and one external

• Shift direction selectable (transfer from LSB or MSB)

9. Interrupt controller

• Total number of external interrupts : 17 (MB91F353A/353A/352A/351A : 9)

(One non-maskable interrupt pin and 16/8 ordinary interrupt pins that can be used for wakeup in stop mode.)

• Interrupts from internal peripherals

• Programmable priorities (16 levels) for all interrupts except the non-maskable interrupt

10. D/A converter

• 8-bit resolution : 3 channels (MB91F353A/353A/352A/351A : 2 channels)

11. A/D converter

• 10-bit resolution : 12 channels (MB91F353A/353A/352A/351A : 8 channels)

• Serial/parallel conversion type Conversion time : 1.48 µs

• Conversion mode (one shot conversion mode, continuous conversion mode)

• Activation source (software, external trigger, peripheral interrupt)

12. Other interval timer/counter

• 8/16-bit up/down counter

The MB91F353A/353A/352A/351A supports only an 8-bit up/down counter.

• 16-bit timer (U-TIMER) : 5 channels (MB91F353A/353A/352A/351A : 4 channels)

• Watch dog timer

13. I2C bus interface* (supports 400 kbps)

• 1 channel master/slave transmission and reception

• Arbitration and clock synchronization functions

14. I/O ports

•3 V I/O ports

(5 V input is supported for those ports that are also used for external interrupts (16 ports, MB91F353A/353A/

352A/351A : 8 ports).

• Up to 126 ports (MB91F353A/353A/352A/351A : Up to 84 ports)

(Continued)

3

MB91350A Series

(Continued)

15. Other features

• Internal oscillator circuit as clock source, and PLL multiplication can be selected

•INIT

pin provided as a reset pin (the oscillation stabilization wait time when the INIT pin is reset is clock

cycle × 2.)

• Watch dog timer reset and software reset are also provided.

• Support for stop and sleep modes for low power consumption, capable of saving power by operating the CPU

at 32 kHz.

• Gear function

• Built-in time base timer

• Package : MB91F355A/F356B/355A/354A/F357B : LQFP-176 (lead pitch 0.50 mm)

MB91F353A/353A/352A/351A : LQFP-120 (lead pitch 0.50 mm)

• CMOS technology(0.35 µm)

• Power supply voltage : 3.3 V ± 0.3 V

2.7 V to 3.6 V (MB91F356B/F357B only)

* : Purchase of Fujitsu I

components in an I

Philips.

2

2

C components conveys a license under the Philips I2C Patent Rights to use these

C system provided that the system conforms to the I2C Standard Specification as defined by

4

■ PIN ASSIGNMENTS

• MB91F353A/353A/352A/351A

AN7

AN6

AN5

AN4

AN3

AN2

AN1

AN0

SS

V

AVSS/AVRL

AVRH

(TOP VIEW)

CC

AV

DAVC

DAVS

DA0

DA1

PH5/SCK3

PH4/SO3

PH3/SI3

PH2/SCK2

PH1/SO2

PH0/SI2

PO2/OC2

PO0/OC0

MB91350A Series

VSSVCC

PI5/SCK1

PI4/SO1

PI3/SI1

PI2/SCK0

P20/D16

P21/D17

P22/D18

P23/D19

P24/D20

P25/D21

P26/D22

P27/D23

P30/D24

P31/D25

P32/D26

P33/D27

P34/D28

P35/D29

P36/D30

P37/D31

P40/A00

SS

V

VCC

P41/A01

P42/A02

P43/A03

P44/A04

P45/A05

P46/A06

P47/A07

P50/A08

P51/A09

P52/A10

P53/A11

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

3132333435363738394041424344454647484950515253545556575859

103

999897969594939291

102

101

100

60

PI1/SO0

90

PI0/SI0

89

PK7/INT7/ATG

88

PK6/INT6/FRCK

87

PK5/INT5

86

PK4/INT4

85

PK3/INT3

84

PK2/INT2

83

PK1/INT1

82

PK0/INT0

81

PM5/SCK7

80

PM4/SO7/TRG4

79

PM3/SI7/TRG3

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

CC

V

VSS

PM2/SCK6/ZIN0/TRG2

PM1/SO6/BIN0/TRG1

PM0/SI6/AIN0/TRG0

PN4/PPG4

PN2/PPG2

PN0/PPG0

PA3/CS3

PA2/CS2

PA1/CS1

PA0/CS0

P94/AS

P93

P91

P90/SYSCLK

X1A

P54/A12

P55/A13

P56/A14

P57/A15

P60/A16

P61/A17

P62/A18

P63/A19

P64/A20

SS

V

PL1/SCL

SS

V

VCC

PL0/SDA

P83/RD

P80/IN0/RDY

P82/IN2/BRQ

P81/IN1/BGRNT

(FPT-120P-M21)

NMI

MD2

P84/WR0

P85/IN3/WR1

MD1

MD0

INIT

CC

V

X1

X0

SS

V

X0A

5

MB91350A Series

• MB91F355A/F356B/F357B/355A/354A

(TOP VIEW)

PG5/SCK5

NMI

X1A

V

X0A

MD2

MD1

MD0

X0

V

X1

INIT

V

VCC

PC0/DREQ2

PC1/DACK2

PC2/DSTP2/DEOP2

PB0/DREQ0

PB1/DACK0

PB2/DSTP0/DEOP0

PB3/DREQ1

PB4/DACK1

PB5/DSTP1/DEOP1

PB6/IOWR

PB7/IORD

PA0/CS0

PA1/CS1

PA2/CS2

PA3/CS3

V

P80/IN0/RDY

P81/IN1/BGRNT

P82/IN2/BRQ

P85/IN3/WR1

P90/SYSCLK

VCC

P83/RD

P84/WR0

P91

P92/MCLK

P93

P94/AS

V

VCC

PG4/SO5

PG3/SI5

PG2/SCK4

PG1/SO4

PG0/SI4

PH5/SCK3

PH4/SO3

PH3/SI3

PH2/SCK2

PH1/SO2

PH0/SI2

PI5/SCK1

PI4/SO1

132

131

130

129

128

127

126

125

124

123

122

121

133

134

135

SS

136

137

138

139

140

141

CC

142

143

144

SS

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

SS

162

163

164

165

166

167

168

169

170

171

172

173

174

SS

175

176

12345678910111213141516171819202122232425262728293031323334353637383940414243

120

PI3/SI1

PI2/SCK0

PI1/SO0

119

118

117

CC

PI0/SI0

V

VSS

116

115

114

PJ7/INT15

PJ6/INT14

PJ5/INT13

PJ4/INT12

113

112

111

110

PJ3/INT11

PJ2/INT10

PJ1/INT9

PJ0/INT8

109

108

107

106

PK7/INT7/ATG

PK6/INT6/FRCK

PK5/INT5

PK4/INT4

PK3/INT3

PK2/INT2

105

104

103

102

101

100

PK1/INT1

PK0/INT0

VCCVSS

PL1/SCL

PL0/SDA

VSSPM5/SCK7/ZIN1/TRG5

PM4/SO7/BIN1/TRG4

PM3/SI7/AIN1/TRG3

9998979695949392919089

PM2/SCK6/ZIN0/TRG2

PM1/SO6/BIN0/TRG1

88

PM0/SI6/AIN0/TRG0

87

PN5/PPG5

86

PN4/PPG4

85

PN3/PPG3

84

PN2/PPG2

83

PN1/PPG1

82

PN0/PPG0

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

CC

V

VSS

PO7/OC7

PO6/OC6

PO5/OC5

PO4/OC4

PO3/OC3

PO2/OC2

PO1/OC1

PO0/OC0

PP3/TOT3

PP2/TOT2

PP1/TOT1

PP0/TOT0

CC

V

VSS

AVSS/AVRL

AVRH

CC

AV

AN11

AN10

AN9

AN8

AN7

AN6

AN5

AN4

AN3

AN2

AN1

AN0

DA2

DA1

DA0

DAVC

DAVS

P20/D16

P21/D17

P22/D18

P23/D19

P24/D20

P25/D21

P26/D22

P27/D23

P30/D24

P31/D25

P32/D26

P33/D27

P34/D28

P35/D29

P36/D30

P37/D31

SS

V

VCC

P40/A00

P41/A01

P42/A02

P43/A03

P44/A04

P45/A05

P46/A06

P47/A07

P50/A08

P51/A09

P52/A10

P53/A11

P54/A12

P55/A13

P56/A14

SS

V

VCC

P57/A15

P60/A16

P61/A17

P62/A18

P63/A19

P64/A20

P65/A21

P66/A22

P67/A23

(FPT-176P-M02)

6

■ PIN DESCRIPTION

MB91350A Series

Pin no.

1

LQFP*

1 to 8 1 to 8

9 to 16 9 to 16

19 to 26 17, 20 to 26

27 to 34 27 to 34

37 to 41 35 to 39

42 to 44 ⎯

47, 48 106,105 DA0, DA1 ⎯ D/A converter output pins

LQFP*

Pin name

2

D16 to D23

P20 to P27 Can be used as ports while in external bus 8-bit mode.

D24 to D31

P30 to P37 Can be used as ports while in single-chip mode.

A00 to A07

P40 to P47 Can be used as ports while in single-chip mode.

A08 to A15

P50 to P57 Can be used as ports while in single-chip mode.

A16 to A20

P60 to P64

A21 to A23

P65 to P67

I/O

circuit

type*

C

C

C

C

C

C

3

Bit 16 to bit 23 of the external data bus.

Valid only in external bus mode.

Bit 24 to bit 31 of the external data bus.

Valid only in external bus mode.

Bit 0 to bit 7 of the external address bus.

Valid only in external bus mode.

Bit 8 to bit 15 of the external address bus.

Valid only in external bus mode.

Bit 16 to bit 20 of the external address bus.

Valid only in external bus mode.

Can be used as ports while in single-chip mode or when the

external address bus is not used.

Bit 21 to bit 23 of the external address bus.

Valid only in external bus mode.

Can be used as ports while in single-chip mode or when the

external address bus is not used.

Function

49 ⎯ DA2 ⎯ D/A converter output pin

50 to 57 113 to 120 AN0 to AN7 G Analog input pins

58 to 61 ⎯ AN8 to AN11 G Analog input pins

TOT0 to TOT3

67 to 70 ⎯

PP0 to PP3

OC0

71 97

PO0

Reload timer output ports.

This pin is valid when timer output is enabled.

D

General-purpose I/O ports.

This pin is valid when the timer output function is

disabled.

Output compare output pin

General-purpose I/O port.

D

This pin can be used as a port when the output compare

output is not used.

(Continued)

7

MB91350A Series

Pin no.

1

LQFP*

LQFP*

72 ⎯

73 98

74 to 78 ⎯

81 70

82 ⎯

2

OC3 to OC7

PO3 to PO7

Pin name

OC1

PO1

OC2

PO2

PPG0

PN0

PPG1

PN1

I/O

circuit

type*

D

D

D

D

D

3

Function

Output compare output pin

General-purpose I/O port.

This pin can be used as a port when the output compare

output is not used.

Output compare output pin

General-purpose I/O port.

This pin can be used as a port when the output compare

output is not used.

Output compare output pins

General-purpose I/O ports.

These pins can be used as ports when the output compare

outputs are not used.

PPG timer output pin

General-purpose I/O port.

This pin can be used as a port when the PPG timer output is

not used.

PPG timer output pin

General-purpose I/O port.

This pin can be used as a port when the PPG timer output is

not used.

83 71

84 ⎯

85 72

86 ⎯

PPG2

PN2

PPG3

PN3

PPG4

PN4

PPG5

PN5

PPG timer output pin

General-purpose I/O port.

D

This pin can be used as a port when the PPG timer output is

not used.

PPG timer output pin

General-purpose I/O port.

D

This pin can be used as a port when the PPG timer output is

not used.

PPG timer output pin

General-purpose I/O port.

D

This pin can be used as a port when the PPG timer output is

not used.

PPG timer output pin

General-purpose I/O port.

D

This pin can be used as a port when the PPG timer output is

not used.

(Continued)

8

MB91350A Series

Pin no.

LQFP*

1

87 73

88 74

LQFP*

2

Pin name

SI6

AIN0

TRG0

PM0

SO6

BIN0

TRG1

PM1

I/O

circuit

type*

D

D

3

Function

Data input for serial I/O6.

Since this input is always used when serial I/O6 input is

operating, output using the port must be stopped beforehand

unless this operation is the intended operation.

Input for the up/down counter.

Since this input is always used when input is enabled, output

using the port must be stopped beforehand unless this operation

is the intended operation.

External trigger input for PPG timer 0.

Since this input is always used when input is enabled, output

using the port must be stopped beforehand unless this operation

is the intended operation.

General-purpose I/O port.

This pin can be used as a port when serial I/O, up/down counter,

and PPG timer output are not used.

Data output from serial I/O6.

This function is valid when data output from serial I/O6 is

enabled.

Input for the up/down counter.

Since this input is always used when input is enabled, output

using the port must be stopped beforehand unless this operation

is the intended operation.

External trigger input for PPG timer 1.

Since this input is always used when input is enabled, output

using the port must be stopped beforehand unless this operation

is the intended operation.

General-purpose I/O port.

This pin can be used as a port when serial I/O, up/down counter,

and PPG timer output are not used.

89 75

SCK6

ZIN0

TRG2

PM2

Clock I/O for serial I/O 6.

This function is valid when clock output from serial I/O6 is

enabled or when an external shift clock input is used.

Input for the up/down counter.

Since this input is always used when input is enabled, output

using the port must be stopped beforehand unless this operation

is the intended operation.

D

External trigger input for PPG timer 2.

Since this input is always used when input is enabled, output

using the port must be stopped beforehand unless this operation

is the intended operation.

General-purpose I/O port.

This pin can be used as a port when serial I/O, up/down counter,

and PPG timer output are not used.

(Continued)

9

MB91350A Series

Pin no.

LQFP*

1

90 78

91 79

92 80

LQFP*

2

Pin name

SI7

4

AIN1*

TRG3

PM3

S07

4

BIN1*

TRG4

PM4

SCK7

4

ZIN1*

TRG5*

4

PM5

I/O

circuit

type*

D

D

D

3

Function

Data input for serial I/O7.

Since this input is always used when serial I/O7 input is

operating, output using the port must be stopped beforehand

unless this operation is the intended operation.

Input for the up/down counter.

Since this input is always used when input is enabled, output

using the port must be stopped beforehand unless this operation

is the intended operation.

External trigger input for PPG timer 3.

Since this input is always used when input is enabled, output

using the port must be stopped beforehand unless this operation

is the intended operation.

General-purpose I/O port.

This pin can be used as a port when serial I/O, up/down counter,

and PPG timer output are not used.

Data output from serial I/O7.

This function is valid when data output from serial I/O7 is

enabled.

Input for the up/down counter.

Since this input is always used when input is enabled, output

using the port must be stopped beforehand unless this operation

is the intended operation.

External trigger input for PPG timer 4.

Since this input is always used when input is enabled, output

using the port must be stopped beforehand unless this operation

is the intended operation.

General-purpose I/O port.

This pin can be used as a port when serial I/O, up/down counter,

and PPG timer output are not used.

Clock I/O for serial I/O7.

This function is valid when clock output from serial I/O7 is

enabled or when an external shift clock input is used.

Input for the up/down counter.

Since this input is always used when input is enabled, output

using the port must be stopped beforehand unless this operation

is the intended operation.

External trigger input for PPG timer 5.

Since this input is always used when input is enabled, output

using the port must be stopped beforehand unless this operation

is the intended operation.

General-purpose I/O port.

This pin can be used as a port when serial I/O, up/down counter,

and PPG timer output are not used.

(Continued)

10

MB91350A Series

Pin no.

1

LQFP*

LQFP*

94 42

95 41

98 to 103 81 to 86

2

INT0 to INT5

Pin name

SDA

PL0

SCL

PL1

I/O

circuit

type*

F

F

E

3

DATA I/O pin for the I

This pin is valid when standard mode I

2

C bus.

2

C operation is

enabled.

Output using the port must be stopped beforehand unless this

operation is intended (open drain output).

General-purpose I/O port.

Function

This pin can be used as a port when I

2

C operation is disabled

(open drain output).

Clock I/O pin for the I

This pin is valid when standard mode I

2

C bus.

2

C operation is

enabled.

Output using the port must be stopped beforehand unless this

operation is intended (open drain output).

General-purpose I/O port.

This pin can be used as a port when I

2

C operation is disabled

(open drain output).

External interrupt inputs.

Since these inputs are always used when the corresponding

external interrupts are enabled, output using the ports must

be stopped beforehand unless this operation is the intended

operation.

104 87

105 88

PK0 to PK5 General-purpose I/O ports

External interrupt input.

Since this input is always used when the corresponding

INT6

external interrupt is enabled, output using the port must be

stopped beforehand unless this operation is the intended

operation.

E

External clock input pin for the free-run timer.

Since this input is always used when it is selected as the

FRCK

external clock input for the free-run timer, output using the port

must be stopped beforehand unless this operation is the

intended operation.

PK6 General-purpose I/O port

External interrupt input.

Since this input is always used when the corresponding

INT7

external interrupt is enabled, output using the port must be

stopped beforehand unless this operation is the intended

operation.

E

External trigger for the A/D converter.

ATG

Since this input is always used when it is selected as the A/D

activation source, output using the port must be stopped

beforehand unless this operation is the intended operation.

PK7 General-purpose I/O port

(Continued)

11

MB91350A Series

Pin no.

1

LQFP*

LQFP*

106 to 113 ⎯

116 89

117 90

118 91

119 92

120 93

121 94

122 99

I/O

2

Pin name

circuit

type*

3

External interrupt inputs.

Since these inputs are always used when the corresponding

INT8 to INT15

external interrupts are enabled, output using the ports must

E

be stopped beforehand unless this operation is the intended

operation.

PJ0 to PJ7 General-purpose I/O ports

Data input for UART0.

SI0

Since this input is always used when UART0 input is operating, output using the port must be stopped beforehand unless

D

this operation is the intended operation.

PI0 General-purpose I/O port

SO0

Data output from UART0.

This function is valid when UART0 data output is enabled.

D

PI1

General-purpose I/O port.

This function is valid when UART0 data output is disabled.

Clock I/O for UART0.

SCK0

This function is valid when UART0 clock output is enabled or

when an external clock input is used.

D

General-purpose I/O port.

PI2

This function is valid when UART0 clock output is disabled or

when an external clock input is not used.

Data input for UART1.

SI1

Since this input is always used when UART1 input is

operating, output using the port must be stopped beforehand

D

unless this operation is the intended operation.

PI3 General-purpose I/O port

SO1

Data output from UART1.

This function is valid when UART1 data output is enabled.

D

PI4

General-purpose I/O port.

This function is valid when UART1 data output is disabled.

Clock I/O for UART1.

SCK1

This function is valid when UART1 clock output is enabled or

when an external clock input is used.

D

General-purpose I/O port.

PI5

This function is valid when UART1 clock output is disabled or

when an external clock input is not used.

Data input for UART2.

SI2

Since this input is always used when UART2 input is

operating, output using the port must be stopped beforehand

D

unless this operation is the intended operation.

PH0 General-purpose I/O port

Function

(Continued)

12

MB91350A Series

Pin no.

1

LQFP*

LQFP*

123 100

124 101

125 102

126 103

2

I/O

Pin name

SO2

PH1

circuit

type*

D

3

Data output from UART2.

This function is valid when UART2 data output is enabled.

General-purpose I/O port.

This function is valid when UART2 data output is disabled or

when an external shift clock input is used.

Clock I/O for UART2.

SCK2

This function is valid when UART2 clock output is enabled or

when an external clock input is used.

D

General-purpose I/O port.

PH2

This function is valid when UART2 clock output is disabled or

when an external clock input is not used.

Data input for UART3.

SI3

Since this input is always used when UART3 input is operating, output using the port must be stopped beforehand unless

D

this operation is the intended operation.

PH3 General-purpose I/O port

SO3

Data output from UART3.

This function is valid when UART3 data output is enabled.

D

PH4

General-purpose I/O port.

This function is valid when UART3 data output is disabled.

Function

127 104

128 ⎯

129 ⎯

Clock I/O for UART3.

SCK3

This function is valid when UART3 clock output is enabled or

when an external clock input is used.

D

General-purpose I/O port.

PH5

This function is valid when UART3 clock output is disabled or

when an external clock input is not used.

Data input for UART4.

SI4

Since this input is always used when UART4 input is operating, output using the port must be stopped beforehand unless

D

this operation is the intended operation.

PG0 General-purpose I/O port

SO4

Data output from UART4.

This function is valid when serial I/O4 data output is enabled.

D

PG1

General-purpose I/O port.

This function is valid when serial I/O4 data output is disabled.

(Continued)

13

MB91350A Series

Pin no.

LQFP*

1

130 ⎯

131 ⎯

132 ⎯

133 ⎯

LQFP*

2

I/O

Pin name

circuit

type*

3

Clock I/O for UART4.

SCK4

This function is valid when serial I/O4 clock output is enabled or

when an external clock input is used.

D

General-purpose I/O port.

PG2

This function is valid when serial I/O4 clock output is disabled

or when an external clock input is not used.

Data input for serial I/O5.

SI5

Since this input is always used when serial I/O5 input is

operating, output using the port must be stopped beforehand

D

unless this operation is the intended operation.

PG3 General-purpose I/O port

SO5

Data output from serial I/O5.

This function is valid when serial I/O5 data output is enabled.

D

PG4

General-purpose I/O port.

This function is valid when serial I/O5 data output is disabled.

Clock I/O for serial I/O5.

SCK5

This function is valid when serial I/O5 clock output is enabled or

when an external shift clock input is used.

D

General-purpose I/O port.

PG5

This function is valid when serial I/O5 clock output is disabled

or when an external clock input is not used.

Function

134 51 NMI

H NMI (non-maskable interrupt) input

135 61 X1A B Clock (oscillation) output (sub clock)

137 60 X0A B Clock (oscillation) input (sub clock)

H Mode pins 2 to 0.

These pins set the basic operating mode. Connect the pins to

V

138 to 140 52 to 54 MD2 to MD0

J

CC or VSS.

Input circuit type :

The production version (MASK ROM version) is the "H" type.

The Flash ROM version is the "J" type.

141 58 X0 A Clock (oscillation) input (main clock)

143 57 X1 A Clock (oscillation) output (main clock)

144 55 INIT

I External reset input

DMA external transfer request input.

147 ⎯

DREQ2

Since this input is always used when it is selected as the DMA

activation source, output using the port must be stopped

C

beforehand unless this operation is the intended operation.

PC0 General-purpose I/O port

(Continued)

14

MB91350A Series

Pin no.

LQFP*

1

148 ⎯

149 ⎯

150 ⎯

LQFP*

2

I/O

Pin name

circuit

type*

3

DMA external transfer request acceptance output.

DACK2

This function is valid when DMA transfer request acceptance

output is enabled.

C

General-purpose I/O port.

PC1

This function is valid when DMA transfer request acceptance

output is enabled.

DMA external transfer end output.

DEOP2

This function is valid when DMA external transfer end output is

enabled.

DMA external transfer stop input.

DSTP2

C

This function is valid when DMA external transfer stop input is

enabled.

General-purpose I/O port.

PC2

This function is valid when DMA external transfer end output

and external transfer stop input are disabled.

DMA external transfer request input.

DREQ0

Since this input is always used when it is selected as the DMA

activation source, output using the port must be stopped

C

beforehand unless this operation is the intended operation.

PB0 General-purpose I/O port

Function

151 ⎯

152 ⎯

153 ⎯

DMA external transfer request acceptance output.

DACK0

This function is valid when DMA transfer request acceptance

output is enabled.

C

General-purpose I/O port.

PB1

This function is valid when DMA transfer request acceptance

output is disabled.

DMA external transfer end output.

DEOP0

This function is valid when DMA external transfer end output is

enabled.

DMA external transfer stop input.

DSTP0

C

This function is valid when DMA external transfer stop input is

enabled.

General-purpose I/O port.

PB2

This function is valid when DMA external transfer end output

and external transfer stop input are disabled.

DMA external transfer request input.

DREQ1

Since this input is always used when it is selected as the DMA

activation source, output using the port must be stopped

C

beforehand unless this operation is the intended operation.

PB3 General-purpose I/O port.

(Continued)

15

MB91350A Series

Pin no.

LQFP*

1

154 ⎯

155 ⎯

156 ⎯

LQFP*

2

Pin name

DACK1

PB4

DEOP1

DSTP1

PB5

IOWR

PB6

I/O

circuit

type*

C

C

C

3

Function

DMA external transfer request acceptance output.

This function is valid when DMA transfer request acceptance

output is enabled.

General-purpose I/O port.

This function is valid when DMA external transfer request

acceptance output is disabled.

DMA external transfer end output.

This function is valid when DMA external transfer end output

is enabled.

DMA external transfer stop input.

This function is valid when DMA external transfer stop input is

enabled.

General-purpose I/O port.

This function is valid when DMA external transfer end output

and external transfer stop input are disabled.

Write strobe output for DMA fly-by transfer.

This function is valid when write strobe output for DMA fly-by

transfer is enabled.

General-purpose I/O port.

This function is valid when write strobe output for DMA fly-by

transfer is disabled.

157 ⎯

158 66

159 67

160 68

IORD

PB7

CS0

PA0

CS1

PA1

CS2

PA2

Read strobe output for DMA fly-by transfer.

This function is valid when read strobe output for DMA fly-by

transfer is enabled.

C

General-purpose I/O port.

This function is valid when read strobe output for DMA fly-by

transfer is disabled.

Chip select 0 output.

This function is valid in external bus mode.

C

General-purpose I/O port.

This function is valid in single-chip mode.

Chip select 1 output.

This function is valid when chip select 1 output is enabled.

C

General-purpose I/O port.

This function is valid when chip select 1 output is disabled.

Chip select 2 output.

This function is valid when chip select 2 output is enabled.

C

General-purpose I/O port.

This function is valid when chip select 2 output is disabled.

(Continued)

16

MB91350A Series

Pin no.

LQFP*

1

161 69

164 45

165 46

LQFP*

2

Pin name

CS3

PA3

RDY

IN0

P80

BGRNT

IN1

I/O

circuit

type*

C

D

D

3

Function

Chip select 3 output.

This function is valid when chip select 3 output is enabled.

General-purpose I/O port.

This function is valid when chip select 3 output is disabled.

External ready input.

This function is valid when external ready input is enabled.

Input capture input pin.

Since this input is always used when it is selected for input

capture input, output using the port must be stopped

beforehand unless this operation is the intended operation.

General-purpose I/O port.

This function is valid when external ready input is disabled.

External bus open acceptance output.

Outputs an “L” level when the external bus is open.

This function is valid when output is enabled.

Input capture input pin.

Since this input is always used when it is selected for input

capture input, output using the port must be stopped

beforehand unless this operation is the intended operation.

166 47

167 48

P81

BRQ

IN2

P82

RD

P83

General-purpose I/O port.

This function is valid when external bus open acceptance is

disabled.

External bus open request input.

A high level is input to this pin to request for the external bus

to be made open.

This function is valid when input is enabled.

Input capture input pin.

D

Since this input is always used when it is selected for input

capture input, output using the port must be stopped

beforehand unless this operation is the intended operation.

General-purpose I/O port.

This function is valid when external bus open request is

disabled.

External bus read strobe output.

This function is valid in external bus mode.

D

General-purpose I/O port.

This function is valid in single-chip mode.

(Continued)

17

MB91350A Series

(Continued)

Pin no.

LQFP*

1

LQFP*

2

Pin name

I/O

circuit

type*

3

Function

WR0

168 49

P84

External bus write strobe output.

This function is valid in external bus mode.

D

General-purpose I/O port.

This function is valid in single-chip mode.

External bus write strobe output.

WR1

This function is valid when WR1

is enabled.

Input capture input pin.

169 50

IN3

Since this input is always used when it is selected for input

D

capture input, output using the port must be stopped beforehand unless this operation is the intended operation.

General-purpose I/O port.

P85

This function is valid when external bus write enable output is

disabled.

System clock output.

SYSCLK

170 62

P90

This function is valid when system clock output is enabled. A

clock having the same frequency as the external bus operat-

C

ing frequency is output (stopped in stop mode).

General-purpose I/O port.

This function is valid when system clock output is disabled.

171 63 P91 C General-purpose I/O port

output in external bus mode

Memory clock output.

MCLK

172 ⎯

P92

This function is valid when memory clock output is enabled. A

clock having the same frequency as the external bus operat-

C

ing frequency is output (stopped in sleep mode).

General-purpose I/O port.

This function is valid when memory clock output is disabled.

173 64 P93 C General-purpose I/O port

AS

174 65

P94

Address strobe output.

This function is valid when address strobe output is enabled.

C

General-purpose I/O port.

This function is valid when address load output is disabled.

*1 : FPT-176P-M02

*2 : FPT-120P-M21

*3 : Refer to “■ I/O CIRCUIT TYPE” for details on the I/O circuit types.

*4 : These functions are not supported on the FPT-120P-M21.

18

[Power supply and GND pins]

Pin number

1

LQFP*

LQFP*

MB91350A Series

2

Pin name Function

17, 35, 65, 79, 93, 96,

114, 136, 145, 162, 175

18, 36, 66, 80, 97, 115,

142, 146, 163, 176

45 107 DAVS D/A converter GND pin

46 108 DAVC D/A converter power supply pin

62 109 AV

63 110 AVRH A/D converter reference power supply pin

64 111 AV

*1 : FPT-176P-M02

*2 : FPT-120P-M21

18, 40, 43, 59,

76, 96, 112

19, 44, 56, 77,

95

VSS

V

CC

CC A/D converter analog power supply pin

SS/AVRL A/D converter analog GND pin

GND pins. Use the same potential for all

pins.

3.3 V power supply pins. Use the same

potential for all pins.

19

MB91350A Series

■ I/O CIRCUIT TYPE

Type Circuit type Remarks

X1

Clock input

Oscillation feedback resistance :

approx. 1 MΩ

A

B

X0

Standby control

X1A

Clock input

X0A

Standby control

Pull-up control

Oscillation feedback resistance for low

speed (sub clock oscillation) :

approx. 7 MΩ

• CMOS level output

• CMOS level input

P-chP-ch

Digital output

N-ch

C

Digital output

With standby control

With pull-up control

20

Digital input

Standby control

Pull-up control

• CMOS level output

• CMOS level hysteresis input

P-chP-ch

Digital output

N-ch

D

Digital output

With standby control

With pull-up control

Digital input

Standby control

(Continued)

MB91350A Series

Type Circuit type Remarks

• CMOS level output

P-ch

P-ch

N-ch

E

Digital output

Digital output

Digital input

N-ch

Digital output

• CMOS level hysteresis input

Withstand voltage of 5 V

• N-ch (Open drain input)

• CMOS level hysteresis input

F

With standby control

Withstand voltage of 5 V

Digital input

Standby control

Analog input

P-ch

N-ch

With switch

G

Analog input

Control

P-ch

H

N-ch

CMOS level hysteresis input

Digital input

P-ch P-ch

CMOS level hysteresis input

With pull-up resistor

I

Digital input

(Continued)

21

MB91350A Series

(Continued)

Type Circuit type Remarks

• CMOS level input

N-ch

N-ch

MB91F353A/F355A/F356B/F357B

•

only

J

N-ch

N-ch

N-ch

Diffused resistor

Control signal

Mode input

22

■ HANDLING DEVICES

• Preventing Latch-up

MB91350A Series

Latch-up may occur in a CMOS IC if a voltage greater than V

pin or if an above-rating voltage is applied between V

CC and VSS. A latch-up,if it occurs, significantly increases

CC or less than VSS is applied to an input or output

the power supply current and may cause thermal destruction of an element. When you use a CMOS IC, don’t

exceed the absolute maximum rating.

• Treatment of Unused Pins

Do not leave unused input pins open, as this may cause a malfunction. Handle by using a pull-up or pull-down

resistor.

• Power Supply Pins

In products with multiple V

CC and VSS pins, the pins of the same potential are internally connected in the device

to avoid abnormal operations including latch-up. However, you must connect the pins to the external power

supply and ground lines in order to lower the electro-magnetic emission level, to prevent abnormal operation of

strobe signals caused by the rise in the ground level, and to conform to the total output current rating. Moreover,

connect the current supply source to the V

It is also advisable to connect a ceramic bypass capacitor of approximately 0.1 µF between V

CC and VSS pins of this device at the low impedance.

CC and VSS pins

near this device.

• Crystal Oscillator Circuit

Noise near the X0, X1, X0A and X1A pins may cause the device to malfunction. Design the printed circuit board

so that X0, X1, X0A, X1A, the crystal oscillator (or ceramic oscillator), and the bypass capacitor to ground are

located close to the device as possible.

It is strongly recommended that the PC board artwork be designed such that the X0, X1, X0A and X1A pins are

surrounded by ground plane, as stable operation can be obtained by using this layout.

Please ask the crystal maker to evaluate the oscillational characteristics of the crystal and this device.

• Notes on Using an External Clock

When using an external clock, as a general rule you should simultaneously supply the clock signal to X0 and a

clock signal with the reverse phase to X1. However, the stop mode (oscillator stop mode) must not be used

under this configuration (This is because the X1 pin stops at High level output in STOP mode) .

Using an external clock (normal)

X0

X1

MB91350A series

Note : STOP mode (oscillation stop mode) cannot be used.

• Clock Control Block

Hold the signal for the oscillation stabilization wait time when inputting a Low level to the INIT pin.

23

MB91350A Series

• Notes on Using the Sub Clock

When the X0A and X1A pins are not connected to an oscillator, pull down the X0A pin and leave the X1A pin open.

Using an external clock (normal)

X0

OPEN

X1

MB91350A series

• Treatment of NC and OPEN Pins

Pins marked as NC and OPEN must be left open.

• Mode Pins (MD0 to MD2)

These pins should be connected directly to the V

CC or VSS pins.

To prevent the device erroneously switching to test mode due to noise, design the printed circuit board such that

the distance between the mode pins and V

CC or VSS pins is as short as possible and the connection impedance

is low.

• Operation at Start-up

The INIT

Immediately after the power supply is turned on, the Low level input needs to be held to the INIT

pin must be at Low level when the power supply is turned on.

pin for the

oscillation stabilization wait time of the oscillator circuit to ensure that the oscillator has time to settle (For INIT

via the INIT

pin, the oscillation stabilization wait time setting is initialized to the minimum value).

• Oscillation Input at Power On

When the power is turned on, maintain the clock input until the device is released from the oscillation stabilization

wait state.

• Precautions While Operating in PLL Clock Mode

On this microcontroller, if the crystal oscillator is disconnected or the external reference clock input stops while

PLL clock mode is selected, the microcontroller may continue to operate at the free-run frequency of the selfoscillating circuit within the PLL. However, Fujitsu does not guarantee this operation.

• External Bus Setting

This model guarantees an external bus frequency of 25 MHz.

If the base clock frequency is set to 50 MHz when the DIVR1 (external bus base clock division setting register)

register is still set to the default value, the external bus frequency will be set to 50 MHz. When you change the

base clock frequency, change the base clock frequency after setting the external bus within 25 MHz.

• MCLK and SYSCLK

The difference between MCLK and SYSCLK is that MCLK stops in SLEEP/STOP mode but SYSCLK stops only

in STOP mode. Use the clock that is appropriate for each application.

Upon initialization, MCLK is disabled (PORT) and SYSCLK is enabled. To use MCLK, the port function register

(PFR) needs to be set to enable the use of the clock.

24

MB91350A Series

• Pull-up Control

If a pull-up resistor is provided to a pin that is used as an external bus pin, there is no guarantee that the pin will

conform to the specifications given in “■ ELECTRICAL CHARACTERISTICS 4. AC Characteristics (4) Normal

Bus Access Read/Write Operation, (5) Multiplex Bus Access Read/Write operation and (7) Hold Timing”.

Furthermore, even if a port has been configured to use a pull-up resistance, this setting is invalid during stop

mode with HIZ=1 and during hardware standby mode.

• Sub Clock Select

At least one NOP instruction needs to be executed immediately after switching the clock source from main clock

mode to sub clock mode.

(Idi #0x0b, r0)

(Idi #_CLKR, r12)

stb r0, @r12 // sub-clock mode

nop // Must insert NOP instruction

• Bit Search Module

The BSD0, BSD1, and BDSC registers can only be accessed in words.

•D-bus Memory

Do not set the code area to memory on the D-bus because instructions cannot be fetched from the D-bus.

Executing an instruction fetch to the D-bus area will cause incorrect data to be interpreted as code, possibly

causing the device to run out of control.

• Low Power Consumption Mode

When entering sleep or stop mode, be sure to read the standby control register (STCR) immediately after writing

to it.

More specifically, use the following sequence.

Furthermore, after recovering from standby mode, set the I flag, ILM, and ICR registers such that the CPU

branches to the interrupt handler for the interrupt that triggered the controller to recover from standby mode.

(Idi #value_of_standby, r0)

(Idi #_STCR, r12)

stb r0, @r12 // set STOP/SLEEP bit

Idub @r12, r0 // Must read STCR

Idub @r12, r0 // after reading, go into standby mode

NOP // Must insert NOP × 5

NOP

NOP

NOP

NOP

• Switching the Function of Shared Ports

Use the Port Function Register (PFR) to switch between using an external pin as a port or a shared pin. Note,

however, that bus pins are switched depending on the external bus settings.

25

MB91350A Series

•Prefetch

If prefetch is enabled in a area that is configured as little endian, limit access to the corresponding area to

word-length (32-bit) access.

Byte or halfword does not allow a proper access to data.

• I/O Port Access

Ports can only be accessed in bytes.

• Built-in RAM

Immediately after a reset is released, the internal RAM capacity restriction function begins operating, allowing

only 4 Kbytes to be used for both data and program execution irrespective of the on-chip RAM capacity.

Update the setting to clear the restriction function.

At least one NOP instruction is required immediately after updating this setting.

Please refer to the “MB91350A Series HARDWARE MANUAL CHAPTER 19 DATA INTERNAL RAM/INSTRUCTION INTERNAL RAM ACCESS RESTRICTION FUNCTIONS” for the details.

•Flash Memory

In programming mode, Flash memory cannot be used for the interrupt vector table (However, a reset can be

performed) .

• Notes on the PS Register

As the PS register is processed in advance by some instructions, when the debugger is being used, the following

exception handling may result in execution breaking in an interrupt handling routine or the displayed values of

the flags in the PS register being updated.

As the microcontroller is designed to carry out reprocessing correctly upon returning from such an EIT event,

the operation before and after the EIT always proceeds according to specification.

1. The following behavior may occur if any of the following occurs in the instruction immediately after a DIVOU/

DIVOS instruction :

(a) a user interrupt or NMI is accepted; (b) single-step execution is performed; or (c) execution breaks due

to a data event or from the emulator menu.

• The D0 and D1 flags are updated in advance.

• An EIT handling routine (user interrupt, NMI, or emulator) is executed.

• Upon returning from the EIT, the DIVOU/DIVOS instruction is executed and the D0 and D1 flags are

updated to the same values as in (1).

2. The following behavior occurs when an ORCCR, STILM, MOV Ri or PS instruction is executed to enable a

user interrupt or NMI source while that interrupt is in the active state.

• The PS register is updated in advance.

• The EIT handling routine (user interrupt, NMI, or emulator) is executed.

• Upon returning from the EIT, the above instructions are executed and the PS register is updated to the

same value as in (1).

26

MB91350A Series

[Note on Debugger]

• Single-Step Execution of the RETI Command

If single-step execution is used in an environment where an interrupt occurs frequently, the corresponding

interrupt handling routine will be executed repeatedly to the exclusion of other processing. This will prevent the

main routine and the handlers for low priority level interrupts from being executed (For example, if the time-base

timer interrupt is enabled, stepping over the RETI instruction will always break on the first line of the time-base

timer interrupt handler) .

Disable the corresponding interrupt when the corresponding interrupt handling routine no longer needs debugging.

• Break Function

If the range of addresses that cause a hardware break (including event breaks) is set to the address of the

current system stack pointer or to an area that contains the stack pointer, execution will break after each

instruction regardless of whether the user program actually contains data access instructions.

To prevent this, do not set (word) access to the area containing the address of the system stack pointer as the

target of the hardware break (including event breaks).

• Internal ROM area

Do not set DMAC transfer destination to an address in the internal ROM area.

• Simultaneous Occurrence of a Software Break (INTE instruction) and a User Interrupt/NMI

When a software break and a user interrupt/NMI occur simultaneously, the emulator debugger may react as

follows.

• The debugger stops pointing to a location other than a programmed breakpoint.

• The program does not resume execution correctly after breaking.

If this symptom occurs, use a hardware break in place of the software break. When using a monitor debugger,

do not set a break at the relevant location.

• A malfunction may occur if the stack pointer is in an area that is configured for DSU operand break. Do not

set a data event breaks that apply to accesses to an area that contains the address of the system stack pointer.

27

MB91350A Series

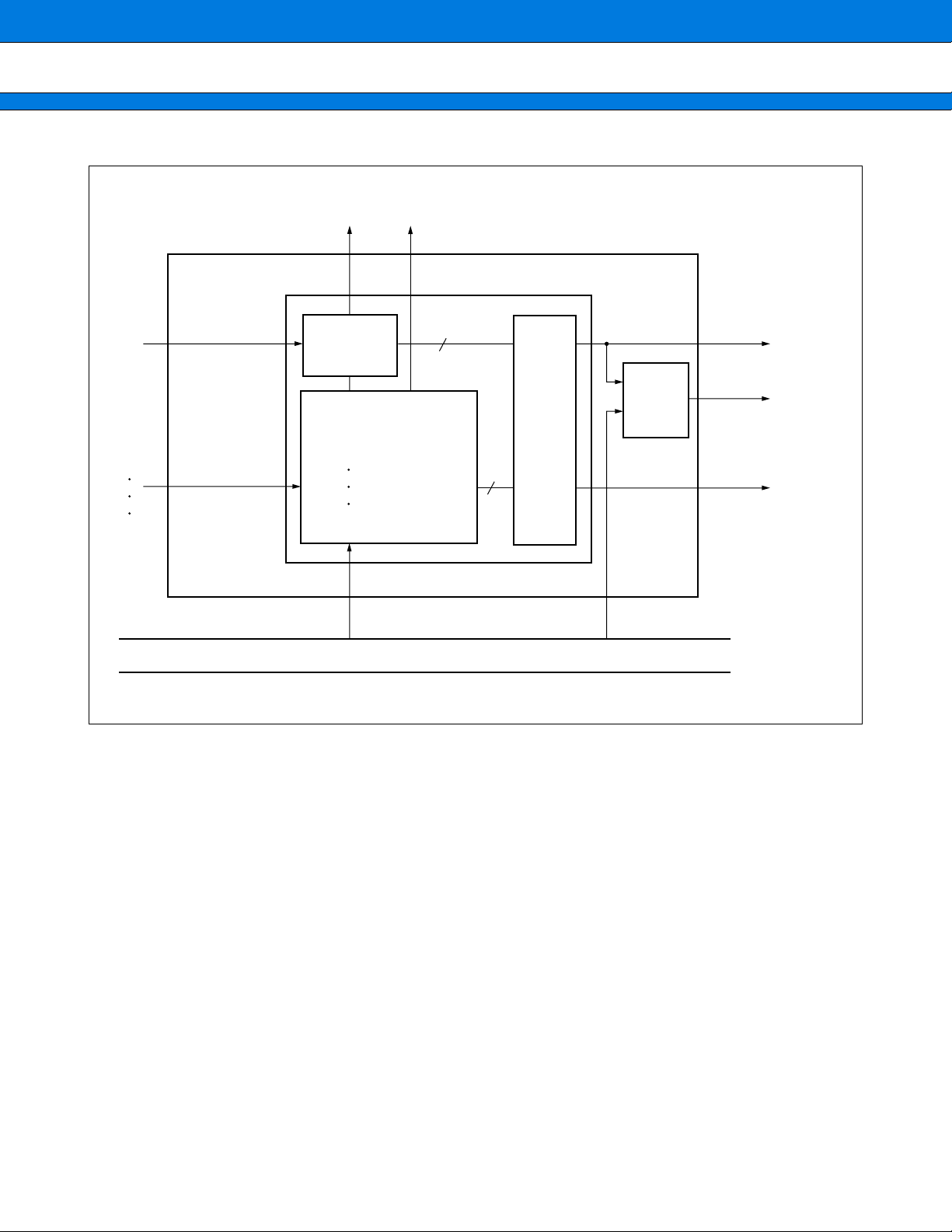

■ BLOCK DIAGRAMS

• MB91F353A/353A/352A/351A

FR CPU

32 32

X0, X1

MD0 to MD2

INIT

X0A, X1A

INT0 to INT7

NMI

SI0 to SI3

SO0 to SO3

SCK0 to SCK3

Bit search

RAM

16 Kbytes(stack)*

ROM 512 Kbytes*

RAM 8 Kbytes

Clock

control

Clock timer

Interrupt

Controller

8 channels

External interrupt

4 channels

UART

32↔16

Adapter

16

32

Bus

Converter

32

DMAC 5 channels

External memory

I/F

PORT

3 channels

PPG

4 channels

Reload timer

Free-run timer

A20 to A00

D31 to D16

RD

WR1, WR0

RDY

BRQ

BGRNT

SYSCLK

PORT

TRG0 to TRG4

PPG0, PPG2, PPG4

FRCK

28

4 channels

U-timer

SI6, SI7

SO6, SO7

SCK6, SCK7

AN0 to AN7

AT G

AVRH, AV

AVSS/AVRL

DAVC, DAVS

CC

DA0, DA1

2 channels

SIO

8 channels

A/D converter

2 channels

D/A converter

* : MB91352A : RAM 8 Kbytes (stack) , ROM 384 Kbytes

MB91351A : RAM 16 Kbytes (stack) , ROM 384 Kbytes

4 channels

Input capture

2 channels

Output compare

1 channel

2

C

I

1 channel

8-bit up/down counter

IN0 to IN3

OC0, OC2

SDA

SCL

AIN0

BIN0

ZIN0

• MB91F355A/F356B/F357B/355A/354A

MB91350A Series

FR CPU

X0, X1

MD0 to MD2

INIT

X0A, X1A

INT0 to INT15

NMI

SI0 to SI4

SO0 to SO4

SCK0 to SCK4

Bit search

RAM (stack)

ROM/Flash

RAM

(Execute instruction)

Clock

control

Clock timer

Interrupt

Controller

16 channels

External interrupt

5 channels

UART

32

32 ↔ 16

Adapter

16

32 32

Bus

Converter

32

DMAC 5 channels

External memory

I/F

PORT

6 channels

PPG

4 channels

reload timer

Free-run timer

DREQ0 to DREQ2

DACK0 to DACK2

DEOP0/DSTP0 to DEOP2/DSTP2

IOWR

IORD

A23 to A00

D31 to D16

RD

WR1, WR0

RDY

BRQ

BGRNT

SYSCLK

PORT

TRG0 to TRG5

PPG0 to PPG5

TOT0 to TOT3

FRCK

SI5 to SI7

SO5 to SO7

SCK5 to SCK7

AN0 to AN11

AT G

AVRH, AV

DA0 to DA2

DAVC, DAVS

CC

AVSS/AVRL

5 channels

U-Timer

3 channels

SIO

12 channels

A/D converter

3 channels

D/A converter

4 channels

input capture

8 channels

output compare

1 channel

2

C

I

2 channels

8/16-bit up/down

counter

IN0 to IN3

OC0 to OC7

SDA

SCL

AIN0, AIN1

BIN0, BIN1

ZIN0, ZIN1

MB91F355A/MB91F357B MB91F356B MB91355A MB91354A

ROM/Flash 512 Kbytes (Flash) 256 Kbytes (Flash) 512 Kbytes 384 Kbytes

RAM (stack) 16 Kbytes 16 Kbytes 16 Kbytes 8 Kbytes

RAM (Execute instruction) 8 Kbytes 8 Kbytes 8 Kbytes 8 Kbytes

29

MB91350A Series

■ CPU AND CONTROL UNIT

Internal architecture

The FR family CPU is a high performance core based on a RISC architecture while incorporating advanced

instructions for embedded controller applications.

1. Features

• RISC architecture

Basic instructions : Executed at 1 instruction per cycle

• 32-bit architecture

General-purpose registers : 32-bit × 16 registers

• 4GB linear memory space

• Built-in multiplier

32-bit × 32-bit multiplication : 5 cycles

16-bit × 16-bit multiplication : 3 cycles

• Enhanced interrupt handling

Fast response speed (6 cycles)

Multiple interrupts supported

Level masking (16 levels)

• Enhanced I/O manipulation instructions

Memory-to-memory transfer instructions

Bit manipulation instructions

• High code efficiency

Basic instruction word length : 16-bit

• Low-power consumption

Sleep mode and stop mode

• Gear function

30

MB91350A Series

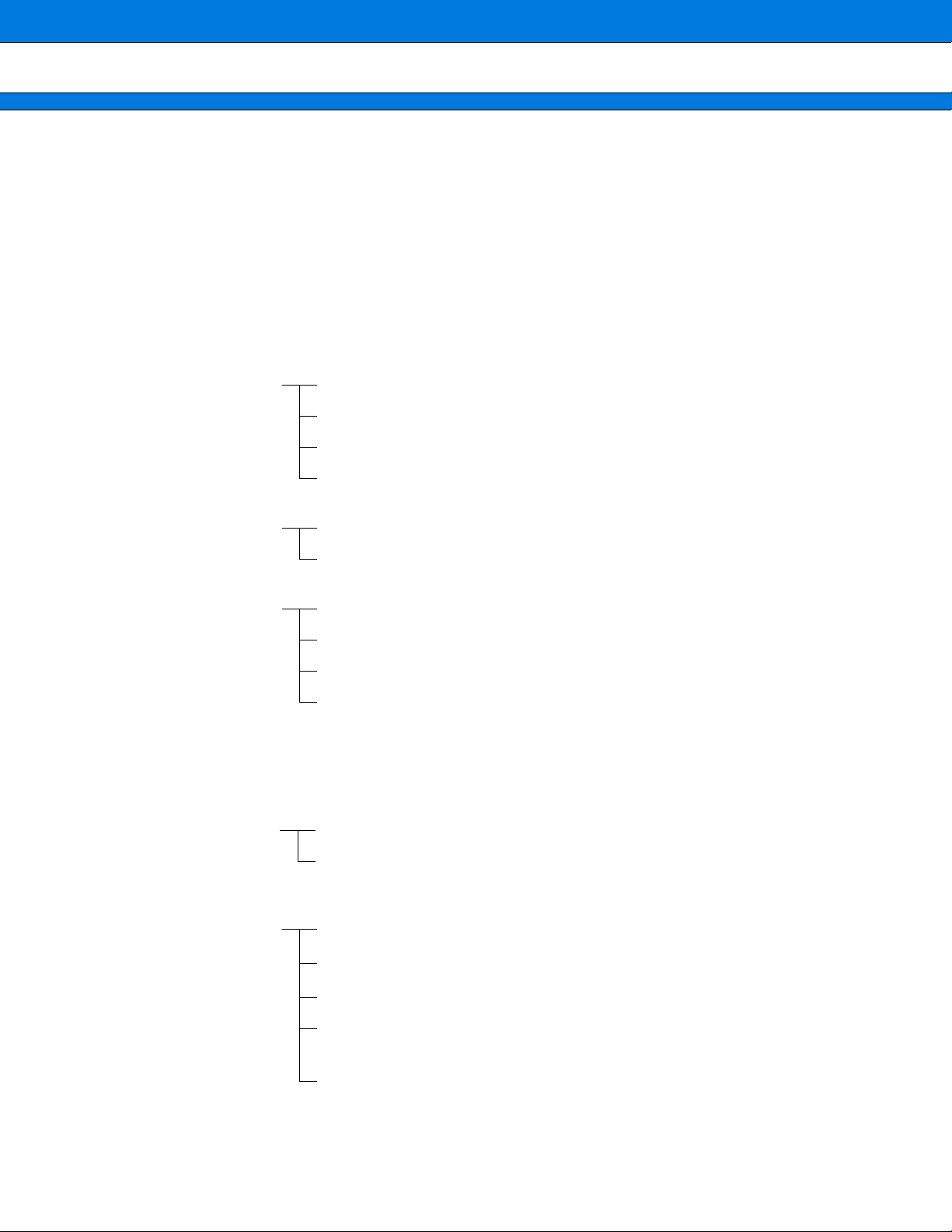

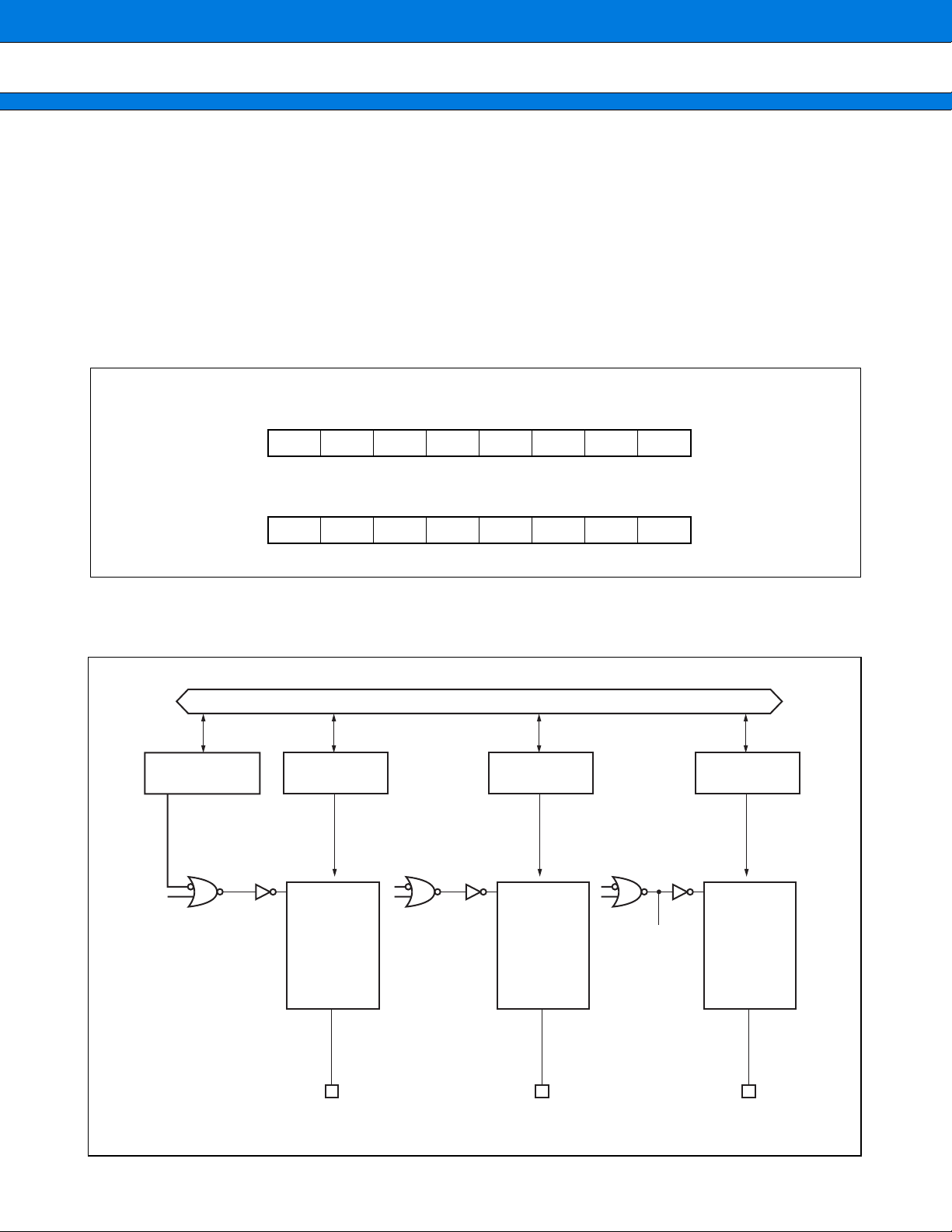

2. Internal architecture

The FR-family CPU has a Harvard architecture in which the instruction and data buses are separated. A

32-bit ↔ 16-bit bus converter is connected to the 32-bit bus (F-bus), providing an interface between the CPU

and peripheral resources. A Harvard ↔ Princeton bus converter is connected to both the I-bus and D-bus,

providing an interface between the CPU and the bus controller.

FR CPU

D-bus I-bus

32

Data

RAM

32-bit

16-bit

bus converter

16

D address

D data

Address

Data

I address

I data

32

32

32

32

32

Harvard

Princeton

bus

converter

External address

24

External data

16

R-bus

Peripheral resources Internal I/O bus controller

F-bus

31

MB91350A Series

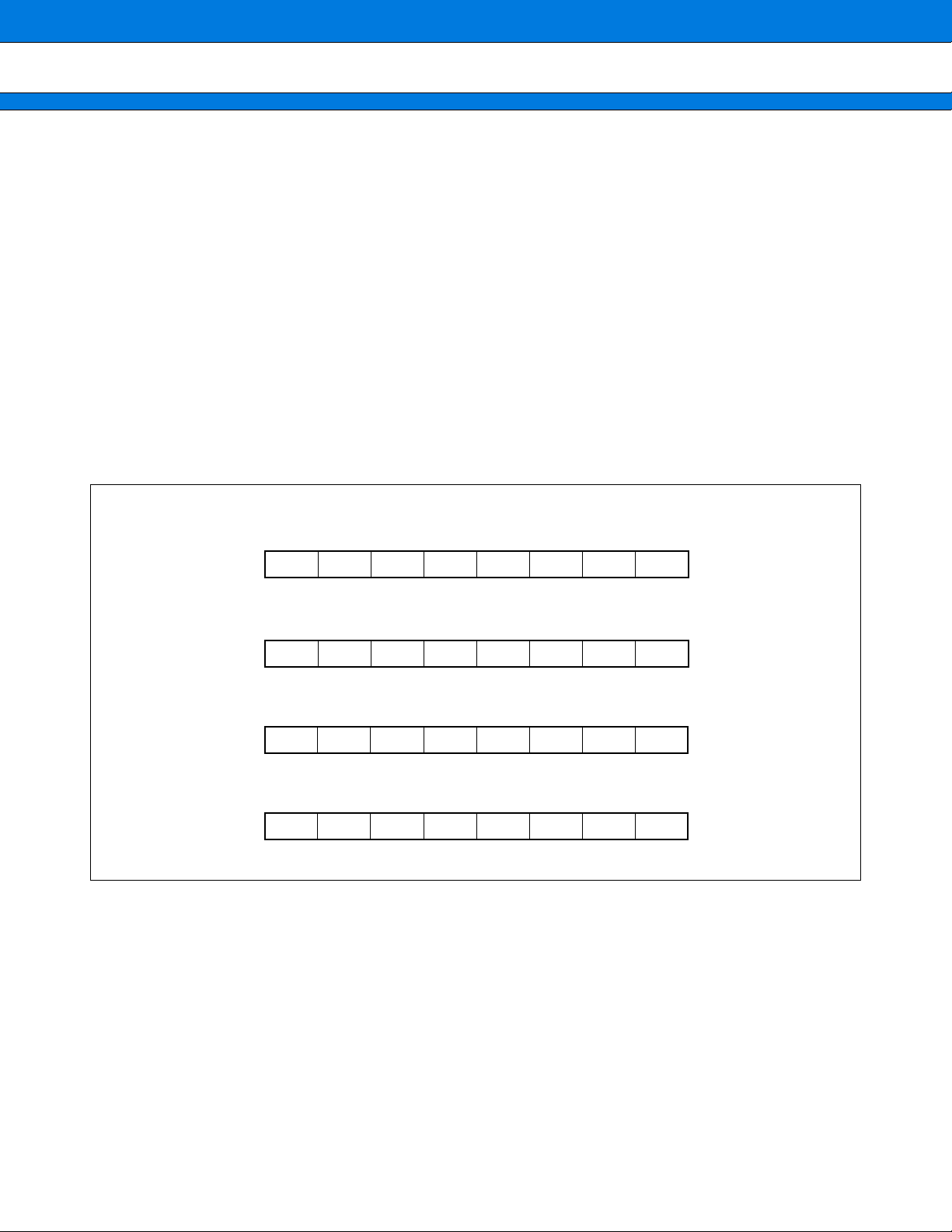

3. Programming model

• Basic programming model

32-bit

[Initial Value]

GENERAL

PURPOSE

REGISTERS

Program counter

Program status

Table base register

Return pointer

System stack pointer

User stack pointer

R0

R1

R12

R13

R14

R15

PC

PS

TBR

RP

SSP

USP

AC

FP

SP

⎯ ILM ⎯ SCR CCR

XXXX XXXXH

XXXX XXXXH

0000 0000H

32

Multiplication and division

result registers

MDH

MDL

4. Registers

• General purpose registers

MB91350A Series

32-bit

[Initial Value]

R0

R1

R12

R13

R14

R15

AC

FP

SP

XXXX XXXXH

XXXX XXXXH

0000 0000H

Registers R0 to R15 are general-purpose registers. The registers are used as the accumulator and memory

access pointers for CPU operations.

Of these 16 registers, the registers listed below are intended for special applications. Some instructions have

been enhanced for this purpose.

R13 : Virtual accumulator

R14 : Frame pointer

R15 : Stack pointer

The initial values of R0 to R14 after a reset are indeterminate. R15 is initialized to 00000000

H (SSP value).

• PS (Program Status)

This register holds the program status and is divided into the ILM, SCR, and CCR.

The undefined bits in the following illustration are all reserved bits. Reading these bits always returns “0”. Writing

to them has no effect.

bit 31 bit 20 bit 16

PS

ILM SCR CCR

bit 10 bit 7bit 8 bit 0

⎯⎯

33

MB91350A Series

• CCR (Condition Code Register)

CCR

bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

⎯⎯ SINZVC

Initial Value

- - 00XXXX

B

S : Stack flag. Cleared to “0” by a reset.

I : Interrupt enable flag. Cleared to “0” by a reset.

N : Negative flag. The initial value after a reset is indeterminate.

Z : Zero flag. The initial value after a reset is indeterminate.

V : Overflow flag. The initial value after a reset is indeterminate.

C : Carry flag. The initial value after a reset is indeterminate.

• SCR (System Condition Code Register)

bit 10 bit 9 bit 8

SCR XX0

D1 D0 T

Initial Value

B

Flag for stepwise division

Stores intermediate data for stepwise division operations.

Step trace trap flag

A flag specifying whether the step trace trap function is enabled or not.

The step trace trap function is used by the emulator. This function cannot be used by a user program while

using the emulator.

• ILM

bit 20 bit 19 bit 18 bit 17 bit 16

ILM4 ILM3 ILM2 ILM1 ILM0

ILM 01111

Initial Value

B

This register stores the interrupt level mask value. The value in the ILM register is used as the level mask.

Initialized to “15” (01111B) by a reset.

• PC (Program Counter)

bit 31 bit 0

PC

Initial Value

XXXXXXXX

H

The program counter contains the address of the instruction currently being executed.

The initial value after a reset is indeterminate.

• TBR (Table Base Register)

bit 31 bit 0

TBR

Initial Value

000FFC00

H

The table base register contains the start address of the vector table used for handling EIT events.

The initial value after a reset is 000FFC00

H.

34

• RP (Return Pointer)

MB91350A Series

bit 31 bit 0

RP

Initial Value

XXXXXXXX

H

The return pointer contains the address to which to return from a subroutine.

When the CALL instruction is executed, the value in the PC is transferred to the RP.

When the RET instruction is executed, the value in the RP is transferred to the PC.

The initial value after a reset is indeterminate.

• SSP (System Stack Pointer)

bit 31 bit 0

SSP

Initial Value

00000000

H

The SSP is the system stack pointer and functions as R15 when the S flag is “0”.

The SSP can be specified explicitly.

The SSP is also used as the stack pointer that specifies the stack for saving the PS and PC when an EIT event

occurs.

The initial value after a reset is 00000000

H.

• USP (User Stack Pointer)

bit 31 bit 0

USP

Initial Value

XXXXXXXX

H

The USP is the user stack pointer and functions as R15 when the S flag is “1”.

The USP can be specified explicitly.

The initial value after a reset is indeterminate.

This pointer cannot be used by the RETI instruction.

• Multiply & Divide Registers

bit 31 bit 0

MDH

MDL

These registers are 32-bit wide registers that store the results of multiplication and division operations.

The initial value after a reset is indeterminate.

35

MB91350A Series

■ MODE SETTINGS

The FR family uses mode pins (MD2 to MD0) and a mode register (MODR) to set the operation mode.

1. Mode Pins

The MD2, MD1, and MD0 pins specify how the mode vector fetch is performed.

Mode Pins

Mode name

MD2 MD1 MD0

0 0 0 internal ROM mode vector Internal

0 0 1 external ROM mode vector External

Values other than those listed in the table are prohibited.

2. Mode Register (MODR)

The data that is written to the mode register from the address at 000F FFF8H by the mode vector fetch is called

the mode data.

After the mode register (MODR) , has been set, the device operates according to the configured operating mode.

The mode register is set by all of the reset sources. User programs cannot write to the mode register.

Reset vector access

area

Remarks

The bus width is specified by the

mode register.

Note : No data exists at the address (0000 07FF

H) of the mode register in the previous FR family.

[Register description]

MODR Initial Value

000F FFF8

bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

H XXXXXXXXB

0 0 0 0 0 ROMA WTH1 WTH0

Operating mode setting bits

[bit7-bit3] Reserved bit

Always set these bits to “00000

B”. Operation is not guaranteed if these bits are set to a value other than “00000B”.

[bit2] ROMA (internal ROM enable bit)

The ROMA bit is used to set whether to enable the internal F-bus RAM and F-bus ROM areas.

ROMA Function Remarks

0

1

External ROM

mode

Internal ROM

mode

Internal F-bus RAM is valid; the area (8 0000

H to 10 0000H) of internal ROM is used

as an external area.

Internal F-bus RAM and F-bus ROM are valid.

[bit1, bit0] WTH1, WTH0 (Bus width setting bits)

Used to set the bus width to be used in external bus mode.

In external bus mode, the BW1 and BW0 bits of AMD0 (CS0 area) are set to the value of these bits.

WTH1 WTH0 function Remarks

0 0 8-bit bus width

external bus mode

0 1 16-bit bus width

10 ⎯ Setting prohibited

1 1 single chip mode single chip mode

36

MB91350A Series

■ MEMORY SPACE

1. Memory space

The FR family has 4 Gbytes of logical address space (232 addresses) available to the CPU by linear access.

• Direct Addressing Areas

The following address space areas are used as I/O areas.

These areas are called direct addressing areas. The addresses of operands in these areas can be specified

directly within an instruction.

The size of the directly addressable areas depends on the size of the data being accessed as shown below.

→ Byte data access : 000

H to 0FFH

→ Half word data access : 000H to 1FFH

→ Word data access : 000H to 3FFH

2. Memory Map

Memory Map of MB91F355A/F353A/F357B/355A/353A

0000 0000H

0000 0400H

0001 0000H

0003 E000H

0004 0000H

0004 4000H

0005 0000H

0008 0000H

Single chip

mode

I/O

I/O

Access

disabled

Built-in RAM

8 Kbytes

(Execute instruction)

Built-in RAM

16 Kbytes (Stack)

Access

disabled

Internal ROM

external bus mode

I/O

I/O

Access

disabled

Built-in RAM

8 Kbytes

(Execute instruction)

Built-in RAM

16 Kbytes (Stack)

Access

disabled

External area

External ROM

external bus mode

I/O

I/O

Access

disabled

Built-in RAM

8 Kbytes

(Execute instruction)

Built-in RAM

16 Kbytes (Stack)

Access

disabled

Direct

addressing area

Refer to

“■ I/O MAP”.

Built-in ROM

512 Kbytes

0010 0000H

Access

Built-in ROM

512 Kbytes

External area

External area

disabled

FFFF FFFFH

• Each mode is set depending on the mode vector fetch after INIT

is negated.

• The available area of internal RAM is restricted immediately after a reset is released. At least one NOP

instruction is required immediately after overwriting the setting for the available RAM area.

37

MB91350A Series

Memory Map of MB91354A

0000 0000

0000 0400

0001 0000

0003 E000

0004 0000

0004 2000

0005 0000

0008 0000

000A 0000

0010 0000

Single chip mode

H

H

H

H

H

H

H

H

H

Access

disabled

Built-in RAM

8 Kbytes

(Execute instruction)

Built-in RAM

8 Kbytes (Stack)

Access

disabled

Built-in ROM

384 Kbytes

H

Access

disabled

I/O

I/O

Internal ROM

external bus mode

I/O

I/O

Access

disabled

Built-in RAM

8 Kbytes

(Execute instruction)

Built-in RAM

8 Kbytes (Stack)

Access

disabled

External area

Access

disabled

Built-in ROM

384 Kbytes

External area

External ROM

external bus mode

I/O

I/O

Access

disabled

Built-in RAM

8 Kbytes

(Execute instruction)

Built-in RAM

8 Kbytes (Stack)

Access

disabled

External area

Direct

addressing area

Refer to “■ I/O MAP”.

FFFF FFFF

• Each mode is set depending on the mode vector fetch after INIT

H

is negated.

• The available area of internal RAM is restricted immediately after a reset is released. At least one NOP

instruction is required immediately after overwriting the setting for the available RAM area.

38

Memory Map of MB91352A

MB91350A Series

0000 0000H

0000 0400H

0001 0000H

0003 E000H

0004 0000H

0004 2000H

0005 0000H

000A 0000H

0010 0000H

Single chip

mode

I/O

I/O

Access

disabled

Built-in RAM

8 Kbytes

(Execute instruction)

Built-in RAM

8 Kbytes (Stack)

Access

disabled

Built-in ROM

384 Kbytes

Access

disabled

Internal ROM

external bus mode

I/O

I/O

Access

disabled

Built-in RAM

8 Kbytes

(Execute instruction)

Built-in RAM

8 Kbytes (Stack)

Access

disabled

External area

Built-in ROM

384 Kbytes

External area

External ROM

external bus mode

I/O

I/O

Access

disabled

Built-in RAM

8 Kbytes

(Execute instruction)

Built-in RAM

8 Kbytes (Stack)

Access

disabled

External area

Direct

addressing area

Refer to

“■ I/O MAP”.

FFFF FFFFH

• Each mode is set depending on the mode vector fetch after INIT

is negated.

• The available area of internal RAM is restricted immediately after a reset is released. At least one NOP

instruction is required immediately after overwriting the setting for the available RAM area.

39

MB91350A Series

Memory Map of MB91351A

0000 0000H

0000 0400H

0001 0000H

0003 E000H

0004 0000H

0004 4000H

0005 0000H

000A 0000H

0010 0000H

Single chip

mode

I/O

I/O

Access

disabled

Built-in RAM

8 Kbytes

(Execute instruction)

Built-in RAM

16 Kbytes (Stack)

Access

disabled

Built-in ROM

384 Kbytes

Access

disabled

Internal ROM

external bus mode

I/O

I/O

Access

disabled

Built-in RAM

8 Kbytes

(Execute instruction)

Built-in RAM

16 Kbytes (Stack)

Access

disabled

External area

Built-in ROM

384 Kbytes

External area

External ROM

external bus mode

I/O

I/O

Access

disabled

Built-in RAM

8 Kbytes

(Execute instruction)

Built-in RAM

16 Kbytes (Stack)

Access

disabled

External area

Direct

addressing area

Refer to

“■ I/O MAP”.

FFFF FFFFH

• Each mode is set depending on the mode vector fetch after INIT

is negated.

• The available area of internal RAM is restricted immediately after a reset is released. At least one NOP

instruction is required immediately after overwriting the setting for the available RAM area.

40

Memory Map of MB91F356B

MB91350A Series

0000 0000

0000 0400

0001 0000

0003 E000

0004 0000

0004 4000

0005 0000

0008 0000

000C 0000

0010 0000

FFFF FFFF

Single chip mode

H

H

H

H

H

H

H

Access

disabled

Built-in RAM

8 Kbytes

(Execute instruction)

Built-in RAM

16 Kbytes (Stack)

Access

disabled

H

H

Built-in ROM

H

256 Kbytes

Access

disabled

H

I/O

I/O

Internal ROM

external bus mode

I/O

I/O

Access

disabled

Built-in RAM

8 Kbytes

(Execute instruction)

Built-in RAM

16 Kbytes (Stack)

Access

disabled

External area

Access

disabled

Built-in ROM

256 Kbytes

External area

External ROM

external bus mode

I/O

I/O

Access

disabled

Built-in RAM

8 Kbytes

(Execute instruction)

Built-in RAM

16 Kbytes (Stack)

Access

disabled

External area

Direct

addressing area

Refer to “■ I/O MAP”.

• Each mode is set depending on the mode vector fetch after INIT

is negated.