Page 1

FUJITSU SEMICONDUCTOR

CONTROLLER MANUAL

MB91191/MB91192 Series

CM71-10113-1E

FR20

32-Bit Micro Controller

Hardware Manual

Page 2

Page 3

FR20

32-Bit Micro Controller

MB91191/MB91192 Series

Hardware Manual

FUJITSU LIMITED

Page 4

Page 5

PREFACE

■ Purpose of This Document and Intended Reader

The MB91191/MB91192 are developed as one of the "32-bit single-chip microcontroller FR20 series"

around the new RISC architecture CPU as its cores, and the specifications for these products are optimized

for structures on which high-performance CPU processing power is required.

The functions and operations of the MB91191/MB91192 are described in this document specifically for

engineers who actually develop products using the MB91191 and MB91192. Please read through this

manual. For more information on various instructions, refer to "Instruction Manual".

Trademarks

■ Trademarks

FR is the abbreviation of FUJITSU RISC controller, which is a product of Fujitsu LIMITED.

Embedded Algorithm TM is a registered trademark of Advanced Micro Devices, Inc.

Other system and product names used in this manual are trademarks of the related companies and

organizations.

i

Page 6

■ Organization of This Document

This manual contains the following 21 chapters and an appendix.

CHAPTER 1 Overview of MB91191/MB91192 Series

This chapter includes basic explanations including features of the MB91191/MB91192 series, block

diagrams, and a function outline.

CHAPTER 2 Handling Devices

This chapter describes points to note when using the MB91191/MB91192 series.

CHAPTER 3 CPU

This chapter provides basic explanations for such elements as the architecture, specifications, and

commands, etc., required to understand the CPU core functions of the FR series.

CHAPTER 4 External Bus Interface

This chapter describes an outline of the external bus interface, the register configuration/fun ctions, the

bus operation, and the bus timing, and program examples for the bus operation are explained.

CHAPTER 5 I/O Port

This chapter describes an outline of the I/O port and the register configuration/functions.

CHAPTER 6 FG Input

This chapter describes an outline of the FG input section, the register configuration/fu nctions, and their

operation.

CHAPTER 7 FRC Capture

This chapter describes an outline of the FRC capture section, the register configuratio n/functions, and

each input section operation.

CHAPTER 8 Programmable Pulse Generator (PPG0, 1)

This chapter describes an outline of the programmable pulse generator (PPG0, 1), the register

configuration/functions, and their operation.

CHAPTER 9 Real Timing Generator (RTG)

This chapter describes an outline of the real timing generator (RTG), the register configuration/

functions, and their operation.

CHAPTER 10 Timer

This chapter describes an outline of the timer section, the register configuration/functions, and timer

section operation.

CHAPTER 11 12-bit PWM

This chapter describes an outline of the PWM, the register configuration/functions, and the PWM

operations.

CHAPTER 12 8-bit Pulse Width Counter

This chapter describes an outline of the 8-bit pulse width counter, the register configuration/functions,

and 8-bit pulse width counter operations.

CHAPTER 13 External Interrupt

External interrupt comprises of the key input interrupt and external interrupt sections. This chapter

describes an outline of the external interrupt 1 (key input circuit) and exter nal interrupt (INT0 to 2), and

the register configuration/functions, and their operation.

ii

Page 7

CHAPTER 14 Delayed Interrupt Module

This chapter describes an outline of the delayed interrupt m odule, the register configuration/functions,

and delayed interrupt module operations.

CHAPTER 15 Interrupt Controller

This chapter describes an outline of the interrupt controller, the register configuration/functions, and the

interrupt controller operations.

CHAPTER 16 10-bit A/D Converter

This chapter describes an outline of th e 10-bit A/D converter, the regi ster configuration/functions, and

the 10-bit A/D converter operations.

CHAPTER 17 Serial I/O

This chapter describes an outline of the serial I/O, the register configuration/functions, and the serial

data RAM and serial I/O operations.

CHAPTER 18 10-bit General-purpose Prescaler

This chapter describes an outline of the 10-bit general-purpose prescaler, the register configuration/

functions, and the 10-bit general-purpose prescaler operations.

CHAPTER 19 Bit Search Module

This chapter describes an outline of the bit search m odule, the register configuration/functions, the bit

search module operations, and save/return processes.

CHAPTER 20 Wait Controller

This chapter describes an outline of the wait control section, and the register configuration/functions.

CHAPTER 21 Flash Memory

This chapt er de sc ribe s an outl ine of th e fl ash mem ory , the register configuration/functions and the flash

memory operations.

Appendix

Details that could not be described within the body text, such as I/O map, interrupt vector, peripheral

circuit measurement speed, restrictions and commands list for us e o f th e M B 9119 1 /M B 9119 2 s erie s ar e

described in the appendix.

iii

Page 8

• The contents of this document are subject to change without notice. Customers are advised to consult with

FUJITSU sales representatives before ordering.

• The information, su ch as des criptions o f function an d applicat ion circuit examples, in this d ocument are pres ented

solely for the purpose of reference t o show examples of operations and us es of FUJITSU semiconductor device;

FUJITSU does not warrant proper operation of the device with respect to use based on such information. When you

develop equipment incorporating the device based on such information, you must assume any responsibility arising

out of such use of the information. FUJITSU assumes no liability for any damages whatsoever arising out of the

use of the information.

• Any information in this document, including descriptions of function and schematic diagrams, shall not be

construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or

any other right of FUJITSU or any third party or does FUJITSU warrant non-infringement of any third-party's

intellectual property right or other right by using such information. FUJITSU assumes no liability for any

infringement of the intellectual property rights or other rights of third parties which would result from the use of

information co ntained herein.

• The products d escribed in this document a re designed, developed and ma nufactured as contemplated for general

use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but

are not designed, de veloped and manufactured as cont emplated (1) for use accompanying fatal risks or dangers

that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to

death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility,

aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control

in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial

satellite). Please note that FUJITSU will not be liable against you and/or any third party for any claims or damages

arising in connection with above-mentioned uses of the products.

• Any semiconduct or devices have an inheren t chance of failure. You must protect against injury, da mage or loss

from such failures by incorporating safety design measures into your facility and equipment such as redundancy,

fire protection, and prevention of over-cu rr e nt leve ls an d oth er abnormal operating conditions.

• If any products described in this document represent goods or technologies subject to certain restrictions on export

under the Foreig n Exchan ge and Fore ign Trad e Law o f Japan, the pri or aut horizat ion by Japanese govern ment wil l

be required for export of those products from Japan.

Copyright© 2004 FUJITSU LIMITED All rights reserved

iv

Page 9

How to Read This Document.

■ Format of This Book

The explanation concerning the main term used in this book is shown as follows.

Term Meaning

I-bus It is a bus of the widt h o f 16 bits for an intern al ins truction . Becaus e the FR20 series has

adopted internal Harvard Architecture, the instruction and data are the independent

buses. The bus converter is connected with I-BUS.

D-bus It is a data bus of the width of the internal 32 bits. An internal resource is con nected

with D-bus.

C-bus It is an internal multiplex bus. The C-bus connects to the I-bus and D-bus via the switch.

The external interface module is connected with C-BUS. The external data bus

multiplexes data and instructions.

R-bus It is a data bus of the width of the internal 16 bits. R-bus is connected with D-bus

through the adaptor.

Various I/O, the clock generation block, and the interruption controller are connected

with R-bus.

The R-bus is 16-bit width, so the address and data are multiplexed. If the CPU accesses

these resources, it takes a number of cycles.

E-unit It is an operation execution unit.

φ It is a system clock. It is a clock output from the clock generation block to the each

internal resource connected with R-bus. The system clock at the highest speed shows

the same cycle as source oscillation but is divided into 1, 1/2, 1/4, and 1/8 (or 1/2, 1/4,

1/8, and 1/16) by PCK1 and PCK0 of the clock generator GCR register.

θ It is a system clock. It is an operation clock of resource and CPU connected with buses

other than R-bus.

The system clock at the highest speed shows the same cycle as source oscillation but is

divided into 1, 1/2, 1/4, and 1/8 (or 1/2, 1/4, 1/8, and 1/16) by CCK1 and CCK0 of the

clock generator GCR register.

v

Page 10

vi vii

Page 11

CONTENTS

CHAPTER 1 Overview of MB91191/MB91192 Series ..................................................... 1

1.1 Feature of MB91191/MB91192 Series ............................................................................................... 2

1.2 Block Diagram of All MB91191/MB91192 Series ............................................................................... 4

1.3 Package Dimension ............................................................................................................................ 5

1.4 Pin Assignment ................................................................................................................................... 7

1.5 Pin Function Description ..................................................................................................................... 9

1.6 I/O Circuit Type ................................................................................................................................ . 15

CHAPTER 2 Handling Devices ...................................................................................... 17

2.1 Precautions When Handling Devices ............................................................................................... 18

2.2 Others .......................... ................................................................. .................................................... 22

CHAPTER 3 CPU ............................................................................................................ 23

3.1 Memory Space .................................................................................................................................. 24

3.2 CPU Architecture ....................................................................................................................... ....... 26

3.3 Dedicated Registers ......................................................................................................................... 29

3.3.1 Program Status Register (PS) ..................................................................................................... 32

3.4 General-purpose Register ................................................................................................................ 36

3.5 Data Construction ............................................................................................................................. 37

3.6 Word Alignment ................................................................................................................................ 38

3.7 Memory Map .............................................................................................................................. ....... 39

3.8 Overview of Instructions ................................................................................................................... 40

3.8.1 Branch Command with Delay Slot ............................................................................................... 42

3.8.2 Branch Command without Delay Slot .......................................................................................... 44

3.9 EIT (Exception, Interruption, and Trap) ............................................................................................ 45

3.9.1 Interrupt Level of EIT ...................................................................................................... ...... ....... 46

3.9.2 Interrupt Stack Operation ............................................................................................................ 47

3.9.3 EIT Vector Table .......................................................................................................................... 48

3.9.4 Multiple EIT Processing ............................................................................................................... 49

3.9.5 Operation of EIT ................................................................................................................... ....... 51

3.10 Reset Sequence .................................... ....................................... ...... ....... ...... ....... ...... . ...... ...... ....... 55

3.11 Memory Access Mode ............................................................................................................... ....... 56

3.12 Clock Generation Section (Low Power Consumption Mechanism) .................................................. 59

3.12.1 Reset Factor Register (RSRR) and Watchdog Timer Cycle Control Register (WTCR) ............... 61

3.12.2 Standby Control Register (STCR) ............................................................................................... 63

3.12.3 Timebase Timer Clear Register (CTBR) ..................................................................................... 64

3.12.4 Gear Control Register (GCR) ...................................................................................................... 65

3.12.5 Watchdog Reset Generation Delay Register (WPR) ................................................................... 67

3.12.6 Reset Factor Retention .. ....................................... ...... ...... ....... ...... ....... ...... .......................... ....... 68

3.12.7 Stop Status .................................................................................................................................. 70

3.12.8 Sleep Status ......................................................................................................................... ....... 73

3.12.9 State Transition in Standby Mode ............................................................................................... 76

3.12.10 Gear Function ................................................................................................................. ...... ....... 77

3.12.11 Clock Series Diagram .................................................................................................................. 80

Page 12

3.12.12 Clock Series of Peripheral Resource ........................................................................................... 81

3.12.13 Watchdog Function ...................................................................................................................... 82

CHAPTER 4 External Bus Interface .............................................................................. 85

4.1 Overview of External Bus Interface .................................................................................................. 86

4.2 Block Diagram ....... ...... ....... ...... ....... ...... ....................................... ...... ....... ...... ....... ...... ....... ...... ....... 87

4.3 Area of Bus Interface ........................................................................................................................ 88

4.4 Bus Interface ........................................................................................................................ ...... ....... 89

4.5 Register of External bus Interface .................................................................................................... 90

4.5.1 Area Selection Register (ASR) and Area Mask Register (AMR) ................................................. 91

4.5.2 Area Mode Register 1 (AMD1) .................................................................................................... 94

4.5.3 Little Endian Register (LER) ........................................................................................................ 96

4.6 Bus Operation ............................................................................................................................ ....... 97

4.6.1 Relationship between Data Bus Width and Control Signal .......................................................... 98

4.6.2 Bus Access of Big Endian ........................................................................................................... 99

4.6.3 Bus Access of Little Endian ....................................................................................................... 104

4.6.4 Comparison between Big Endian and Little Endian for External Access .................................. 108

4.7 Bus Timing ...................................................................................................................................... 112

4.8 Program Example of External Bus Operation ................................................................................. 113

CHAPTER 5 I/O Port ..................................................................................................... 117

5.1 Overview of I/O Port ....................................................................................................................... 118

5.2 Port 0 .............................................................................................................................................. 119

5.3 Port 1 .............................................................................................................................................. 121

5.4 Port 2, 3 .......................................................................................................................................... 123

5.5 Port 5 .............................................................................................................................................. 125

5.6 Port 6, 7 .......................................................................................................................................... 127

5.7 Port 4, 8, 9 ...................................................................................................................................... 131

5.8 Port A, B ......................................................................................................................................... 135

5.9 Port C, D ......................................................................................................................................... 137

CHAPTER 6 FG Input ................................................................................................... 141

6.1 Overview of FG Input ...................................................................................................................... 142

6.2 Capstan Input ................................................................................................................................. 143

6.3 Drum Input ....................................................................... ...... ....... ...... ....... ...... ....... ........................ 148

6.4 Reel Input ....................................................................................................................................... 152

CHAPTER 7 FRC Capture ............................................................................................ 157

7.1 Overview of FRC Capture ............................................................................................................... 158

7.2 Register of FRC Capture ................................................................................................................ 160

7.3 Operation of FRC Capture .............................................................................................................. 165

CHAPTER 8 Programmable Pulse Generator (PPG0, 1) ........................................... 167

8.1 Overview of Programmable Pulse Generator (PPG0, 1) ................................................................ 168

8.2 Register of Programmable Pulse Generator (PPG0, 1) .................................................................. 171

8.3 PPG Data RAM ............................................................................................................................... 173

8.4 Configuration of Frame Data .......................................................................................................... 174

viii

Page 13

8.5 Operation of PPG ........................................................................................................................... 175

CHAPTER 9 Real Timing Generator (RTG) ................................................................ 177

9.1 Overview of Real Timing Generator (RTG) .................................................................................... 178

9.2 Register of Real Timing Generator (RTG) ...................................................................................... 181

9.3 Operation of Real Timing Generator (RTG) .................................................................................... 183

CHAPTER 10 Timer ........................................................................................................ 185

10.1 Overview of Timer ........................................................................................................................... 186

10.2 Overview of 16-bit Timer (Timer 0 to 4) .......................................................................................... 188

10.3 Register of 16-bit Timer (Timer 0 to 4) ............................................................................................ 190

10.4 Operation of 16-bit Timer (Timer 0 to 4) ......................................................................................... 193

10.5 Overview of 8-/16-bit Timer/Counter ............................................................................................... 195

10.6 Register of 8-/16-bit Timer/Counter ................................................................................................ 197

10.7 Operation of 8-/16-bit Timer/Counter .............................................................................................. 201

CHAPTER 11 12-bit PWM ............................................................................................... 203

11.1 Overview of 12-bit PWM ................................................................................................................. 204

11.2 Register of 12-bit PWM ................................................................................................................... 206

11.3 Operation of 12-bit PWM ................................................................................................................ 208

CHAPTER 12 8-bit Pulse Width Counter ...................................................................... 211

12.1 Overview of 8-bit Pulse Width Counter ........................................................................................... 212

12.2 Register of 8-bit Pulse Width Counter ............................................................................................ 213

12.3 Operation of 8-bit Pulse Width Counter .......................................................................................... 215

CHAPTER 13 External Interrupt .................................................................................... 217

13.1 Overview of External Interrupt ........................................................................................................ 218

13.2 External Interrupt 1 (Key Input Circuit) ........................................................................................... 219

13.3 External Interrupt (INT0 to 2) .......................................................................................................... 221

CHAPTER 14 Delayed Interrupt Module ....................................................................... 225

14.1 Overview of Delayed Interrupt Module ........................................................................................... 226

14.2 Delayed Interrupt Control Register (DICR) ..................................................................................... 227

14.3 Operation of Delayed Interrupt Module ........................................................................................... 228

CHAPTER 15 Interrupt Controller ................................................................................. 229

15.1 Overview of Interrupt Controller ...................................................................................................... 230

15.2 Interrupt Control Register (ICRxx) .................................................................................................. 232

15.3 Operation of Interrupt Controller ..................................................................................................... 233

CHAPTER 16 10-bit A/D Converter ............................................................................... 237

16.1 Overview of 10-bit A/D Converter ................................................................................................... 238

16.2 Register of 10-bit A/D Converter ..................................................................................................... 239

16.3 Operation of 10-bit A/D Converter .................................................................................................. 245

16.4 State Transition of 10-bit A/D Converter ......................................................................................... 247

ix

Page 14

CHAPTER 17 Serial I/O .................................................................................................. 249

17.1 Overview of Serial I/O ..................................................................................................................... 250

17.2 Register of Serial I/O ...................................................................................................................... 252

17.3 Serial Data RAM ............................................................................................................................. 256

17.4 Operation of Serial I/O .................................................................................................................... 257

CHAPTER 18 10-bit General-purpose Prescaler ......................................................... 261

18.1 Overview of 10-bit General-purpose Prescaler ............................................................................... 262

18.2 Register of 10-bit General-purpose Prescaler ................................................................................ 263

18.3 Operation of 10-bit General-purpose Prescaler .............................................................................. 265

CHAPTER 19 Bit Search Module ................................................................................... 267

19.1 Overview of Bit Search Module ...................................................................................................... 268

19.2 Register of Bit Search Module ........................................................................................................ 269

19.3 Operation of Bit Search Module ...................................................................................................... 271

CHAPTER 20 Wait Controller ........................................................................................ 275

20.1 Outline of Wait Control Section ....................................................................................................... 276

20.2 Wait Control Register (WAITC) ....................................................................................................... 277

CHAPTER 21 Flash Memory .......................................................................................... 279

21.1 Overview of Flash Memory ............................................................................................................. 280

21.2 Flash Memory Status Register (FSTR) .. ....... ...... ....... ...... ...... ....... ...... ....................................... ..... 284

21.3 Operation of Flash Memory ............................................................................................................ 286

21.4 Flash Memory Auto Algorithm (Embedded Al gorithm TM) ..................................... ...... ....... ...... ..... 288

21.5 Auto Algorithm Execute State ......................................................................................................... 292

APPENDIX ......................................................................................................................... 297

Appendix A I/O Map ................................................................................................................................ 298

Appendix B Interrupt vector ..................................................................................................................... 306

Appendix C Measurement accuracy of peripheral circuit ........................................................................ 308

Appendix D Restrictions for Using MB91191/MB91192 series ............................................................... 309

Appendix E Instruction List ...................................................................................................................... 310

E.1 Instruction list of FR series ............................................................................................................. 314

x

Page 15

CHAPTER 1

Overview of MB91191/

MB91192 Series

This chapter includes basic explanations including

features of the MB91191/MB91192 series, block

diagrams, and a function outline.

1.1 Feature of MB91191/MB91192 Series

1.2 Block Diagram of All MB91191/MB91192 Series

1.3 Package Dimension

1.4 Pin Assignment

1.5 Pin Function Description

1.6 I/O Circuit Type

1

Page 16

CHAPTER 1 Overview of MB91191/MB91192 Series

1.1 Feature of MB91191/MB91192 Series

The MB91191/MB91192 series is a single-chip microcontroller with a built-in peripheral I/

O resource suited to software servo control of VTRs that require high-speed CPU

processing, featuring a 32-bit RISC-CPU (FR20 series) at its core.

■ Feature of MB91191/MB91192 Series

CPU

●

• 32-bit RISC (FR20), load/store architecture, 5 stages pipeline

• 32-bit general-purpose register x 16

• One instruction/one cycle, 16-bit fixed length instructions (basic instruction)

• Commands for memory to memory transfer, bit processing, and barrel shift, etc.: Commands suitable for

embedded applications

• Commands for function entry/exit, command for multi loading/storing of register contents: Commands

supporting high-level languages

• Register interlock function: Simplification of assembler description

• Branch instruction with a delay slot: Decrease of overhead for branch processing

• Support at internal into/instruction level of multipliers

- 32-bit multiplication with sign: 5 cycles

- 16-bit multiplication with sign: 3 cycles

• Interruption (save of PC and PS): 6 cycles and 16 priority levels

Bus interface

●

• 16-bit address output, 8-/16-bit data I/O

• Basic bus cycle: 2 clock cycle

• Support interface to various memories

• Multiplexed data/address input/output

• Auto-wait cycle: 0 to 7 cycles can be set randomly per area.

• Unused data and address pins can be used as I/O ports.

• Support of little endian mode

Bit search module

●

• 1-cycle search for the change bit position of the first 1/0 from the MSB within a word

Serial I/O

●

• Internal buffer RAM x 3ch (up to 128 bytes can be transferred automatically)

• Independent mode of the transmission/reception buffer (up to 64 bytes can be transferred automatically)

A/D converter (Successive Approximation Type)

●

• 10-bit x 16ch

• Successive appr oximation conversion method (conversion time: 8.4 µs @20MHz)

• Channel scan func tion

• Hardware and software conversion start functions

• Internal FIFO (Software conversion: 6 stages, Hardware conversion: 6 stages)

2

Page 17

Timer

●

• 16-bit x 4ch

• 16-bit timer/Counter x 1ch (with square wave output)

• 8-/16-bit timer/Counter x 1ch (with square wave output)

FG Input

●

• Incorporates capstan, drum, and reel input circuit

Capture

●

• Internal 24-bit free-run counter (Minimum resolution = 50ns@20 MHz)

• Internal FIFO (Data: 21-bit x 8, Detection: 8-bit x 8)

Programmable pules generator

●

• Internal buffer RAM (PPG0: 256 bytes, PPG1: 64 bytes)

• Output timing precision: 800 ns (@20 MHz)

• Includes an A/DC hardware start function

Real time timing generator

●

• RTG: incorporates 3 circuits

• Output timing precision: 400 ns/800 ns selectable

• Timing output ports: 5 ports

PWM

●

• 12-bit PWM x 6ch (rate, multi-type)

• Base frequency = 78.1 KHz/39.0 KHz (@20MHz) selectable

PWC

●

• 8-bit PWC x 1ch (with mask input)

• Measurement precision: 400 ns (@20 MHz)

General-purpose Prescaler

●

• 10-bit prescaler x 1ch (with square wave and pulse outputs)

• Dedicated internal oscillator circuit

• Includes load function driven by PPG output

Interrupt control

●

• External interrupt input: 3 inputs

• Key input interrupt: 8 inputs

3

Page 18

CHAPTER 1 Overview of MB91191/MB91192 Series

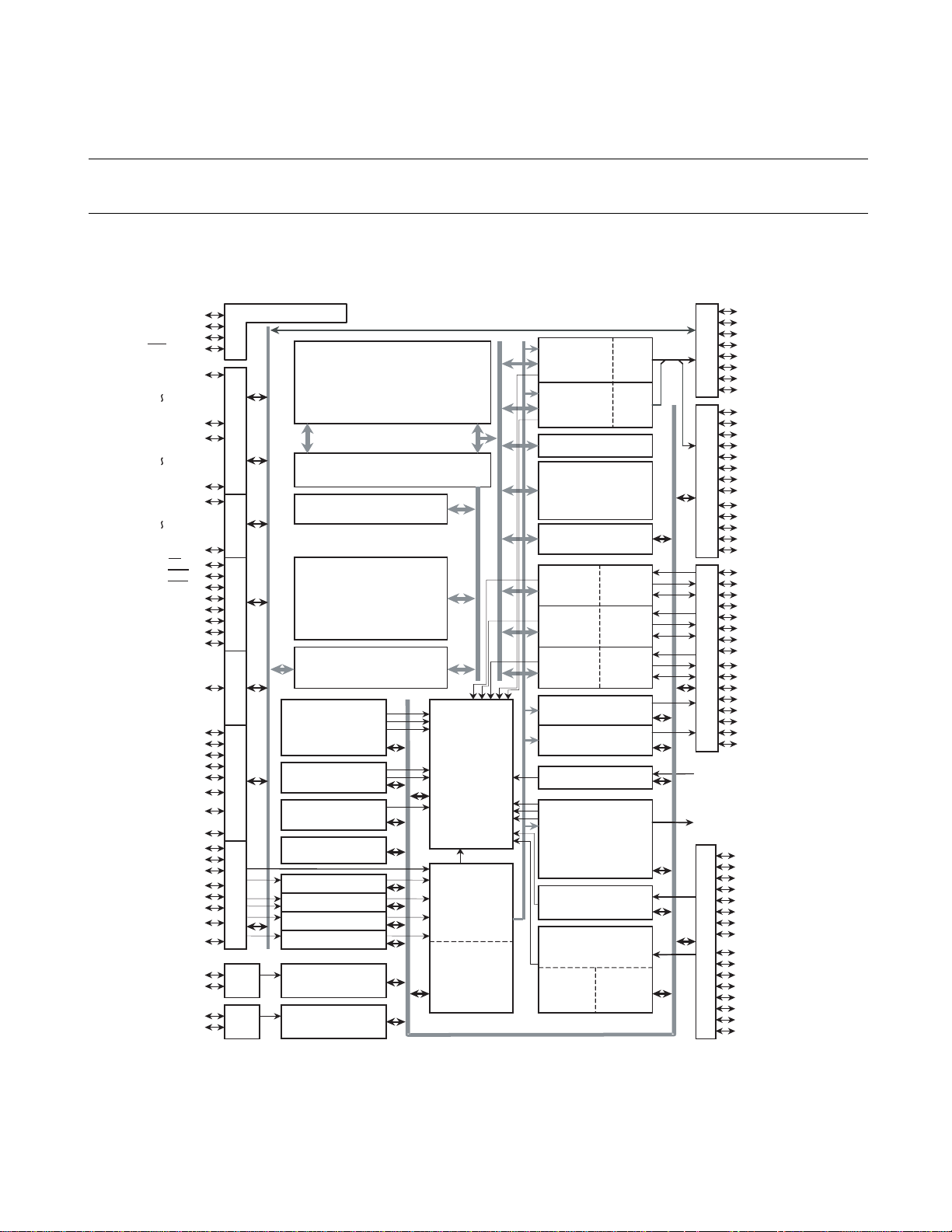

1.2 Block Diagram of All MB91191/MB91192 Series

Figure 1.2-1 shows the block diagram of all MB91191/MB91192 series.

■ Block Diagram of All MB91191/MB91192 Series

Figure 1.2-1 Block diagram of all MB91191/MB91192 series

MD0

MD1

MD2

RST

P37/D31

P30/D24

P27/D23

P20/D16

P57/A15

P50/A08

P60/RD

P61/WR0

P62/WR1

P63/ALE

P64

P65

P66/T5O1

P67/T4O

P70/XOUT

P17/RTO 4

P16/RTO 3

P15/RTO 2

P14/RTO 1

P13/RTO 0

P12/EC5/INT1

P11/EC4/INT0

P10/PMSK

P07/EXI 2/PMI

P06/EXI1

P05/EXI 0

P04/CFG

P03/DFG

PO2/DPG

P01/RFG0

P00/RFG1

OSCI

OSCO

XO

X1

Mode Control

P

O

R

T

2

/

3

P

O

R

T

5

P

O

R

T

6

P

O

R

T

7

P

O

R

T

1

P

O

R

T

0

OSC

OSC

FR20 CPU Core

I-bu s D-bus

I-bu s D-bus

RAM 2KB

MB91191R : ROM 254KB

MB91192 : ROM 384KB

MB91F191A: FLASH 254KB

MB91F192 : FLASH 384KB

External Bus CTL

16bit Timer0-3

Interrapt

8/16bit Timer

Controler

16bit Timer4

8bit PWC

CFG

DFG

RFG0

RFG1

fifo

C-unit

29bit x 8

10bit Programale

Prescaler

C-bus

24bit FRC

RAM 256Byte

RAM 64Byte

PPG0

PPG1

Bit Search

MB91191R :RAM 6KB

MB91192 :RAM 8KB

MB91F191A:RAM 6KB

MB91F192 :RAM 8KB

D-bus R-bus

Serial

RAM

128Byte

RAM

128Byte

RAM

128Byte

ch0

Serial

ch1

Serial

ch2

12bit PWM00-02

12bit PWM10-12

External-Interrapt

16bit RTGO-2

External-Interrapt

(Key input)

10bit A/DC

fifo

(soft)

fifo

(hard)

P

O

R

T

4

P

O

R

T

8

/

9

P

O

R

T

C

/

D

INT2-0 (from por t1,D )

RTO4-0 (t o port 1)

P

O

R

T

A

/

B

P47

P46/PPG18

P45/PPG17

P44/PPG16

P43/PPG15

P42/PPG14

P41/PPG13

P40/PPG12

P87/PPG11

P86/PPG10

P85/PPG09

P84/PPG08

P83/PPG07

P82/PPG06

P81/PPG05

P80/PPG04

P94/PPG03

P93/PPG02

P92/PPG01

P91/PPG00

P90/PO

PD0/SI2

PD1/SO2

PD2/SCK 2

PD3/SI1 /INT 2

PD4/SO1

PD5/SCK1

PD6/SCS0

PD7/SI0

PC0/SO0

PC1/SCK0

PC2/PWM 12/SCS1

PC3/PWM11/SCS2

PC4/PWM10

PC5/PWM02

PC6/PWM01

PC7/PWM00

PA7/AN-F/KEY7

PA6/AN-E/KEY6

PA5/AN-D/KEY5

PA4/AN-C/KEY4

PA3/AN-B/KEY3

PA2/AN-A/KEY2

PA1/AN-9 /KEY1

PA0/AN-8 /KEY0

PB7/AN-7

PB6/AN-6

PB5/AN-5

PB4/AN-4

PB3/AN-3

PB2/AN-2

PB1/AN-1

PB0/AN-0

4

Page 19

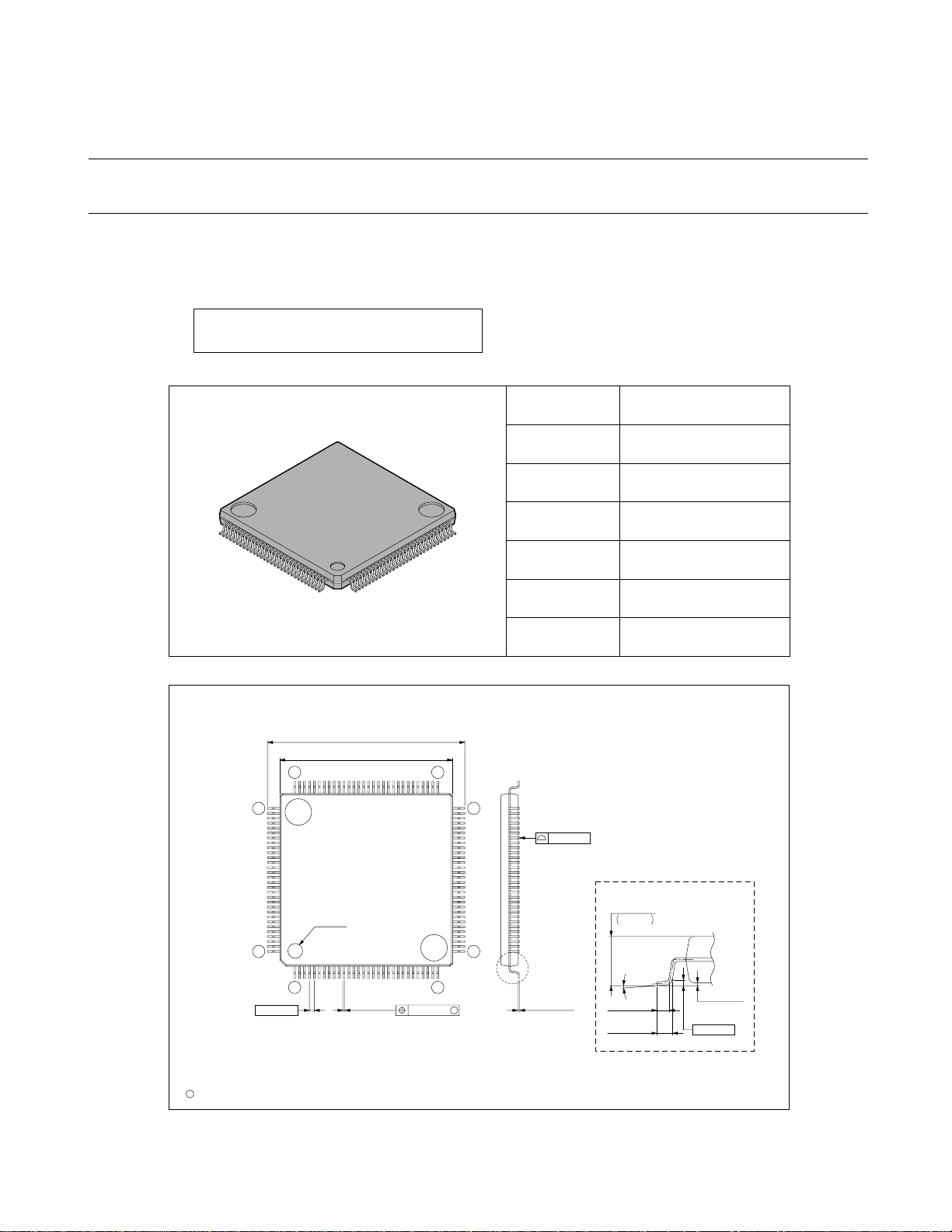

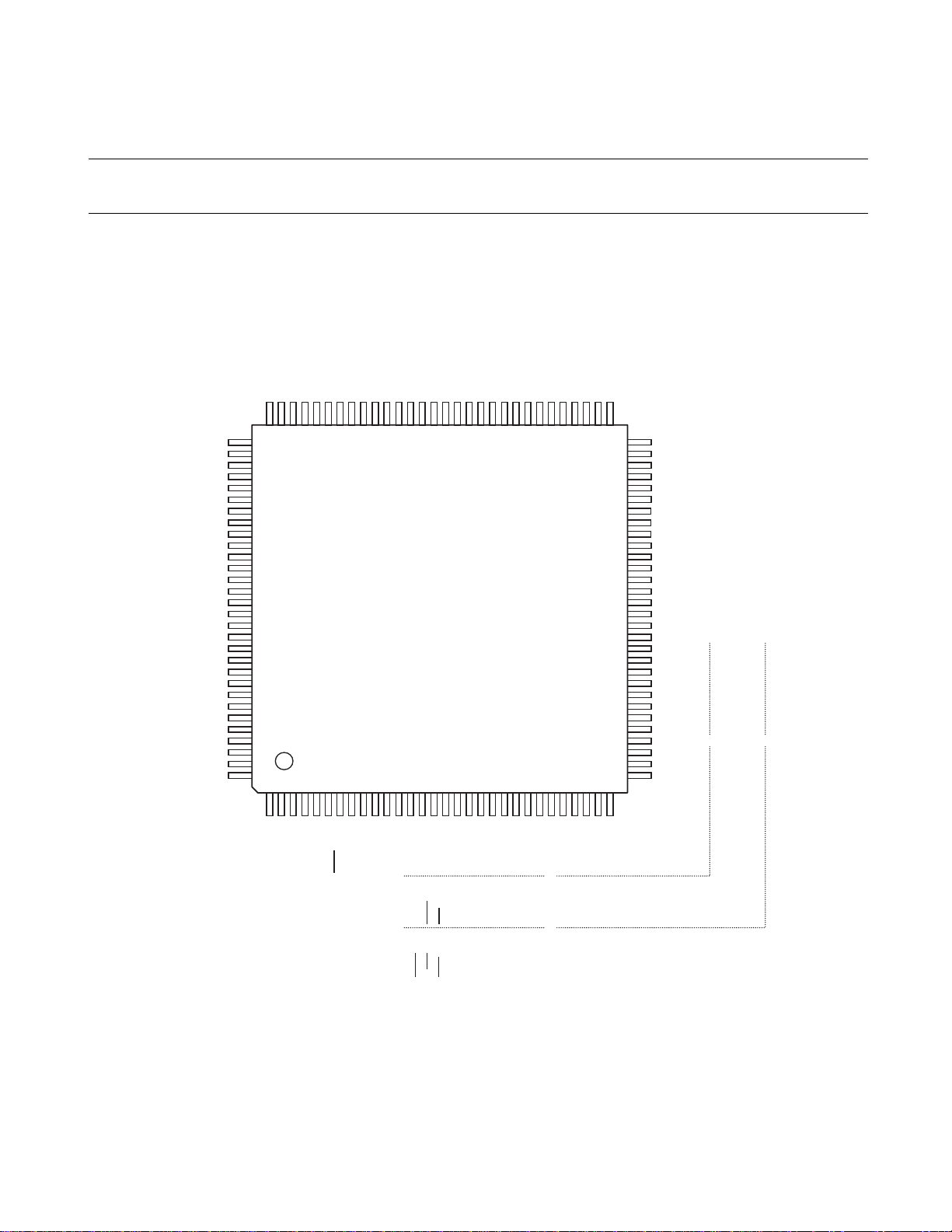

1.3 Package Dimension

120-pin plastic LQFP Lead pitch 0.40 mm

Package width ×

package length

14.0 × 14.0 mm

Lead shape Gullwing

Sealing method Plastic mold

Mounting height 1.70 mm MAX

Weight 0.62 g

Code

(Reference)

P-LFQFP120-14×14-0.40

120-pin plastic LQFP

(FPT-120P-M05)

(FPT-120P-M05)

C

2003 FUJITSU LIMITED F120006S-c-4-5

0.07(.003)

M

INDEX

16.00±0.20(.630±.008)SQ

14.00±0.10(.551±.004)SQ

130

31

6091

120

6190

LEAD No.

(Stand off)

0.10±0.10

(.004±.004)

0.25(.010)

(.024±.006)

0.60±0.15

(.020±.008)

0.50±0.20

(Mounting height)

0~8˚

Details of "A" part

1.50

+0.20

–0.10

+.008

–.004

.059

"A"

0.40(.016)

0.16±0.03

(.006±.001)

0.145±0.055

(.006±.002)

0.08(.003)

*

Dimensions in mm (inches).

Note: The values in parentheses are reference values.

FPT-120P-M05

Note 1)* : These dimensions do not include resin protrusion.

Note 2) Pins width and pins thickness include plating thickness.

Note 3) Pins width do not include tie bar cutting remainder.

MB91191/MB91192 series is available in one type of packages.

■ Package Dimension (LQFP-120)

Figure 1.3-1 Package Dimension of FTP-120-M05

5

Page 20

CHAPTER 1 Overview of MB91191/MB91192 Series

0.35 0.05

5

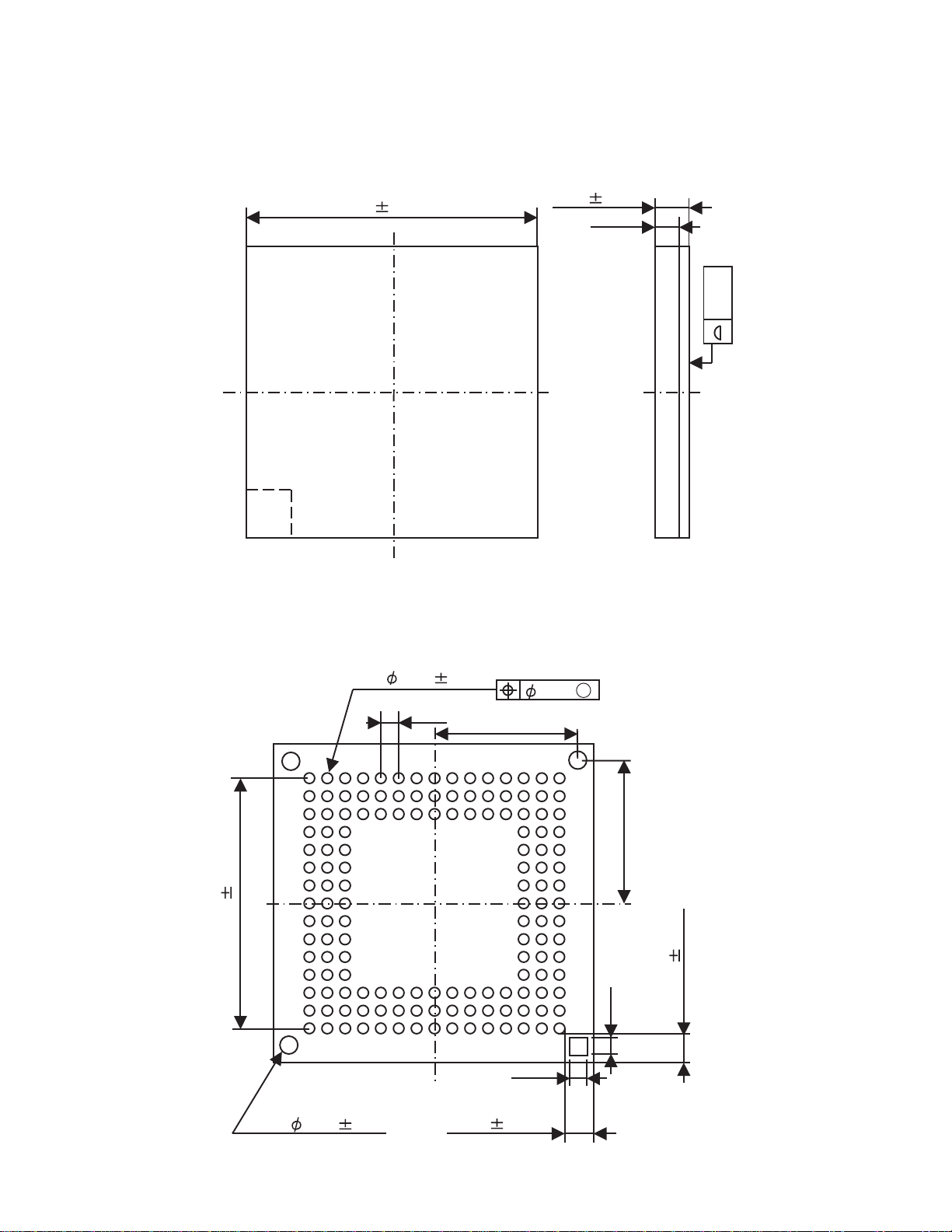

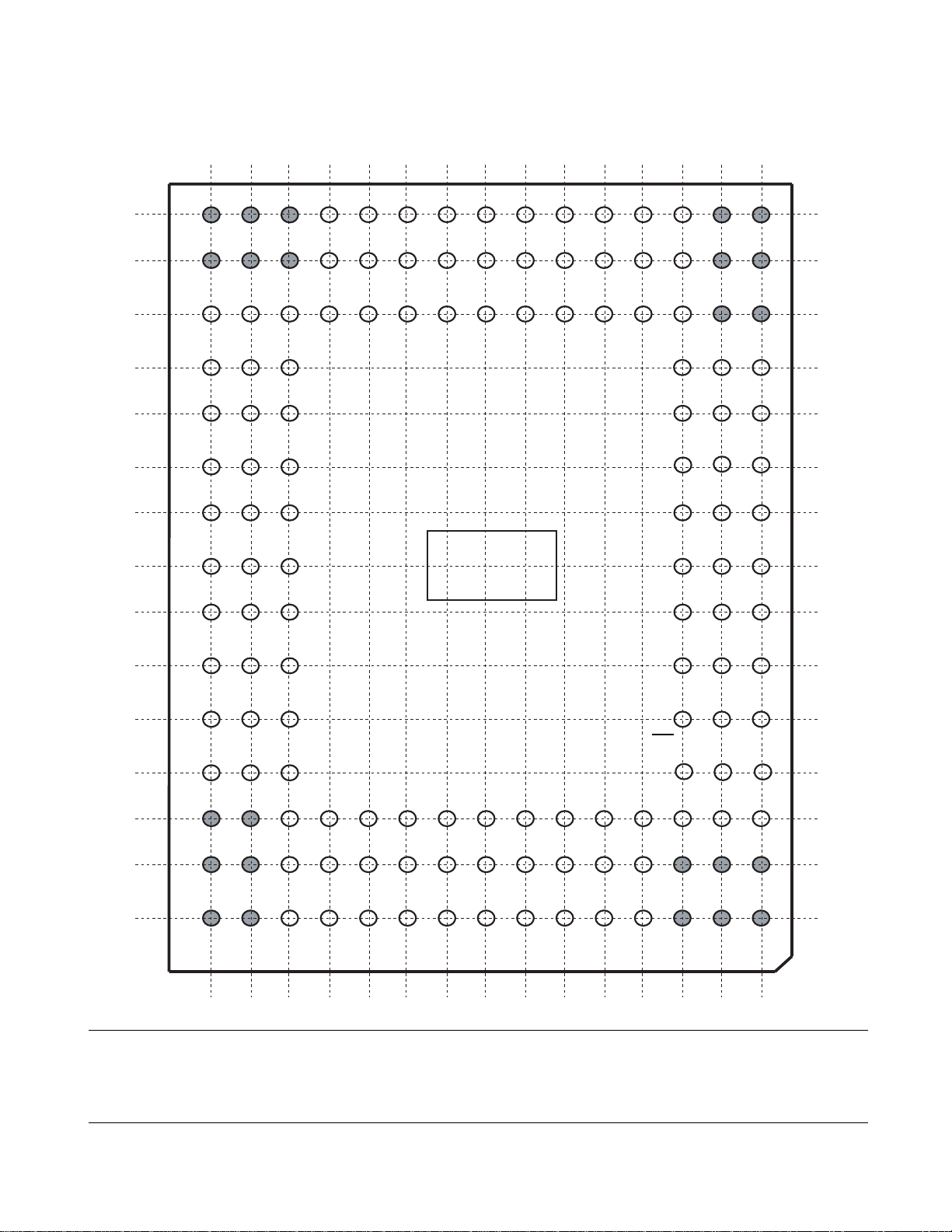

■ Package Dimension (FLGA-144)

Figure 1.3-2 Package dimension of FLGA-144

(INDEX AREA)

11.00

0.05 S Q.

1.10

0.10

(0.80)

0.05

0.05

9.10

3 0.45 0.05

144

0.65

0.755

.175

0.45

0.050

0.08

M

5.175

0.755 0.050

0.45

6

Page 21

1.4 Pin Assignment

Figure 1.4-1 and Figure 1.4-2 show the pin assignment of the MB91191/MB91192 series.

■ Pin Assignment (LQFP-120)

Figure 1.4-1 Pin assignment of LQFP-120

SS

VDD

PA1/AN-9/KEY1

PA2/AN-A/KEY2

PA3/AN-B/KEY3

PA4/AN-C/KEY4

PA5/AN-D/KEY5

PA6/AN-E/KEY6

PA7/AN-F/KEY7

PD0/SI2

PD1/SO2

PD2/SCK2

PD3/SI1/IN T2

PD4/SO1

PD5/SCK1

PD6/SCS0

PD7/SI0

PC0/SO0

PC1/SCK0

PC2/PWM5/SCS1

PC3/PWM4/SCS2

PC4/PWM3

PC5/PWM2

PC6/PWM1

V

PC7/PWM0

OSCI/PCK

OSCO

P90/PO

P91/PPG00

P92/PPG01

PA0/AN-8/KEY0

PB7/AN-7

PB6/AN-6

PB5/AN-5

PB4/AN-4

PB3/AN-3

PB2/AN-2

PB1/AN-1

PB0/AN-0

AVDD

AVRH

AVSS

V

SS

P17/RTO4

P16/RTO3

P15/RTO2

P14/RTO1

P13/RTO0

P12/EC5/IN T1

P11/EC4/IN T0

P10/PMSK

P07/EXI 2/PMI

P06/EXI1

P05/EXI0

P04/CFG

P03/DFG

P02/DPG

P01/RFG0

P00/RFG1

VDD

95

100

105

110

115

120

90

X0X1MD2

VSS

85

80

75

70

Top View

5

MD1

10

MD0

RST

P70/XOUT

P67/T4O

P66/T5O1

15

P65

P64

P63

P62

P61

20

P60

P20

P21

P22

P23

P24

65

25

P25

P26

P27

VDDP30

60

P93/PPG02

P94/PPG03

P80/PPG04

P81/PPG05

P82/PPG06

55

P83/PPG07

P84/PPG08

P85/PPG09

P86/PPG10

P87/PPG11

50

P40/PPG12

P41/PPG13

P42/PPG14

P43/PPG15

P44/PPG16

45

P45/PPG17

P46/PPG18

P47

P57

P56

40

P55

P54

P53

P52

P51

35

P50

V

SS

P37

P36

P35

30

P31

P32

P33

P34

A15

A14

A13

A12

A11

A10

A09

A08

D31/A07

D30/A06

D29/A05

P57

P56

P55

P54

P53

P52

P51

P50

D31/A15

D30/A14

D29/A13

8bit MPX mode

A00/D24

A01/D25

A02/D26

A03/D27

A08/D24

A09/D25

A10/D26

A11/D27

A04/D28

16bit MPX mode

A12/D28

P25

P26

P20

P21

P22

RD

RD

A00/D16

A01/D17

A02/D18

P23

A03/D19

ALE

P62

WR0

ALE

WR1

WR0

P24

A04/D20

A05/D21

A06/D22

P27

A07/D23

7

Page 22

CHAPTER 1 Overview of MB91191/MB91192 Series

■ Pin Assignment (FLGA-144)

Figure 1.4-2 Pin assignment of FLGA-144

59 56 53 50 47 44 41 38 3 5 32

P94 P82 P85 P40 P43 P46 P56 P53 P 50 P36

58 55 52 4 9 46 45 42 39 36 33

P80 P83 P86 P41 P44 P45 P57 P54 P51 P37

62 63 6 1 60 57 54 51 48 43 40 3 7 34 31

P91 P90 P92 P93 P81 P84 P87 P42 P47 P55 P52 VSS P35

65 66 64 30 28 29

OSCO OSCI VDD P34 P32 P33

68 69 67 27 25 26

PC7 PC6 VSS P31 VDD P30

71 72 70

PC4 PC3

74 75 73 2 1 19 20

PC1 PC0 PC2 P 24 P22 P23

PC5

Top View

77 76 78

PD6 PD7 PD5 P21 P60 P20

22

24

P 27

1 8 16 17

P25

23

P26

Note:

80 7 9 81 1 3 15 14

PD3 PD4 PD2 P 63 P61 P62

83 8 2 84 1 0 12 11

PD0 PD1 PA7 P66 P64 P65

86 85 87 7 9 8

PA5 PA6 PA4 RST P67 P70

89 88 90

PA2 PA3 PA1 MD2 MD0 MD1

91 94 97 100 103 108 111 114 117 120 1 3 2

PA0 PB5 PB2 AVDD P13 P10 P05 P02 VDD X0 VSS X1

93 96 99 102 105 106 109 112 1 15 118

PB6 PB3 PB0 AVSS P16 P15 P12 P07 P04 P01

92 95 98 01 104 107 110 1 13 116 119

PB7 PB4 P B1 AVRH P17 P14 P11 P06 P03 P00

VSS

4 6 5

For the MB91191 series, the FLGA- 144 package does not suppl y. It only supplies for the MB9119 2

series.

8

Page 23

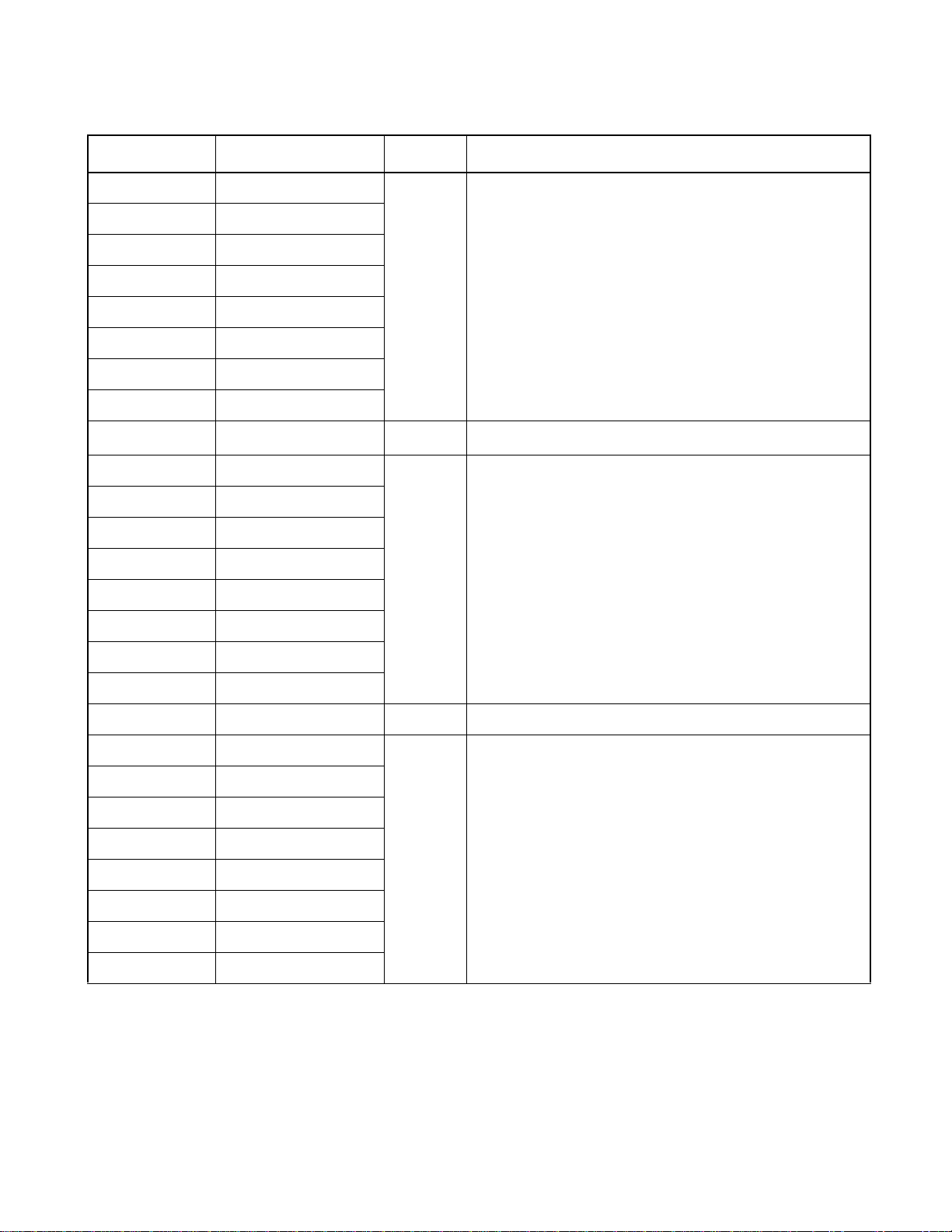

1.5 Pin Function Description

Table 1.5-1 lists the pin function of MB91191/MB91192 series.

The numbers shown in the tables has nothing to do with package pin numbers. For pin

numbers, see "1.4 Pin Assignment".

■ Pin Function List

Table 1.5-1 Pin Function List

Pin No. (LQFP) Pin name Form Function

1 X0(I)

2 X1(O)

3 Vss - It is Vss pin.

4 MD2

5 MD1

6 MD0

7 RST

8

9

10

11 P65 It is general-purpose I/O port. It is CMOS input.

12 P64 It is general-purpose I/O port. It is CMOS input.

13

P70/XOUT

P67/T4O

P66/T5O1 This pin is shared with timer 5 square wave output. It is

P63/ALE/ALE This pin is shared with address strobe output.

A It is crystal oscillation pin.

B

B It is reset input pin. It is CMOS schmitt input.

C

C

It is operating mode specification pin.

It is CMOS schmitt input.

This pin is shared with clock output (X0/2, PCK/2). It is

CMOS input.

This pin is shared with timer 4 square wave output. It is

CMOS input.

CMOS input.

It is CMOS input.

14

15

16

P62/P62/WR1

P61/WR0

P60/RD

/WR0 This pin is shared with write strobe output 0.

/RD This pin is shared with read strobe output.

This pin is shared with write strobe output 1.

It is CMOS input.

It is CMOS input.

It is CMOS input.

9

Page 24

CHAPTER 1 Overview of MB91191/MB91192 Series

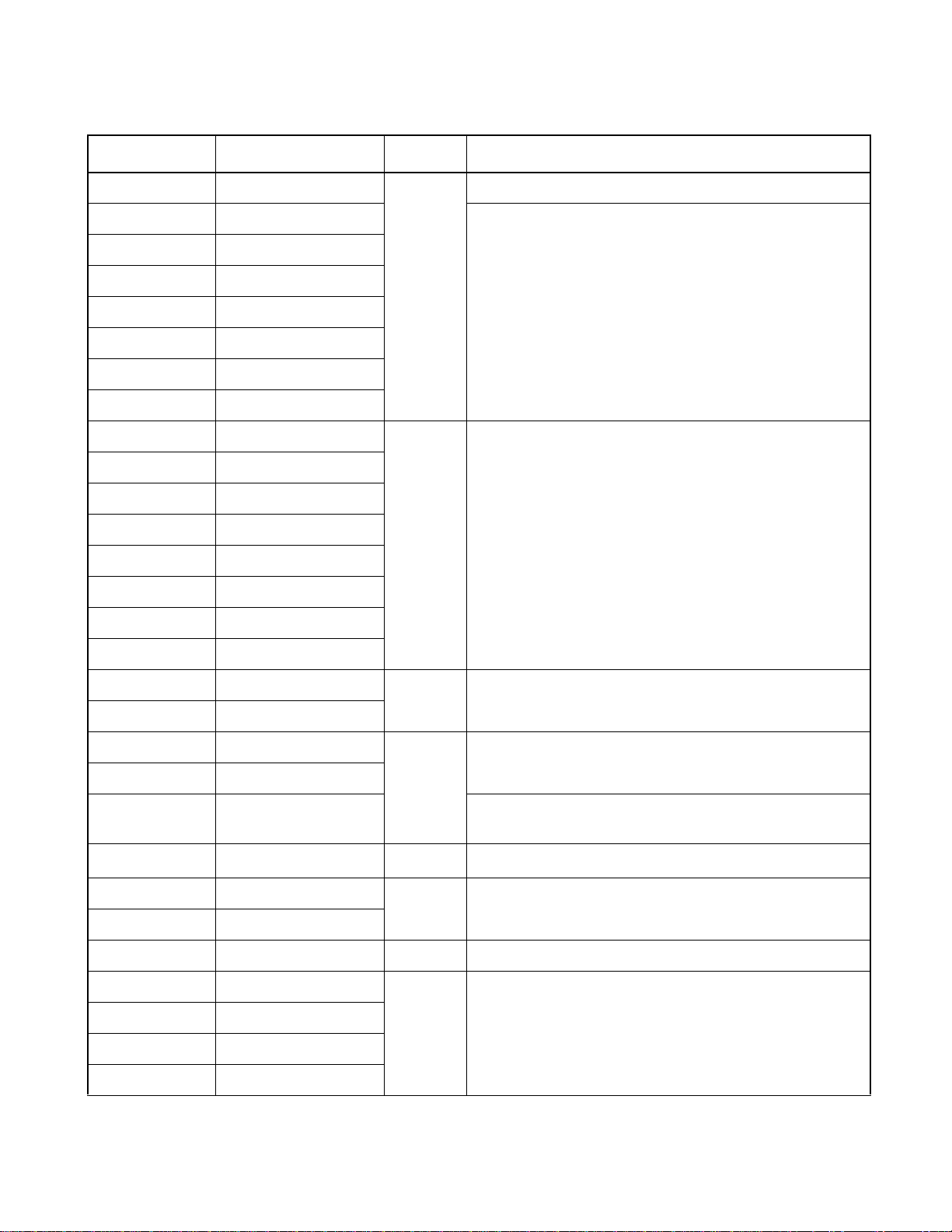

Table 1.5-1 Pin Function List

Pin No. (LQFP) Pin name Form Function

17 P20/P20/D16:A00

18 P21/P21/D17:A01

19 P22/P22/D18:A02

20 P23/P23/D19:A03

C

21 P24/P24/D20:A04

It is general-purpose I/O port.

It is CMOS input.

22 P25/P25/D21:A05

23 P26/P26/D22:A06

24 P27/P27/D23:A07

V

25

DD

- It is power supply pin.

26 P30/D24:A00/D24:A08

27 P31/D25:A01/D25:A09

28 P32/D26:A02/D26:A10

29 P33/D27:A03/D27:A11

C

30 P34/D28:A04/D28:A12

It is high-current I/O port and shared with external bus pins.

It is CMOS input.

31 P35/D29:A05/D29:A13

32 P36/D30:A06/D30:A14

33 P37/D31:A07/D31:A15

34 Vss - It is Vss pin.

10

35 P50/A08/P50

36 P51/A09/P51

37 P52/A10/P52

38 P53/A11/P53

39 P54/A12/P54

40 P55/A13/P55

41 P56/A14/P56

42 P57/A15/P57

C

It is high-current I/O port and shared with external bus pins.

It is CMOS input.

Page 25

Table 1.5-1 Pin Function List

Pin No. (LQFP) Pin name Form Function

43 P47

44 P46/PPG18

45 P45/PPG17

46 P44/PPG16

47 P43/PPG15

48 P42/PPG14

49 P41/PPG13

50 P40/PPG12

51 P87/PPG11

52 P86/PPG10

53 P85/PPG09

54 P84/PPG08

55 P83/PPG07

56 P82/PPG06

57 P81/PPG05

C

C

It is general-purpose I/O port. It is CMOS input.

This pin is shared with PPG output.

It is CMOS input.

This pin is shared with PPG output.

It is CMOS input.

58 P80/PPG04

59 P94/PPG03

60 P93/PPG02

61 P92/PPG01

62 P91/PPG00

63

64

P90/PO This pin is shared with general-purpose prescaler output. It is

V

DD

65 OSCO (O)

66 OSCI/PCK(I)

C

C

- It is power supply pin.

A

This pin is shared with PPG output.

It is CMOS input.

This pin is shared with PPG output.

It is CMOS input.

CMOS input.

It is crystal oscillation pin for dedicated general-purpose

prescaler.

67 Vss - It is Vss terminal.

68 PC7/PWM0

69 PC6/PWM1

C

70 PC5/PWM2

This pin is shared with PWM output.

It is CMOS input.

71 PC4/PWM3

11

Page 26

CHAPTER 1 Overview of MB91191/MB91192 Series

Table 1.5-1 Pin Function List

Pin No. (LQFP) Pin name Form Function

72

73

74

75

76

77

78

79

80

81

PC3/PWM4/SCS2

PC2/PWM5/SCS1 This pin is shared with PWM ou tput a nd serial 1 chip select. It

PC1/SCK0 This pin is shared with serial 0 shift clock.

PC0/SO0

PD7/SI0

PD6/SCS0 This pin is shared with serial 0 chip select input.

PD5/SCK1 This pin is shared with serial 1 shift clock.

PD4/SO1

PD3/SI1/INT2

PD2/SCK2 This pin is shared with serial 2 shift clock.

F

C

F

C

F

This pin is shared with PWM output and serial 2 chip select. It

is CMOS schmitt input.

is CMOS schmitt input.

It is CMOS schmitt input.

This pin is shared with serial 0 serial output.

It is CMOS input.

This pin is shared with serial 0 serial input.

It is CMOS schmitt input.

It is CMOS schmitt input.

It is CMOS schmitt input.

This pin is shared with serial 1 serial input.

It is CMOS input.

This pin is shared with serial 1 serial input and external

interrupt 2. It is CMOS schmitt input.

It is CMOS schmitt input.

82

83

84 PA7/AN-F/KEY7

85 PA6/AN-E/KEY6

86 PA5/AN-D/KEY5

87 PA4/AN-C/KEY4

88 PA3/AN-B/KEY3

89 PA2/AN-A/KEY2

90 PA1/AN-9/KEY1

91 PA0/AN-8/KEY0

PD1/SO2

PD0/SI2

C

F

E

This pin is shared with serial 2 serial output.

It is CMOS input.

This pin is shared with serial 2 serial input.

It is CMOS schmitt input.

This pin is shared with analog input and key input.

It is CMOS schmitt input.

12

Page 27

Table 1.5-1 Pin Function List

Pin No. (LQFP) Pin name Form Function

92 PB7/AN-7

93 PB6/AN-6

94 PB5/AN-5

95 PB4/AN-4

D

96 PB3/AN-3

This pin is shared with analog input.

It is CMOS schmitt input.

97 PB2/AN-2

98 PB1/AN-1

99 PB0/AN-0

AV

100

DD

- It is A/D converter power supply pin.

101 AVRH - It is A/D converter reference power supply pin.

102 AVss - It is Vss pin of A/D converter.

103 Vss - It is Vss pin.

104 P17/RTO4

105 P16/RTO3

106 P15/RTO2

C

This pin is shared with RTG output.

It is CMOS input.

107 P14/RTO1

108 P13/RTO0

109

P12/EC5/INT1

This pin is shared with timer 5 clock input and external

interrupt input. It is CMOS schmitt input.

110

111

P11/EC4/INT0 This pin is shared with timer 4 clock input and external

F

interrupt input. It is CMOS schmitt input.

P10/PMSK This pin is shared with PWC mask input.

It is CMOS schmitt input.

13

Page 28

CHAPTER 1 Overview of MB91191/MB91192 Series

Table 1.5-1 Pin Function List

Pin No. (LQFP) Pin name Form Function

112

P07/EXI2/PMI

113 P06/EXI1

114 P05/EXI0

115

116

117

P04/CFG This pin is shared with capstan FG input.

P03/DFG This pin is shared with drum FG input.

P02/DPG This pin is shared with drum pulse input.

118 P01/RFG0

119 P00/RFG1

120

V

DD

This pin is shared with external capture input and PWC input.

It is CMOS schmitt input.

This pin is shared with external capture input.

It is CMOS schmitt input.

It is CMOS schmitt input.

F

It is CMOS schmitt input.

It is CMOS schmitt input.

This pin is shared with reel FG input.

It is CMOS schmitt input.

- It is power supply pin.

14

Page 29

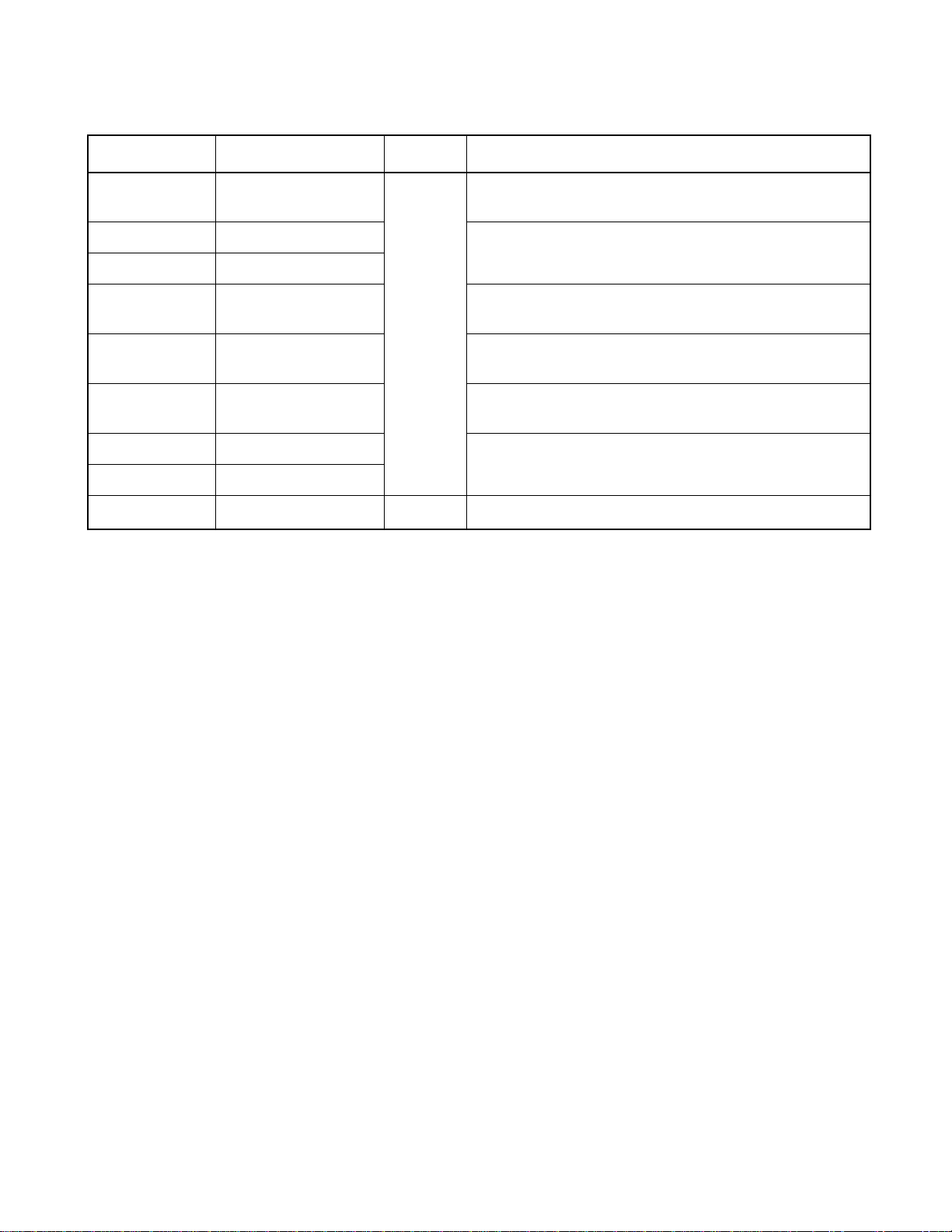

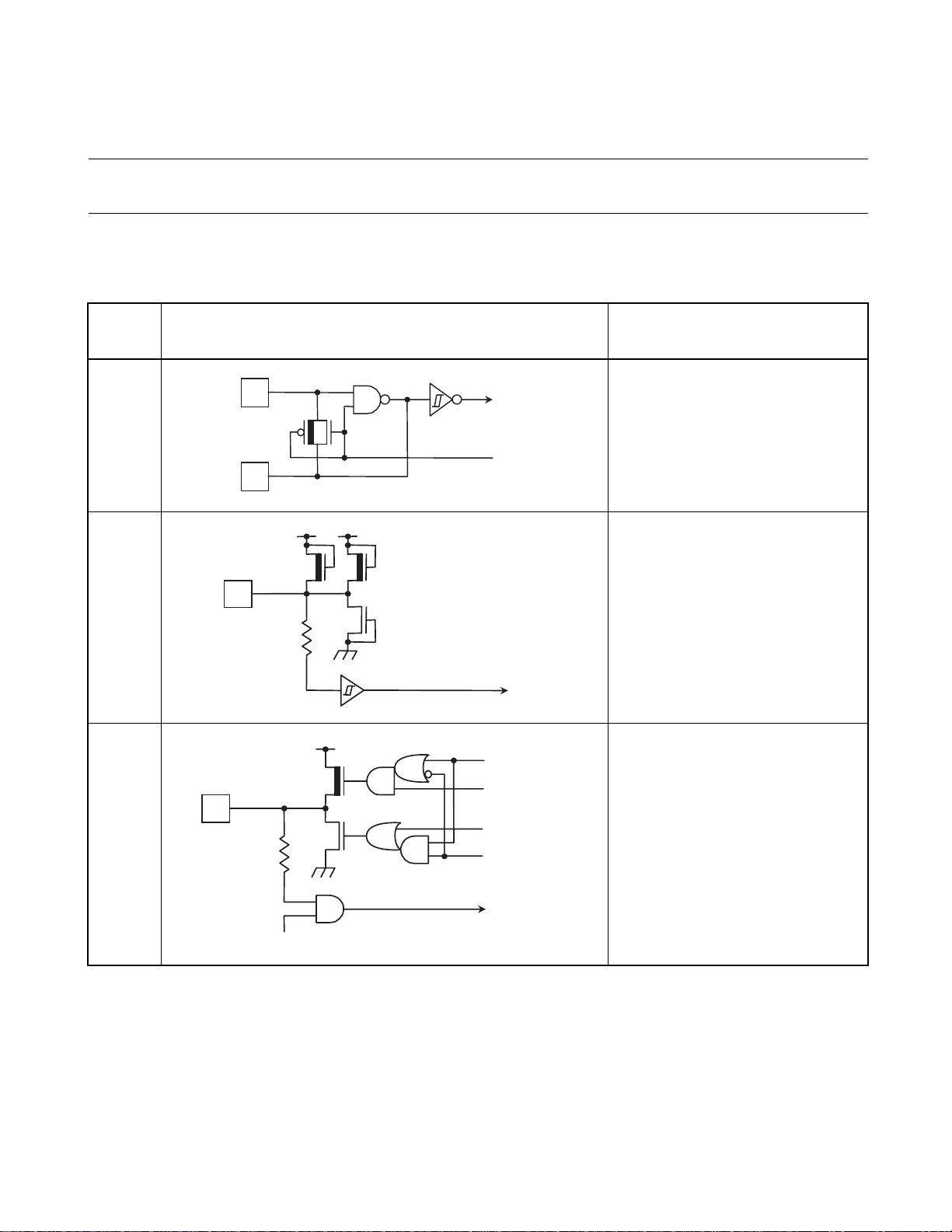

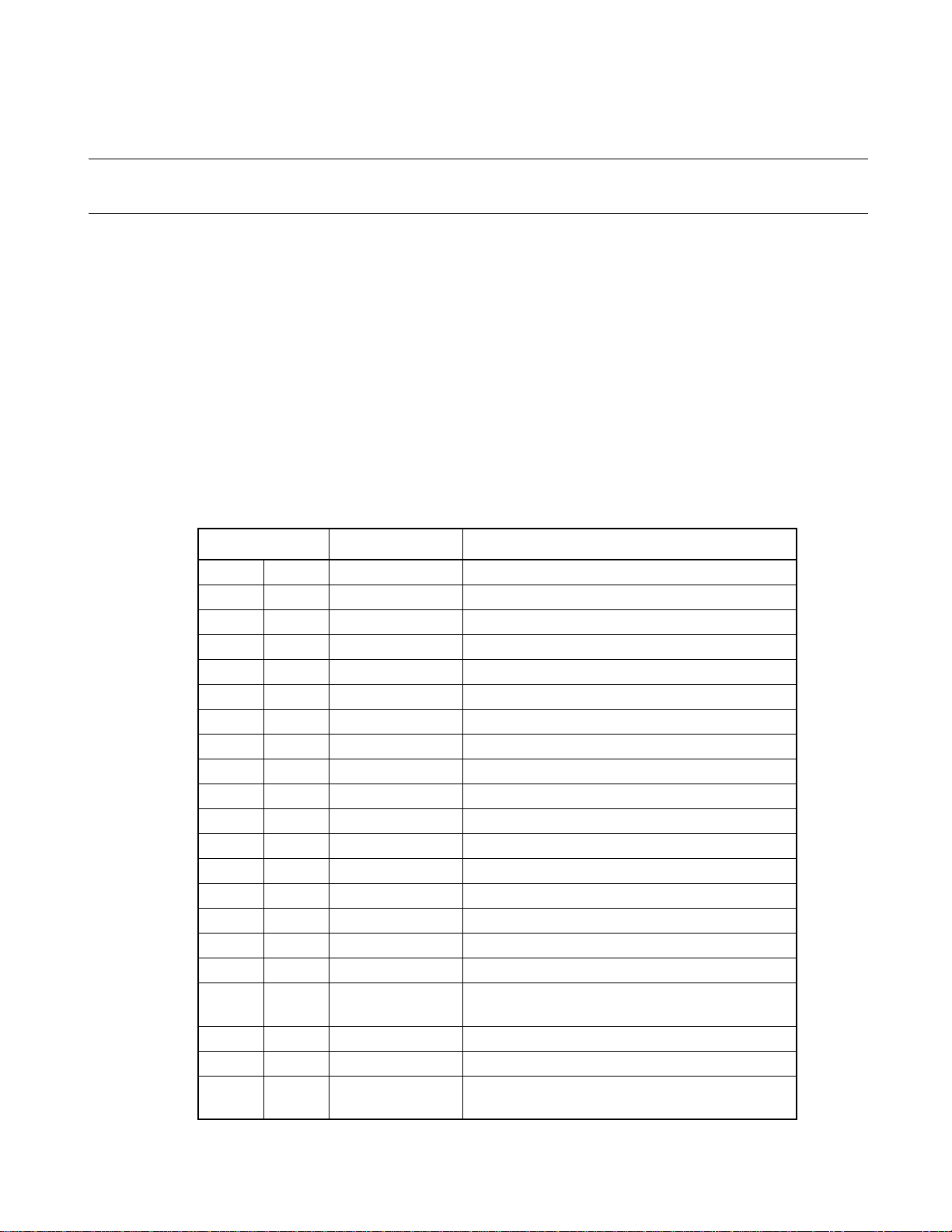

1.6 I/O Circuit Type

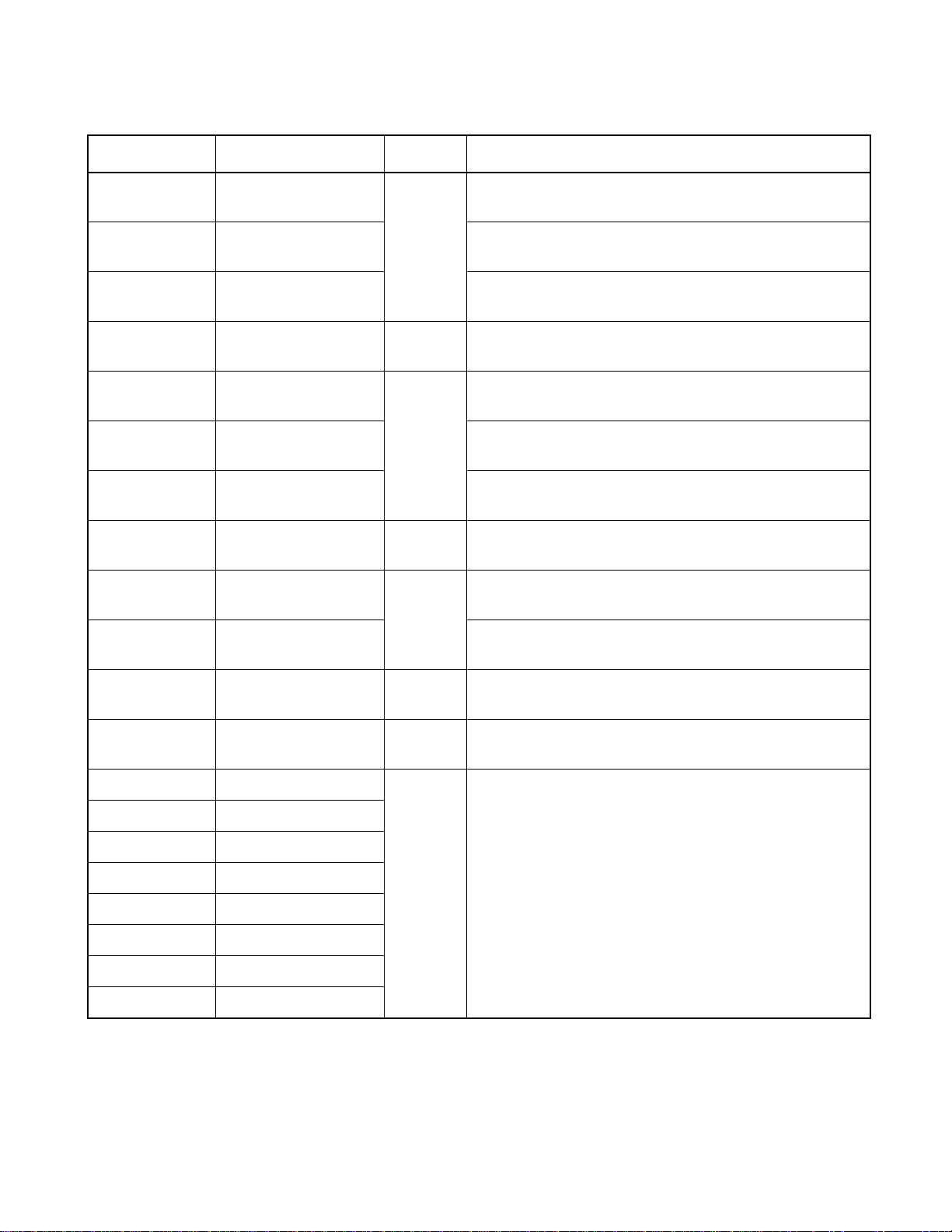

Table 1.6-1 shows the I/O circuit type.

■ I/O Circuit Type

Table 1.6-1 I/O circuit types

Classifi-

cation

A

B

X0,OSCI

X1,OSCO

Circuit Type Remark

• Oscillation return resistance about

Clock input

Standby control

1MΩ

• CMOS schmitt inpu t

Input

• CMOS level output

Output data

DC test

• CMOS input without standby

control

C

DC test

Direction CTL

Input

Standby control = 1 fix

15

Page 30

CHAPTER 1 Overview of MB91191/MB91192 Series

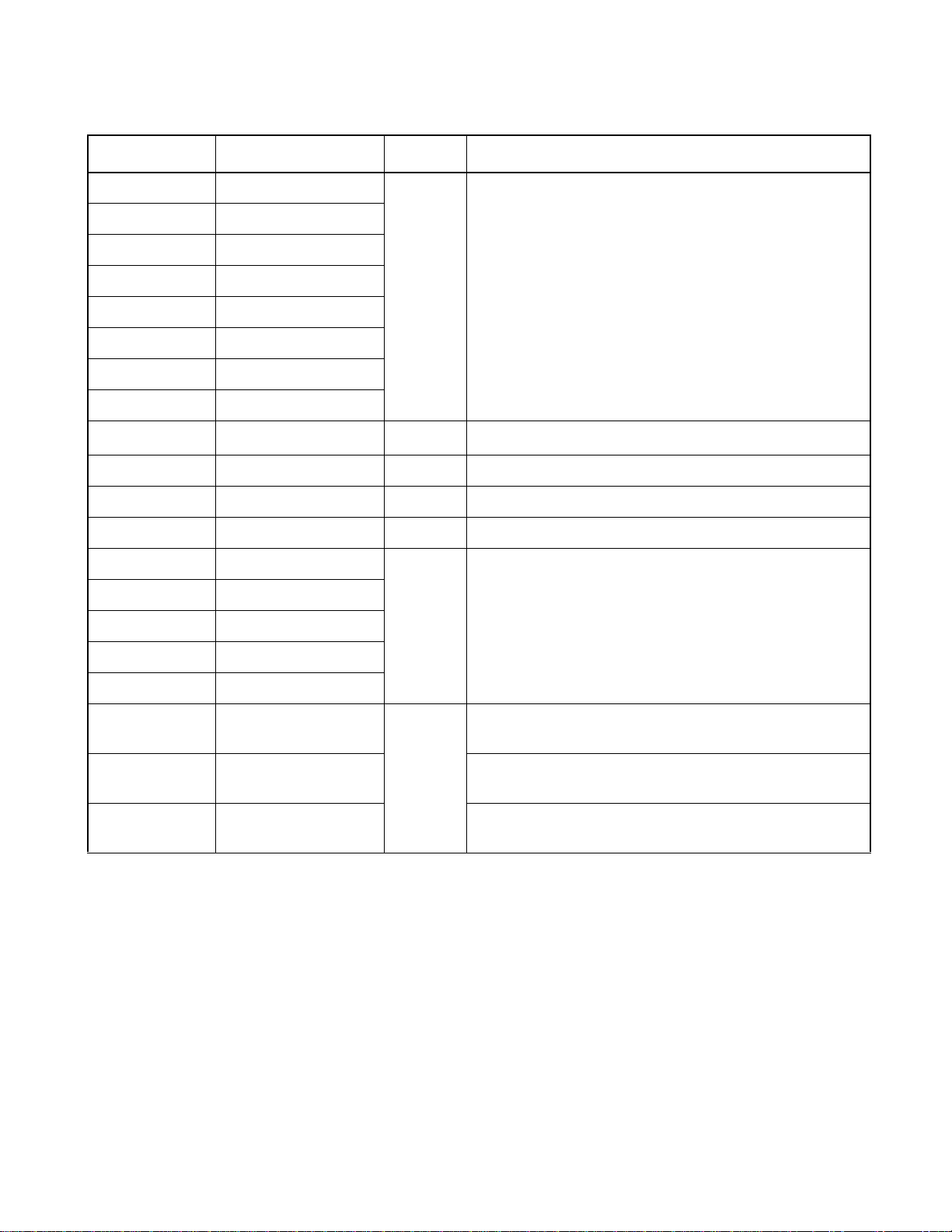

Table 1.6-1 I/O circuit types

Classifi-

cation

D

E

Input control

Circuit Type Remark

• CMOS level output

Output data

DC test

DC test

Direction CTL

Analog input

CH selection

Digital input

• CMOS input with input control

• Analog input

• CMOS level output

Output data

DC test

• CMOS schmitt input with input

control

• Analog input

DC test

Direction CTL

F

Input control

Standby control = 1 fix

Analog input

CH selection

Digital input

Output data

DC test

DC test

Direction CTL

Input

• CMOS level output

• CMOS schmitt input without

standby control

16

Page 31

CHAPTER 2

Handling Devices

This chapter describes points to note when using the

MB91191/MB91192 series.

2.1 Precautions When Handling Devices

2.2 Others

17

Page 32

CHAPTER 2 Handling Devices

2.1 Precautions When Handling Devices

The semiconductor device breaks down at a certain probability. Moreover, the failure of

the semiconductor device is greatly controlled by the condition (circuit condition and

environmental condition, etc.) used.

To have the high use, the semiconductor device is explained about reliability about the

matter which should be noted and considered as follows.

■ Precautions when Designing

Here, the matter which should be noted when an electronic equipment is designed with a semiconductor

device is described.

Observance of absolute maximum rating

●

When an excessive stress (voltage, current, and temperature, etc.) adds, the semiconductor device has the

possibility to destroy. The value that this thres hold was provided is an absolute maximum rating. Therefore,

care must be taken not to exceed the rating even for one item.

Observance of recommended operation condition

●

The recommended operation condition is a condition to guarantee normal movement of the semiconductor

device. All standard values for electric features are assured within this condition range. Always u se under

the recommended operation condition. When this condition is exceeded and used, the adverse effect is

occasionally caused for reliability.

Use by the item, the condition, and th e logi cal combinatio n not described t o thi s material is not guaranteed.

Please consult with the section in charge of sales of our company about use by conditions other than being

described for the idea beforehand.

Processing and protection of terminal

●

In the semiconductor device, there are a power supply and various input/output terminals. The followi ng

attention is necessary for these.

• Prevention of over-voltage/over-current

Deterioration is caused in the device when the voltage/current which exceeds the maximum rating is

applied to each terminal, and when it is remarkable, it becomes destruction. Please prevent such an overvoltage/over-current occurring when you design the equipment.

• Protection of output terminal

If the output terminal is short circu ited with the power terminal or other output terminal, or when large

capacity load is connected, a large electrical current may result. If this condition is prolonged, the device

will be damaged, so this kind of connection should not be made.

• Processing of unused input terminal

18

If the input terminal with very high impedance is used while opened, the operation might become unstable.

Ensure connections to the power terminal and ground terminal have the appropriate resistance.

Page 33

Latch up

●

The semiconductor device is composed by the formation of the region of the P-type and the N-type on the

substrate. Internal parasitism PN junction (thyristor structure) might keep doing on-line when the voltage of

an external abnormal voltage is added, and the heavy-current which exceeds hundreds of mA flow to the

power supply terminal. This is called a latch up. The reliability of the device is not only damaged when this

phenomenon occurs but also there is dreading the arrival heat generation, smoking, and the ignition to

destruction. Please note the following points to prevent this.

• There must not be what the voltage more than the maximum rating adds the terminal. Please note

abnormal noise and surge etc.

• An abnormal current must not flow in consideration of the power supply turning on sequence.

Restriction of safety etc. and observance of standard

●

All over the world, various restrictions and standards of safety and the EMI, etc. have been installed. Please

suit these restriction and standard when the customer designs the equipment.

Fail safe design

●

The semiconductor device breaks down at a certain probability. The customer safely designs such as the

device redundancy, fire spreading prevention, exceeding current prevention, and prevention of malfunction

not to occur the injury accident, fire accident, and social damage consequently when the semiconductor

device is broken.

Attention concer nin g usag e

●

The our company semiconductor device is intended to be used for a standard usage (associated equipment

for office appliances such as computers/OA and industries/communications/the measurements and

personal/home equipment etc.). The customer concerns the usage of threatening the life by the breakdown

and malfunction, dreading the damage to the human body, or the special application which the extreme

high reliability is requested (fro aviation/space, atomic control, device for relayed the bottom of the sea,

running control, the medical device to keep the life, etc.), be sure to consult with the sales divisio n of our

company. When you use without the consultation and acknowledge that the responsibility cannot be

assumed about the occurring damage etc.

■ Precautions when Mounting Package

In the package, there are a lead insertion type and a surface mounting type. In both cases, quality assurance

for heat resistance at the soldering stage only applies to the mounting under conditions recommended by us.

Please inquire the section in charge of sales of our company about details of the mounting condition.

Lead insertion type

●

There are two ways to mount the lead insertion type package onto the printing board-the first is to directly

solder it onto the printing board, and the second is to mount it on the printing board using the socket.

When soldering it directly to the printing board, the flow soldering method (wave soldering method)

whereby the solder is melted after inserting the lead through the hole in the printing board is generally used.

In this case, heat stress in excess of the usual maximum rating preservation temperature is added to the lead

part at the soldering stage. Please mount under the mounting recommendation condition of our company.

When the mounting method using the socket is used, if surface processing of the socket contact point and

surface processing of the IC lead are different, contact failure may be generated after a prolonged period.

Therefore, checking the surface processing of the socket contact and surface processing of the IC lead is

recommended before mounting.

19

Page 34

CHAPTER 2 Handling Devices

Surface mounting type

●

The lead used in the surface mounting type package is thinner than that for the insertion type, so its shape is

easily changed. In line with the increased number of pins in the package, the lead pitch is also narrow, and

opening defects due to the lead change and short circuits due to the solder bridge can easily be caused, so

an appropriate mounting technique is required. We recommend the solder re-flow method, and implement

rank classification of the mounting conditions per product. Please mount according to the rank

classification of the our company recommendation.

About keeping the semiconductor device

●

The plastic package is made of resin, so moisture is absorbed if left in a natural environment. When the

heat when mounting on the moisture absorption package joins, the decrease and the package crack of the

wet-proofing by the interfacial flaking off generation might be generated. Please note the following points.

• The be dewy of moisture happens to the product in the place with a rapid temperature change. Store it in

a place with minimum temperature fluctuations that avoid such an environment.

• The depository of the product recommends the use of a dry box. Please keep under the relative humidity

to 70% RH and the temperature to 5 to 30 °C.

• Silica-gel is used as a dry medicine in our company with a damp-proof and high as packing material of

the semiconductor device if necessary an aluminum laminate bag. Put the semiconductor device in the

laminated aluminum bag and close it tightly for storage.

• Please avoid the place where a lot of places and dust where the corrosively gas is generated.

About the baking

●

The moisture absorption package can be dehumidified by executing the baking (heating dryness). Please

execute the baking by the condition which our company recommends.

Static electricity

●

Please note the following points so that the semiconductor device may cause destruction by static electricity

easily.

• Please adjust the relative humidity of th e working environment to 40% to 70% RH. Please examine the

use of TEL device (apparatus for generating ion) etc. if necessary.

• Earth the conveyer, soldering tank and iron, and peripheral incidental equipment to be used.

• In order to prevent electrocution of human body, try to earth through a ring or armlet with high

resistance (about 1MΩ), wear conductive clothing and shoes, and place a conductive mat on the floor to

minimize static build-up.

• Please execute the earth or the electrification prevention to the treatment device and meters.

• Avoid using materials that are easily charged, such as polystyrene foam, to store the assembled board.

20

Page 35

■ Precautions

The reliability of the semiconductor is affected by the peripheral temperature as mentioned before, and

other environmental conditions. Please note the following points.

Humidity

●

As for environment long-term use under the high humidity environment, something wrong with the leak

character might occur in not only the device but also printed wiring board, etc. Please consider the dampproof processing such as giving when the high humidity is assumed.

Static electricity discharge

●

The semiconductor device might cause the malfunction by being generate the electrical discharge in Kon

when electrified thing exists in high voltage near the device. For this case, please treat the prevention of

electrification or the prevention of the electrical discharge.

Corrosively gas, dust, and oil

●

If the device is used within a corrosive gas environment or where dust and oil, etc. may become attached,

the effect may be detrimental due to chemical reactions. Protective measures should be considered when

used under such an environment.

Radiation and cosmic ray

●

A general device does not assume the environment exposed to the radiation and the cosmic ray in the

design. Therefore, use this to shield.

Smoking and ignition

●

The device of the resin molding type is not nonflammability. Do not use the device near any ignitable

substance. In the event of smoke or fire may be generated toxic gases.

Additionally, please consult the section in charge of sales of our company about use under a special

environment for the idea.

21

Page 36

CHAPTER 2 Handling Devices

2.2 Others

The others are explained

■ External Reset Input

When "L" level is input to the RST pin, to ensure the inside ach ieves reset status, "L" level input to the

RST

pin is required for at least five machine cycles.

■ Note on Using External Clock

When using the external clock, drive the X0. Figure 2.2-1 shows the example of using an external clock.

Figure 2.2-1 Example of using an external clock

OPEN

X0

X1

MB91191/MB91192 series

*:Be sure to make X1 pin open.

■ Power Supply Pin

If there are multiple VDD and VSS pins, from the point of view of device design, pins to be of the same

potential are connected the inside of the device to prevent such malfunctioning as latch up. To reduce

unnecessary radiation, prevent malfunctioning of the strobe signal due to the rise of ground level, and

observe the standard for total output current, be sure to connect the V

and ground externally.

Also try to ensure that connection to the V

the power supply source. In addition, We will recommend the ceramic capacitor of about 0.1 µF to be

connected as bypass capacitor between V

■ Crystal Oscillation Circuit

The noise near X0 and the X1 terminal becomes original of the malfunction of this device. The printing

board should be designed so that the X0, X1, crystal oscillator (or ceramic oscillator), and bypass capacitor

to the ground are arranged as close as possible.

Printing board artwork around the X0 and X1 terminals to the ground is strongly recommended, as steady

operation can be expected.

■ Handling NC Pin

Use the Non Connect (N.C.) terminal while open.

■ Mode (MD0 to MD2) Pin

Please tie directly to VDD or VSS and use these terminals.

In order to prevent erroneous entry to test mode due to noise, the pattern length between each mode

terminal and V

at low impedance.

or VSS on the printing board should be as short as possible, and they should be connected

DD

■ At Power On

When the power is turned on, the RST pin must be started from "L" level status, and changed to "H" level

after at least five cycles of the internal operation clock have passed, after the power source reaches the V

level.

and VSS pins to the po wer supp ly

DD

, Vss on this device is at the lowest impedance possible f rom

DD

and VSS near this device.

DD

DD

22

Page 37

CHAPTER 3

CPU

This chapter provides basic explanations for such

elements as the architecture, specifications, and

commands, etc., required to understand the CPU core

functions of the FR series.

3.1 Memory Space

3.2 CPU Architecture

3.3 Dedicated Registers

3.4 General-purpose Register

3.5 Data Construction

3.6 Word Alignment

3.7 Memory Map

3.8 Overview of Instructions

3.9 EIT (Exception, Interruption, and Trap)

3.10 Reset Sequence

3.11 Memory Access Mode

3.12 Clock Generation Section (Low Power Consumption Mechanism)

23

Page 38

CHAPTER 3 CPU

3.1 Memory Space

The logical address space of the FR20 series is 4 Gbytes (232 addresses), and the CPU

performs linear access.

■ Direct Addressing Area

The under-mentioned area of the address space is used for I/O. This area is called the "direct addressing

area" and operand addresses can be specified directly within the command. A direct area is different as

follows depending on the size of the accessed data.

• Byte data access:0-0FF

• Half word data access:0-1FF

• Word data access:0-3FF

■ Memory Map

Figure 3.1-1 shows the memory map of the MB91191/MB91192.

H

H

H

24

Page 39

Figure 3.1-1 MB91191/MB91192 Memory Map

00000000

000001FF

00000200

000002FF

00000300

0000037F

00000380

000003BF

000003C0

000003FF

00000400

000007FF

00000800

00000FFF

00001000

0000107F

00001080

000010FF

00001100

0000E7FF

0000E800

0000FFFF

00010000

000BFFFF

000C0000

000C07FF

000C0800

000FFFFB

000FFFFC

00100000

FFFFFFFF

H

H

H

PPG0 Data RAM area 256byte

H

H

I/O area

SIO0 Data RAM area 128byte

H

H

PPG1 Data RAM area 64byte

H

H

I/O area

H

H

H

H

I/O area

Access interdiction

H

H

SIO1 Data RAM area 128byte

H

H

SIO2 Data RAM area 128byte

H

H

Access interdiction

H

H

Internal RAM area 6Kbyte

H

H

Access interdiction

H

H

Internal RAM

H

H

Internal ROM

H

Reset vector

H

H

area 2Kbyte

area (254kByte)

External expansion area

H

MB91191R MB91192

Direct

Access

Area

1KB

Initial vector area

I/O area

PPG0 Data RAM area 256byte

SIO0 Data RAM area 128byte

PPG1 Data RAM area 64byte

I/O area

I/O area

Access interdiction

SIO1 Data RAM area 128byte

SIO2 Data RAM area 128byte

Access interdiction

Internal RAM area 8Kbyte

Access interdiction

Internal RAM

area 2Kbyte

Access interdiction

Internal ROM

area (384kByte)

Reset vector

External expansion area

00000000

000001FF

00000200

000002FF

00000300

0000037F

00000380

000003BF

000003C0

000003FF

00000400

000007FF

00000800

00000FFF

00001000

0000107F

00001080

000010FF

00001100

0000DFFF

0000E000

0000FFFF

00010000

0007FFFF

00080000

000807FF

00080800

0009FFFF

000A0000

000FFFFB

000FFFFC

00100000

FFFFFFFF

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

Note:

Under single-chip mode, access to the external extension area is impossible.

Select internal RO M external bus mode using the mode register to access the external exte nsion

area.

25

Page 40

CHAPTER 3 CPU

3.2 CPU Architecture

The FR20 CPU is a high performance core that adopts highly functional commands for

the embedded application as well as RISC architecture.

■ Feature of CPU Architecture

Adoption of RISC architecture

●

• Basic instruction: one instruction one cycle

32 bit architecture

●

• General-purpose register 32 bits × 16

Linear memory space of 4 GB

●

Installing of multipliers

●

• 32 bits x multiplication 32 bits: 5 cycles

• 16 bits x multiplication 16 bits: 3 cycles

Reinforcement of interruption processing function

●

• High-speed response speed (6 cycles)

• Support for multiple interr up ts

• Lev el mask function (16 levels)

Reinforcement of instruction for I/O operation

●

• Memory memory transfer operation

• Bit processing instruction

High code efficiency

●

• 16 bits in basic instruction word length

Low power consumption

●

• Sleep mode, stop mode

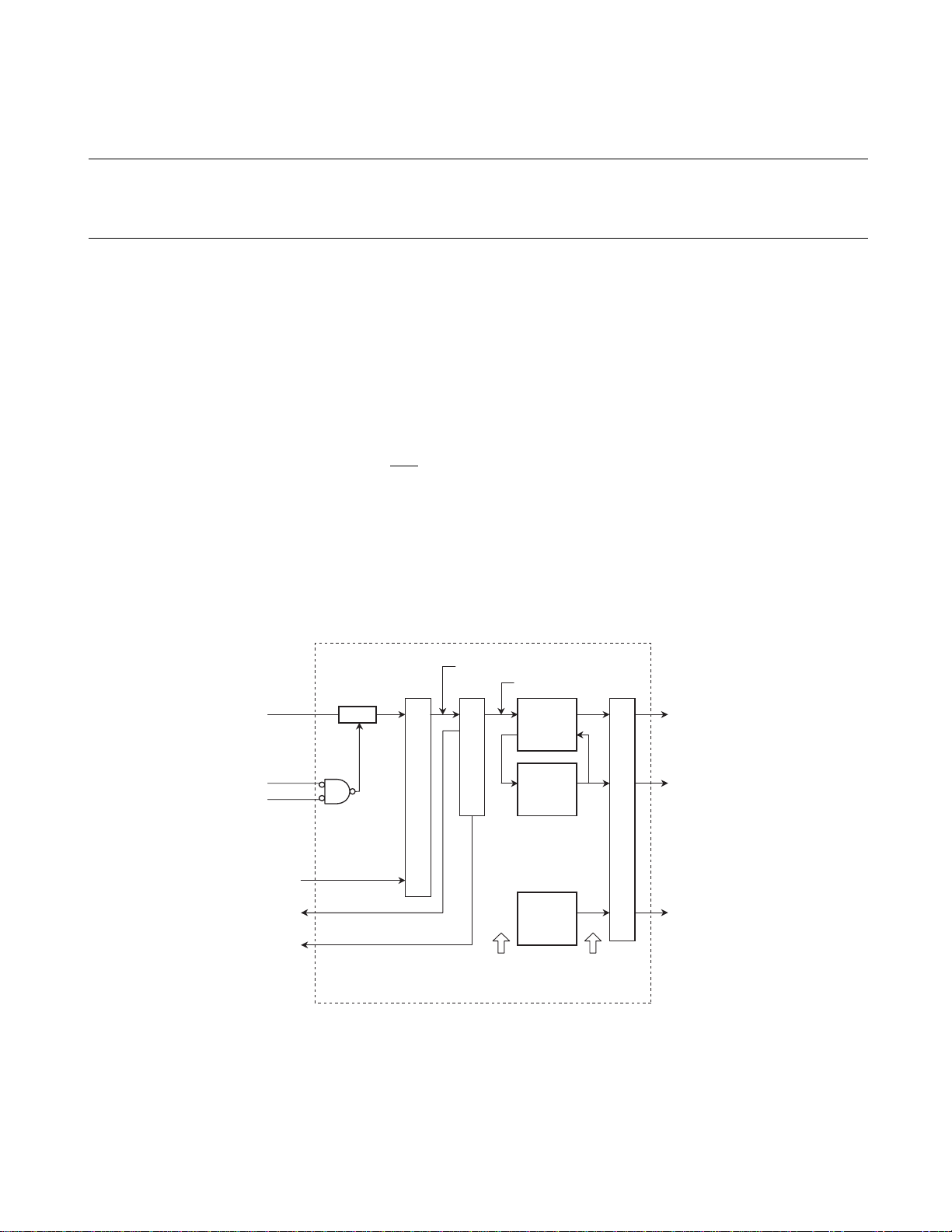

■ Construction of Internal Architecture

The FR20 CPU adopts the Harvard architecture structure whereby the command bus and data bus are

independent.

26

The on chip command cache is connected to the command bus (T-bus). A 32-bit <--> 16-bit bus converter

is connected to the data bus (D-bus), and performed interfaces between the CPU and peripheral resources.

A Harvard <--> Princeton bus converter is connected to both the I-bus and D-bus, performed and interfaces

between the CPU and bus controller.

Page 41

Figure 3.2-1 shows the construction of internal architecture.

Figure 3.2-1 Construction of Internal architecture

FR20 CPU

D-BUS I-BUS

Instruction

Cache

32bit

16bit

Bus converter

R-bus C-bus

Harvard

Princeton

Bus converter

●

Resource

CPU

Bus controller

The FR20's 32-bit RISC architecture is compactly implemented on the CPU. A five-level command

pipeline method is adopted to execute one command per cycle. The pipeline is composed of the following

stages.

• Instruction fetch (IF): The instruction address is output, and the instruction is fetched.

• Instruction decode (ID): The decode does the fetched instruction. The register is read.

• Execution (EX): The operation is executed.

• Memory access (MA): Loading into the memory or the store is accessed.

• Write-back (WB): Writes th e operation results (or loaded memory data) to the register.

Figure 3.2-2 shows the instruction pipeline.

Figure 3.2-2 Instruction pipeline

CLK

Instruction 1 WB

Instruction 2 MA

Instruction 3 EX

Instruction 4 ID

Instruction 5 IF

Instruction 6

WB

MA

EX

ID

IF

WB

MA

EX

ID

WB

MA

EX

WB

MA

WB

The instruction is never in any order executed. Accordingly, if command A enters the pipeline before

command B, command A always reaches write backstage before command B.

As a rule, the instruction is executed at the speed of one instruction per cycle. However, a number of cycles

27

Page 42

CHAPTER 3 CPU

are required to execute commands for the load/store command to which memory wait is attached, branch

commands that do not have delay slots, and multi -cycle commands. Also, when the supplied instruction is

slow, the execution speed of the instruction decrease.

Refer to "3.8 Overview of Instructions" for details.

32-bit ↔ 16-bit bus converter

●

Interfaces between the D-BUS that quickly accesses at 32-bit width and the R-BUS that accesses at 16-bit

width, and realizes data access from the CPU to built-in peripheral circuit.

When 32-bit width access is performed from the CPU, this bus converter accesses the R-BUS by

converting it to 16-bit width access twice. Some of built-in peripheral circuits have access width-related

restrictions.

Harvard ↔ Princeton bus converter

●

Coordinates between the CPU command access and data access, and realizes smooth interface with the

external bus.

In CPU, the instruction bus and the data bus are the independent Harvard architecture structures. On the

other hand, the bus controller that controls the external bus has a Princeton architectural structure with a

single bus. This bus converter ranks the priority order for command access and data access of the CPU, and

controls access to the bus controller. This operation always optimizes the external bus access ranking.

It also has a two-word write buffer to eliminate CPU bus waiting time and a one-word pre-fetch buffer to

fetch commands.

28

Page 43

3.3 Dedicated Registers

Use the dedicated registers for specified purposes. Program counter (PC), program