Page 1

FUJITSU MICROELECTRONICS

DATA SHEET

DS04-21215-3Ea

ASSP

IF Band

PLL Frequency Synthesizer

MB15C101

■ DESCRIPTION

The Fujitsu Microelectronics MB15C101 is an exclusive Int ermediate Frequency (IF) band Phase Locked Loop (PLL)

frequency synthesizer with pulse swallow operation. The r eference divider and comparison divider have fixed divide

ratios, so that it is not required to set the divide ratios by a microcontroller externally.

It operates with a supply voltage of 3.0 V typ. and dissipates 1.0 mA typ.(270MHz) of current realized through the

use of Fujitsu Microelectronics’s CMOS technology.

The MB15C101 is ideally suitable for PHS systems.

■ FEATURES

• Low power supply current: ICC = 1.0 mA typ. (VCC = 3 V, 270MHz)

• Pulse swallow function; Prescaler: 16/17

• Setting frequency (Selectable by Div input.)

– fosc = 19.2 MHz, fIF = 233.15 MHz (Div = “H”)

– fosc = 19.2 MHz, fIF = 259.20 MHz (Div = “L”)

• Lock detector

• Low power supply voltage: V

• Wide operating temperature: Ta = –40 to +85°C

■ PACKAGE

8-pin plastic SSOP

CC = 2.4 V min.

16-pad plastic BCC

1999.4

(FPT-8P-M03)

(LCC-16P-M06)

1Copyright©1999-2008 FUJITSU MICROELECTRONICS LIMITED All rights reserved

Page 2

MB15C101

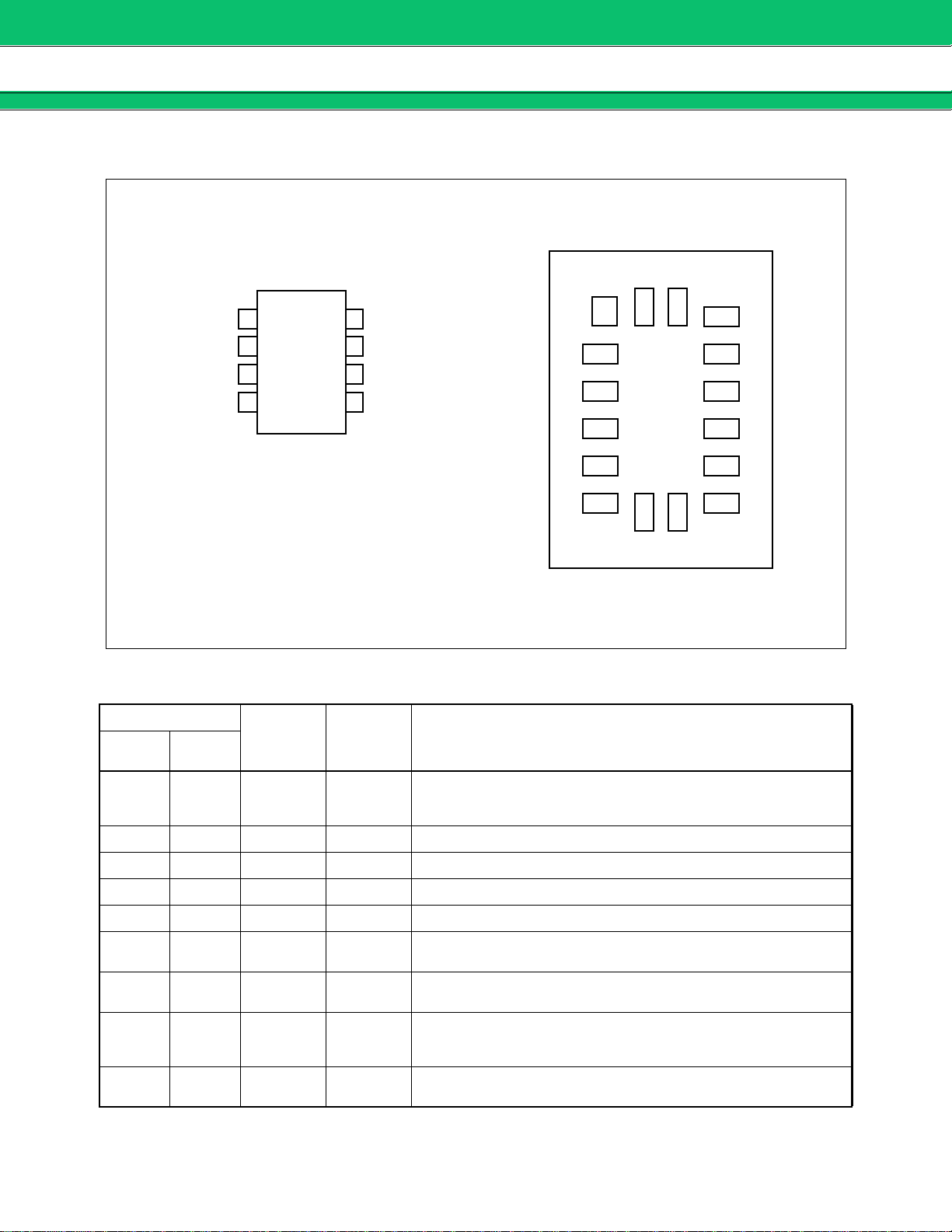

■ PIN ASSIGNMENT

(TOP VIEW)

N.C. N.C.

VCC

DO

GND

fin

(TOP VIEW)

1

2

3

4

(FPT-8P-M03)

■ PIN DESCRIPTIONS

Pin No.

SSOP-8BCC-

16

1,6,7,8,

–

9,14,

15,16

110V

Pin

name

N.C – No connection

16 15

DIV

fout

LD

1

2

3

4

5

6

78

N.C. N.C.

IN

OSC

8

LD

7

fout

6

DIV

5

N.C.

OSCin

N.C.

(LCC-16P-M06)

I/O Descriptions

CC – Po wer supply voltage input (2.4 V to 3.6 V).

14

13

12

11

10

N.C.

fin

GND

D

O

VCC

9

N.C.

211D

O O Charge pump output

312GND –Ground

4 13 fin I Prescaler input. Connection should be with AC coupling.

5 2 Div I

63fout O

Divide ratio switching input. Two kinds of divide ratios are

selectable by Div input “H” or “L”.

Test purpose output. This pin is an open drain output so that

should be left open usually.

Lock detector output.

74LD O

LD = H ; Lock

LD = L ; Unlock

8 5 OSCin I

Reference counter input. Connection should be with AC

coupling.

2

Page 3

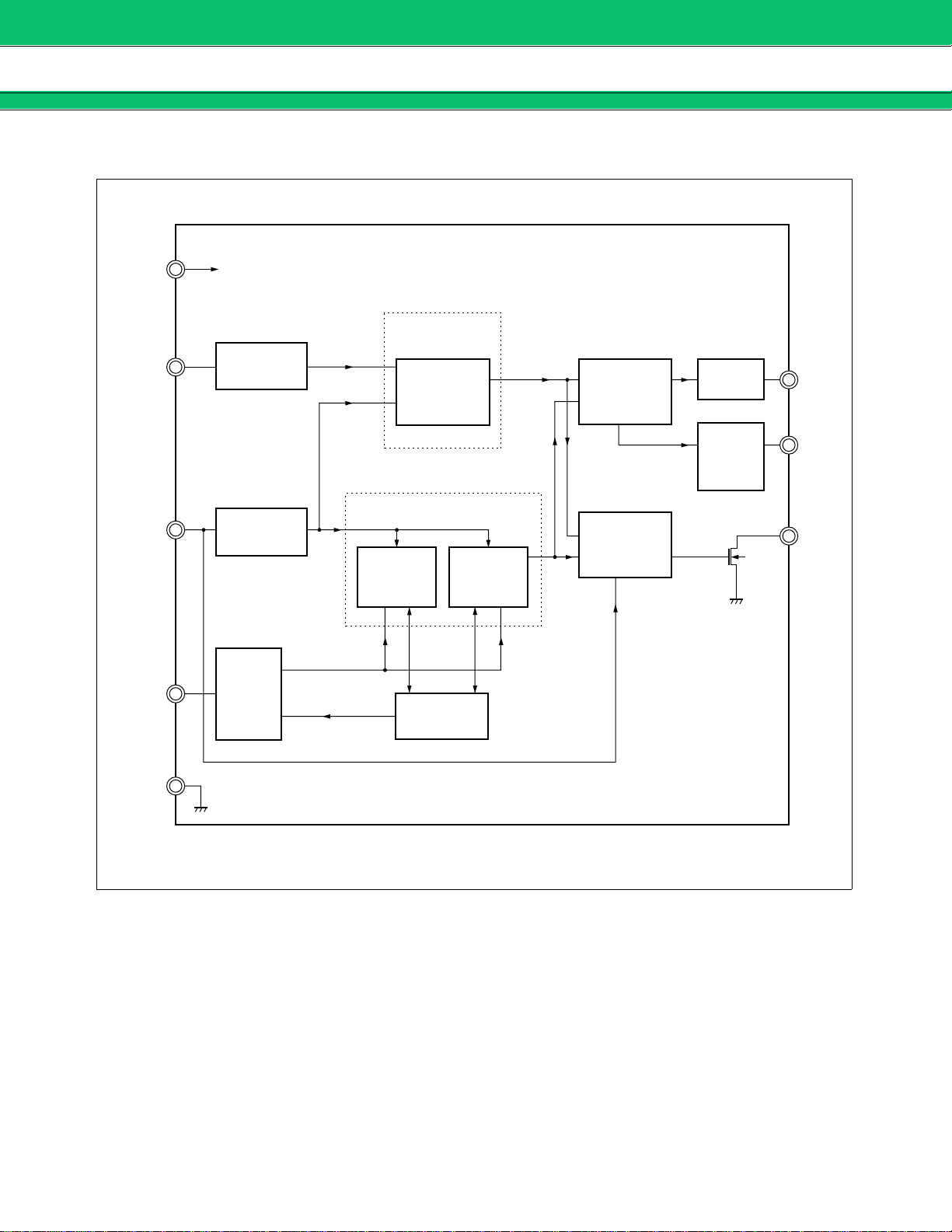

■ BLOCK DIAGRAM

VCC

OSCIN

Oscillator

input

buffer

Reference divider

Reference

counter

(R)

MB15C101

fr

Phase

comparator

fp

charge

pump

Do

DIV

fin

GND

Data

setting

circuit

Prescaler

16 / 17(P)

Comparison divider

Swallow

counter

(A)

Control circuit

Main

counter

(N)

Output

selector

Lock

detector

LD

fout

3

Page 4

MB15C101

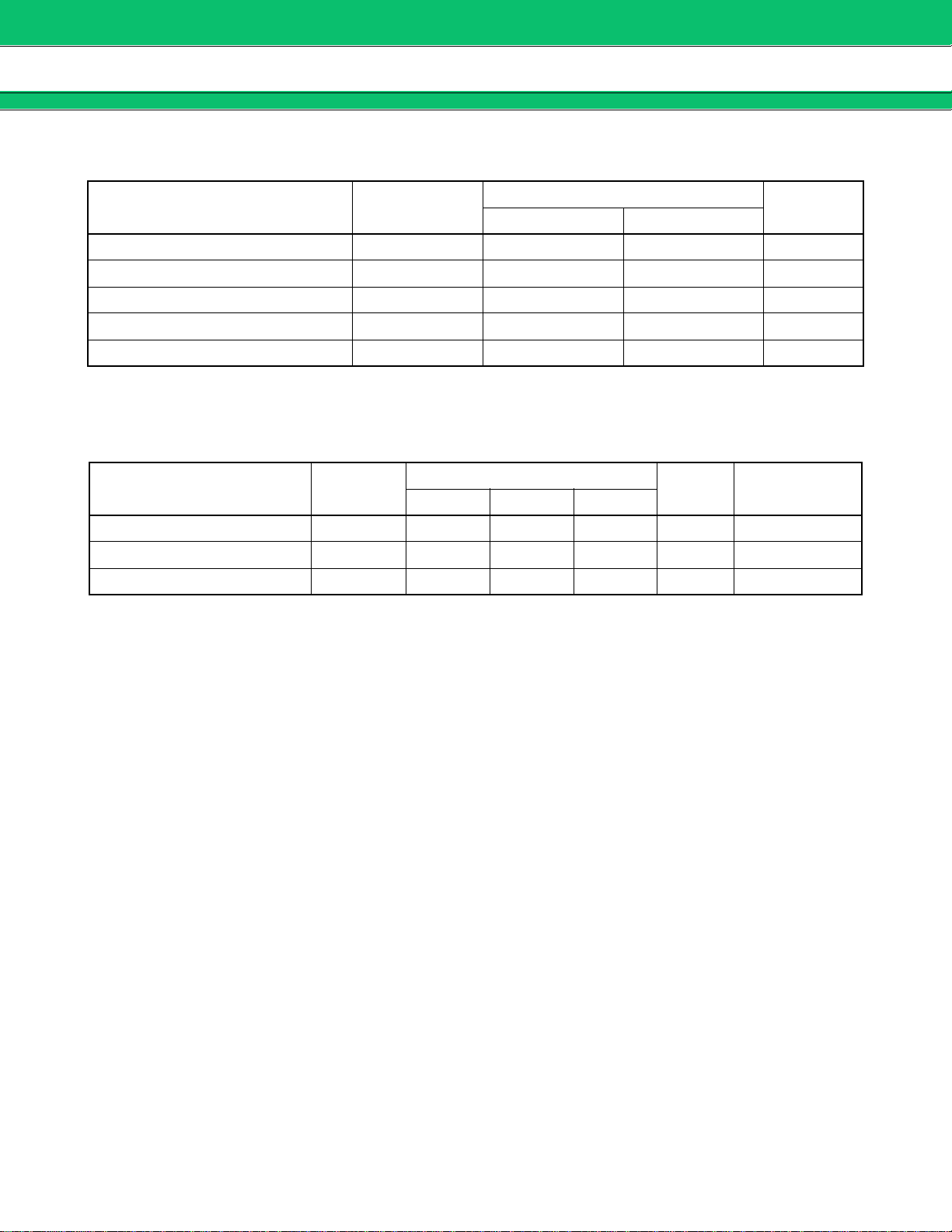

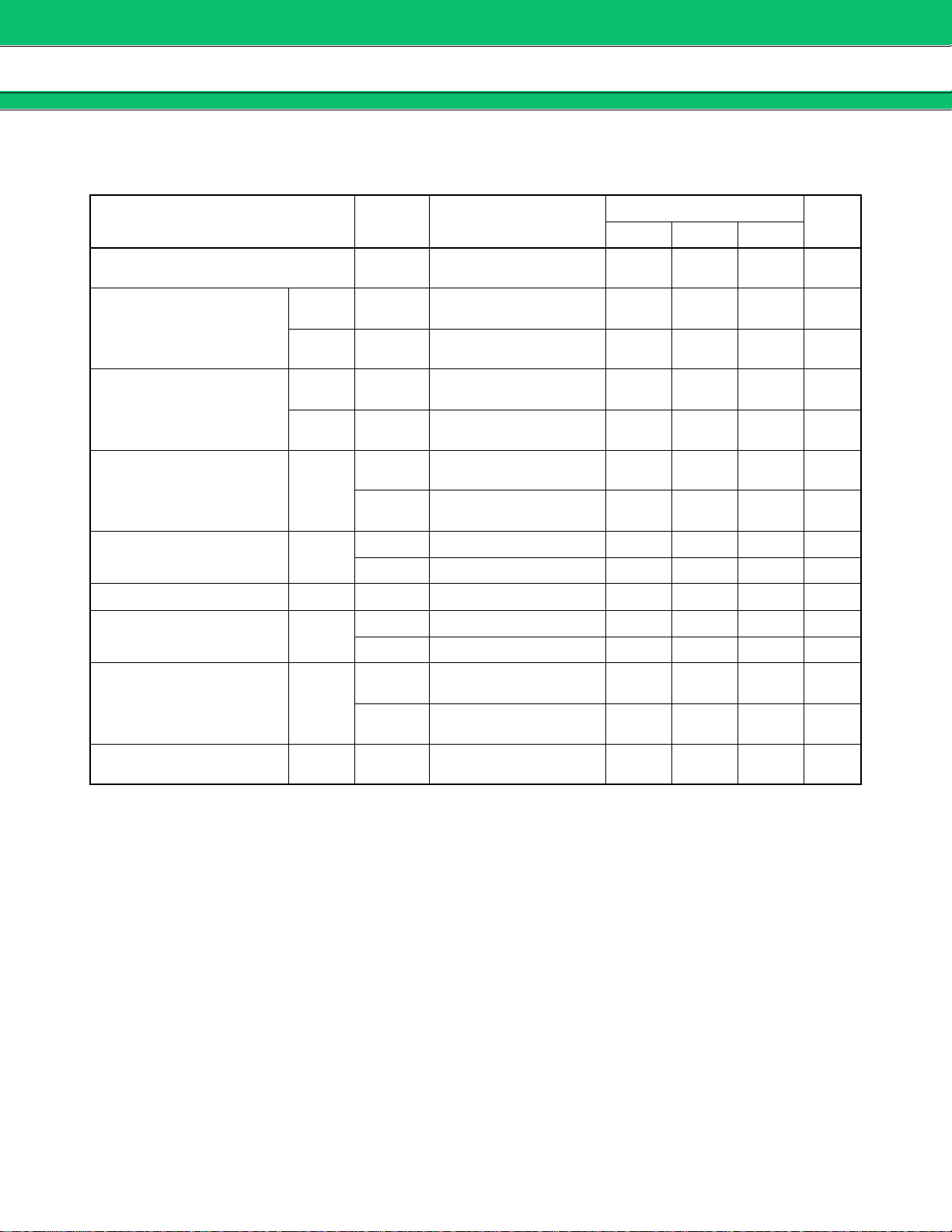

■ ABSOLUTE MAXIMUM RATINGS

Parameter Symbol

Unit

Min. Max.

Rating

Power supply voltage V

Input voltage V

Output voltage V

Output current I

Storage temperature T

CC –0.5 +4.0 V

I –0.5 VCC +0.5 V

OUT –0.5 VCC +0.5 V

OUT 0+5mA

STG –55 +125 °C

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current,

temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

■ RECOMMENDED OPERATING CONDITIONS

Parameter Symbol

Min. Typ. Max.

Power supply voltage V

Input voltage V

CC 2.4 3.0 3.6 V

IN GND – VCC V

Operating temperature Ta –40 – +85 °C

Handling Precautions

• This device should be transported and stored in anti-static containers.

Value

Unit Note

• This is a static-sensitive device; take proper anti-ESD precautions. Ensure that personnel a nd equipment are

properly grounded. Cover workbenches with grounded conductive mats.

• Always turn the power supply off before inserting or removing the device from its socket.

• Protect leads with a conductive sheet when handling or transporting PC boards with devices.

4

Page 5

■ ELECTRICAL CHARACTERISTICS

Parameter Symbol Condition

Power supply current I

CC

MB15C101

Recommended operating conditions unless otherwise noted.

Value

Min. Typ. Max.

PLL is locked.(270MHz)

V

CC = 3.0 V, Ta = +25°C

0.1 1.0 2.0 mA

Unit

fin fin

Operating frequency

OSC

fin Pfin

Input sensitivity

OSC

Input voltage Div

Input current Div

Input current OSC

Output voltage Do

Output current Do

High impedance cut off

current

Do I

AC coupling by 100 0 pF

capacitor

IN fosc

AC coupling by 100 0 pF

capacitor

AC coupling by 100 0 pF

capacitor

IN Vosc

V

V

I

I

IN IOSC – –100 – 100 µA

V

V

I

I

OFF 0 ≤ VDO ≤ VCC ––3nA

AC coupling by 100 0 pF

capacitor

IH –

IL –––

IH –––1.0µA

IL ––1.0––µA

OH VCC = 3.0 V, IOH=–0.3mA 2.6 – – V

OL VCC = 3.0 V, IOL= 0.3mA – – 0.4 V

VCC = 3.0 V, VOH = 2V,

OH

Ta = +25°C

VCC = 3.0 V, VOL = 1V,

OL

Ta = +25°C

50 – 270 MHz

3–26MHz

–10 – +2 dBm

0.5 – – Vpp

CC ×

V

0.7

––V

CC ×

V

0.3

V

– –6.0 – mA

–6.0–mA

5

Page 6

MB15C101

■ FUNCTIONAL DESCRIPTIONS

Two different frequencies can be selected by Div input “H” or “L”.

The divide ratios are calculated using the following equation:

f

VCO = {(P × N) + A} × fOSC ÷ R (A < N)

Symbol Description Div = “H” Div = “L”

fvco Output frequency of external VCO 233.15 MHz 259.20 MHz

fosc Reference oscillation frequency 19.2 MHz 19.2 MHz

N Divide ratio of the main counter 291 33

A Divide ratio of the swallow counter 7 12

P

R Divide ratio of the reference counter 384 (fr = 50 kHz) 40 (fr = 480 kHz)

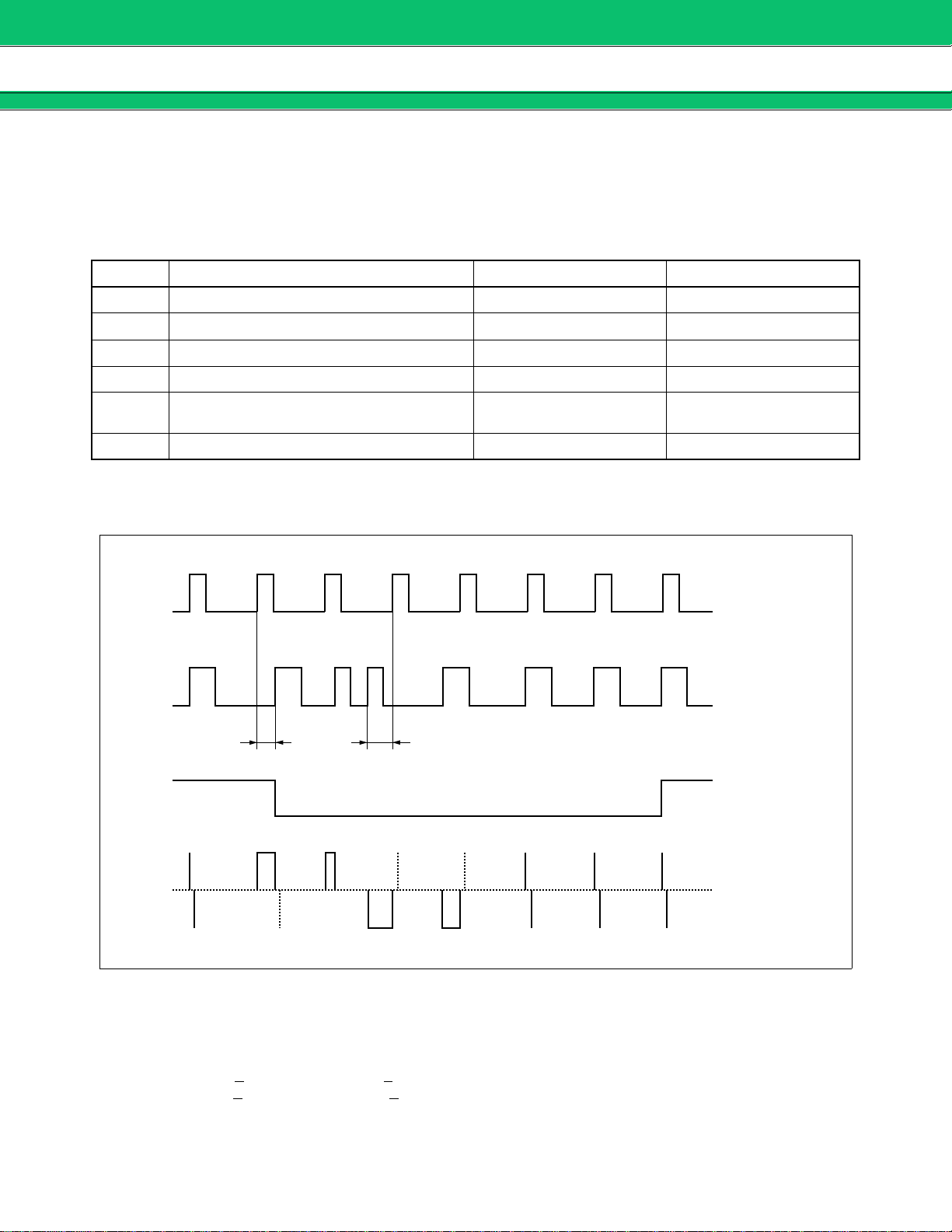

■ PHASE DETECTOR TIME CHART

Preset divide ratio of dual modulus

prescaler

16/17 16/17

fr

fp

WLtWU

t

LD

D

O High impedance

Note: • .Phase error detection range: –2π to +2π

• Pulses on Do output signal during locked state are output to prevent dead zone.

• LD output becomes low when phase is t

WU or more. LD output becomes high wh en phase error is tWL or

less and continues to be so for three cycles or more.

•.t

WU and tWL depend on OSCin input frequency.

t

WU > 8/fosc (s) (e. g.tWU > 625.0ns, foscin = 12.8 MHz)

tWL < 16/fosc (s) (e. g. tWL < 1250.0ns, foscin = 12.8 MHz)

6

Page 7

■ MEASURMENT CIRCUIT (for measuring input sensitivity fin/OSCin)

SSOP-8

V

CC

1

8

1000 pF

MB15C101

S.G

S.G

BCC-16

50

0.1 µF

2

3

4

1000 pF

Ω

9

V

CC

10

7

6

5

87

6

5

VCC

2 K

Ω

1000 pF

50

DIV : H or L

Ω

Oscilloscope

S.G

S.G

50 Ω

0.1 µF

1000 pF

11

12

13

14

15 16

V

CC

4

2 KΩ

3

2

1

50 Ω

Oscilloscope

DIV : H or L

7

Page 8

MB15C101

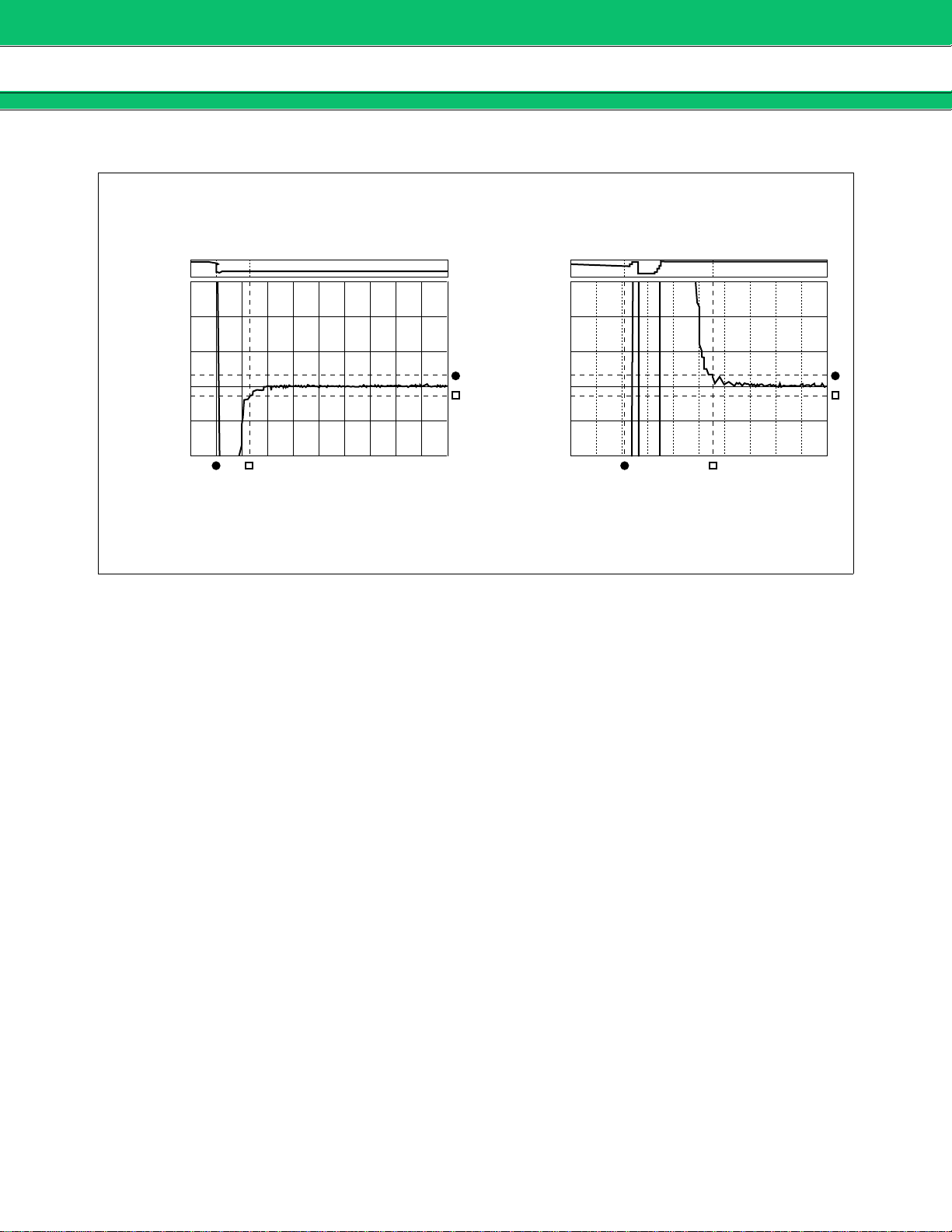

■ TYPICAL CHARACTERISTICS

1. fin Input Sensitivity

Pfin (dBm)

2. OSC

Vosc (dBm)

(dBm)

10

5

0

−5

−10

−15

−20

−25

−30

−35

−40

−45

−50

0 100 200 300 400 500 600 700 800 900

IN Input Sensitivity

(dBm)

10

5

0

−5

−10

−15

−20

−25

−30

−35

−40

−45

−50

0 102030405060708090

SPEC

fin (MHz)

SPEC

fosc (MHz)

Ta = +25 °C

VCC = 2.4 V

V

CC = 3.0 V

V

CC = 3.6 V

Ta = +25 °C

VCC = 2.4 V

V

CC = 3.0 V

V

CC = 3.6 V

1000 (MHz)

100 (MHz)

8

Page 9

3. fin Input Impedance

4 : 11.867 Ω−131.54 Ω 4.0331 pF

300.000 000 MHz

1 : 58.875 Ω

−850.16 kΩ

50 MHz

2 : 16.891 Ω

−416.2 Ω

100 MHz

3 : 12.047 Ω

−202.87 Ω

200 MHz

1

2

4

3

MB15C101

4. OSC

IN Input Impedance

START .500 000 MHz

STOP 1 000.000 000 MHz

4 : 068.25 Ω−1.4236 Ω 4.3 pF

26.000 000 MHz

5.1345 Ω

1 :

−10.288 kΩ

3 MHz

529.87 Ω

2 :

−3.6659 kΩ

10 MHz

114.44 Ω

3 :

−1.8514 kΩ

4

20 MHz

1

2

3

START .500 000 MHz STOP 100.000 000 MHz

9

Page 10

MB15C101

5. Do Outut Current

VOH – IOH

CC = 3.0 V, Ta =+ 25 °C

3.0

2.5

2.0

1.5

VOH (V)

1.0

0.5

0.0

0 −2 −4 −6 −8 −10 −12

IOH (mA)

V

Measurement Circuit

S.G.

VOL – IOL

V

3.0

2.5

2.0

1.5

VOL (V)

1.0

0.5

0.0

024681012

IOL (mA)

fin

OSCin

50 Ω

1000 pF

CC = 3.0 V, Ta = +25 °C

VCC

V

CC

GND

Do

IOH

Parameter Analyzer

10

S.G.

50 Ω

1000 pF

fin

OSCin

VCC

CC

V

GND

Do

IOL

Parameter Analyzer

Page 11

■ REFERENCE INFORMATION

1. Application Measurement

• Test Results

Lockup time ±1 kHz

Un lock → Lock

Pow er on → Lock

Reference leakage (∆f = 58 kHz) –88.5 dBc

Phase noise (∆f = 1 kHz)

V

CC (V) 3.0 V

VCO

• Measurement Circuit

(∆f = 10 kHz)

(∆f = 100 kHz)

(∆f = 1 MHz)

–111.0 dBc/Hz

–118.0 dBc/Hz

–134.0 dBc/Hz

Discrete VCO (Kv = 3.5 MHz/V)

Lock Frequency = 274.0 MHz (fr = 58 kHz)

MB15C101

Results

2.3 ms

3.4 ms

–88.0 dBc/Hz

18 Ω 18 Ω

S.G

1000 pF

1000 pF

50 Ω

fin

OSCin

VCC = 3.0 V

MB15C101

Loop Filter

C1

R2

C2

R1

18 Ω

C3

Spectrum

Analyzer

VCO

C1 = 6800 pF

C2 = 0.068 µF

C3 = 4800 pF

R1 = 3.0 kΩ

R2 = 3.9 KΩ

11

Page 12

MB15C101

2. Phase Noise

∆ f = 1 kHz

ATTEN 10dB

RL −1.5 dBm 10 dB/

D

CENTER 273.999827 MHz

RBW 30 Hz VBW 3.0 Hz

∆ f = 100 kHz

ATTEN 10 dB

RL −1.5 dBm 10 dB/

D

SPAN 2.0 kHz

SPAN 200 kHz

∆MKR −73.83 dB

1.000 kHz

SPAN 2.000 kHz

SWP 3.00 sec

∆MKR −88.50 dB

58.0 kHz

∆ f = 10 kHz

ATTEN 10dB

RL −1.5 dBm 10 dB/

D

CENTER 273.999827 MHz

RBW 100 Hz VBW 30 Hz

∆ f = 1 MHz

ATTEN 10dB

RL −30.0 dBm 10 dB/

D

SPAN 20 kHz

SPAN 2 MHz

∆MKR −91.83 dB

10.00 kHz

SPAN 20.00 kHz

SWP 30. 0 sec

∆MKR −105.5 dB

275.000 MHz

12

CENTER 274.0002 MHz

RBW 1.0 kHz VBW 30 Hz

SPAN 200.0 kHz

SWP 30.0 sec

START 274.000 MHz

RBW 1.0 Hz VBW 100 Hz

STOP 276.000 MHz

SWP 100 sec

Page 13

3. Lockup Time: Un-Lock to Lock

MB15C101

∆ Mkr : 2.30 ms

30.00300

MHz

1.00

kHz/div

29.99800

MHz

Un-Lock to Lock : DIV = “L” to “H”

0 s

20.0000000 ms

∆ Mkr : 3.40 ms

30.00300

MHz

1.000

kHz/div

29.99800

MHz

0 s

V

CC “OFF” to VCC “ON”

10.0000000 ms

13

Page 14

MB15C101

■ ORDERING INFORMATION

Part number Package Remarks

MB15C101PFV

MB15C101PV1

8-pin, Plastic SSOP

(FPT-8P-M03)

16-pad, Plastic BCC

(LCC-16P-M06)

14

Page 15

■ PACKAGE DIMENSIONS

MB15C101

8-pin plastic SSOP

(FPT-8P-M03)

0.80(.0315)

TYP

*

3.50±0.10

(.138±.004)

INDEX

2.40(.094)REF

(.165±.004) (.244±.008)NOM

"A"

0.35±0.10

(.014±.004)

0.10(.004)

M

*: This dimension does not include resin protrusion.

+0.20

–0.10

1.25

.049

0.15

.006

+.008

–.004

5.20(.205)4.20±0.10

+0.05

–0.02

+.002

–.001

(Mounting height)

0.10(.004)

6.20±0.20

Details of "A" part

0 10°

0.10±0.10(.004±.004)

(STAND OFF)

0.50±0.20

(.020±.008)

C

1994 FUJITSU LIMITED F08005S-1C-2

Dimensions in mm (inches)

(Continued)

15

Page 16

MB15C101

(Continued)

16-pad plastic BCC

(LCC-16P-M06)

4.55±0.10

(.179±.004)

INDEX AREA

1 6

0.05(.002)

C

1999 FUJITSU LIMITED C16017S-1C-1

0.80(.031)MAX

Mounting height

3.40±0.10

(.134±.004)

0.075±0.025

(.003±.001)

(Stand off)

0.40±0.10

(.016±.004)

0.80(.031)

REF

2.45(.096)

TYP

Details of "A" part

(.030±.004)

0.40±0.10

(.016±.004)

0.65(.026)

TYP

9

6

0.75±0.10

3.40(.134)TYP

0.325±0.10

"A"

Details of "B" part

(.013±.004)

1.725(.068)

REF

0.60±0.10

(.024±.004)

"B"

0.60±0.10

(.024±.004)

14914

Dimensions in mm (inches)

1.15(.045)

REF

1

16

Page 17

MEMO

MB15C101

17

Page 18

MB15C101

MEMO

18

Page 19

MEMO

MB15C101

19

Page 20

FUJITSU MICROELECTRONICS LIMITED

Shinjuku Dai-Ichi Seimei Bldg. 7-1, Nishishinjuku 2-chome, Shinjuku-ku,

Tokyo 163-0722, Japan Tel: +81-3-5322-3347 Fax: +81-3-5322-3387

http://jp.fujitsu.com/fml/en/

For further information please contact:

North and South America

FUJITSU MICROELECTRONICS AMERICA, INC.

1250 E. Arques Avenue, M/S 333

Sunnyvale, CA 94085-5401, U.S.A.

Tel: +1-408-737-5600 Fax: +1-408-737-5999

http://www.fma.fujitsu.com/

Europe

FUJITSU MICROELECTRONICS EUROPE GmbH

Pittlerstrasse 47, 63225 Langen,

Germany

Tel: +49-6103-690-0 Fax: +49-6103-690-122

http://emea.fujitsu.com/microelectronics/

Korea

FUJITSU MICROELECTRONICS KOREA LTD.

206 KOSMO TOWER, 1002 Daechi-Dong,

Kangnam-Gu,Seoul 135-280

Korea

Tel: +82-2-3484-7100 Fax: +82-2-3484-7111

http://www.fmk.fujitsu.com/

Asia Pacific

FUJITSU MICROELECTRONICS ASIA PTE LTD.

151 Lorong Chuan, #05-08 New Tech Park,

Singapore 556741

Tel: +65-6281-0770 Fax: +65-6281-0220

http://www.fujitsu.com/sg/services/micro/semiconductor/

FUJITSU MICROELECTRONICS SHANGHAI CO., LTD.

Rm.3102, Bund Center, No.222 Yan An Road(E),

Shanghai 200002, China

Tel: +86-21-6335-1560 Fax: +86-21-6335-1605

http://cn.fujitsu.com/fmc/

FUJITSU MICROELECTRONICS PACIFIC ASIA LTD.

10/F., World Commerce Centre, 11 Canton Road

Tsimshatsui, Kowloon

Hong Kong

Tel: +852-2377-0226 Fax: +852-2376-3269

http://cn.fujitsu.com/fmc/tw

All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose

of reference to show examples of operations and uses of FUJITSU MICROELECTRONICS device; FUJITSU MICROELECTRONICS

does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information.

FUJITSU MICROELECTRONICS assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use

or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU MICROELECTRONICS

or any third party or does FUJITSU MICROELECTRONICS warrant non-infringement of any third-party's intellectual property right or

other right by using such information. FUJITSU MICROELECTRONICS assumes no liability for any infringement of the intellectual

property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without

limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured

as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect

to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in

nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in

weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU MICROELECTRONICS will not be liable against you and/or any third party for any claims or damages arising

in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by

incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current

levels and other abnormal operating conditions.

Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of

the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

Edited Strategic Business Development Dept.

Loading...

Loading...