Freescale Semiconductor MPC5604B, MPC5604C Reference Manual

Freescale Semiconductor

Rev. 8.2, 09/2013

MPC5604B/C Microcontroller

Reference Manual

This is the MPC5604B/C Reference Manual set consisting of the following files:

• MPC5604B/C Reference Manual Addendum (MPC5604B/CRMAD), Rev. 2

MPC5604BCRM

• MPC5604B/C Reference Manual (MPC5604B/CRM), Rev. 8

© Freescale Semiconductor, Inc., 2013. All rights reserved.

Freescale Semiconductor

MPC5604BRMAD

Reference Manual Addendum

MPC5604B/C Microcontroller

Reference Manual Addendum

Rev. 2, 09/2013

This addendum describes corrections to the

MPC5604B/C Microcontr oller Refer ence Manual, order

number MPC5604BCRM. For convenience, the addenda

items are grouped by revision. Please check our website

at http://www.freescale.com/powerarchitecture for the

latest updates.

The current version available of the MPC5604B/C

Microcontroller Reference Manual is Revision 8.1.

Table of Contents

1 Addendum List for Revision 8.1 . . . . . . . . . . . . . . 2

2 Addendum List for Revision 8. . . . . . . . . . . . . . . . 2

3 Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . 4

© Freescale Semiconductor, Inc., 2013. All rights reserved.

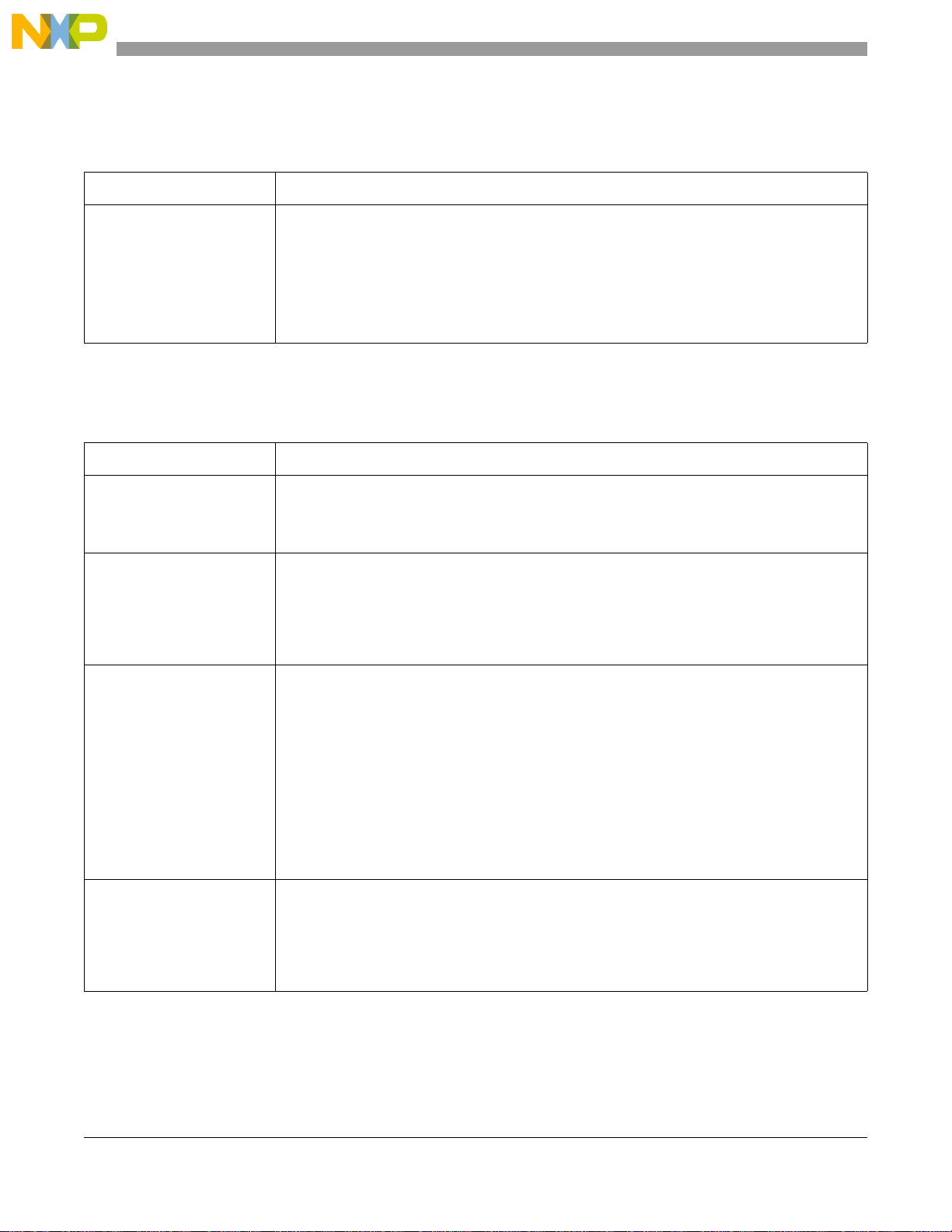

1 Addendum List for Revision 8.1

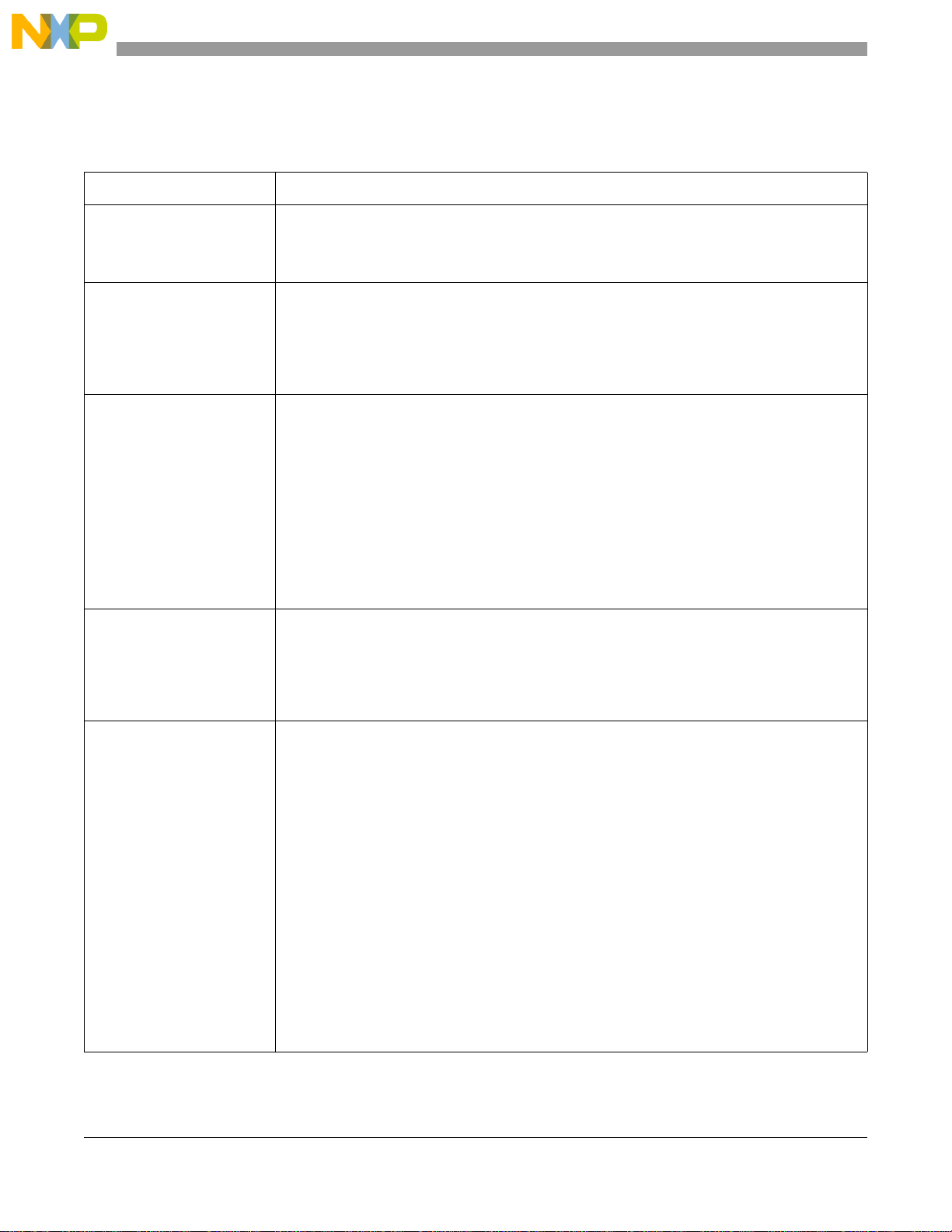

Table 1. MPC5604BCRM Rev 8.1 Addenda

Location Description

Chapter 27, “Flash Memory”

page 644

Add a note below Table 27-4, “CFlash TestFlash Structure”.

NOTE

Unique Device ID – Memory location. This device now includes a 128-bit Unique

Identification number (UID) which is programmed during device fabrication.

Start – Stop Address Size (Bytes) Content:

• 0x00403C10 0x00403C17 8 UID 1

• 0x00403C18 0x00403C1F 8 UID 2

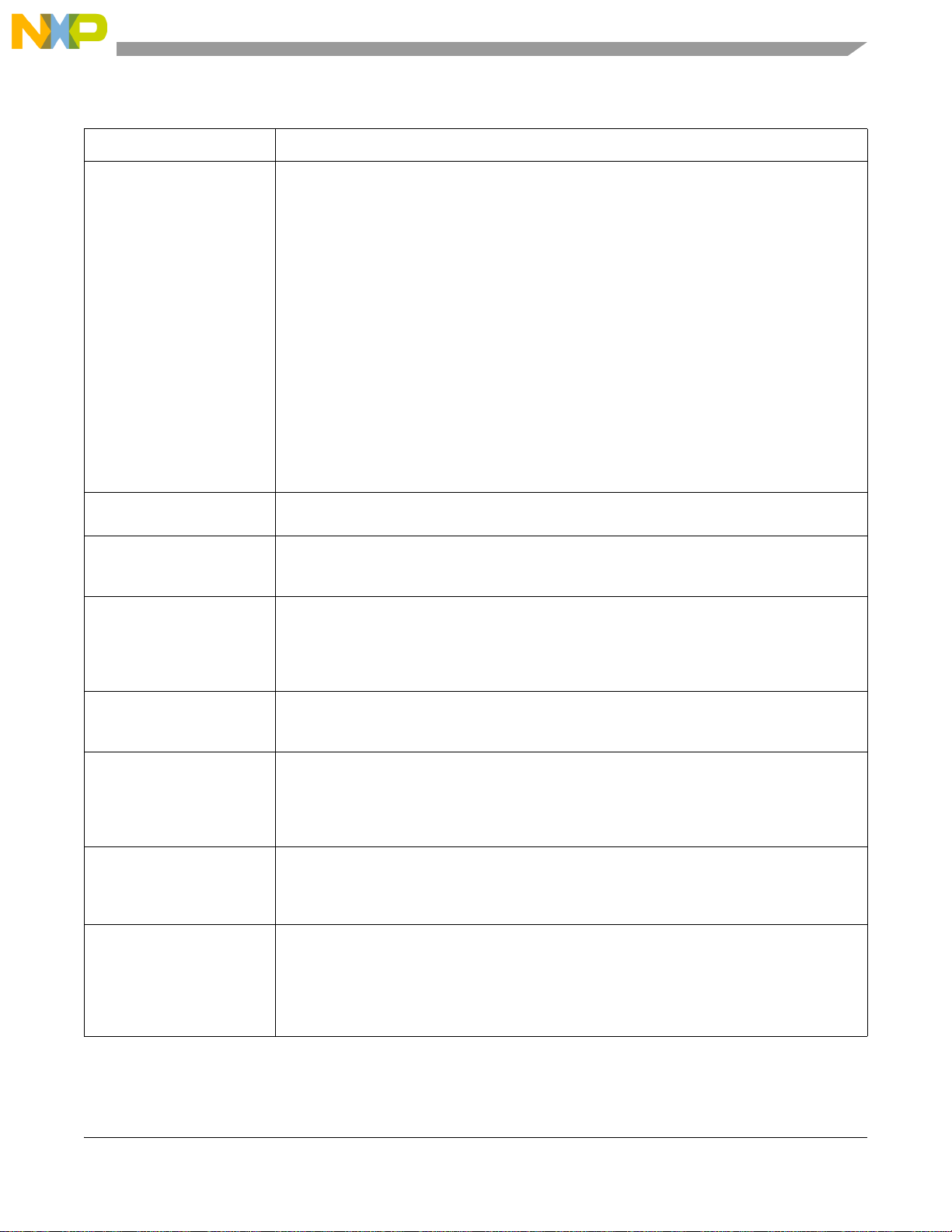

2 Addendum List for Revision 8

Table 2. MPC5604BCRM Rev 8 Addenda

Location Description

Chapter 4, Signal description,

page 60

Chapter 6, Clock Description,

page 113

Chapter 9, Reset Generation

Module (MC_RGM), page

209

In Table 4-3, Functional port pin descriptions, row PH[9], change the pin numbers for

MPC560xB 64 LQFP and MPC560xC 64 LQFP from “—” to 60.

In row PH[10], change the pin numbers for MPC560xB 64 LQFP and MPC560xC 64 LQFP

from “—” to 53.

Add Note: to Section 6.8.4.1, Crystal clock monitor:

Note: Functional FXOSC monitoring can only be guaranteed when the FXOSC frequency is

greater than (FIRC / 2

Add Note: to Section 6.8.4.2, FMPLL clock monitor:

Note: Functional FMPLL monitoring can only be guaranteed when the FMPLL frequency is

greater than (FIRC / 4) + 0.5 MHz.

Replace Section 9.4.7, Boot Mode Capturing, with the following:

The MC_RGM samples P A[9:8] whenev er RESET is asserted until five FIRC (16 MHz internal

RC oscillator) clock cycles before its deassertion edge. The result of the sampling is used at

the beginning of reset PHASE3 for boot mode selection and is retained after RESET has been

deasserted for subsequent boots after reset sequences during which RESET is not asserted.

RCDIV

)+0.5MHz.

Chapter 13, Real Time Clock /

Autonomous Periodic

Interrupt (RTC/API), page

262

Note: In order to ensure that the boot mode is correctly captured, the application needs to

apply the valid boot mode value the entire time that RESET is asserted.

RESET can be asserted as a consequence of the internal reset generation. This will force

re-sampling of the boot mode pins. (See Table 9-12 for details.)

In Table 13-3 (RTCC field descriptions), update Note in RTCC[APIVAL] field description:

Note: API functionality starts only when APIVAL is nonzero. The first API interrupt takes two

more cycles because of synchronization of APIVAL to the RTC cloc k, and APIVAL + 1 cycles

for subsequent occurrences. After that, interrupts are periodic in nature. Because of

synchronization issues, the minimum supported value of APIVAL is 4.

MPC5604BRMAD, Rev. 2

Freescale Semiconductor2

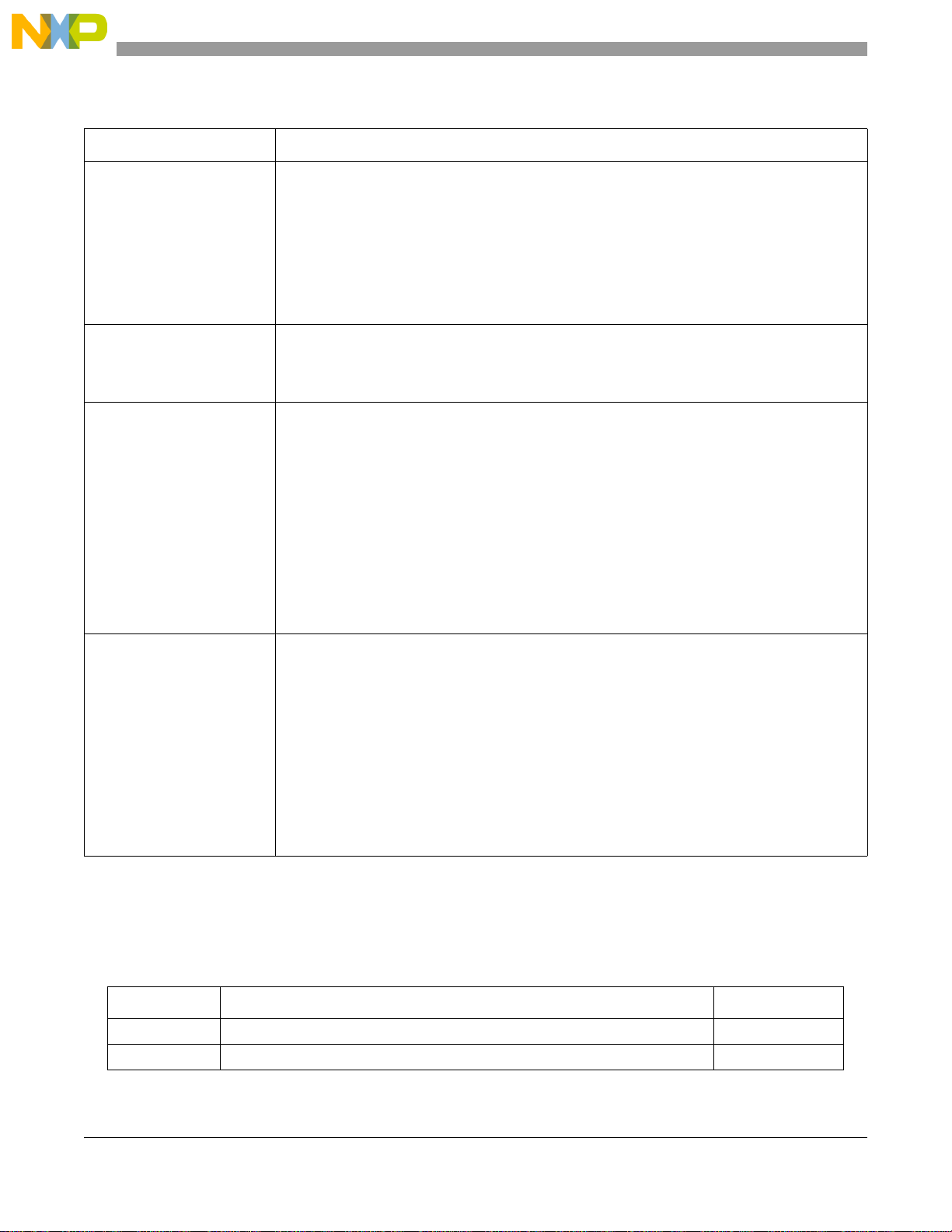

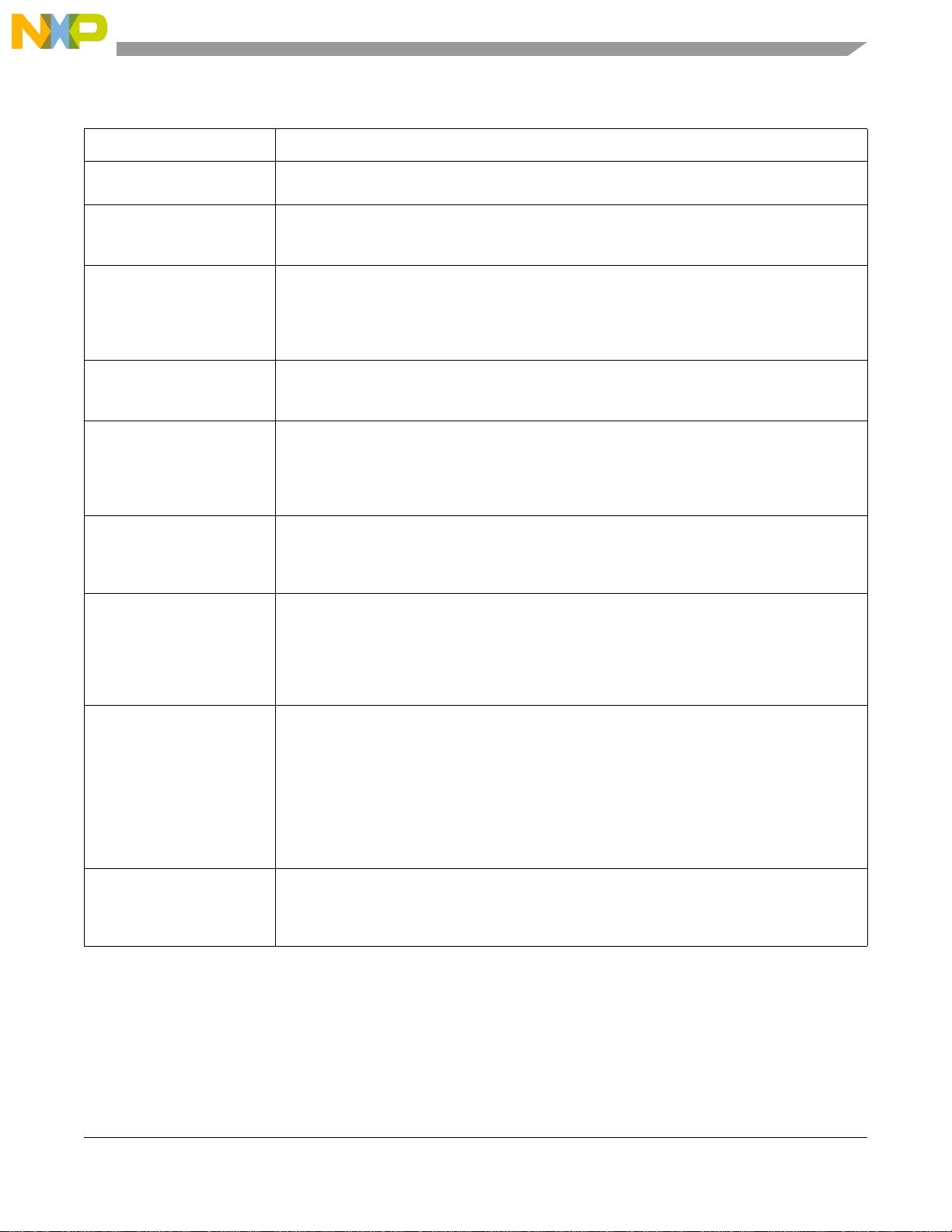

Table 2. MPC5604BCRM Rev 8 Addenda

Location Description

Chapter 21, LINFlex, p. 412 Insert the following section:

21.8.2.1.6 Overrun

Once the message buffer is full, the next valid message reception leads to an

overrun and a message is lost. The hardware sets the BOF bit in the LINSR to

signal the overrun condition. Which message is lost depends on the

configuration of the RX message buffer:

• If the buffer lock function is disabled (LINCR1[RBLM] = 0) the last

message stored in the buffer is overwritten by the new incoming

message. In this case the latest message is always available to the

application.

• If the buffer lock function is enabled (LINCR1[RBLM] = 0) the most

recent message is discarded and the previous message is available in the

buffer.

Chapter 22, FlexCAN,

throughout chapter

Chapter 22, FlexCAN, page

429

Chapter 22, FlexCAN, page

461

Chapter 22, FlexCAN, page

462

Chapter 22, FlexCAN, page

463

Chapter 25, Analog-to-Digital

Converter (ADC), page

Chapter 25, Analog-to-Digital

Converter (ADC), page 597

Remove references throughout the chapter to “low-cost MCUs.”

Add this Note in the RTR field description of Table 22-4 (Message Buffer Structure field

description):

Note: Do not configure the last Message Buffer to be the RTR frame.

In Section 22.4.9.4, Protocol timing, update the Note following Figure 22-16 (CAN engine

clocking scheme) to read: “This clock selection feature may not be available in all MCUs. A

particular MCU may not have a PLL, in which case it would have only the oscillator clock, or

it may use only the PLL clock feeding the FlexCAN module. In these cases, the CLK_SRC bit

in the CTRL Register has no effect on the module operation.”

Update the table title of Table 22-20 from “CAN Standard Compliant Bit Time Segment Settings”

to “Bosch CAN 2.0B standard compliant bit time segment settings.”

In Section 22.4.9.4, Protocol timing, update the Note following Table 22-20 to read: “Other

combinations of Time Segment 1 and Time Segment 2 can be valid. It is the user’s

responsibility to ensure the bit time settings are in compliance with the CAN standard. For bit

time calculations, use an IPT (Information Processing Time) of 2, which is the value

implemented in the FlexCAN module.”

In Section 28.3.5.2, Presampling channel enable signals, in Table 28-7, Presampling voltage

selection based on PREVALx fields, in the 01 row, change the “Presampling voltage” field to:

V1 = V

DD_HV_ADC0

In Section 25.3.2, Analog clock generator and conversion timings, remove the paragraph:

The direct clock should basically be used only in low power mode when the device is using

only the 16 MHz fast internal RC oscillator, but the conversion still requires a 16 MHz clock

(an 8 MHz clock is not fast enough). In all other cases, the ADC should use the clock divided

by two internally.

or V

DD_HV_ADC1

.

MPC5604BRMAD, Rev. 2

Freescale Semiconductor 3

Table 2. MPC5604BCRM Rev 8 Addenda

Location Description

Chapter 25, Analog-to-Digital

Converter (ADC), p. 600

Chapter 25, Analog-to-Digital

Converter (ADC), page 603

Chapter 25, Analog-to-Digital

Converter (ADC), page 610

Chapter 26, Cross Triggering

Unit (CTU), page 633

In Section 25.3.4.2, CTU in trigger mode, replace the sentence:

If another CTU conversion is triggered before the end of the conversion, that request is

discarded.

with:

If another CTU conversion is triggered before the end of the conversion, that request is

discarded. However, if the CTU has triggered a conversion that is still ongoing on a channel,

it will buffer a second request fo r the channel and wait for the end of the first conv ersion before

requesting another conversion. Thus, two conversion requests close together will both be

serviced.

Add Note to Section 25.3.10, Auto-clock-off mode:

Note: The auto-clock-off feature cannot operate when the digital interface runs at the same

rate as the analog interface. This means that when MCR.ADCCLKSEL = 1, the analog clock

will not shut down in IDLE mode.

In Section 25.4.6.2, Main Status Register (MSR), replace the ADCST ATUS field description with

the following:

The value of this parameter depends on ADC status:

000 IDLE — The ADC is powered up but idle.

001 Power-down — The ADC is powered down.

010 Wait state — The ADC is waiting for an external multiplexer . This occurs only when the

DSDR register is nonzero.

011 Reserved

100 Sample — The ADC is sampling the analog signal.

101 Reserved

110 Conversion — The ADC is converting the sampled signal.

111 Reserved

At the end of Section 26.4.1, Event Configuration Registers (CTU_EVTCFGRx) (x = 0...63), add

the following Note:

NOTE

The CTU tracks issued conversion requests to the ADC. When the ADC

is being triggered by the CTU and there is a need to shut down the ADC,

the ADC must be allowed to complete conversions before being shut

down. This ensures that the CTU is notified of completion; if the ADC

is shut down while performing a CTU-triggered conversion, the CTU is

not notified and will not be able to trigger further conversions until the

device is reset.

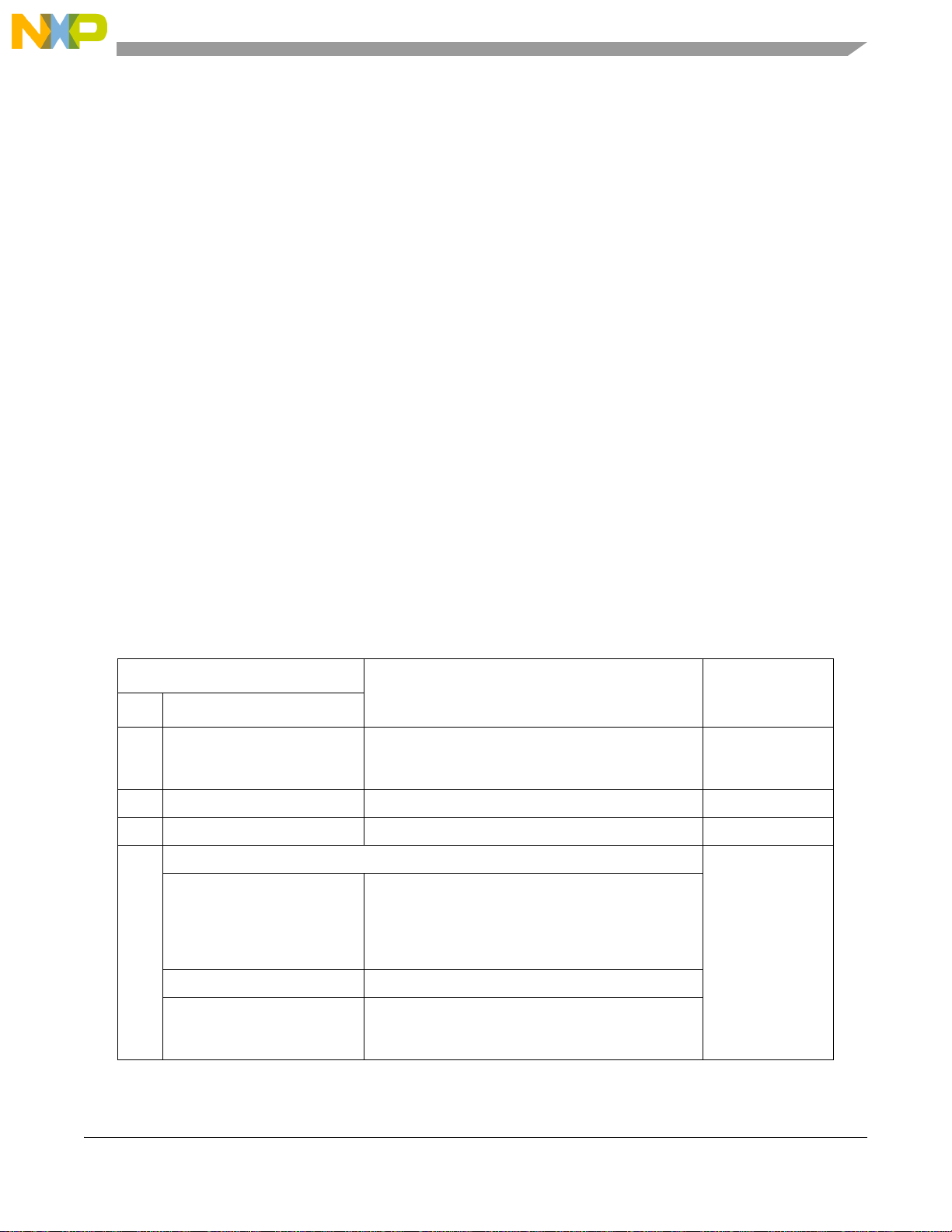

3 Revision History

Table 3 provides a revision history for this reference manual addendum document.

Table 3. Revision History Table

Rev. Number Substantive Changes Date of Release

2.0 Add a note below Table 27-4, “CFlash TestFlash Structure” 09/2013

1.0 Initial release. 05/2012

MPC5604BRMAD, Rev. 2

Freescale Semiconductor4

How to Reach Us:

Home Page:

www.freescale.com

Web Support:

http://www.freescale.com/support

USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

+1-800-521-6274 or +1-480-768-2130

www.freescale.com/support

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH

Technical Information Center

Schatzbogen 7

81829 Muenchen, Germany

+44 1296 380 456 (English)

+46 8 52200080 (English)

+49 89 92103 559 (German)

+33 1 69 35 48 48 (French)

www.freescale.com/support

Japan:

Freescale Semiconductor Japan Ltd.

Headquarters

ARCO Tower 15F

1-8-1, Shimo-Meguro, Meguro-ku,

Tokyo 153-0064

Japan

0120 191014 or +81 3 5437 9125

support.japan@freescale.com

Asia/Pacific:

Freescale Semiconductor China Ltd.

Exchange Building 23F

No. 118 Jianguo Road

Chaoyang District

Beijing 100022

China

+86 10 5879 8000

support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and

software implementers to use F reescale S emiconductor prod ucts. There ar e

no express or implied copyright licenses granted hereunder to design or

fabricate any integrated circuits or integrated circuits based on the

information in this document.

Freescale Semiconducto r reserves the right to mak e changes without further

notice to any products herein. F reescale Se miconductor m akes no w arranty,

representation or guarantee regarding the suitability of its products for any

particular purpose, nor does Freescale Semiconductor assume any liability

arising out of the application or use of any produ ct or circuit, an d specific ally

disclaims any and all liability, including without limitation consequential or

incidental damages. “Typical” par ameter s that m a y be pro vided in Freescale

Semiconductor data sheets and/or speci fications can and do v ary in differ ent

applications and actual performance may vary over time. All operating

parameters, including “Typicals”, must be validated for each customer

application by customer’s technical experts. Freescale Semiconductor does

not convey any license under its patent rights nor the rights of others.

Freescale Semicondu ctor products are not de signed, intended, or authorized

for use as components in systems intended for surgical implant into the body ,

or other applications intended to support or sustain life, or for any other

application in which the failure of the Freescale Semiconductor product could

create a situation where personal injury or death may occur. Should Buyer

purchase or use Freescal e Semiconductor products f or an y such unintended

or unauthorized application, B uyer sha ll indemnify and hold Freescale

Semiconductor and its officers, employees, subsidiaries, affiliates, and

distributors harmless against all claims, costs, damages, and expenses, and

reasonable attorney fees arising out of, directly or indirectly, any claim of

personal injury or death associated with such unintended or unauthorized

use, even if such claim alleges that Freescale Semiconductor was negligent

regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale

Semiconductor, Inc. All other product or service names are the property

of their respective owners.© Freescale Semiconductor, Inc. 2013. All rights

reserved.

MPC5604BRMAD

Rev. 2

09/2013

Freescale Semiconductor

Rev. 8.1, 05/2012

MPC5604B/C Microcontroller

Reference Manual

by: Microcontroller Solutions Group

This is the MPC5604B/C Reference Manual set consisting of the following files:

MPC5604BCRM

• MPC5604B/C Reference Manual Addendum (MPC5604B/CRMAD), Rev. 1

• MPC5604B/C Reference Manual (MPC5604B/CRM), Rev. 8

© Freescale Semiconductor, Inc., 2012. All rights reserved.

Freescale Semiconductor

MPC5604BRMAD

Reference Manual Addendum

MPC5604B/C Microcontroller

Reference Manual Addendum

by: Microcontroller Solutions Group

Rev. 1, 05/2012

This addendum document describes corrections to the

MPC5604B/C Microcontr oller Refer ence Manual, order

number MPC5604BCRM. For convenience, the addenda

items are grouped by revision. Please check our website

at http://www.freescale.com/powerarchitecture for the

latest updates.

The current version available of the MPC5604B/C

Microcontroller Reference Manual is Revision 8.

Table of Contents

1 Addendum for Revision 8 . . . . . . . . . . . . . . . . . . . 2

2 Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . 4

© Freescale Semiconductor, Inc., 2012. All rights reserved.

Addendum List for Revision 8

1 Addendum List for Revision 8

Table 1. MPC5604BCRM Rev 8 Addenda

Location Description

Chapter 4, Signal description,

page 60

Chapter 6, Clock Description,

page 113

Chapter 9, Reset Generation

Module (MC_RGM), page

209

Chapter 13, Real Time Clock /

Autonomous Periodic

Interrupt (RTC/API), page

262

Chapter 21, LINFlex, p. 412 Insert the following section:

In Table 4-3, Functional port pin descriptions, row PH[9], change the pin numbers for

MPC560xB 64 LQFP and MPC560xC 64 LQFP from “—” to 60.

In row PH[10], change the pin numbers for MPC560xB 64 LQFP and MPC560xC 64 LQFP

from “—” to 53.

Add Note: to Section 6.8.4.1, Crystal clock monitor:

Note: Functional FXOSC monitoring can only be guaranteed when the FXOSC frequency is

greater than (FIRC / 2

Add Note: to Section 6.8.4.2, FMPLL clock monitor:

Note: Functional FMPLL monitoring can only be guaranteed when the FMPLL frequency is

greater than (FIRC / 4) + 0.5 MHz.

Replaced Section 9.4.7, Boot Mode Capturing, with the following:

The MC_RGM samples P A[9:8] whenev er RESET is asserted until five FIRC (16 MHz internal

RC oscillator) clock cycles before its deassertion edge. The result of the sampling is used at

the beginning of reset PHASE3 for boot mode selection and is retained after RESET has been

deasserted for subsequent boots after reset sequences during which RESET is not asserted.

Note: In order to ensure that the boot mode is correctly captured, the application needs to

apply the valid boot mode value the entire time that RESET is asserted.

RESET can be asserted as a consequence of the internal reset generation. This will force

re-sampling of the boot mode pins. (See Table 9-12 for details.)

In Table 13-3 (RTCC field descriptions), update Note in RTCC[APIVAL] field description:

Note: API functionality starts only when APIVAL is nonzero. The first API interrupt takes two

more cycles because of synchronization of APIVAL to the RTC cloc k, and APIVAL + 1 cycles

for subsequent occurrences. After that, interrupts are periodic in nature. Because of

synchronization issues, the minimum supported value of APIVAL is 4.

RCDIV

)+0.5MHz.

21.8.2.1.6 Overrun

Once the message buffer is full, the next valid message reception leads to an

overrun and a message is lost. The hardware sets the BOF bit in the LINSR to

signal the overrun condition. Which message is lost depends on the

configuration of the RX message buffer:

• If the buffer lock function is disabled (LINCR1[RBLM] = 0) the last

message stored in the buffer is overwritten by the new incoming

message. In this case the latest message is always available to the

application.

• If the buffer lock function is enabled (LINCR1[RBLM] = 0) the most

recent message is discarded and the previous message is available in the

buffer.

MPC5604B Reference Manual Errata, Rev. 1

Freescale Semiconductor2

Table 1. MPC5604BCRM Rev 8 Addenda

Location Description

Addendum List for Revision 8

Chapter 22, FlexCAN,

throughout chapter

Chapter 22, FlexCAN, page

429

Chapter 22, FlexCAN, page

461

Chapter 22, FlexCAN, page

462

Chapter 22, FlexCAN, page

463

Chapter 25, Analog-to-Digital

Converter (ADC), page

Chapter 25, Analog-to-Digital

Converter (ADC), page 597

Remove references throughout the chapter to “low-cost MCUs.”

Added this Note in the RTR field description of Table 22-4 (Message Buffer Structure field

description):

Note: Do not configure the last Message Buffer to be the RTR frame.

In Section 22.4.9.4, Protocol timing, updated the Note following Figure 22-16 (CAN engine

clocking scheme) to read: “This clock selection feature may not be available in all MCUs. A

particular MCU may not have a PLL, in which case it would have only the oscillator clock, or

it may use only the PLL clock feeding the FlexCAN module. In these cases, the CLK_SRC bit

in the CTRL Register has no effect on the module operation.”

Updated the table title of Table 22-20 from “CAN Standard Compliant Bit Time Segment

Settings” to “Bosch CAN 2.0B standard compliant bit time segment settings.”

In Section 22.4.9.4, Protocol timing, updated the Note following Table 22-20 to read: “Other

combinations of Time Segment 1 and Time Segment 2 can be valid. It is the user’s

responsibility to ensure the bit time settings are in compliance with the CAN standard. For bit

time calculations, use an IPT (Information Processing Time) of 2, which is the value

implemented in the FlexCAN module.”

In Section 28.3.5.2, Presampling channel enable signals, in Table 28-7, Presampling voltage

selection based on PREVALx fields, in the 01 row, change the “Presampling voltage” field to:

V1 = V

DD_HV_ADC0

or V

DD_HV_ADC1

.

In Section 25.3.2, Analog clock generator and conversion timings, remove the paragraph:

The direct clock should basically be used only in low power mode when the device is using

only the 16 MHz fast internal RC oscillator, but the conversion still requires a 16 MHz clock

(an 8 MHz clock is not fast enough). In all other cases, the ADC should use the clock divided

by two internally.

Chapter 25, Analog-to-Digital

Converter (ADC), p. 600

In Section 25.3.4.2, CTU in trigger mode, replace the sentence:

If another CTU conversion is triggered before the end of the conversion, that request is

discarded.

with:

If another CTU conversion is triggered before the end of the conversion, that request is

discarded. However, if the CTU has triggered a conversion that is still ongoing on a channel,

it will buffer a second request fo r the channel and wait for the end of the first conv ersion before

requesting another conversion. Thus, two conversion requests close together will both be

serviced.

Chapter 25, Analog-to-Digital

Converter (ADC), page 603

Add Note to Section 25.3.10, Auto-clock-off mode:

Note: The auto-clock-off feature cannot operate when the digital interface runs at the same

rate as the analog interface. This means that when MCR.ADCCLKSEL = 1, the analog clock

will not shut down in IDLE mode.

MPC5604B Reference Manual Errata, Rev. 1

Freescale Semiconductor 3

Revision History

Location Description

Table 1. MPC5604BCRM Rev 8 Addenda

Chapter 25, Analog-to-Digital

Converter (ADC), page 610

Chapter 26, Cross Triggering

Unit (CTU), page 633

In Section 25.4.6.2, Main Status Register (MSR), replace the ADCSTATUS field description with

the following:

The value of this parameter depends on ADC status:

000 IDLE — The ADC is powered up but idle.

001 Power-down — The ADC is powered down.

010 Wait state — The ADC is waiting for an external multiplexer . This occurs only when the

DSDR register is nonzero.

011 Reserved

100 Sample — The ADC is sampling the analog signal.

101 Reserved

110 Conversion — The ADC is converting the sampled signal.

111 Reserved

At the end of Section 26.4.1, Event Configuration Registers (CTU_EVTCFGRx) (x = 0...63), add

the following Note:

NOTE

The CTU tracks issued conversion requests to the ADC. When the ADC

is being triggered by the CTU and there is a need to shut down the ADC,

the ADC must be allowed to complete conversions before being shut

down. This ensures that the CTU is notified of completion; if the ADC

is shut down while performing a CTU-triggered conversion, the CTU is

not notified and will not be able to trigger further conversions until the

device is reset.

2 Revision History

Table 2 provides a revision history for this reference manual addendum document.

Table 2. Revision History Table

Rev. Number Substantive Changes Date of Release

1.0 • Initial release. 05/2012

MPC5604B Reference Manual Errata, Rev. 1

Freescale Semiconductor4

MPC5604B/C Microcontroller

MPC5604BCRM

Rev. 8

5 May 2011

Reference Manual

Devices Supported:

MPC5602B

MPC5602C

MPC5603B

MPC5603C

MPC5604B

MPC5604C

MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 1

MPC5604B/C Microcontroller Reference Manual, Rev. 8

2 Freescale Semiconductor

Chapter 1

Preface

1.1 Overview .........................................................................................................................................19

1.2 Audience ..........................................................................................................................................19

1.3 Guide to this reference manual ........................................................................................................19

1.4 Register description conventions ....................................................................................................22

1.5 References .......................................................................................................................................23

1.6 How to use the MPC5604B documents ..........................................................................................23

1.6.1 The MPC5604B document set ........................................................................................23

1.6.2 Reference manual content ..............................................................................................24

1.7 Using the MPC5604B .....................................................................................................................25

1.7.1 Hardware design .............................................................................................................25

1.7.2 Input/output pins .............................................................................................................26

1.7.3 Software design ..............................................................................................................27

1.7.4 Other features .................................................................................................................27

Chapter 2

Introduction

2.1 The MPC5604B microcontroller family .........................................................................................29

2.2 Features ...........................................................................................................................................29

2.2.1 MPC5604B family comparison ......................................................................................29

2.2.2 Block diagram ................................................................................................................32

2.2.3 Chip-level features ..........................................................................................................33

2.3 Packages ..........................................................................................................................................34

2.4 Developer support ...........................................................................................................................34

Chapter 3

Memory Map

Chapter 4

Signal description

4.1 Introduction .....................................................................................................................................39

4.2 Package pinouts ...............................................................................................................................39

4.3 Pad configuration during reset phases .............................................................................................42

4.4 Voltage supply pins .........................................................................................................................43

4.5 Pad types .........................................................................................................................................43

4.6 System pins .....................................................................................................................................44

4.7 Functional ports ...............................................................................................................................44

4.8 Nexus 2+ pins ..................................................................................................................................61

Chapter 5

Microcontroller Boot

5.1 Boot mechanism ..............................................................................................................................63

5.1.1 Flash memory boot .........................................................................................................64

5.1.2 Serial boot mode .............................................................................................................66

MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 3

5.1.3 Censorship ......................................................................................................................66

5.2 Boot Assist Module (BAM) ............................................................................................................71

5.2.1 BAM software flow ........................................................................................................71

5.2.2 LINFlex (RS232) boot ....................................................................................................79

5.2.3 FlexCAN boot ................................................................................................................80

5.3 System Status and Configuration Module (SSCM) ........................................................................82

5.3.1 Introduction ....................................................................................................................82

5.3.2 Features ...........................................................................................................................82

5.3.3 Modes of operation .........................................................................................................83

5.3.4 Memory map and register description ............................................................................83

Chapter 6

Clock Description

6.1 Clock architecture ...........................................................................................................................93

6.2 Clock gating ....................................................................................................................................94

6.3 Fast external crystal oscillator (FXOSC) digital interface ..............................................................95

6.3.1 Main features ..................................................................................................................95

6.3.2 Functional description ....................................................................................................95

6.3.3 Register description ........................................................................................................96

6.4 Slow external crystal oscillator (SXOSC) digital interface ............................................................97

6.4.1 Introduction ....................................................................................................................97

6.4.2 Main features ..................................................................................................................97

6.4.3 Functional description ....................................................................................................97

6.4.4 Register description ........................................................................................................98

6.5 Slow internal RC oscillator (SIRC) digital interface ......................................................................99

6.5.1 Introduction ....................................................................................................................99

6.5.2 Functional description ....................................................................................................99

6.5.3 Register description ......................................................................................................100

6.6 Fast internal RC oscillator (FIRC) digital interface ......................................................................101

6.6.1 Introduction ..................................................................................................................101

6.6.2 Functional description ..................................................................................................101

6.6.3 Register description ......................................................................................................102

6.7 Frequency-modulated phase-locked loop (FMPLL) .....................................................................102

6.7.1 Introduction ..................................................................................................................102

6.7.2 Overview ......................................................................................................................102

6.7.3 Features .........................................................................................................................103

6.7.4 Memory map ................................................................................................................103

6.7.5 Register description ......................................................................................................104

6.7.6 Functional description ..................................................................................................107

6.7.7 Recommendations ........................................................................................................110

6.8 Clock monitor unit (CMU) ............................................................................................................110

6.8.1 Introduction ..................................................................................................................110

6.8.2 Main features ................................................................................................................111

6.8.3 Block diagram ..............................................................................................................111

6.8.4 Functional description ..................................................................................................112

MPC5604B/C Microcontroller Reference Manual, Rev. 8

4 Freescale Semiconductor

6.8.5 Memory map and register description ..........................................................................114

Chapter 7

Clock Generation Module (MC_CGM)

7.1 Overview .......................................................................................................................................119

7.2 Features .........................................................................................................................................120

7.3 Modes of Operation .......................................................................................................................121

7.3.1 Normal and Reset Modes of Operation ........................................................................121

7.4 External Signal Description ..........................................................................................................121

7.5 Memory Map and Register Definition ..........................................................................................121

7.5.1 Register Descriptions ....................................................................................................125

7.6 Functional Description ..................................................................................................................129

7.6.1 System Clock Generation .............................................................................................129

7.6.2 Output Clock Multiplexing ...........................................................................................130

7.6.3 Output Clock Division Selection ..................................................................................131

Chapter 8

Mode Entry Module (MC_ME)

8.1 Introduction ...................................................................................................................................133

8.1.1 Overview ......................................................................................................................133

8.1.2 Features .........................................................................................................................135

8.1.3 Modes of Operation ......................................................................................................135

8.2 External Signal Description ..........................................................................................................136

8.3 Memory Map and Register Definition ..........................................................................................136

8.3.1 Register Description .....................................................................................................144

8.4 Functional Description ..................................................................................................................166

8.4.1 Mode Transition Request ..............................................................................................166

8.4.2 Modes Details ...............................................................................................................167

8.4.3 Mode Transition Process ..............................................................................................172

8.4.4 Protection of Mode Configuration Registers ................................................................182

8.4.5 Mode Transition Interrupts ...........................................................................................182

8.4.6 Peripheral Clock Gating ...............................................................................................184

8.4.7 Application Example ....................................................................................................185

Chapter 9

Reset Generation Module (MC_RGM)

9.1 Introduction ...................................................................................................................................187

9.1.1 Overview ......................................................................................................................187

9.1.2 Features .........................................................................................................................188

9.1.3 Modes of operation .......................................................................................................189

9.2 External signal description ............................................................................................................190

9.3 Memory map and register definition .............................................................................................190

9.3.1 Register descriptions ....................................................................................................192

9.4 Functional Description ..................................................................................................................203

9.4.1 Reset State Machine .....................................................................................................203

MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 5

9.4.2 Destructive Resets ........................................................................................................207

9.4.3 External Reset ...............................................................................................................207

9.4.4 Functional Resets ..........................................................................................................208

9.4.5 STANDBY Entry Sequence .........................................................................................208

9.4.6 Alternate Event Generation ..........................................................................................208

9.4.7 Boot Mode Capturing ...................................................................................................209

Chapter 10

Power Control Unit (MC_PCU)

10.1 Introduction ...................................................................................................................................211

10.1.1 Overview ......................................................................................................................211

10.1.2 Features .........................................................................................................................212

10.1.3 Modes of Operation ......................................................................................................212

10.2 External Signal Description ..........................................................................................................213

10.3 Memory Map and Register Definition ..........................................................................................213

10.3.1 Register Descriptions ....................................................................................................214

10.4 Functional Description ..................................................................................................................218

10.4.1 General .........................................................................................................................218

10.4.2 Reset / Power-On Reset ................................................................................................218

10.4.3 MC_PCU Configuration ...............................................................................................218

10.4.4 Mode Transitions ..........................................................................................................218

10.5 Initialization Information ..............................................................................................................221

10.6 Application Information ................................................................................................................221

10.6.1 STANDBY Mode Considerations ................................................................................221

Chapter 11

Voltage Regulators and Power Supplies

11.1 Voltage regulators ..........................................................................................................................223

11.1.1 High power regulator (HPREG) ...................................................................................223

11.1.2 Low power regulator (LPREG) ....................................................................................223

11.1.3 Ultra low power regulator (ULPREG) .........................................................................224

11.1.4 LVDs and POR .............................................................................................................224

11.1.5 VREG digital interface .................................................................................................224

11.1.6 Register description ......................................................................................................225

11.2 Power supply strategy ...................................................................................................................225

11.3 Power domain organization ...........................................................................................................226

Chapter 12

Wakeup Unit (WKPU)

12.1 Overview .......................................................................................................................................229

12.2 Features .........................................................................................................................................231

12.3 External signal description ............................................................................................................231

12.4 Memory map and register description ...........................................................................................231

12.4.1 Memory map ................................................................................................................231

12.4.2 NMI Status Flag Register (NSR) ..................................................................................232

MPC5604B/C Microcontroller Reference Manual, Rev. 8

6 Freescale Semiconductor

12.4.3 NMI Configuration Register (NCR) .............................................................................233

12.4.4 Wakeup/Interrupt Status Flag Register (WISR) ...........................................................234

12.4.5 Interrupt Request Enable Register (IRER) ...................................................................235

12.4.6 Wakeup Request Enable Register (WRER) ..................................................................235

12.4.7 Wakeup/Interrupt Rising-Edge Event Enable Register (WIREER) .............................236

12.4.8 Wakeup/Interrupt Falling-Edge Event Enable Register (WIFEER) .............................236

12.4.9 Wakeup/Interrupt Filter Enable Register (WIFER) ......................................................237

12.4.10 Wakeup/Interrupt Pullup Enable Register (WIPUER) .................................................237

12.5 Functional description ...................................................................................................................238

12.5.1 General .........................................................................................................................238

12.5.2 Non-maskable interrupts ..............................................................................................238

12.5.3 External wakeups/interrupts .........................................................................................240

12.5.4 On-chip wakeups ..........................................................................................................241

Chapter 13

Real Time Clock / Autonomous Periodic Interrupt (RTC/API)

13.1 Overview .......................................................................................................................................243

13.2 Features .........................................................................................................................................243

13.3 Device-specific information ..........................................................................................................245

13.4 Modes of operation ........................................................................................................................245

13.4.1 Functional mode ...........................................................................................................245

13.4.2 Debug mode ..................................................................................................................246

13.5 Register descriptions .....................................................................................................................246

13.5.1 RTC Supervisor Control Register (RTCSUPV) ...........................................................246

13.5.2 RTC Control Register (RTCC) .....................................................................................247

13.5.3 RTC Status Register (RTCS) ........................................................................................249

13.5.4 RTC Counter Register (RTCCNT) ...............................................................................250

13.6 RTC functional description ...........................................................................................................250

13.7 API functional description ............................................................................................................251

Chapter 14

CAN Sampler

14.1 Introduction ...................................................................................................................................253

14.2 Main features .................................................................................................................................253

14.3 Register description .......................................................................................................................254

14.3.1 Control Register (CR) ...................................................................................................254

14.3.2 Sample register n (n = 0..11) ........................................................................................255

14.4 Functional description ...................................................................................................................256

14.4.1 Enabling/Disabling the CAN sampler ..........................................................................256

14.4.2 Baud rate generation .....................................................................................................257

Chapter 15

e200z0h Core

15.1 Overview .......................................................................................................................................261

15.2 Microarchitecture summary ..........................................................................................................261

MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 7

15.3 Block diagram ...............................................................................................................................263

15.4 Features .........................................................................................................................................263

15.4.1 Instruction unit features ................................................................................................264

15.4.2 Integer unit features ......................................................................................................264

15.4.3 Load/Store unit features ...............................................................................................265

15.4.4 e200z0h system bus features ........................................................................................265

15.4.5 Nexus 2+ features .........................................................................................................265

15.5 Core registers and programmer’s model .......................................................................................266

Chapter 16

Interrupt Controller (INTC)

16.1 Introduction ...................................................................................................................................269

16.2 Features .........................................................................................................................................269

16.3 Block diagram ...............................................................................................................................270

16.4 Modes of operation ........................................................................................................................271

16.4.1 Normal mode ................................................................................................................271

16.5 Memory map and register description ...........................................................................................272

16.5.1 Module memory map ...................................................................................................272

16.5.2 Register description ......................................................................................................273

16.6 Functional description ...................................................................................................................280

16.6.1 Interrupt request sources ...............................................................................................289

16.6.2 Priority management ....................................................................................................289

16.6.3 Handshaking with processor .........................................................................................291

16.7 Initialization/application information ............................................................................................293

16.7.1 Initialization flow .........................................................................................................293

16.7.2 Interrupt exception handler ...........................................................................................293

16.7.3 ISR, RTOS, and task hierarchy .....................................................................................295

16.7.4 Order of execution ........................................................................................................296

16.7.5 Priority ceiling protocol ................................................................................................297

16.7.6 Selecting priorities according to request rates and deadlines .......................................297

16.7.7 Software configurable interrupt requests ......................................................................298

16.7.8 Lowering priority within an ISR ..................................................................................299

16.7.9 Negating an interrupt request outside of its ISR ..........................................................299

16.7.10 Examining LIFO contents ............................................................................................300

Chapter 17

Crossbar Switch (XBAR)

17.1 Introduction ...................................................................................................................................301

17.2 Block diagram ...............................................................................................................................301

17.3 Overview .......................................................................................................................................302

17.4 Features .........................................................................................................................................302

17.5 Modes of operation ........................................................................................................................302

17.5.1 Normal mode ................................................................................................................302

17.5.2 Debug mode ..................................................................................................................302

17.6 Functional description ...................................................................................................................302

MPC5604B/C Microcontroller Reference Manual, Rev. 8

8 Freescale Semiconductor

17.6.1 Overview ......................................................................................................................302

17.6.2 General operation .........................................................................................................303

17.6.3 Master ports ..................................................................................................................303

17.6.4 Slave ports ....................................................................................................................304

17.6.5 Priority assignment .......................................................................................................304

17.6.6 Arbitration ....................................................................................................................304

Chapter 18

Memory Protection Unit (MPU)

18.1 Introduction ...................................................................................................................................307

18.2 Features .........................................................................................................................................308

18.3 Modes of operation ........................................................................................................................309

18.4 External signal description ............................................................................................................309

18.5 Memory map and register description ...........................................................................................309

18.5.1 Memory map ................................................................................................................309

18.5.2 Register description ......................................................................................................310

18.6 Functional description ...................................................................................................................322

18.6.1 Access evaluation macro ..............................................................................................322

18.6.2 Putting it all together and AHB error terminations ......................................................324

18.7 Initialization information ...............................................................................................................324

18.8 Application information ................................................................................................................324

Chapter 19

System Integration Unit Lite (SIUL)

19.1 Introduction ...................................................................................................................................327

19.2 Overview .......................................................................................................................................327

19.3 Features .........................................................................................................................................329

19.4 External signal description ............................................................................................................329

19.4.1 Detailed signal descriptions ..........................................................................................330

19.5 Memory map and register description ...........................................................................................331

19.5.1 SIUL memory map .......................................................................................................331

19.5.2 Register protection ........................................................................................................332

19.5.3 Register descriptions ....................................................................................................333

19.6 Functional description ...................................................................................................................350

19.6.1 Pad control ....................................................................................................................350

19.6.2 General purpose input and output pads (GPIO) ...........................................................350

19.6.3 External interrupts ........................................................................................................351

19.7 Pin muxing ....................................................................................................................................352

Chapter 20

2

Inter-Integrated Circuit Bus Controller Module (I

20.1 Introduction ...................................................................................................................................355

20.1.1 Overview ......................................................................................................................355

20.1.2 Features .........................................................................................................................355

20.1.3 Block diagram ..............................................................................................................356

C)

MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 9

20.2 External signal description ............................................................................................................356

20.2.1 SCL ...............................................................................................................................356

20.2.2 SDA ..............................................................................................................................356

20.3 Memory map and register description ...........................................................................................356

20.3.1 Module memory map ...................................................................................................356

20.3.2 I2C Bus Address Register (IBAD) ...............................................................................357

20.3.3 I2C Bus Frequency Divider Register (IBFD) ...............................................................358

20.3.4 I2C Bus Control Register (IBCR) .................................................................................364

20.3.5 I2C Bus Status Register (IBSR) ....................................................................................365

20.3.6 I2C Bus Data I/O Register (IBDR) ...............................................................................366

20.3.7 I2C Bus Interrupt Config Register (IBIC) ....................................................................367

20.4 Functional description ...................................................................................................................367

20.4.1 I-Bus protocol ...............................................................................................................367

20.4.2 Interrupts .......................................................................................................................371

20.5 Initialization/application information ............................................................................................372

20.5.1 I2C programming examples ..........................................................................................372

Chapter 21

LIN Controller (LINFlex)

21.1 Introduction ...................................................................................................................................377

21.2 Main features .................................................................................................................................377

21.2.1 LIN mode features ........................................................................................................377

21.2.2 UART mode features ....................................................................................................377

21.2.3 Features common to LIN and UART ...........................................................................377

21.3 General description .......................................................................................................................378

21.4 Fractional baud rate generation .....................................................................................................379

21.5 Operating modes ...........................................................................................................................381

21.5.1 Initialization mode ........................................................................................................382

21.5.2 Normal mode ................................................................................................................382

21.5.3 Low power mode (Sleep) .............................................................................................382

21.6 Test modes .....................................................................................................................................382

21.6.1 Loop Back mode ...........................................................................................................382

21.6.2 Self Test mode ..............................................................................................................383

21.7 Memory map and registers description .........................................................................................383

21.7.1 Memory map ................................................................................................................383

21.8 Functional description ...................................................................................................................409

21.8.1 UART mode ..................................................................................................................409

21.8.2 LIN mode ......................................................................................................................411

21.8.3 8-bit timeout counter ....................................................................................................419

21.8.4 Interrupts .......................................................................................................................421

Chapter 22

FlexCAN

22.1 Introduction ...................................................................................................................................423

22.1.1 Overview ......................................................................................................................423

MPC5604B/C Microcontroller Reference Manual, Rev. 8

10 Freescale Semiconductor

22.1.2 FlexCAN module features ............................................................................................424

22.1.3 Modes of operation .......................................................................................................425

22.2 External signal description ............................................................................................................425

22.2.1 Overview ......................................................................................................................425

22.2.2 Signal descriptions ........................................................................................................426

22.3 Memory map and register description ...........................................................................................426

22.3.1 FlexCAN memory mapping .........................................................................................426

22.3.2 Message buffer structure ..............................................................................................428

22.3.3 Rx FIFO structure .........................................................................................................431

22.3.4 Register description ......................................................................................................433

22.4 Functional description ...................................................................................................................451

22.4.1 Overview ......................................................................................................................451

22.4.2 Local priority transmission ...........................................................................................452

22.4.3 Transmit process ...........................................................................................................452

22.4.4 Arbitration process .......................................................................................................453

22.4.5 Receive process ............................................................................................................454

22.4.6 Matching process ..........................................................................................................455

22.4.7 Data coherence .............................................................................................................456

22.4.8 Rx FIFO ........................................................................................................................459

22.4.9 CAN protocol related features ......................................................................................460

22.4.10 Modes of operation details ...........................................................................................464

22.4.11 Interrupts .......................................................................................................................465

22.4.12 Bus interface .................................................................................................................465

22.5 Initialization/Application information ...........................................................................................466

22.5.1 FlexCAN initialization sequence ..................................................................................466

22.5.2 FlexCAN addressing and SRAM size configurations ..................................................467

Chapter 23

Deserial Serial Peripheral Interface (DSPI)

23.1 Introduction ...................................................................................................................................469

23.2 Features .........................................................................................................................................470

23.3 Modes of operation ........................................................................................................................471

23.3.1 Master mode .................................................................................................................471

23.3.2 Slave mode ...................................................................................................................471

23.3.3 Module Disable mode ...................................................................................................471

23.3.4 Debug mode ..................................................................................................................472

23.4 External signal description ............................................................................................................472

23.4.1 Signal overview ............................................................................................................472

23.4.2 Signal names and descriptions ......................................................................................472

23.5 Memory map and register description ...........................................................................................474

23.5.1 Memory map ................................................................................................................474

23.5.2 DSPI Module Configuration Register (DSPIx_MCR) .................................................475

23.5.3 DSPI Transfer Count Register (DSPIx_TCR) ..............................................................478

23.5.4 DSPI Clock and Transfer Attributes Registers 0–5 (DSPIx_CTARn) .........................478

23.5.5 DSPI Status Register (DSPIx_SR) ...............................................................................486

MPC5604B/C Microcontroller Reference Manual, Rev. 8

Freescale Semiconductor 11

23.5.6 DSPI Interrupt Request Enable Register (DSPIx_RSER) ............................................488

23.5.7 DSPI PUSH TX FIFO Register (DSPIx_PUSHR) .......................................................490

23.5.8 DSPI POP RX FIFO Register (DSPIx_POPR) ............................................................492

23.5.9 DSPI Transmit FIFO Registers 0–3 (DSPIx_TXFRn) .................................................493

23.6 Functional description ...................................................................................................................494

23.6.1 Modes of operation .......................................................................................................495

23.6.2 Start and stop of DSPI transfers ...................................................................................496

23.6.3 Serial peripheral interface (SPI) configuration .............................................................497

23.6.4 DSPI baud rate and clock delay generation ..................................................................500

23.6.5 Transfer formats ...........................................................................................................503

23.6.6 Continuous serial communications clock .....................................................................511

23.6.7 Interrupt requests ..........................................................................................................514

23.6.8 Power saving features ...................................................................................................515

23.7 Initialization and application information .....................................................................................516

23.7.1 How to change queues ..................................................................................................516

23.7.2 Baud rate settings .........................................................................................................516

23.7.3 Delay settings ...............................................................................................................518

23.7.4 Calculation of FIFO pointer addresses .........................................................................518

Chapter 24

Timers

24.1 Introduction ...................................................................................................................................523

24.2 Technical overview ........................................................................................................................523

24.2.1 Overview of the STM ...................................................................................................525

24.2.2 Overview of the eMIOS ...............................................................................................525

24.2.3 Overview of the PIT .....................................................................................................527

24.3 System Timer Module (STM) .......................................................................................................527

24.3.1 Introduction ..................................................................................................................527

24.3.2 External signal description ...........................................................................................528

24.3.3 Memory map and register definition ............................................................................528

24.3.4 Functional description ..................................................................................................532

24.4 Enhanced Modular IO Subsystem (eMIOS) .................................................................................532

24.4.1 Introduction ..................................................................................................................532

24.4.2 External signal description ...........................................................................................535

24.4.3 Memory map and register description ..........................................................................535

24.4.4 Functional description ..................................................................................................547

24.4.5 Initialization/Application information ..........................................................................577

24.5 Periodic Interrupt Timer (PIT) ......................................................................................................580

24.5.1 Introduction ..................................................................................................................580

24.5.2 Features .........................................................................................................................581

24.5.3 Signal description .........................................................................................................581

24.5.4 Memory map and register description ..........................................................................581

24.5.5 Functional description ..................................................................................................586

24.5.6 Initialization and application information ....................................................................587

MPC5604B/C Microcontroller Reference Manual, Rev. 8

12 Freescale Semiconductor

Chapter 25

Analog-to-Digital Converter (ADC)