Page 1

5

4

3

2

1

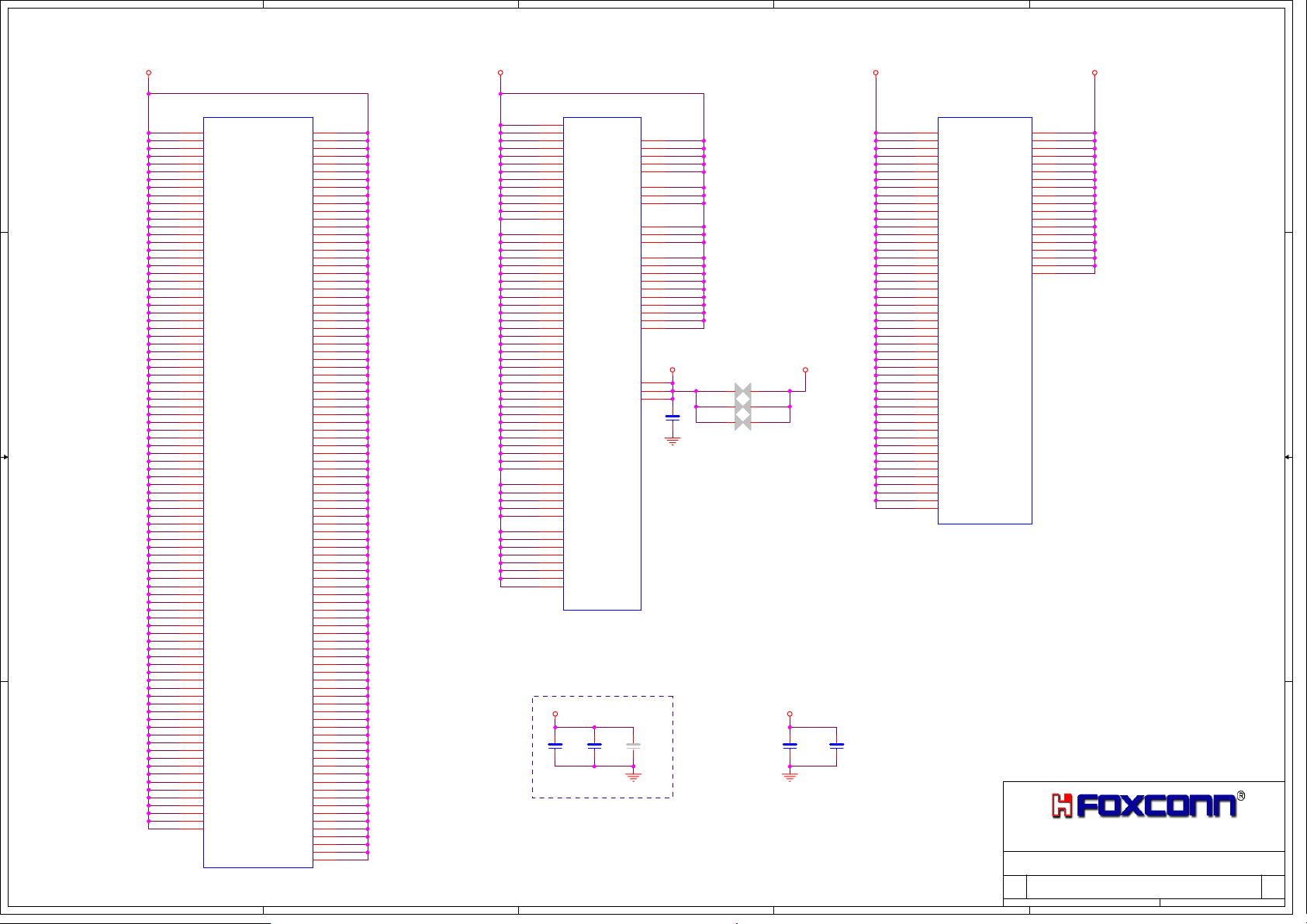

Cover Sheet

Block Diagram

Power On Sequence

1

2

3

H55M01

Fab1.0

H55MXV-6KS3H GTI

Power Delivery Map 4

D D

CPU 1-6

DDR3 CHA - B

PCIE X16 X8 switch

5 -10

11 -15

16 -18

19 -28PCH 1 - 9 SPI ,PCIRST

CPU:

Intel Lynnfield/Havendale processors in LGA1156 Package

System Chipset:

PCH(Ibex Peck)

CLOCK Gen. 29

PCIE X4 ,X1 ,VGA SLOT 30- 32

PCI SLOT 1,2 33-34

LAN1 ,LAN2 35-38

JMB363,368 39-40

1394 VT6308S 41-42

C C

Main Memory:

Dual Channel / DDR-III * 2 (Max 8GB)

On Board Device:

Clock Generator :ICS9LRS4105

LAN1:RealTek 8111DL

AUDIO ALC889 43-44

FP-USB1,USB2,USB3 45-47

SATA CONNECTOR

FOX3

KB/USB

ATX/FP/BUZ/VFD

POWER

XDP

EMI

B B

48

49-53

54

55

56-63

64

65

HDA Codec:ALC88S/ALC662

BIOS:SPI Flash ROM 8M

Expansion Slots:

PCI EXPRESS 16X SLOT *1

PCI EXPRESS 4X SLOT * 1

PCI SLOT * 2

Fab.A

Fab.B

Fab.C

A A

5

4

3

SKUVersion Function BOM

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Cover Sheet

Cover Sheet

Cover Sheet

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

H55MXV

H55MXV

H55MXV

150Tuesday, December 29, 2009

150Tuesday, December 29, 2009

150Tuesday, December 29, 2009

1

AA3

AA3

AA3

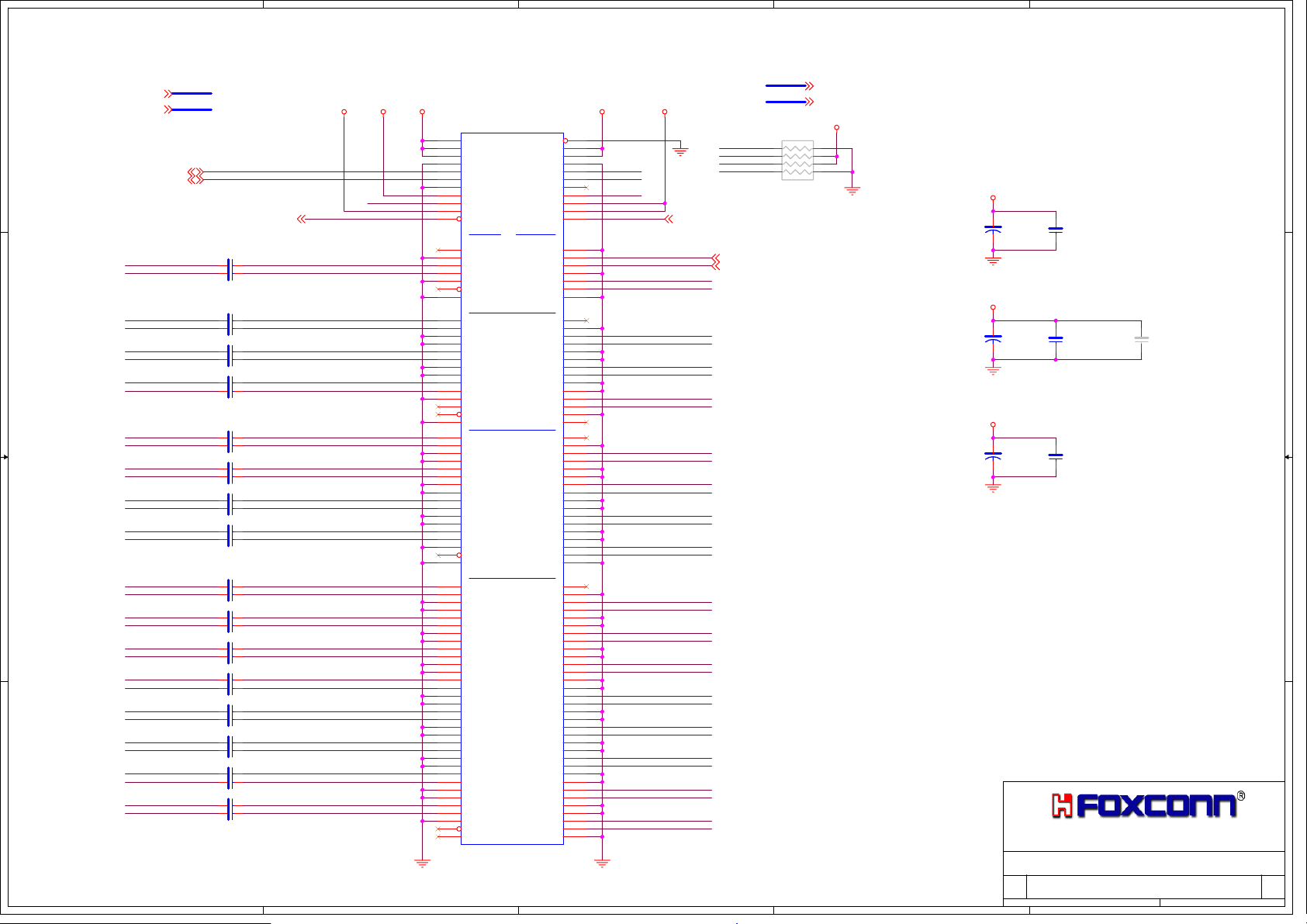

Page 2

5

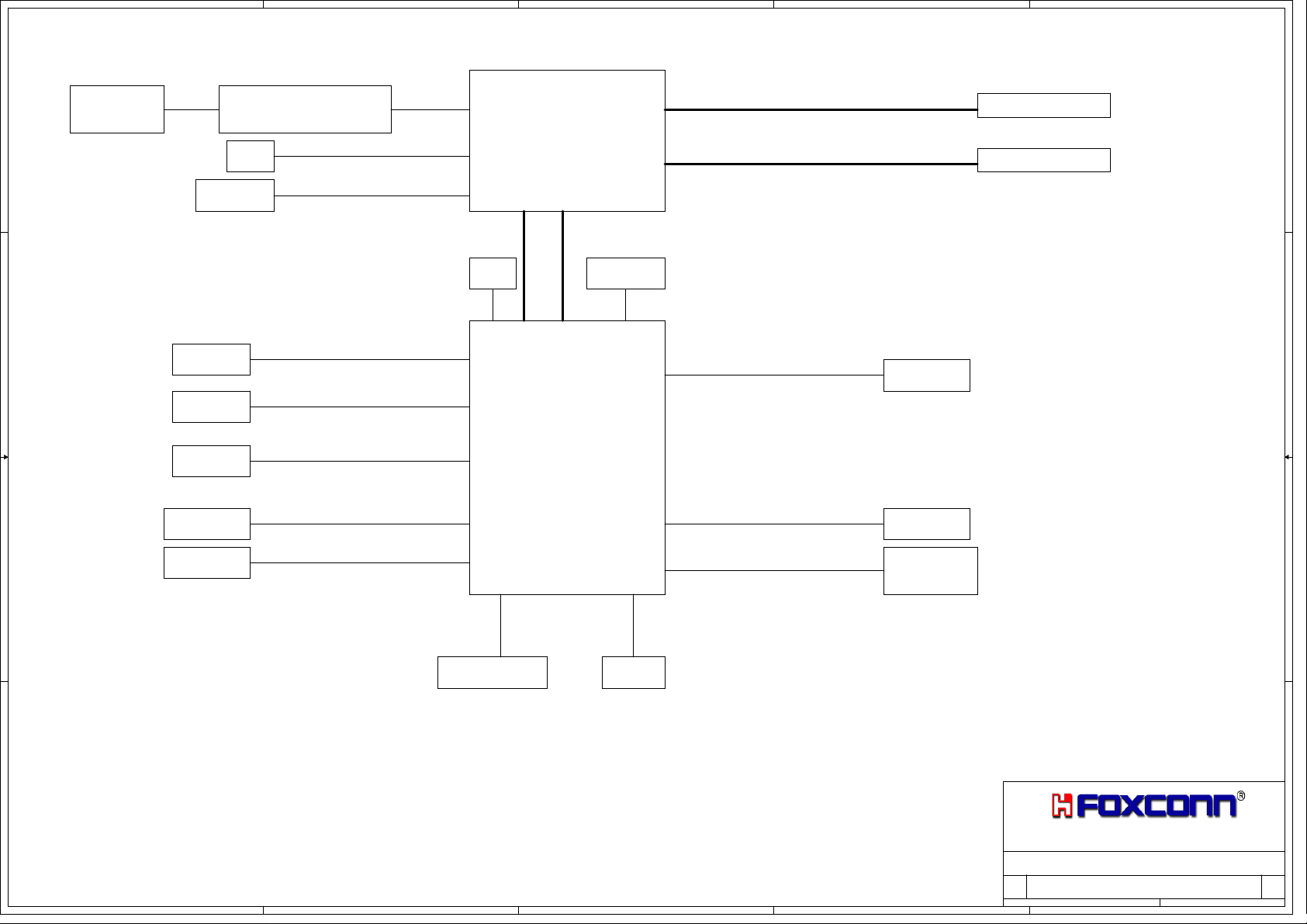

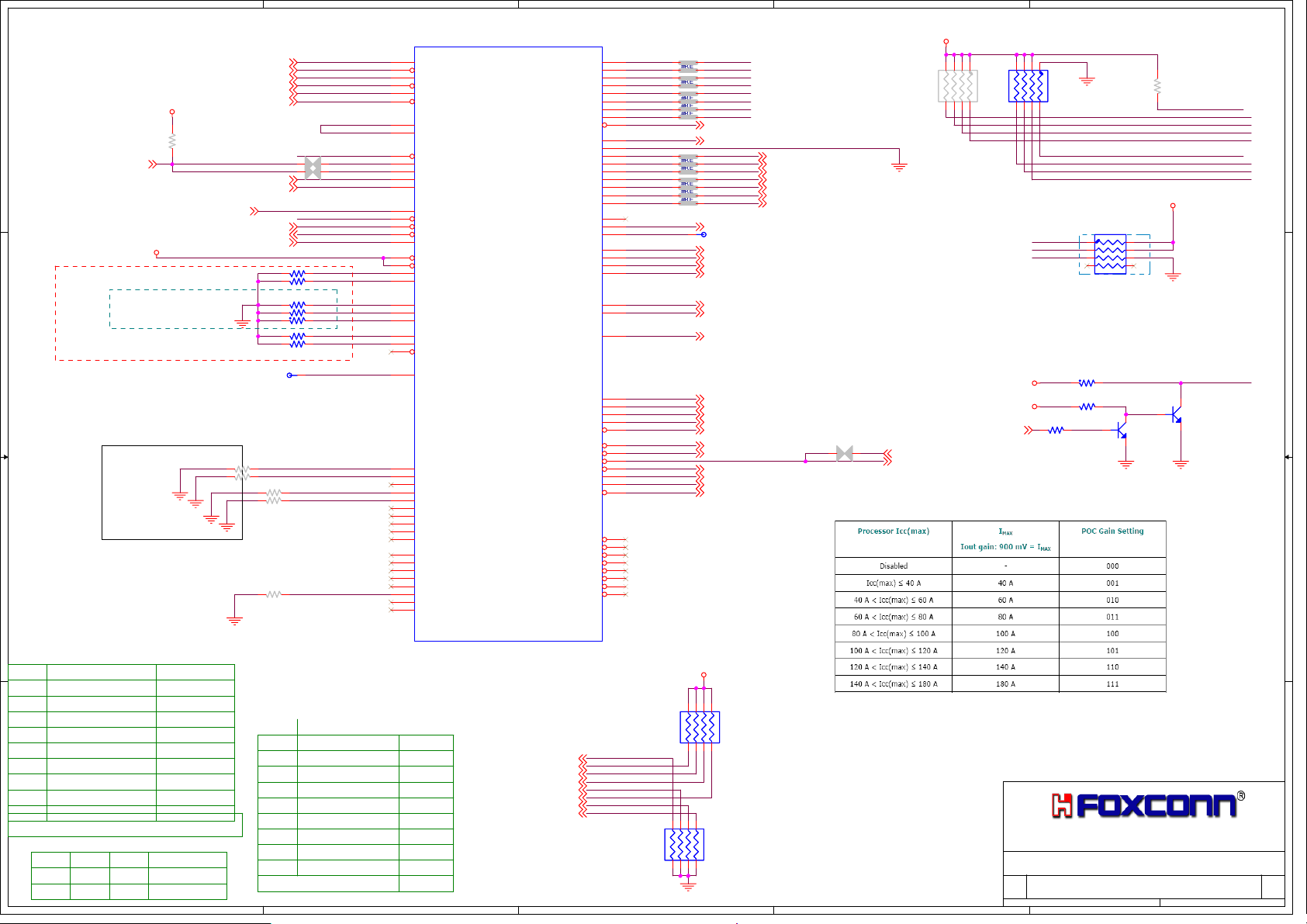

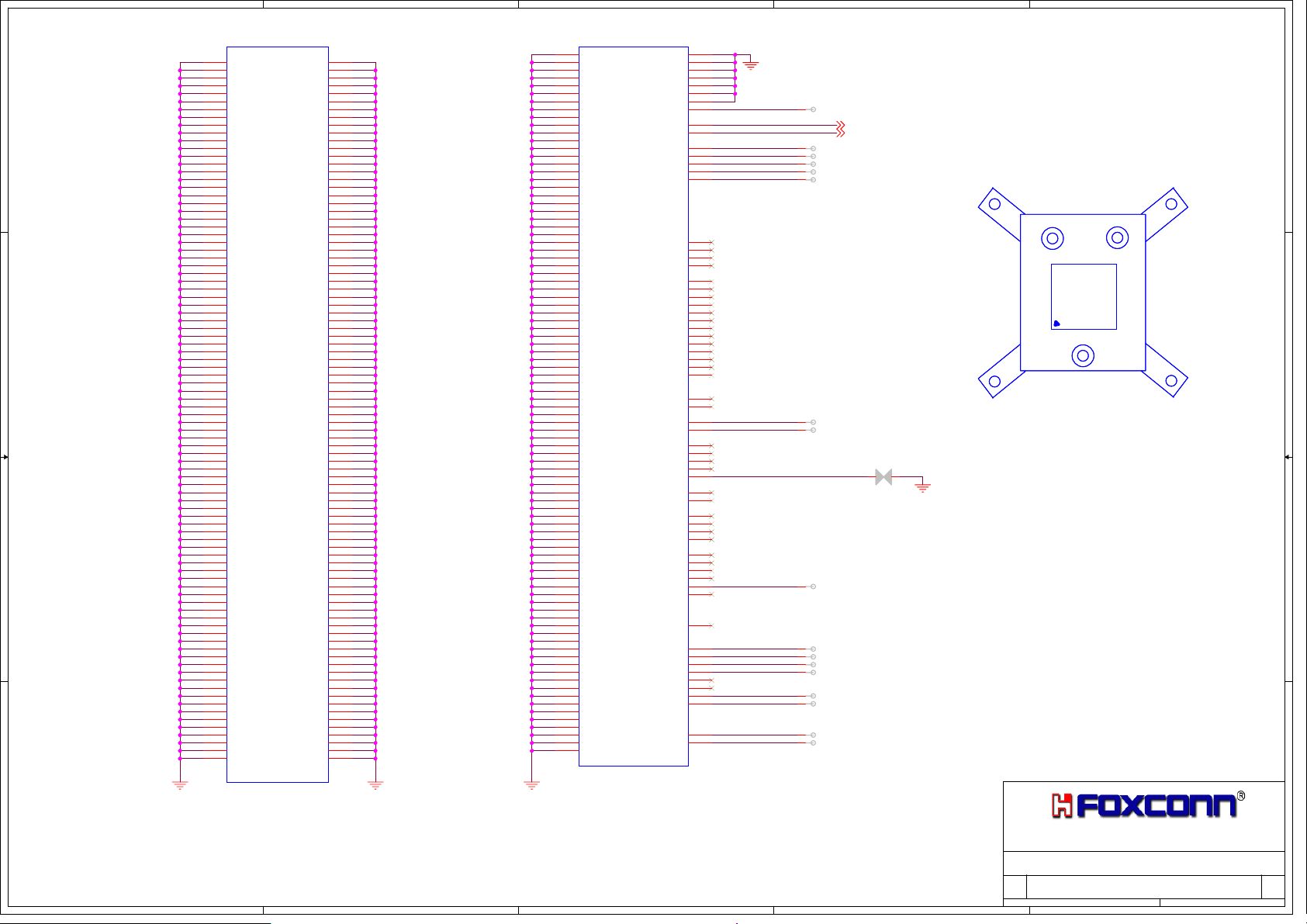

BLOCK DIAGRAM

4

3

2

1

POWER

D D

SUPPLY

CONNECTOR

VREG

VRD11.1

XDP

PCIE (GEN 2)

INTEL PROCESSOR

LYNNFIELD/HAVENDALE

LGA1156

PCIE GEN2 x16

CHANNEL A DDR3 SDRAM (800/1066/1333)

CHANNEL B DDR3 SDRAM (800/1066/1333)

DDR3 SDRAM CONN 1

DDR3 SDRAM CONN 1

DMIFDI

XDP CK505 CLOCK

C C

PCIE X4

PCI EXPRESS

PCIE

LAN1

8111DL

DVI

INTEL

PCH

HDMI

PCI1

USB

BP*6 / FP*8

B B

PCI2

AUDIOCODEC

ALC888S

SATA 2.0 (6 PORTS) FOX2

A A

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

FOXCONN PCEG

H55MXV

H55MXV

H55MXV

250Wednesday, April 21, 2010

250Wednesday, April 21, 2010

250Wednesday, April 21, 2010

1

AA3

AA3

AA3

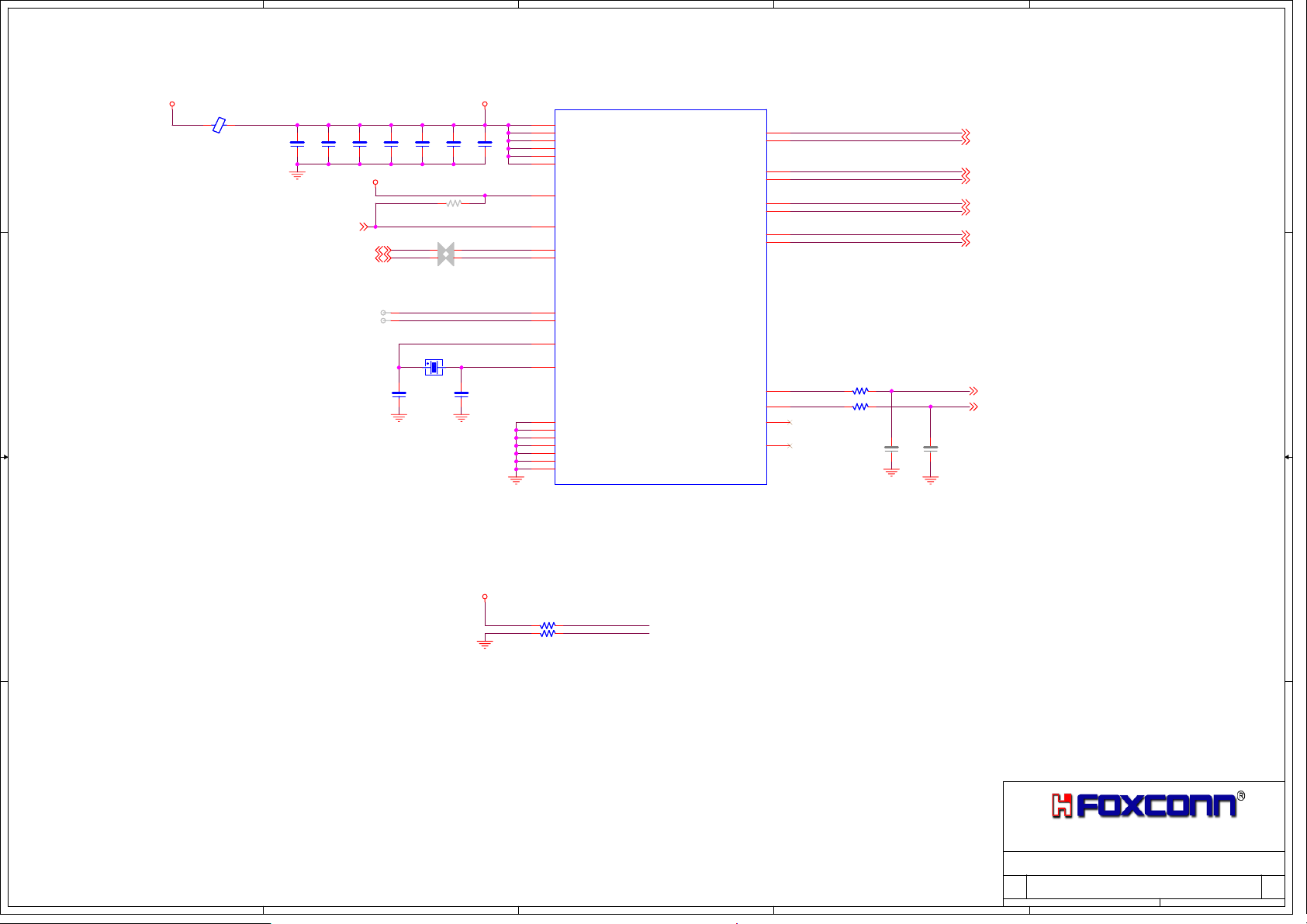

Page 3

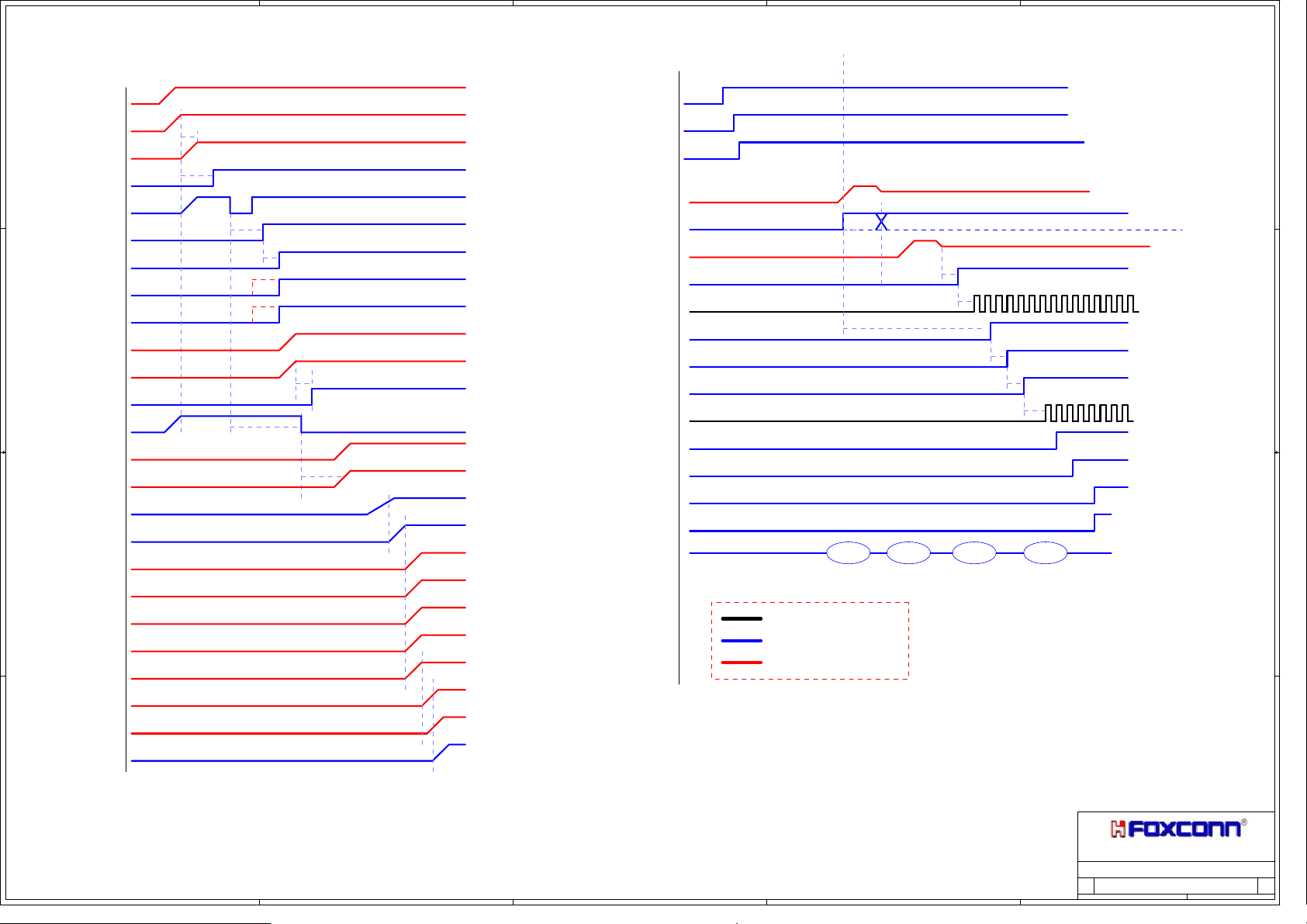

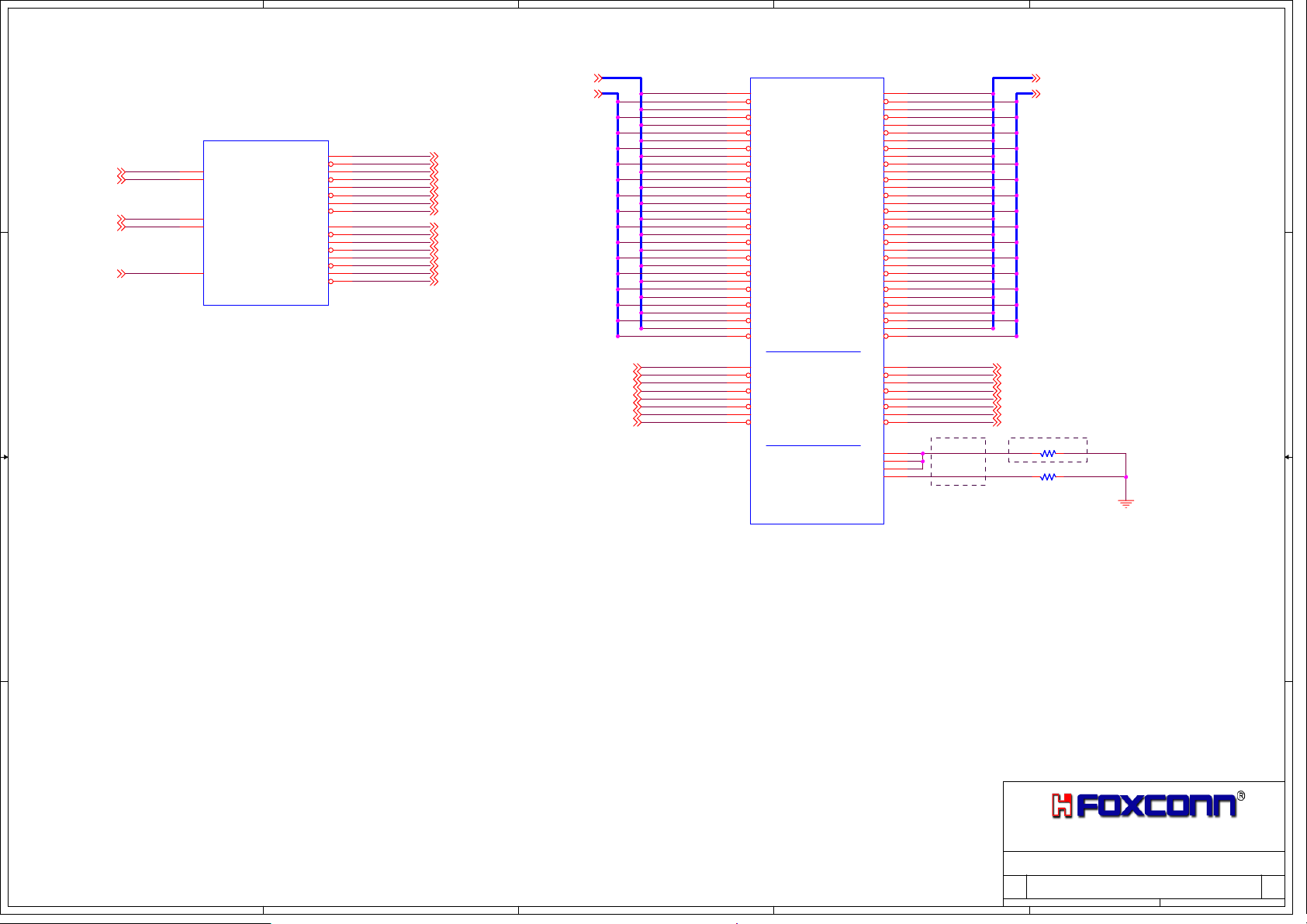

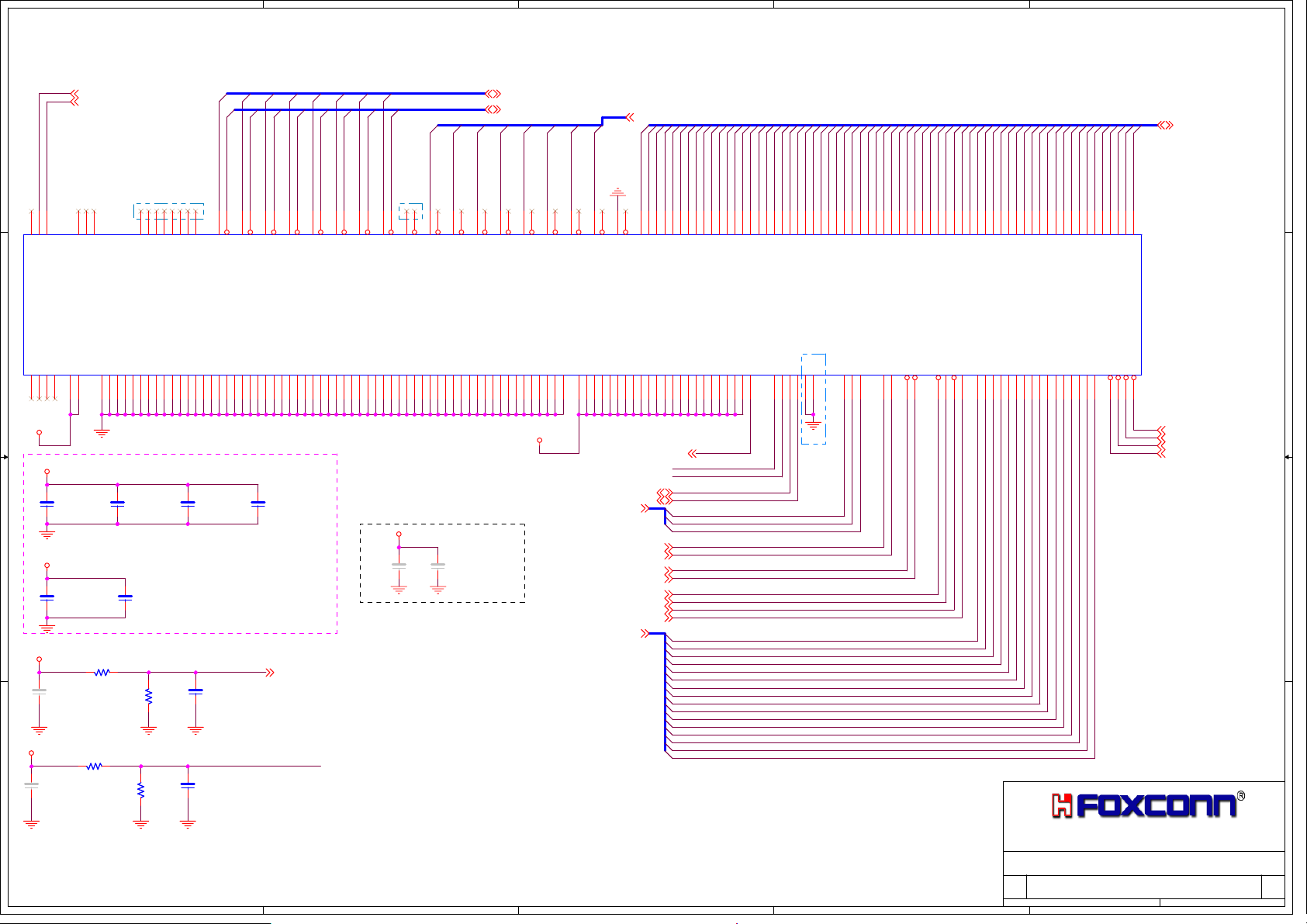

POWER ON SEQUENCE

5

4

3

from PS_ON#

2

1

AC Power

D D

+5VSB

Power Ramp:

0.2-20ms

+3VDUAL

S_RSMRST#

10mS min.

S_PWRBTN#

S_SLP_S4#

S_SLP_S3#

Can deassert before SLP_S5#, but

S_SLP_M#

no later the SLP_S3# deassertion

L1_SLP_LAN#

C C

+3V_EPW

+V_1.05_ME

from 3VDUAL trun on by SLP_M#

from 3VDUAL trun on by SLP_M#

PCH_MEPWRGD

O_PS_ON#

+12V/+5V

+3V

ATX_PWRGD

<500mS

PSU: RiseTime

0.2 20ms

PSU: RiseTime

0.2 20ms

4.4V

S_LPCPD# (SUS_STAT#)

5VDAUL_S3#O

B B

+5VDUAL

H_VTTPWRGD

H_DFGT_VR_EN

H_VID_DFGT_R_[0:6]

+V_1.1_AXG

H_VID[0:7]

+VCORE

VR_READY

CK505 Clocks

ATX_PWRGD

PWRGD_3V

H_DRAMPWRGD

PCH CLKs

H_PWRGD

S_PLTRST#

H_CPURST#

SPI BUS

VIDdefault = 0110110 (36h)

POC VIDs Driven

PLL Spin up:

1.8ms max

from PS_ON# 100~500mS (PSU spec)

From PCH_PROCPWROK to CPU_VCCPWRGD

Soft Strap

Load

Self-Cfg of

MAC & PHY

50uS~3mS

From Vcore controller to CLK GEN and PCH SYSPWGD

ATX PWGD (5V) to SIO (3V)

SIO (3V) to PCH_PWROK

From PCH_DRAMPWROK to CPU

No spec on when PCH clk outputs

(1, 5, 50, or 100ms)

From PCH_SUS_STAT# to SIO LPC PD#

From PCH_PLTRST#

ME FW partly

read

CLK Init

+5V_DUAL_USB

+V_1.8_SFR

+V_1.1_VTT

+V_1.5_SM

+V_1.05_PCH

+V_SM_VTT

H_VTTPWRGD

A A

5

From +5VDUAL

From +V_1.5_SM

From +V_1.5_SM

From +V_1.05_PCH

4

3

Black Line --> Clocks

Blue Line --> Logical State

Red Line --> Power Rails

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Power On Sequence

Power On Sequence

Power On Sequence

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

FOXCONN PCEG

H55MXV

H55MXV

H55MXV

1

350Wednesday, April 21, 2010

350Wednesday, April 21, 2010

350Wednesday, April 21, 2010

B00A2

B00A2

B00A2

of

of

of

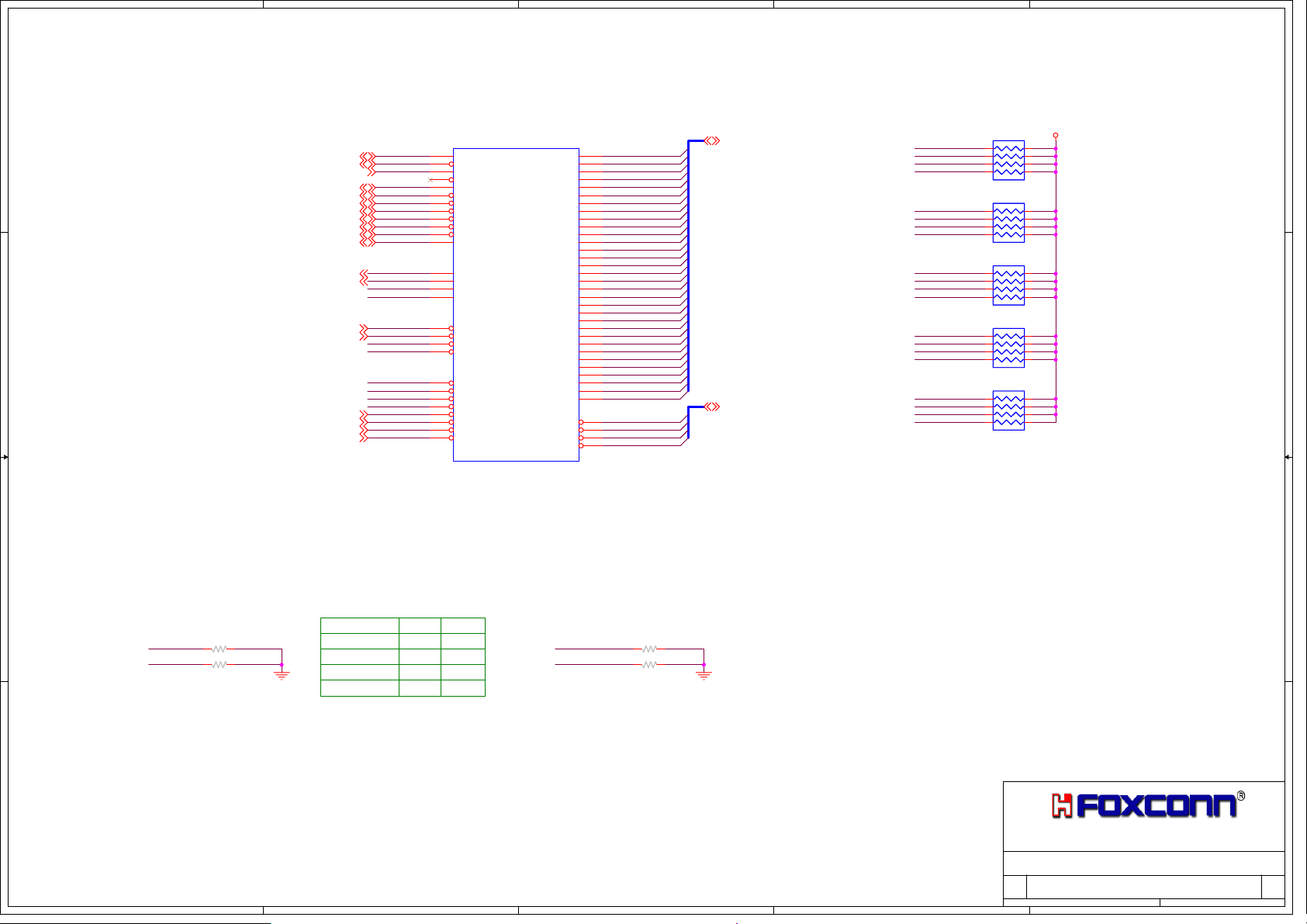

Page 4

5

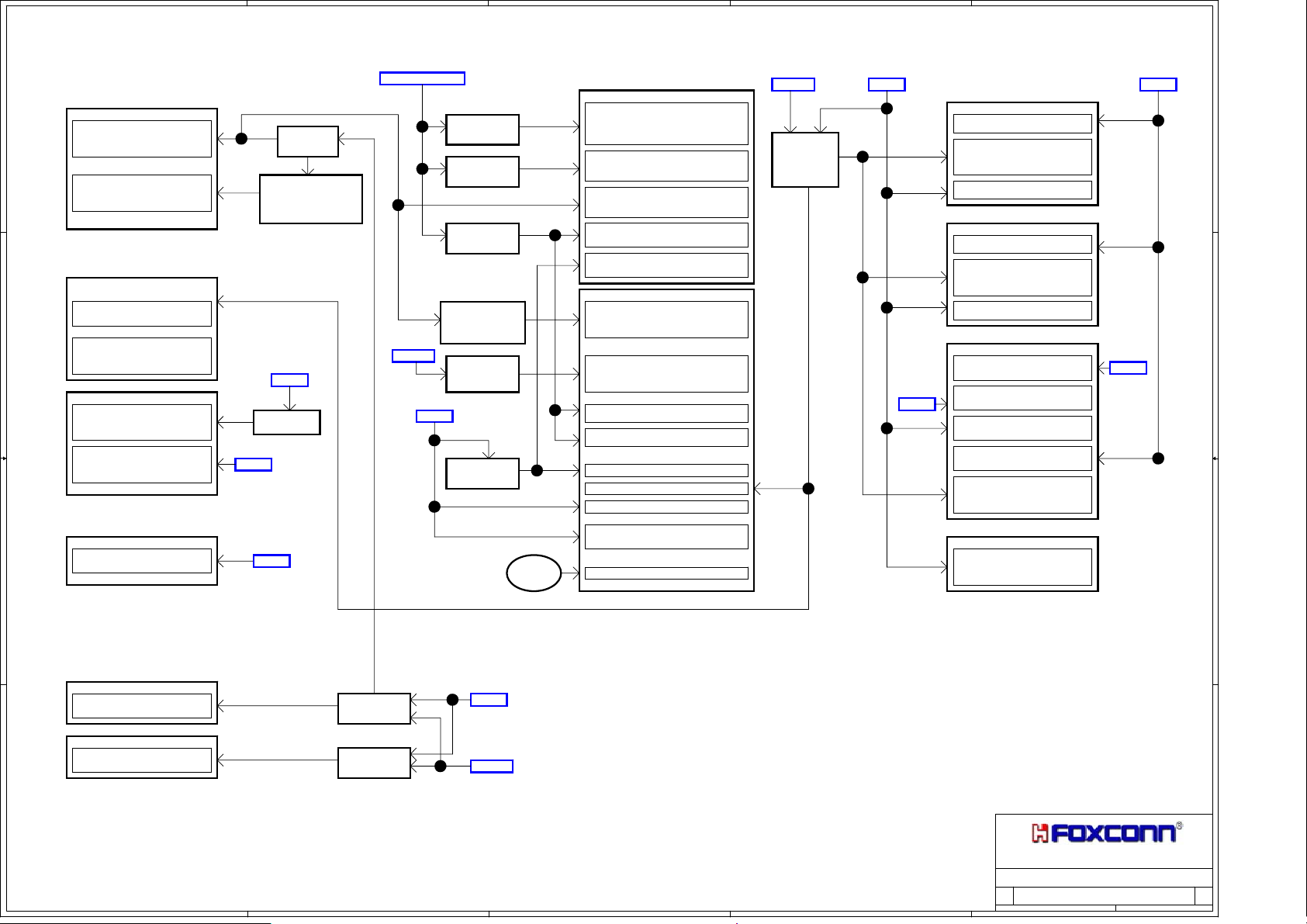

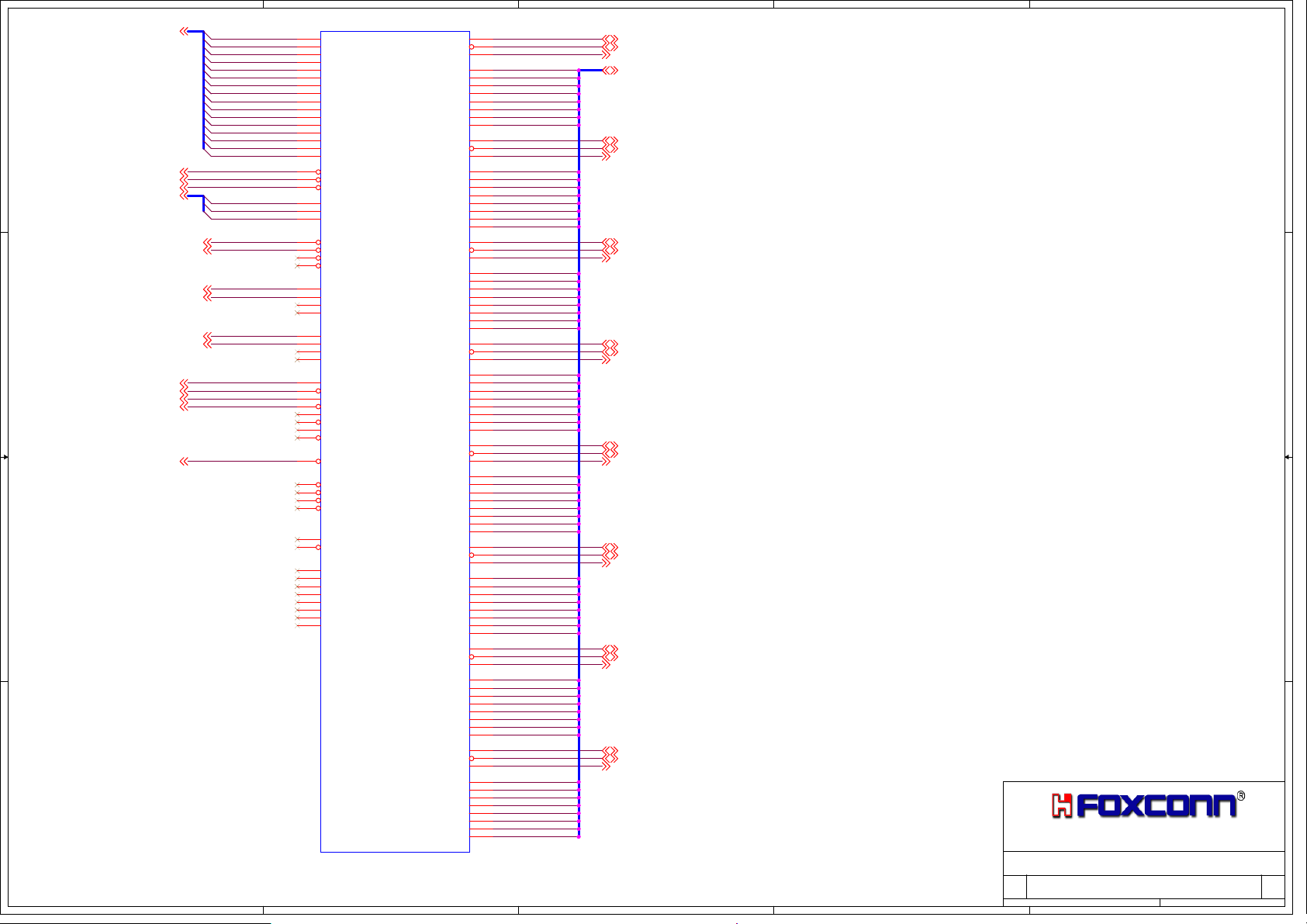

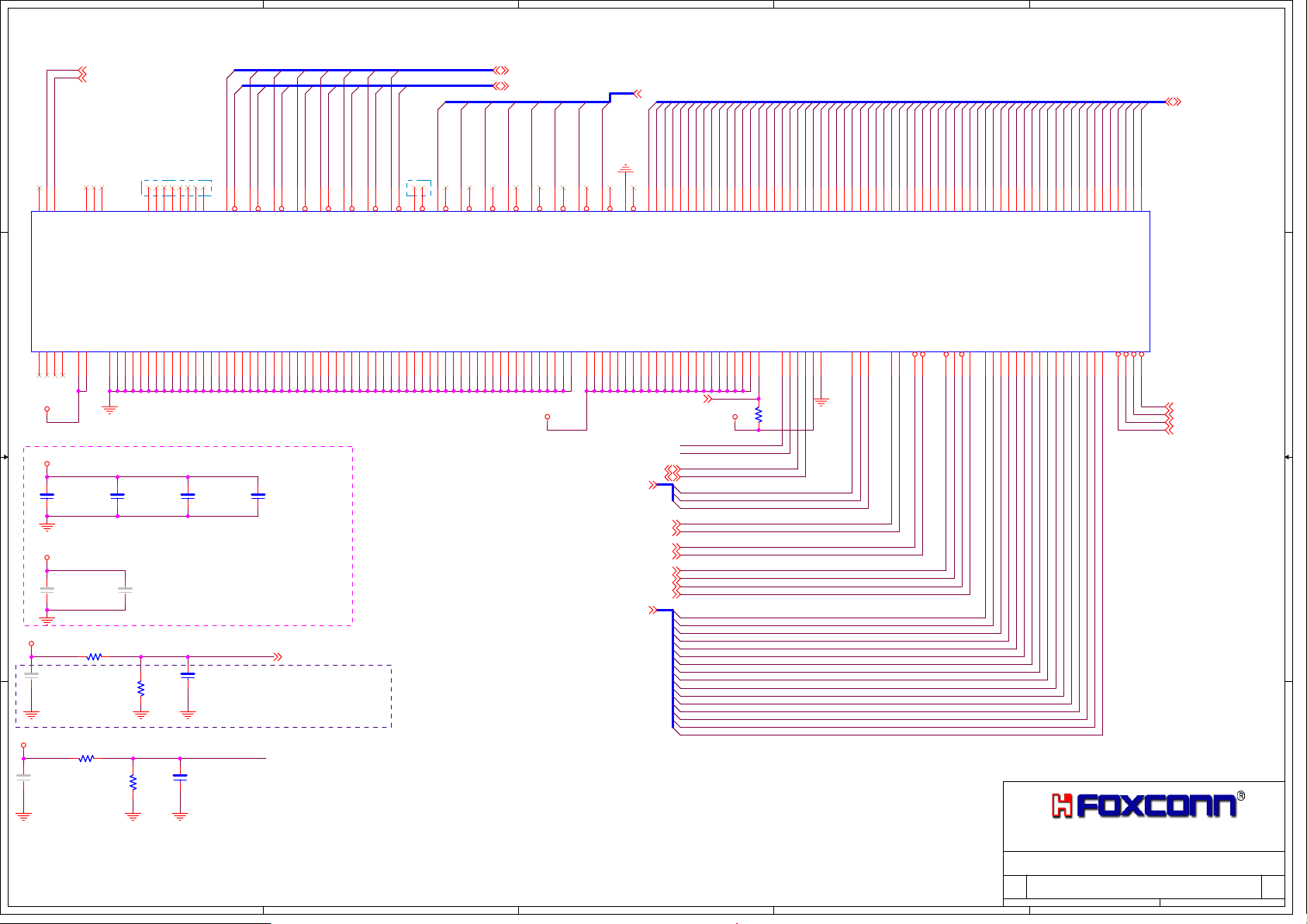

POWER DELIVERY MAP

4

3

2

1

+12V_VIN(4PIN)

LYN/HVN(95W)

D D

DDR3(2 DIMM)

+V_1.5_SM=1.5V

+V_SM_VTT=0.75V

SWITCHING

Icc=20A

Max=25A

+V_1.5_SM(1.5V) to

+V_SM_VTT (0.75V)

Icc=0.75A Max=1A

SWITCHING

Icc=90A

Max=100A

SWITCHING

Icc=16A

Max=20A

SWITCHING

Icc=30A

Max=35A

+VCORE (CPU Vcore)

Voltage=1.1V

Icc(Max)=90A Max=100A

4-Phases Swithing

+V_1.1_AXG(Havendale only)

Voltage=1.1V

Icc=16A Max=20A

+V_1.5_SM(DDR III)

Voltage=1.5V

+V_1.1_VTT(1.1/1.05V)

ACPI

Controller

+3VDUAL

Icc=1.25A

VCCPLL(1.8V)

RTL8111DL GbE Lan

+3VDUAL

600mW

C C

DVDD12/EVDD12

289mA

+5VSB

+12V

HDA Codec

+5VA

Voltage=5V

Icc=200mA

VCC

Voltage=3.3V

Icc=40mA

12V TO +5VA

Icc=200mA

+3V

+V_1.5_SM to

+V_1.05_PCH

Icc=6.5A

Max=8A

SWITCHING

Icc=2A

Max=2.5A

+3V

+3V TO

+V_1.8_SFR

Icc=1.5A

IBEX PEAK(5.5W)

VCCCORE(+V_1.05_PCH)

Voltage=1.05V

Icc(Max)=6.5A

VCCME(+V_1.05_ME)

Voltage=1.05V

Icc(Max)=2.4072A

VCCDMI 0.0655A

V_CPU_IO 33uA

VCCPNAND=1.8V 0.01559A

+3VDUAL 0.168A

3.3V 0.3572A

VCCME(V_3P3_EPW)

Super I/O

+5V

B B

Icc=60mA

+5V

RTC

Battery

0.0862A

VCCRTC 0.0022A

+3V+5VSB

PCI Express X16

+12V=5.5A

+3VDUAL

Icc(Max)=0.375A(wake)

Icc(Max)=0.02A(no wake)

+3V=3A

PCI Express X4

+12V=0.5A

+3VDUAL

Icc(Max)=0.375A(wake)

Icc(Max)=0.02A(no wake)

+3V=3A

PCI Slot

-12V

Icc(Max)=0.1A

+5V

+5V

Icc(Max)=5A

+3V

Icc(Max)=7.6A

+12V

Icc(Max)=0.5A

+3VDUAL

Icc(Max)=0.375A(wake)

Icc(Max)=0.02A(no wake)

CK505

+3V (Core)

Voltage=3.3V

Ivdd=250mA

12V

-12V

PS2

+5V_DUAL=500mA(S0, S1)

+5V_DUAL=2mA(S3)

USB2.0 12 Ports

+5V_DUAL_USB=6A(S0, S1)

+5V_DUAL_USB=?A(S3)

A A

5

ACPI

Controller

+5V_DUAL

ACPI

Controller

+5V_DUAL_USB

4

+5V

+5VSB

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Power Delivery Map

Power Delivery Map

Power Delivery Map

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

3

2

Date: Sheet

FOXCONN PCEG

H55MXV

H55MXV

H55MXV

1

450Wednesday, April 21, 2010

450Wednesday, April 21, 2010

450Wednesday, April 21, 2010

B00C

B00C

B00C

of

of

of

Page 5

5

C_CPU_CLK_DP21

C_CPU_CLK_DN21

C_PE_100M_DMI_DP21

C_PE_100M_DMI_DN21

C_PCH_DP_120M_DP21

R305

R305

49.9

49.9

+/-1%

+/-1%

Dummy

Dummy

C_PCH_DP_120M_DN21

H_VTTPWRGD44,46

H_DRAMPWRGD18

H_PECI17

H_PROCHOT#44

H_THERMTRIP#17

H_PM_SYNC17

R190 20 Ohm+/-1%

R190 20 Ohm+/-1%

R189 20 Ohm+/-1%

R189 20 Ohm+/-1%

R279 100 Ohm

R279 100 Ohm

R274 24.9 +/-1%

R274 24.9 +/-1%

R275 130 +/-1%R275 130 +/-1%

R278 49.9 +/-1%

R278 49.9 +/-1%

R293 49.9 +/-1%

R293 49.9 +/-1%

TP9TP9

*

*

*

*

R204 1.5K Dummy

R204 1.5K Dummy

#REFDE41

#REFDE41

H_CPURST#

#REFDE40

#REFDE40

1 2

1 2

dummy

dummy

dummy

dummy

H_PECI

H_CATERR#

H_THERMTRIP#

H_PM_SYNC

*

*

*

*

+/-1%

+/-1%

*

*

*

*

*

*

*

*

H_TP_DFGT_DPRSLPVR

H_CPU_CFG0

R2441.5KDummy

R2441.5KDummy

H_CPU_CFG1

R2451.5KDummy

R2451.5KDummy

R2341.5KDummy

R2341.5KDummy

*

*

R2031.5KDummy

R2031.5KDummy

*

*

*

*

H_TDO_TDI_M

H_CPU_CFG3

H_CPU_CFG4

H_CPU_CFG15

V_1P1_VTT

D D

H_PWRGD18,47

L<1.0"

W=10

S=15

C C

update by wesley 09/29

B B

*

*

V_1P1_VTT

+V_1.8_SFR power

Reference

L<1.3"

W=8

S=15

CFG Table

CFG

0 PEG Config Table

1

2

3

4

5

6

A A

7

15

CFG[0..5] HAVE INTERNAL PULL-UP

lynnfiel EDS Page 52. wesley wang033009

H / L Description

PEG Config Table

PEG Config Table

Normal / Reverse

Disable / Enable

ENGINEERING EXPERIMENT

ENGINEERING EXPERIMENT

PEG Config Table

SEL1 PCI-E Config

SEL2

1111

1

SEL0

0

5

PEG SEL0

PEG SEL1

PEG SEL2

Lane Normal

DP Presence

RESERVED

RESERVED

1 x 16

2 x 8

Power On Config

Function Default

VID0 MSI0

VID1

VID2

VID3

VID4

VID5

VID6

VID7

PSI# RESERVED Low

MSI1

MSI2

IMON CONFIG0

IMON CONFIG1

IMON CONFIG2

RESERVED

VRD SELECT Low

Z0901

Z0902

COMP2

COMP3

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

COMP1

COMP0

4

AA7

AA6

AA3

AA4

AA8

AF37

AF38

AF34

AH36

AH35

AG37

AH37

AG35

AG39

AH34

AF35

AH39

AB5

AB4

B11

C11

AG1

AD1

AE1

AF2

AF36

AK38

E10

H10

G12

H12

K10

K12

4

Y8

J10

E8

G8

F10

H9

E9

F9

K8

J12

L8

K9

H7

L11

HU1E

HU1E

BCLK0

BCLK0*

PEG_CLK

PEG_CLK*

BCLK1

BCLK1*

TDI_M

TDO_M

RSTIN*

VCCPWRGOOD_1

VCCPWRGOOD_0

VTTPWRGOOD

SM_DRAMPWROK

PECI

CATERR*

PROCHOT*

THERMTRIP*

PM_SYNC

PM_EXT_TS0*

PM_EXT_TS1*

COMP2

COMP3

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

COMP1

COMP0

SKTOCC*

GFX_DPRSLPVR

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CPU Socket

CPU Socket

Low

High

High

Low

Low

High

Low

5/10

5/10

MISC

MISC

VID0/MSID0

VID1/MSID1

VID2/MSID2

VID3/MSID3

VID4/MSID4

VID5/MSID5

VID6/MSID6

VID7/MSID7

PSI*

GFX_VR_EN

GFX_IMON

GFX_VID0

GFX_VID1

GFX_VID2

GFX_VID3

GFX_VID4

GFX_VID5

GFX_VID6

FC_AE38

VTT_SELECT

FC_AG40

VCC_SENSE

VSS_SENSE

VTT_SENSE

VSS_SENSE_VTT

VAXG_SENSE

VSSAXG_SENSE

ISENSE

TDO

TCK

TMS

TRST*

PRDY*

PREQ*

DBR*

BCLK_ITP*

BCLK_ITP

TAPPWRGOOD

RESET_OBS*

BPM0*

BPM1*

BPM2*

BPM3*

BPM4*

BPM5*

BPM6*

BPM7*

H_VID044

H_VID144

H_VID244

H_VID344

H_VID444

H_VID544

H_VID644

H_VID744

3

MSID0

MSID1

MSID2

MSID3

MSID4

MSID5

MSID6

MSID7

GFX_VID0

GFX_VID1

GFX_VID2

GFX_VID3

GFX_VID4

GFX_VID5

GFX_VID6

H_TP_AG40

H_TDO

H_TDI

H_TCK

H_TMS

H_TRST#

H_PRDY#

H_RSTOUT#

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

U40

U39

U38

U37

U36

U35

U34

U33

AG38

F12

F6

G10

B12

E12

E11

C12

G11

J11

AE38

AF39

AG40

T35

T34

AE35

AE36

A13

B13

T40

AM38

AM37

TDI

AN37

AN40

AM39

AJ38

AK37

AL40

AK40

AK39

AK34

AL39

H_VID0

#REFDE31#REFDE31

H_VID1

#REFDE32#REFDE32

H_VID2

#REFDE34#REFDE34

H_VID3

#REFDE36#REFDE36

H_VID4

#REFDE37#REFDE37

H_VID5

#REFDE33#REFDE33

H_VID6

#REFDE38#REFDE38

H_VID7

#REFDE39#REFDE39

H_MCP_PSI# 44

H_DFGT_VR_EN 45

#REFDE20#REFDE20

#REFDE19#REFDE19

#REFDE18#REFDE18

#REFDE17#REFDE17

#REFDE16#REFDE16

#REFDE15#REFDE15

#REFDE14#REFDE14

H_VTT_VID1 46

TP14TP14

H_VCC_SENSE 44

H_VSS_SENSE 44

H_VCCTT_SENSE 46

H_VSSTT_SENSE 46

H_VCCAXG_SENSE 45

H_VSSAXG_SENSE 45

H_MCP_ISENSE_DP 44

H_TDO 47

H_TDI 47

H_TCK 47

H_TMS 47

H_TRST# 47

H_PRDY# 47

H_PREQ# 47

H_XDP_CLKOUT_DN 47

H_XDP_CLKOUT_DP 47

H_TAPPWRGOOD 47

H_RSTOUT# 47

H_VID_DFGT_R_0 45

H_VID_DFGT_R_1 45

H_VID_DFGT_R_2 45

H_VID_DFGT_R_3 45

H_VID_DFGT_R_4 45

H_VID_DFGT_R_5 45

H_VID_DFGT_R_6 45

1 2

#REFDE8

#REFDE8

dummy

dummy

2

V_1P1_VTT

Dummy

Dummy

78

FP_RST# 18,40,47

XDP_CPU_RST# 47

642

*

*

135

RN16

RN16

51

51

+/-5%

+/-5%

V_1P1_VTT

3D3V_DUAL

S_PLTRST#18,33,47

*

*

RN20

RN20

135

78

51

51

+/-5%

+/-5%

642

H_TDI

H_TMS

H_TCK

R391 10K

R391 10K

*

*

+/-5%

+/-5%

RN18

RN18

*

*

1

3

5

7 8

Close to CPU

51

51

+/-5%

+/-5%

R290

R290

1 2

150

150

R299

R299

10K

10K

*

*

+/-5%

+/-5%

B

+/-5%

+/-5%

2

4

6

B

Q41

Q41

MMBT3904-7-F

MMBT3904-7-F

E C

1

*

*

R572

R572

51 Ohm

51 Ohm

Dummy

Dummy

V_1P1_VTT

E C

H_PECI

H_CPURST#

H_PM_SYNC

H_RSTOUT#

H_PRDY#

H_TRST#

H_THERMTRIP#

H_CATERR#

H_CPURST#

Q42

Q42

MMBT3904-7-F

MMBT3904-7-F

H_TDO

VRD design guide Page 43

AL33

AL32

AK33

AK32

AM31

AL30

AK30

AK31

V_1P1_VTT

*

*

RN40

RN40

135

78

1K

1K

+/-5%

+/-5%

642

*

*

RN41

RN41

135

78

1K

1K

+/-5%

+/-5%

642

3

2

Title

Title

Title

CPU-1:MISC

CPU-1:MISC

CPU-1:MISC

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet

VID3~5

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

H55MXV

H55MXV

H55MXV

1

B00A3

B00A3

B00A3

550Wednesday, April 21, 2010

550Wednesday, April 21, 2010

550Wednesday, April 21, 2010

of

Page 6

5

D D

H_FDI_FSYNC0_120

H_FDI_LSYNC0_120

H_FDI_FSYNC1_120

H_FDI_LSYNC1_120

H_FDI_INT_120

C C

AC4

AD4

AC3

AD3

AC2

HU1D

HU1D

FDI_FSYNC0

FDI_LSYNC0

FDI_FSYNC1

FDI_LSYNC1

FDI_INT

CPU Socket

CPU Socket

U6

FDI_TX0

FDI_TX0*

FDI_TX1

FDI_TX1*

FDI_TX2

FDI_TX2*

FDI_TX3

FDI_TX3*

FDI_TX4

FDI_TX4*

FDI_TX5

FDI_TX5*

FDI_TX6

FDI_TX6*

FDI_TX7

FDI_TX7*

U5

V4

V3

U8

U7

W8

W7

W5

W4

R8

R7

Y4

Y3

Y6

Y5

DISPLAY LINK

DISPLAY LINK

4/10

4/10

4

X_EXP_A_RX_DP[15..0]13

X_EXP_A_RX_DN[15..0]13

H_FDI_TX_DP0 20

H_FDI_TX_DN0 20

H_FDI_TX_DP1 20

H_FDI_TX_DN1 20

H_FDI_TX_DP2 20

H_FDI_TX_DN2 20

H_FDI_TX_DP3 20

H_FDI_TX_DN3 20

H_FDI_TX_DP4 20

H_FDI_TX_DN4 20

H_FDI_TX_DP5 20

H_FDI_TX_DN5 20

H_FDI_TX_DP6 20

H_FDI_TX_DN6 20

H_FDI_TX_DP7 20

H_FDI_TX_DN7 20

H_DMI_RX_DP016

H_DMI_RX_DN016

H_DMI_RX_DP116

H_DMI_RX_DN116

H_DMI_RX_DP216

H_DMI_RX_DN216

H_DMI_RX_DP316

H_DMI_RX_DN316

3

X_EXP_A_RX_DP0

X_EXP_A_RX_DN0

X_EXP_A_RX_DP1

X_EXP_A_RX_DN1

X_EXP_A_RX_DP2

X_EXP_A_RX_DN2

X_EXP_A_RX_DP3

X_EXP_A_RX_DN3

X_EXP_A_RX_DP4

X_EXP_A_RX_DN4

X_EXP_A_RX_DP5

X_EXP_A_RX_DN5

X_EXP_A_RX_DP6

X_EXP_A_RX_DN6

X_EXP_A_RX_DP7

X_EXP_A_RX_DN7

X_EXP_A_RX_DP8

X_EXP_A_RX_DN8

X_EXP_A_RX_DP9

X_EXP_A_RX_DN9

X_EXP_A_RX_DP10

X_EXP_A_RX_DN10

X_EXP_A_RX_DP11

X_EXP_A_RX_DN11

X_EXP_A_RX_DP12

X_EXP_A_RX_DN12

X_EXP_A_RX_DP13

X_EXP_A_RX_DN13

X_EXP_A_RX_DP14

X_EXP_A_RX_DN14

X_EXP_A_RX_DP15

X_EXP_A_RX_DN15

C9

D9

B8

C8

A7

A6

B6

C6

A5

B5

B4

C4

C3

D3

D2

E2

E1

F1

G3

G2

G1

H1

J3

J2

J1

K1

L2

L3

P3

P4

T3

T4

R1

T1

U3

U2

U1

V1

W3

W2

HU1C

HU1C

PEG_RX0

PEG_RX0*

PEG_RX1

PEG_RX1*

PEG_RX2

PEG_RX2*

PEG_RX3

PEG_RX3*

PEG_RX4

PEG_RX4*

PEG_RX5

PEG_RX5*

PEG_RX6

PEG_RX6*

PEG_RX7

PEG_RX7*

PEG_RX8

PEG_RX8*

PEG_RX9

PEG_RX9*

PEG_RX10

PEG_RX10*

PEG_RX11

PEG_RX11*

PEG_RX12

PEG_RX12*

PEG_RX13

PEG_RX13*

PEG_RX14

PEG_RX14*

PEG_RX15

PEG_RX15*

DMI_RX0

DMI_RX0*

DMI_RX1

DMI_RX1*

DMI_RX2

DMI_RX2*

DMI_RX3

DMI_RX3*

CPU Socket

CPU Socket

3/10

3/10

PEG_TX0

PEG_TX0*

PEG_TX1

PEG_TX1*

PEG_TX2

PEG_TX2*

PEG_TX3

PEG_TX3*

PEG_TX4

PEG_TX4*

PEG DMI

PEG DMI

PEG_TX5

PEG_TX5*

PEG_TX6

PEG_TX6*

PEG_TX7

PEG_TX7*

PEG_TX8

PEG_TX8*

PEG_TX9

PEG_TX9*

PEG_TX10

PEG_TX10*

PEG_TX11

PEG_TX011

PEG_TX12

PEG_TX12*

PEG_TX13

PEG_TX13*

PEG_TX14

PEG_TX14*

PEG_TX15

PEG_TX15*

DMI_TX0

DMI_TX0*

DMI_TX1

DMI_TX1*

DMI_TX2

DMI_TX2*

DMI_TX3

DMI_TX3*

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

C7

D7

E7

E6

E5

F5

F3

F4

G6

G5

H4

H3

F7

G7

J6

J5

K3

K4

H8

J8

L6

L5

M4

M3

K7

L7

N6

N5

M8

N8

R5

R6

L1

M1

N3

N2

N1

P1

R2

R3

D11

C10

B10

A11

2

X_EXP_A_TX_DP0

X_EXP_A_TX_DN0

X_EXP_A_TX_DP1

X_EXP_A_TX_DN1

X_EXP_A_TX_DP2

X_EXP_A_TX_DN2

X_EXP_A_TX_DP3

X_EXP_A_TX_DN3

X_EXP_A_TX_DP4

X_EXP_A_TX_DN4

X_EXP_A_TX_DP5

X_EXP_A_TX_DN5

X_EXP_A_TX_DP6

X_EXP_A_TX_DN6

X_EXP_A_TX_DP7

X_EXP_A_TX_DN7

X_EXP_A_TX_DP8

X_EXP_A_TX_DN8

X_EXP_A_TX_DP9

X_EXP_A_TX_DN9

X_EXP_A_TX_DP10

X_EXP_A_TX_DN10

X_EXP_A_TX_DP11

X_EXP_A_TX_DN11

X_EXP_A_TX_DP12

X_EXP_A_TX_DN12

X_EXP_A_TX_DP13

X_EXP_A_TX_DN13

X_EXP_A_TX_DP14

X_EXP_A_TX_DN14

X_EXP_A_TX_DP15

X_EXP_A_TX_DN15

H_GRCOMP

H_GRBIAS

0.4''<L<1.4"

W=10mil

X_EXP_A_TX_DP[15..0] 13

X_EXP_A_TX_DN[15..0] 13

H_DMI_TX_DP0 16

H_DMI_TX_DN0 16

H_DMI_TX_DP1 16

H_DMI_TX_DN1 16

H_DMI_TX_DP2 16

H_DMI_TX_DN2 16

H_DMI_TX_DP3 16

H_DMI_TX_DN3 16

R188 49.9

R188 49.9

*

*

R191 750

R191 750

*

*

1

PCIE COMP SIGNAL TERMINATION

+/-1%

+/-1%

+/-1%

+/-1%

B B

A A

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

CPU-3:FDI/PCIE/DMI

CPU-3:FDI/PCIE/DMI

CPU-3:FDI/PCIE/DMI

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet

FOXCONN PCEG

H55MXV

H55MXV

H55MXV

650Wednesday, April 21, 2010

650Wednesday, April 21, 2010

650Wednesday, April 21, 2010

1

B00A3

B00A3

B00A3

of

Page 7

5

HU1A

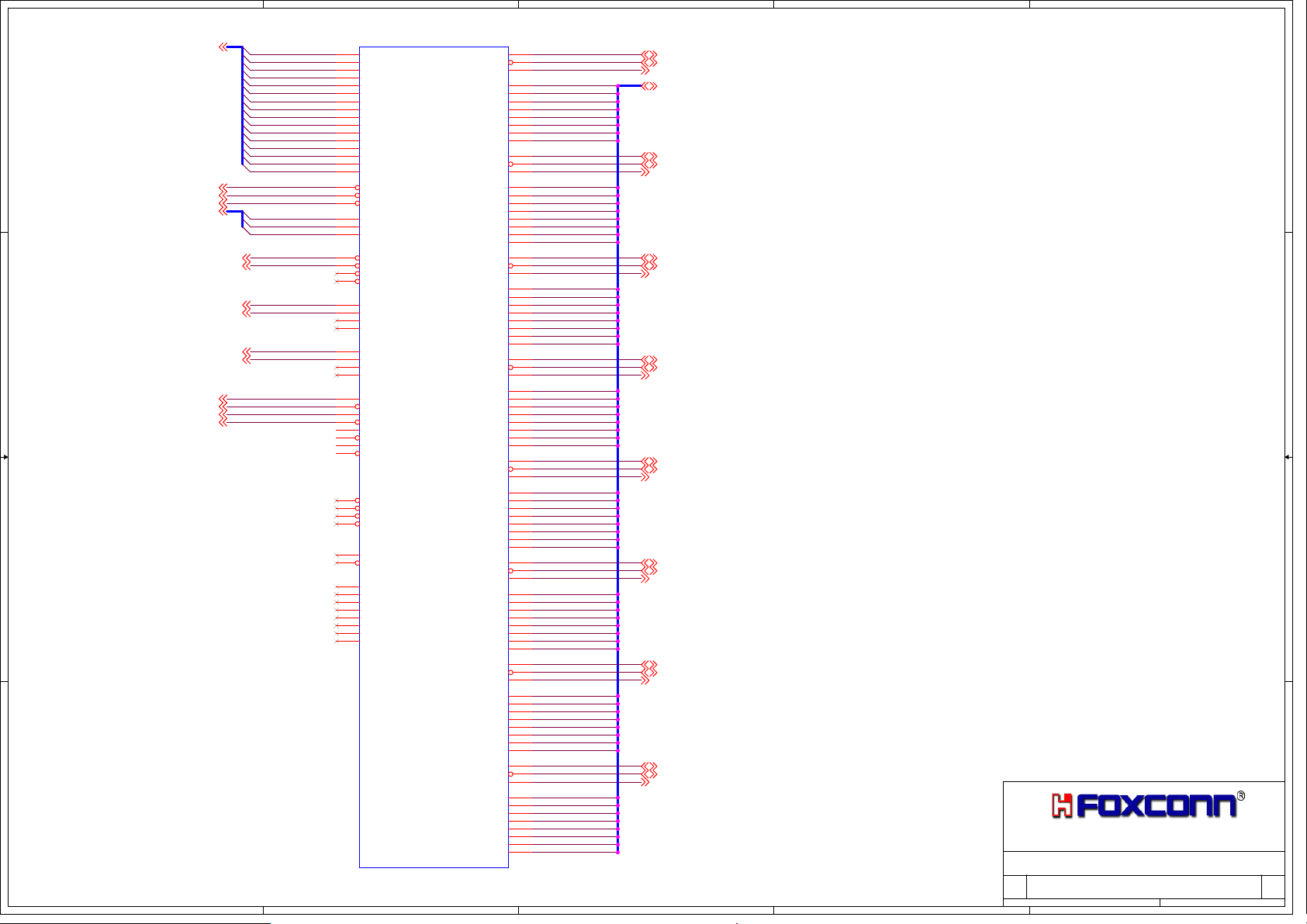

D3_MAA_A[15..0]11

D D

D3_WE_A#11

D3_CAS_A#11

D3_RAS_A#11

D3_SBS_A[2..0]11

D3_SCS_A_#011

D3_SCS_A_#111

D3_SCKE_A011

D3_SCKE_A111

D3_ODT_A011

C C

D3_CK_DDR_A_DP011

D3_CK_DDR_A_DN011

D3_CK_DDR_A_DP111

D3_CK_DDR_A_DN111

B B

A A

D3_ODT_A111

D3_DRAMRST#11,12

5

D3_MAA_A0

D3_MAA_A1

D3_MAA_A2

D3_MAA_A3

D3_MAA_A4

D3_MAA_A5

D3_MAA_A6

D3_MAA_A7

D3_MAA_A8

D3_MAA_A9

D3_MAA_A10

D3_MAA_A11

D3_MAA_A12

D3_MAA_A13

D3_MAA_A14

D3_MAA_A15

D3_SBS_A0

D3_SBS_A1

D3_SBS_A2

D3_SCS_A_#0

D3_SCS_A_#1

D3_SCKE_A0

D3_SCKE_A1

D3_ODT_A0

D3_ODT_A1

AW18

AY15

AV15

AU15

AW14

AY13

AV14

AW13

AU14

AW12

AT19

AU13

AW11

AU24

AT11

AR10

AT22

AU22

AT20

AV20

AU19

AU12

AV21

AW24

AU21

AU23

AU10

AW10

AV10

AY10

AV23

AV24

AW23

AY24

AR22

AR21

AP18

AN18

AN21

AP21

AP19

AN19

AV8

AK22

AM22

AL23

AK23

AL10

AM10

AP10

AN10

AR11

AP11

AK9

AL9

AK11

AM11

HU1A

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_WE*

SA_CAS*

SA_RAS*

SA_BS0

SA_BS1

SA_BS2

SA_CS0*

SA_CS1*

SA_CS2*

SA_CS3*

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_ODT0

SA_ODT1

SA_ODT2

SA_ODT3

SA_CK0

SA_CK0*

SA_CK1

SA_CK1*

SA_CK2

SA_CK2*

SA_CK3

SA_CK3*

SM_DRAMRST*

SA_CS4*

SA_CS5*

SA_CS6*

SA_CS7*

SA_DQS8

SA_DQS8*

SA_ECC_CB0

SA_ECC_CB1

SA_ECC_CB2

SA_ECC_CB3

SA_ECC_CB4

SA_ECC_CB5

SA_ECC_CB6

SA_ECC_CB7

CPU Socket

CPU Socket

4

DDR_A

DDR_A

1/10

1/10

4

SA_DQS0

SA_DQS0*

SA_DM0

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQS1

SA_DQS1*

SA_DM1

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQS2

SA_DQS2*

SA_DM2

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQS3

SA_DQS3*

SA_DM3

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQS4

SA_DQS4*

SA_DM4

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQS5

SA_DQS5*

SA_DM5

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQS6

SA_DQS6*

SA_DM6

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQS7

SA_DQS7*

SA_DM7

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

AK3

AJ3

AJ2

AH1

AJ4

AL2

AL1

AG2

AH2

AK1

AK2

AP2

AP3

AN1

AN3

AN2

AR3

AR2

AM3

AM2

AP1

AR4

AU4

AU3

AU1

AT4

AU2

AW3

AW4

AT3

AT1

AV2

AV4

AY6

AW6

AV6

AW5

AY5

AU8

AY8

AU5

AV5

AV7

AW7

AR28

AT29

AN29

AN27

AT28

AP28

AP30

AN26

AR27

AR29

AN30

AV32

AW32

AW31

AU30

AU31

AV33

AU34

AV30

AW30

AU33

AW33

AW36

AV35

AU35

AW35

AY35

AV37

AU37

AY34

AW34

AV36

AW37

AR39

AR38

AT38

AT39

AT40

AN38

AN39

AU38

AU39

AP39

AP40

D3_DATA_A0

D3_DATA_A1

D3_DATA_A2

D3_DATA_A3

D3_DATA_A4

D3_DATA_A5

D3_DATA_A6

D3_DATA_A7

D3_DATA_A8

D3_DATA_A9

D3_DATA_A10

D3_DATA_A11

D3_DATA_A12

D3_DATA_A13

D3_DATA_A14

D3_DATA_A15

D3_DATA_A16

D3_DATA_A17

D3_DATA_A18

D3_DATA_A19

D3_DATA_A20

D3_DATA_A21

D3_DATA_A22

D3_DATA_A23

D3_DATA_A24

D3_DATA_A25

D3_DATA_A26

D3_DATA_A27

D3_DATA_A28

D3_DATA_A29

D3_DATA_A30

D3_DATA_A31

D3_DATA_A32

D3_DATA_A33

D3_DATA_A34

D3_DATA_A35

D3_DATA_A36

D3_DATA_A37

D3_DATA_A38

D3_DATA_A39

D3_DATA_A40

D3_DATA_A41

D3_DATA_A42

D3_DATA_A43

D3_DATA_A44

D3_DATA_A45

D3_DATA_A46

D3_DATA_A47

D3_DATA_A48

D3_DATA_A49

D3_DATA_A50

D3_DATA_A51

D3_DATA_A52

D3_DATA_A53

D3_DATA_A54

D3_DATA_A55

D3_DATA_A56

D3_DATA_A57

D3_DATA_A58

D3_DATA_A59

D3_DATA_A60

D3_DATA_A61

D3_DATA_A62

D3_DATA_A63

3

D3_DQS_A_DP0 11

D3_DQS_A_DN0 11

D3_DM_A0 11

D3_DATA_A[63..0] 11

D3_DQS_A_DP1 11

D3_DQS_A_DN1 11

D3_DM_A1 11

D3_DQS_A_DP2 11

D3_DQS_A_DN2 11

D3_DM_A2 11

D3_DQS_A_DP3 11

D3_DQS_A_DN3 11

D3_DM_A3 11

D3_DQS_A_DP4 11

D3_DQS_A_DN4 11

D3_DM_A4 11

D3_DQS_A_DP5 11

D3_DQS_A_DN5 11

D3_DM_A5 11

D3_DQS_A_DP6 11

D3_DQS_A_DN6 11

D3_DM_A6 11

D3_DQS_A_DP7 11

D3_DQS_A_DN7 11

D3_DM_A7 11

3

2

Title

Title

Title

CPU-4:DDR3_CHA

CPU-4:DDR3_CHA

CPU-4:DDR3_CHA

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

H55MXV

H55MXV

H55MXV

1

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

750Wednesday, April 21, 2010

750Wednesday, April 21, 2010

750Wednesday, April 21, 2010

1

B00A3

B00A3

B00A3

Page 8

5

D3_MAA_B[15..0]12

D D

D3_WE_B#12

D3_CAS_B#12

D3_RAS_B#12

D3_SBS_B[2..0]12

D3_SCS_B_#012

D3_SCS_B_#112

D3_SCKE_B012

D3_SCKE_B112

C C

D3_CK_DDR_B_DP012

D3_CK_DDR_B_DN012

D3_CK_DDR_B_DP112

D3_CK_DDR_B_DN112

B B

A A

5

D3_ODT_B012

D3_ODT_B112

D3_MAA_B0

D3_MAA_B1

D3_MAA_B2

D3_MAA_B3

D3_MAA_B4

D3_MAA_B5

D3_MAA_B6

D3_MAA_B7

D3_MAA_B8

D3_MAA_B9

D3_MAA_B10

D3_MAA_B11

D3_MAA_B12

D3_MAA_B13

D3_MAA_B14

D3_MAA_B15

D3_SBS_B0

D3_SBS_B1

D3_SBS_B2

D3_SCS_B_#0

D3_SCS_B_#1

D3_SCKE_B0

D3_SCKE_B1

D3_ODT_B0

D3_ODT_B1

AU20

AU18

AV18

AU17

AY18

AV17

AW17

AU16

AT17

AY16

AY25

AW16

AW15

AW28

AY12

AV11

AU26

AW27

AW26

AU25

AW25

AV12

AY27

AW29

AV26

AV29

AW8

AU27

AU29

AV27

AU28

AR17

AR16

AT15

AR15

AN17

AN16

AR19

AR18

AM23

AM24

AL24

AK24

AR14

AR13

AR12

AT13

AN15

AP14

AM12

AN12

AN14

AP13

AY9

AU9

AV9

HU1B

HU1B

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_WE*

SB_CAS*

SB_RAS*

SB_BS0

SB_BS1

SB_BS2

SB_CS0*

SB_CS1*

SB_CS2*

SB_CS3*

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_ODT0

SB_ODT1

SB_ODT2

SB_ODT3

SB_CK0

SB_CK0*

SB_CK1

SB_CK1*

SB_CK2

SB_CK2*

SB_CK3

SB_CK3*

SB_CS4*

SB_CS5*

SB_CS6*

SB_CS7*

SB_DQS8

SB_DQS8*

SB_ECC_CB0

SB_ECC_CB1

SB_ECC_CB2

SB_ECC_CB3

SB_ECC_CB4

SB_ECC_CB5

SB_ECC_CB6

SB_ECC_CB7

CPU Socket

CPU Socket

4

AF4

SB_DQS0

AE5

SB_DQS0*

AE4

SB_DM0

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQS1

SB_DQS1*

SB_DM1

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQS2

SB_DQS2*

SB_DM2

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQS3

SB_DQS3*

SB_DM3

SB_DQ24

SB_DQ25

SB_DQ26

DDR_B

DDR_B

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQS4

SB_DQS4*

SB_DM4

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQS5

SB_DQS5*

SB_DM5

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQS6

SB_DQS6*

SB_DM6

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQS7

SB_DQS7*

SB_DM7

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

2/10

2/10

SB_DQ61

SB_DQ62

SB_DQ63

4

AD7

AD6

AH8

AJ8

AC7

AC6

AF5

AE6

AH6

AJ5

AH4

AG5

AH7

AK6

AL4

AG6

AG4

AJ7

AK7

AN6

AM6

AM7

AL6

AN5

AP6

AR5

AL5

AM4

AN7

AP5

AR8

AP8

AT7

AT6

AR7

AR9

AM8

AN8

AR6

AL8

AT9

AT25

AR24

AN24

AN23

AP23

AR25

AR26

AT23

AP22

AP25

AT26

AP32

AR32

AN32

AT32

AP31

AR33

AM32

AT31

AR31

AR34

AT33

AR36

AR37

AM33

AR35

AT36

AN33

AP36

AP34

AT35

AN34

AP37

AL37

AM36

AK35

AL35

AM35

AJ36

AJ37

AN35

AM34

AJ35

AL36

D3_DATA_B0

D3_DATA_B1

D3_DATA_B2

D3_DATA_B3

D3_DATA_B4

D3_DATA_B5

D3_DATA_B6

D3_DATA_B7

D3_DATA_B8

D3_DATA_B9

D3_DATA_B10

D3_DATA_B11

D3_DATA_B12

D3_DATA_B13

D3_DATA_B14

D3_DATA_B15

D3_DATA_B16

D3_DATA_B17

D3_DATA_B18

D3_DATA_B19

D3_DATA_B20

D3_DATA_B21

D3_DATA_B22

D3_DATA_B23

D3_DATA_B24

D3_DATA_B25

D3_DATA_B26

D3_DATA_B27

D3_DATA_B28

D3_DATA_B29

D3_DATA_B30

D3_DATA_B31

D3_DATA_B32

D3_DATA_B33

D3_DATA_B34

D3_DATA_B35

D3_DATA_B36

D3_DATA_B37

D3_DATA_B38

D3_DATA_B39

D3_DATA_B40

D3_DATA_B41

D3_DATA_B42

D3_DATA_B43

D3_DATA_B44

D3_DATA_B45

D3_DATA_B46

D3_DATA_B47

D3_DATA_B48

D3_DATA_B49

D3_DATA_B50

D3_DATA_B51

D3_DATA_B52

D3_DATA_B53

D3_DATA_B54

D3_DATA_B55

D3_DATA_B56

D3_DATA_B57

D3_DATA_B58

D3_DATA_B59

D3_DATA_B60

D3_DATA_B61

D3_DATA_B62

D3_DATA_B63

3

D3_DQS_B_DP0 12

D3_DQS_B_DN0 12

D3_DM_B0 12

D3_DATA_B[63..0] 12

D3_DQS_B_DP1 12

D3_DQS_B_DN1 12

D3_DM_B1 12

D3_DQS_B_DP2 12

D3_DQS_B_DN2 12

D3_DM_B2 12

D3_DQS_B_DP3 12

D3_DQS_B_DN3 12

D3_DM_B3 12

D3_DQS_B_DP4 12

D3_DQS_B_DN4 12

D3_DM_B4 12

D3_DQS_B_DP5 12

D3_DQS_B_DN5 12

D3_DM_B5 12

D3_DQS_B_DP6 12

D3_DQS_B_DN6 12

D3_DM_B6 12

D3_DQS_B_DP7 12

D3_DQS_B_DN7 12

D3_DM_B7 12

3

2

Title

Title

Title

CPU-5:DDR3_CHB

CPU-5:DDR3_CHB

CPU-5:DDR3_CHB

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

H55MXV

H55MXV

H55MXV

1

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

850Wednesday, April 21, 2010

850Wednesday, April 21, 2010

850Wednesday, April 21, 2010

1

B00A3

B00A3

B00A3

Page 9

5

VCORE V_1P1_VTT V_1P1_AXG V_1P5_SM

HU1F

C23

C24

C25

C27

C28

C30

C31

C33

C34

C36

C37

C39

C40

D23

D24

D26

D27

D29

D30

D32

D33

D35

D36

D38

D39

G20

G21

G23

G24

G26

G27

G29

G30

G32

G33

G35

G36

G38

G39

H19

H20

H22

H23

H25

A23

A24

A26

A27

A33

A35

A36

A38

B23

B25

B26

B28

B29

B31

B32

B34

B35

B37

B38

E22

E23

E25

E26

E28

E29

E31

E32

E34

E35

E37

E38

E40

F21

F22

F24

F25

F27

F28

F30

F31

F33

F34

F36

F37

F39

F40

HU1F

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6

VCC_7

VCC_NCTF_1

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_NCTF_2

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56

VCC_57

VCC_58

VCC_59

VCC_60

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

VCC_72

VCC_73

VCC_74

VCC_75

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

VCC_81

VCC_82

VCC_83

VCC_84

VCC_85

VCC_86

VCC_87

VCC_88

CPU Socket

CPU Socket

VCC_89

VCC_90

VCC_91

VCC_92

VCC_93

VCC_94

VCC_95

VCC_96

VCC_97

VCC_98

VCC_99

VCC_100

VCC_101

VCC_102

VCC_103

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

VCC_110

VCC_111

VCC_112

VCC_113

VCC_114

VCC_115

VCC_116

VCC_117

VCC_118

VCC_119

VCC_120

VCC_121

VCC_122

CPU POWER

CPU POWER

VCC_123

VCC_124

VCC_125

VCC_126

VCC_127

VCC_128

VCC_129

VCC_130

VCC_131

VCC_132

VCC_133

VCC_134

VCC_135

VCC_136

VCC_137

VCC_138

VCC_139

VCC_140

VCC_141

VCC_142

VCC_143

VCC_144

VCC_145

VCC_146

VCC_147

VCC_148

VCC_149

VCC_150

VCC_151

VCC_152

VCC_153

VCC_154

VCC_155

VCC_156

VCC_157

VCC_158

VCC_159

VCC_160

VCC_161

VCC_162

VCC_163

VCC_164

VCC_165

VCC_166

VCC_167

VCC_168

VCC_169

VCC_170

VCC_171

VCC_172

VCC_173

VCC_174

VCC_175

VCC_176

VCC_177

VCC_178

VCC_179

VCC_180

VCC_181

6/10

6/10

VCC_182

H26

H28

H29

H31

H32

H34

H35

H37

H38

H40

J18

J19

J21

J22

J24

J25

J27

J28

J30

J31

J33

J34

J36

J37

J39

J40

K17

K18

K20

K21

K23

K24

K26

K27

K29

K30

K32

K33

K35

K36

K38

K39

L17

L19

L20

L22

L23

L25

L26

L28

L29

L31

L32

L34

L35

L37

L38

L40

M17

M19

M21

M22

M24

M25

M27

M28

M30

M33

M34

M36

M37

M39

M40

N33

N35

N36

N38

N39

P33

P34

P35

P36

P37

P38

P39

P40

R33

R34

R35

R36

R37

R38

R39

R40

D D

C C

B B

A A

5

4

HU1G

HU1G

AA38

VTT_1

AC38

VTT_2

AC39

VTT_3

AC40

VTT_4

AD38

VTT_5

AD39

VTT_6

AD40

VTT_7

AE39

VTT_8

AE40

VTT_9

V38

VTT_10

V39

VTT_11

V40

VTT_12

Y38

VTT_13

AA33

VTT_14

AA34

VTT_15

AA35

VTT_16

AA36

VTT_17

AA37

VTT_18

AC33

VTT_19

AC34

VTT_20

AC35

VTT_21

AC36

VTT_22

AC37

VTT_23

AD33

VTT_24

AD34

VTT_25

AD35

VTT_26

AD36

VTT_27

AD37

VTT_28

AE33

VTT_29

AE34

VTT_30

AF33

VTT_31

AG33

VTT_32

AJ31

VTT_33

AJ32

VTT_34

V33

VTT_35

V34

VTT_36

V35

VTT_37

V36

VTT_38

V37

VTT_39

Y33

VTT_40

Y34

VTT_41

Y35

VTT_42

Y36

VTT_43

Y37

VTT_44

AC8

VTT_45

AE8

VTT_46

AJ17

VTT_47

AJ19

VTT_48

AK19

VTT_49

AJ21

VTT_50

AJ25

VTT_51

AJ27

VTT_52

AJ29

VTT_53

AK20

VTT_54

AK21

VTT_55

AL20

VTT_56

AL21

VTT_57

7/10

7/10

CPU Socket

CPU Socket

V_1P1_VTT

C280

C280

4.7uF

4.7uF

*

*

*

*

+/-10%

+/-10%

CLOSE TO CPU

4

3

T6

VTT_58

T7

VTT_59

T8

VTT_60

V7

VTT_61

V8

VTT_62

AB7

VTT_63

AC5

VTT_64

AJ23

VTT_65

V6

VTT_66

W1

VTT_67

W6

VTT_68

L10

VTT_69

M10

VTT_70

M11

VTT_71

M9

VTT_72

N7

VTT_73

P6

CPU POWER

CPU POWER

VTT_74

P7

VTT_75

P8

VTT_76

T2

VTT_77

V2

VTT_78

V_1P8_SFR_R

AF7

VCCPLL_1

AF8

VCCPLL_2

AG8

VCCPLL_3

*

*

10V, X5R, +/-10%

10V, X5R, +/-10%

C279

C279

C304

C304

*

*

0.1uF

0.1uF

0.1uF

0.1uF

Dummy

Dummy

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

3

C321

C321

1uF

1uF

#REFDE44

#REFDE44

1 2

#REFDE47

#REFDE47

1 2

#REFDE49

#REFDE49

dummy

dummy

1 2

dummy

dummy

dummy

dummy

V_1P8_SFR

V_1P5_SM

C316

C316

*

*

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

C317

C317

*

*

22uF

22uF

6.3V,X5R,+/-20%

6.3V,X5R,+/-20%

@F2

@F2

2

HU1H

HU1H

A14

VAXG_1

A15

VAXG_2

A17

VAXG_3

A18

VAXG_4

B14

VAXG_5

B15

VAXG_6

B17

VAXG_7

B18

VAXG_8

C14

VAXG_9

C15

VAXG_10

C17

C18

C20

C21

D14

D15

D17

D18

D20

D21

E14

E15

E17

E18

E20

F14

F15

F17

F18

F19

G14

G15

G17

G18

H14

H15

H17

J14

J15

J16

K14

K15

K16

L14

L15

L16

M14

M15

M16

2

VAXG_11

VAXG_12

VAXG_13

VAXG_14

VAXG_15

VAXG_16

VAXG_17

VAXG_18

VAXG_19

VAXG_20

VAXG_21

VAXG_22

VAXG_23

VAXG_24

VAXG_25

VAXG_26

VAXG_27

VAXG_28

VAXG_29

VAXG_30

VAXG_31

VAXG_32

VAXG_33

VAXG_34

VAXG_35

VAXG_36

VAXG_37

VAXG_38

VAXG_39

VAXG_40

VAXG_41

VAXG_42

VAXG_43

VAXG_44

VAXG_45

VAXG_46

VAXG_47

VAXG_48

VAXG_49

CPU Socket

CPU Socket

MCH POWER

MCH POWER

8/10

8/10

AJ11

VDDQ_1

AJ13

VDDQ_2

AJ15

VDDQ_3

AT10

VDDQ_6

AT18

VDDQ_4

AT21

VDDQ_5

AU11

VDDQ_7

AV13

VDDQ_8

AV16

VDDQ_9

AV19

VDDQ_10

AV22

VDDQ_11

AV25

VDDQ_12

AV28

VDDQ_13

AW9

VDDQ_14

AY11

VDDQ_15

AY14

VDDQ_16

AY17

VDDQ_17

AY23

VDDQ_18

AY26

VDDQ_19

Title

Title

Title

CPU-6:POWER

CPU-6:POWER

CPU-6:POWER

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

Date: Sheet of

H55MXV

H55MXV

H55MXV

1

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

950Wednesday, April 21, 2010

950Wednesday, April 21, 2010

950Wednesday, April 21, 2010

1

of

B00A3

B00A3

B00A3

Page 10

5

HU1I

HU1I

A16

VSS_1

A25

VSS_2

A28

VSS_3

A34

VSS_4

A37

VSS_5

AA5

VSS_6

AB3

VSS_7

AB33

VSS_8

D D

C C

B B

A A

AB34

AB35

AB36

AB37

AB38

AB39

AB40

AB6

AB8

AC1

AD5

AD8

AE3

AE37

AE7

AF1

AF40

AF6

AG34

AG36

AG7

AH3

AH33

AH38

AH5

AJ1

AJ12

AJ14

AJ16

AJ18

AJ20

AJ22

AJ24

AJ26

AJ28

AJ30

AJ33

AJ34

AJ40

AJ6

AJ9

AK10

AK17

AK36

AK4

AK5

AK8

AL11

AL13

AL16

AL19

AL22

AL25

AL28

AL3

AL31

AL34

AL38

AL7

AM1

AM40

AM5

AM9

AN13

AN20

AN22

AN25

AN28

AN31

AN36

AN4

AN9

AP12

AP15

AP16

AP17

AP20

AP24

AP26

AP27

AP29

AP33

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_30

VSS_31

VSS_32

VSS_33

VSS_276

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_277

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_278

VSS_279

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_77

VSS_280

VSS_281

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_91

CPU Socket

CPU Socket

9/10

9/10

GND

GND

VSS_282

VSS_92

VSS_283

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_284

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_285

VSS_286

VSS_110

VSS_287

VSS_111

VSS_288

VSS_289

VSS_290

VSS_113

VSS_114

VSS_115

VSS_291

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

AP35

AP38

AP4

AP7

AP9

AR1

AR20

AR23

AR30

AR40

AT12

AT14

AT16

AT2

AT24

AT27

AT30

AT34

AT37

AT5

AT8

AU32

AU36

AU6

AU7

AV3

AV31

AV34

AV38

AY33

AY36

AY4

AY7

B16

B24

B27

B30

B33

B36

B7

B9

C13

C16

C19

C22

C26

C29

C32

C35

C38

C5

D10

D12

D13

D16

D19

D22

D25

D28

D31

D34

D37

D4

D40

D5

D6

D8

E13

E16

E19

E21

E24

E27

E3

E30

E33

E36

E39

E4

F11

F13

F16

F2

F20

F23

F26

F29

F32

F35

F38

4

HU1J

HU1J

F8

VSS_179

G13

VSS_180

G16

VSS_181

G19

VSS_182

G22

VSS_183

G25

VSS_184

G28

VSS_185

G31

VSS_186

G34

VSS_187

G37

VSS_188

G4

VSS_189

G40

VSS_190

G9

VSS_191

H11

VSS_192

H13

VSS_193

H16

VSS_194

H18

VSS_195

H2

VSS_196

H21

VSS_197

H24

VSS_198

H27

VSS_199

H30

VSS_200

H33

VSS_201

H36

VSS_202

H39

VSS_203

H5

VSS_204

H6

VSS_205

J13

VSS_206

J17

VSS_207

J20

VSS_208

J23

VSS_209

J26

VSS_210

J29

VSS_211

J32

VSS_212

J35

VSS_213

J38

VSS_214

J4

VSS_215

J7

VSS_216

J9

VSS_217

K11

VSS_218

K13

VSS_219

K19

VSS_220

K2

VSS_221

K22

VSS_222

K25

VSS_223

K28

VSS_224

K31

VSS_225

K34

VSS_226

K37

VSS_227

K40

VSS_228

K5

VSS_229

K6

VSS_230

L13

VSS_231

L18

VSS_232

L21

VSS_233

L24

VSS_234

L27

VSS_235

L30

VSS_236

L33

VSS_237

L36

VSS_238

L39

VSS_239

L4

VSS_240

L9

VSS_241

M13

VSS_242

M18

VSS_243

M2

VSS_244

M20

VSS_245

M23

VSS_246

M26

VSS_247

M29

VSS_248

M32

VSS_249

M35

VSS_250

M38

VSS_251

M5

VSS_252

M6

VSS_253

M7

VSS_254

N34

VSS_255

N37

VSS_256

N4

VSS_257

N40

VSS_258

P2

VSS_259

P5

VSS_260

R4

VSS_261

T33

VSS_262

T36

VSS_263

T37

VSS_264

T38

VSS_265

T5

VSS_266

U4

VSS_267

V5

VSS_268

CPU Socket

CPU Socket

3

VSS_269

VSS_270

VSS_271

VSS_272

VSS_273

VSS_274

VSS_275

CGC_TP_NCTF

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

RSVD_1

RSVD_4

RSVD_5

RSVD_9

RSVD_10

GND

GND

RSVD_13

RSVD_14

RSVD_15

RSVD_16

RSVD_17

RSVD_18

RSVD_19

RSVD_20

RSVD_21

RSVD_22

RSVD_23

RSVD_24

RSVD_25

RSVD_26

RSVD_27

RSVD_28

RSVD_29

RSVD_30

RSVD_TP

RSVD_32

RSVD_33

RSVD_34

RSVD_35

RSVD_36

RSVD_37

VSS_292

RSVD_39

RSVD_40

RSVD_41

RSVD_42

RSVD_43

RSVD_44

RSVD_45

RSVD_46

RSVD_47

RSVD_48

RSVD_49

RSVD_50

RSVD_NCTF_1

RSVD_NCTF_2

RSVD_NCTF_3

RSVD_NCTF_4

RSVD_NCTF_5

RSVD_NCTF_6

RSVD_NCTF_7

RSVD_NCTF_8

RSVD_NCTF_9

RSVD_NCTF_10

RSVD_NCTF_11

10/10

10/10

W33

W34

W35

W36

W37

W38

Y7

B39

AF3

AG3

A12

AD2

AE2

AH40

AJ39

AM14

AM13

AK15

AK16

AM25

AL29

AM30

AK29

AK28

AM29

AM28

AL27

AK27

AM26

AM27

AL26

AK26

AK25

AN11

L12

M12

AM21

AM20

AM19

AM18

T39

AL18

AK18

AM15

AM16

AL15

AL14

AL17

AM17

AK14

AK13

AL12

AK12

AY3

C2

D1

AY37

AW38

AV1

AW2

AV39

AU40

A4

B3

H_TP_CGC

HTP2

HTP9

HTP10

HTP11

HTP13

HTP7

HTP8

H_INSENSE_DN

HTP12

HTP5

HTP6

HTP16

HTP17

HTP14

HTP15

HTP1

HTP3

TP6TP6

TP3TP3

TP11TP11

TP12TP12

TP13TP13

TP15TP15

TP8TP8

TP10TP10

TP16TP16

TP5TP5

TP7TP7

TP19TP19

TP20TP20

TP17TP17

TP18TP18

TP2TP2

TP4TP4

2

D3_DQ_VREF_A 11

D3_DQ_VREF_B 12

#REFDE35

#REFDE35

1 2

dummy

dummy

1

update by wesley 0715

HU1_1HU1_1

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

CPU-7:GND

CPU-7:GND

CPU-7:GND

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet

FOXCONN PCEG

H55MXV

H55MXV

H55MXV

10 50Wednesday, April 21, 2010

10 50Wednesday, April 21, 2010

10 50Wednesday, April 21, 2010

1

B00A3

B00A3

B00A3

of

Page 11

5

CHANNEL A BANK 1

SMB ADDRESS:00

4

3

2

1

D3_DM_A2

143

135

DQS10*

DM2/DQS11

D3_DQS_A_DP[7..0] 7

D3_DQS_A_DN[7..0] 7

D3_DM_A4

D3_DM_A3

203

152

153

144

DQS12*

DQS11*

DM4/DQS13

DM3/DQS12

D3_DM_A5

212

204

DQS13*

DM5/DQS14

V_1P5_SM

D3_DM_A[7..0] 7

D3_DATA_A62

D3_DATA_A61

D3_DATA_A60

D3_DATA_A59

D3_DATA_A58

D3_DATA_A57

D3_DATA_A56

D3_DATA_A55

D3_DATA_A54

D3_DATA_A53

D3_DATA_A52

D3_DATA_A51

D3_DATA_A50

D3_DATA_A49

D3_DATA_A48

D3_DATA_A47

D3_DATA_A46

D3_DATA_A45

D3_DATA_A44

D3_DATA_A43

D3_DATA_A42

D3_DATA_A41

D3_DATA_A40

D3_DATA_A39

D3_DATA_A38

D3_DATA_A37

D3_DATA_A36

D3_DATA_A35

D3_DATA_A34

D3_DATA_A33

D3_DATA_A32

D3_DATA_A31

D3_DATA_A30

D3_DATA_A29

D3_DATA_A28

D3_DATA_A27

D3_DATA_A26

D3_DATA_A25

D3_DATA_A24

D3_DATA_A23

D3_DATA_A22

D3_DATA_A21

D3_DATA_A20

D3_DATA_A19

D3_DATA_A18

D3_DATA_A17

D3_DATA_A16

D3_DATA_A15

D3_DATA_A14

D3_DATA_A13

D3_DATA_A12

D3_DATA_A11

D3_DATA_A10

D3_DATA_A9

D3_DATA_A8

D3_DATA_A7

D3_DATA_A6

D3_DATA_A5

D3_DATA_A4

D3_DATA_A3

D3_DATA_A2

D3_DATA_A1

230

191

DM7/DQS16

VDDQ

231

189

NC/DQS16*

VDDQ

VDDQ

186

161

183

DM8/DQS17

VDDQ

162

DQS17*

VDDQ

182

179

D3_DATA_A0

122

123

128

DQ<0>3DQ<1>4DQ<2>9DQ<3>10DQ<4>

DQ<5>

DQ<6>

VDDQ

VDDQ

VDDQ

VDDQ

VDD78VDD75VDD72VDD69VDD66VDD65VDD62VDD60VDD57VDD54VDD51VDDSPD

176

173

170

129

DQ<7>

131

132

137

138

140

DQ<15>

DQ<16>21DQ<17>22DQ<18>27DQ<19>28DQ<20>

VREFDQ1SCL

SDA

VREFCA

67

118

238

141

237

13

DQ<8>12DQ<9>

DQ<10>18DQ<11>19DQ<12>

DQ<13>

DQ<14>

DDRIII

DDRIII

236

146

147

DQ<21>

DQ<22>

SA1

SA0

117

DQ<23>

149

150

155

DQ<24>30DQ<25>31DQ<26>36DQ<27>37DQ<28>

DQ<29>

BA071BA1

BA2

52

190

156

DQ<30>

DQ<31>

DQ<32>81DQ<33>82DQ<34>87DQ<35>88DQ<36>

CKE050CKE1

169

200

201

206

207

DQ<37>

DQ<38>

DQ<39>

S0*

S1*76CK1/NU*64CK1/NU63CK0*

193

209

210

DQ<40>90DQ<41>91DQ<42>96DQ<43>97DQ<44>

CK0

185

184A0188A1181

215

216

DQ<45>

DQ<46>

A261A3

180

100

DQ<47>

DQ<48>99DQ<49>

A459A558A6

178

105

106

DQ<50>

A756A9

177

218

219

DQ<51>

DQ<52>

A8

175

224

225

DQ<53>

DQ<54>

A10/AP70A1155A12

174

108

109

DQ<55>

DQ<56>

A13

196

172

114

115

DQ<57>

DQ<58>

A14

A15

171

227

228

DQ<59>

DQ<60>

RESET*

168

233

DQ<61>

DQ<62>

CAS*74RAS*

192

D3_DM_A7

D3_DM_A6

221

222

213

DQS15*

DQS14*

DM6/DQS15

VDDQ

197

194

00

DDR_SPD12

SMB_CLK_MAIN12,14,35,41,47

SMB_DATA_MAIN12,14,35,41,47

D3_SBS_A[2..0]7

D3_SCKE_A17

D3_SCKE_A07

D3_SCS_A_#17

D3_SCS_A_#07

D3_CK_DDR_A_DN17

D3_CK_DDR_A_DP17

D3_CK_DDR_A_DN07

D3_CK_DDR_A_DP07

D3_MAA_A[15..0]7

DDR_SPD

D3_CA_VREF_A

D3_DQ_VREF_A

D3_SBS_A2

D3_SBS_A1

D3_SBS_A0

D3_MAA_A0

D3_MAA_A1

D3_MAA_A2

D3_MAA_A3

D3_MAA_A4

D3_MAA_A5

D3_MAA_A6

D3_MAA_A7

D3_MAA_A8

D3_MAA_A9

D3_MAA_A10

D3_MAA_A11

D3_MAA_A12

D3_MAA_A13

D3_MAA_A14

D3_MAA_A15

D3_DATA_A63

234

DQ<63>

WE*

73

D3_DATA_A[63..0] 7

D3_WE_A# 7

D3_RAS_A# 7

D3_CAS_A# 7

D3_DRAMRST# 7,12

D3_ODT_A1 7

D3_ODT_A0 7

D D

DIMM1

DIMM1

D3_DQS_A_DN7

D3_DQS_A_DP7

D3_DQS_A_DP6

D3_DQS_A_DN6

D3_DQS_A_DN5

D3_DQS_A_DP5

D3_DQS_A_DP4

D3_DQS_A_DN4

D3_DQS_A_DN3

D3_DQS_A_DP3

D3_DQS_A_DP2

D3_DQS_A_DN2

D3_DQS_A_DN1

D3_DQS_A_DP1

D3_DQS_A_DP0

D3_DQS_A_DN0

158

159

164

VSS

217

R429

R429

1K

1K

+/-1%

+/-1%

VSS

214

R431

R431

1K

1K

+/-1%

+/-1%

VSS

CB<5>

CB<6>

VSS

VSS

VSS

211

208

205

*

*

*

*

*

*

165

6

7

CB<7>

DQS<0>

DQS*<0>

VSS

VSS

VSS

VSS

VSS

VSS

202

199

166

163

160

157

C404

C404

1uF

1uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

D3_DQ_VREF_A

C423

C423

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

C434

C434

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

15

16

DQS<1>

DQS*<1>

VSS

VSS

VSS

154

151

148

*

*

D3_CA_VREF_A

33

24

34

25

DQS<3>

DQS<2>

DQS*<3>

DQS*<2>

VSS

VSS

VSS

VSS

VSS

145

142

139

136

133

130

C424

C424

1uF

1uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

D3_DQ_VREF_A 10

VSS

84

94

85

DQS<4>

DQS*<4>

VSS

VSS

VSS

127

124

121

119

DQS<5>

VSS

112

103

DQS<7>

DQS<6>

DQS*<7>

DQS*<6>

DQS*<5>

VSS

VSS

VSS

VSS

VSS

VSS

VSS98VSS95VSS92VSS89VSS86VSS83VSS80VSS47VSS44VSS41VSS38VSS35VSS32VSS29VSS26VSS23VSS20VSS17VSS14VSS11VSS8VSS5VSS2VDDQ

116

113

110

107

104

101

3D3V_SYS

C428

C428

*

*

Dummy

Dummy

10uF

10uF

+/-10%

+/-10%

111

102

93

195

ODT177ODT0

RSVD

VTT

FREE1

FREE2

FREE349FREE4

48

240

187

V_1P5_SM

C430

C430

1uF

1uF

*

*

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

C429

C429

4.7uF

4.7uF

*

*

10V,X5R,+/-10%

10V,X5R,+/-10%

R432

R432

Dummy

Dummy

C452

C452

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

R416

R416

Dummy

Dummy

C403

C403

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

68

167

53

CB<0>39CB<1>40CB<2>45CB<3>46CB<4>

VSS

VSS

VSS

VSS

VSS

VSS

239

235

232

229

226

223

NC/PAR_IN

VTT

120

NC/TEST4

NC/ERR_OUT

CLOSE TO DIMM POWER PIN

C406

C406

1uF

1uF

*

*

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

C433

C433

*

*

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

@F2

@F2

1K

1K

*

*

+/-1%

+/-1%

1K

1K

*

*

+/-1%

+/-1%

*

*

220

*

*

79

C C

198

V_SM_VTT

V_SM_VTT

B B

PLAECE CLOSE TO CH-A DIMM

V_1P5_SM

*

*

V_1P5_SM

*

*

A A

D3_DM_A1

D3_DM_A0

125

126

134

42

43

DQS9*

DQS<8>

DQS*<8>

DM0/DQS9

DM1/DQS10

Place close to +3V

C435

C435

*

*

1uF

1uF

Dummy

Dummy

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

DDR3 CONN:CHA_1

DDR3 CONN:CHA_1

DDR3 CONN:CHA_1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

FOXCONN PCEG

H55MXV

H55MXV

H55MXV

11 50Wednesday, April 21, 2010

11 50Wednesday, April 21, 2010

11 50Wednesday, April 21, 2010

1

B00A3

B00A3

B00A3

Page 12

5

4

3

2

1

CHANNEL B BANK 1

SMB ADDRESS:010

D3_DM_B2

143

135

DQS10*

DM2/DQS11

D3_DQS_B_DP[7..0] 8

D3_DQS_B_DN[7..0] 8

D3_DM_B4

D3_DM_B3

203

152

153

144

DQS12*

DQS11*

DM4/DQS13

DM3/DQS12

D3_DM_B[7..0] 8

D3_DATA_B39

D3_DATA_B38

D3_DATA_B37

D3_DATA_B36

D3_DATA_B35

D3_DATA_B34

D3_DATA_B33

D3_DATA_B32

D3_DATA_B31

D3_DATA_B30

D3_DATA_B29

D3_DATA_B28

D3_DATA_B27

D3_DATA_B26

D3_DATA_B25

D3_DATA_B24

D3_DATA_B23

D3_DATA_B22

D3_DATA_B21

D3_DATA_B20

D3_DATA_B19

D3_DATA_B18

D3_DATA_B17

D3_DATA_B16

D3_DATA_B15

D3_DATA_B14

D3_DATA_B13

D3_DATA_B12

D3_DATA_B11

D3_DATA_B10

D3_DATA_B9

D3_DATA_B8

D3_DATA_B7

D3_DATA_B6

D3_DATA_B5

D3_DATA_B4

D3_DATA_B3

D3_DATA_B2

D3_DATA_B1

230

191

DM7/DQS16

VDDQ

D3_DATA_B0

131

132

137

138

140

141

146

147

149

150

155

156

DQ<30>

DQ<31>

DQ<32>81DQ<33>82DQ<34>87DQ<35>88DQ<36>

CKE050CKE1

S1*76CK1/NU*64CK1/NU63CK0*

169

200

S0*

193

231

161

162

NC/DQS16*

DM8/DQS17

VDDQ

VDDQ

VDDQ

189

186

183

182

DQ<0>3DQ<1>4DQ<2>9DQ<3>10DQ<4>

DQS17*

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDD78VDD75VDD72VDD69VDD66VDD65VDD62VDD60VDD57VDD54VDD51VDDSPD

179

176

173

170

122

123

128

129

13

DQ<5>

DQ<6>

DQ<7>

DQ<8>12DQ<9>

DQ<10>18DQ<11>19DQ<12>

DQ<13>

DQ<14>

DQ<15>

DQ<16>21DQ<17>22DQ<18>27DQ<19>28DQ<20>

DQ<21>

DQ<22>

DQ<23>

DQ<24>30DQ<25>31DQ<26>36DQ<27>37DQ<28>

DQ<29>

DDRIII

DDRIII

VREFDQ1SCL

SDA

SA1

SA0

VREFCA

67

236

118

238

237

117

BA071BA1

BA2

52

190

201

206

DQ<37>

DQ<38>

207

D3_DATA_B43

D3_DATA_B42

D3_DATA_B41

D3_DATA_B40

DQ<39>

DQ<40>90DQ<41>91DQ<42>96DQ<43>97DQ<44>

CK0

185

184A0188A1181

D3_DATA_B48

D3_DATA_B47

D3_DATA_B46

D3_DATA_B45

D3_DATA_B44

209

210

215

216

DQ<45>

DQ<46>

DQ<47>

DQ<48>99DQ<49>

A261A3

A459A558A6

180

D3_DATA_B50

D3_DATA_B49

100

178

D3_DATA_B53

D3_DATA_B52

D3_DATA_B51

105

106

218

219

DQ<50>

DQ<51>

DQ<52>

DQ<53>

A756A9

A10/AP70A1155A12

A8

175

177

D3_DATA_B56

D3_DATA_B55

D3_DATA_B54

224

225

108

DQ<54>

DQ<55>

174

196

D3_DATA_B60

D3_DATA_B59

D3_DATA_B58

D3_DATA_B57

109

114

115

227

DQ<56>

DQ<57>

DQ<58>

DQ<59>

DQ<60>

A13

A14

A15

RESET*

172

171

168

D3_DATA_B62

D3_DATA_B61

228

233

DQ<61>

DQ<62>

CAS*74RAS*

192

D3_DM_B7

D3_DM_B6

D3_DM_B5

221

212

222

213

204

DQS15*

DQS14*

DQS13*

DM6/DQS15

DM5/DQS14

VDDQ

197

194

D3_DATA_B[63..0] 8

D3_DATA_B63

234

DQ<63>

WE*

73

D3_ODT_B1 8

D3_ODT_B0 8

D D

DIMM2

DIMM2

D3_DQS_B_DN3

D3_DQS_B_DP3

D3_DQS_B_DP2

D3_DQS_B_DN2

D3_DQS_B_DN1

D3_DQS_B_DP1

D3_DQS_B_DP0

D3_DQS_B_DN0

RSVD

FREE1

187

195

ODT177ODT0

FREE2

FREE349FREE4

48

68

167

53

NC/TEST4

NC/PAR_IN

NC/ERR_OUT

VSS

VSS

VSS

VTT

VTT

239

235

232

229

120

240

VSS

VSS

226

223

158

CB<0>39CB<1>40CB<2>45CB<3>46CB<4>

VSS

VSS

VSS

VSS

220

217

214

211

159

VSS

208

CB<5>

VSS

6

7

164

165

CB<6>

CB<7>

DQS<0>

VSS

VSS

VSS

VSS

VSS

205

202

199

166

163

160

DQS*<0>

VSS

24

15

25

16

DQS<2>

DQS<1>

DQS*<2>

DQS*<1>

VSS

VSS

VSS

VSS

VSS

VSS

VSS

157

154

151

148

145

142

139

79

C C

198

D3_DQS_B_DP5

D3_DQS_B_DP4

D3_DQS_B_DN4

84

33

94

85

34

DQS<5>

DQS<4>

DQS<3>

DQS*<4>

DQS*<3>

VSS

VSS

VSS

VSS

VSS

VSS

VSS

136

133

130

127

124

121

119

D3_DQS_B_DN7

D3_DQS_B_DP7

D3_DQS_B_DP6

D3_DQS_B_DN6

D3_DQS_B_DN5

111

102

93

112

103

DQS<7>

DQS<6>

DQS*<7>

DQS*<6>

DQS*<5>

VSS

VSS

VSS

VSS

VSS

VSS

VSS98VSS95VSS92VSS89VSS86VSS83VSS80VSS47VSS44VSS41VSS38VSS35VSS32VSS29VSS26VSS23VSS20VSS17VSS14VSS11VSS8VSS5VSS2VDDQ

116

113

110

107

104

101

D3_DM_B1

D3_DM_B0

134

42

43

125

126

DQS9*

DQS<8>

DQS*<8>

DM0/DQS9

DM1/DQS10

V_SM_VTT

V_1P5_SM

CLOSE TO DIMM POWER PIN

V_1P5_SM

C405

C427

R441

R441

1K

1K

+/-1%

+/-1%

C427

1uF

1uF

*

*

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

*

*

C436

C436

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

D3_CA_VREF_B

*

*

C450

C450

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

D3_DQ_VREF_B

C448

C448

1uF

1uF

*

*

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

V_SM_VTT

B B

A A

C401

C401

4.7uF

4.7uF

*

*

10V,X5R,+/-10%

10V,X5R,+/-10%

Dummy

Dummy

PLAECE CLOSE TO CH-B DIMM

V_1P5_SM

R434

R434

*

*

C451

C451

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

Dummy

Dummy

V_1P5_SM

R451 1K

R451 1K

*

*

C449

C449

Dummy

Dummy

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

*

*

+/-1%

+/-1%

C425

C425

1uF

1uF

*

*

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

C407

C407

*

*

0.1uF

0.1uF

Dummy

Dummy

16V, X7R, +/-10%

16V, X7R, +/-10%

1K

1K

+/-1%

+/-1%

*

*

5

*

*

R450

R450

1K

1K

+/-1%

+/-1%

C405

1uF

1uF

*

*

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

D3_DQ_VREF_B 10

4

SMB_CLK_MAIN11,14,35,41,47

SMB_DATA_MAIN11,14,35,41,47

D3_SBS_B[2..0]8

D3_CK_DDR_B_DN18

D3_CK_DDR_B_DP18

D3_CK_DDR_B_DN08

D3_CK_DDR_B_DP08

D3_MAA_B[15..0]8

DDR_SPD11

D3_CA_VREF_B

D3_DQ_VREF_B

D3_SBS_B2

D3_SBS_B1

D3_SBS_B0

D3_SCKE_B18

D3_SCKE_B08

D3_SCS_B_#18

D3_SCS_B_#08

D3_MAA_B0

D3_MAA_B1

D3_MAA_B2

D3_MAA_B3

D3_MAA_B4

D3_MAA_B5

D3_MAA_B6

D3_MAA_B7

D3_MAA_B8

D3_MAA_B9

D3_MAA_B10

D3_MAA_B11

D3_MAA_B12

D3_MAA_B13

D3_MAA_B14

D3_MAA_B15

3

3D3V_SYS

R433

R433

*

*

0

0

+/-5%

+/-5%

10

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

DDR3 CONN:CHB_1

DDR3 CONN:CHB_1

DDR3 CONN:CHB_1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

FOXCONN PCEG

H55MXV

H55MXV

H55MXV

D3_WE_B# 8

D3_RAS_B# 8

D3_CAS_B# 8

D3_DRAMRST# 7,11

1

B00A3

B00A3

B00A3

12 50Wednesday, April 21, 2010

12 50Wednesday, April 21, 2010

12 50Wednesday, April 21, 2010

Page 13

PCIEX16

5

4

3

2

1

RN9

RN9

*

*

1

3

5

7 8

8.2K

8.2K

+/-5%

+/-5%

X_EXP_A_RX_DP[15..0] 6

X_EXP_A_RX_DN[15..0] 6

3D3V_SYS

2

4

6

Dummy

Dummy

12V_SYS

EC14

EC14

270uF

270uF

*

*

16V, +/-20%

16V, +/-20%

3D3V_SYS

EC18

EC18

1000uF

1000uF

*

*

+/-20%

+/-20%

3D3V_DUAL

EC17

EC17

1000uF

1000uF

*

*

+/-20%

+/-20%

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet of

2

Date: Sheet of

C157

C157

*

*

0.1uF

0.1uF

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

C170

C170

*

*

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

C171

C171

*

*

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

@F2

@F2

C426

C426

*

*

0.1uF

0.1uF

Dummy

Dummy

16V, X7R, +/-10%

16V, X7R, +/-10%

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

PCIE 16X Slot

PCIE 16X Slot

PCIE 16X Slot

H55MXV

H55MXV

H55MXV

13 50Wednesday, April 21, 2010

13 50Wednesday, April 21, 2010

13 50Wednesday, April 21, 2010

1

B00A3

B00A3

B00A3

of

X_EXP_A_TX_DP[15..0]6

D D

C C

B B

A A

X_EXP_A_TX_DN[15..0]6

S_SMB_CLK_RESUME18,25,26,27,41

S_SMB_DATA_RESUME18,25,26,27,41

X_EXP_A_TX_DP0

X_EXP_A_TX_DN0

X_EXP_A_TX_DP1

X_EXP_A_TX_DN1

X_EXP_A_TX_DP2