Page 1

亞美商匯

5

4

3

2

1

Foxconn Precision Co. Inc.

D D

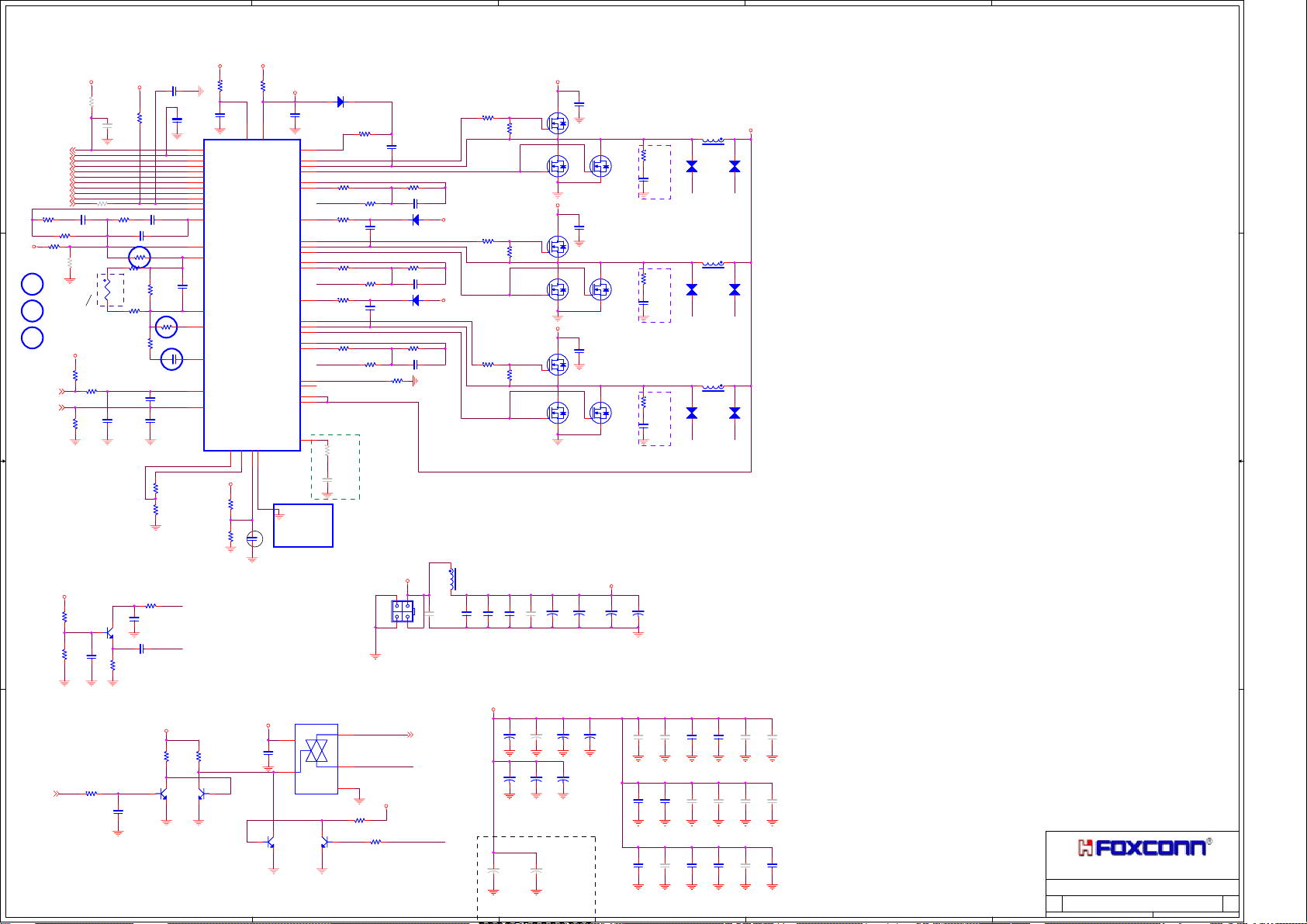

G41M05 Schematic

Fab.A

Data: 2008/7/30

C C

B B

A A

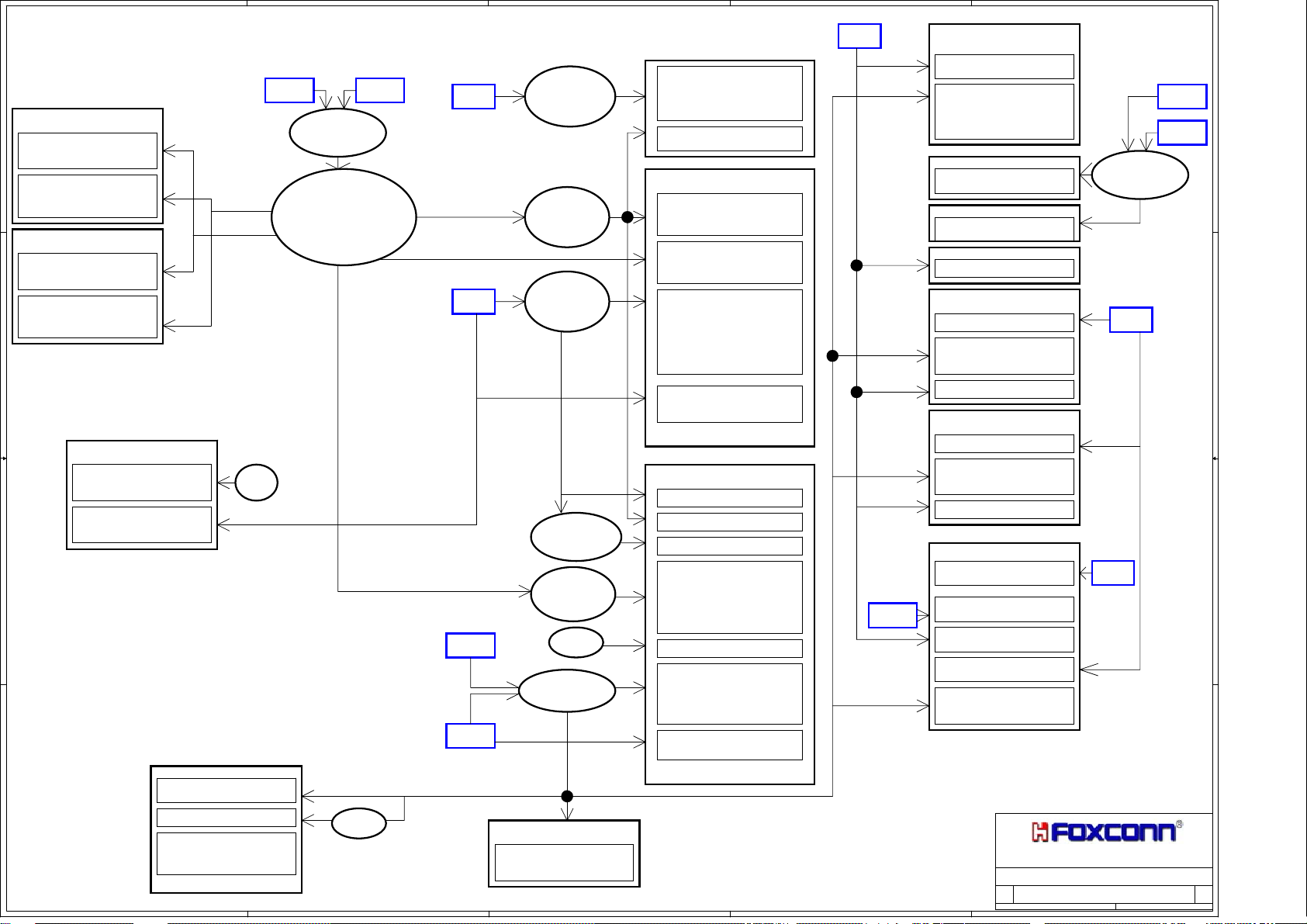

Page Index

01. Index Page

02. Topology

03. Rest Map

04. Clock Distribution

05. Power Delivery Map

06. Power Sequence

07. CLOCKGEN

08. Power / MISC Connectors

09. VRD11.1-RT8857

10. 1D125V 1D5V FSB

11. STR1D8V 3D3_DUAL

12. LGA775 -1

13. LGA775 -2

14. Eaglelake -GMCH -1

15. Eaglelake -GMCH -2

16. Eaglelake -GMCH -3

17. Eaglelake -GMCH -4

18. DDR2 Channel A Termination

19. DDR2 Channel A DIMM1

20. DDR2 Channel B Termination

21. DDR2 Channel B DIMM2

22. PCI Express x16 Gfx Slot

23. VGA

24. DVI

25. ICH7 -1

26. ICH7 -2

27. ICH7 -3

28. REAR USB

29. FRONT USB

30. PCI Express x1Slot

31. LAN-RTL8101E/8111B/8111C

32 AUDIO 662

33. Super I/O -IT8720F

34. Keyboard / Mouse / Fan

35. Serial Port / IR / CIR

36. BOARD ID

37. Changlist

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Index Page

Index Page

Index Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

FOXCONN PCEG

G41M05

G41M05

G41M05

1

134Thursday, October 22, 2009

134Thursday, October 22, 2009

134Thursday, October 22, 2009

AC

AC

AC

of

of

of

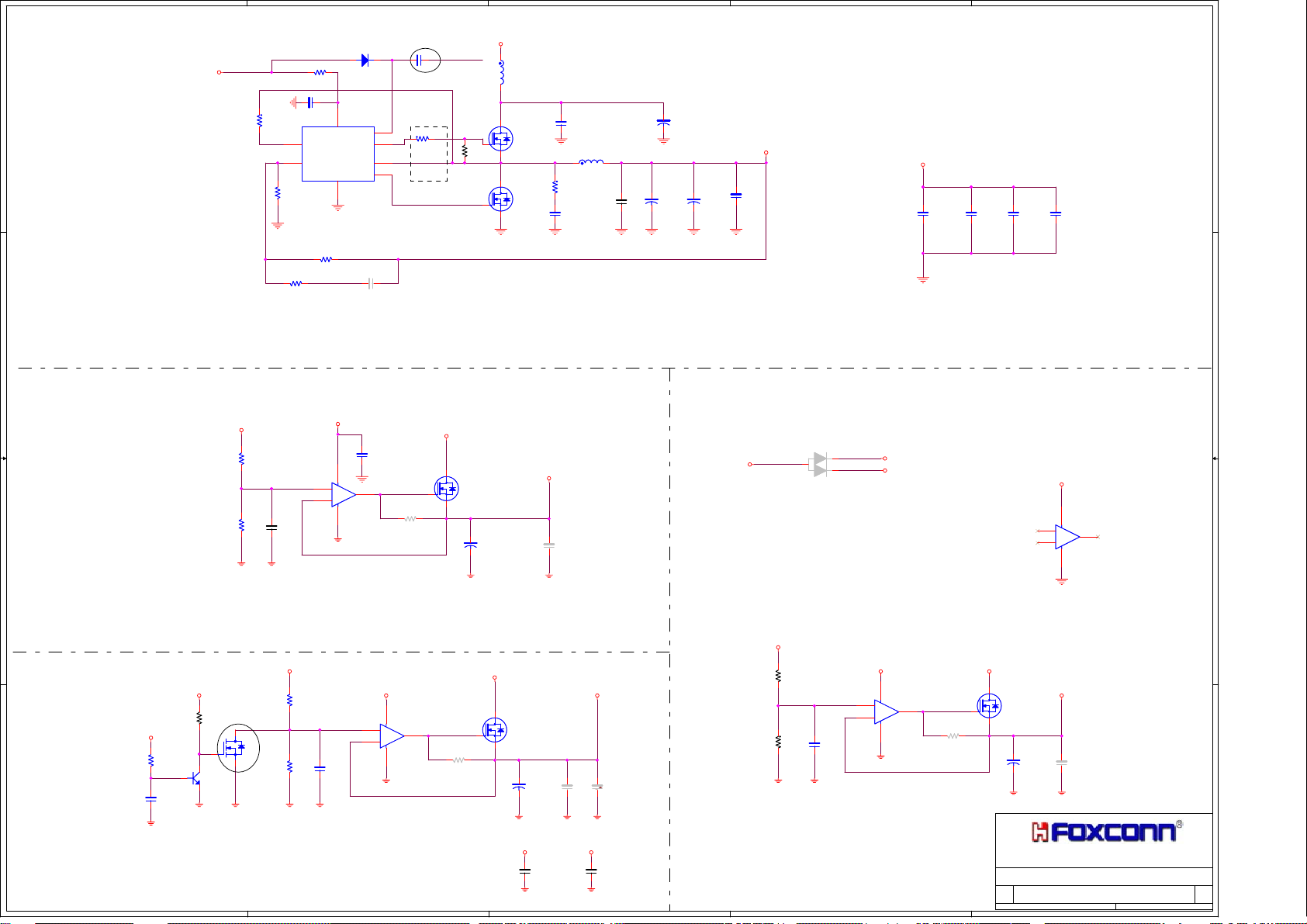

Page 2

亞美商匯

5

4

3

2

1

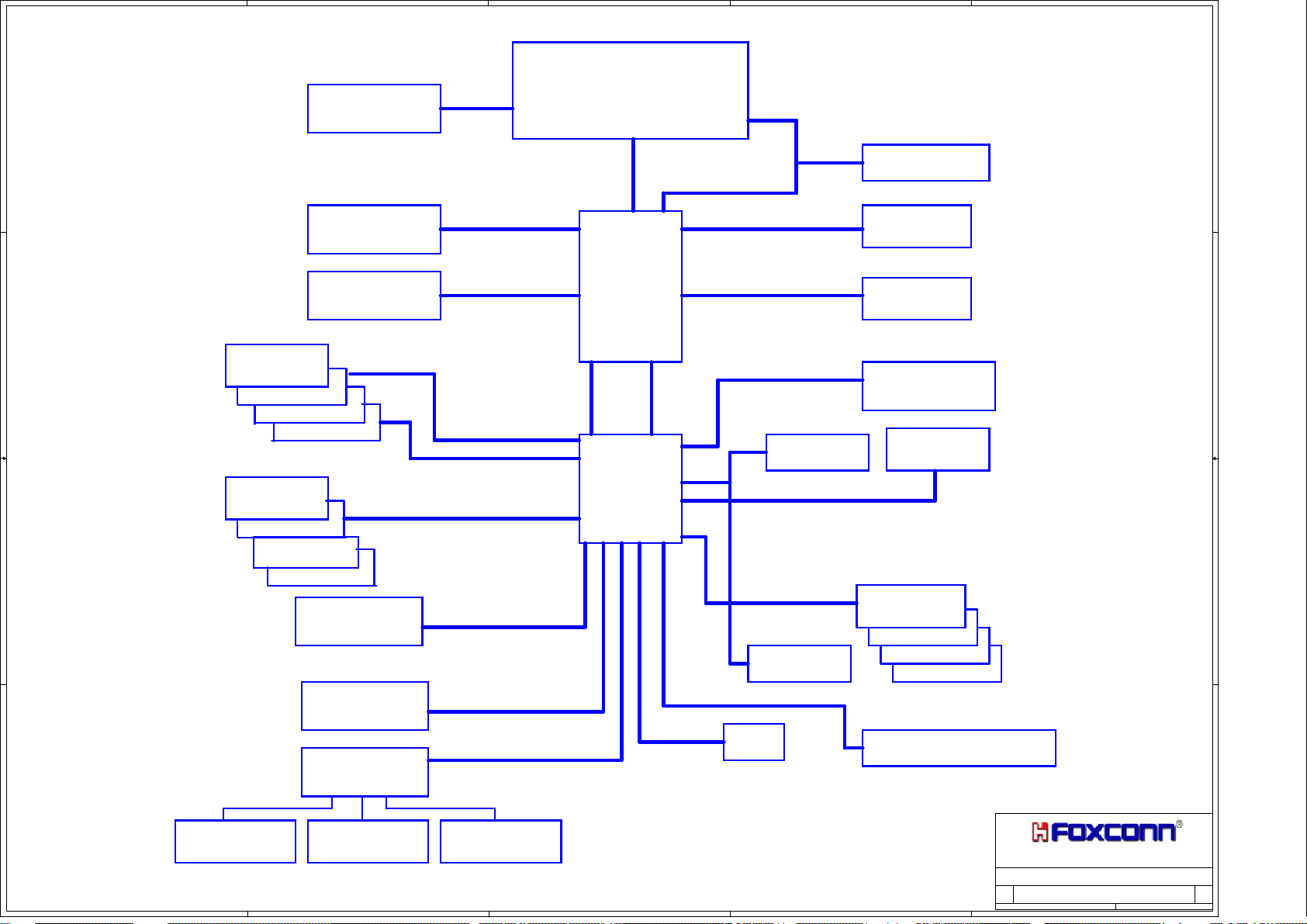

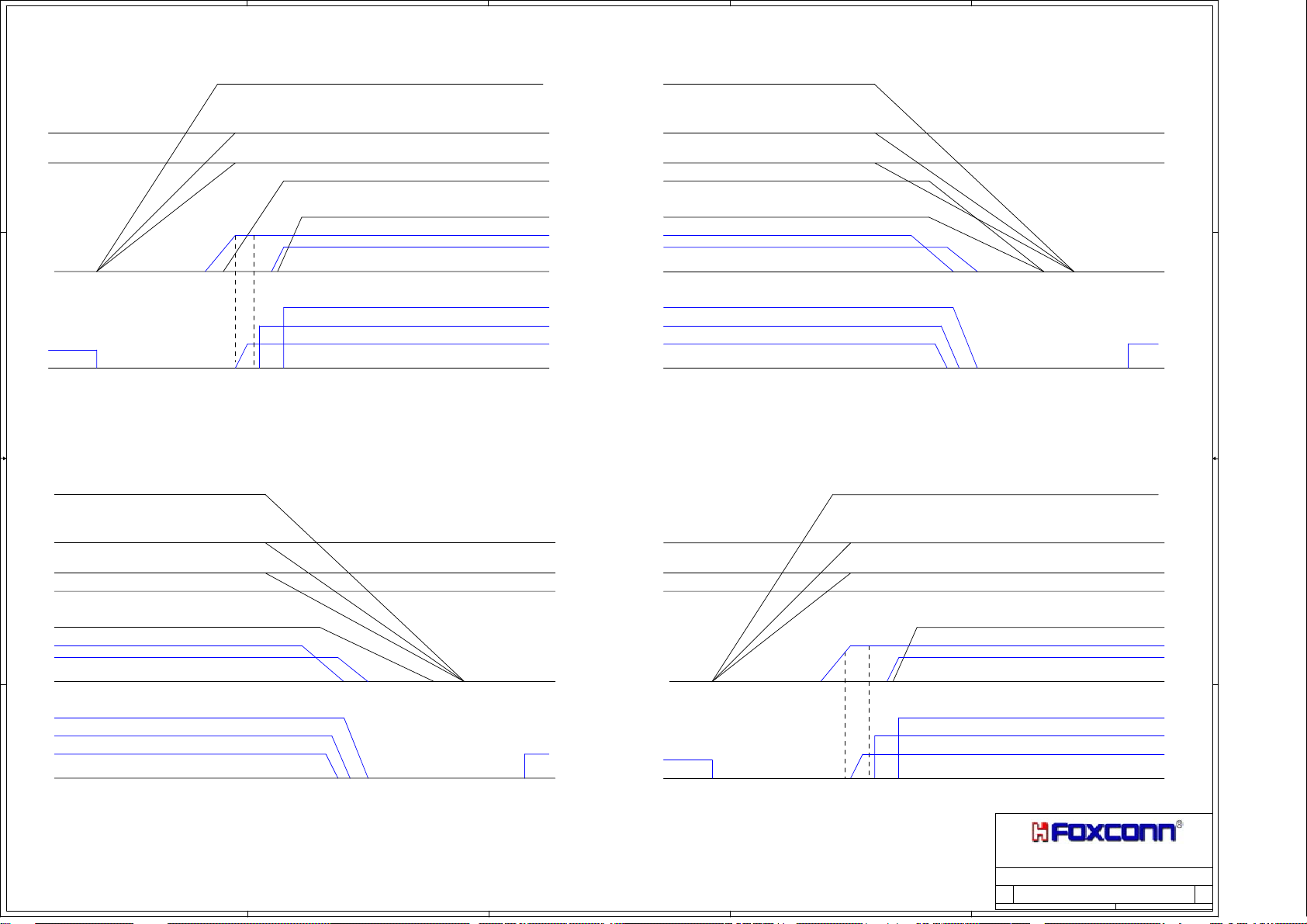

Yorkfield

Wolfdale

VRD 11.1

D D

3 Phase PWM

LGA775 Processor

Socket T

800/1066/1333/1600(oc) FSB

PCI Express x 16

External Graphics

Card

VGA Connector

PCI Express x16 Port

GMCH

DDR2 667/800/1066

DDR2 667/800/1066

Eaglelake

C C

B B

Back Panel

USB2.0 Port 7

USB2.0 Port 8

USB2.0 Port 5

USB2.0 Port 6

Header

USB2.0 Port 1

USB2.0 Port 2

USB2.0 Port 3

USB2.0 Port 4

IDE

4 Lanes

Direct Media Interface (DMI)

Controller Link

ICH7

LPC I/F

PCIe port

SPI Flash

SPI Flash

(BIOS)

CK-505 Clock

Channel A DDR2

DIMM1

Channel B DDR2

DIMM1

LAN

Realtek

PCI Slot 1X2

Serial ATA

SATA Connector 1

AHCI, RAID0,1,5,10

SATA Connector 2

SATA Connector 3

SATA Connector 4

PCI Express x 1

Super I/O

IT8720/FX

A A

IR/CIR

5

Serial & Parallel

4

LPC I/F

Floppy

Drive Connector

TPM

3

TPM

2

HDA Codec

Realtek ALC662/888

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

TOPOLOGY

TOPOLOGY

TOPOLOGY

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

G41M05

G41M05

G41M05

1

234Friday, August 28, 2009

234Friday, August 28, 2009

234Friday, August 28, 2009

AC

AC

AC

of

of

of

Page 3

亞美商匯

5

4

3

2

1

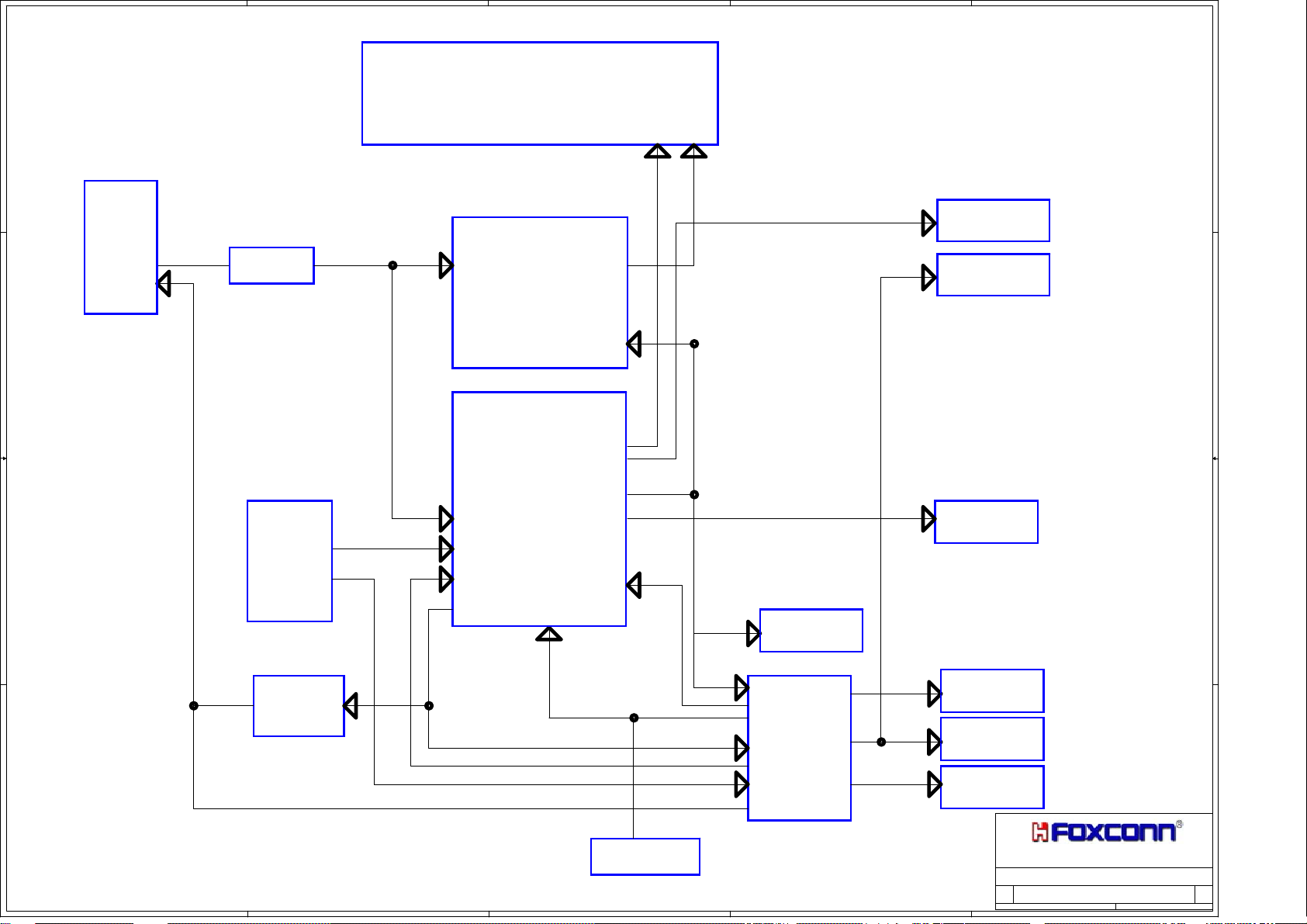

CPU

(Cedar Mill/Presler/Conroe/Allendale)

D D

ATX

Power

PWRGD_PS PWROK

PS_ON#

Translation

Circuitry

PWRGD_3V

LGA775 processor

CPURST#

GMCH

CPURST#

CPU_PWRGD

Vtt_PwrGd

PCI Express x16

CK505

Broadwater

C C

RSTIN#

ICH7

ICH_PWRGD

SLP_M#

Front Panel

FR_RST

B B

SW_ON

PWROK

SYS_RESET#

PWRBTN#

SLP_S3#

CK_PWRGD

PCIRST#

PLTRST#

ACZ_RST#

LAN_RSTSYNC

RCIN#

RSMRST#

RST#

TPM

RST#

Audio

Power on/off

circuit

A A

RSMRST circuit

5

4

3

RST#

KBRST

RSMRST#

Super IO

SLP_S3#

PSOUT

PSIN

PSOUT#

2

RST#

PCI Slot 1

PCIe Slot

RST#

PCIe LAN

RST#

IDE Controller

Title

Title

Title

Reset Map

Reset Map

Reset Map

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

G41M05

G41M05

G41M05

1

334Friday, August 28, 2009

334Friday, August 28, 2009

334Friday, August 28, 2009

AC

AC

AC

of

of

of

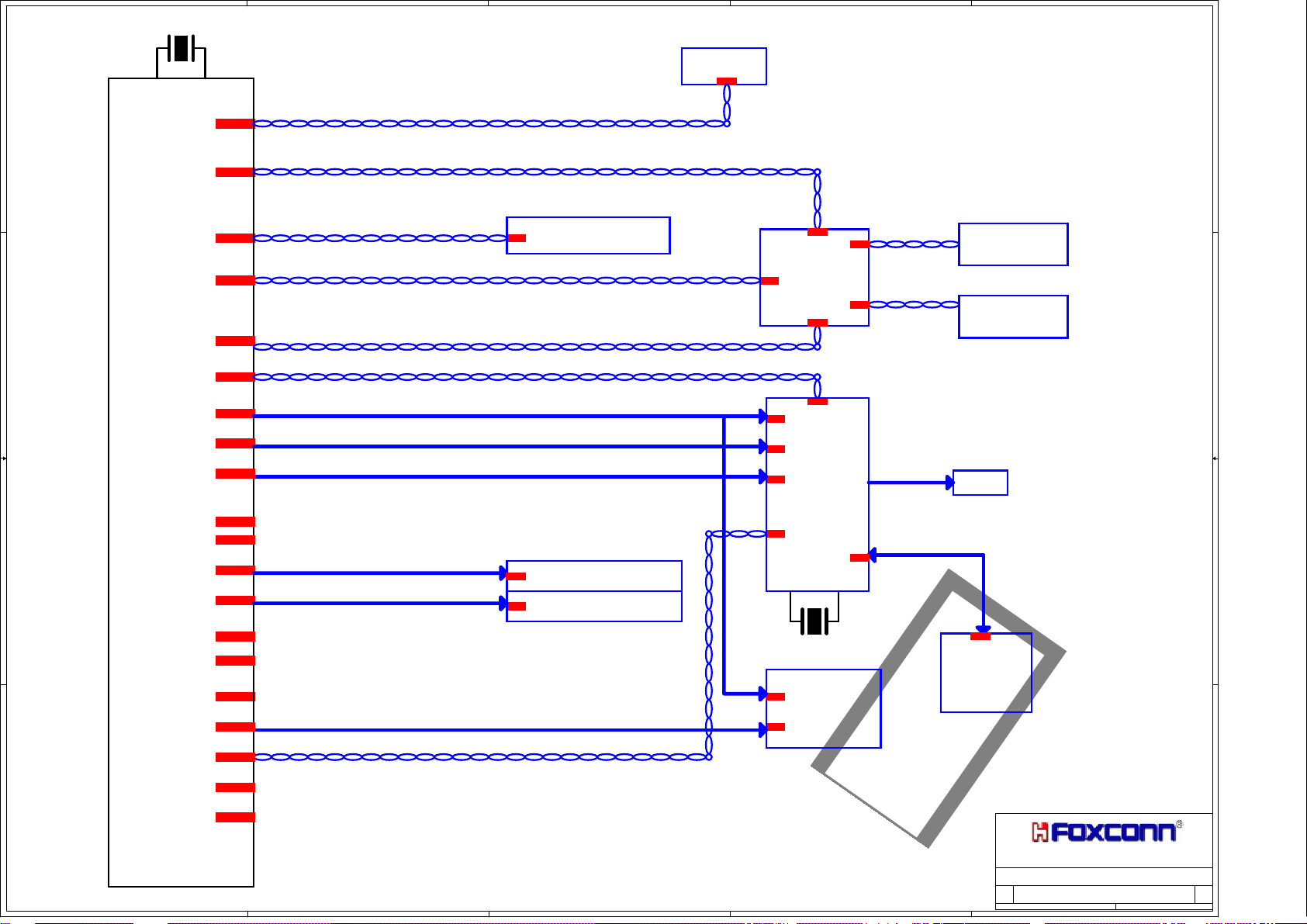

Page 4

亞美商匯

5

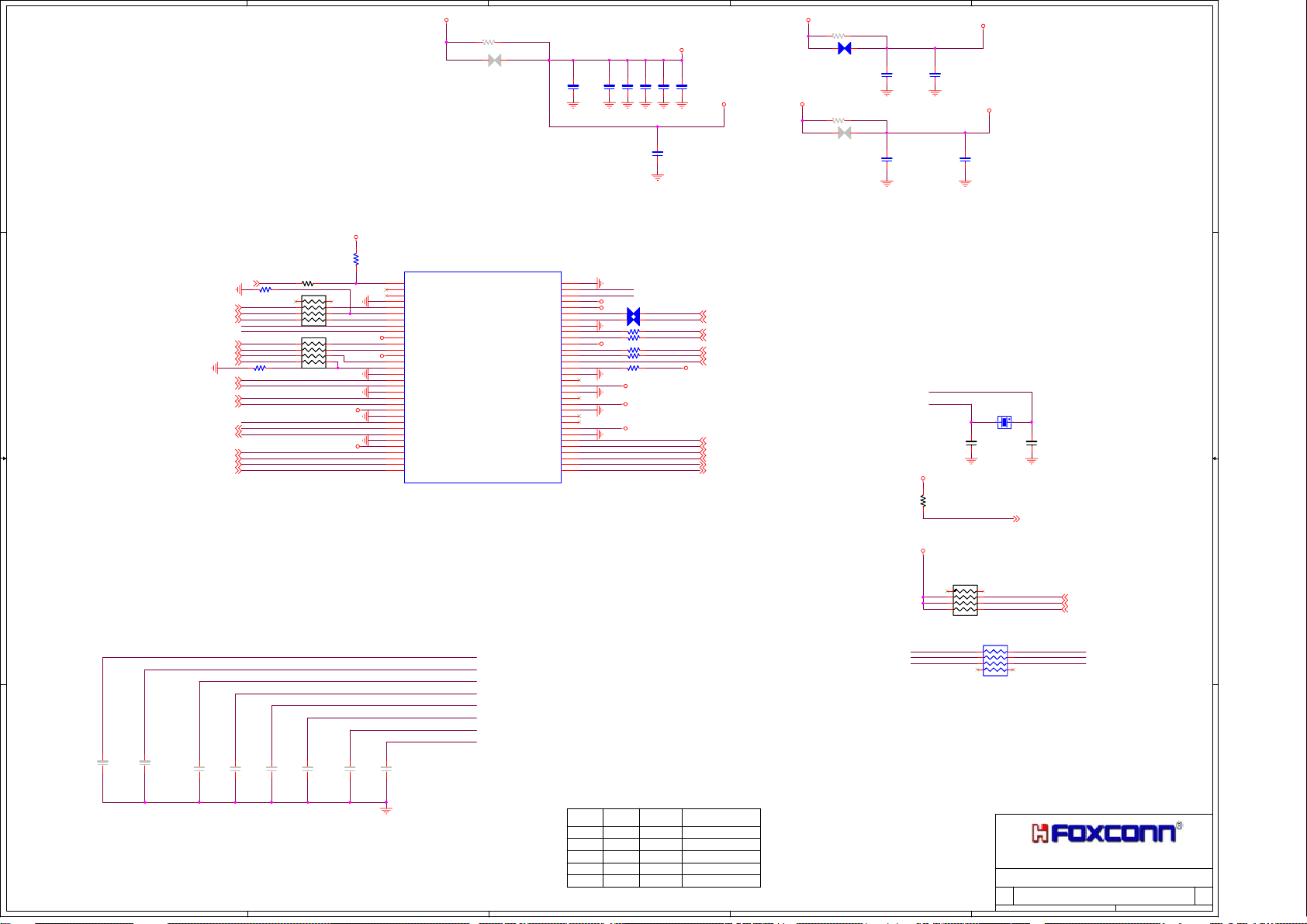

14.318MHz

4

3

2

1

CPU

D D

C C

ICS9LPRS908DGLF

CPU 200/266/333 MHz Diff Pair

MCH 200/266/333 MHz Diff Pair

PCI Express 100 MHz Diff Pair

DOT 96 MHz Diff Pair

PCI Express/DMI 100 MHz Diff Pair

PCI Express/DMI 100 MHz Diff Pair

USB/SIO 48 MHz

ICH 33 MHz

REF 14 MHz

PCI Express x16 Gfx

G41

SPI Clock

Channel A DDR2

DIMM1

Channel B DDR2

DIMM1

SPI

ICH7

Azalia Bit Clock

B B

PCI 33 MHz

TPM 33 MHz

PCI Slot 1

TPM

32.768KHz

HD Audio

SIO 33 MHz

SATA 100 MHz Diff Pair

PCI Express 100 Mhz Diff Pair

A A

5

4

3

Super I/O

2

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Clock Distribution

Clock Distribution

Clock Distribution

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

FOXCONN PCEG

G41M05

G41M05

G41M05

1

434Friday, August 28, 2009

434Friday, August 28, 2009

434Friday, August 28, 2009

of

of

of

AC

AC

AC

Page 5

亞美商匯

5

4

3

2

1

3.3V

ATX P/S

5V

D D

DDR2 Channel A

Vdd (Core)=1.8V

Ivdd(Max)=TBD(per channel)

Vtt (Core)

0.9V

Ivterm(Max)=200mA

(per channel)

DDR2 Channel B

Vdd (Core)=1.8V

Ivdd(Max)=TBD(per channel)

Vtt (Core)

0.9V

Ivterm(Max)=200mA

(per channel)

C C

5VDUAL

Icc(Max)=

10A

Single Phase Switch

5V to 1.8V

Ivdd(Max)=TBD

LDO

1.8V to 0.9V

Ivterm(Max)=1.2A

5VSB

12V

3.3V

VRD 11

Switching

Three Phase

Linear 1.8V

to 1.2V

6A

GMCH 1.25 V

21.34A

Switching

Proceessor

Vccp (CPU Vcore)

Voltage=1.15~1.5V

Icc(Max)=125A

3-Phases Swithing

1.2V FSB

Vtt=5.3A

Broadwater GMCH

FSB_Vtt

1.2V FSB Vtt

Icc(Max)=1.3A

1.8V VCCSM

1.8V VCC_SMCLK

Vcore (Core Logic)

1.25V

Icc(Max)=18.8A(Integrated)

*1.25V (DMI&PCIe)

VCCA_EXP 2.5A

1.25V

VCC_CL 3.8A

3.3V VCCA_DAC 70mA

3.3V VCC3_3 15.8mA

Super I/O

3.3V

Icc(Max)=50mA

3.3SBV

Icc(Max)=50mA(S0)

3.3SBV

Icc(Max)=38mA(S3)

USB2.0 10 Ports

+5V DUAL=5A(S0, S1)

+5V DUAL=20mA(S3)

PS2

+5V DUAL=345mA(S0, S1)

+5V DUAL=2mA(S3)

FWH

3.3V=107mA(S0, S1)

PCI Express X16

slot (1)

+12V=5.5A

3.3VSB

Icc(Max)=0.375A(wake)

Icc(Max)=0.02A(no wake)

+3.3V=3A

PCI Express X1

5V

5VSB

5VDUAL

Icc(Max)=

4.345A(S0,S1)

22mA(S3)

12V

Per slot (1)

HDA Codec

Vcc

5V

Icc(Max)=200mA

Vcc

3.3V

Icc(Max)=40mA

B B

LDO

12V

to 5V

5VSB

3.3V

Linear 1.25V

to 1.05V

V_1P05V_ICH

2A

Linear 1.8V

to 1.5V

V_1P5V_ICH

2.2A

RTC

Battery

5V_STBY to 3.3SB

1.5A

ICH7

1.25V VCCDMI 40mA

1.2V VCC_CPU_IO 14mA

1.05V (Core) VCC1_05

1.17A

1.5V (USB &SATA) VCC1_5A

1.12A

1.5V (PCIe)VCC1_5B

0.77A

1.5V VCCGLAN1_5

74mA

RTC=5uA

3.3V VccCL3_3 12mA

3.3V VccSUS3_3 141mA

3.3V VccLAN (10/100) 12mA

3.3V VccSUSHDA 4mA

3.3V VCC3_3 310mA

3.3V VccGLAN3_3 1mA

3.3V VccHDA 4mA

5V

+12V=0.5A

3.3VSB

Icc(Max)=0.375A(wake)

Icc(Max)=0.02A(no wake)

+3.3V=3A

PCI Per Slot (X2)

-12V

Icc(Max)=0.1A

5V

Icc(Max)=5A

3.3V

Icc(Max)=7.6A

12V

Icc(Max)=0.5A

3.3VSB

Icc(Max)=0.375A(wake)

Icc(Max)=0.02A(no wake)

-12V

Nineveh GbE Lan

A A

3.3V STBY

IO LED 15.5nA

1.8V ANALOG 418.2mA

1.0V Internal 1.8

to 1.0 VR core

277.2mA

5

BJT

CK505

Vdd (Core)

3.3V

Ivdd(Max)=250mA

4

3

2

Title

Title

Title

Power Delivery Map

Power Delivery Map

Power Delivery Map

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

G41M05

G41M05

G41M05

1

534Friday, August 28, 2009

534Friday, August 28, 2009

534Friday, August 28, 2009

AC

AC

AC

of

of

of

Page 6

亞美商匯

5

4

3

2

1

S5->S0

D D

+5V_DUAL

+3D3V_DUAL

1ms to 10ms

C C

PS_ONJ

S0->S3

+12V_SYS

+12V_SYS

+5V_SYS

+3D3V_SYS

+1D8V_STR

VTT_DDR

VTT_VR

Vcc

Vcc_PWRGD

VRM_OUTEN

VIDPWRGD

S0->S5

+12V_SYS

+5V_SYS

+3D3V_SYS

+1D8V_STR

VTT_DDR

VTT_VR

Vcc

Vcc_PWRGD

VRM_OUTEN

VIDPWRGD

S3->S0

+5V_DUAL

+3D3V_DUAL

PS_ONJ

+12V_SYS

+5V_SYS

B B

A A

+3D3V_SYS

VTT_DDR

VTT_VR

Vcc

Vcc_PWRGD

VRM_OUTEN

VIDPWRGD

5

4

+5V_DUAL

+3D3V_DUAL

PS_ONJ

+5V_DUAL

+3D3V_DUAL

+1D8V_STR+1D8V_STR+1D8V_STR +1D8V_STR

1ms to 10ms

PS_ONJ

Title

Title

Title

Power Sequence

Power Sequence

Power Sequence

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

3

2

Date: Sheet

G41M05

G41M05

G41M05

+5V_SYS

+3D3V_SYS

VTT_DDR

VTT_VR

Vcc

Vcc_PWRGD

VRM_OUTEN

VIDPWRGD

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

634Friday, August 28, 2009

634Friday, August 28, 2009

1

634Friday, August 28, 2009

AC

AC

AC

of

of

of

Page 7

亞美商匯

5

D D

4

3D3V_SYS

FB17 0

FB17 0

+/-5%

+/-5%

CP3

CP3

Dummy

Dummy

Dummy

Dummy

X_COPPER

X_COPPER

3

3D3V_SYS

3D3V_CLK

C1184.7uF

12

*

*

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

C1620.1uF

C1620.1uF

12

12

*

*

*

*

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

3D3V_CLK_48M

3D3V_CLK

C1450.1uF

C1450.1uF

C1184.7uF

C1500.1uF

C1500.1uF

C1230.1uF

C1230.1uF

C1200.1uF

C1200.1uF

12

12

12

*

*

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

C1480.1uF

C1480.1uF

12

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

3D3V_CLK_48M

16V, X7R, +/-10%

16V, X7R, +/-10%

3D3V_SYS

FB16 0

FB16 0

+/-5%

+/-5%

CP2

CP2

FB18 0

FB18 0

+/-5%

+/-5%

CP7

CP7

Dummy

Dummy

Dummy

Dummy

2

Dummy

Dummy

X_COPPER

X_COPPER

X_COPPER

X_COPPER

C1144.7uF

C1144.7uF

12

*

*

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

3D3V_CLK_REF

C157

C157

12

4.7uF

4.7uF

*

*

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

3D3V_CLK_SATA

C1190.1uF

C1190.1uF

12

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

3D3V_CLK_SATA

C1330.1uF

C1330.1uF

12

*

*

3D3V_CLK_REF

16V, X7R, +/-10%

16V, X7R, +/-10%

1

CK_14M_ICH22

CK_33M_PCI236

CK_33M_SIO30

CK_33M_PCI136

C C

B B

50V, NPO, +/-5%

50V, NPO, +/-5%

C122

C122

C134

C134

10pF

10pF

10pF

10pF

*

*

*

*

A A

Dummy

Dummy

Dummy

Dummy

5

CK_33M_TPM30

CK_33M_ICH24

CK_48M_ICH22

CK_48M_SIO30

CK_96M_P_GMCH14

CK_96M_N_GMCH14

CK_SATA_100M_P_ICH23

CK_SATA_100M_N_ICH23

CK_PE_100M_P_LAN28

CK_PE_100M_N_LAN28

CK_PE_100M_P_16PORT20

CK_PE_100M_N_16PORT20

DPL_REFSSCLKIN_P14

DPL_REFSSCLKIN_N14

50V, NPO, +/-5%

50V, NPO, +/-5%

C149

C149

10pF

10pF

*

*

Dummy

Dummy

*

CK_33M_PCI2

CK_33M_SIO

CK_33M_PCI1

ICS_FSBSEL2

ICS_FSBSEL1

CK_33M_TPM

CK_33M_ICH

CK_48M_ICH

CK_48M_SIO

R118 4.7K +/-5%

R118 4.7K +/-5%

*

*

96M_P_GMCH

96M_N_GMCH

SATA_100M_P_ICH

SATA_100M_N_ICH

VRMPWRGD

PE_100M_P_16PORT

PE_100M_N_16PORT

50V, NPO, +/-5%

50V, NPO, +/-5%

C146

C146

C125

C125

22pF

22pF

10pF

*

*

50V, NPO, +/-5%

50V, NPO, +/-5%

10pF

Dummy

Dummy

*

*

Dummy

Dummy

*

*

*

*

*

R1214.7K +/-5%*R1214.7K +/-5%

1

3

5

7 8

1

3

5

7 8

3D3V_CLK_SATA

50V, NPO, +/-5%

50V, NPO, +/-5%

C132

C132

10pF

10pF

*

*

Dummy

Dummy

R11133+/-5%*R11133+/-5%

RN12

RN12

2

33

33

4

+/-5%

+/-5%

6

RN47

RN47

2

33

33

4

+/-5%

+/-5%

6

3D3V_CLK

3D3V_CLK

3D3V_CLK

3D3V_CLK_48M

ICS_FSBSEL0

50V, NPO, +/-5%

50V, NPO, +/-5%

*

*

R120

R120

*

*

4.7K

4.7K

+/-5%

+/-5%

C127

C127

10pF

10pF

Dummy

Dummy

50V, NPO, +/-5%

50V, NPO, +/-5%

*

*

4

U37

U37

1

*REF0/GSEL

2

**DOC_0

3

**DOC_1

4

GND4

5

PCICLK0_2X

6

**SEL_STOP/PCICLK1_2X

7

PCICLK2_2X

8

FSLC/PCICLK3_2X

9

FSLB/PCICLK4_2X

10

VDDPCI

11

PCICLK5_2X

12

PCICLK6_2X

13

VDD48

14

FSLA/USB_48

15

*SEL24_48#/24_48Mhz

16

GND16

17

DOT96T_LR/PCIeT_LR0

18

DOT96C_LR/PCIeC_LR0

19

GND19

20

SATACLKT_LR

21

SATACLKC_LR

22

VDDSATA

23

GND23

24

Vtt_PwrGd#/WOL_STOP#

25

PCIeT_LR0

26

PCIeC_LR0

27

GND27

28

VDD

29

PCIeT_LR1

30

PCIeC_LR1

31

PCIeT_LR2

32

PCIeC_LR2

CK_33M_PCI1

CK_33M_PCI2

CK_48M_SIO

CK_48M_ICH

CK_33M_SIO

CK_33M_ICH

CK_14M_ICH

CK_33M_TPM

50V, NPO, +/-5%

50V, NPO, +/-5%

C126

C126

10pF

10pF

Dummy

Dummy

RESET_IN#/RESET#

ICS9LPRS916

ICS9LPRS916

PCIeT_LR6/CPU_STOP#*

PCIeC_LR6/CPU_STOP#*

ICS9LPRS916JGLF-T

ICS9LPRS916JGLF-T

GND64

VDDREF

SDATA

SCLK

GND57

CPUT_L0***

CPUC_L0***

VDDCPU

CPUT_L1F***

CPUC_L1F***

RLATCH**

GNDA

24.576Mhz

VDDA

GND46

25Mhz

GND43

GND39

PCIeT_LR5

PCIeC_LR5

PCIeT_LR4

PCIeC_LR4

PCIeT_LR3

PCIeC_LR3

64

63

X1

62

X2

61

60

VDD

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

VDD

43

42

41

40

VDD

39

38

37

36

35

34

33

X1

X2

3D3V_CLK_REF

3D3V_CLK

CP10 X_COPPERCP10 X_COPPER

CP11 X_COPPERCP11 X_COPPER

R731 33 Ohm +/-1%

R731 33 Ohm +/-1%

*

*

R732 33 Ohm +/-1%

R732 33 Ohm +/-1%

*

*

3D3V_CLK

R733 33 Ohm +/-1%

R733 33 Ohm +/-1%

*

*

R734 33 Ohm +/-1%

R734 33 Ohm +/-1%

*

*

R112 4.7K +/-5%

R112 4.7K +/-5%

*

*

3D3V_CLK

3D3V_CLK

3D3V_CLK

PE_100M_P_GMCH

PE_100M_N_GMCH

PE_100M_P_ICH

PE_100M_N_ICH

BSEL TABLE

00

0

0

FS_AFS_BFS_C

1

1

0

0

0

1 1 0 400MHz(1600)

1 1 0 400MHz(1600)

3

SMB_DATA_MAIN 18,19,20,22,27,31,36

SMB_CLK_MAIN 18,19,20,22,27,31,36

CK_200M_P_CPU 12

CK_200M_N_CPU 12

CK_200M_P_GMCH 14

CK_200M_N_GMCH 14

ICH_SYS_RSTJ 8,12,22

3D3V_CLK

CK_PE_100M_P_GMCH 14

CK_PE_100M_N_GMCH 14

CK_PE_100M_P_ICH 22

CK_PE_100M_N_ICH 22

CK_PE_100M_P_1PORT 27

CK_PE_100M_N_1PORT 27

FSB Frequency

133MHz(533)

200MHz(800)

266MHz(1066)

333MHz(1333)100

X1

X2

C117

C117

27pF

27pF

+/-5%

+/-5%

3D3V_CLK

R127

R127

*

*

8.2K

8.2K

+/-5%

+/-5%

FSB_VTT

RN15

RN15

*

*

470

470

+/-5%

+/-5%

ICS_FSBSEL0

ICS_FSBSEL1

ICS_FSBSEL2

2

X3

X3

12

C116

C116

XTAL-14.318MHz

XTAL-14.318MHz

27pF

27pF

*

*

+/-5%

+/-5%

VRMPWRGD 9,22

FSBSEL0

FSBSEL2

FSBSEL1

RN14

RN14

5786

3

4

*

*

1

2

2.2K Ohm

2.2K Ohm

+/-5%

+/-5%

Title

Title

Title

CLOCKGEN

CLOCKGEN

CLOCKGEN

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet

Date: Sheet

FSBSEL0 12,14

FSBSEL2 12,14

FSBSEL1 12,14

FSBSEL0

FSBSEL1

FSBSEL2

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

G41M05

G41M05

G41M05

1

1

3

5

7 8

*

*

VRMPWRGD

2

4

6

AC

AC

734Friday, August 28, 2009

734Friday, August 28, 2009

734Friday, August 28, 2009

AC

of

of

Page 8

亞美商匯

5

4

3

2

1

3D3V_SYS

5V_SB

R375

R375

*

*

4.7K

4.7K

+/-5%

D D

PS_ONJ30

+/-5%

C466

C466

0.1uF

0.1uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

5V_SYS

C C

HDD_LEDJ23

ICH_SYS_RSTJ7,12,22

B B

HDD_LEDJ

*

*

3D3V_SB

R391

R391

330

330

+-5%

+-5%

C490

C490

220pF

220pF

50V, NPO, +/-5%

50V, NPO, +/-5%

Dummy

Dummy

R393

R393

10K

10K

*

*

+/-5%

+/-5%

C492

C492

220pF

220pF

*

*

50V, NPO, +/-5%

50V, NPO, +/-5%

Dummy

Dummy

FP1

FP1

1 2

3

5

7 8

9

Header_2X5_K10

Header_2X5_K10

Front Panel Switch/LED

HD_LED+ 1 2 Power

HD_LED- 3 4 Power LED(Green)

GND 5 6 Power button

Reset button 7 8 Power

NC 9 10 Key

X

X

3D3V_SYS 3D3V_SYS-12V_SYS 12V_SYS

4

6

5V_SYS

13

14

15

16

17

18

19

20

21

22

23

24

+3.3V3

-12V

GND4

PSON

GND5

GND6

GND7

RSVD

+5V3

+5V4

+5V5

GND8

5V_SYS

*

*

+3.3V1

+3.3V2

PWR0K

+5V_AUX

+12V_1

+12V_2

+3.3V4

Header_2x12

Header_2x12

R390

R390

330

330

+-5%

+-5%

C487

C487

220pF

220pF

Dummy

Dummy

MMBT3904-7-F

MMBT3904-7-F

PWR1

PWR1

GND1

+5V1

GND2

+5V2

GND3

5V_SB

*

*

*

*

1

2

3

4

5

6

7

8

9

10

11

12

R378

R378

4.7K

4.7K

+/-5%

+/-5%

C471

C471

220pF

220pF

Dummy

Dummy

Q49

Q49

5V_SYS

PBTNJ_SIO

B

E C

R388 1K

R388 1K

5V_SB

PBTNJ_SIO 30

3D3V_SYS

*

*

*

*

+/-1%

+/-1%

Change to 5% or not

R387

R387

10K

10K

+/-5%

+/-5%

5V_SYS

*

*

*

*

R374

R374

4.7K

4.7K

+/-5%

+/-5%

PWRG_ATX

C463

C463

0.1uF

0.1uF

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

Dummy

Dummy

PWR_LED 30

3D3V_SYS 5V_SYS -12V_SYS 12V_SYS

C476

C476

0.1uF

0.1uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

PWRG_ATX 11,30

*

*

Dummy

Dummy

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

C481

C481

0.1uF

0.1uF

C97

C97

0.1uF

0.1uF

3D3V_SYS

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

5V_SYS

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

5V_SB

C332

C332

0.1uF

0.1uF

*

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

C452

C452

0.1uF

0.1uF

C350

C350

0.1uF

0.1uF

*

place at power connecter

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

3D3V_SYS 3D3V_SYS

C454

C454

10nF

10nF

*

*

Dummy

Dummy

25V, X7R, +/-10%

25V, X7R, +/-10%

5V_SYS 5V_SYS

C462

C462

0.1uF

0.1uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

C464

C464

0.1uF

0.1uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

25V, X7R, +/-10%

25V, X7R, +/-10%

1 2

C465

C465

0.1uF

0.1uF

C347

C347

0.1uF

0.1uF

*

*

C488

C488

0.1uF

0.1uF

12V_SYS

1D1V_MCH

*

*

25V, X7R, +/-10%

25V, X7R, +/-10%

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

25V, X7R, +/-10%

25V, X7R, +/-10%

12

*

*

Dummy

Dummy

C455

C455

12

0.1uF

0.1uF

C240

C240

0.1uF

0.1uF

C473

C473

0.1uF

0.1uF

SPEAKER HEADER

SPEAKER

SPEAKER

1

C472

C472

0.1uF

0.1uF

+

-

3

1

3

3

4

4

Header_1X4_K2

Header_1X4_K2

@SPEAKER

@SPEAKER

BUZ

BUZ

BUZZER

BUZZER

Buzzer

Buzzer

@Buzzer

@Buzzer

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Power/MISC Connectors

Power/MISC Connectors

Power/MISC Connectors

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

G41M05

G41M05

G41M05

834Friday, August 28, 2009

834Friday, August 28, 2009

834Friday, August 28, 2009

of

of

1

of

ACustom

ACustom

ACustom

5V_SYS

5V_SYS

R358

R358

*

*

4.7K

4.7K

+/-5%

+/-5%

Q47

Q47

SPKR22

SIO_BEEP30

A A

5

1

2

BAT54C

BAT54C

4

3

RN45

RN45

*

*

1

3

5

7 8

100 Ohm

100 Ohm

+/-5%

+/-5%

R367 2.2K

R367 2.2K

*

*

+/-5%

+/-5%

2

4

6

Q46

Q46

B

MMBT3904-7-F

MMBT3904-7-F

E C

*

*

25V, X7R, +/-10%

25V, X7R, +/-10%

12

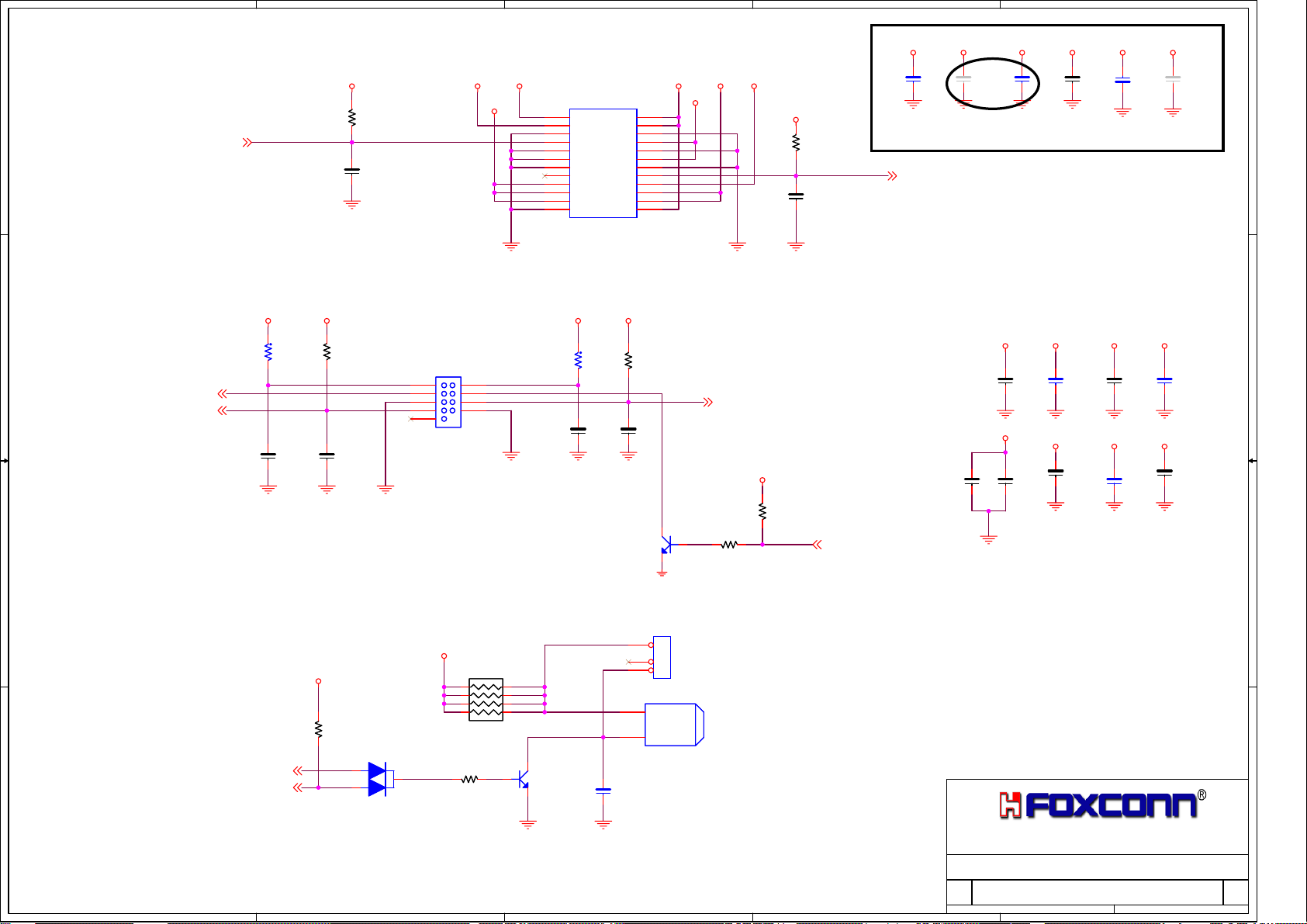

Page 9

亞美商匯

5

4

3

2

1

*

*

COMP

*

*

PR30

PR30

910 Ohm

910 Ohm

+/-1%

+/-1%

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

PC4

PC4

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VID7

COMP

VFB

PC23

PC23

*

*

22pF

22pF

50V, NPO, +/-5%

50V, NPO, +/-5%

50V, X7R, +/-10%

50V, X7R, +/-10%

*

*

VFB

5V_SYS 12V_VRM

PR4

PR4

2.2

2.2

PC5

PC5

1uF

1uF

*

*

+/-10%

+/-10%

c0603h9

c0603h9

U12

U12

34

VR_RDY

33

EN

3

VID0

4

VID1

5

VID2

6

VID3

7

VID4

8

VID5

9

VID6

10

VID7

2

PSI

16

DIFFOUT

17

COMP

18

VFB

19

DROOP

20

VDFB

21

CSSUM

22

DAC

14

VSP

15

VSN

ILIM

12

12V_VRM

*

*

*

*

PR72

PR72

10K

10K

+/-1%

+/-1%

PR62

PR62

1K

1K

+/-1%

+/-1%

11

ROSC

24

VCC

*

*

*

*

PR7

PR7

1

1

40

VCCP

DRVON

12VMON

PAD_GND

NCP5395TMNR2G

NCP5395TMNR2G

23

49

PC183

PC183

10nF

10nF

25V, X7R, +/-10%

25V, X7R, +/-10%

change to 0 ohm

12V_VCCP

PC6

PC6

10uF

10uF

*

*

+/-10%

+/-10%

c1206h18

c1206h18

37

BST1

38

TG1

39

SWN1

36

BG1

32

CS1N

31

CS1P

44

BST2

43

TG2

42

SWN2

41

BG2

30

CS2N

29

CS2P

48

BST3

47

TG3

46

SWN3

1

BG3

28

CS3N

27

CS3P

35

G4

45

26

CS4N

25

CS4P

>300us FILTER

13

IMON

BOTTOM PAD

CONNECT TO

GND Through

8 VIAs

PD1

PD1

BAT54HT1G

BAT54HT1G

BST1

TG1

SWN1

BG1

CS1N

PR10 0

PR10 0

CS1

BST2

TG2

SWN2

BG2

CS2N

PR23 0

PR23 0

CS2

BST3

TG3

SWN3

BG3

CS3N

PR32 0

PR32 0

CS3

G4

PR41

PR41

Dummy

Dummy

330Ohm

330Ohm

+/-1%

+/-1%

PC48

PC48

1uF

1uF

*

*

+/-10%

+/-10%

Dummy

Dummy

c0603h9

c0603h9

CA

PR63 2.2

PR63 2.2

*

*

PR15

PR15

2.2

2.2

r0805h6

r0805h6

*

*

PR28

PR28

2.2

2.2

r0805h6

r0805h6

*

*

*

*

*

*

*

*

*

*

*

*

r0805h6

r0805h6

PR13

PR13

2.49K

2.49K

+/-1%

+/-1%

PC13

PC13

220nF

220nF

+/-10%

+/-10%

c0603h9

c0603h9

PR25

PR25

2.49K

2.49K

+/-1%

+/-1%

PC24

PC24

220nF

220nF

+/-10%

+/-10%

c0603h9

c0603h9

PR35

PR35

2.49K

2.49K

+/-1%

+/-1%

PR61 0

PR61 0

PC8

PC8

220nF

220nF

*

*

+/-10%

+/-10%

c0603h9

c0603h9

Dummy

Dummy

PR11 100KOhm

PR11 100KOhm

*

*

PC12 220nF

PC12 220nF

*

*

PD2

PD2

C A

BAT54HT1G

BAT54HT1G

Dummy

Dummy

PR24 100KOhm

PR24 100KOhm

*

*

PC20 220nF

PC20 220nF

*

*

PD3

PD3

C A

BAT54HT1G

BAT54HT1G

Dummy

Dummy

PR33 100KOhm

PR33 100KOhm

*

*

PC36 220nF

PC36 220nF

*

*

*

*

12V_VRM

PWR2

PWR2

2

4

1

3

Header_2X2

Header_2X2

+/-1%

+/-1%

+/-10%

+/-10%

c0603h9

c0603h9

+/-1%

+/-1%

+/-10%

+/-10%

c0603h9

c0603h9

+/-1%

+/-1%

+/-10%

+/-10%

c0603h9

c0603h9

C103

C103

100nF

100nF

*

*

25V, X5R,+/-10%

25V, X5R,+/-10%

Dummy

Dummy

12V_VCCP

12V_VCCP

12

*

*

L13

L13

Choke 1uH

Choke 1uH

*

*

R85 2.2

R85 2.2

+/-5%

+/-5%

R87

R87

10KOhm

10KOhm

+/-1%

+/-1%

R84 2.2

R84 2.2

R86

R86

+/-5%

+/-5%

10KOhm

10KOhm

+/-1%

+/-1%

R131 2.2

R131 2.2

R132

R132

+/-5%

+/-5%

10KOhm

10KOhm

+/-1%

+/-1%

Input LC circuit

C124

C124

C92

C92

C105

C105

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

*

*

*

*

*

*

Dummy

Dummy

12V_VIN

12

C89

C89

*

*

4.7uF

4.7uF

DS

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

Q9

G

AOD452ALQ9AOD452AL

DS

DS

Q12

Q12

Q14

G

AOD472AL

AOD472AL

12

C90

C90

*

*

4.7uF

4.7uF

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

Q10

Q10

AOD452AL

AOD452AL

Q13

Q13

G

AOD472AL

AOD472AL

12

C131

C131

*

*

4.7uF

4.7uF

Q17

Q17

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

AOD452AL

AOD452AL

Q20

Q20

G

AOD472AL

AOD472AL

EC18

EC18

1000uF

1000uF

*

*

+/-20%

+/-20%

DS

DS

Q14

AOD472AL

AOD472AL

Q15

Q15

AOD472AL

AOD472AL

Q21

Q21

AOD472AL

AOD472AL

12V_VIN

*

*

EC16

EC16

1000uF

1000uF

+/-20%

+/-20%

*

*

*

*

*

*

EC21

EC21

1000uF

1000uF

*

*

+/-20%

+/-20%

G

12V_VIN

DS

G

DS

G

12V_VIN

DS

G

DS

G

EC17

EC17

C102

C102

1000uF

1000uF

0.1uF

0.1uF

*

*

+/-20%

+/-20%

300nH@100KHz

300nH@100KHz

R81

R81

2.2

2.2

12

r0805h6

r0805h6

C104

C104

2.2nF

2.2nF

c0603h9

c0603h9

CS1

50V, X7R, +/-10%

50V, X7R, +/-10%

Close to L/S MOS

VCORE OUTPUT

MLCC CAP

300nH@100KHz

300nH@100KHz

PR26

PR26

2.2

2.2

12

r0805h6

r0805h6

PC27

PC27

2.2nF

2.2nF

c0603h9

c0603h9

CS2

50V, X7R, +/-10%

50V, X7R, +/-10%

Close to L/S MOS

300nH@100KHz

300nH@100KHz

PR39

PR39

2.2

2.2

12

r0805h6

r0805h6

PC46

PC46

2.2nF

2.2nF

c0603h9

c0603h9

CS3

50V, X7R, +/-10%

50V, X7R, +/-10%

Close to L/S MOS

PCP1PCP1

PCP3PCP3

PCP5PCP5

VCCP

L14

L14

12

*

*

12

PCP2PCP2

CS1N

L15

L15

12

*

*

12

PCP4PCP4

CS2N

L20

L20

12

*

*

12

PCP6PCP6

CS3N

VCCP

D D

VRMPWRGD7,22

VRM_EN12

VID012

VID112

VID212

VID312

VID412

VID512

VID612

VID712

P_PSI_N13

PR8

PR8

12

12

+/-1%

+/-1%

5V_SYS

C C

B B

Dummy

Dummy

PR17

PR17

100KOhm

100KOhm

+/-1%

+/-1%

VCC_SENSE12

VSS_SENSE12

Fsw= 280kHz

OCP ~170A

PR16

PR16

*

*

1K +/-1%

1K +/-1%

*

*

PR21

PR21

*

*

240KOhm

240KOhm

Dummy

Dummy

+/-1%

+/-1%

Close to PL1

VCCP

*

*

*

*

5V_SYS

PR65

PR65

*

*

9.09KOhm

9.09KOhm

+/-1%

+/-1%

PR54

PR54

*

*

1K

1K

+/-1%

+/-1%

3D3V_SYS

*

*

PR6

PR6

Dummy

Dummy

680

680

PC11

PC11

680pF

680pF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

T

T

PR36

PR36

51 Ohm

51 Ohm

*

*

PR40

PR40

51 Ohm

51 Ohm

B

PC51

PC51

0.1uF

0.1uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

VTT_OUT_RIGHT

Dummy

Dummy

PC7

PC7

*

*

0.1uF

0.1uF

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

PR12 0

PR12 0

*

*

Dummy

Dummy

*

*

PR22 820

PR22 820

*

*

PRT1

PRT1

4.7K

4.7K

r0603h10

r0603h10

PR29 820

PR29 820

PR38

PR38

0

0

Dummy

Dummy

PC136

PC136

*

*

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

PQ12

PQ12

MMBT3904-7-F

MMBT3904-7-F

E C

*

*

PR66

PR66

33KOhm

33KOhm

+/-1%

+/-1%

PR5

PR5

*

*

2KOhm

2KOhm

+/-1%

+/-1%

PR14

PR14

4.12K

4.12K

+/-1%

+/-1%

PC17 22pF

PC17 22pF

*

*

50V, NPO, +/-5%

50V, NPO, +/-5%

PR19

PR19

2.7K

2.7K

*

*

+/-1%

+/-1%

*

*

+/-1%

+/-1%

*

*

+/-1%

+/-1%

*

*

*

*

12

PC52

PC52

*

*

150pF

150pF

50V, NPO, +/-5%

50V, NPO, +/-5%

PC53

PC53

33nF

33nF

*

*

+/-10%

+/-10%

Dummy

Dummy

PC111 0.1uF

PC111 0.1uF

PSI_N_IN

PC14

PC14

1.8nF

1.8nF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

*

*

PR27

PR27

1K

1K

+/-1%

+/-1%

*

*

PR31

PR31

750

750

+/-1%

+/-1%

PC33 10nF

PC33 10nF

Dummy

Dummy

PC39

PC39

10nF

10nF

25V, X7R, +/-10%

25V, X7R, +/-10%

Dummy

Dummy

PC54

PC54

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

PR42

PR42

*

*

20K

20K

+/-1%

+/-1%

PR43

PR43

*

*

10K

10K

+/-1%

+/-1%

PR64

PR64

*

*

51KOhm

51KOhm

+/-1%

+/-1%

VCCP

5V_SYS

Q28

*

*

B

Q28

VCC

5

C318

C318

0.1uF

0.1uF

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

C

4

74V1G66CTR

74V1G66CTR

Q29

Q29

Q27

Q27

E C

IO

OI

GND

B

E C

MMBT3904-7-F

MMBT3904-7-F

1

2

3

R273 1K

R273 1K

*

*

R278 1K

R278 1K

P_PSI_N

PSI_N_IN

5V_SYS

*

*

4

P_PSI_N 13

HCPURSTJ

*

*

TC25

TC25

100uF

100uF

2V,+30/-20%

2V,+30/-20%

Dummy

Dummy

EC28

EC28

EC24

EC24

EC25

EC33

EC33

820uF

820uF

820uF

820uF

*

*

*

*

+/-20%

+/-20%

+/-20%

+/-20%

Dummy

Dummy

EC27

EC27

EC26

EC26

820uF

820uF

820uF

820uF

*

*

*

*

+/-20%

+/-20%

+/-20%

+/-20%

TC26

TC26

100uF

100uF

*

*

2V,+30/-20%

2V,+30/-20%

Dummy

Dummy

EC25

820uF

820uF

820uF

820uF

*

*

*

*

+/-20%

+/-20%

+/-20%

+/-20%

EC34

EC34

820uF

820uF

*

*

+/-20%

+/-20%

12

12

C214

C214

C228

C228

*

*

*

*

22uF

22uF

22uF

22uF

Dummy

Dummy

Dummy

Dummy

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

12

12

C209

C209

C221

C221

*

*

*

*

10uF

10uF

10uF

10uF

+/-10%

+/-10%

12

12

C191

C191

C219

C219

*

*

*

*

10uF

10uF

22uF

22uF

Dummy

Dummy

+/-10%

+/-10%

3

12

12

C216

C216

C226

C226

*

*

*

*

10uF

10uF

10uF

10uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

+/-10%

+/-10%

12

12

C224

C224

C207

C207

*

*

*

*

22uF

22uF

22uF

22uF

Dummy

Dummy

Dummy

Dummy

+/-10%

+/-10%

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

12

12

C194

C194

C231

C231

*

*

*

*

10uF

10uF

10uF

10uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

+/-10%

+/-10%

12

12

C229

C229

C215

C215

*

*

*

*

22uF

22uF

22uF

22uF

Dummy

Dummy

Dummy

Dummy

+/-10%

+/-10%

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

+/-10%

+/-10%

12

*

*

Dummy

Dummy

12

*

*

Dummy

Dummy

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

12

C208

C208

C225

C225

*

*

22uF

22uF

22uF

22uF

Dummy

Dummy

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

12

C220

C220

C195

C195

*

*

22uF

22uF

10uF

10uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

+/-10%

+/-10%

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

VRD11.1-NCP5395

VRD11.1-NCP5395

VRD11.1-NCP5395

G41M05

G41M05

G41M05

1

DCustom

DCustom

DCustom

of

of

of

934Friday, August 28, 2009

934Friday, August 28, 2009

934Friday, August 28, 2009

5V_SYS

*

*

*

*

R279

R279

R275

R275

1K

1K

1K

1K

MMBT3904-7-F

*

*

MMBT3904-7-F

C322

C322

10uF

10uF

5

Q33

Q33

Q30

Q30

B

E C

E C

MMBT3904-7-F

MMBT3904-7-F

B

MMBT3904-7-F

MMBT3904-7-F

A A

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

R277 5.1KOhm+/-1%R277 5.1KOhm+/-1%

HCPURSTJ12,14

Page 10

亞美商匯

5

4

3

2

1

1125V_PHASE

*

*

DS

Q41

Q41

P3055LDG

P3055LDG

*

*

R225

R225

10K

10K

+/-5%

+/-5%

G

G

EC41

EC41

1000uF

1000uF

+/-20%

+/-20%

12V_SYS

*

*

L31

L31

1uH@1KHz

1uH@1KHz

DS

Q25

Q25

AOD452AL

AOD452AL

1125V_PHASE

DS

Q24

Q24

AOD472AL

AOD472AL

close to Q61 Drain

C316

C316

0.1uF

0.1uF

*

*

25V, X7R, +/-10%

25V, X7R, +/-10%

L28

L28

*

*

2.5uH@100KHz

2.5uH@100KHz

R257

R257

2.2

2.2

+/-5%

+/-5%

C308

C308

12

2.2nF

2.2nF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

*

*

Pull FB trace out after Cout

1D5V_CORE

1A

50 mils

C441

C441

0.1uF

0.1uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

Dummy

Dummy

EC37

EC37

270uF

270uF

*

*

16V, +/-20%

16V, +/-20%

Need to change to RUBYCON

16MBZ470MEFC8X11.5

C273

C273

EC35

EC35

1000uF

1000uF

0.1uF

0.1uF

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

*

*

*

*

+/-20%

+/-20%

EC36

EC36

1000uF

1000uF

+/-20%

+/-20%

*

*

FSB_VTT

12

1D1V_MCH

C265

C265

10uF

10uF

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

3

Q36

Q36

Dummy

Dummy

BAT54A

BAT54A

1D1V_MCH

12

C4172.2uF

C4172.2uF

6.3V, Y5V, +80%/-20%

6.3V, Y5V, +80%/-20%

12

C4192.2uF

C4192.2uF

*

*

*

*

6.3V, Y5V, +80%/-20%

6.3V, Y5V, +80%/-20%

12

C2591uF

C2591uF

C2621uF

C2621uF

*

*

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

12V_SYS

411

U18D

U18D

12

+

+

14

13

-

-

LM324DR2G

LM324DR2G

12

*

*

2

1

1D1V_MCH

1D5V_CORE

C342

D13

D13

R285 10

12V_SYS

D D

C C

3D3V_SB

R359

R359

*

*

1.8KOhm

1.8KOhm

+/-1%

+/-1%

@1.5V

R360

R360

*

*

1.5KOhm

1.5KOhm

+/-1%

+/-1%

R285 10

+/-5%

+/-5%

C326 1uF 16V, X7R, +/-10%

C326 1uF 16V, X7R, +/-10%

R291

R291

14.3K

14.3K

+/-1%

+/-1%

Rocset

7

COMP/OCSET

6

FB

APW7120KE-TRL

APW7120KE-TRL

R290

R290

*

*

115 Ohm

115 Ohm

+/-1%

+/-1%

VOUT= 0.8V(1+R638 / R658)

R638,R658 must less than 1k

R286

R286

*

*

220

220

+/-1%

+/-1%

Dummy

Dummy

1D5V_REF

C447

C447

0.1uF

0.1uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

LS4148-F

LS4148-F

*

*

*

*

5

U15

U15

BOOT

VCC

UGATE

PHASE

LGATE

GND

3

R282

R282

47 Ohm

47 Ohm

*

*

+/-1%

+/-1%

C330

C330

18nF

18nF

50V, X7R, +/-10%

50V, X7R, +/-10%

Dummy

Dummy

12V_SYS

12

C449

C449

*

*

0.1uF

0.1uF

25V, X7R, +/-10%

25V, X7R, +/-10%

411

U18A

U18A

3

+

+

1

2

-

-

LM324DR2G

LM324DR2G

C342

1 2

CA

0.1uF

0.1uF

25V, X7R, +/-10%

25V, X7R, +/-10%

1

2

8

4

Near MOSFET

*

*

50 mils

R353

R353

1K

1K

Dummy

Dummy

*

*

+/-5%

+/-5%

Can change to 0402 or not

*

*

R227

R227

2.2

2.2

+/-5%

+/-5%

1D125V FOR CHIP

1D5V_STR

G

B B

Reserved

Reserved

1D5V_SYS

3D3V_SB

5

6

12V_SYS

411

+

+

-

-

U18B

U18B

7

LM324DR2G

LM324DR2G

50 mils

G

R329

R329

1K

1K

Dummy

Dummy

*

*

+/-5%

+/-5%

Can change to 0402 or not

1D5V_STR

DS

Q34

Q34

P3055LDG

P3055LDG

*

*

EC40

EC40

1000uF

1000uF

+/-20%

+/-20%

1D05V_SYS

C460

C460

*

*

10uF

10uF

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

Dummy

Dummy

1A

50 mils

3D3V_SB

R370

R370

*

*

21KOhm

21KOhm

+/-1%

Q38

Q38

2N7002

2N7002

*

*

+/-1%

@1.2V

R369

R369

12KOhm

12KOhm

+/-1%

+/-1%

C451

C451

1uF

1uF

*

*

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

R361

R361

*

*

1K

1K

+/-5%

+/-5%

Q42

Q42

MMBT3904-7-F

MMBT3904-7-F

E C

VREF1D2

1D5V_CORE

R355

R355

*

*

470

470

+/-5%

+/-5%

B

C432

C432

1uF

1uF

*

*

10V, Y5V, +80%/-20%

A A

10V, Y5V, +80%/-20%

12V_SYS

411

U18C

U18C

10

+

+

8

LM324DR2G

LM324DR2G

9

-

-

Can change to 0402 or not

Dummy

Dummy

*

*

1D5V_STR

50 mils

G

R133

R133

1K

1K

+/-5%

+/-5%

DS

Q18

Q18

P3055LDG

P3055LDG

*

*

EC30

EC30

1000uF

1000uF

+/-20%

+/-20%

FSB_VTT3D3V_SB

C153

C153

10uF

10uF

*

*

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

Dummy

Dummy

6.3A

C160

C160

0.1uF

0.1uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

Dummy

Dummy

50 mils

R365

R365

*

*

2.2KOhm

2.2KOhm

+/-1%

+/-1%

R366

R366

1.02KOhm

1.02KOhm

+/-1%

+/-1%

@1.05V

1.8V

C450

C450

0.1uF

0.1uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

1D05V_SYS

FSB_VTT FSB_VTT

C158

C158

0.1uF

FSB_VTT

5

4

0.1uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

C155

C155

0.1uF

0.1uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

3

Title

Title

Title

1D125V 1D5V FSB

1D125V 1D5V FSB

1D125V 1D5V FSB

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

G41M05

G41M05

G41M05

1

10 34Friday, August 28, 2009

10 34Friday, August 28, 2009

10 34Friday, August 28, 2009

AC

AC

AC

of

of

of

Page 11

亞美商匯

5

4

3

2

1

DDR_VTT

5V_SB

R364

R364

*

*

10K

10K

+/-5%

+/-5%

5V_SB 12V_SYS

2N7002DW

2N7002DW

1

S1

S2

2

G1

G2

6

D1

D2

Q48

Q48

1D8V_GPIO1022

1D8V_GPIO1422

D18

D18

1

2

BAT54C

BAT54C

4

5

3

R373

R373

*

*

442 Ohm

442 Ohm

+/-1%

+/-1%

Dummy

Dummy

1D8V_Switch 18V_PHASE

3

R392 10

R392 10

+/-5%

+/-5%

R381

R381

*

*

14.3KOhm

14.3KOhm

+/-1%

+/-1%

Rocset

7

6

R386

R386

*

*

210Ohm

210Ohm

+/-1%

+/-1%

Don't in CIS

VOUT= 0.8V(1+R638 / R658)

R638,R658 must less than 1k

Dummy

Dummy

*

R372

R372

1.02KOhm

1.02KOhm

+/-1%

+/-1%

Dummy

Dummy

*

*

*

C491

C491

1uF

1uF

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

COMP/OCSET

FB

APW7120KE-TRL

APW7120KE-TRL

R385

R385

220 Ohm

220 Ohm

+/-1%

+/-1%

1

2

5

U19

U19

VCC

GND

3

R377

R377

226Ohm

226Ohm

+/-1%

+/-1%

D20

D20

BAT54C

BAT54C

BOOT

UGATE

PHASE

LGATE

C475 18nF

C475 18nF

Dummy

Dummy

*

*

3

1

2

8

4

Near MOSFET

50V, X7R, +/-10%

50V, X7R, +/-10%

C461

C461

1 2

*

*

0.1uF

0.1uF

25V, X7R, +/-10%

25V, X7R, +/-10%

R337

R337

2.2

2.2

+/-5%

+/-5%

5V_DUAL

*

*

L35

L35

1uH@1KHz

1uH@1KHz

close to Q61 Drain

EC43

*

*

Dummy

Dummy

*

*

C445

C445

0.1uF

0.1uF

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

EC43

470uF

470uF

6.3V, +/-20%

6.3V, +/-20%

EC32

EC32

1000uF

1000uF

*

*

+/-20%

+/-20%

DS

Q40

Q40

G

AOD452AL

AOD452AL

R344

R344

*

*

10K

10K

+/-5%

+/-5%

18V_PHASE

DS

Q43

Q43

G

AOD472AL

AOD472AL

12

C446

C446

*

*

0.1uF

0.1uF

25V, X7R, +/-10%

25V, X7R, +/-10%

R362

R362

2.2

2.2

+/-5%

+/-5%

C453

C453

12

2.2nF

2.2nF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

L36

L36

*

*

2.5uH@100KHz

2.5uH@100KHz

Pull FB trace out after Cout

1.8V Voltage

1.8V Power requires

17A maximum current

12

C391

C391

*

*

10uF

10uF

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

EC44

EC44

EC45

EC45

1000uF

1000uF

1000uF

1000uF

*

*

+/-20%

+/-20%

*

*

*

*

+/-20%

+/-20%

1D5V_STR

EC39

EC39

1000uF

1000uF

+/-20%

+/-20%

1D5V_STR

U17

EC52

EC52

1000uF

1000uF

*

*

+/-20%

+/-20%

*

*

*

*

R357

R357

100KOhm

100KOhm

+/-1%

+/-1%

R356

R356

100KOhm

100KOhm

+/-1%

+/-1%

U17

1

VIN

3

REFEN

RT9173

RT9173

C426

C426

0.1uF

0.1uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

VCNTL

VCNTL

VCNTL

VCNTL

VOUT

GND

3D3V_SYS

8

7

6

5

4

2

VTT_DDR

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

EC42

EC42

C411

C411

1000uF

1000uF

0.1uF

0.1uF

*

*

*

*

+/-20%

+/-20%

Need to Check Change to Dummy

D D

SLP_S4J15,22

C C

1D8V_STR

5V_SB

Q44

B B

*

*

A A

EC46

EC46

1000uF

1000uF

+/-20%

+/-20%

Q44

3

Vin

2

Vout

1

ADJ

AZ1084D-ADJTRE1

AZ1084D-ADJTRE1

3D3VADJ

3D3V_DUAL

5

3D3V_SB

Max. output current = 3A

R379

R379

*

*

301

301

+/-1%

+/-1%

EC48

EC48

1000uF

1000uF

*

*

R380

R380

+/-20%

+/-20%

*

*

499

499

+/-1%

+/-1%

Vout=Vref(1+R2/R1)+IadjR2

R1 is Up Resistor.

Iadj=50uA

Vref=1.25V

915 series failure issue

4

D29

1

2

3D3V_SB

D29

3

BAT54C

BAT54C

3

*

*

RN44

RN44

1

3

5

7 8

10K Ohm

10K Ohm

+/-5%

+/-5%

Ring

*

*

RN46

RN46

1

3

5

7 8

10K Ohm

10K Ohm

+/-5%

+/-5%

ICH_RIJ_PU

4

5

3

2

4

6

2

4

6

ICH_RIJ_PU

PWRG_ATX8,30

PWRG_ATX

12V_SYS

CA

5V_SB

D17

D17

LS4148-F

LS4148-F

5V_DUAL

2N7002DW

2N7002DW

1

S1

2

G1

6

D1

Q39

Q39

PWOKJ

2N7002DW

2N7002DW

S2

G2

D2

PWOKJ

PWOK-

PWOK+

S1

G1

D1

Q45

Q45

ICH_RIJ_PU 22

4

S2

5

G2

3

D2

1

2

6

PWOK-

2

PWOK+

G

5V_SB

G

D S

5V_SYS

L

H

AP3310H

AP3310H

Q51

Q51

D S

Q50

Q50

AOD452AL

AOD452AL

12

*

*

PWOK+25

EC49

EC49

1000uF

1000uF

*

*

+/-20%

+/-20%

5V_DUAL

C486

C486

10uF

10uF

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

Title

Title

Title

STR 1D8V 3D3V_DUAL 5V_DUAL

STR 1D8V 3D3V_DUAL 5V_DUAL

STR 1D8V 3D3V_DUAL 5V_DUAL

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

PWOK+

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

G41M05

G41M05

G41M05

1

AC

AC

11 34Friday, August 28, 2009

11 34Friday, August 28, 2009

11 34Friday, August 28, 2009

AC

of

of

of

NRIB32

NRIA32

Page 12

亞美商匯

5

HDJ[63..0]

2 OF 7

2 OF 7

U11B

HDJ0

HDJ1

HDJ2

HDJ3

HDJ4

D D

C C

HDJ5

HDJ6

HDJ7

HDJ8

HDJ9

HDJ10

HDJ11

HDJ12

HDJ13

HDJ14

HDJ15

HDBIJ0

HDBIJ014

HDSTBNJ014

HDSTBPJ014

HDJ16

HDJ17

HDJ18

HDJ19

HDJ20

HDJ21

HDJ22

HDJ23

HDJ24

HDJ25

HDJ26

HDJ27

HDJ28

HDJ29

HDJ30

HDJ31

HDBIJ1 HDBIJ3

HDBIJ114

HDSTBNJ114

HDSTBPJ114

U11B

B4

D00#

C5

D01#

A4

D02#

C6

D03#

A5

D04#

B6

D05#

B7

D06#

A7

D07#

A10

D08#

A11

D09#

B10

D10#

C11

D11#

D8

D12#

B12

D13#

C12

D14#

D11

D15#

A8

DBI0#

C8

DSTBN0#

B9

DSTBP0#

G9

D16#

F8

D17#

F9

D18#

E9

D19#

D7

D20#

E10

D21#

D10

D22#

F11

D23#

F12

D24#

D13

D25#

E13

D26#

G13

D27#

F14

D28#

G14

D29#

F15

D30#

G15

D31#

G11

DBI1#

G12

DSTBN1#

E12

DSTBP1#

Socket-IntelPrescottCPU

Socket-IntelPrescottCPU

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DBI2#

DSTBN2#

DSTBP2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBI3#

DSTBN3#

DSTBP3#

HDJ32

G16

HDJ33

E15

HDJ34

E16

HDJ35

G18

HDJ36

G17

HDJ37

F17

HDJ38

F18

HDJ39

E18

HDJ40

E19

HDJ41

F20

HDJ42

E21

HDJ43

F21

HDJ44

G21

HDJ45

E22

HDJ46

D22

HDJ47

G22

HDBIJ2

D19

G20

G19

D20

D17

A14

C15

C14

B15

C18

B16

A17

B18

C21

B21

B19

A19

A22

B22

C20

A16

C17

HDJ48

HDJ49

HDJ50

HDJ51

HDJ52

HDJ53

HDJ54

HDJ55

HDJ56

HDJ57

HDJ58

HDJ59

HDJ60

HDJ61

HDJ62

HDJ63

HDBIJ2 14

HDSTBNJ2 14

HDSTBPJ2 14

HDBIJ3 14

HDSTBNJ3 14

HDSTBPJ3 14

4

HDJ[63..0] 14

HAJ[35..3]

HAJ[35..3]14

4 mils width, 10 mils spacing

3

HAJ[35..3]

HAJ[35..3]14

U11A

HAJ3

HAJ4

HAJ5

HAJ6

HAJ7

HAJ8

HAJ9

HAJ10

HAJ11

HAJ12

HAJ13

HAJ14

HAJ15

HAJ16

HREQJ[4..0]14

HAJ17

HAJ18

HAJ19

HAJ20

HAJ21

HAJ22

HAJ23

HAJ24

HAJ25

HAJ26

HAJ27

HAJ28

HAJ29

HAJ30

HAJ31

HAJ32

HAJ33

HAJ34

HAJ35

HADSTBJ114

HREQJ0

HREQJ1

HREQJ2

HREQJ3

HREQJ4

HADSTBJ014

PECI30

U11A

L5

A03#

P6

A04#

M5

A05#

L4

A06#

M4

A07#

R4

A08#

T5

A09#

U6

A10#

T4

A11#

U5

A12#

U4

A13#

V5

A14#

V4

A15#

W5

A16#

N4

RSVD1

P5

RSVD2

K4

REQ0#

J5

REQ1#

M6

REQ2#

K6

REQ3#

J6

REQ4#

R6

ADSTB0#

G5

PCREQ#

AB6

A17#

W6

A18#

Y6

A19#

Y4

A20#

AA4

A21#

AD6

A22#

AA5

A23#

AB5

A24#

AC5

A25#

AB4

A26#

AF5

A27#

AF4

A28#

AG6

A29#

AG4

A30#

AG5

A31#

AH4

A32#

AH5

A33#

AJ5

A34#

AJ6

A35#

AC4

RSVD3

AE4

RSVD4

AD5

ADSTB1#

Socket-IntelPrescottCPU

Socket-IntelPrescottCPU

ADS#

BNR#

RSP#

BPRI#

DBSY#

DRDY#

HITM#

IERR#

INIT#

LOCK#

TRDY#

BINIT#

DEFER#

EDRDY#

MCERR#

AP0#

AP1#

BR0#

TESTHI08

TESTHI09

TESTHI10

DP0#

DP1#

DP2#

DP3#

GTLREF1

GTLREF0

CS_GTLREF

RESET#

RS0#

RS1#

RS2#

1 OF 7

1 OF 7

D2

C2

D4

HIT#

TP_RSPJ

H4

G8

B2

C1

E4

HIERRJ

AB2

P3

C3

E3

TP_BINITJ

AD3

G7

HGTLREF_1_2

F2

TP_MCERRJ

AB3

TP_APJ0

U2

TP_APJ1

U3

HBR0J

F3

TESTHI_8

G3

TESTHI_9

G4

TESTHI_10

H5

TP_DPJ0

J16

TP_DPJ1

H15

TP_DPJ2

H16

TP_DPJ3

J17

HGTLREF_1_2

H2

HGTLREF_0_3

H1

E24

G23

B3

F5

A3

HADSJ 14

HBNRJ 14

HITJ 14

TP16TP16

HBPRIJ 14

HDBSYJ 14

HDRDYJ 14

HITMJ 14

INITJ 23

HLOCKJ 14

HTRDYJ 14

TP19TP19

HDEFERJ 14

TP20TP20

TP17TP17

TP21TP21

HBR0J 14

TP10TP10

TP7TP7

TP6TP6

TP5TP5

TP4TP4

HCPURSTJ 9,14

HRSJ0 14

HRSJ1 14

HRSJ2 14

THERMDA/THERMDC

1. width=10 mils, spacing=10 mils.

2. route the lines in parallel

2

3 OF 7

3 OF 7

U11C

U11C

SMIJ23

A20MJ23

FERRJ23

INTR23

NMI23

IGNNEJ23

STPCLKJ23

HVCCA13

HVSSA13

HVCCPLL13

CK_200M_P_CPU7

CK_200M_N_CPU7

VCC_SENSE9

VSS_SENSE9

HVCCA

HVSSA

VCC_PLL

HVCCPLL

VID09

VID19

VID29

VID39

VID49

VID59

VID69

VID79

VID_SELECT

TP15TP15

THERMDA30

THERMDC30

P2

SMI#

K3

A20M#

R3

FERR#/PBE#

K1

LINT0

L1

LINT1

N2

IGNNE#

M3

STPCLK#

A23

VCCA

B23

VSSA

D23

RSVD5

C23

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VID7

VCCIOPLL

AM2

VID0

AL5

VID1

AM3

VID2

AL6

VID3

AK4

VID4

AL4

VID5

AM5

FC11

AM7

FC12

AN7

FC16

F28

BCLK0

G28

BCLK1

AE8

SKTOCC#

AL1

THERMDA

AK1

THERMDC

AN3

VCCSENSE

AN4

VSSSENSE

AN5

VCC_MB_REG

AN6

VSS_MB_REG

Changed pin name

Changed pin name

from RSV

from RSV

F29

RSVD9

TESTHI00

TESTHI01

TESTHI11

TESTHI12

TESTHI02

TESTHI03

TESTHI04

TESTHI05

TESTHI06

TESTHI07

FORCEPH

TESTHI13

PWRGOOD

PROCHOT#

THERMTRIP#

BOOTSELECT

Socket-IntelPrescottCPU

Socket-IntelPrescottCPU

RSVD11

RSVD12

COMP0

COMP1

COMP2

COMP3

COMP4

COMP5

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD21

RSVD24

MSID1

MSID0

LL_ID0

LL_ID1

F26

W3

P1

W2

F25

G25

G27

G26

G24

F24

AK6

G6

L2

AH2

N1

AL2

M2

A13

T1

G2

R1

J2

T2

N5

AE6

C9

G10

D16

A20

E23

F23

J3

V1

W1

Y1

V2

AA2

1

TESTHI_0

TESTHI_1

DPSLP#

TESTHI_12

TESTHI_2_7

FORCEPHJ

CPU_SLPJ

PROCHOTJ

HCOMP0

HCOMP1

HCOMP2

HCOMP3

HCOMP4

DPRSTP#

H_TEST

HGTLREF_0_3

MS_ID1

MS_ID0

CPU_BOOT

TP_CPU_V2

TP_CPU_AA2

FSB_VTT

CPU_PWRG 22

THERMTRIPJ 23

FSB_VTT

*

*

R254

R254

*

*

51 Ohm

51 Ohm

+/-5%

+/-5%

R242

R242

49.9

49.9

+/-1%

+/-1%

R237

R237

TP23TP23

51 Ohm

51 Ohm

*

*

TP22TP22

+/-5%

+/-5%

R238 62

HTCK

HTDI

HTDO

HTMS

HTRSTJ

HBPM0J

HBPM1J

HBPM2J

HBPM3J

HBPM4J

HBPM5J

FSBSEL0

FSBSEL1

FSBSEL2

C302

C302

0.1uF

0.1uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

Dummy

Dummy

VTT_OUT_RIGHT

Dummy

Dummy

AE1

AD1

AF1

AC1

AG1

AJ2

AJ1

AD2

AG2

AF2

AG3

AC2

AK3

AJ3

G29

H30

G30

R288

R288

*

*

4.12K

4.12K

+/-1%

+/-1%

R238 62

+/-5%

+/-5%

R239 62

R239 62

+/-5%

+/-5%

VTT_OUT_RIGHT

R250 62

VTT_OUT_LEFT

Place at CPU end of route

R255 62 +/-5%

R255 62 +/-5%

*

*

Place at CPU end of route

RN31

RN31

7 8

51

51

5

6

+/-5%

+/-5%

3

4

*

*

1

2

RN30

RN30

7 8

51

51

5

6

+/-5%

+/-5%

3

4

*

*

1

2

R240 49.9 +/-1%

R240 49.9 +/-1%

*

B B

A A

*

10 mils width

Dummy

Dummy

7 mils spacing to low speed signals

14mils spacing to high speed signals

max. 1200mils

R249 49.9 +/-1%

R249 49.9 +/-1%

*

*

R160 49.9 +/-1%

R160 49.9 +/-1%

*

*

10 mils width

7 mils spacing to low speed signals

14mils spacing to high speed signals

max. 1200mils

R241 49.9 +/-1%

R241 49.9 +/-1%

*

*

R243 49.9 +/-1%

R243 49.9 +/-1%

*

*

MS_ID1

MS_ID0

51 Ohm

51 Ohm

Dummy

Dummy

MSID0: NC = 2005 Mainstream / Value, 2006 65W FMB

Vss = 2005 Performance FMB

MSID1: Vss = 2005 Performance,2005 Mainstream/Value,2006 65W FMB

5

R236

R236

HBR0J

TESTHI_9

TESTHI_8

TESTHI_10

H_TEST

TESTHI_12

TESTHI_1

HCOMP4

HCOMP2

HCOMP0

HCOMP3

HCOMP1

*

*

*

*

R251

R251

Dummy

Dummy

51 Ohm

51 Ohm

VTT_OUT_RIGHT

FSB_VTT

VTT_OUT_RIGHT

VTT_OUT_RIGHT

7 8

5

6

3

4

*

*

1

2

7 8

5

6

3

4

*

*

1

2

R253 51 Ohm +/-5%

R253 51 Ohm +/-5%

*

*

R129 51 Ohm +/-5%

R129 51 Ohm +/-5%

*

*

R128 51 Ohm +/-5%

R128 51 Ohm +/-5%

*

*

R264 130 +/-1%R264 130 +/-1%

R281 130 +/-1%R281 130 +/-1%

R246 62 +/-5%

R246 62 +/-5%

*

*

R276 62 +/-5%

R276 62 +/-5%

*

*

Place at CPU end of route

R269 680 Ohm +/-1%

R269 680 Ohm +/-1%

*

*

C307

C307

1uF

1uF

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

*

*

RN29

RN29

680

680

+/-5%

+/-5%

RN25

RN25

680

680

+/-5%

+/-5%

DPSLP#

TESTHI_0

TESTHI_2_7

FORCEPHJ

PROCHOTJ

HIERRJ

HCPURSTJ

VID_SELECT

VTT_OUT_RIGHT

4

VID6

VID1

VID3

VID7

VID0

VID2

VID5

VID4

R256

R256

*

*

57.6 Ohm

57.6 Ohm

+/-1%

+/-1%

R233 10 Ohm

R233 10 Ohm

R252

R252

*

*

100 Ohm

100 Ohm

+/-1%

+/-1%

O.635*VTT

*

*

+/-1%

+/-1%

*

*

VTT_OUT_RIGHT

HBPM2J

RN24

RN24

7 8

5

6

3

4

*

*

1

2

7 8

5

6

3

4

*

*

1

2

Place BPM termination near CPU

TP_CPU_G1

reserve for Kentsfield CPU support

PROCHOTJ

R280 0 +/-5%

R280 0 +/-5%

*

*

Dummy

Dummy

51

51

+/-5%

+/-5%

RN28

RN28

51

51

+/-5%

+/-5%

VTT_OUT_LEFT

R235

R235

51 Ohm

51 Ohm

*

*

+/-5%

+/-5%

TP_CPU_G1 13

HBPM3J

HTDI

HTMS

HBPM1J

HBPM0J

HBPM5J

HBPM4J

ICH_THRM_UP 22,30

Stuff to enable Thermal event

meet the 0.63Vtt value before

BIOS GPIO setting. This is a Intel spec.

GPIO26: Default low

GPIO13: Default input

HGTLREF_0_3

C296

C296

220pF

220pF

50V, NPO, +/-5%

50V, NPO, +/-5%

GTL_GPIO1322

GTL_GPIO2622

1D5V_CORE

12

#REFDE10

#REFDE10

COPPER

COPPER

VCC_PLL

C399

*

*

C399

12

10nF

10nF

*

*

25V, X7R, +/-10%

25V, X7R, +/-10%

Dummy

Dummy

VTT_OUT_RIGHT

R263

R263

*

*

49.9

49.9

+/-1%

+/-1%

R259 10 Ohm

R259 10 Ohm

R258

R258

*

*

100 Ohm

100 Ohm

+/-1%

+/-1%

*

*

+/-1%

+/-1%

C398

C398

12

10uF

10uF

*

*

Dummy

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

R260

R260

*

*

576 Ohm

576 Ohm

+/-1%

+/-1%

3

Dummy

placed near pin D23, within 500 mils

R261

R261

C310

C310

1.3KOhm

1.3KOhm

1uF

1uF

+/-1%

+/-1%

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

R250 62

+/-5% Dummy

+/-5% Dummy

In Design Guide is NC

ICH_SYS_RSTJ7,8,22

VTT_OUT_RIGHT VTT_OUT_LEFT

C297

C297

0.1uF

0.1uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

Dummy

Dummy

O.667*VTT

HGTLREF_1_2

C295

C295

220pF

220pF

*

*

50V, NPO, +/-5%

50V, NPO, +/-5%

GTLREF voltage should be 0.63*VTT

12 mils width, 15 mils spacing

divider should be within 1.5" of the GTLREF pin

0.22nF caps should be placed near CPU pin

place series resistor as close to divider

2

HTDO

*

*

ICH_SYS_RSTJ

FSBSEL07,14

FSBSEL17,14

FSBSEL27,14

R287 100KOhm

R287 100KOhm

*

*

+/-1%

+/-1%

C323

C323

*

*

2.2uF

2.2uF

6.3V, Y5V, +80%/-20%

6.3V, Y5V, +80%/-20%

HTCK

*

*

HTRSTJ

*

*

U11D

U11D

4 OF 7

4 OF 7

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTTPWRGD

VTT_OUT1

VTT_OUT2

VTT_SEL

VTT_OUT_RIGHT

R295

R295

20K

20K

+/-1%

+/-1%

Q31

Q31

MMBT3904-7-F

MMBT3904-7-F

LGA775-1

LGA775-1

LGA775-1

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

A29

B25

B29

B30

C29

A26

B27

C28

A25

A28

A27

C30

A30

C25

C26

C27

B26

D27

D28

D25

D26

B28

D29

D30

AM6

AA1

J1

F27

R283

R283

*

*

1K

1K

+/-5%

+/-5%

VTT_OUT_RIGHT

VTT_OUT_LEFT

Q32

Q32

2N7002

2N7002

TCK

TDI

TDO

TMS

TRST#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

DBR#

ITPCLKOUT0

ITPCLKOUT1

BSEL0

BSEL1

BSEL2

Socket-IntelPrescottCPU

Socket-IntelPrescottCPU

5V_SB

*

*

B

E C

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

FSB_VTT

VTT_PWRGD

VTT_PWRGD

#REFDE27

#REFDE27

VRM_EN

12

*

*

C319

C319

COPPER

COPPER

2.2uF

2.2uF

6.3V, Y5V, +80%/-20%

6.3V, Y5V, +80%/-20%

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

G41M05

G41M05

G41M05

1

12 34Friday, October 23, 2009

12 34Friday, October 23, 2009

12 34Friday, October 23, 2009

VTT_OUT_RIGHT

VTT_OUT_LEFT

VRM_EN 9

of

of

of

AC

AC

AC

Page 13

亞美商匯

5

U11E

U11E

AG22

VCCP1

K29

VCCP2

AM26

VCCP3

AL8

VCCP4

AE12

VCCP5

AE11

VCCP6

W23

VCCP7

W24

VCCP8

D D

C C

B B

A A

W25

VCCP9

T25

VCCP10

Y28

VCCP11