Page 1

5

smd.db-x7.ru

4

3

2

1

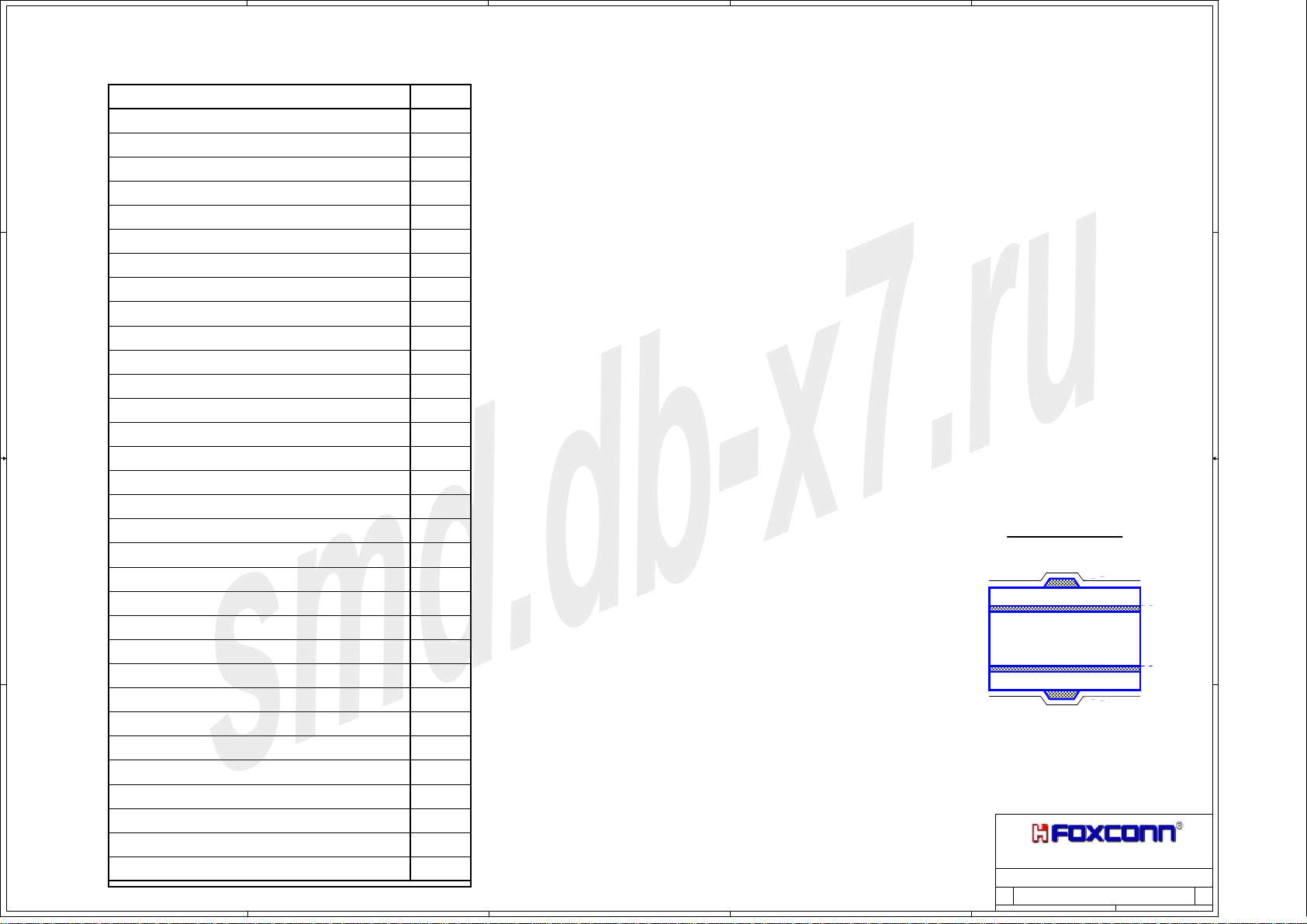

CONTENT SHEET

D D

C C

B B

A A

Cover Sheet

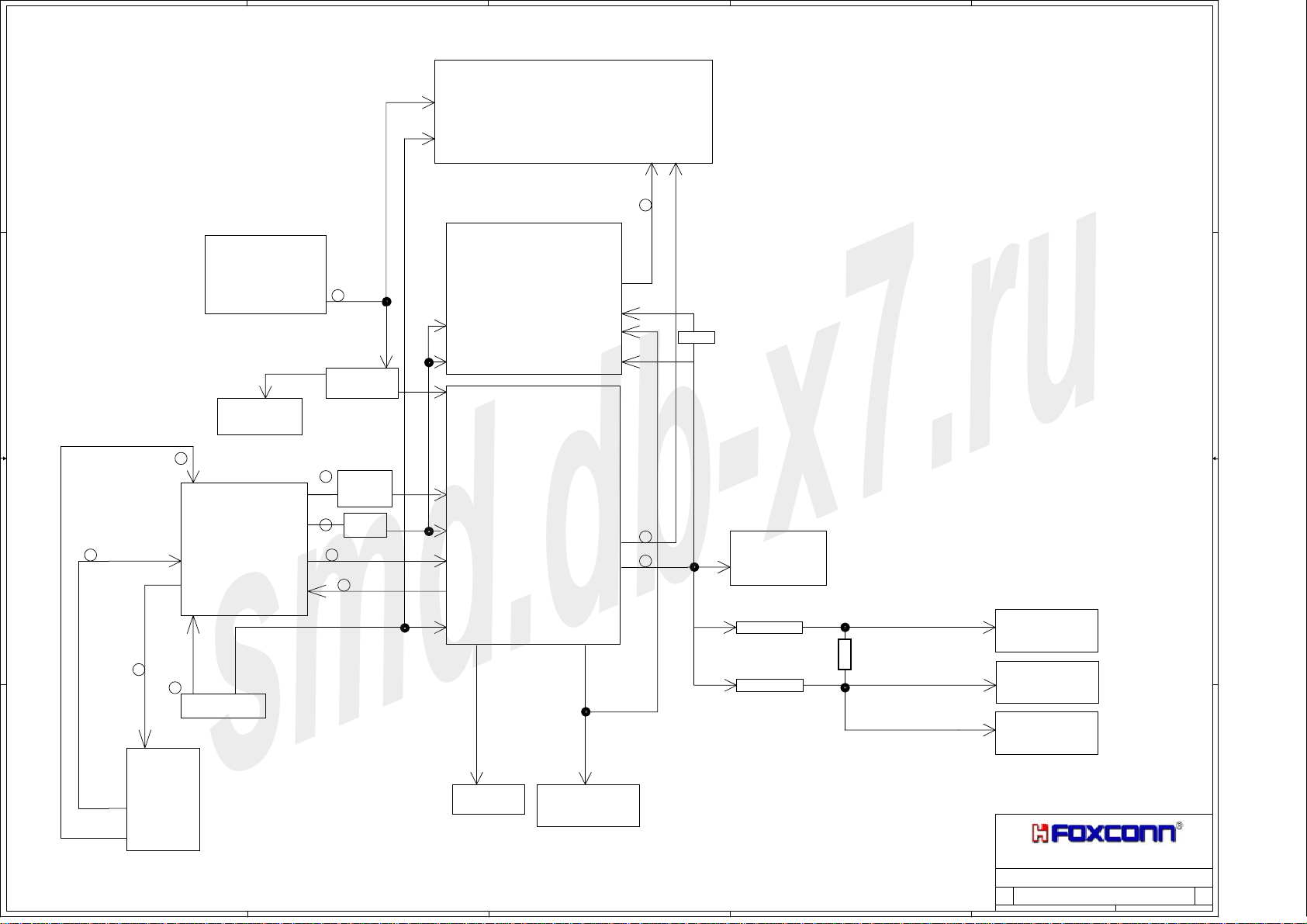

Block Diagram

Clock Distribution

Power Delivery Map

Platform Sequence

Reset Map

CK505 ClockGen

VRD11.1-NCP5395

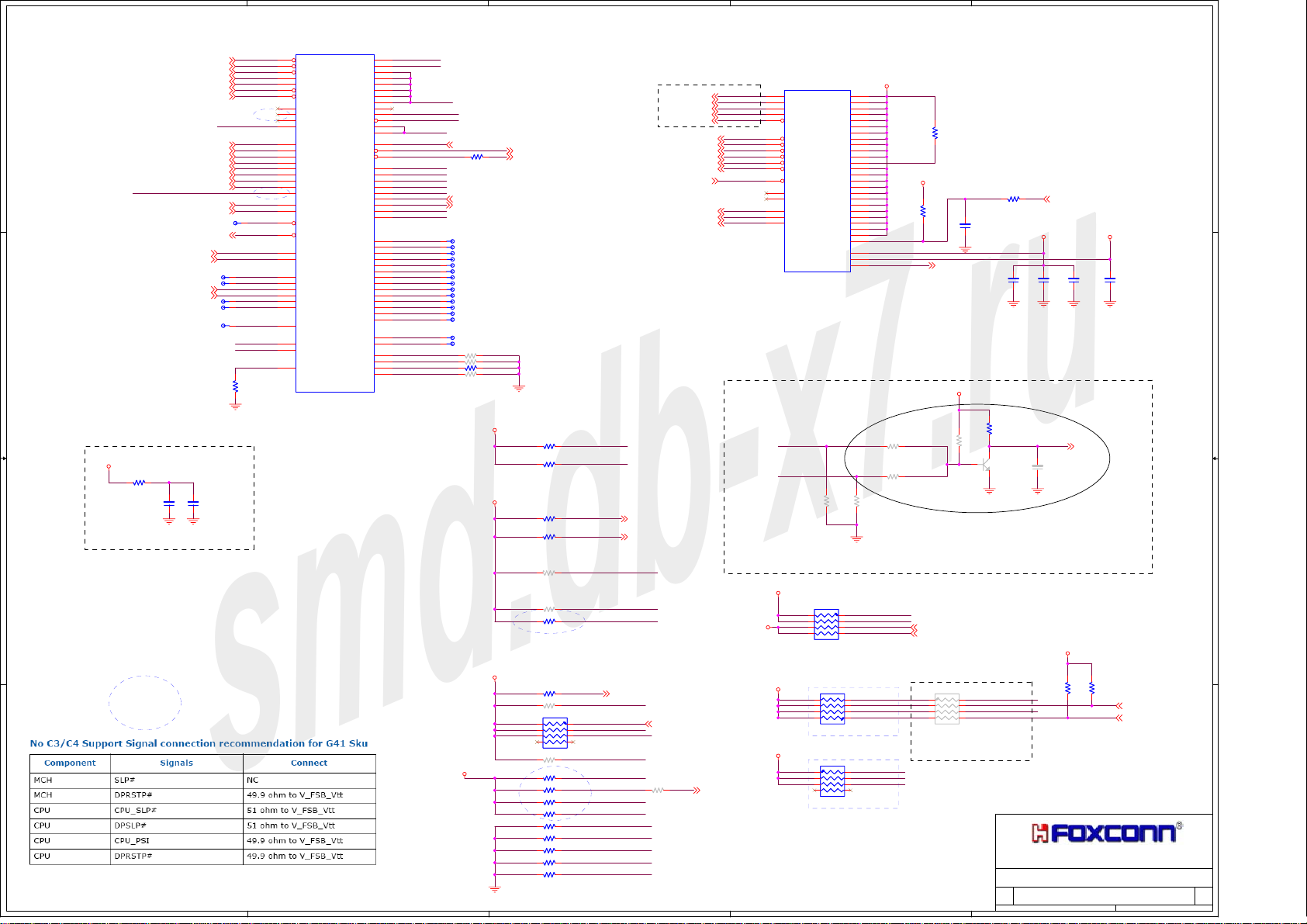

Eaglelake -GMCH-1~4

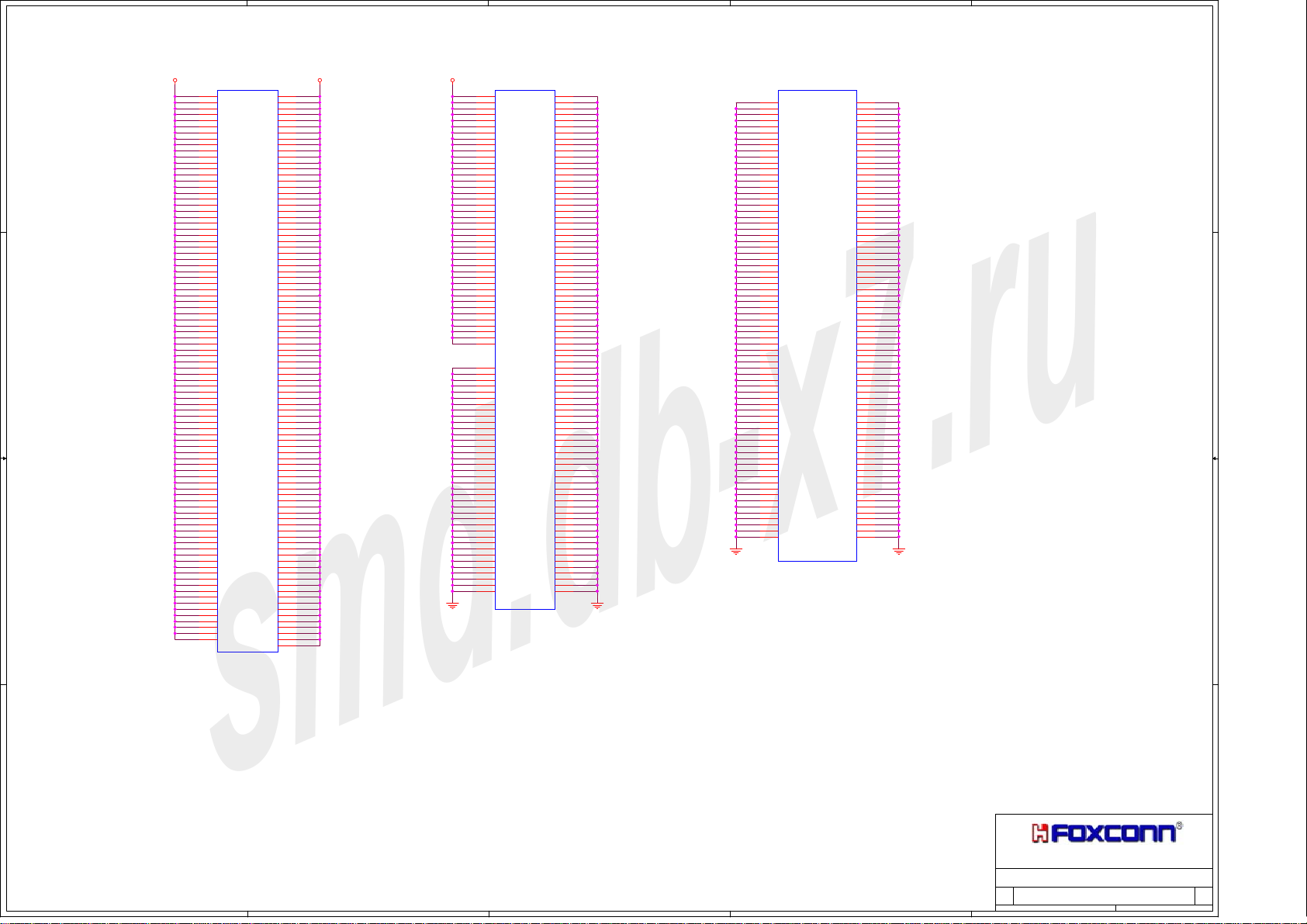

DDRIII-CHA/DIMM 2

DDRIII-CHB/DIMM 1

TPM/OBR/INTRUDER

1D1V/1D5V/FSB_VTT

STR1D5V 3D3_DUAL 5V_DUAL

VGA

PCI-E X16 Slot

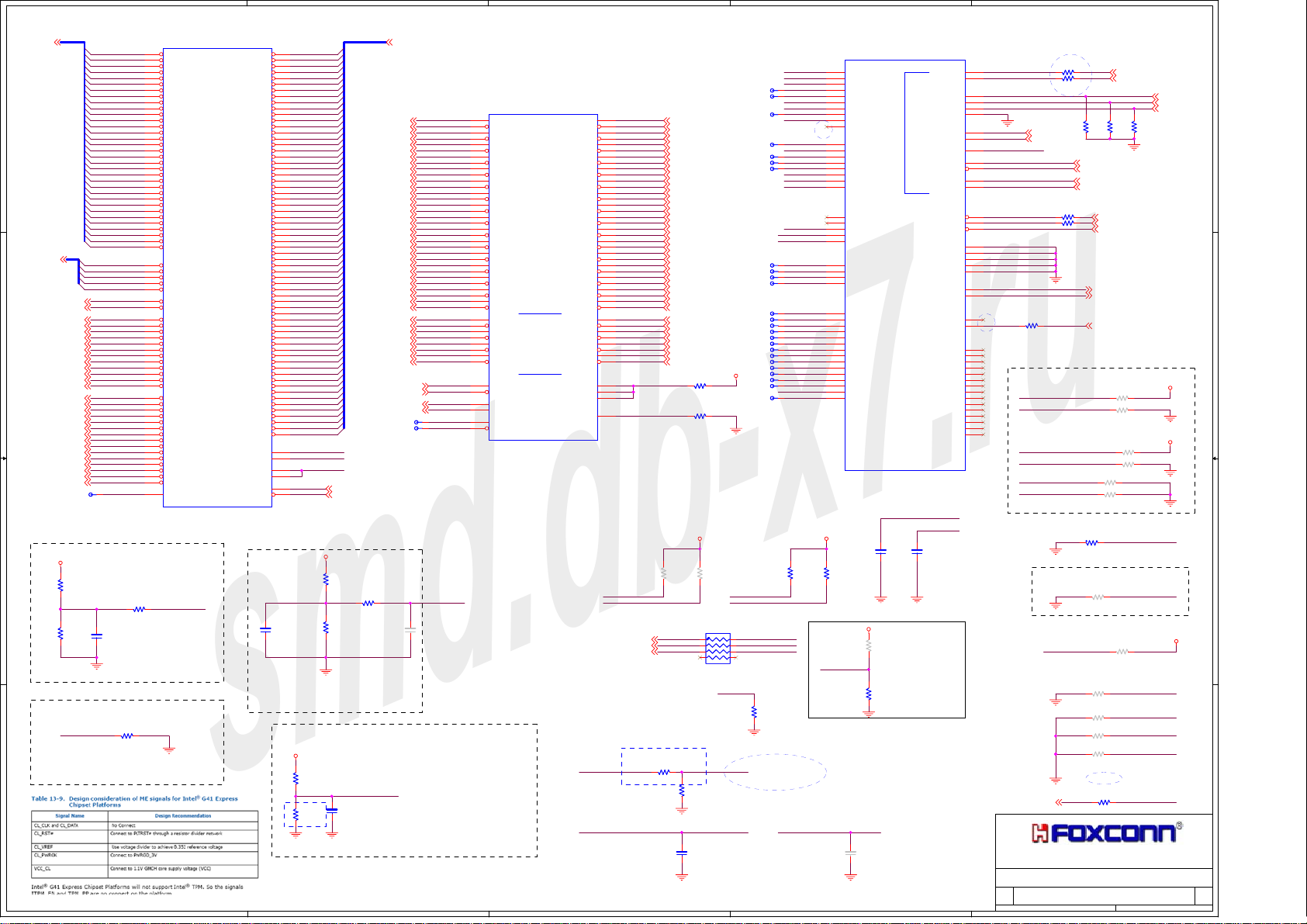

ICH7-1~4

LAN-BCM57760

Super I/O -IT8721F/BX

HDA Codec ALC662

Serial/Parellel CONN

PCI Express x1 Slot

ATX/FP/SPK

CPU / System Fan/SMBUS

KB/MS/SPI/XDP

USB Connector

GPIO / IRQ / IDSEL Map

Change List 37

1

2

3

4

5

6

7

8

9~11LGA775 -1~3

12~15

16

17

18

19

20

21

22

23~25

26

27

28~29

30

31

32

33

34

35

36

Archer

CPU:

System Chipset:

Main Memory:

On Board Device:

Expansion Slots:

PWM Controller:

Intel Conroe, Wolfdale, Yorkfield processors in LGA775 Package.

TDP=95W

North Bridge ... Eaglelake-G41

South Bridge ... ICH7

Dual Channel / DDR-III * 2

Clock Generator ... IDTCV186-2APAG8

Super I/O ... IT8721F/BX

LAN-BCM57760

HDA Codec ... ALC662

BIOS ... SPI Flash ROM(8M)

PCI EXPRESS 16X SLOT *1

PCI EXPRESS 1X SLOT * 1

Controller ... NCP5395TMNR2G (3Phase)

DTX(9.6"x7.9")

(Version: A )

Board Stack-up

(1080 Prepreg Considerations)

Solder Mask

PREPREG 2.7mils

CORE 47mils

PREPREG 2.7mils

Solder Mask

Single End 50ohm Top/Bottom : 4mils

USB2.0 - 90ohm : 15/4.5/7.5/4.5/15

SATA - 95ohm : 15/4/8/4/15

PCIE - 95ohm : 15/4/8/4/15

DMI - 95ohm : 15/4/8/4/15

1.9mils Cu plus plating

1.9mils Cu plus plating

1 oz. (1.2mils)

Cu Power

Plane

1 oz. (1.2mils)

Cu GND

Plane

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

FOXCONN PCEG

Cover Sheet

Cover Sheet

Cover Sheet

Archer

Archer

Archer

1

137Wednesday, December 09, 2009

137Wednesday, December 09, 2009

137Wednesday, December 09, 2009

AC

AC

AC

Page 2

5

smd.db-x7.ru

4

VRD 11.1

3 Phase PWM

3

LGA775 Processor

2

1

D D

PCI-E X16

GFX Connector

XDP Header

Level Shift

16 Lanes

SWITCH

Socket T

FSB

800/1066/1333

DDRIII 1066

CK-505 Clock Generator

Channel A DDRIII

DIMM2

GMCH

Eaglelake-G41

C C

Back Panel

USB Port 4

USB Port 5

USB Port 6

USB Port 7

VGA Connector

USB

VGA

DMI I/F

4 Lanes

ICH-7

B B

Front Panel

USB Port 0

PCI-E X1 Slot 1

PCI-E X1

DDRIII 1066

PCIE 1X

SATA I/F

Channel B DDRIII

DIMM1

LAN

BCM57760

Serial ATA

SATA Connector 1

SATA Connector 2

USB Port 1

USB Port 2

USB Port 3

Super I/O

A A

5

IT8721F/BX

PS2

Keyboard / Mouse

4

LPC I/F

3

HD Link

SPI I/F

Realtek ALC662

BIOS

SPI Flash 8M

2

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

FOXCONN PCEG

Block Diagram

Block Diagram

Block Diagram

Archer

Archer

Archer

1

237Wednesday, December 09, 2009

237Wednesday, December 09, 2009

237Wednesday, December 09, 2009

AC

AC

AC

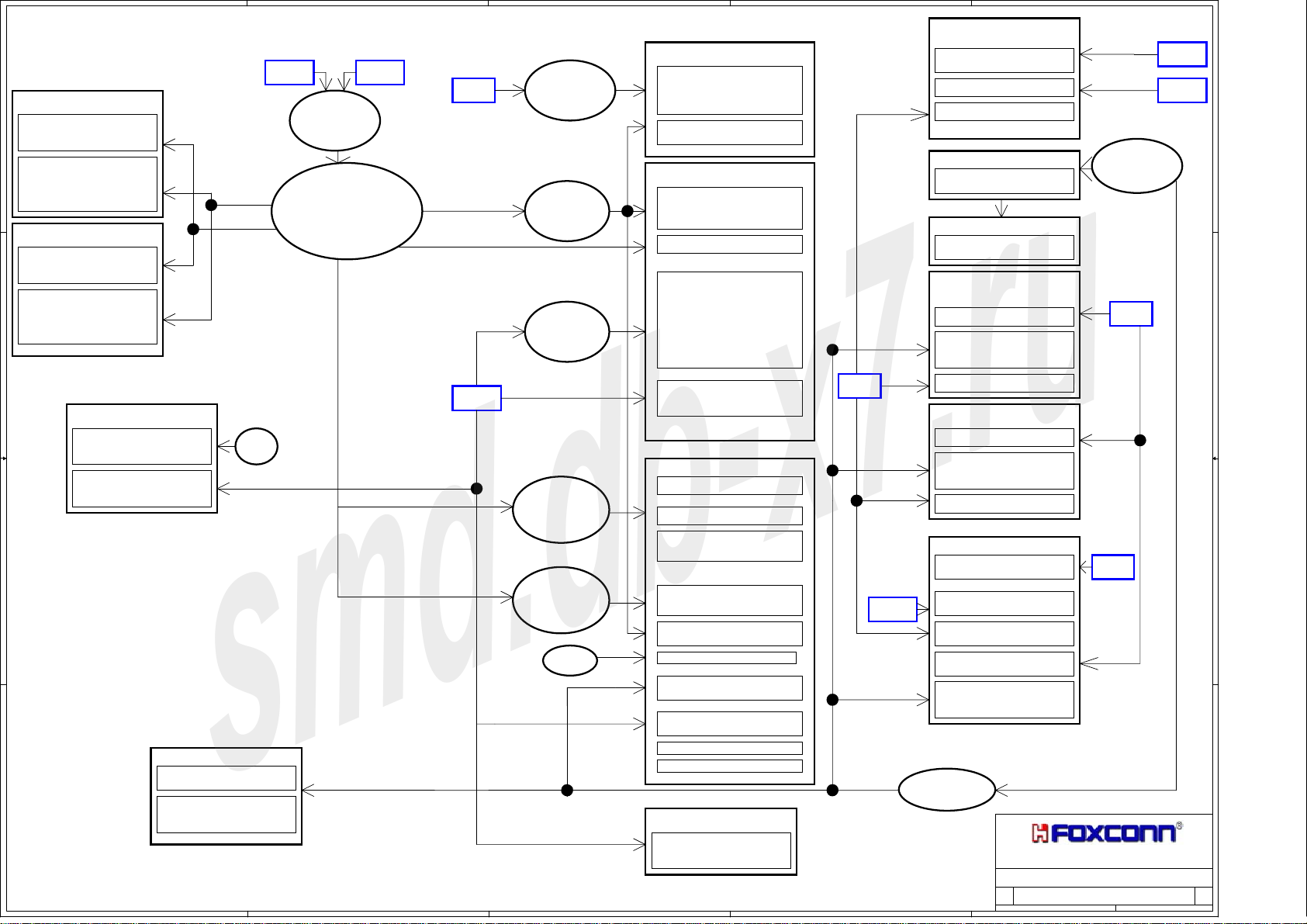

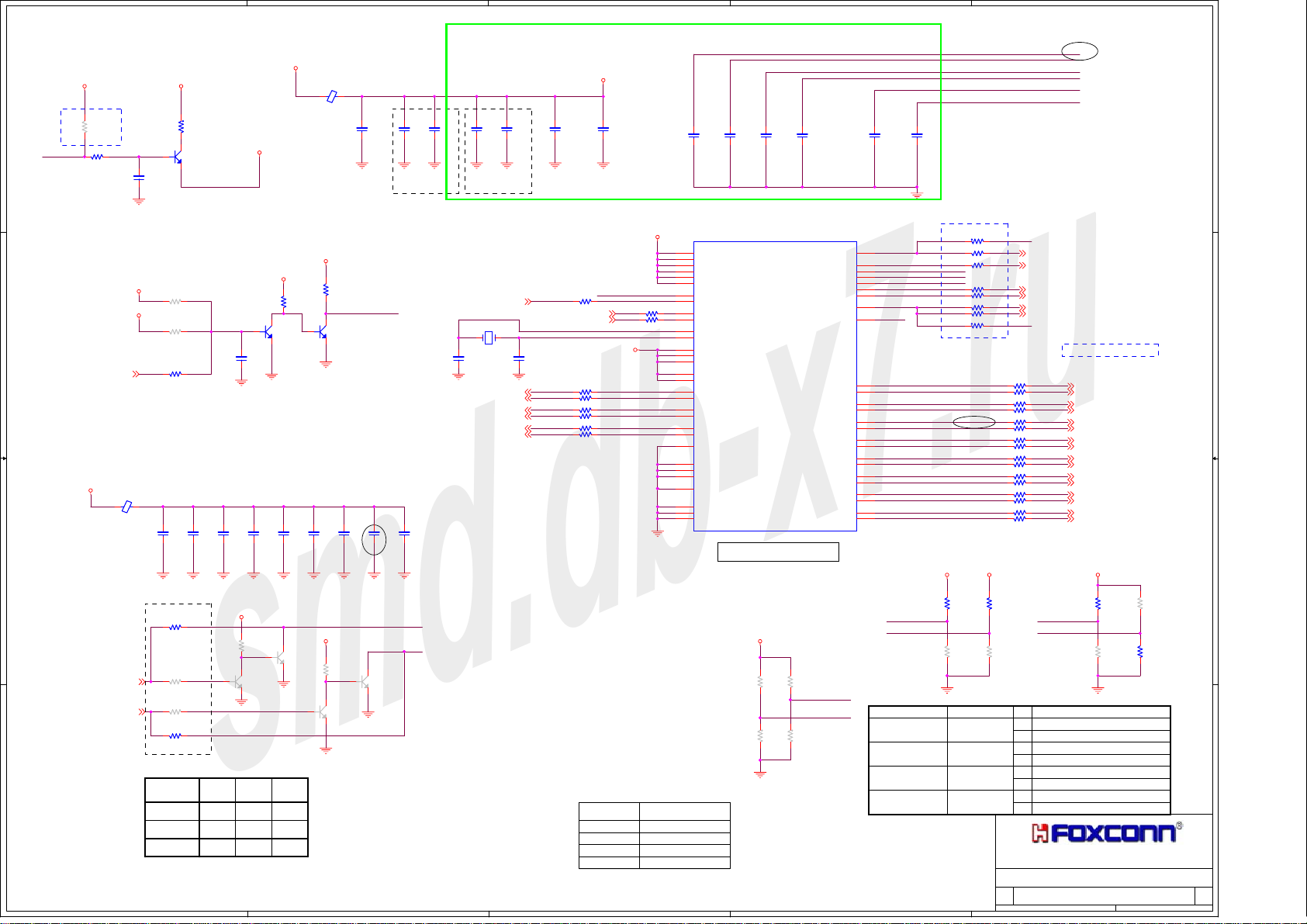

Page 3

5

smd.db-x7.ru

14.318MHz

4

3

2

1

CPU

D D

CPU 200/266/333 MHz Diff Pair

MCH 200/266/333 MHz Diff Pair

DDRIII 2 Slots 8 Diff CLKs

PCI Express 100 MHz Diff Pair

DOT 96 MHz Diff Pair

C C

CK-505

PCI Express/DMI 100 MHz Diff Pair

PCI Express/DMI 100 MHz Diff Pair

USB/SIO 48 MHz

ICH 33 MHz

REF 14 MHz

PCI Express x16 Gfx

GMCH

Eaglelake

Channel A DDRIII

DIMM2

Channel B DDRIII

DIMM1

DDRIII 1066

DDRIII 1066

ICH7

Azalia Bit Clock

B B

LAN

BCM57760

SIO 33 MHz

SATA 100 MHz Diff Pair

A A

5

PCI Express 100 Mhz Diff Pair

XDP 200/266/333 MHz Diff Pair

4

25M Hz

3

32.768KHz

Super I/O

PCI Express x1 Slot 1

XDP

2

HD Audio

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

FOXCONN PCEG

Clock Distribution

Clock Distribution

Clock Distribution

Archer

Archer

Archer

1

AC

AC

337Wednesday, December 09, 2009

337Wednesday, December 09, 2009

337Wednesday, December 09, 2009

AC

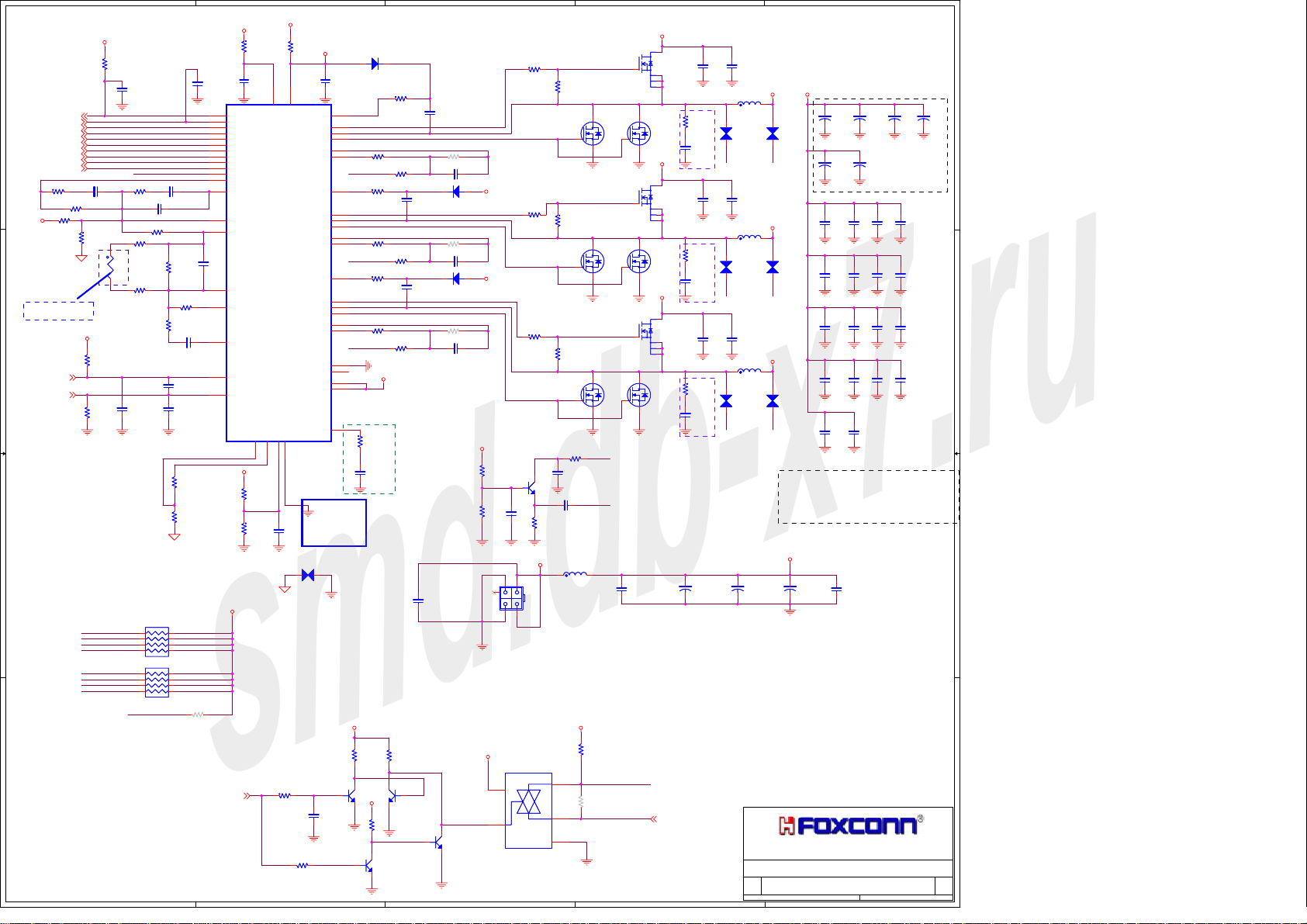

Page 4

5

smd.db-x7.ru

5V

DDR3 Channel A

D D

Vdd (Core)=1.5V

Ivdd(Max)=1.8A(per channel)

Vtt (Core)

0.75V

Ivterm(Max)=210mA

(per channel)

DDR3 Channel B

Vdd (Core)=1.5V

Ivdd(Max)=1.8A(per channel)

Vtt (Core)

0.75V

Ivterm(Max)=210mA

(per channel)

C C

5V_DUAL

Icc(Max)=

4.345A(S0,S1)

22mA(S3)

Single Phase Switch

5VDUAL to 1.5V_STR

Ivdd(Max)=14A

Ivdd(Max)=650mA(S3)

LDO

1.5V to 0.75V

Ivterm(Max)=0.42A

4

5VSB

uATX P/S

12V

VRD 11.1

Switching

3 Phase

Linear 1.8V

to 1.2V

6A

GMCH 1.1V

21.34A

Switching

3

2

1

Super I/O

Proceessor

Vccp (CPU Vcore)

Voltage=1.15~1.5V

Icc(Max)=70A

3-Phases Swithing

1.2V FSB

Vtt=4.6A

Eaglelake GMCH

FSB_Vtt

1.2V FSB Vtt

Icc(Max)=1.3A

1.5V_STR 3.73A

Vcore (Core Logic)

1.1V

Icc(Max)=13.8A(Integrated)

*1.1V (DMI&PCIe)

VCCA_EXP 2.47A

1.1V

VCC_CL 4.3A

5V_SYS

5V_SB_SYS

3D3_SYS

USB2.0 8 Ports

+5V DUAL=4A(S0, S1)

+5V DUAL=20mA(S3)

PS2

+5V DUAL=345mA(S0, S1)

+5V DUAL=2mA(S3)

PCI Express X16

slot (1)

+12V=5.5A

3.3VSB

Icc(Max)=0.375A(wake)

Icc(Max)=0.02A(no wake)

5V_DUAL

Icc(Max)=

TBD A(S0,S1)

22mA(S3)

12V

5V

5VSB

3.3V

3.3V VCCA_DAC 66mA

3.3V VCC3_3 15.8mA

3.3V

HDA Codec

Vcc

5V

Icc(Max)=200mA

Vcc

3.3V

Icc(Max)=40mA

B B

BCM57760 Lan

A A

5

3.3V_SB

700mA

AVDD12 /DVDD12/EVDD12

340mA

LDO

12V

to 5V

ICH7

5V

Linear 1.5V

to 1.5V

TBD A

Linear 15V

to 1.05V

TBD A

RTC

Battery

VCC1_5A (USB and SATA)

0.97A

VCC1_5B (PCIE)

0.74A

VCCDMIPLL (DMI)

TBD A 1.5V

1.05V (Core)

Vcc1_05 1.31A

1.2V (FSB_Vtt)

V_CPU_IO 14mA

RTC=TBD uA

3.3V

VccSus3_3 0.7A

3.3V

VCC3_3 0.58A

5V Ref 6mA

5VRefSus 10mA

CK505

Vdd (Core)

3.3V

Ivdd(Max)=250mA

4

3

2

+3.3V=3A

PCI Express X1

Per slot (1)

+12V=0.5A

3.3VSB

Icc(Max)=0.375A(wake)

Icc(Max)=0.02A(no wake)

+3.3V=3A

PCI Slot(2)

-12V

Icc(Max)=0.1A

5V

Icc(Max)=5A

3.3V

Icc(Max)=7.6A

12V

Icc(Max)=0.5A

3.3VSB

Icc(Max)=0.375A(wake)

Icc(Max)=0.02A(no wake)

5V_DUAL to

3.3SB TBD A

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

-12V

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

Power Delivery Map

Power Delivery Map

Power Delivery Map

Archer

Archer

Archer

1

AC

AC

437Wednesday, December 09, 2009

437Wednesday, December 09, 2009

437Wednesday, December 09, 2009

AC

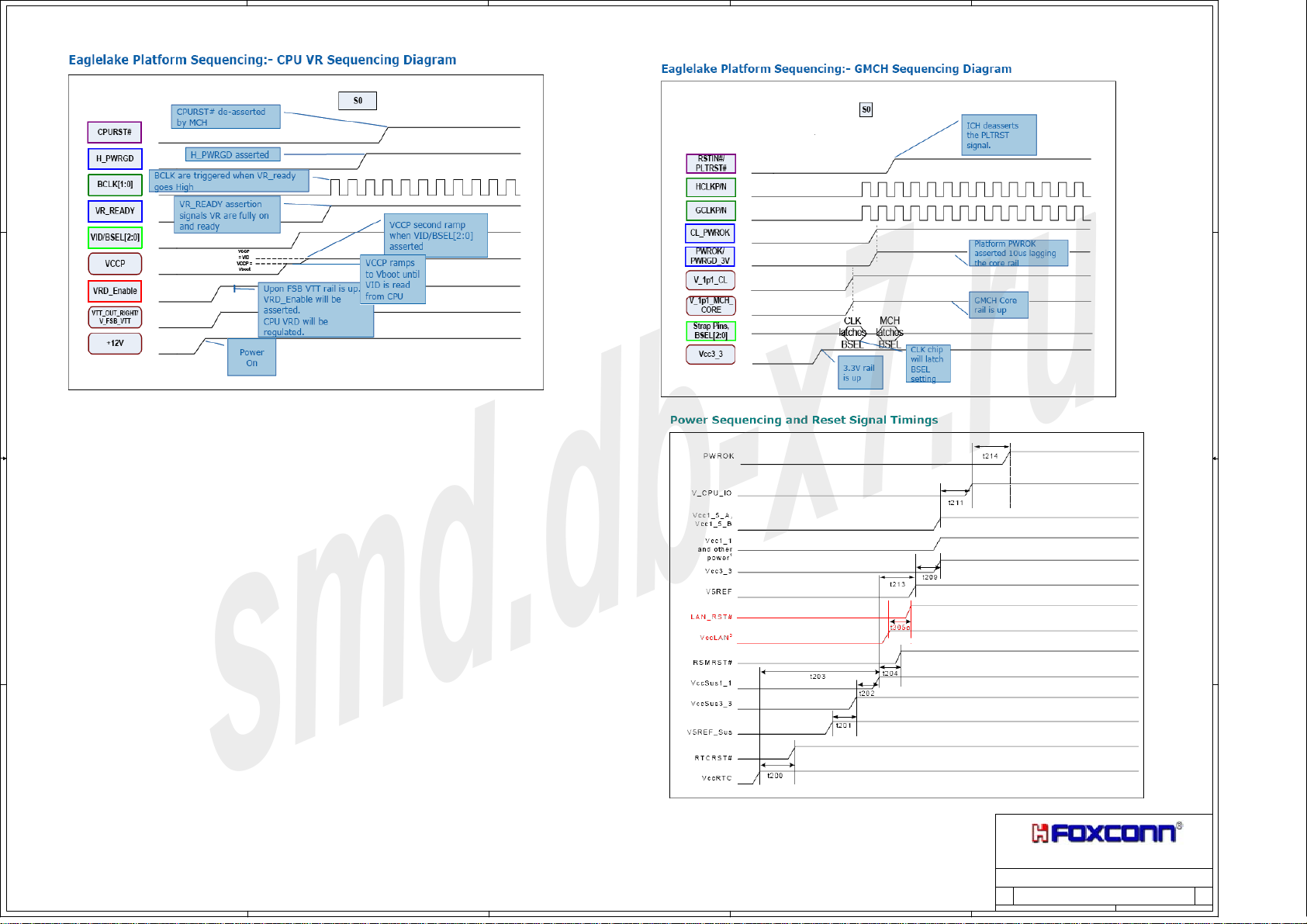

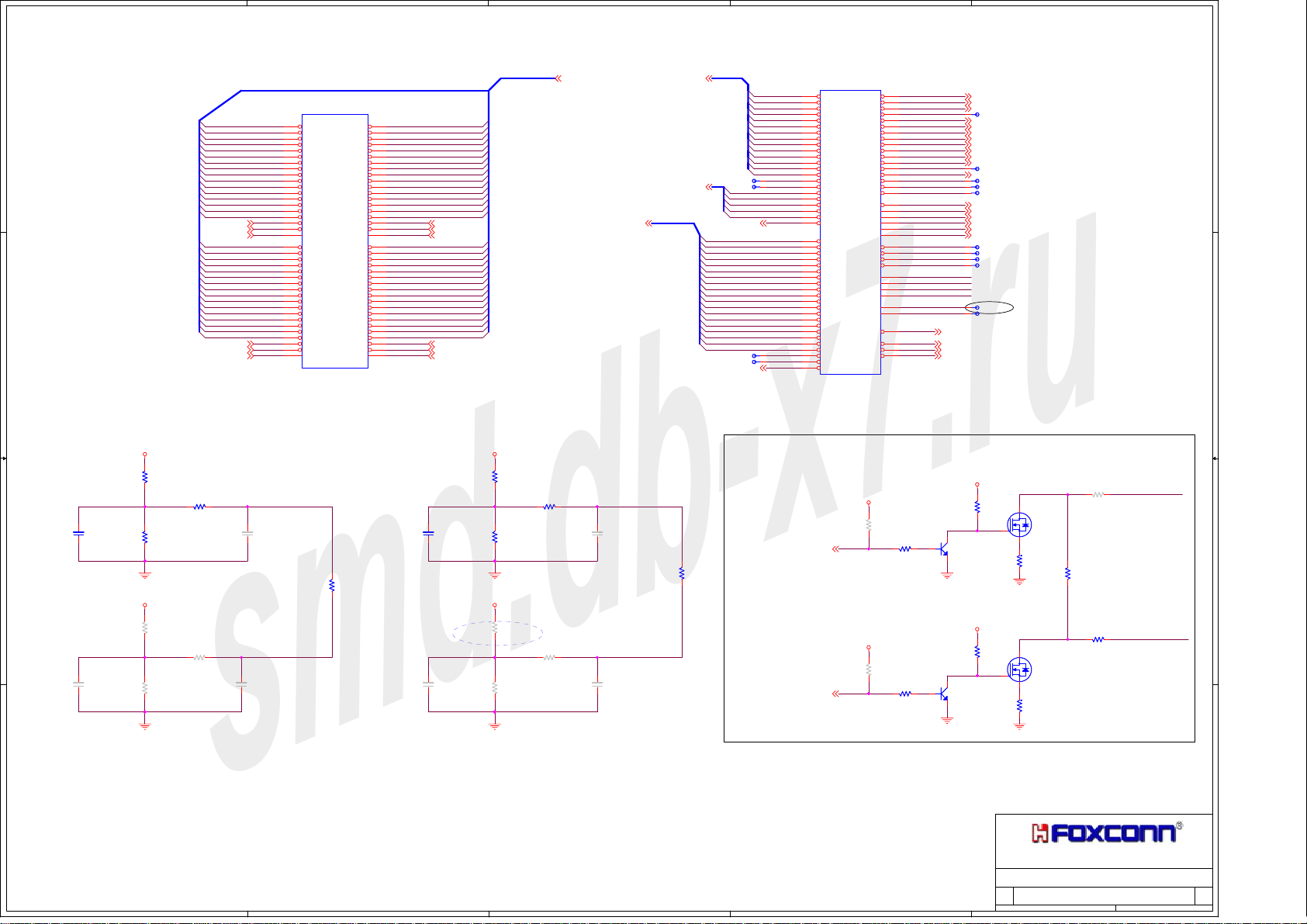

Page 5

5

smd.db-x7.ru

D D

C C

4

3

2

1

B B

A A

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

FOXCONN PCEG

Platform Sequence

Platform Sequence

Platform Sequence

Archer

Archer

Archer

1

AC

AC

537Wednesday, December 09, 2009

537Wednesday, December 09, 2009

537Wednesday, December 09, 2009

AC

Page 6

5

smd.db-x7.ru

4

3

2

1

LGA775 Processor

VTTPWRGD

D D

DBR#

CPU

CPURST#

CPU_PWRGD

10

VRD11.1 CPU POWER

VR_READY

C C

CK505

CK_PWRGD

A1

VCCH

Super IO

5

ATXPWRGD

B B

PS_ONJ

4

PSON#

A A

PWROK

ATX

Power

ATXPG

PSON#

PANSWH#

PWRBTINJ_SIO

1

FRONT PANEL

RSMRST#

PWROK1

PWRON#

SUSB#

SUSC#

FP_RSTJ

6

Translation

Circuitry

A2

RSMRST

circuit

6

Buffer

2

PWRBTNJ

3

PWRGD_3V

SLP_S3J

Eaglelake

CLPWROK

PWROK

ICH_VRMPWRGD

RSMRST#

PWROK

PWRBTN#

SLP_S3J

SLP_S5J

SYS_RESET#

SLP_S4J

1D5V_STR

VTT_DDR

GMCH

ICH7

CPURST#

CL_RSTB

HDA_RSTB

RSTIN#

PCIRST#

CPU_PWRG

PLTRST#

HDA_RSTB

RST#

Audio

Divider

8

9

Super IO

LRERST#

Buffer(Dummy)

Buffer

PLTRSTJ_LAN

0 ohm

PLTRSTJ_ALL

RST#

BCM57760

PWRGD

PCIE-16X Slot

PWRGD

PCIE-1X Slot

5V_SB

5

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

FOXCONN PCEG

Reset Map

Reset Map

Reset Map

Archer

Archer

Archer

1

637Wednesday, December 09, 2009

637Wednesday, December 09, 2009

637Wednesday, December 09, 2009

AC

AC

AC

Page 7

5

smd.db-x7.ru

3D3V_SYS

C15

C15

100pF

100pF

*

*

50V, NPO, +/-5%

50V, NPO, +/-5%

3D3V_CLK

B

R1

R1

15

15

R0805

R0805

+/-1%

+/-1%

Q1

Q1

MMBT3904

MMBT3904

sot23_bech11

sot23_bech11

E C

VDD_CLK_R

VDD_CLK_R

*

*

FB_L0805_100 Ohm

FB_L0805_100 Ohm

3D3V_CLK

D D

V_OUT

*

*

R106

R106

10K

10K

Dummy

Dummy

R2 33

R2 33

*

*

FB1

FB1

4

C1

C1

*

*

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

close to pin 2

3

3D3V_CLK

C6

C3

C3

0.1uF

0.1uF

C4

*

*

*

*

0.1uF

0.1uF

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

C2

C2

*

*

*

*

4.7uF

4.7uF

C0805

C0805

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

close to pin 9 close to pin 16,31 close to pin 47 close to pin 53

C5

C5

C4

C6

*

*

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

C7

C7

*

*

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

Dummy

Dummy

2

CK_48M_SIO

CK_48M_ICH

LPC_CLK_TPM

CK_33M_SIO

CK_33M_ICH

CK_14M_ICH

Dummy

Dummy

Dummy

C9

C9

10pF

10pF

50V, NPO, +/-5%

50V, NPO, +/-5%

Dummy

C11

C11

C10

C10

*

*

*

*

10pF

10pF

10pF

10pF

50V, NPO, +/-5%

50V, NPO, +/-5%

50V, NPO, +/-5%

50V, NPO, +/-5%

*

*

Dummy

Dummy

C8

C8

*

*

*

*

10pF

10pF

50V, NPO, +/-5%

50V, NPO, +/-5%

Dummy

Dummy

Dummy

Dummy

C13

C13

10pF

10pF

50V, NPO, +/-5%

50V, NPO, +/-5%

Dummy

Dummy

C14

C14

*

*

10pF

10pF

50V, NPO, +/-5%

50V, NPO, +/-5%

1

Reserved for EMI Caps

3D3V_CLK

3D3V_SYS

B

C16

C16

12

0.1uF

0.1uF

*

*

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

C0603

C0603

C21

C21

C22

C22

*

*

10uF

10uF

10uF

10uF

c0805h14

c0805h14

c0805h14

c0805h14

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

3D3V_CLK

R645

R645

*

*

1K

1K

+/-5%

+/-5%

Dummy

Dummy

B

Q86

Q86

MMBT3904

MMBT3904

Dummy

Dummy

E C

00

100200 MHz

3D3V_SYS

*

*

Q2

MMBT3904Q2MMBT3904

E C

*

*

E C

R6

R6

10K

10K

C23

C23

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

Q88

Q88

MMBT3904

MMBT3904

Dummy

Dummy

*

*

R13

R13

10K

10K

CK_PWRGD

Q3

B

MMBT3904Q3MMBT3904

E C

VDD_CLK_IO

C24

C24

C25

C25

*

*

*

*

0.1uF

0.1uF

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

3D3V_CLK

R646

R646

*

*

1K

1K

+/-5%

+/-5%

Dummy

Dummy

B

Q87

Q87

B

MMBT3904

MMBT3904

Dummy

Dummy

E C

*

*

Q89

Q89

MMBT3904

MMBT3904

Dummy

Dummy

E C

4

C28

C28

0.1uF

0.1uF

C27

C27

*

*

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

FSC

FSA

FSB_VTT

R5 1K+/-5%

R5 1K+/-5%

*

*

Dummy

Dummy

VCCP

R10 10K

R10 10K

*

*

Dummy

FB2

FB2

*

*

FB_L0805_100 Ohm

FB_L0805_100 Ohm

FSBSEL210,12

FSBSEL010,12

5

Dummy

R20 10K

R20 10K

*

*

C19

C19

C20

C20

*

*

*

10uF

10uF

c0805h14

c0805h14

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

*

*

*

*

*

*

*

*

*

B

FSA FSB FSC

*

*

10uF

10uF

c0805h14

c0805h14

Share Common PADS

R647 0 +/-5%

R647 0 +/-5%

R643 4.7K +/-5%

R643 4.7K +/-5%

Dummy

Dummy

R644 4.7K +/-5%

R644 4.7K +/-5%

Dummy

Dummy

R648 0 +/-5%

R648 0 +/-5%

Host Clock

Frequency

333 MHz 0 0 1

266 MHz 0

C C

VR_READY8,10,23

VDD_CLK_R

B B

A A

Ce = 2 * 20 pF - (5pF + 2pF) = 40 pF - 7 pf = 33 pF

FSBSEL110,12

X1

X1

XTAL-14.318MHz

XTAL-14.318MHz

1 2

C17

C17

*

*

33pF

33pF

50V, NPO, +/-5%

50V, NPO, +/-5%

CK_XDP_P34

CK_XDP_N34

CK_N_GMCH12

CK_P_GMCH12

CK_N_CPU10

CK_P_CPU10

16V, X7R, +/-10%

16V, X7R, +/-10%

C18

C18

*

*

33pF

33pF

50V, NPO, +/-5%

50V, NPO, +/-5%

R9 1K

R9 1K

*

*

SMB_DATA_MAIN16,17,33,34

SMB_CLK_MAIN16,17,33,34

VDD_CLK_IO

R23 33

R23 33

*

*

R25 33

R25 33

*

*

R27 33

R27 33

*

*

R29 33

R29 33

*

*

R30 33

R30 33

*

*

R31 33

R31 33

*

*

CFG1, CFG0

CK_PWRGD

FSBSEL1_R

R126 0

R126 0

R127 0

R127 0

OSC_CK14M_XTAL_OUT

OSC_CK14M_XTAL_IN

CK_XDP_P_SRC8_R

CK_XDP_N_SRC8_R

CK_N_GMCH_R

CK_P_GMCH_R

CK_N_CPU_R

CK_P_CPU_R

0, 0

0, 1

1, 0

1, 1

3

*

*

*

*

SATA

PLL4

PLL3

PLL3

PLL4

U1

U1

2

VDD_PCI

9

VDD_48

16

VDD_PLL3

31

VDD_SRC

47

VDD_CPU

53

VDD_REF

48

CKPWRGD/PD#

49

FS_B/TEST_MODE

55

SDA

56

SCL

51

XTAL_OUT

52

XTAL_IN

12

VDD_I/O

20

VDD_PLL3_IO

26

VDD_SRC_IO_1

37

VDD_SRC_IO_2

41

VDD_CPU_IO

39

SRCT8/CPU_ ITPT

38

SRCC8/CPU_ ITPC

42

CPUC1

43

CPUT1

45

CPUC0

46

CPUT0

44

VSS_CPU

15

VSS_IO

23

VSS_SRC2

19

VSS_PLL3

34

VSS_SRC1

50

VSS_REF

11

VSS_48

8

VSS_PCI

Change to to CV1862 APAG--0812

DEFAULT

IDTCV186-2APAG8

IDTCV186-2APAG8

3D3V_CLK

*

*

R50

R50

47K

47K

Dummy

Dummy

R52

R52

33K

33K

Dummy

Dummy

IDT-CV186-2APAG8

IDT-CV186-2APAG8

Dummy

Dummy

Dummy

Dummy

*

*

R51

R51

47K

47K

R53

R53

33K

33K

REF/FS_C/TestSel

PCIF5/ITP_EN

PCI4/SRC5_EN

PCI3/CFGP

PCI2/TME

PCI1/CR#_B

PCI0/CR#_A

USB 48/FS_A

IO_Vout

SRCC7/CR#_E

SRCT7/CR#_F

SRCC6

SRCT6

CPU_Stop#/SRCC5

PCI_Stop#/SRCT5

SRCC4

SRCT4

SRCC3/CR#_D

SRCT3/CR#_C

SATAC/SRCC2

SATAT/SRCT2

SRCC1/SE2

SRCT1/SE1

SRCC0/DOT96C

SRCT0/DOT96T

CK_14M_ICH

CK_48M_ICH

54

7

6

5

4

3

1

10

40

35

36

32

33

29

30

28

27

25

24

22

21

18

17

14

13

PCI2/TME

(PIN4)

PCI3/CFGP

(PIN5)

PCI4/SRC5_EN

(PIN6)

PCI_F5/ITP_EN

(PIN7)

2

CK_14M

CK_33M_ICH_R

CK_33M_PCI2_R

CK_PCI3_STRAP

CK_TME

CK_33M_SIO_R

LPC_CLK_TPM_R

CK_48MCK_48M

CK_48MCK_48M

V_OUT

CK_REFSSCLK_N_GMCH_R

CK_REFSSCLK_P_GMCH_R

CK_PE_100M_N_1PORT_1_R

CK_PE_100M_P_1PORT_1_R

CK_DMI_N_GMCH_R

CK_DMI_P_GMCH_R

CK_PE_100M_N_16PORT_R

CK_PE_100M_P_16PORT_R

CK_DMI_N_ICH_R

CK_DMI_P_ICH_R

CK_SATA_100M_N_ICH_R

CK_SATA_100M_P_ICH_R

CK_PE_100M_N_LAN_R

CK_PE_100M_P_LAN_R

CK_96M_N_GMCH_R

CK_96M_P_GMCH_R

3D3V_CLK 3D3V_CLK3D3V_CLK

CK_33M_ICH_R

CK_33M_PCI2_R

PIN NAME

R3 2K+/-5%R3 2K+/-5%

R11 33

R11 33

*

*

R12 33

R12 33

*

*

R7 33

R7 33

*

*

R8 33

R8 33

*

*

R16 15 +/-1%

R16 15 +/-1%

*

*

R17 15 +/-1%

R17 15 +/-1%

*

*

R18 2K+/-5%R18 2K+/-5%

*

*

*

*

R42

R42

10K

10K

*

*

*

*

R46

R46

10K

10K

Dummy

Dummy

NET

CK_TME

CK_PCI3_STRAP

CK_33M_PCI2_R

CK_33M_ICH_R

FSC

CK_14M_ICH 23

CK_33M_ICH 25

CK_33M_SIO 27

LPC_CLK_TPM 18

CK_48M_SIO 27

CK_48M_ICH 23

FSA

Change 33M clock-0820

R22 33

R22 33

*

*

R24 33

R24 33

*

*

R26 33

R26 33

*

*

R28 33

R28 33

*

*

R19 33

R19 33

*

*

R21 33

R21 33

*

*

R32 33

R32 33

*

*

R33 33

R33 33

*

*

R34 27Ohm +/-1%

R34 27Ohm +/-1%

*

*

R35 27Ohm +/-1%

R35 27Ohm +/-1%

*

*

R36 33

R36 33

*

*

R37 33

R37 33

*

*

R38 33

R38 33

*

*

R39 33

R39 33

*

*

R40 33

R40 33

*

*

R41 33

R41 33

*

*

R43

R43

10K

10K

Reserved

Reserved

R47

R47

10K

10K

Dummy

Dummy

1

0

1

0

1

0

1

0

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

CK_REFSSCLK_N_GMCH 12

CK_REFSSCLK_P_GMCH 12

CK_PE_100M_N_1PORT_1 31

CK_PE_100M_P_1PORT_1 31

CK_DMI_N_GMCH 12

CK_DMI_P_GMCH 12

CK_PE_100M_N_16PORT 22

CK_PE_100M_P_16PORT 22

CK_DMI_N_ICH 23

CK_DMI_P_ICH 23

CK_SATA_100M_N_ICH 24

CK_SATA_100M_P_ICH 24

CK_PE_100M_N_LAN 26

CK_PE_100M_P_LAN 26

CK_96M_N_GMCH 12

CK_96M_P_GMCH 12

*

*

R44

R44

10K

CK_TME

CK_PCI3_STRAP

Strapping description

Overclocking DISABLED

Overclocking ENABLED

CGF TABLE DISABLED

CGF TABLE ENABLED

SRC5

CPU_STOP# and PCI_STOP#

CPU_ITP

SRC8

10K

*

*

R48

R48

10K

10K

Dummy

Dummy

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

CK505 ClockGen

CK505 ClockGen

CK505 ClockGen

Archer

Archer

Archer

1

*

*

R45

R45

10K

10K

Dummy

Dummy

*

*

R49

R49

10K

10K

DEFAULT

DEFAULT

DEFAULT

DEFAULT

737Wednesday, December 09, 2009

737Wednesday, December 09, 2009

737Wednesday, December 09, 2009

AC

AC

AC

Page 8

5

smd.db-x7.ru

3D3V_SYS

PR106

PR106

*

*

1K

1K

+/-5%

+/-5%

Dummy

Dummy

PC91

PC91

*

*

0.1uF

0.1uF

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

D D

C C

B B

A A

VR_READY7,10,23

P_VR_EN10

P_VID010

P_VID110

P_VID210

P_VID310

P_VID410

P_VID510

P_VID610

P_VID710

PR96

PR96

PC74

PC74

12

12

680pF

680pF

+/-1%

+/-1%

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

PR90

PR90

*

*

1K +/-1%

1K +/-1%

*

*

5V_SYS

Dummy PR17 and PR21

for default.

Follow MFG check result.

03/02/09

Place close

to inductor

P_VCC_SENSE10

P_VSS_SENSE10

Fsw= 280kHz

OCP ~170A

NCP5395:PR62-0 ohm

NCP5395T:PR62-1.2K, PR72-use 10K

PR52

PR52

100KOhm

100KOhm

+/-1%

+/-1%

Dummy

Dummy

PR91

PR91

200KOhm

200KOhm

+/-1%

+/-1%

T

T

VRM_GND

VCCP

PR71

PR71

*

*

100

100

+/-5%

+/-5%

PR100

PR100

*

*

100

100

+/-5%

+/-5%

Delete PR42 and PR43.

Connect to VRM_GND.

Follow MFG check result.

03/02/11

P_VID7

P_VID6

P_VID5

P_VID4

P_VID3

P_VID2

P_VID1

P_VID0

PR69 1K

PR69 1K

*

*

PRT3

PRT3

4.7K

4.7K

r0603h10

r0603h10

PR94 1K

PR94 1K

*

*

PC72

PC72

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

Dummy

Dummy

5

PR103

PR103

4.12K

4.12K

*

*

+/-1%

+/-1%

*

*

50V, NPO, +/-5%

50V, NPO, +/-5%

PR66 4.12K

PR66 4.12K

*

*

*

*

+/-1%

+/-1%

*

*

+/-1%

+/-1%

RN1

RN1

*

*

1

3

5

7 8

680 +/-5%

680 +/-5%

RN2

RN2

*

*

1

3

5

7 8

680 +/-5%

680 +/-5%

VR_READY

To prevent CPU power

not stable-062209

P_PSI_N

PC111

PC111

1.8nF

1.8nF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

PC67 22pF

PC67 22pF

+/-1%

+/-1%

*

*

PR86

PR86

1K

1K

+/-1%

+/-1%

PR104

PR104

*

*

470

470

+/-5%

+/-5%

PC75 15nF

PC75 15nF

PC103

PC103

10nF

10nF

*

*

25V, X7R, +/-10%

25V, X7R, +/-10%

Dummy

Dummy

PC107

PC107

*

*

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

Dummy

Dummy

PR108

PR108

*

*

11.5KOhm

11.5KOhm

+/-1%

+/-1%

PR88

PR88

*

*

17.8KOhm

17.8KOhm

+/-1%

+/-1%

VRM_GND

2

4

6

2

4

6

PR8 1K

PR8 1K

For Auto PSI

5V_SYS

PC98

PC98

0.1uF

0.1uF

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

Reserved

Reserved

PU5

PU5

34

VR_RDY

33

EN

3

VID0

4

VID1

5

VID2

6

VID3

7

VID4

8

VID5

9

VID6

10

VID7

2

PSI

16

DIFFOUT

COMP

17

COMP

VFB

18

VFB

19

DROOP

PC104

PC104

*

*

22pF

22pF

50V, NPO, +/-5%

50V, NPO, +/-5%

20

VDFB

PR80

PR80

21

*

*

CSSUM

560 Ohm

560 Ohm

+/-1%

+/-1%

22

DAC

50V, X7R, +/-10%

50V, X7R, +/-10%

*

*

14

VSP

15

VSN

12V_VRM

Change PR62 to 1.2k .

Follow MFG check

result.

03/02/10

VTT_OUT_RIGHT

*

*

Dummy

Dummy

HCPURSTJ9,10,12,34

*

*

PR95

PR95

2.2

2.2

r0805h6

r0805h6

PC82

PC82

+80/-20%

+80/-20%

4.7uF

4.7uF

c0805h14

c0805h14

NCP5395T

ROSC

ILIM

11

12

PR53

PR53

*

*

10K

10K

+/-1%

+/-1%

PR101

PR101

1.2K

1.2K

+/-5%

+/-5%

25V, X7R, +/-10%

25V, X7R, +/-10%

r0402h4

r0402h4

PR117 5.1KOhm

PR117 5.1KOhm

6.3V, X5R, +/-20%

6.3V, X5R, +/-20%

4

12V_VRM

*

*

24

40

VCC

VCCP

GND

PAD_GND

NCP5395TMNR2G

NCP5395TMNR2G

23

49

PC112

PC112

10nF

10nF

*

*

1 2

VRM_GND

C109

C109

10uF

10uF

c0805h14

c0805h14

PR113 1K

PR113 1K

4

PR77

PR77

12V_VCCP

1

1

r0805h6

r0805h6

BST1

SWN1

CS1N

CS1P

BST2

SWN2

CS2N

CS2P

BST3

SWN3

CS3N

CS3P

DRVON

CS4N

CS4P

IMON

BOTTOM PAD

CONNECT TO

GND Through

8 VIAs

PCP7PCP7

+/-1%

+/-1%

*

*

*

*

*

*

TG1

BG1

TG2

BG2

TG3

BG3

G4

PQ28

PQ28

MMBT3904

MMBT3904

sot23_bech11

sot23_bech11

PC110

PC110

+80/-20%

+80/-20%

4.7uF

4.7uF

c0805h14

c0805h14

37

38

39

36

32

31

44

43

42

41

30

29

48

47

46

1

28

27

35

45

26

25

13

B

MMBT3904

MMBT3904

sot23_bech11

sot23_bech11

VCCP

PD5

PD5

CA

BAT54HT1G

BAT54HT1G

PR107 2.2

PR107 2.2

BST1

TG1

SWN1

CS1N

PR63 0

PR63 0

*

*

CS1

PR111 2.43KOhm

PR111 2.43KOhm

PR93

PR93

2.2

2.2

BST2

r0805h6

r0805h6

TG2

SWN2

BG2

CS2N

PR105 0

PR105 0

*

*

CS2

PR58 2.43KOhm

PR58 2.43KOhm

PR68

PR68

2.2

2.2

BST3

r0805h6

r0805h6

TG3

SWN3

BG3

CS3N

PR74 0

PR74 0

*

*

CS3

PR87 2.43KOhm

PR87 2.43KOhm

G4

VCCP

>300us FILTER

PR109

PR109

330Ohm

330Ohm

+/-1%

+/-1%

PC47

PC47

1uF

1uF

*

*

+/-10%

+/-10%

c0603h9

c0603h9

5V_SYS

*

*

*

*

PR112

PR112

1K

1K

5V_SYS

E C

E C

*

*

PR114

PR114

1K

1K

B

Q39

Q39

E C

r0805h6

r0805h6

*

*

+/-1%

+/-1%

PC77

PC77

*

*

220nF

220nF

+/-10%

+/-10%

c0603h9

c0603h9

*

*

+/-1%

+/-1%

PC97

PC97

*

*

220nF

220nF

+/-10%

+/-10%

c0603h9

c0603h9

*

*

+/-1%

+/-1%

*

*

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

PR116

PR116

1K

1K

B

PQ29

PQ29

MMBT3904

MMBT3904

sot23_bech11

sot23_bech11

Q40

Q40

MMBT3904

MMBT3904

sot23_bech11

sot23_bech11

PC117

PC117

220nF

220nF

*

*

+/-10%

+/-10%

c0603h9

c0603h9

Dummy

Dummy

PR73 100KOhm

PR73 100KOhm

*

*

PC101 220nF

PC101 220nF

*

*

PD4

PD4

C A

BAT54HT1G

BAT54HT1G

Dummy

Dummy

PR89 100KOhm

PR89 100KOhm

*

*

PC99 220nF

PC99 220nF

*

*

PD6

PD6

C A

BAT54HT1G

BAT54HT1G

Dummy

Dummy

PR79 100KOhm

PR79 100KOhm

*

*

PC79 220nF

PC79 220nF

*

*

PWR1

PWR1

C12

C12

0.1uF

0.1uF

Hearer_2X2

Hearer_2X2

PWR4NWP1

PWR4NWP1

B

E C

+/-1%

+/-1%

+/-10%

+/-10%

c0603h9

c0603h9

+/-1%

+/-1%

+/-10%

+/-10%

c0603h9

c0603h9

+/-1%

+/-1%

+/-10%

+/-10%

c0603h9

c0603h9

3

5V_SYS

5V_SYS

3

12V_VCCP

12V_VCCP

PR76

PR76

*

*

9.09KOhm

9.09KOhm

+/-1%

+/-1%

PR72

PR72

*

*

1K

1K

+/-1%

+/-1%

5

5

4

*

*

2

1

VCC

74V1G66CTR

74V1G66CTR

2.2

2.2

PR84

PR84

r0805h6

r0805h6

2.2

2.2

PR92

PR92

r0805h6

r0805h6

PR97

PR97

r0805h6

r0805h6

B

E C

PC114

PC114

0.1uF

0.1uF

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

*

*

12V_VRM

4

3

C

2.2

2.2

*

*

PQ23

PQ23

MMBT3904

MMBT3904

sot23_bech11

sot23_bech11

PR99

PR99

33KOhm

33KOhm

+/-1%

+/-1%

Q28

Q28

IO

OI

GND

PR78

PR78

10KOhm

10KOhm

+/-1%

+/-1%

G

PR82

10KOhm

10KOhm

+/-1%

+/-1%

G

PR81

PR81

10KOhm

10KOhm

+/-1%

+/-1%

G

*

*

12

PC80

PC80

150pF

150pF

50V, NPO, +/-5%

50V, NPO, +/-5%

PC83

PC83

33nF

33nF

*

*

+/-10%

+/-10%

PL1

PL1

*

*

1.2uH@100KHz

1.2uH@100KHz

FSB_VTT

1

2

3

PR98

PR98

51KOhm

51KOhm

+/-1%

+/-1%

*

*

PR75

PR75

680

680

*

*

DS

DS

DS

COMP

PR115

PR115

0

0

Dummy

Dummy

PQ16

PQ16

AOD472AL

AOD472AL

PQ26

PQ26

AOD472AL

AOD472AL

PQ27

PQ27

AOD472AL

AOD472AL

VFB

PQ18

PQ18

G

4

DS

G

G

4

DS

G

G

4

DS

G

C1105

C1105

0.1uF

0.1uF

*

*

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

P_PSI_N

P_PSI

2

VIN

5

D

dfn5jah11

dfn5jah11

S

?

?

1

?

?

?

?

2

?

?

?

?

3

?

?

PQ19

PQ19

AOD472AL

AOD472AL

VIN

5

D

PQ24

PQ24

dfn5jah11

dfn5jah11

S

?

?

1

?

?

?

?

2

?

?

?

?

3

?

?

PQ20

PQ20

AOD472AL

AOD472AL

VIN

5

D

PQ22

PQ22

dfn5jah11

dfn5jah11

S

?

?

1

?

?

?

?

2

?

?

?

?

3

?

?

PQ21

PQ21

AOD472AL

AOD472AL

P_PSI 10

2

PC51

PC51

10uF

10uF

*

*

*

*

+/-10%

+/-10%

c1206h18

c1206h18

Reserved

Reserved

PR102

PR102

2.2

2.2

12

r0805h6

r0805h6

PC89

PC89

*

*

2.2nF

2.2nF

c0603h9

c0603h9

CS1

50V, X7R, +/-10%

50V, X7R, +/-10%

Close to L/S MOS

PC92

PC92

10uF

10uF

*

*

*

*

+/-10%

+/-10%

c1206h18

c1206h18

Reserved

ReservedPR82

PR110

PR110

2.2

2.2

12

r0805h6

r0805h6

PC68

PC68

*

*

2.2nF

2.2nF

c0603h9

c0603h9

CS2

50V, X7R, +/-10%

50V, X7R, +/-10%

Close to L/S MOS

PC71

PC71

10uF

10uF

*

*

*

*

+/-10%

+/-10%

c1206h18

c1206h18

Reserved

Reserved

PR83

PR83

2.2

2.2

12

r0805h6

r0805h6

PC100

PC100

*

*

2.2nF

2.2nF

c0603h9

c0603h9

CS3

50V, X7R, +/-10%

50V, X7R, +/-10%

Close to L/S MOS

EC553

EC553

1500uF

1500uF

*

*

16V, +/-20%

16V, +/-20%

ce50d100h220

ce50d100h220

1

PC76

PC76

0.1uF

0.1uF

25V, X7R, +/-10%

25V, X7R, +/-10%

0.8V~1.55V/90A

VCCP

VCCP

PL6

PL6

Choke 300nH

Choke 300nH

*

*

PCP2PCP2

PC69

PC69

0.1uF

0.1uF

25V, X7R, +/-10%

25V, X7R, +/-10%

VCCP

PL5

PL5

Choke 300nH

Choke 300nH

*

*

PCP3PCP3

PC108

PC108

0.1uF

0.1uF

25V, X7R, +/-10%

25V, X7R, +/-10%

VCCP

PL7

PL7

Choke 300nH

Choke 300nH

*

*

PCP5PCP5

EC552

EC552

1500uF

1500uF

*

*

16V, +/-20%

16V, +/-20%

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

*

*

12

PCP1PCP1

CS1N

*

*

*

*

12

PCP4PCP4

*

*

CS2N

*

*

*

*

12

PCP6PCP6

CS3N

*

*

MLCC 22µF ± 20% 17pcs

Northeast corner inside processor socket cavity

01/08/09

Aluminum Polymer

4pcs North of processor - as close to RM keep-out as possible

3pcs East of processor - as close to RM keep-out as possible

01/08/09

VIN

EC554

EC554

1500uF

1500uF

*

*

16V, +/-20%

16V, +/-20%

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

VRD11.1-NCP5395

VRD11.1-NCP5395

VRD11.1-NCP5395

Archer

Archer

Archer

PEC9

PEC9

820uF

820uF

*

*

+/-20%

+/-20%

PEC14

PEC14

820uF

820uF

*

*

+/-20%

+/-20%

PC118

PC118

22uF

22uF

*

*

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

PC81

PC81

22uF

22uF

*

*

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

PC87

PC87

22uF

22uF

*

*

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

PC78

PC78

22uF

22uF

*

*

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

PC109

PC109

22uF

22uF

*

*

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

PC52

PC52

10uF

10uF

*

*

+/-10%

+/-10%

c1206h18

c1206h18

Reserved

Reserved

VCORE OUTPUT

OS-CON CAP

PEC16

PEC16

820uF

820uF

*

*

+/-20%

+/-20%

PEC8

PEC8

820uF

820uF

+/-20%

+/-20%

PC86

PC86

PC70

PC70

22uF

22uF

22uF

22uF

*

*

*

*

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

PC85

PC85

PC96

PC96

22uF

22uF

22uF

22uF

*

*

*

*

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

PC102

PC102

PC93

PC93

22uF

22uF

22uF

22uF

*

*

*

*

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

PC90

PC90

PC84

PC84

22uF

22uF

22uF

22uF

*

*

*

*

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

PC116

PC116

22uF

22uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

837Wednesday, December 09, 2009

837Wednesday, December 09, 2009

837Wednesday, December 09, 2009

1

PEC13

PEC13

820uF

820uF

+/-20%

+/-20%

PC115

PC115

22uF

22uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

PC94

PC94

22uF

22uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

PC105

PC105

22uF

22uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

PC88

PC88

22uF

22uF

6.3V,X5R,+/-10%

6.3V,X5R,+/-10%

PEC17

PEC17

820uF

820uF

*

*

+/-20%

+/-20%

ACustom

ACustom

ACustom

Page 9

5

smd.db-x7.ru

4

3

2

1

HDJ[63..0]

HDJ[63..0] 12

CPU_1B

CPU_1B

2 OF 7

D D

C C

VTT_OUT_RIGHT VTT_OUT_RIGHT

R57

R57

*

*

57.6

57.6

+/-1%

+/-1%

CPU_GTLREF0_DIVIDER

C30

C30

*

*

1uF

1uF

c0603h9

c0603h9

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

B B

C34

C34

*

*

1uF

1uF

c0603h9

c0603h9

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

Dummy

Dummy

*

*

FSB_VTT

*

*

*

*

R64

R64

100

100

+/-1%

+/-1%

R71

R71

57.6

57.6

+/-1%

+/-1%

Dummy

Dummy

R78

R78

100

100

+/-1%

+/-1%

Dummy

Dummy

R60 10

R60 10

R75 10

R75 10

HDJ0

HDJ1

HDJ2

HDJ3

HDJ4

HDJ5

HDJ6

HDJ7

HDJ8

HDJ9

HDJ10

HDJ11

HDJ12

HDJ13

HDJ14

HDJ15

HDBIJ012

HDSTBNJ012

HDSTBPJ012

HDJ16

HDJ17

HDJ18

HDJ19

HDJ20

HDJ21

HDJ22

HDJ23

HDJ24

HDJ25

HDJ26

HDJ27

HDJ28

HDJ29

HDJ30

HDJ31

HDBIJ112

HDSTBNJ112

HDSTBPJ112

GTLREF voltage should be 0.67*VTT

12 mils width, 15 mils spacing

divider should be within 1.5" of the GTLREF pin

0.22nF caps should be placed near CPU pin

place series resistor as close to divider

*

*

*

*

*

*

Dummy

Dummy

*

*

C31

C31

220pF

220pF

50V, NPO, +/-5%

50V, NPO, +/-5%

Dummy

Dummy

CPU_GTLREF3CPU_GTLREF3_DIVIDER

C35

C35

220pF

220pF

50V, NPO, +/-5%

50V, NPO, +/-5%

Dummy

Dummy

B4

C5

A4

C6

A5

B6

B7

A7

A10

A11

B10

C11

D8

B12

C12

D11

A8

C8

B9

G9

F8

F9

E9

D7

E10

D10

F11

F12

D13

E13

G13

F14

G14

F15

G15

G11

G12

E12

CPU_Conroe_Rev1.0_LGA775

CPU_Conroe_Rev1.0_LGA775

cpu_lga775h67

cpu_lga775h67

D00#

D01#

D02#

D03#

D04#

D05#

D06#

D07#

D08#

D09#

D10#

D11#

D12#

D13#

D14#

D15#

DBI0#

DSTBN0#

DSTBP0#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

DBI1#

DSTBN1#

DSTBP1#

*

*

2 OF 7

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DBI2#

DSTBN2#

DSTBP2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBI3#

DSTBN3#

DSTBP3#

R69

R69

0

0

G16

E15

E16

G18

G17

F17

F18

E18

E19

F20

E21

F21

G21

E22

D22

G22

D19

G20

G19

D20

D17

A14

C15

C14

B15

C18

B16

A17

B18

C21

B21

B19

A19

A22

B22

C20

A16

C17

HDJ32

HDJ33

HDJ34

HDJ35

HDJ36

HDJ37

HDJ38

HDJ39

HDJ40

HDJ41

HDJ42

HDJ43

HDJ44

HDJ45

HDJ46

HDJ47

HDBIJ2 12

HDSTBNJ2 12

HDSTBPJ2 12

HDJ48

HDJ49

HDJ50

HDJ51

HDJ52

HDJ53

HDJ54

HDJ55

HDJ56

HDJ57

HDJ58

HDJ59

HDJ60

HDJ61

HDJ62

HDJ63

HDBIJ3 12

HDSTBNJ3 12

HDSTBPJ3 12

C32

C32

*

*

1uF

1uF

c0603h9

c0603h9

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

C36

C36

*

*

1uF

1uF

c0603h9

c0603h9

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

Dummy

Dummy

*

*

R58

R58

49.9

49.9

+/-1%

+/-1%

R65

R65

*

*

100

100

+/-1%

+/-1%

VTT_OUT_LEFT

*

*

R72

R72

49.9

49.9

+/-1%

+/-1%

Dummy

Dummy

R79

R79

*

*

100

100

+/-1%

+/-1%

Dummy

Dummy

R61 10

R61 10

*

*

R76 10

R76 10

*

*

Dummy

Dummy

CPU_GTLREF1CPU_GTLREF1_DIVIDERCPU_GTLREF0

C33

C33

*

*

220pF

220pF

50V, NPO, +/-5%

50V, NPO, +/-5%

Dummy

Dummy

C37

C37

*

*

220pF

220pF

50V, NPO, +/-5%

50V, NPO, +/-5%

Dummy

Dummy

HAJ[35..3]

HAJ[35..3]12

CPU_GTLREF2CPU_GTLREF2_DIVIDER

HAJ[35..3]

HAJ[35..3]12

HREQJ[4..0]12

HAJ3

HAJ4

HAJ5

HAJ6

HAJ7

HAJ8

HAJ9

HAJ10

HAJ11

HAJ12

HAJ13

HAJ14

HAJ15

HAJ16

TP_CPU_N4

TP3TP3

TP_CPU_P5

TP5TP5

HREQJ0

HREQJ1

HREQJ2

HREQJ3

HREQJ4

HADSTBJ012

HAJ17

HAJ18

HAJ19

HAJ20

HAJ21

HAJ22

HAJ23

HAJ24

HAJ25

HAJ26

HAJ27

HAJ28

HAJ29

HAJ30

HAJ31

HAJ32

HAJ33

HAJ34

HAJ35

TP_CPU_AC4

TP14TP14

TP_CPU_AE4

TP15TP15

HADSTBJ112

CPU_1A

CPU_1A

L5

A03#

P6

A04#

M5

A05#

L4

A06#

M4

A07#

R4

A08#

T5

A09#

U6

A10#

T4

A11#

U5

A12#

U4

A13#

V5

A14#

V4

A15#

W5

A16#

N4

RSVD1

P5

RSVD2

K4

REQ0#

J5

REQ1#

M6

REQ2#

K6

REQ3#

J6

REQ4#

R6

ADSTB0#

TESTHI_10

AB6

A17#

W6

A18#

Y6

A19#

Y4

A20#

AA4

A21#

AD6

A22#

AA5

A23#

AB5

A24#

AC5

A25#

AB4

A26#

AF5

A27#

AF4

A28#

AG6

A29#

AG4

A30#

AG5

A31#

AH4

A32#

AH5

A33#

AJ5

A34#

AJ6

A35#

AC4

RSVD3

AE4

RSVD4

AD5

ADSTB1#

CPU_Conroe_Rev1.0_LGA775

CPU_Conroe_Rev1.0_LGA775

cpu_lga775h67

cpu_lga775h67

1 OF 7

1 OF 7

ADS#

BNR#

HIT#

FC35

BPRI#

DBSY#

DRDY#

HITM#

IERR#

INIT#

LOCK#

TRDY#

FC36

DEFER#

FC37

FC29

FC30

BR0#

BPMB0#

BPMB1#

BPMB2#

BPMB3#

FC31

FC32

FC33

FC34

GTLREF0

GTLREF1

GTLREF2

GTLREF3

FC10

FC15

RESET#

RS0#

RS1#

RS2#

D2

C2

D4

TP_CPU_H4

H4

G8

B2

C1

E4

AB2

P3

C3

E3

TP_CPU_AD3

AD3

G7

TP_CPU_AB3

AB3

TP_CPU_U2

U2

TP_CPU_U3

U3

HBR0J

F3

BPMB0J

G1

BPMB1J

C9

BPMB2J

G4

BPMB3J

G3

TESTHI_10

H5

TP_CPU_J16

J16

TP_CPU_H15

H15

TP_CPU_H16

H16

TP_CPU_J17

J17

CPU_GTLREF0

H1

CPU_GTLREF1

H2

CPU_GTLREF2

F2

CPU_GTLREF3

G10

TP_CPU_E24

E24

TP_CPU_H29

H29

G23

B3

F5

A3

HADSJ 12

HBNRJ 12

HITJ 12

TP1TP1

HBPRIJ 12

HDBSYJ 12

HDRDYJ 12

HITMJ 12

HIERRJ 10

INITJ 24

HLOCKJ 12

HTRDYJ 12

TP2TP2

HDEFERJ 12

TP4TP4

TP6TP6

TP7TP7

HBR0J 10,12

BPMB0J 10

BPMB1J 10

BPMB2J 10

BPMB3J 10

TESTHI_10 10

TP8TP8

TP9TP9

TP10TP10

TP11TP11

TP12TP12

TP13TP13

HCPURSTJ 8,10,12,34

HRSJ0 12

HRSJ1 12

HRSJ2 12

Reserved for CPU_GTLREF Adjusting

12V_SYS

3D3V_AUX

*

*

R63

R63

10K

10K

Dummy

Dummy

R66 1K

R66 1K

B

*

*

*

R77

R77

10K

10K

Dummy

Dummy

R80 1K

R80 1K

*

B

*

*

R70

R70

*

*

0

0

CPU_GTLREF_CTRL123

CT2CT1 GTLREF

00 0.615 x VTT

01 0.630 x VTT

10 0.650 x VTT

11 0.670 x VTT

CPU_GTLREF_CTRL223

Default

3D3V_AUX

Q9

Q9

MMBT3904

MMBT3904

sot23_bech11

sot23_bech11

E C

Q11

Q11

MMBT3904

MMBT3904

sot23_bech11

sot23_bech11

E C

12V_SYS

*

*

R62

R62

DS

1K

1K

G

R67

R67

1.3K

1.3K

+/-1%

+/-1%

*

*

R74

R74

DS

1K

1K

G

R81

R81

576

576

+/-1%

+/-1%

R0603

R0603

Q8

2N7002Q82N7002

Q10

Q10

2N7002

2N7002

R68

R68

0

0

R59 0

R59 0

Dummy

Dummy

*

*

R73 0

R73 0

*

*

*

*

CPU_GTLREF0_DIVIDER

CPU_GTLREF1_DIVIDER

A A

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

FOXCONN PCEG

LGA775 -1

LGA775 -1

LGA775 -1

Archer

Archer

Archer

1

937Wednesday, December 09, 2009

937Wednesday, December 09, 2009

937Wednesday, December 09, 2009

AC

AC

AC

Page 10

5

smd.db-x7.ru

CPU_1C

CPU_1C

MS_ID1

MS_ID0

CPU_BOOT

R90

R90

51

51

P2

SMI#

K3

A20M#

R3

FERR#/PBE#

K1

LINT0

L1

LINT1

N2

IGNNE#

M3

STPCLK#

A23

VCCA

B23

VSSA

C23

VCCIOPLL

D23

VCC_PLL

AM2

VID0

AL5

VID1

AM3

VID2

AL6

VID3

AK4

VID4

AL4

VID5

AM5

VID6

AM7

VID7

AN7

VID_SELECT

F28

BCLK0

G28

BCLK1

AE8

SKTOCC#

G5

PECI

AL1

THERMDA

AK1

THERMDC

AN3

VCC_SENSE

AN4

VSS_SENSE

AN5

VCC_MB_REG

AN6

VSS_MB_REG

AL8

VCCP4

AL7

VSS186

AL3

VRDSEL

V1

MSID1

W1

MSID0

Y1

BOOTSELECT

CPU_Conroe_Rev1.0_LGA775

CPU_Conroe_Rev1.0_LGA775

cpu_lga775h67

cpu_lga775h67

SMIJ24

A20MJ24

FERRJ24

INTR24

NMI24

IGNNEJ24

STPCLKJ24

D D

C C

1D5V_ICH

B B

Follow Intel Recommendation

P_VID08

P_VID18

P_VID28

P_VID38

P_VID48

P_VID58

P_VID68

CPU_THERMDA27

CPU_THERMDC27

P_VCC_SENSE8

P_VSS_SENSE8

HVCCPLL

12

*

*

P_VID78

CK_P_CPU7

CK_N_CPU7

TP23TP23

TP25TP25

TP29TP29

TP31TP31

TP35TP35

C45

C45

*

*

10nF

10nF

25V, X7R, +/-10%

25V, X7R, +/-10%

VID_SELECT

R97 0

R97 0

*

*

R0603

R0603

C44

C44

10uF

10uF

c0805h14

c0805h14

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

placed near pin D23, within 500 mils

HVCCPLL

TP16TP16

PECI27

TP_CPU_AL8

TP_CPU_AL7

TP_CPU_AL3

*

*

A A

5

3 OF 7

3 OF 7

TESTHI_0

TESTHI_1

TESTHI_2

TESTHI_3

TESTHI_4

TESTHI_5

TESTHI_6

TESTHI_7

DPSLP#

SLP#

TDI_M

TDO_M

PWRGOOD

PROCHOT#

THERMTRIP#

COMP0

COMP1

COMP2

COMP3

DPRSTP#

FC17

FC18

COMP8

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

FC39

FC26

FC23

FC22

FC21

FC20

4

TESTHI_0

F26

TESTHI_1

W3

F25

G25

G27

G26

G24

F24

AK6

FC8

P1

L2

W2

TESTHI_M

U1

N1

PROCHOTJ

AL2

H_THERMTRIPJ

M2

HCOMP0

A13

HCOMP1

T1

HCOMP2

G2

HCOMP3

R1

HCOMP4

J2

FC3

PM_DPRSTP#

T2

P_PSI

Y3

HCOMP7

AE3

HCOMP8

B13

TP_CPU_F29

F29

TP_CPU_G6

G6

TP_CPU_AH2

AH2

TP_CPU_N5

N5

TP_CPU_AE6

AE6

TP_CPU_D16

D16

TP_CPU_A20

A20

TP_CPU_E23

E23

TP_CPU_F23

F23

TP_CPU_V2

V2

TP_CPU_E7

E7

TP_CPU_D14

D14

TP_CPU_E6

E6

TP_CPU_D1

D1

TP_CPU_AA2

AA2

TP_CPU_E29

E29

TP_CPU_A24

A24

TP_CPU_J3

J3

TP_CPU_F6

F6

TP_CPU_E5

E5

Follow Intel Recommendation

4

TESTHI_2_7

DPSLP#

PM_SLP

CPU_PWRG 23

R83 0

R83 0

*

*

PM_DPRSTP# 12

P_PSI 8

TP17TP17

TP18TP18

TP19TP19

TP20TP20

TP21TP21

TP22TP22

TP24TP24

TP26TP26

TP27TP27

TP28TP28

TP30TP30

TP32TP32

TP33TP33

TP34TP34

TP36TP36

TP37TP37

R86 1K Dummy

R86 1K Dummy

*

*

R87 1K Dummy

R87 1K Dummy

*

*

R89 51

R89 51

*

*

R88 1K Dummy

R88 1K Dummy

*

*

FSB_VTT

VTT_OUT_RIGHT

VTT_OUT_LEFT

FSB_VTT

PROCHOTJ 23

THERMTRIPJ 24

R92 51

R92 51

*

*

R95 51

R95 51

*

*

R100 62

R100 62

*

*

R101 62

R101 62

*

*

R103 130

+/-1%

+/-1%

R105 49.9

R105 49.9

*

*

+/-1%

+/-1%

R272 680

R272 680

*

*

R107 62

R107 62

*

*

R110 100 Dummy

R110 100 Dummy

*

*

RN6

RN6

*

*

1

2

3

4

5786

R113 49.9

R113 49.9

*

*

+/-1%

+/-1%

R111 51 Reserved

R111 51 Reserved

*

*

R112 51 Reserved

R112 51 Reserved

*

*

R114 49.9

R114 49.9

*

*

+/-1%

+/-1%

R104 49.9

R104 49.9

*

*

+/-1%

+/-1%

R115 49.9

R115 49.9

*

*

+/-1%

+/-1%

R116 49.9

R116 49.9

*

*

+/-1%

+/-1%

R117 49.9

R117 49.9

*

*

+/-1%

+/-1%

R118 49.9

R118 49.9

*

*

+/-1%

+/-1%

R119 24.9

R119 24.9

*

*

+/-1%

+/-1%

TESTHI_0

TESTHI_2_7

HIERRJ

HCPURSTJ

51

51

+/-5%

+/-5%

Dummy

Dummy

Reserved

Reserved

Reserved

Reserved

DummyR103 130

Dummy

Dummy

Dummy

3

PROCHOTJ

HCOMP7

VID_SELECT

HBR0J 9,12

CPU_PWRG

TESTHI_10

TESTHI_M

TESTHI_1

HCOMP4

DPSLP#

PM_SLP

PM_DPRSTP#

P_PSI

HCOMP0

HCOMP1

HCOMP2

HCOMP3

HCOMP8

3

If not used, pull up through 51 to 1k ohm

to vtt_out_right or ground respectively,i.e

reserved the termination circuit

HTCK34

HTDI34

HTDO34

HTMS34

HTRSTJ34

HBPM0J34

HBPM1J34

HBPM2J34

HBPM3J34

HBPM4J34

HBPM5J34

FP_RSTJ23,32,34

FSBSEL07,12

FSBSEL17,12

FSBSEL27,12

HIERRJ 9

HCPURSTJ 8,9,12,34

VTT_OUT_LEFT

TESTHI_10 9

R679 0 +/-5%

R679 0 +/-5%

*

*

Dummy

Dummy

CPUSLPJ 24

HTCK

HTDI

HTDO

HTMS

HTRSTJ

HBPM0J

HBPM1J

HBPM2J

HBPM3J

HBPM4J

HBPM5J

FP_RSTJ

FSBSEL0

FSBSEL1

FSBSEL2

CPU_1D

CPU_1D

AE1

TCK

AD1

TDI

AF1

TDO

AC1

TMS

AG1

TRST#

AJ2

BPM0#

AJ1

BPM1#

AD2

BPM2#

AG2

BPM3#

AF2

BPM4#

AG3

BPM5#

AC2

DBR#

AK3

ITPCLK0

AJ3

ITPCLK1

G29

BSEL0

H30

BSEL1

G30

BSEL2

CPU_Conroe_Rev1.0_LGA775

CPU_Conroe_Rev1.0_LGA775

cpu_lga775h67

cpu_lga775h67

MS_ID0

MS_ID1

VTT_OUT_RIGHT

VTT_OUT_RIGHT

FSB_VTT

4 OF 7

4 OF 7

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

FC40

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL

*

*

R98

R98

51

51

Dummy

Dummy

RN3

RN3

*

*

1

2

3

4

5786

51

51

+/-5%

+/-5%

RN4

RN4

4

2

51

51

+/-5%

+/-5%

RN7

RN7

*

*

1

3

5

7 8

470

470

+/-5%

+/-5%

2

FSB_VTT

A29

B25

B29

B30

C29

A26

B27

C28

A25

A28

A27

C30

A30

C25

C26

C27

B26

D27

D28

D25

D26

B28

D29

D30

AM6

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

VTT_SEL

F27

R93 0 Dummy

R93 0 Dummy

R96 0

R96 0

*

*

R99

R99

51

51

Dummy

Dummy

HBPM5J

HBPM4J

BPMB2J

BPMB3J

HBPM2J

HBPM0J

5786

HBPM3J

3

*

*

HBPM1J BPMB1J

1

FSBSEL0

2

FSBSEL1

4

FSBSEL2

6

2

*

*

TPEC_VCC

VTT_OUT_RIGHT

R85

R85

*

*

1K

1K

VTT_SEL 19

VTT_SEL VTT

No Connect 1.2V

1.2V 1.2V

Vss 1.1V

*

*

*

*

Dummy

Dummy

BOM Note:

1.Stuff R108 for 95W YORKFIELD support

2.Stuff R109 for 65W CONROE/WOLFDALE support

3.Empty Q6 for VTT tool test

4.Reserve R110 and R111 for CPU support before CONROE

BPMB2J 9

BPMB3J 9

RN5 0

RN5 0

1

*

*

3

5

7 8

8P4R0603

8P4R0603

Dummy

Dummy

Reserve for Kentsfield CPU support

R82

R82

0

0

C38

C38

*

*

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

VTT_OUT_RIGHT

R94

R94

*

*

1K

1K

Dummy

Dummy

B

2

4

6

1

R84 0

R84 0

*

*

VR_READY 7,8,23

VTT_OUT_RIGHT VTT_OUT_LEFT

C40

C42

C42

*

*

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

R91

R91

100

100

Q12

Q12

*

*

MMBT3904

MMBT3904

sot23_bech11

sot23_bech11

E C

Dummy

Dummy

BPMB2J

BPMB0J

BPMB3J

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

C40

C39

C39

*

*

*

*

0.1uF

0.1uF

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

P_VR_EN 8

C43

C43

0.1uF

0.1uF

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

Dummy

Dummy

VTT_OUT_LEFT

*

*

R108

R108

51

51

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

LGA775 -2

LGA775 -2

LGA775 -2

Archer

Archer

Archer

C41

C41

*

*

0.1uF

0.1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

16V, X7R, +/-10%

*

*

R109

R109

51

51

BPMB0J 9

BPMB1J 9

10 37Wednesday, December 09, 2009

10 37Wednesday, December 09, 2009

1

10 37Wednesday, December 09, 2009

AC

AC

AC

Page 11

5

smd.db-x7.ru

4

3

2

1

CPU_1E

CPU_1E

5 OF 7

AG22

K29

AM26

AE12

D D

C C

B B

AE11

AC25

AN14

AD28

AC29

AC27

AM18

AM19

AC26

AF15

AE14

AC24

AC23

AN26

AN25

AN11

AN18

AD24

AE23

AE22

AN19

AE21

AM30

AE19

AC30

AE15

AN21

AC28

AE18

AD25

AD26

AM29

AD27

AG29

AM22

AK18

AH28

AH21

W23

W24

W25

AL18

W30

AM9

W29

W26

AJ26

AJ12

T25

Y28

Y30

Y26

M29

U24

J23

AB8

J8

J28

T30

AC8

N23

U29

Y23

Y27

Y25

V8

K8

M30

K27

M24

T8

N25

M8

N30

M25

M26

L8

U25

Y8

U23

M23

N27

U28

K28

U8

AD8

K24

5 OF 7

VCCP1

VCCP93

VCCP2

VCCP94

VCCP3

VCCP95

VCCP5

VCCP96

VCCP6

VCCP97

VCCP7

VCCP98

VCCP8

VCCP99

VCCP9

VCCP100

VCCP10

VCCP101

VCCP11

VCCP102

VCCP12

VCCP103

VCCP13

VCCP104

VCCP14

VCCP105

VCCP15

VCCP106

VCCP16

VCCP107

VCCP17

VCCP108

VCCP18

VCCP109

VCCP19

VCCP110

VCCP20

VCCP111

VCCP21

VCCP112

VCCP22

VCCP113

VCCP23

VCCP114

VCCP24

VCCP115

VCCP25

VCCP116

VCCP26

VCCP117

VCCP27

VCCP118

VCCP28

VCCP119

VCCP29

VCCP120

VCCP30

VCCP121

VCCP31

VCCP122

VCCP32

VCCP123

VCCP33

VCCP124

VCCP34

VCCP125

VCCP35

VCCP126

VCCP36

VCCP127

VCCP37

VCCP128

VCCP38

VCCP129

VCCP39

VCCP130

VCCP40

VCCP131

VCCP41

VCCP132

VCCP42

VCCP133

VCCP43

VCCP134

VCCP44

VCCP135

VCCP45

VCCP136

VCCP46

VCCP137

VCCP47

VCCP138

VCCP48

VCCP139

VCCP49

VCCP140

VCCP50

VCCP141

VCCP51

VCCP142

VCCP52

VCCP143

VCCP53

VCCP144

VCCP54

VCCP145

VCCP55

VCCP146

VCCP56

VCCP147

VCCP57

VCCP148

VCCP58

VCCP149

VCCP59

VCCP150

VCCP60

VCCP151

VCCP61

VCCP152

VCCP62

VCCP153

VCCP63

VCCP154

VCCP64

VCCP155

VCCP65

VCCP156

VCCP66

VCCP157

VCCP67

VCCP158

VCCP68

VCCP159

VCCP69

VCCP160

VCCP70

VCCP161

VCCP71

VCCP162

VCCP72

VCCP163

VCCP73

VCCP164

VCCP74

VCCP165

VCCP75

VCCP166

VCCP76

VCCP167

VCCP77

VCCP168

VCCP78

VCCP169

VCCP79

VCCP170

VCCP80

VCCP171

VCCP81

VCCP172

VCCP82

VCCP173

VCCP83

VCCP174

VCCP84

VCCP175

VCCP85

VCCP176

VCCP86

VCCP177

VCCP87

VCCP178

VCCP88

VCCP179

VCCP89

VCCP180

VCCP90

VCCP181

VCCP91

VCCP182

VCCP92

VCCP183

VCCP184

CPU_Conroe_Rev1.0_LGA775

CPU_Conroe_Rev1.0_LGA775

cpu_lga775h67

cpu_lga775h67

AK12

AH22

T29

AM14

AM25

AE9

Y29

AK25

AK19

AG15

J22

T24

AG21

AM21

J25

U30

AL21

AG25

AJ18

J19

AH30

J15

AG12

AJ22

J20

AH18

AH26

W27

AL25

AN8

AH14

U27

T23

R8

AK22

AN29

AG11

AK26

J10

AJ15

AG26

AN9

AH15

AF18

AL15

J26

J18

J21

AG27

AK15

AF11

AD23

AM15

AF8

AK21

AG30

AJ21

AM11

AL11

AJ11

K30

AL14

AN30

AH25

AL12

AJ9

AK11

AG14

N29

AL30

AJ25

AH9

J29

J11

K25

P8

K23

AL19

AM8

T26

N28

AH12

AL22

AN15

AJ8

U26

AJ19

T27

AK8

AN12

AG9

N26

VCCPVCCP VCCP

CPU_1F

CPU_1F

AF9

VCCP185

AF22

VCCP186

AH11

VCCP187

AJ14

VCCP188

AH19

VCCP189

AH29

VCCP190

AH27

VCCP191

AG28

VCCP192

AL26

VCCP193

AM12

VCCP194

J24

VCCP195

J13

VCCP196

T28

VCCP197

W28

VCCP198

J12

VCCP199

J27

VCCP200

AG19

VCCP201

AL9

VCCP202

AD30

VCCP203

AF21

VCCP204

Y24

VCCP205

AK14

VCCP206

J9

VCCP207

M27

VCCP208

AF14

VCCP209

J30

VCCP210

AG18

VCCP211

AA8

VCCP212

AG8

VCCP213

AL29

VCCP214

AD29

VCCP215

W8

VCCP216

AH8

VCCP217

N24

VCCP218

AN22

VCCP219

J14

VCCP220

K26

VCCP221

AF19

VCCP222

N8

VCCP223

AF12

VCCP224

M28

VCCP225

AK9

VCCP226

C10

VSS1

D12

VSS2

C24

VSS4

K2

VSS5

C22

VSS6

AN1

VSS7

B14

VSS8

K7

VSS9

AE16

VSS10

B11

VSS11

AL10

VSS12

AK23

VSS13

H12

VSS14

AF7

VSS15

AK7

VSS16

H7

VSS17

E14

VSS18

L28

VSS19

Y5

VSS20

E11

VSS21

AL16

VSS22

AL24

VSS23

AK13

VSS24

D21

VSS26

AL20

VSS27

D18

VSS28

AN2

VSS29

AK16

VSS30

AK20

VSS31

AM27

VSS32

AM1

VSS33

AL13

VSS34

AL17

VSS35

C19

VSS36

E28

VSS37

AH7

VSS38

AK30

VSS39

D24

VSS40

CPU_Conroe_Rev1.0_LGA775

CPU_Conroe_Rev1.0_LGA775

cpu_lga775h67

cpu_lga775h67

6 OF 7

6 OF 7

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

AL23

A12

L25

J7

AE28

AE29

K5

J4

AE30

AN20

AF10

AE24

AM24

AN23

H9

H8

H13

AC6

AC7

AH6

C16

AM16

AE25

AE27

AJ28

AJ7

F19

AH13

AD7

AH16

AK17

E17

AH17

AH20

AE5

AH23

AE7

AM13

AH24

AJ30

AJ10

AF3

AK5

AJ16

AF6

AK29

AJ17

F22

AH3

AK10

AM10

F16

AJ23

F13

AG7

F10

L26

AD4

H11

L24

L23

AM23

A15

AH10

B24

L3

H27

A21

AE2

AJ29

AK27

AK28

B20

AM20

H26

B17

H25

H24

AA3

AA7

H23

AA6

H10

CPU_1G

CPU_1G

H22

VSS126

H21

VSS127

H20

VSS128

H19

VSS129

H18

VSS130

AB7

VSS131

H17

VSS132

AJ24

VSS133

AM17

VSS134

AC3

VSS135

H14

VSS136

P28

VSS137

V6

VSS138

AK2

VSS139

P27

VSS140

P26

VSS141

AM28

VSS142

AJ13

VSS143

W4

VSS144

P25

VSS145

AJ20

VSS146

W7

VSS147

P23

VSS148

AG13

VSS149

AG16

VSS150

AG17

VSS151

C7

VSS152

Y2

VSS153

L30

VSS154

L29

VSS155

D15

VSS156

AL27

VSS157

Y7

VSS158

L27

VSS159

AA29

VSS160

N6

VSS161

N7

VSS162

AA28

VSS163

AN13

VSS164

AA27

VSS165

AA26

VSS166

P4

VSS167

AA25

VSS168

AA24

VSS169

P7

VSS170

E26

VSS171

V30

VSS172

R2

VSS173

V29

VSS174

V28

VSS175

R5

VSS176

V27

VSS177

R7

VSS178

E20

VSS179

AN10

VSS180

V25

VSS181

T3

VSS182

V24

VSS183

V23

VSS184

T6

VSS185

E25

VSS187

R29

VSS189

R28

VSS190

R27

VSS191

R26

VSS192

R25

VSS193

U7

VSS194

R24

VSS195

R23

VSS196

P30

VSS197

V3

VSS198

P29

VSS199

AF16

VSS200

CPU_Conroe_Rev1.0_LGA775

CPU_Conroe_Rev1.0_LGA775

cpu_lga775h67

cpu_lga775h67

7 OF 7

7 OF 7

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

AE10

AF13

H6

A18

A2

E2

D9

C4

A6

D6

D5

A9

D3

B1

B5

B8

AJ4

AE26

AH1

V7

C13

AK24

AB30

L6

L7

AB29

M1

AB28

E8

AG20

AN17

AB27

AB26

AN16

M7

AB25

AB24

AB23