Page 1

FLUKE 900

SERVICE MANUAL

NOTE: This manual documents FLUKE900 instruments S/N 4720000 and above.

It also documents any FLUKE 900 vnth the Simulation Option (900-001) installed.

Print Date: September 1992

MN-0004

FLUKE P/N 889691

(c) Copyright 1992

All rights reserved

ZTEST Electronics Inc.

1305 Matheson Blvd.

Mississauga, Ontario

Canada L4W1R1

Page 2

Page 3

Table of Contents

1 Service Manual Introduction.................................................................................................................. 1-1

1.1 Description of Operator, Service Manuals .................................................................................. 1-1

1.2 Basic Operation of Keyboard and Display

2 Theory of Operation................................................................................................................................ 2-1

2.1 General............................................................................................................................................. 2-1

2.2 Interface Buffer.............................................................................................................................. 2-2

2.3 Micro Board................................................................................................................................... 2-3

2.4 High Speed Board.........................................................................................................................

2.5 Test Clips........................................................................................................................................ 2-11

3 Selftest........................................................................................................................................................ 3-1

3.1 Reading Selftest Results................................................................................................................

3.1.1 General Selftest Results....................................................................................................... 3-2

3.1.2 Rag Results........................................................................................................................... 3-3

3.1.3 Chip Size LED Error Codes................................................................................................. 3-5

3.2 Running and Reading Individual Selftests................................................................................... 3-6

3.3 Individual Selftest Descriptions.................................................................................................... 3-6

TEST 0 SLFT_CLIP........................................................................................................................ 3 - 6

TESTS 1,2 PULLO_MON, PULLl_MON..................................................................................... 3 - 7

TESTS3,4PULL0_FLT,PULL1_FLT.............................................................................................. 3-7

TESTS5,6SYNCO_Hres_FLT,SYNCl_Hres_FLT

TESTS 7,8 SYNCO Lres FLT, SYNCl Lres_FLT........................................................................... 3 - 7

TESTS 9,10 PINDIS0_FET, PINDIS1_FLT

TESTS 11,12SLFrSTO_FLT,SLFTSTl_FLT................................................................................... 3-7

TESTS 13,14 VccON_FLT, GndON_FLT

TEST 15 PULLPOS FREQ............................................................................................................. 3 - 8

TESTS 16,17 TRIGOALO_EQUAL, TRIGQAL1_EQUAL.......................................................... 3 - 8

TESTS 18,19 QALO EQUAL, QALl EQUAL .............................................................................. 3 - 8

TESTS 20,21 TRIGiT EQUAL, TRIG1_EQUAL.......................................................................... 3 - 8

TESTS 22,23 PULLO_TRIG_EQUAL, PULL1_TRIG_EQUAL

TEST 24 PULL0_TRIGQAL.......................................................................................................... 3 - 8

TESTS 25,26 FM_STAT_NFLT, FM_STAT_FLT......................................................................... 3 - 9

TEST 27 FMASK_WB_TEST........................................................................................................ 3 - 9

TEST 28 FMASK CAL................................................................................................................... 3 - 9

TESTS 29,31,33,35,37,39 FMxx_FLT

TESTS 30,32,34,36,38,40 FMxx_NFLT......................................................................................... 3 - 9

TEST 41 ACT_DIS_CLR...............................................................................................................

TESTS 42,43 PULLO_ACT_TSTON, PULL1_ACT_TSTQN....................................................... 3 -10

TESTS 44,45 PULL0_ACT ACTSTR, PULL1_ACT_ACTSTR

TESTS 46,47 FREQ_BIAS_'§HORT, FREQ_BIAS_LONG

Interface Buffer shift register subtest.................................................................................... 3-10

Frequency HW subtest.......................................................................................................... 3-11

Threshold HW subtest........................................................................................................... 3-11

Reset HW subtest................................................................................................................... 3-11

Result bytes: ........................................................................................................................... 3-12

TEST 48 KEYBQARD OPEN........................................................................................................ 3 - 14

TEST49TEST_CYCLE................................................................................................................... 3-14

TEST50UART_TEST..................................................................................................................... 3-16

TEST 51 DGATE_TEST................................................................................................................ 3 -17

TEST 52 PULLO XTRIG

..............................................................................................................

.................................................................................. 1-1

2-6

3-1

.........................................................................

..................................................................................

.................................................................................... 3 - 7

..................................................

........................................................................................... 3 - 9

....................................................

.........................................................

3-7

3 - 7

3 - 8

3 - 9

3 -10

3-10

3 - 19

Page 4

Page 5

TEST 53 PULLl XTRIG................................................................................................................. 3 - 20

TEST 54 PULL_XEVENT.............................................................................................................

TEST55SHADINIT........................................................................................................................ 3-21

TEST E60 WALK_SIZELEDS....................................................................................................... 3 - 22

TESTE61 TESTMEMORY............................................................................................................ 3-22

TESTE62WALKMONLEDS......................................................................................................... 3-23

TEST E63 UPDATE VCC LIM..................................................................................................... 3 - 23

TEST E64 SHAD ADDR .7........................................................................................................... 3 - 24

TESTE70KEY_CLOSURE............................................................................................................. 3-24

TEST E71 DISP_RAM................................................................................................................... 3 - 24

TESTE74DISP_CHAR_SET

TESTE75CART_SLFT................................................................................................................... 3-25

TEST E76 TEST C ENG................................................................................................................. 3 - 25

TEST E77 ACT_CROSS................................................................................................................ 3 - 25

TESTE78TRG_CROSS................................................................................................................ 3-26

TESTE79FRQ_CROSS.................................................................................................................. 3-26

TEST E80 FLT_CROSS.................................................................................................................. 3 - 26

3.4 System Error Codes.................................................................................................................. 3-27

4 Troubleshooting....................................................................................................................................... 4-1

4.1 Test Result Interpretation............................................................................................................. 4-1

4.2 Selftest / Circuit Block Reference Table....................................................................................... 4-2

4.3 Selftest Circuit Block Diagrams

4.4 Failure Examples............................................................................................................................ 4-23

4.4.1 IB Reversal........................................................................................................................... 4-23

4.4.2 Static-blown HSB................................................................................................................ 4-24

4.4.3 Missing -5 V......................................................................................................................... 4 - 25

......................................................................................................... 3-25

...................................................................................................

3 - 21

4 - 4

5 Maintenance............................................................................................................................................. 5 -1

5.1 Performing a Complete System Checkout..................................................................................... 5-1

5.2 Performing Adjustments................................................................................................................. 5-2

5.2.1 Adjustment to Vcc................................................................................................................ 5-2

5.2.2 Adjustment to Display Contrast

5.2.3 Changing System Firmware ............................................................................................... 5 - 2

5.2.4 Fuses and 110/220 V Conversion........................................................................................ 5-3

5.3 Disassembly and Assembly Instructions........................................................................................ 5-3

5.3.1 Microprocessor Board.......................................................................................................... 5 - 3

5.3.2 Keyboard.............................................................................................................................. 5 - 4

5.3.3 Speaker................................................................................................................................. 5 - 5

5.3.4 Display Controller

5.3.5 Display.................................................................................................................................. 5 - 5

5.3.6 High Speed Board................................................................................................................ 5 - 6

5.3.7 Power Supply....................................................................................................................... 5-6

5.3.7.1 Fan.............................................................................................................................. 5 - 6

5.3.8 Interface Buffer Board......................................................................................................... 5 - 7

5.4 Calibration Procedures ................................................................................................................... 5-7

5.4.1 Interface Buffer Calibration................................................................................................ 5 - 7

5.4.2 High Speed Board Calibration

5.4.2.1 Calibration Data Format............................................................................................. 5-7

............................................................................................................... 5 - 5

.........................................................................................

............................................................................................ 5-7

5-2

5.42.2 Calibration Standards............................................................................................... 5-8

5.4.2.3 HSB Component Placement...................................................................................... 5 - 8

5.4.2.4 The Offset Shift (OS) Definition............................................................................... 5 - 9

5.4.2.4.1 Example 1 (for negative offsets)

..................................................................

5-9

u

Page 6

Page 7

5.4.2A2 Example 2 (for positive offsets)......................................................................... 5-10

5.4.2.5 The Correcting Component Definition

5.4.2.6 Calibration Procedure

5.4.2.6.1 Offsets Block

..............................................................................................

.................................................................................................. 5 -12

...................................................................

5-10

5-12

5.4.2.6.2 Limits Block.................................................................................................. 5-12

5.4.2.6.3 Selftest buffer and 86 gate related condition................................................. 5-13

5.4.2.6.4 LM360 comparator related condition

.............................................................

5-16

5.5 Board Revisions, Upgrades and ECOs.......................................................................................... 5-16

5.5.1 Modification to MB for 64k Cartridges.............................................................................. 5-16

5.5.2 900 System Firmware......................................................................................................... 5-17

6 Schematics................................................................................................................................................6-1

6.1 INTERFACE BUFFER - IB............................................................................................................ 6 - 1

6.2 MICRO BOARD - MB rev.2 (M2) ............................................................................................... 6 - 3

6.3 HIGH SPEED BOARD - HS rev.2/3 (H3)

...................................................................................

6 - 5

7 Fluke 900 Parts Lists................................................................................................................................ 7-1

7.1 900 Final Assembly........................................................................................................................ 7-2

7.2 A1 Interface Buffer IB................................................................................................................... 7-4

7.3 A2 Micro Board M2 ...................................................................................................................... 7-6

7.4A3 Highspeed H3

...........................................................................................................................

7-8

7.5 A4 Power Supply Module PA....................................................................................................... 7-11

7.6 900-001 Simulation Option......................................................................................................... 7-12

111

Page 8

Page 9

FLUKE 900 SERVICE MANUAL

Service Manual Introduction

1 Service Manual Introduction

1.1 Description of Operator, Service Manuals

Documentation for the FLUKE 900 Dynamic Troubleshooter includes the Service Manual,

Operator Manual and Training Manual. For the purposes of maintenance and repair relevant

sections of the Operator Manual are:

Section 1.2 on Specifications

Section 1.4 on Ship>ping, Unpacking, and Connection

Section 1.5 on Keyboard Operation

Section 1.6 on Option Setting

It is recommended that the reader become familiar with this information and peitiaps the section

on Technical Principles from the Operator Manual before undertaking service repair of the unit

While some tasks in the Maintenance section of this Service Manual are relatively simple,

calibration and most troubleshooting require a thorough imderstanding of the information

presented in sections 1,2 and 3 of this Service Manual.

1.2 Basic Operation of Keyboard and Display

The FLUKE 900 display has 4 major areas:

- Information area in the upper portion of the screen

- Status line reverse highli^ited in the middle of the screen

- Command line for entering instractions below the status line

- Function key labels reverse highlighted at the bottom of screen

There are 5 Function

Permanently labelled keys are represented

of levels and sub-levels with the Function Keys. (^, on the left of the Function Keys, moves

operation up one level of the menu tree, brings up more labels on the same level of the tree.

Data that is typed in appears on the command line, but is only acted upon after [ento») is

pressed. @ perfonns a backspace function on the command line; 1^™^) ii erases the last word;

[cNTRj gg erases the whole line.

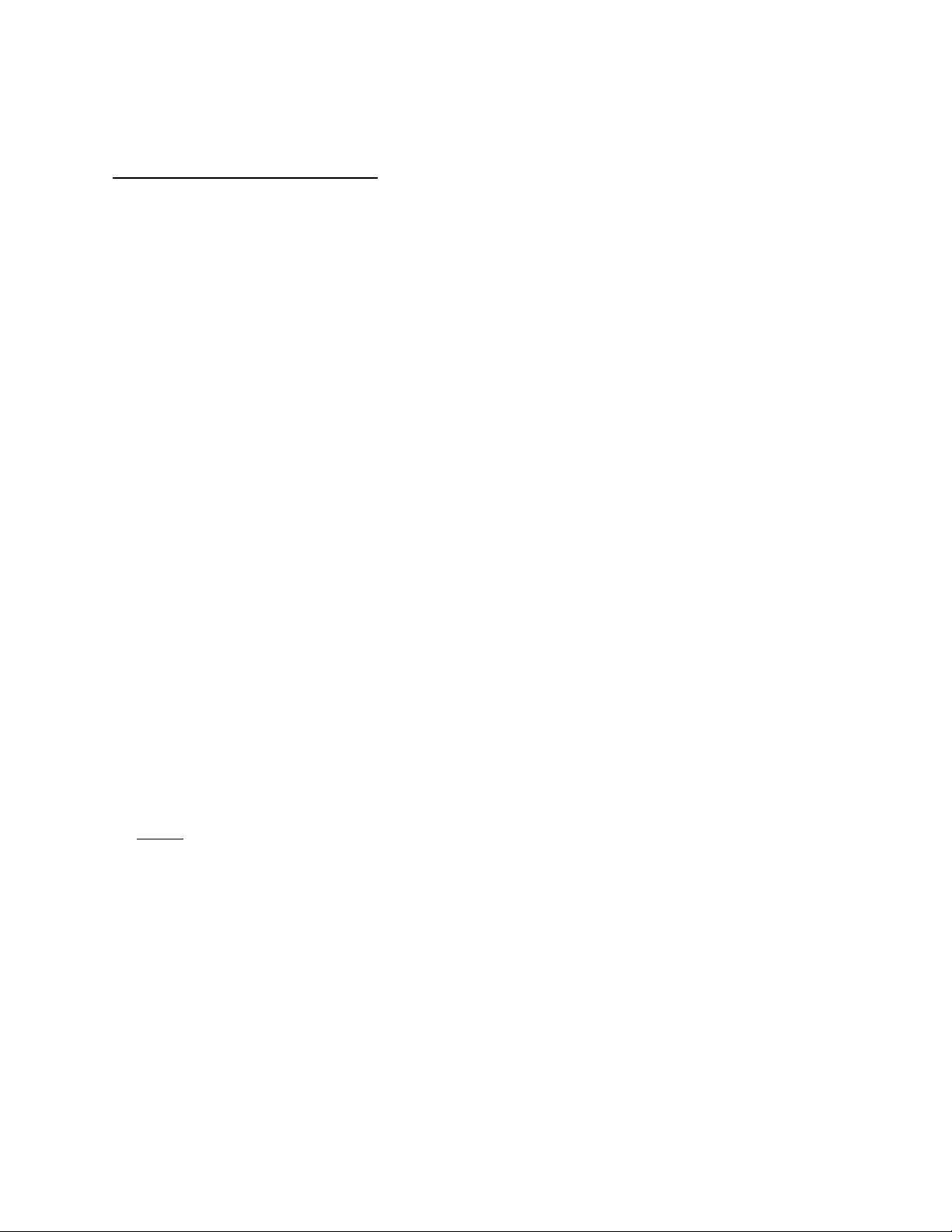

The Debug mode is used for observing selftest results, running selftests and printing results. It

may be entered, after a successful selftest, by pressing ES(system) IH) EXdebug) from the main

screen of the initial level. Debug is accessible directly after a poweron selftest fails. The menu

tree for the Function Keys after a fail spears as:

Key labels and they are represented in this manual as: (ES(label).

as: l enter j. Operational modes progress down a tree

1 -1

Page 10

Service Manual Introduction FLUKE 900 SERVICE MANUAL

©(restart) will re-execute the poweron selftest.

©(ignore) will bring up the main screen directly. If any of the failed selftests involve actual

testing circuitry (eg. FMxx), the operator will not be permitted to actually run a test cycle. File

manipulation, RD Test and System setting changes are possible, however.

Debug has three main keys: ©(run), ©(display), ©(prt_res). The last one means "print

results" and sends a formatted listing of all test results from the last test(s) executed to the serial

RS232 port, "display" brings to the screen, the characteristic 4 b)4e in^vidual result of the test

whose number was entered on the command line. This test must first have been run, either

explicitly or during the powerup.

The key labels under "run" are words that can be used to compose a command line instmction.

Some typical instmctions are:

Rim_test clip

Run test 0

Run test 40

Run_test 1 thm 40

Run test continuous

Run_test 46 continuous

until_fault

Run_test 1 looping

These two equivalent instructions run the clip continuity test.

A clip must be inserted in the Input Bufter and clipped onto

the Dummy Chip Module which must be plugged into the

ZIF socket. Results are shown on the screen.

Test 40 is executed and result bytes displayed in the case of a

failure.

Tests 1 through 40 are executed successively.

The series of poweron tests are executed repeatedly with the

number of passed and faUed cycles displayed on die screen.

will terminate it upon completion of the currently

executing test. This is a useful bumin procedure.

Test 46 is executed repeatedly while displaying the number of

passed cycles until the point at which a failure occurs.

Test 1 win execute repeatedly to facilitate signal tracing with

an oscilloscope.

1 -2

Page 11

FLUKE 900 SERVICE MANUAL Service Manual Introduction

At any point in the menu tree or any operational mode of the tester, a hard or soft reset may be

executed. Pressing (shift] and (^) simultaneously causes a soft reset that returns the display to

the initial power-on screen. This action does not erase any files that are resident in volatile

system RAM. For service purposes a soft reset during selftest is a convenient way to truncate the

selftest and bring up the main screen immediately. Pressing

a hard reset that clears memory and restarts selftest.

There is a special keyboard mode used mainly for calibration called the "engineering menu". It

may be entered from the main poweron screen by simultaneously pressing (cisto) and an

unlabeled key found between and (testJ. Its use will be described in the section on

calibration.

(cnthj and simultaneously causes

1 -3

Page 12

Service Manual Introduction

This page intentionally left blank.

FLUKE 900 SERVICE MANUAL

1 -4

Page 13

FLUKE 900 SERVICE MANUAL

Theory of Operation

2 Theory of Operation

2.1 General

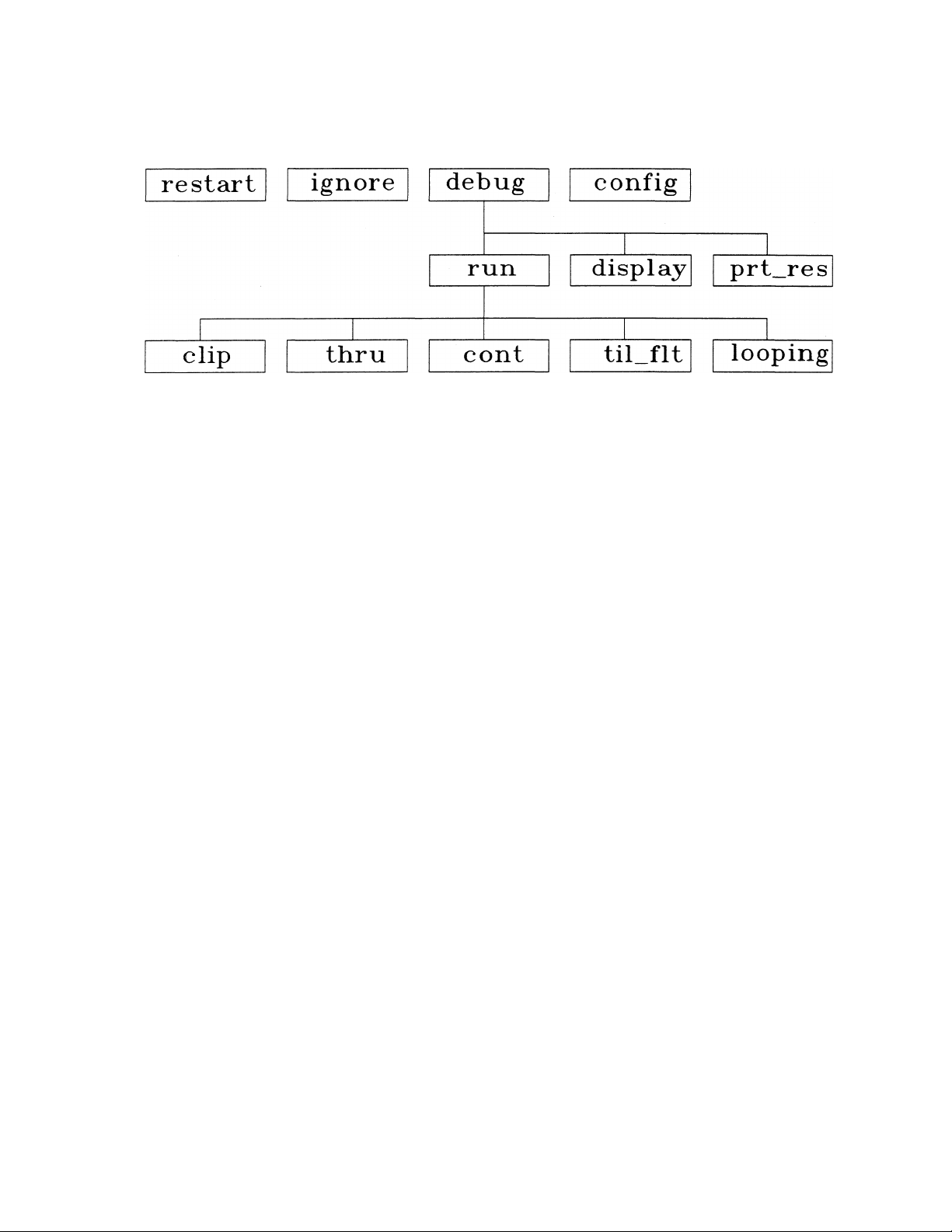

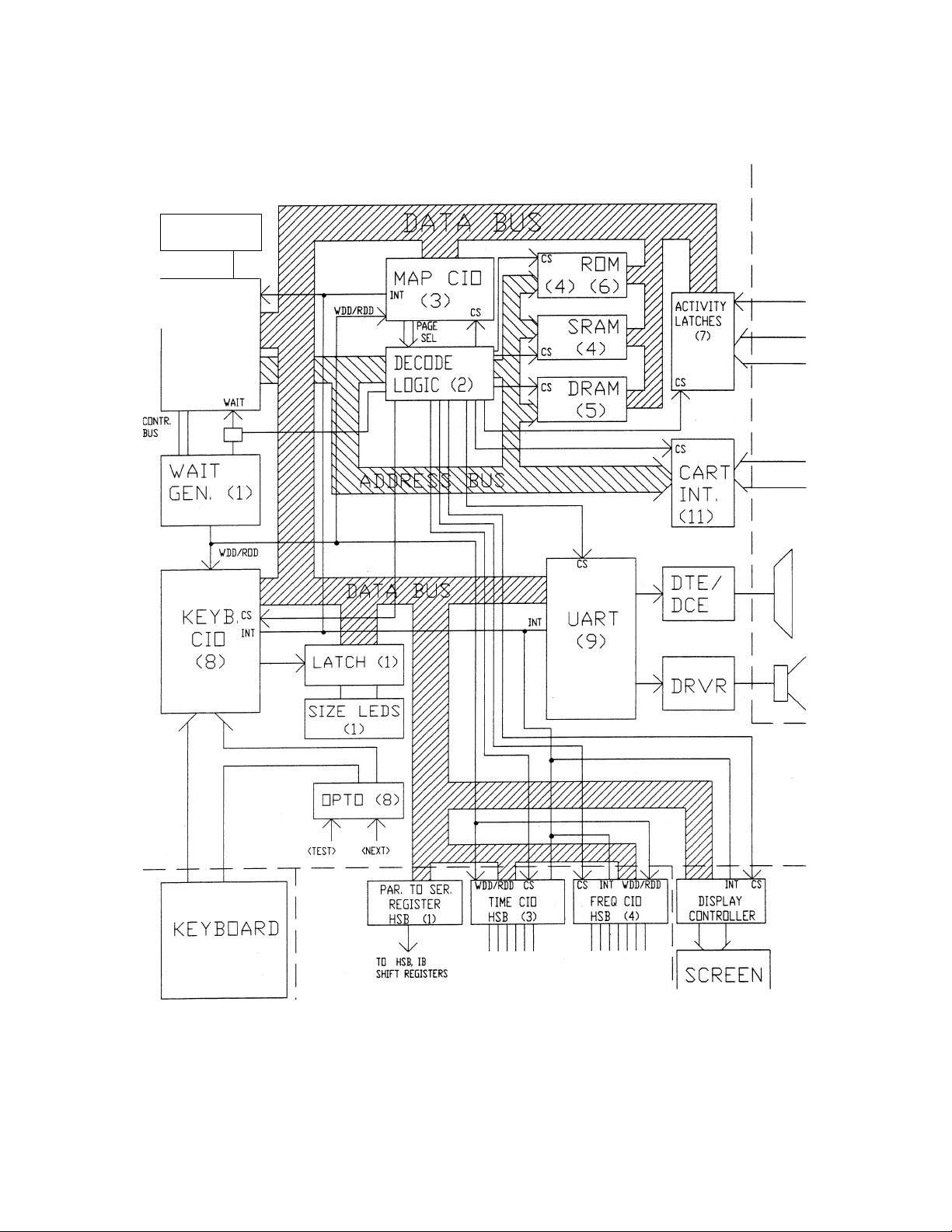

Major functional blocks of the tester correspond, in general, to physical modules. Shown below is

a diagram of the modules and their interconnections.

The Interface Buffer (IB) acquires and conditions signals from the board under test. It accepts 28

signal channels from an interchangeable clip and, by means of a single threshold setting,

translates them into ECL digital data for transmission to the High Speed Board.

The Micro Board (MB) controls the operating system, user interface and test parameter storage.

The Micro Board has a Z80 microprocessor running from about 320K of paged memory space.

The software is mainly comprised of interrapt routines that service four 8536 CIO devices. Two

CIOs are on the MB, the "Keyboard" and "Map" devices, while two CIOs are on the HSB, the

"Time" and "Frequency" devices.

The Micro Board sets up the High Speed Board (H3) with the proper configuration for a test

before letting it run at high speed without intervention. The setup of the test proceeds by loading

a series of shift registers with data impropriate for the test to be performed. Four 8 bit registers

are cascaded to make a set of 32 bits in length. Six such sets are located on the H3, two on the IB.

2-1

Page 14

Theory of Operation

During the test phase, signals received by the H3 are routed immediately to a comparison circuit

to be matched against one of two possible signals. In the case of a signal extracted fix)m a DUT

input pin, the comparison is made with itself ( no failure should appear ). In the case of a DUT

output pin signal, the comparison is made with the identical RD pin signal. The RD pins are

continuously monitored by a resistive load to determine whether tiiey are input or output and

thus how to route the equivalent DUT signals. At each signal transition, the DUT/RD

discrepancy is timed to see if it exceeds a set FMASK value. If so, and if not overridden by a Gate

or Trigger setting, the faults are latched and displayed on the monitor LEDs and LCD Screen.

FLUKE 900 SERVICE MANUAL

2.2 Interface Buffer

Pages 3,4,S,6 of the IB schematics show the signal path for each of the 28 channels that can come

from a DUT. lOK resistors connect each channel to an output bit on the cascaded shift registers

shown on page 1. In actual usage, these are resistors pulled up to 5 volts by default to resolve

floating imconnected inputs on a UUT which could otherwise confuse test results. In addition,

the check for a low condition on a pin is made while attempting to pull it high; the high check is

made with the lOK resistor pulled down to ground.

After the impedance matching components and protection diodes, each chaimel feeds a

comparator referenced to a bias voltage. The ouqjuts are differential E(X levels for relative

noisefiee transmission to the High Speed Board.

The shift registers shown on page 2 are used to control the bias setting for threshold, the Reset

line setting and external frequency multiplexing. Eight bits drive a DAC which resolves a 0 to 5

volt range into 100 mV increments. Five bits control the polarity, voltage and status of the Reset

driver (Page 1). Three bits route one of several lines through an analog multiplexer to a

voltage-controlled oscillator (U25). The measurement of the VCO frequency on the HSB is used

to determine clip size ( from a characteristic voltage divider in each clip), threshold verification

and VCC accuracy.

2-2

Page 15

FLUKE 900 SERVICE MANUAL

Theory of Operation

2.3 Micro Board

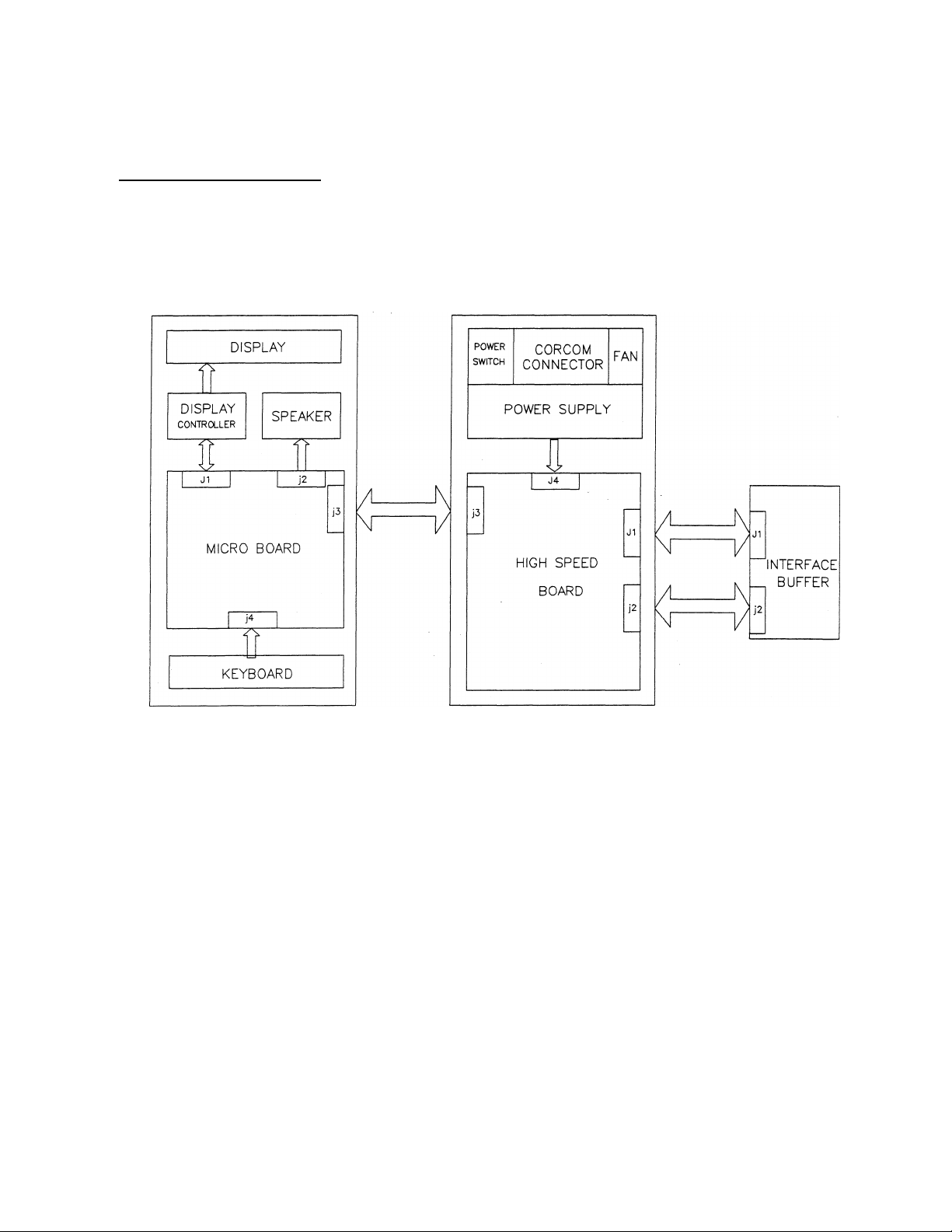

The Micro Board architecture is shown in the accompanying diagram. Note that, for

simplification, bus buffers are not shown and all chip select signals are shown as CS to a device

instead of the actual signal ( eg. CS for MAP CIO is actually MAPSEL ). The Z80 CPU runs at 6

MHz and operates with the Wait State Generator PAL (U69) to give the delayed control signals

WRD and RDD. The CPU signals WR and RD are thus modified for the timing requirements of

the Display Controller and the 8536 CIO chips. The four CIO devices are complex counterAimer

and parallel I/O ports. Two are located on the MB, two on the HSB, and they interrupt the CPU

for servicing of their particular function.

The MAP CIO sets up the memory map and paging scheme through PALs U58, U59, U72, U73.

Port A is configured as output for the PAL chip selects. Port B is output for the EPROM chip

selects. Port C is output for the RAM chip selects. The internal timer on this CIO is used for

general timeout purposes in such functions as cartridge operations and library loading.

The Decode Logic consists of the PALs referred to previously and it generates chip selects for all

peripheral devices and extends the 64K address range of the Z80 as shown in the memory mt^

diagram.

The first 16K is the power on

boot ROM space (ROM

SYSAF is part of it). The

next 8K of CPU address

space is used to access 14

pages of 8K in size residing

on the SYSAF and B ROMs.

The next 8K starting at

address 6(X)0 accesses 14

pages residing on SYSC and

D ROMs. The range 8000 to

COOO is 16K of static RAM.

The first RAM chip has a

battery and retains the

System Mode option

parameters. It also has 8

pages of cartridge memory

and 16 pages of library

ROM. The final 16 K is

overlayed with 4 pages

comprising the DRAM and

used for internal functions

and 48K of ":SYST"

sequences.

4000

6000

8000

AOOO

COOO

FFFF

16k

SYSAF

8k

OVERLAY

8k

OVERLAY

8k

SRAM

8k

SRAM

15k

DRAM

Ci;234S6iS9ABCiQ

C i:24436789A8GD

I N : i M M :; M pages SYSD

i|234S67aT234367a3ABGDEF g

j 15 pages library

23

4 pages rSYST

14 pages SYSAF

14 pages SYSB

14 pages SYSC

The Keyboard CIO outputs levels on port A which are read back on port B when a key is

depressed. Three internal timers designated "watchdog", "key_time" and "key" take care of

2-3

Page 16

Theory of Operation

debouncing and repeating key actions. The itest) and inext) keys found on the Interface Buffer

are routed through the HSB and optocoupled on the MB to connect to the keyboard CIO. The

chip size LEDs are driven by a latch controlled by this CIO.

The dual UART located at Ull is used for two functions. First, the serial RS232 interface is

connected through a DTE/DCE selectable routing circuit so it can interface to various computers

and printers. Second, various standard frequencies are generated to drive a speaker providing

audible beep tones. The socket at U62 contains the battery and circuit for the real time clock

function.

FLUKE 900 SERVICE MANUAL

2-4

Page 17

FLUKE 900 SERVICE MANUAL

MI CR D BOARD A RCHI TEC TU RE

Theory of Operation

□sc

CPU (1)

\/

(1)

INT

TESTDN

MDN BUS

(MSB)

CARTRIDGE

RS232

SPKR,

H I G H S P EED B E AR D

2-5

Page 18

Theory of Operation FLUKE 900 SERVICE MANUAL

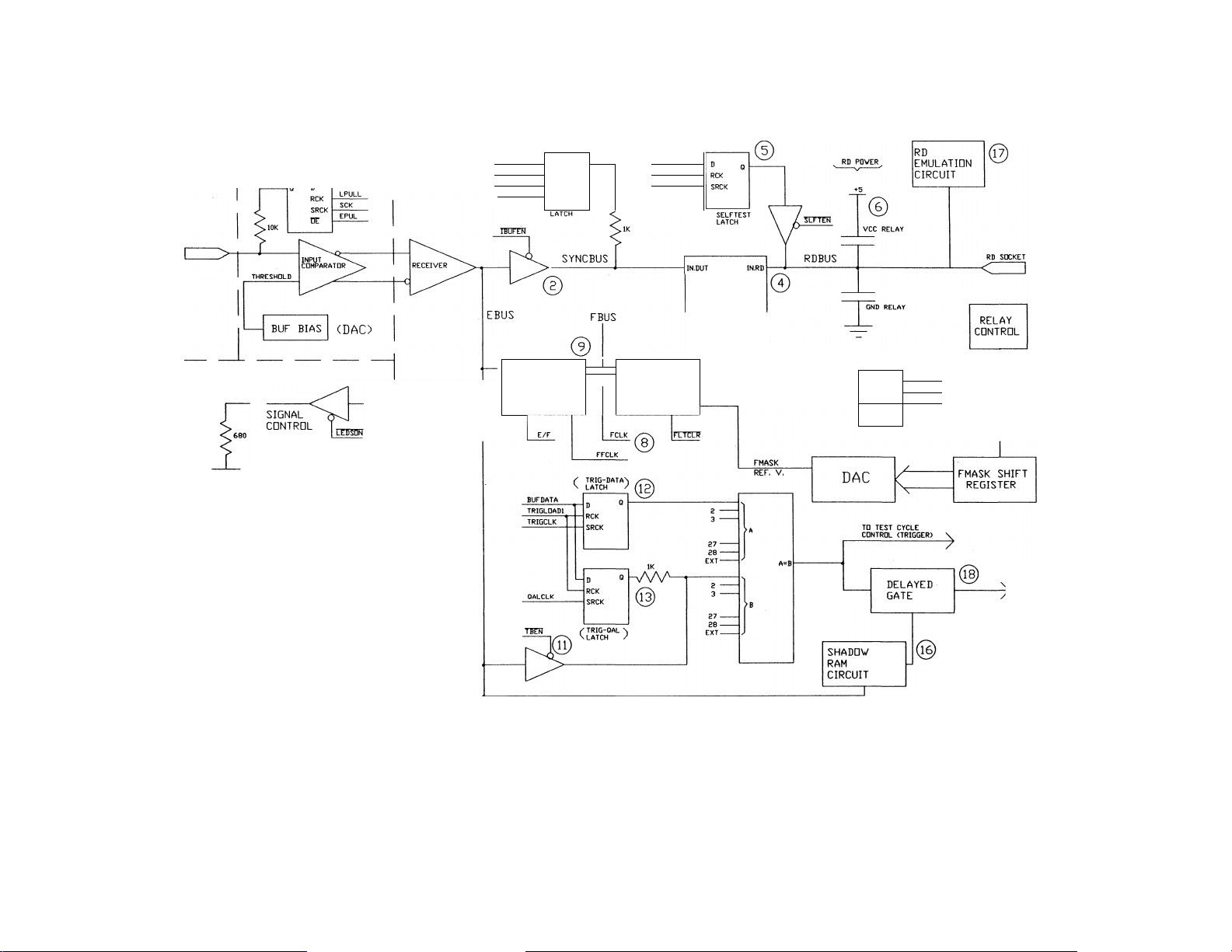

2.4 High Speed Board

The accompanying diagram shows one chamiel routing a signal from the test clip through the

Interface Buffer to the High Speed Board (H3) where it is processed by Dynamic Reference

Comparison. The Micro Board then receives indicators from the H3 to display a test result There

are 28 such channels in parallel. The circuit elements that are depicted as latches in the diagram

are implemented with shift registers that are first serial loaded, then clocked to a parallel ou^t

latch. The diagram’s latches are single bits of a 28 bit shift register comprised of four cascad^ 8

bit 74595s.

2-6

Page 19

TEST

CLIP

INPUT BUFFER

MICRO BOARD

'f-

.-UPS

©

ACTIVITY

MONITDR

HIGH SPEED BGARD

BUFDATA

w

SYNCLÖAD

SYNCCLK

SYRCEN

° Q

RCK

SRCK

SYNC

_____

©

BUFDATA

SLPTLOAÖ

SLFTCLK

C

m

CO

o

o

CO

m

3J

<

o

DIFTEST

BUFFER

□UT <DC)

m

>

z

c

>

MGNBUS

EBUS.IN FAULT.IN

LATCHING

CIRCUIT

OUT

SELECT

\ /

OUT

FRAMING IN

CIRCUIT

CLEAR

vw— °

PIN-DIS

LATCH

SRCK

RCK

©

BUFDATA

öiSloaü

DISCLK

.TO TEST CYCLE

7 CONTROL

ro

•nI

(14)

(D

“O

O

O

O

CD

O

3

FREQUENCY

COUNTER

CMUX)

EXT-

I

GATE-

10)

Page 20

Theory of Operation

The busses shown are as follows:

EBUS

External bus represents DUT signals after conversion to TTL levels using a single

threshold in the IB. EBUS is labelled on pages 2, 4, 6, 8, 9, 10, 11 of the H3

schematics.

RDBUS

Reference device bus carries EBUS input pin signals to the RD socket and RD

output pin signals to the DIFTEST circuit. RDBUS is labelled on pages 7, 8,9,10,

11 of the H3 schematics.

EBUS

Fault bus indicates on which pins the RDBUS and EBUS were different for longer

than the FMASK value. The FBUS consists of the op amp ouQ)ut signals labelled

Fxxon pages 8,9,10,11 of the H3 schematics.

SYNCBUS

Synchronizing bus is either the EBUS or a pattern from the device library,

depending on whether the Sync Vectors technique is employed to synchronize RD

and DUT. The SYNCBUS consists of the 74244 output signals found on the

extreme left side of pages 8,9,10,11 of the H3 schematics.

FLUKE 900 SERVICE MANUAL

MONBUS

Monitor bus is either the same as EBUS or FBUS, depending on which is selected

for display on the monitor LEDs. The Mon bus may be found at connector J3 on

the right side of pages 8,9,10,11, of the H3 schematics and on page 13 of the MB

schematics.

The 18 circuit blocks shown in the diagram on the previous page are the same ones listed across

the top of the Selftest/Circuit Block Reference Table (Section 4.2). Fifteen of the blocks

described below are found on the H3 Board.

1.

PuUups Latch

On the Interface Buffer, signals from the test clips are pulled up to VCC or down

to Gnd through a lOK resistor from the output of this shift register latch. It is found

on page 1 of the IB schematic, Ul, U2, U3, U4. The register at U24 of the BB drives

a DAC which sets the threshold.

Inbuf

These buffers found on pages 8,9,10, 11, of the H3 schematics (U186, U140, U95,

U42), feed the EBUS through to the SYNCBUS. They are tristated when the Sync

Latch is driving.

Sync Latch

Synchronizing patterns from the library data are shifted ink) the registers shown on

pages 8,9,10,11, (U182, U136, U91, U45) and then latched to the output as a test

vector. The stimulus for the RDTest ftmction is provided in the same way.

2-8

Page 21

FLUKE 900 SERVICE MANUAL Theory of Operation

Diftest Buffers

This circuit uses one of two possible resistor values (Hi or Lo) to determine

whether the RDBUS can drive and therefore whether the pin is an output The

final output indicates the discrepancy between RDBUS and EBUS/SYNCBUS. It

may be foimd at the outputs of the exclusive OR gates on pages 8,9,10,11.

Self Test Latch

The shift register latch used to inject patterns onto the RDBUS during power-on

verification in earlier revison boards is incorporated into the Logic Cell Array at

U105, near the ZDF socket of the H3 Board. This is shown as circirit block 17 on the

block diagram. If a RD is inserted during the power-on test an t^arent failure will

result

RD Supply Relays

Certain ZIF socket pins are cormected to VCC or Gnd by closure of the relays

shown on page 7. The shift registers U155 and U102 control their selection.

Pin Dis Latch

These shift register latches can override the fault indication output from the Diftest

circuit to ignore a fault on a pin. They are shown on pages 8, 9, 10, 11, as U180,

U134, U89, U40.

8.

9.

10.

11.

FFCLK Line

The CPU can simulate a fault by asserting this line which is ORed with the pin fault

lines to produce FLTS, the master fault indicator (page 11, A-10). Shift register

U67 (page 3) provides data to a DAC which provides the FMASK reference

voltage used in the framing circuit. The charging of precision capacitors to this

voltage establishes an FMASK value. Note that ttie 74ALS09s driving the

capacitors are specially prescreened to be uniform.

Mon Mux

The latches at U198, U153, U112, U64 hold the individual pin faults. The PALs

driving them are also latches which accumulate faults for 40 ns after the first line

fails but no further. In this way, the results are frozen in a window around the first

fail for later reading by the CPU over the Mon Bus. When no faults are present,

the signal M/F selects U164, U122, U76, U43 (pages 8, 9, 10, 11) to route the

EBUS onto the MONBUS.

Freq Circuit

The 8536 CIO at U27 (page 4) controls the multiplexing and measurement of

signal frequency among the 29 channels (28 pins plus 1 external). Port A is

configured as output and used to drive the muxes at U55, U66, U124, U141. Port B

drives the FREQ PAL except for PBS which is an input flagging the occurrence of

Gate. Port C is an input to read the frequency count.

Trig Buf

These buffers U191, U154, U98, U81 on page 2 enable the EBUS to the trigger

comparator when TBEN signal is active.

2-9

Page 22

Theory of Operation

12. Trig Data Latch

The shift register latches U166, U189, UlOO, U78 are loaded with data indicating Is

and Os of the Trigger word. The first word is serial shifted and latched followed by

the second word which is not latched until the occurrence of the first.

13. Trig Qual Latch

The shift register latches at U168, U188, U96, US6 are loaded with data indicating

which pins have a 1 or 0 and which have "don’t care" conditions. Two successive

words are loaded as in the Trig Data case.

14. Activity Circuit

This circuit on page 7 of the Micro Board schematics operates by latching the state

of all pins at the start of test and generating an exclusive OR pulse if the state ever

changes, hi this way, the PALs U32, U21, U16, U22 are alerted of active pins.

15. Mon Bus Readback

The Mon Bus which comes from the ffigh Speed Board to the Micro Board via the

connector J3 is shown on page 13 of the MB schematics. The latches and PALs on

page 7 use the Mon Bus to hold the state of all pins at the end of test (for the EoT

test result). The state of pins at the start of test is also latched here for the purpose

of checking H or L conditions on DUT pins.

FLUKE 900 SERVICE MANUAL

16,18. Shadow Ram and Delayed Gate Circuit

This circuit is implemented in the Logic CeU Array at U123 (page 6) and associated

PALs. Both of these functions affect the gating of comparison. Shadow RAM

inhibits comparison during reading of an uninitialized DUT memory cell. Delayed

gate inhibits the normal gate signal from going true for a fixed time interval after its

pin conditions are satisfied.

17. RD Emulation Circuit

This Logic Cell Array, located at U105 (page 12), simulates certain Reference

Devices instead of using an RD in the socket. If an H3 Board does not have the

Simulation Option instafied, U105 is still present to perform selftest functions.

Test cycle control is applied to all 28 channels together and is found on page 3 of the H3

schematics. The Time CIO at U26 is configured so РАО, 1,2 enable the Trigger flip flops and

GATE PAL. РАЗ is an output for enabling comparison during selftest. PA4 is an input that

detects whether gate occurred. PA5 is an input indicating a short in the RD socket. PA6, 7 are

inputs that detect whether trigger word 1 and 2 occurred.

Port В controls the Test Cycle PAL; PBl is an input which stops test after a fault has been

captured. PB2, 3, 4, 5 are inputs from a counter which acts as a prescaler for the time-to-fault

interval. An internal CIO timer converts it to a value in the proper range. PB6 is an output that

clears the fault under CPU control, while PB7 is an input indicating a fault is present Port C is

configured as an output and it selects which shift register will receive the data stream from the

register U36 on page 1 of the H3 schematics.

2-10

Page 23

FLUKE 900 SERVICE MANUAL

Theory of Operation

2.5 Test Clips

The standard Test Clips have no active components, but the ribbon cable is temiinated at both

ends with a series 300 ohm resistor for impedance matching. There are 10 Kohm puUup resistors

in the Interface Buffer which are applied to the DUT through the 600 ohms of the Test Clip.

The High Impedence Test Clip has an active buffer at the clip head which presents 500 Kohm

impedence to the DUT. The clip head is powered from the VCC pin of the DUT.

2-11

Page 24

Theory of Operation

This page intentionally left blank.

FLUKE 900 SERVICE MANUAL

2-12

Page 25

FLUKE 900 SERVICE MANUAL

3 Selftest

3.1 Reading Selftest Results

Immediately after poweron, the tester executes a series of selftests that take about one minute.

The selftests may also be initiated at any time by simultaneously pressing (.cntrj and (^. The

tests are number^ 0 to 55 and all but a few are run automaticaUy. These few plus a number of

"extended tests" denoted by Exx (eg. E60), can be run by manually keying them in when analyzing

a problem. All the tests may be run individually in this way to produce "individual test results".

When a failure is encountered during poweron selftest, two rows of digits display "general results"

and sometimes a third and fourth row appear. Rows 1 and 2 indicate the failing test numbers;

rows 3 and 4 indicate fault flags that are tied to memory and shift registers. Flag failiues indicate

major functional problems and general test results indicate which tests are failing. "Individual test

results" are more detailed dispays of the failing tests and they indicate which channels (lines) ate

faulty.

In cases where a failure is severe and the LCD screen may not function, the LEDs around the

ZIF socket may indicate the problem.

Selftest

Hardware and software problems occasionally result in system crashes that present a message on

the command line. One cause of such a crash is a corrupted simulation library file. A summary of

these messages appears in Section 3.4.

3-1

Page 26

Seiftest

FLUKE 900 SERVICE MANUAL

3.1.1 General Selftest Results

The general results on the first two lines are clustered in groups of five as shown in the

example below. The test numbers are shown above and below the digits. 0 indicates Pass, 1

indicates Fail and X indicates that a test result is not available.

0-4 5-9

XOOOO 00000

00000 01000 00011

30-34

The cross reference of test numbers to test names is listed below:

SLFT CLIP

0

PULLO_MON 30 FM40_NFLT

1

PULLl MON

2

PULLO.FLT 32 FM80_NFLT

3

PULLl FLT

4

SYNCO Hres FLT

5

SYNCl Hres FLT

6

SYNCO Lies FLT

7

SYNCl Lres.FLT

8

PINDISO FLT

9

PINDIS1_FLT 39

10

SLFTSTO FLT

11

SLFTSTl FLT

12

VccON FLT 42 PULLO ACT TSTON

13

GndON FLT

14

PULLPOS FREQ

15

TRIGQALO EQUAL

16

TRIGQALl EQUAL

17

qalo_equal 47

18

QALl EQUAL

19

TRIGO EQUAL

20

TRIGl EQUAL

21

PULLO TRIG EQUAL

22

PULLl TRIG EQUAL

23

PULLO TRIGQAL

24

FM_STAT_NFLT

25

FM STAT FLT

26

FMASK WB_TEST

27

FMASK CAL

28

35-39

10-14

mil

40-44

15-19 20-24

00000 00000 OXXll

XXX11

45-49 50-54

25-29

11100

XXXXX

55-59

29

FM40 FLT

FM80 FLT

31

33

FM120 FLT

34

FM120 NFLT

FM160_FLT

35

36

FM160 NFLT

37 FM200.FLT

FM200_NFLT

38

FM240 FLT

40 FM240 NFLT

41

ACT DIS CLR

PULLl ACT TSTON

43

44

PULLO ACT ACTSTR

45 PULLl ACT ACTSTR

46

FREQ_BIAS SHORT

FREQ_BIAS_LONG

48 KEYBOARD OPEN

49 TEST_CYCLE

50 UART.TEST

DGATE TEST

51

52

PULLO.XTRIG

53 PULLl XTRIG

54

PULL_XEVENT

SHAD.INTT

55

3-2

Page 27

FLUKE 900 SERVICE MANUAL

Tests 0,47 and SO are not automatically run during the poweran selftest, but can be nin by

themselves explicitly. This is also the case for a group of tests known as "engineering" or

"extended" tests which are designated Exx as follows:

Seiftest

E60

E61

E62

E63

E64 SHAD ADDR

E70

E71

E74 DISP CHAR SET

E75

E76

E77

E78

E79

E80

2 Flag

Flags may ^pear on lines 3 and 4 of the general results screen. A 0 means "OK" and a 1

means "fault". At the present time, only the first row is used.

WALK SIZELEDS

TEST MEMORY

WALK MONLEDS

UPDATE_VCC_UM

KEY CLOSURE

DISP RAM

CART_SLFT

TEST C ENG

ACT_CROSS

TRG CROSS

FRQ_CROSS

FLT_CROSS

Results

BYTEO

I

00000000

00000000

BYTEl BYTE2

I I

00000000 00000000

00000000 00000000

BYTE3

I

00000000

00000000

11111111

BIT: 76543210

BYTEO: Indicates DRAM chip which failed memory test

B7: U86

B6: U82

B5: U87

B4: U83

B3: U88

B2:U84

Bl: U89

BO: U85

3-3

Page 28

Seiftest

FLUKE 900 SERVICE MANUAL

BYTEl: Indicates shift register bank which failed

B7: INTERFACE BUFFER OB U1,U2,U3,U4)

B6: DELAYED GATE

B5: SELFTEST (HSB U38,U76,U115,U150)

B4: FMASK (HSB U72)

B3: TRIGGER QUALIFIER (HSB U57,U87,U142,U162)

B2: TRIGGER DATA (HSB U66,U91,U140,U163)

BLPIN DISABLE (HSB U41,U80,U119,U154)

BO: SYNC (HSB U46,U82,U121,U156)

BYTE2: General

B7; NVRAM bad

B6: NVRAM checksum error, rewritten with default data

B5: Not used

B4: Not used

B3: ROM bad (U77)

B2: ROM bad (U76)

Bl: ROM bad (U75)

BO: ROM bad (U74)

BYTE3: General

B7,6,5,4: Not used

B3: FMASK calibration error

B2: Threshold calibration error

Bl: FLTS line not readable

BO: Threshold setting error

3-4

Page 29

FLUKE 900 SERVICE MANUAL Selftest

3.1.3 Chip Size LED Error Codes

If self test fails, on rare occasions, the chip size LEDs may light to indicate an error. In the list

below, the 8 LEDs are shown with a 0 for unlighted and a 1 for lighted.

00000001: KEYBOARD CIO PortA. CPU cannot communicate.

00000010: KEYBOARD CIO PortB

00000011: TIME QO PortA

00000100: TIME CIO PortB

00000101: FREQ CIO PortA

00000110: FREQ CIO PortB

00000111: Display not ready

00001000: ROM checksum error

00001001: SRAM error

00001010: Stack underflow

00001011: Unimplemented interrupt occurred

00001100: Invalid intermpt vector

00001101: Not used

00001110: Incorrect peripheral serviced

00001111: UART transmit error

00010000: UART other errors ( special receive conditions)

00010001: UART parity error

00010010: DRAM error

00010011 : Overlay error

00010100: Not used

00010101: MAP CIO PortA

00010110: MAP CIO PortB

00010111 : Display memory error

3-5

Page 30

Seiftest

FLUKE 900 SERVICE MANUAL

3.2 Running and Reading Individual Selftests

The individual selftest results indicate which specific lines or channels are failing. A full printout

of all failing individual results may be printed out as explained in Section 1.2. Altemativdy, a

single individual result may be viewed on the display by pressing the following keys after the

general poweron seUtest fails: ED(debug) ©(display) "test #" ien^j. The individual result then

appears as £010* bytes with a 1 indicating a problem.

BYTEO

BYTEl

I

00000000 00000000

BIT: 76543210 76543210

BYTEO

b7:X

b6:X

b5:X

b4: EXT LEAD

b3: PIN 1

b2: PIN 28

bl: PIN 2

bO: PIN 27

Refer to the individual descriptions of Section 3.3 for any bit assignments that may differ fixm

those generaEy used above. In particular, bits 5,6,7 of BYTE 0, which are not used for most tests,

may have a meaning which is noted for a specific test

BYTEl

b7: PIN 3

b6: PIN 26

b5: PIN 4

b4: PIN 25

b3: PEST 5

b2: PEST 24

bl:PESr 6

bO: PIN 23

BYTE2 BYTE3

I I

00000000 00000000

76543210 76543210

BYTE2

b7: PEST 7

b6: PEST 22

b5: PESf 8

b4: PIN 21

b3: PEST 9

b2: PTN 20

bl: PEST 10

bO: PIN 19

BYTE3

b7:PIN 11

b6: PIN 18

b5: PIN 12

b4: PB4 17

b3: PEST 13

b2: PEST 16

bl: PIN 14

bO: Pm 15

3.3 Individual Selftest Descriptions

3-6

TEST 0 SLFT_CLIP

The SLFT_CLIP routine is used for verifying test clips. The test clip in question is inserted

into the Interface Buffer and the other end is inserted into the ZEF RD socket via the Test

Oip Verification Module. When the test is running, die size of the current test clip is

displayed. The failure information is displayed as follows (Only special bits are shown, all

others refer to tegular pin number):

BYTE 0 - B7 -

B6B5B4-

Not used

Not used

Clip size code invalid

Frequency reading invalid

Page 31

FLUKE 900 SERVICE MANUAL

TESTS 1 2

PULLO_MON, PULL1_MON

These tests supply a walking 0 or 1 across all lines from the pull-tq)s latch, through the iiqnit

buffer, to the MONBUS where the levels are read by the (TPU.

TESTS 3,4

PULL0_FLT, PULL1_FLT

These tests supply a walking 0 or 1 across all lines fixnn the pull-ups latch, through die iiqnit

buffer, through the fault circuitry to the MONBUS where the levels are read by the CPU.

TESTS 5,6

SYNCO_Hres_FLT, SYNCl_Hres_FLT

These tests supply a walking 0 or 1 across all lines from the sync latch, through the HI

resistors, through the fault circuitry to the MONBUS where the levels are read by the CPU.

Selftest

TESTS 7 8

SYNC0_Lres_FLT, SYNC1_Lres_FLT

These tests supply a walking 0 or 1 across all lines from the sync latch, through the LO

resistors, through the fault circuitry to the MONBUS where the levels are read by the CPU.

TESTS 9,10

PINDISO_FLT, PINDIS1_FLT

These tests supply a walking 0 or 1 across aU lines from the pin disabling latch, through the

fault circuitry to the MONBUS where the levels are read by the CPU.

TESTS 11,12

SLFTSTO_FLT, SLFTST1_FLT

These tests supply a walking 0 or 1 across all lines from the selftest latch, through the fault

circuitry to the MONBUS where the levels are read by the CPU.

TESTS 13,14 VccON_FLT, GndON_FLT

These tests walk the Vcc or Gnd relays on. Their operation is verified through the fault

circuitry to the MONBUS where the levels are read by the CPU.

3-7

Page 32

Seiftest

FLUKE 900 SERVICE MANUAL

TEST 15

PULLPOS_FREQ

This test walks a positive pulse through the pull-ups latch to tiie frequency circuitry,

TESTS 16,17

TRIGQALO_EQUAL, TRIGQAL1_EQUAL

These tests walk a 0 or a 1 through the trigger and qualifier latches and the results are

determined through reading the EQUAL line.

TESTS 18,19

QAL0_EQUAL, QAL1_EQUAL

These tests walk a 0 or a 1 through the qualifier latches and the results are determined

through reading the EQUAL line.

NOTE: For tests 18 and 19, an X in the general test result means that individual

results are imavailable.

TPQT^ Pn P1

TRIGO_EQUAL, TRIG1_EQUAL

These tests walk a 0 or a 1 through the trigger latches and the results are determined through

reading the EQUAL line.

NOTE: For tests 20 and 21, an X in the general test result means that individual

results are unavailable.

TESTS 22 23

PULLO_TRIG_EQUAL, PULL1_TRIG_EQUAL

These tests walk a 0 or a 1 through the pull-ups latches, through the trigger circuitry and are

read through the EQUAL line.

NOTE: For tests 22 and 23, an X in the general test result means that individual

results are unavailable.

TEST 24

PULLO TRIGQAL

This test walks a 0 through the pull-tq>s latches, through the trigger and qualifier circuitry and

the results are determined through reading the EQUAL line.

3-8

Page 33

FLUKE 900 SERVICE MANUAL

NOTE: For test 24, an X in the goieral test result means that individual results are

unavailable.

TESTS 25,26

FM_STAT_NFLT, FM_STAT_FLT

These tests perform a static FMASK test All lines are expected to pass for the "_NFLT" test

while all lines are expected to fail for the "FLT" test

TEST 27

FMASK_WB_TEST

This test does an approximate test using fixed values for FMASK. It uses a tolerance three

times that of the FMxx tests. This test is performed to determine whether or not the FMASK

curve is within a very wide margin.

TEST 28 FMASK_CAL

Selftest

This routine determines the calibration values to be used by FMASK.

TESTS 29,31,33,35,37,39

FMxx_FLT

These tests use a pulse of fixed duration (40, 80,120,160,200 and 240ns) and set FMASK to

just below the duration of the pulse. All lines are expected to produce a fault Those which

do not are flagged as faulty.

TESTS 30,32,34,36,38,40

FMxx_NFLT

These tests use a pulse of fixed duration (40, 80,120,160,200 and 240ns) and set FMASK to

just above the duration of the pulse. AH lines are expected to produce no fault Those which

do are flagged as faulty.

TEST 41 ACT_DIS_CLR

This test checks the disabling and clearing functions of the activity circuitry. It disables the

activity circuit and pulses all lines. Any lines which indicate activity are flagged as faulty. It

also verifies that the activity latches may be cleared and that a single edge on all lines

produces a 1 (activity occurred) in all latches.

3-9

Page 34

Seiftest

FLUKE 900 SERVICE MANUAL

The bits in the tesults indicate nonnal pin numbers with the exception of the following:

BYTE 0 - B7 - NAJ

B6- N/U

B5 - Could not clear PAL latches.

B4 - Could not activate aU lines with a single edge.

TESTS 42 43

PULLO_ACT_TSTON, PULL1_ACT_TSTON

These tests walk a rising edge(l) or a falling edge(0) horn the puU-iq>s latches through the

activity circuitiy. The activity circuit is controlled by the TSTON signal.

TESTS 44, 45

PULLO_ACT_ACTSTR, PULL1_ACT_ACTSTR

These tests walk a rising edge(l) or a falling edge(0) fiom the pull-ups latches through the

activity circuitry. The activity circuit is controlled by die ACTSTR signal.

TESTS 46,47

freq_bias_short, freq_bias_long

These two tests are almost identical, the only difference being that the long test verifies aU

possible values of threshold and the short test only tests at 1 volt increments. The tests are a

collection of several subtests involving frequency and threshold hardware on the High Speed

Board and Input Buffer and they are detiuled below. As they are being done, the left part of

the screen shows timing values from the frequency test and the right side of the screen shows

the highest and lowest differences between expected and measured voltage values.

Many of the subtests require that a voltage on the Interface Buffer be measured. One of

several possible voltages is selected using the analog mux on the input buffer. This feeds the

into the VCO, the output of which is sent to the High Speed Board where the frequency is

measured. The same thing is also done for 0 volts and 2.5 volts to obtain a calibration ratio

that is used to determine the exact voltage of the signal selected.

Interface Buffer shift register subtest

This tests to see if data can be shifted through the shift registers on the Interface Buffer

correctly. There are two banks of registers on the board. Only the puUup registers are

explicitly tested because there is no feedback line from the threshold registers. The

threshold registers are implicitly tested by the other tests. The test procedure is as follows:

a) shift data - msbit = 0

b) read the voltage of the msbit: must be <2V

c) shift data - msbit = 1

d) read the voltage of the msbit: must be >2V

3-10

Page 35

FLUKE 900 SERVICE MANUAL

If this test fails it does not set one of the data bits but rather sets the shifting error flag.

Frequency HW subtest

The frequency hardware tested is on the High Speed Board. It can be configured in

several different ways (the setup for this is shown in the MODE box on the schematic), aU

of which are independently tested.

1. Read a fiequency. A 25MHz clock is generated and the frequency is measured.

2. Read the period. Pin #2 is selected through the frequency mux (this hardware is

tested in a different selftest). It is setup to read the period and then the CPU

generates a cycle of fixed duration on this line using the puUup registers on the

Interface Buffer. The period displayed should be approximately 990 us.

3. Read the high time and low time. These are done in the same way as the period test

except the times are displayed. Low time should be approximately 815 us and high

time 175 us.

Selftest

Threshold HW subtest

This subtest programs a value of threshold and reads it back to verify that it is within an

acceptable range. The variation between the measured value and the value programmed

(in mV) is displayed on the screen. The long test goes through all possible settings

between 0 and 5 volts and the short test only goes in steps of 1 volt

After the threshold setting has been tested the threshold is calibrated to compensate for

input offsets in the comparators. The puUups are used to set the actual threshold on the

input to the comparator to 4.16 and 0 volts and then the threshold is adjusted to see what

offset added to the amount programmed (4.2 and 0 volts) will be closest to the actual

threshold of the comparators. If the adjustment exceeds an allowable amount the

calibration part of this test win fail.

Reset HW subtest

For this subtest the reset relays are set so that power for reset comes from 5 volts and the

output is fed into the analog mux.

a) reset = high: must be > 4 volts

b) reset = low: must be < 1 volt

c) reset = off: must be < 4 volts & > 1 volt

3-11

Page 36

Seiftest

Result bytes:

BYTE 0

b7b6b5b4b3-

b2bl -

bO-

BYTE 1

b7b6b5-

b4b3b2-

bl-

bO-

0

0

0

0

Threshold calibration failed. Ignore this bit unless the other bits in this byte

are clear. If they are clear and this bit fails the output of the threshold Op

Amp has too great an offset

Unable to complete test. Something is wrong with the CPU - CIO interface.

The threshold was too high. The output of the Op Amp was greater than

expected by more than the allowable amount

The threshold was too low. The ouQnit of the Op Amp was less than

expected by more than the allowable amoimt

Vcc(IB) is too high ( > 5.2V ). The main Vcc voltage as read at the

Interface Buffer is too high. If this test fails, ALL other selftests are invalid.

Vcc(IB) is too low ( < 4.84V ). The main Vcc voltage as read at the

Interface Buffer is too low. If this test fails ALL other selftests are invalid.

0

0

0

Unable to turn off the reset line. The reset output fiom the Interface Buffer

could not be made to go tri-state.

Unable to drive the reset line low.

Buffer could not be made to go low.

Unable to drive the reset line high.

Buffer could not be made to go high.

FLUKE 900 SERVICE MANUAL

The reset output from the Interface

The reset ou^ut from the Interface

3-12

BYTE 2

b7-

b6-

b5b4b3-

Period measured was too long. There are several possible causes. The

25MHz crystal could be oscillating at the wrong frequency, the WSG pal

could be faulty, almost any of the 4 frequency chips could be bad.

Period measured was too short. There are several possible causes. The

25MHz crystal could be oscillating at the wrong fiequency, the WSG pal

could be faulty, almost any of the 4 frequency chips could be bad.

No results obtained from period read. The test has timed out. Something is

wrong with the CPU - CIO interface.

Unable to set up the period read. Something is wrong with the CPU - CIO

interface.

HW oscillator (25MHz) is too fast. There are several possible causes. The

25MHz crystal could be oscillating at the wrong frequency, almost any of the

4 frequency chips could be bad, the 2925 clock generator could be bad, there

could be a problem in the fiequency muxes.

Page 37

FLUKE 900 SERVICE MANUAL

b2 - HW oscillator (25MHz) is too slow. There are several possible causes. The

25MHz crystal could be oscillating at the wrong frequency, almost any of the

4 frequency chips coiild be bad, the 2925 clock generator could be bad, there

could be a problem in the frequency muxes.

bl - No results obtained from freq read. The test has timed out Something is

wrong with the CPU - CIO interface.

bO - Unable to set up the frequency read. Something is wrong with the CPU -

CIO interface.

BYTE 3

b7-

b6-

b5

b4

b3

b2-

bl

bO

The active low duty cycle measured was too long. There are several possible

causes. The 25Nfflz crystal could be oscillating at the wrong frequency,

almost any of the 4 frequency chips could be bad, the WSG pal could be

faulty, the 2925 clock generator could be bad, there could be a problem in

the frequency muxes.

The active low duty cycle measured was too short. There are several possible

causes. The 25MHz crystal could be oscillating at the wrong frequency,

almost any of the 4 frequency chips could be bad, the WSG pal could be

faulty, the 2925 clock generator could be bad, there could be a problem in

the frequency muxes.

No results obtained from low read. The test has timed out. Something is

wrong with the CPU - CIO interface.

Unable to set up the low read. Something is wrong with the CPU - CIO

interface.

The active high duty cycle measured was too long. There are several possible

causes. The 25MHz crystal could be oscillating at the wrong frequency,

almost any of the 4 frequency chips could be bad, the WSG pal could be

faulty, the 2925 clock generator could be bad, there could be a problem in

the frequency muxes.

The active high duty cycle measured was too short. There are several

possible causes. The 25MHz crystal could be oscillating at the wrong

frequency, almost any of the 4 frequency chips could be bad, the WSG pal

could be faulty, the 2925 clock generator could be bad, there could be a

problem in the frequency muxes.

No results obtained from high read. The test has timed out. Something is

wrong with the CPU - CIO interface.

Unable to setup the high read. Something is wrong with the CPU - CIO

interface.

Selftest

3-13

Page 38

Seiftest

FLUKE 900 SERVICE MANUAL

TEST 48

KEYBOARD_OPEN

This test verifies that all keys are in the open state including the keys on the buffer. The last

two bytes of the individual test result will contain two set bits which may be intetpreted from

the following matrix to identify the key that was depressed.

KEYBOARD MATRIX

byte 3—> b7

2

I

J4| 16 I

V

bO

bl

b2

b3

b4

b5

b6

b7

1 I G I A I ESC I SHFT I CNTR | Y | S | M

2 I II C I F2 I space I < , I = + I U | 0

3 1 K I E I F5 |BoL<- I PgUp ''I : ; I W | Q

41 LI F I F4 |EoL-> |PgDn v| ? _ I X | R

5 I # 3 I ! 1 I ETC I ENTER |sparel| ( 9 | & 7 | %5

6 I $ 4 I § 2 I NEXT I TEST |spare21 ) 0 | * 8 | "6

7 I J I D I F3 I spares I > . I / - I V | P

8 I HI B I FI I CE I |<—>1 I Z I TIN

TEST 49 TEST_CYCLE

b6 b5

15 1

14 1 13

b4

b3

1 12

b2

1 11

bl

1 10

bO

1 9

3-14

This test verifies that:

- the following lines are not broken or shorted:

/SYNCEN

/SHORT interrupt line

/RELEN

- the following timers are good:

Test time timer

10 ms system timer

1 ms free rumiing timer

- gate and trigger work properly

Page 39

FLUKE 900 SERVICE MANUAL

/SHORT is checked to see if the line is hi^ (ie. not shorted to ground). /SYNCEN and

/RELEN are tested by having sync latches or relays cause a fault and verifying that the fault

occurred.

Four bytes of test results are presented:

BYTE 0

b7 thru 5-0 (not used)

b4 -/STRFRQ output ofTC PAL not woiking

b3 - Interrupts failed

b2 - /SYNCEN line test failed

bl - /SHORT test failed

bO - /RELEN test failed

NOTE: only interrupts generated by TIME port are tested.

BYTE 1

b7 thru 3 - 0 ( not used )

b2 - test time timer

bl -10 ms timer

bO -1 ms timer

Selftest

Each bit in bytes 2 and 3 corresponds to one execution of the test cycle, set up to produce the

expected results. If any bit in bytes 2 or 3 is set it means that results were not as expected. For

example, if b6 in byte 2 is set it means that the gate function was observed to be not active or

faults were detected. Trigger is programmed with one word Gevel) in byte 2 trigger test; for

byte 3, trigger is programmed with two words (edge). For aU W2 related tests (byte 3 bits 3

thru 0), W1 always occurs.

BYTE 2

b7 - gate did not occur no faults

b6 - gate occurred no faults

b5 - gate did not occur, fatilts

b4 - gate occurred, faults

b3 - trigger did not occur, no faults

b2 - trigger occurred, no fault

bl - trigger did not occur, faults

bO - trigger occurred, faults

BYTE 3

b7 - trigger W1 did not occur, no faults

b6 - trigger W1 occurred, no faults

b5 - trigger W1 did not occur, faults

b4 - trigger W1 occurred, faults

b3 - trigger W2 did not occur, no faults

b2 - trigger W2 occurred, no faults

bl - trigger W2 did not occur, faults

bO - trigger W2 occurred, faults

3-15

Page 40

Seiftest

FLUKE 900 SERVICE MANUAL

TEST 50

UART_TEST

The RSCNT3, RSCNT2, and RSCNTl lines on the Micro Board control the configuration of

the rs232 port (DTE.DCE). These lines are put into a normally illegal state that allows the

outputs of the UART to be fed into the inputs. This can be done in two ways and all tests are

done in both configurations.

There are two tests: the first tests the control lines (DTR, CTS,...) and the second transmits

data between the transmitter and receiver. The second test is not done if the first fails.

1. Test the control lines (byte 2 & 3 results). Each of the control lines is tested with the

other control line in a fixed state, first hi^ then tested again with it low. At the top of

the results for each byte the setting of the configuration lines is shown. For each test

the state of the state of the two ou^ut control lines is shown as well as the input line

and what state is expected on it

2. Test the data lines. This test is NOT done unless test 1 passes. The baud rate is

programmed to 9600 regardless of the setting of the rs232 port. At the end of the test

it is reprogrammed with the correct value. A small block of data is sent and compared

with what was received. The receiving of data is interrupt driven so that this test may

fail if there is something wrong with this part of the board. The setting of the

configuration lines is shown for each test.

RESULT BYTES

BYTE 0 = all bits 0

BYTE 1

b7-0

b6-0

b5 - 0

b4-0

b3-0

b2 - 0

bl -1 if serial data test failed with RSCNT[3,2,1]=001

bO -1 if serial data test failed with RSCNT[3,2,1]=110

NOTE RSCNT[3,2,1] means that control signals RSCNT3, RSCNT2, RSCNTl to Ul,

U2, U7 on the Micro Board (page 9 of schematics) were held in the states shown

during the test.

3-16

Page 41

FLUKE 900 SERVICE MANUAL

BYTE 2 -RSCNT[3,2,1] = 001

b7-DTR=0, RTS=1, test for CTS=1

b6 - DTR=0, RTS=0, test for CTS=0

b5-DTR=l, RTS=1, test for CTS=1

b4 - DTR=1, RTS=0, test for CTS=0

b3 - DTR=0, RTS=0, test for DCD=0

b2 - DTR=1, RTS=0, test for DCD=1

bl - DTR=0, RTS=1, test for DCD=0

bO - DTR=1, RTS=1, test for DCD=1

BYTE 3 -RSCNT[3,2,1] = 110

b7-DTR=0, RTS=1, test for CTS=1

b6 - DTR=0, RTS=0, test for CTS=0

b5 - DTR=1, RTS=1, test for CTS=1

b4-DTR=l, RTS=0, test for CTS=0

b3-DTR=0, RTS=0, test for DCD=0

b2-DTR=l, RTS=0, test for DCD=1

bl-DTR=0, RTS=1, test for DCD=0

bO - DTR=1, RTS=1, test for DCD=1

Selftest

TEST 51

DGATE_TEST

This test is performed only if the Simulation Option (900-001) is installed. It verifies the

functionality of the delayed-gate circuit. It checks the operation of the pre-scaler, the delay

function, the duration function and the delayed-gate-activity circuit. Results are interpreted

as follows:

B7

1

_

j

________

BYTEO1

0

1 1

BYTEl1 /15

.667MI1.786MI2•083MI 2.5M 13

|1

BYTE21

1

D U

128

BYTE31

128

1

1 B6

1 0

1 /14

1 64

1 64

D

1

--

1-------------

1DGATE

ACT

1

/12

1

32

1

32

1

B5

R A

E L A Y

B4

1

T

-------------

1DGATE

CLR

1

/10

1

16

1

16

1

B3

1

-4- —

1

1

1

— 4- —.

INF

DUR

/8

.125MI4• 17MI

T

8

1

8

1

B2 1

1

0 1

1

1 DELAY 1

/6 1

1

PRE-

SCALER 1 FAIL

6.25M

I

4 1

1

4 1

1

Bl

1 BO

--l- — — — — — —

1 INVERT

/4

1 /2

112.5M

0 N

2

2

1 1

1 1

3-17

Page 42

Seiftest

FLUKE 900 SERVICE MANUAL

INVERT FAIL

PRE-SCALER

0 DELAYINF. DUR. DGATE ACT DGATE CLR-

Note:

For Example:

Sequence of results during test:

While this test is running in "looping" mode, the expected values and the measured

results are displayed continuously on-screen in the following format (NOTE: Tbe

NEXT key advances to the next part of the test):

Message #

Could not invert gate signal.

A division factor other than one in BYTE 1 failed.

The test for bypassing the delayed gate circuit failed

The test for infinite duration failed (Duration prematurely terminated.

The dgate activity latch failed to register activity.

The dgate activity latch was not cleared by TESTSTR.

Expected

Minimum

140.00 n

Minimum Measured Maximum

Measured Value

160.00 n

Expected

Maximum

180.00 n

Circuitry Tested

#1 24.950 M

#2 12.450 M

#3 8.2833 M

#4 6.2000 M

#5

#6

#7

#8

#9

#10

#11 2.2227 M 2.2727 M 2.3227 M

#12

#13 1.8731 M

#14 1.7357 M

#15

4.9500 M

4.1167 M

3.5214 M

3.0750 M

2.7278 M 2.7778 M 2.8278 M

2.4500 M

2.0333 M 2.0833 M 2.1333 M

1.6167 M

25.000 M 25.050 M

12.500 M 12.550 M

8.3333 M

6.2500 M 6.3000 M

5.0000 M

4.1667 M 4.2167 M

3.5714 M 3.6214 M

3.1250 M 3.1750 M

2.5000 M 2.5500 M

1.9231 M 1.9731 M

1.7857 M 1.8357 M

1.6667 M

8.3833 M

5.0500 M

1.7167 M

Prescaler - divide by 1

Prescaler - divide by 2

Prescaler - divide by 3

Prescaler - divide by 4

Prescaler - divide by 5

Prescaler - divide by 6

Prescaler - divide by 7

Prescaler - divide by 8

Prescaler - divide by 9

Prescaler - divide by 10

Prescaler - divide by 11

Prescaler - divide by 12

Prescaler - divide by 13

Prescaler - divide by 14

Prescaler - divide by 15

3-18

Page 43

FLUKE 900 SERVICE MANUAL

Selftest

#16

#17

#18

#19

#20

#21 3.7990 u 3.8400 u

#22

#23

#24 119.00 n 120.00 n

#25

#26

#27

#28

#29

#30

#31

79.000 n 120.00 n

199.00 n 240.00 n 281.00 n

439.00 n 480.00 n 521.00 n

919.00 n 960.00 n

1.8790 u 1.9200 u

7.6390 u 7.6800 u 7.7210 u

15.319 u 15.360 u

239.00 n

479.00 n 480.00 n

959.00 n

1.9190 u 1.9200 u

3.8390 u 3.8400 u 3.9610 u Delay - Bit5

7.6790 u 7.6800 u

15.359 u

240.00 n 361.00 n

960.00 n

15.360 u

161.00 n

1.0010 u

1.9610 u Duration - Bit4

3.8810 u

15.401 u

241.00 n

601.00 n

1.0810 u

2.0410 u

7.7610 u

15.441 u

IXuation - BitO

Duration - Bitl

Duration - Bit2

Duration - Bit3

Duration - Bit5

Duration - Bit6

Duration - Bit7

Delay - BitO

Delay - Bitl

Delay - Bit2

Delay - Bit3

Delay - Bit4

Delay - Bit6

Delay - Bit7

#32

#33

79.000 n 120.00 n 201.00 n DGATE Inversion Test

229.00 n

320.00 n 401.00 n

DGATE Infinite Duration Test

TEST 52

PULL0_XTRIG

If the Simulation Option (900-001) is installed, this test verifies the operation of the trigger

circuit inside the shadow RAM ASIC chip configured for extended trigger. It walks a 0

through each line on the puU-ups latches and tries to trigger on each event

3-19

Page 44

Seiftest

FLUKE 900 SERVICE MANUAL

+

-----

IBYTE

1

+

----

IBYTE

+

----

1

01

1

1 1

B7

1 B6 1 B5 1

|ALL=11TSTONI

0

1 FAILI FAILI

1 26 1 4 1 25 1 5

3

B4 1

TRIGI

B3

1

B2

1

28

1

1 1 1 1

24

1

B1

1

2

1

BO

1

1

27

1

1

1

6

1

23

1

1

IBYTE 21 7 I 22 I 8 | 21 | 9 | 20 | 10 | 19 |

IBYTE 31 11 I 18 I 12 I 17 I 13 I 16 | 14 | 15 |

ALL=1 FAE. - Indicates that one or more lines could not be set high initially (i.e. Lines

shorted low). If only one line is shorted, that line is displayed. If multiple

lines are shorted, individual lines cannot be displayed.

TSTON FAIL - The TSTON line failed to control the triggering.

TEST 53

PULL1_XTRIG

If the Simulation Option (900-001) is installed, this test verifies the operation of the trigger

circuit inside the shadow RAM ASIC chip. It walks a 1 through each line on the pull-ups

latches and tries to trigger on each event

I

B7 I B6

I

B5

I

B4 I B3

I

B2 I B1 | BO |

IBYTE 0| 0 IALL=0ITSTONI TRIG| 1 | 28 | 2 | 27 |

I

IBYTE II 3 I 26

I

I FAIL I FAIL

I

4

I I

I

25 I 5 I 24 I 6

I I

I

I

I

23 I

IBYTE 21 7 I 22 I 8 | 21 | 9 | 20 | 10 | 19 |

IBYTE 31 11 I 18 I 12 I 17 I 13 I 16 | 14 | 15 |

ALL=0 FAIL - Indicates that one or more lines could not be set low initially (i.e. Lines

shorted high). If only one line is shorted, that line is displayed. If

multiple lines are shorted, individual lines cannot be displayed.

TSTON FAIL - The TSTON line failed to control the triggering.

3-20

Page 45

FLUKE 900 SERVICE MANUAL

TEST 54

PULL_XEVENT

If the Simulation Option (900-001) is installed, this test verifies the operation of the event

counter inside the shadow RAM ASIC chip configured for extended trigger. The tests are as

follows:

1. Circuit configured as: EVENT-CLOCK=EQUAL, CLOCK-ENABLE=MATCH

- Check for false clocking (clocking with CLOCK-ENABLE inactive)

- Check for proper counting (set count = 255 and provide 255 clocks)

2. Circuit configured as: EVENT-CLOCK=MATCH, CLOCK-ENABLE=TSTON

- Check for false clocking (clocking with CLOCK-ENABLE inactive)