Page 1

268XA

®

Data Acquisition System/Data Logging System

Service Manual

PN 1883791

November 2002

© 2002 Fluke Corporation. All rights reserved. Printed in USA

All product names are trademarks of their r espective comp ani es.

Page 2

Limited Warranty and Limitation of Liability

Each Fluke product is warranted to be free from defects in material and workmanship under

normal use and service. The warranty period is one year and begins on the date of shipment.

Parts, product repairs and services are warranted for 90 days. This warranty extends only to the

original buyer or end-user customer of a Fluke authorized reseller, and does not apply to fuses,

disposable batteries or to any product which, in Fluke’s opinion, has been misused, altered,

neglected, contaminated, or damaged by accident or abnormal conditions of operation or

handling.

Fluke warrants that software will operate substantially in accordance with its functional

specifications for 90 days and that it has been properly recorded on non-defective media. Fluke

does not warrant that software will be error free or operate without interruption. The software is

neither intended nor warranted for use in medical or any other applications where human safety

may be a concern.

Fluke authorized resellers shall extend this warranty on new and unused products to end-user

customers only but have no authority to extend a greater or different warranty on behalf of Fluke.

Warranty support is available only if product is purchased through a Fluke authorized sales outlet

or Buyer has paid the applicable international price. Fluke reserves the right to invoice Buyer for

importation costs of repair/replacement parts when product purchased in one country is submitted

for repair in another country.

Fluke’s warranty obligation is limited, at Fluke’s option, to refund of the purchase price, free of

charge repair, or replacement of a defective product which is returned to a Fluke authorized

service center within the warranty period.

To obtain warranty service, contact your nearest Fluke authorized service center to obtain return

authorization information, then send the product to that service center, with a description of the

difficulty, postage and insurance prepaid (FOB Destination). Fluke assumes no risk for damage in

transit. Following warranty repair, the product will be returned to Buyer, transportation prepaid

(FOB Destination). If Fluke determines that failure was caused by neglect, misuse, contamination,

alteration, accident or abnormal condition of operation or handling, including overvoltage failures

caused by use outside the product’s specified rating, or normal wear and tear of mechanical

components, Fluke will provide an estimate of repair costs and obtain authorization before

commencing the work. Following repair, the product will be returned to the Buyer transportation

prepaid and the Buyer will be billed for the repair and return transportation charges (FOB

Shipping Point).

THIS WARRANTY IS BUYER'S SOLE AND EXCLUSIVE REMEDY AND IS IN LIEU OF ALL

OTHER WARRANTIES, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY

IMPLIED WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE.

FLUKE SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL OR

CONSEQUENTIAL DAMAGES OR LOSSES AND/OR PROFITS, INCLUDING LOSS OF DATA,

ARISING FROM ANY CAUSE OR THEORY.

Since some countries or states do not allow limitation of the term of an implied warranty, or

exclusion or limitation of incidental or consequential damages, the limitations and exclusions of

this warranty may not apply to every buyer. If any provision of this Warranty is held invalid or

unenforceable by a court or other decision-maker of competent jurisdiction, such holding will not

affect the validity or enforceability of any other provision.

2/02

Fluke Corporation Fluke Europe B.V.

P.O. Box 9090 P.O. Box 1186

Everett, WA 98206-9090 5602 BD Eindhoven

U.S.A. The Netherlands

Page 3

WCaution

This is an IEC safety Class 1 product. Before using, the ground

wire in the line cord or rear panel binding post must be connect

to an earth ground for safety.

Interference Information

This equipment generates and uses radio frequency energy and if not installed and used in strict

accordance with the manufacturer’s instructions, may cause interference to radio and television reception. It

has been type tested and found to comply with the limits for a Class B computing device in accordance with

the specifications of Part 15 of FCC Rules, which are designed to provide reasonable protection against

such interference in a residential installation.

Operation is subject to the following two conditions:

• This device may not cause harmful interference.

• This device must accept any interference received, including interference that may cause undesired

operation.

There is no guarantee that interference will not occur in a particular installation. If this equipment does cause

interference to radio or television reception, which can be determined by turning the equipment off and on,

the user is encouraged to try to correct the interference by one of more of the following measures:

• Reorient the receiving antenna

• Relocate the equipment with respect to the receiver

• Move the equipment away from the receiver

• Plug the equipment into a different outlet so that the computer and receiver are on different branch

circuits

If necessary, the user should consult the dealer or an experienced radio/television technician for additional

suggestions. The user may find the following booklet prepared by the Federal Communications Commission

helpful: How to Identify and Resolve Radio-TV Interference Problems. This booklet is available from the U.S.

Government Printing Office, Washington, D.C. 20402. Stock No. 004-000-00345-4.

SAFETY TERMS IN THIS MANUAL

This device has been designed and tested to meet the requirements of EN61010-1

(Safety Requirements for Electrical Equipment for Measurement, Control and Laboratory

Use). It is an Installation Category II device intended for operation from a normal single

phase supply. The DIO relay controls are rated to 250 V ac CAT I and should not be

used in applications that exceed that rating.

warnings and cautions. Use of this equipment in a manner not specified herein may

impair the protection provided by the equipment.

Measurement category I is for measurements performed on circuits not directly

connected to MAINS. Examples are measurements on circuits not derived from MAINS,

and specially protected (internal) MAINS derived circuits.

Measurement category II is for measurements performed on circuits directly connected

to the low voltage installation. Examples are measurements on household appliances,

portable tools and similar equipment.

W WARNING statements identify conditions or practices that could result in personal

injury or loss of life.

CAUTION statements identify conditions or practices that could result in damage to

equipment.

This Users Manual contains information,

Page 4

SYMBOLS MARKED ON EQUIPMENT:

WARNING Risk of electric shock.

Ground (earth) terminal.

Protective ground (earth) terminal. Must be connected to safety earth

ground when the power cord is used.

Attention. Refer to the manual. This symbol indicates that information

about usage of a feature is contained in the manual. This symbol

appears on the Universal Input Module and in the following two places

on the device rear panel:

1. Ground Binding Post (to the left of the line power connector).

2. Alarm/Trigger I/O and Digital I/O connectors.

AC POWER SOURCE

The device is intended to operate from an ac power source that will not apply more than

264 V ac rms between the supply conductors or between either supply conductor and

ground. A protective ground connection by way of the grounding conductor in the power

cord is required for safe operation.

XWWARNING

Use the proper fuse. To avoid fire hazard, for fuse replacement

use only a 1/2 ampere, 250 V time delay line fuse.

DC POWER SOURCE

The device may also be operated from a 9 V to 45 V dc power source when either the

rear panel ground binding post or the power cord grounding conductor is connected

properly. The input is protected by a 4 ampere fuse internal to the device. This fuse

should only be replaced by a qualified Fluke technician.

GROUNDING THE DEVICE

The device utilizes controlled overvoltage techniques that require the device to be

grounded whenever normal mode or common mode ac voltages or transient voltages

may occur. The enclosure must be grounded through the grounding conductor of the

power cord, or if operated on battery with the power cord unplugged, through the rear

panel ground binding post.

USE THE PROPER POWER CORD

Use only the power cord and connector appropriate for the voltage and plug

configuration in your country.

Use only a power cord that is in good condition.

Refer power cord and connector changes to qualified service personnel.

Page 5

XWWARNING

To avoid possible electric shock or damage to the device:

• Read manual before operating.

• Do not position device so that air flow through side vents is

restricted.

• Do not use in a manner not specified in this manual or

safety protection may be impaired.

• Disconnect power cord and ALL other inputs before

replacing a fuse.

• Position the device where power cord can be disconnected.

• Do not exceed maximum voltages.

XWWARNING

DO NOT OPERATE IN EXPLOSIVE ATMOSPHERES

To avoid personal injury or death, do not remove the device cover without first removing

the power source connected to the rear panel. Do not operate the device without the

cover properly installed. There is no need for the operator to remove the cover.

DO NOT ATTEMPT TO OPERATE IF PROTECTION MAY BE IMPAIRED

If the device appears damaged or operates abnormally, protection may be impaired. Do

not attempt to operate the device under these conditions. Refer all question of proper

device operation to qualified service personnel.

DO NOT ATTEMPT TO SERVICE UNLESS YOU ARE A FLUKE QUALIFIED REPAIR TECHNICIAN

To avoid personal injury or death, remove the AC power cord and all analog and digital

connector modules before servicing the device.

Note

All signals must be removed from the analog and digital connector wiring

before opening the connector modules.

Page 6

Page 7

Table of Contents

Chapter Title Page

1 Introduction and Specifications........................................................ 1-1

Introduction....................................................................................................... 1-3

Block Diagrams................................................................................................. 1-5

Specifications .................................................................................................... 1-7

2680A/2686A Combined Specifications....................................................... 1-7

2680A/2686A General Specifications............................................................... 1-8

Real-Time Clock and Calendar......................................................................... 1-9

Trigger In Specifications................................................................................... 1-9

Trigger Out Specifications ................................................................................ 1-9

Master Alarm Output Specification................................................................... 1-10

Communication I/O........................................................................................... 1-10

2686A PC Card Storage .................................................................................... 1-10

Precision Analog Input (PAI) A/D Specifications............................................. 1-11

Specifications PAI A/D DC Voltage Measurement...................................... 1-11

PAI A/D AC Voltage Measurement Specifications...................................... 1-13

PAI A/D 4-Wire Resistance Measurement Specifications............................ 1-15

PAI A/D 2-Wire Resistance Measurement Specifications............................ 1-16

PAI A/D 4-Wire RTD per ITS-1990 Measurement Specifications .............. 1-16

PAI A/D 2-Wire RTD per ITS-1990 Measurement Specifications .............. 1-16

PAI A/D Thermocouple per ITS-1990 Measurement Specifications............ 1-17

PAI A/D Frequency Measurement Specifications........................................ 1-20

Fast Analog Input (FAI) A/D Specifications..................................................... 1-21

FAI A/D DC Voltage Measurement Specifications...................................... 1-21

FAI A/D AC Voltage Measurement Specifications...................................... 1-22

FAI A/D 4-Wire Resistance Measurement Specifications............................ 1-24

FAI A/D 2-Wire Resistance Measurement Specifications............................ 1-25

FAI A/D 4-Wire RTD per ITS-1990 Measurement Specifications .............. 1-25

FAI A/D Thermocouple per ITS-1990 Measurement Specifications............ 1-26

FAI A/D Frequency Measurement Specifications........................................ 1-28

Digital Input/Output Module............................................................................. 1-29

Digital Input/Output Specifications .............................................................. 1-29

Totalizer Input Specifications....................................................................... 1-30

Digital Relay Specifications.......................................................................... 1-30

Options and Accessories.................................................................................... 1-31

i

Page 8

268XA

Service Manual

2 Theory of Operation........................................................................... 2-1

Introduction....................................................................................................... 2-3

Main Power Supply....................................................................................... 2-5

Secondary Supplies....................................................................................... 2-5

Out-Guard Overview..................................................................................... 2-5

Microprocessor......................................................................................... 2-6

FPGA........................................................................................................ 2-7

Other Bus Devices.................................................................................... 2-8

Serial Devices........................................................................................... 2-9

Trigger In/Out, Master Alarm................................................................... 2-9

PCMCIA Interface PCA (2686A-4041)............................................................ 2-10

Backplane PCA (268XA-4001)......................................................................... 2-10

Display Interface........................................................................................... 2-11

Module Interface........................................................................................... 2-11

Module Power Supply PCA (268XA-4031)...................................................... 2-11

Digital Input/Output PCA.................................................................................. 2-11

Microcontroller ............................................................................................. 2-12

Data Input Threshold..................................................................................... 2-12

Digital Input Buffers..................................................................................... 2-13

Digital Output Drivers................................................................................... 2-13

Relay Output Drivers.................................................................................... 2-13

Totalizer Input............................................................................................... 2-14

Totalizer Enable............................................................................................ 2-14

A/D Theory of Operations................................................................................. 2-14

A/D Converter PCA Block Description........................................................ 2-14

Analog Measurement Processor ............................................................... 2-15

Input Protection......................................................................................... 2-15

Input Signal Conditioning......................................................................... 2-15

Analog-to-Digital (a /d) Conv erter............................................................ 2-15

Inguard Microcontroller............................................................................ 2-15

Channel Selection..................................................................................... 2-15

Open Thermocouple Check...................................................................... 2-16

Analog Input PCA Block Description........................................................... 2-16

20-Channel Terminals............................................................................... 2-16

Reference Junction Temperature.............................................................. 2-16

A/D Converter PCA Circuit Description...................................................... 2-16

Stallion Chip............................................................................................. 2-18

Input Protection......................................................................................... 2-18

Input Signal Conditioning......................................................................... 2-18

Function Relays........................................................................................ 2-18

Channel Selection Circuitry...................................................................... 2-19

DC Volts and Thermocouples Measurement Circuitry............................. 2-19

Ohms and RTD Measurement Circuitry................................................... 2-20

AC Volts Measurement Circuitry............................................................. 2-22

Frequency Measurements......................................................................... 2-23

Active Filter (ACV Filter)........................................................................ 2-24

Voltage Reference Circuit ........................................................................ 2-24

Analog/Digital Converter Circuit ............................................................. 2-24

Autozero ................................................................................................... 2-24

Integrate.................................................................................................... 2-25

Deintegrate1.............................................................................................. 2-25

Deintegrate2.............................................................................................. 2-27

Overhead................................................................................................... 2-27

Inguard Digital Kernel Circuitry............................................................... 2-27

ii

Page 9

Contents

Open Thermocouple Detect Circuitry....................................................... 2-28

A4 Analog Input PCA Circuit Description................................................... 2-28

A31 A/D Power Supply Circuit Description................................................. 2-29

Controller/System Power (Outguard) to A3 A/D Converter (Inguard)

Communications ........................................................................................... 2-29

Special Codes................................................................................................ 2-29

Resets............................................................................................................ 2-29

Commands..................................................................................................... 2-30

Perform Scan............................................................................................. 2-30

Perform Self-Test...................................................................................... 2-31

Return Firmware Version......................................................................... 2-31

Return Boot Firmware Version................................................................. 2-31

Set Global Configuration.......................................................................... 2-32

Set Channel Configuration........................................................................ 2-32

Do Housekeeping...................................................................................... 2-32

Checksums.................................................................................................... 2-33

Errors............................................................................................................. 2-33

Power-Up Protocol........................................................................................ 2-33

Inguard Unresponsive................................................................................... 2-33

Inguard Software Description....................................................................... 2-33

Hardware Elements....................................................................................... 2-34

Channel MUX........................................................................................... 2-34

Function Relays........................................................................................ 2-35

Stallion Chip and Signal Conditioning..................................................... 2-36

A/D ........................................................................................................... 2-39

DISCHARGE Signal ................................................................................ 2-42

Open-Thermocouple Detector .................................................................. 2-42

Channel Measurements................................................................................. 2-42

Reading Rates........................................................................................... 2-42

Measurement Types.................................................................................. 2-43

Autoranging.............................................................................................. 2-45

Overload ................................................................................................... 2-45

Housekeeping Readings................................................................................ 2-45

Reading Types .......................................................................................... 2-45

Housekeeping Schedule............................................................................ 2-46

Self-Tests....................................................................................................... 2-47

Power-Up Self-Tests................................................................................. 2-47

Self-Test Command.................................................................................. 2-47

(continued)

3 Maintenance....................................................................................... 3-1

Introduction....................................................................................................... 3-3

Self-Test Diagnostics and Error Codes ............................................................. 3-3

Cleaning............................................................................................................. 3-6

AC Fuse Replacement....................................................................................... 3-7

DC Fuse Replacement....................................................................................... 3-8

4 Performance Verification................................................................... 4-1

Introduction....................................................................................................... 4-3

Configuring the Performance Test Setup...................................................... 4-3

Initializing the Performance Test Setup........................................................ 4-5

Accuracy Performance Tests............................................................................. 4-6

Master Alarm Output Tests........................................................................... 4-7

RS-232 Master Alarm Output Test........................................................... 4-7

Fluke DAQ Master Alarm Output Test .................................................... 4-7

iii

Page 10

268XA

Service Manual

Trigger Input Tests........................................................................................ 4-7

RS-232 Trigger Input Test........................................................................ 4-7

Fluke DAQ Trigger Input Test ................................................................. 4-8

Trigger Output Tests..................................................................................... 4-8

RS-232 Trigger Output Test..................................................................... 4-8

Fluke DAQ Trigger Output Test............................................................... 4-8

Volts DC Accuracy Test (PAI Module)........................................................ 4-9

Volts DC Accuracy Test (FAI Module)........................................................ 4-10

Volts AC Accuracy Test ............................................................................... 4-11

Frequency Accuracy Test.............................................................................. 4-11

Analog Channel Integrity Test...................................................................... 4-12

Open Thermocouple Response Test.............................................................. 4-12

2-Wire Resistance Accuracy Test (PAI) - Optional...................................... 4-13

2-Wire Resistance Accuracy Test (FAI Module) - Optional ........................ 4-14

4-Wire Resistance Accuracy Test (PAI Module).......................................... 4-16

4-Wire Resistance Accuracy Test (FAI Module).......................................... 4-19

Digital Input/Output Tests............................................................................. 4-20

RS-232 Digital Input/Output Test............................................................. 4-20

Fluke DAQ Digital Input/Output Test...................................................... 4-21

DIO Relay/Fuse Tests................................................................................... 4-21

RS-232 DIO Relay Fuse Test................................................................... 4-21

Fluke DAQ DIO Relay Fuse Test............................................................. 4-21

Totalizer Tests............................................................................................... 4-22

RS-232 Totalizer Count Test.................................................................... 4-22

RS-232 Totalizer Count and Enable Test ................................................. 4-22

RS-232 Totalizer Count and Direction Test ............................................. 4-22

RS-232 Totalizer Count and Debounce Test............................................ 4-23

Fluke DAQ Totalizer Count Test.............................................................. 4-23

Fluke DAQ Totalizer Count and Enable Test........................................... 4-23

Fluke DAQ Totalizer Count and Direction Test....................................... 4-24

Fluke DAQ Totalizer Count and Debounce Test...................................... 4-24

5 Calibration.......................................................................................... 5-1

Introduction....................................................................................................... 5-3

Calibration......................................................................................................... 5-3

Methods of Calibration...................................................................................... 5-3

Preparing for Calibration................................................................................... 5-3

Ending Calibration............................................................................................. 5-6

RS-232 Device Configuration Parameters ........................................................ 5-6

Manual Calibration Procedure........................................................................... 5-7

Manual Calibration Commands......................................................................... 5-9

V DC Calibration Procedure......................................................................... 5-10

V AC Calibration Procedure......................................................................... 5-12

Resistance Calibration Procedure.................................................................. 5-13

Frequency Calibration Procedure.................................................................. 5-15

6 Diagnostic Testing and Troubleshooting......................................... 6-1

Introduction....................................................................................................... 6-3

Servicing Surface-Mount Assemblies............................................................... 6-3

Error Detection.................................................................................................. 6-4

FLASH ROM Parameter Defaults................................................................ 6-7

Background Testing...................................................................................... 6-7

Retrieving Error Codes using RS-232........................................................... 6-8

Selecting the Diagnostic Tools.......................................................................... 6-8

iv

Page 11

Contents

Diagnostic Tool dio....................................................................................... 6-8

Diagnostic Tool rELAy................................................................................. 6-9

Diagnostic Tool idS....................................................................................... 6-9

Diagnostic Tool conF.................................................................................... 6-10

Diagnostic Display Test................................................................................ 6-11

COMM Parameter Reset............................................................................... 6-11

Using the RS-232 Interface............................................................................... 6-11

Command Processing.................................................................................... 6-11

Device Configuration.................................................................................... 6-12

Command Set................................................................................................ 6-13

Troubleshooting the Device............................................................................... 6-25

General Troubleshooting............................................................................... 6-25

Sys/Ctrl PCA Troubleshooting...................................................................... 6-36

Troubleshooting the Sys/Ctrl PCA Digital Kernel ................................... 6-36

Troubleshooting the RS-232 Interface...................................................... 6-36

Troubleshooting the Ethernet Interface .................................................... 6-37

Troubleshooting the Keypad, Master Alarm Output, Trigger Input,

and Trigger Out Lines............................................................................... 6-37

Troubleshooting the Power Supply........................................................... 6-37

A2 Display PCA Troubleshooting................................................................ 6-37

Variations in the Display .......................................................................... 6-39

PCMCIA PCA Troubleshooting................................................................... 6-40

A/D Power Supply PCA Troubleshooting.................................................... 6-40

DIO Module Troubleshooting....................................................................... 6-40

Digital Input Buffers................................................................................. 6-41

Digital Output Drivers.............................................................................. 6-41

Relay Output Drivers................................................................................ 6-41

Totalizer Input........................................................................................... 6-42

Totalizer Enable........................................................................................ 6-42

Digital Output PCA Troubleshooting........................................................... 6-42

A3 A/D Converter Module Troubleshooting................................................ 6-42

A3 Kernel.................................................................................................. 6-42

Break/Reset Circuit................................................................................... 6-43

Out of Tolerance Readings....................................................................... 6-43

Troubleshooting Relay Problems.............................................................. 6-44

A4 Analog Input PCA Troubleshooting........................................................ 6-44

Troubleshooting Calibration Failures................................................................ 6-44

Retrieving Calibration Constants.................................................................. 6-45

FlukeDAQ Software.......................................................................................... 6-47

(continued)

7 Replaceable Parts.............................................................................. 7-1

Introduction....................................................................................................... 7-3

How to Obtain Parts .......................................................................................... 7-3

Service Centers.................................................................................................. 7-3

Parts Lists.......................................................................................................... 7-4

8 Schematics......................................................................................... 8-1

Introduction....................................................................................................... 8-3

v

Page 12

268XA

Service Manual

vi

Page 13

List of Tables

Table Title Page

1-1. 268XA General Specifications.............................................................................. 1-8

1-2. 268X Real-Time Clock and Calendar.................................................................... 1-9

1-3. Trigger In Specification......................................................................................... 1-9

1-4. Trigger Out Specification...................................................................................... 1-9

1-5. Master Alarm Output Specification....................................................................... 1-10

1-6. 2686A - Active Channels and Number of Scans to Card Capacity....................... 1-10

1-7. PAI A/D DC Voltage General Specifications........................................................ 1-11

1-8. PAI A/D DC Voltage Range and Resolution Specifications................................. 1-12

1-9. PAI A/D DC Voltage Accuracy Specifications..................................................... 1-12

1-10. PAI A/D AC Voltage General Specifications........................................................ 1-13

1-11. PAI A/D AC Voltage Range and Resolution Specifications................................. 1-13

1-12. PAI A/D AC Voltage Accuracy Specifications..................................................... 1-14

1-13. PAI A/D 4-Wire Resistance Temperature Coefficient .......................................... 1-15

1-14. PAI A/D 4-Wire Resistance Range and Resolution Specifications....................... 1-15

1-15. PAI A/D 4-Wire Resistance Accuracy Specifications........................................... 1-15

1-16. PAI A/D 4-Wire RTD Temperature Coefficient.................................................... 1-16

1-17. PAI A/D 4-Wire RTD Specifications.................................................................... 1-16

1-18. PAI A/D Thermocouple General Specifications.................................................... 1-17

1-19. PAI A/D Thermocouple Specifications ................................................................. 1-18

1-20. PAI A/D Frequency Accuracy Specifications ....................................................... 1-20

1-21. PAI A/D Frequency Sensitivity Specifications...................................................... 1-20

1-22. FAI A/D DC Voltage General Specifications........................................................ 1-21

1-23. FAI A/D DC Voltage Resolution and Repeatability Specifications...................... 1-21

1-24. FAI A/D DC Voltage Accuracy Specifications..................................................... 1-22

1-25. FAI A/D AC Voltage General Specifications........................................................ 1-22

1-26. FAI A/D AC Voltage Range and Resolution Specifications................................. 1-23

1-27. FAI A/D AC Voltage Accuracy Specifications..................................................... 1-23

1-28. FAI A/D 4-Wire Resistance Temperature Coefficient .......................................... 1-24

1-29. FAI A/D 4r-Wire Resistance Range and Resolution Specifications...................... 1-24

1-30. FAI A/D 4-Wire Resistance Accuracy Specifications........................................... 1-24

1-31. FAI A/D 4-Wire RTD Temperature Coefficient.................................................... 1-25

1-32. FAI A/D 4-Wire RTD Specifications.................................................................... 1-25

1-33. FAI A/D Thermocouple General Specifications.................................................... 1-26

1-35. FAI A/D Frequency Accuracy Specifications ....................................................... 1-28

1-36. FAI A/D Frequency Sensitivity Specifications...................................................... 1-28

vii

Page 14

268XA

Service Manual

1-37. DIGITAL I/O Specification................................................................................... 1-29

1-38. Totalizer Specification........................................................................................... 1-30

1-39. DIGITAL I/O Relay Specification......................................................................... 1-30

1-40. Models, Options and Accessories.......................................................................... 1-31

2-1. Contoller Connector Description........................................................................... 2-4

2-2. Backplane Connector Description ......................................................................... 2-10

2-3. Range of Buffer Amplifier..................................................................................... 2-19

2-4. Measurement Matrix for DC Volts........................................................................ 2-20

2-5. Measurement Matrix for Ohms.............................................................................. 2-21

2-6. Measurement Matrix for AC Volts........................................................................ 2-22

2-7. Analog/Digital Converter Measurement Cycle...................................................... 2-25

2-8. Tree Bits................................................................................................................. 2-34

2-9. Channel Bits........................................................................................................... 2-35

2-10. Tree and Channel Switch Settling Times............................................................... 2-35

2-11. Function Relays..................................................................................................... 2-36

2-12. Function Relay Settling Time................................................................................ 2-36

2-13. Stallion Switch Settings......................................................................................... 2-37

2-14. Signal Conditioning Settling Time ........................................................................ 2-38

2-15. A/D Command Codes............................................................................................ 2-40

2-16. A/D Readings to Average to Obtain a Measurement............................................. 2-42

2-17. Frequency Sensitivity............................................................................................. 2-44

2-18. A/D Reading to Average to Obtain a Reference Balance Measurement ............... 2-46

3-1. Self-Test Codes...................................................................................................... 3-4

4-1. Recommended Test Equipment............................................................................. 4-4

5-1. RS-232 Device Configuration for Calibration Procedures.................................... 5-6

5-2. Calibration Commands.......................................................................................... 5-9

5-3. Manual Calibration Command Responses............................................................. 5-10

5-4. Manual V dc Calibration........................................................................................ 5-11

5-5. Manual V ac Calibration........................................................................................ 5-13

5-6. Manual Resistance Calibration.............................................................................. 5-15

5-7. Manual Frequency Calibration.............................................................................. 5-15

6-1. Self-Test Error Codes............................................................................................ 6-5

6-2. FLASH ROM Parameter Defaults......................................................................... 6-7

6-3. Corrective Action for Background Error Checking............................................... 6-7

6-4. Device Firmware Descriptions .............................................................................. 6-10

6-5. Device Default COMM Parameters....................................................................... 6-11

6-6. Device Configuration............................................................................................. 6-13

6-7. RS-232 Command Set............................................................................................ 6-14

6-8. Range Settings....................................................................................................... 6-20

6-9. Relating Selftest Errors to Device Problems.......................................................... 6-26

6-10. Hints for Troubleshooting...................................................................................... 6-35

6-11. A2 Display PCA Initialization Routines................................................................ 6-38

6-12. A3 A/D Converter PCA Jumper Positions............................................................. 6-43

6-13. A/D Module Calibration Constants ....................................................................... 6-46

viii

Page 15

List of Figures

Figure Title Page

1-1. 2680A/2685A Device............................................................................................ 1-4

1-2. 268XA Chassis ...................................................................................................... 1-5

2-1. Communication Control System............................................................................ 2-3

2-2. 268XA Main Supply Circuit.................................................................................. 2-4

2-3. System Interface Unit ............................................................................................ 2-6

2-4. FPGA Block Diagram............................................................................................ 2-8

2-5. A3 A/D Converter Block Diagram........................................................................ 2-17

2-6. DC Volts 300 V Range Simplified Schematic....................................................... 2-20

2-7. RTD Measurement Simplified Schematic............................................................. 2-21

2-8. AC Volts #V Range Simplified Schematic............................................................ 2-23

2-9. Integrator Output Waveform for Input Near 0....................................................... 2-26

2-10. Integrator Output Wavefrom for Input Near + Full Scale ..................................... 2-26

2-11. Integrator Output Waveform for Input Near - Full Scale ...................................... 2-27

2-12. A/D Timing (FAI Normal Reading) ...................................................................... 2-39

2-13. A/D Timing (PAI Normal Reading, PAI and FAI Reference Balance)................. 2-39

2-14. A/D Status Signals................................................................................................. 2-40

3-1. Replacing the Fuse................................................................................................. 3-7

3-2. DC Fuse Location.................................................................................................. 3-9

4-1. Connection Between Device and Host .................................................................. 4-5

4-2. 2-Wire Connections to 5700A............................................................................... 4-15

4-3. 4-Wire Connections to the Universal Input Module (Resistor)............................. 4-16

4-4. 4-Wire Connections to the Universal Input Module (5700A) ............................... 4-17

4-5. DIO Connector Module......................................................................................... 4-20

5-1. Device and Host Computer Calibration Setup....................................................... 5-5

5-2. Universal Input Module Calibration Connections................................................. 5-5

5-3. Two-Wire Calibration Connection........................................................................ 5-6

5-4. Four-Wire Calibration Connection........................................................................ 5-7

6-1. Display Test Pattern #1.......................................................................................... 6-38

6-2. Display Test Pattern #2.......................................................................................... 6-38

7-1. 268XA Final Assembly.......................................................................................... 7-10

7-2. Blank Module ........................................................................................................ 7-11

7-3. DIO Module........................................................................................................... 7-13

7-4. FAI Module............................................................................................................ 7-15

7-5. PAI Module............................................................................................................ 7-17

7-6. Isothermal Input..................................................................................................... 7-18

ix

Page 16

268XA

Service Manual

8-1. Backplane PCA...................................................................................................... 8-3

8-2. Controller/System Power PCA.............................................................................. 8-5

8-3. Digital I/O PCA..................................................................................................... 8-11

8-4. Backplane Extender PCA...................................................................................... 8-15

8-5. Extender PCA........................................................................................................ 8-17

8-6. A/D Supply Assembly........................................................................................... 8-19

8-7. PCMCIA PCA ....................................................................................................... 8-21

8-8. Output PCA............................................................................................................ 8-23

8-9. A/D (PFE) PCA..................................................................................................... 8-25

8-10. A/D (FFE) PCA..................................................................................................... 8-32

8-11. Analog Input Connector PCA................................................................................ 8-39

8-12. Display PCA.......................................................................................................... 8-41

x

Page 17

Chapter 1

Introduction and Specifications

Title Page

Introduction....................................................................................................... 1-3

Block Diagrams................................................................................................. 1-5

Specifications .................................................................................................... 1-7

2680A/2686A Combined Specifications....................................................... 1-7

2680A/2686A General Specifications............................................................... 1-8

Real-Time Clock and Calendar......................................................................... 1-9

Trigger In Specifications................................................................................... 1-9

Trigger Out Specifications ................................................................................ 1-9

Master Alarm Output Specification................................................................... 1-10

Communication I/O........................................................................................... 1-10

2686A PC Card Storage .................................................................................... 1-10

Precision Analog Input (PAI) A/D Specifications............................................. 1-11

Specifications PAI A/D DC Voltage Measurement...................................... 1-11

PAI A/D AC Voltage Measurement Specifications...................................... 1-13

PAI A/D 4-Wire Resistance Measurement Specifications............................ 1-15

PAI A/D 2-Wire Resistance Measurement Specifications............................ 1-16

PAI A/D 4-Wire RTD per ITS-1990 Measurement Specifications .............. 1-16

PAI A/D 2-Wire RTD per ITS-1990 Measurement Specifications .............. 1-16

PAI A/D Thermocouple per ITS-1990 Measurement Specifications............ 1-17

PAI A/D Frequency Measurement Specifications........................................ 1-20

Fast Analog Input (FAI) A/D Specifications..................................................... 1-21

FAI A/D DC Voltage Measurement Specifications...................................... 1-21

FAI A/D AC Voltage Measurement Specifications...................................... 1-22

FAI A/D 4-Wire Resistance Measurement Specifications............................ 1-24

FAI A/D 2-Wire Resistance Measurement Specifications............................ 1-25

FAI A/D 4-Wire RTD per ITS-1990 Measurement Specifications .............. 1-25

FAI A/D Thermocouple per ITS-1990 Measurement Specifications............ 1-26

FAI A/D Frequency Measurement Specifications........................................ 1-28

Digital Input/Output Module............................................................................. 1-29

Digital Input/Output Specifications .............................................................. 1-29

Totalizer Input Specifications....................................................................... 1-30

Digital Relay Specifications.......................................................................... 1-30

Options and Accessories.................................................................................... 1-31

1-1

Page 18

268XA

Service Manual

1-2

Page 19

Introduction

The 268XA Service Manual supports the performance testing, calibration, servicing, and

maintenance of the 2680A Data Acquisition System (DAS), the 2686A Data Logging

System (DLS) and modules. See Figure 1-1 for a view of the 268XA.

The 2686A comes with a removable PC Card (PCMCIA) for stand-alone storage

operation. This socket accepts ATA memory cards up to 2 GB in size.

Each 268XA device can hold from 1 to 6 analog modules. These modules are the

Precision Analog module (PAI), Fast Analog module (FAI), and the Digital IO/Relay and

Totalizer module (DIO). These modules are all isolated from one another. You can add

the DIO module to the device in slot 6 only.

The analog modules measure dc volts, ac volts, ohms, temperature, frequency, and dc

current. Temperature measurements use thermocouples, thermistors or resistance

temperature detectors (RTDs). The devices also have extensive computed math

capability. Besides using data collected from the analog modules and digital totalizer,

time can also be used in computed channel calculations.

The system scans 20 to 120 analog channels and calculates the values for up to 60

computed channels. Interval timers, alarm conditions, and/or an external signal input can

trigger scans. The Fluke DAQ software configures and controls up to 99 268XA devices

via an Ethernet connection. The software provides the means to view scan data and log it

into files.

Introduction and Specifications

Introduction

1

The analog modules that may be used with the 268XA are the FAI module and the PAI

module. The PAI modules emphasize precision with 5 ½ digits of resolution, .02%

accuracy, and can withstand up to 150 V common mode voltage (300 V on channels 1

and 11). The FAI modules emphasize increased measurement speed with 4 ½ digits of

resolution, 0.04% accuracy, and can withstand up to 50 V common mode voltage. Device

specifications are provided later in this chapter.

1-3

Page 20

268XA

Service Manual

2680 SERIES DAQ SYSTEM

REVIEW

MAX

REM

LAST

SCAN

MIN

AUTO

SET

FUNC

MON

Mx+B

F

ALARM

C F RO

mV AC DC

LIMIT

x1Mk

HI

Hz

OFF

PRN

12

CH

LO

CAL

EXT

TR

Figure 1-1. 2680A/2686A Device

alg46f.eps

1-4

Page 21

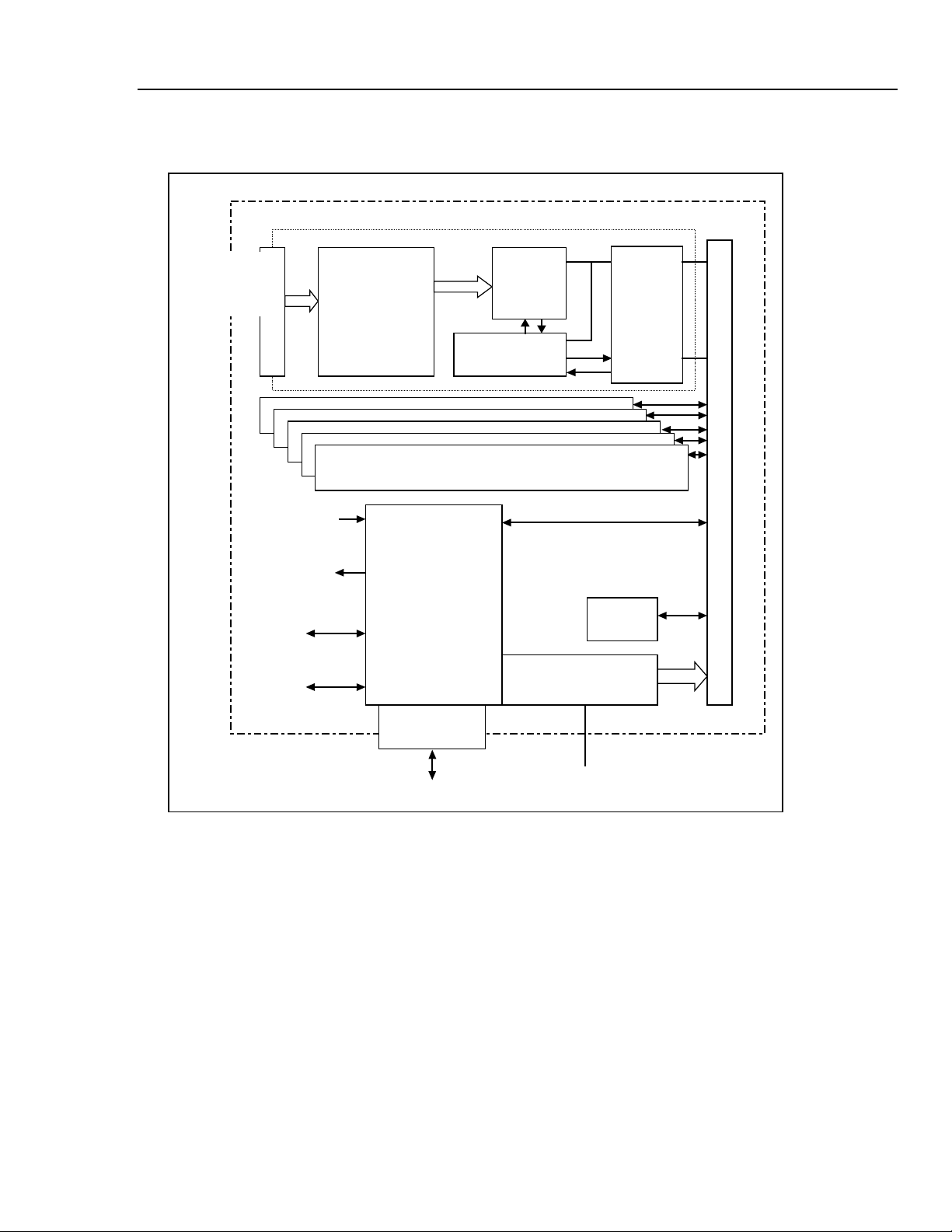

Block Diagrams

Removable 20

channel input

port with built in

temp sensor

A/D #2

A/D #3

A/D #4

External Trig in

External Trig out

TCP/IP

Network

A/D Input Card (one of six)

Switch Matrices

(FET or Relay)

A/D #5

DIO or A/D #6

Controller

RAM

FLASH

Real Time clock

Ethernet

Filter

and

A/D

circuits

Ctrl

Microprocessor

Data

Power

Data

Ctrl

Introduction and Specifications

Block Diagrams

Isolated

Power

Power

Daughter

Card

Optoisolators

Display/

Keypad

M

o

t

h

e

r

b

o

a

r

d

/

C

o

n

t

r

o

l

l

e

r

1

RS232

(cal/test)

RS232

PCMCIA Type II

Memory Slot

ATA Card

Figure 1-2. 268XA Chassis

A/C and Battery

Supply Circuits

Line Voltage or

Battery Voltage

DC

Power

Bus

alg50f.eps

1-5

Page 22

268XA

Service Manual

Digital I/O Output Card

Removable

Connector

Card

A/D #1

External Trig in

Tcp/IP

Network

A/D #2

A/D #3

Digital I/O

Totalizer (1)

A/D #4

A/D #5

(20) and

Relay

Contact

(8 pr)

Ctrl

Controller

RAM

FLASH

Real Time clock

Ethernet

Ctrl

Microprocessor

and drivers

Data

Data

Ctrl

Isolated

Power

Power

Daughter

Card

Optoisolators

Display/

Keypad

M

o

t

h

e

r

b

o

a

r

d

/

C

o

n

t

r

o

l

l

e

r

RS232

(cal/test)

A/C and Battery

RS232

PCMCIA Type II

Memory Slot

ATA Card

Supply Circuits

Line Voltage or

Battery Voltage

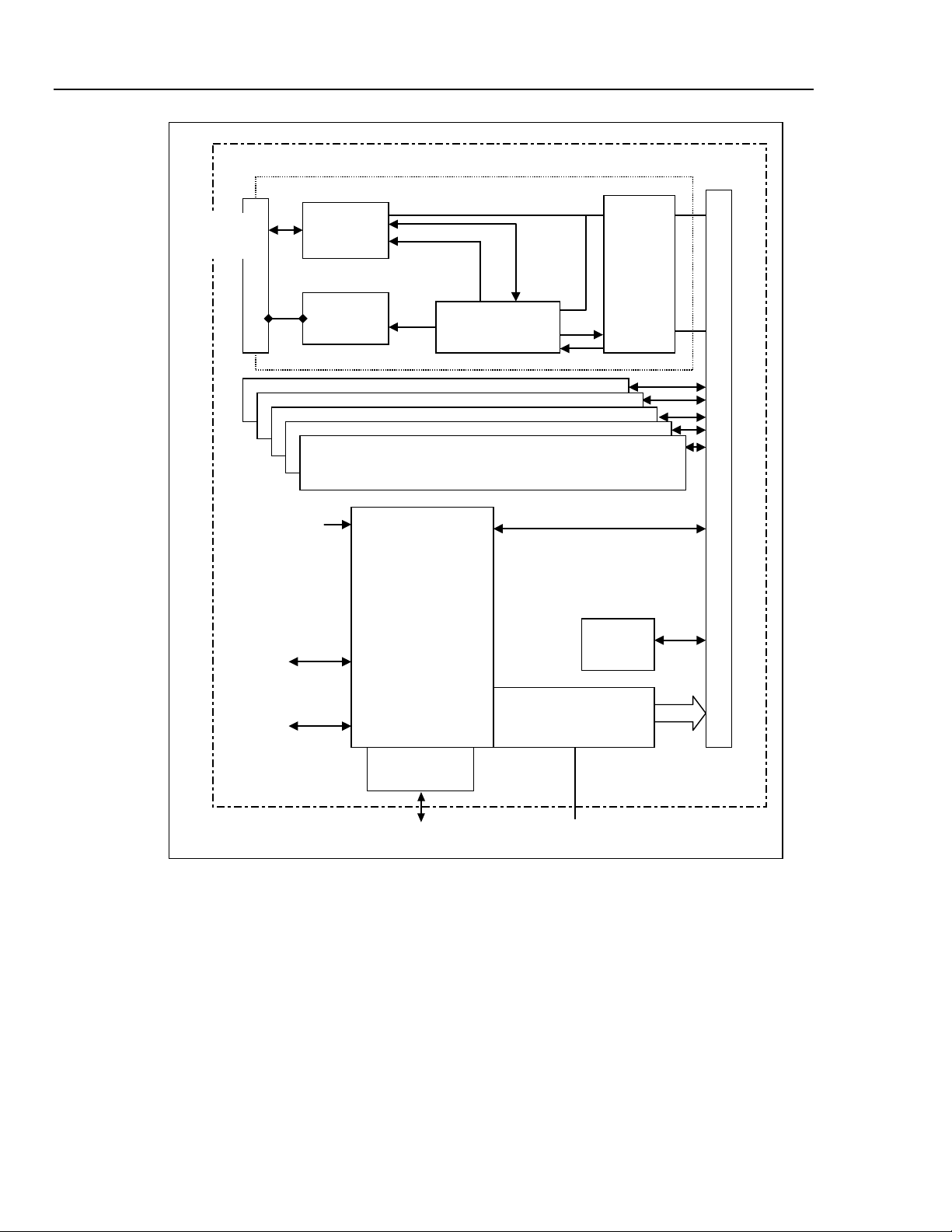

Figure 1-2. 268XA Chassis (cont)

DC

Power

Bus

alg51f.eps

1-6

Page 23

Specifications

Specifications are divided into four sections. The first section contains the specifications

that apply to both the 2680A and 2686A devices. The second section contains

specifications that apply only to the Precision A/D Input (PAI) module. The third section

contains specifications that apply only to the Fast A/D Input (FAI) module. The last

section contains informat ion on ly for the dig ita l I/O rela y an d the tota li zer (D IO ) mo dule .

2680A/2686A Combined Specifications

The following specifications apply to both the 2680A and 2686A devices. The topics

include:

• General Specifications

• PAI/FAI Environmental Specifications

• DIO Digital I/O and Totalizer Interface

Introduction and Specifications

Specifications

1

1-7

Page 24

268XA

Service Manual

2680A/2686A General Specifications

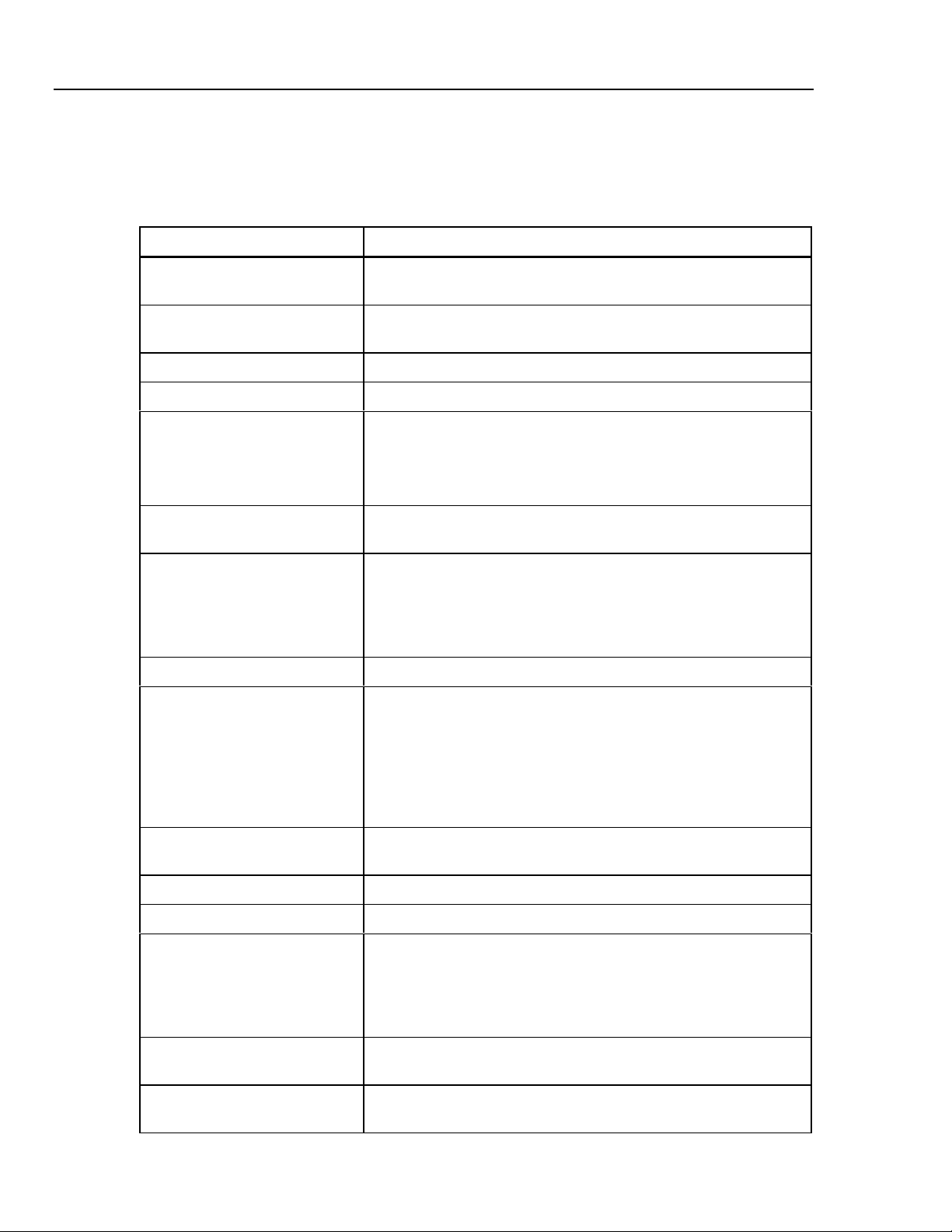

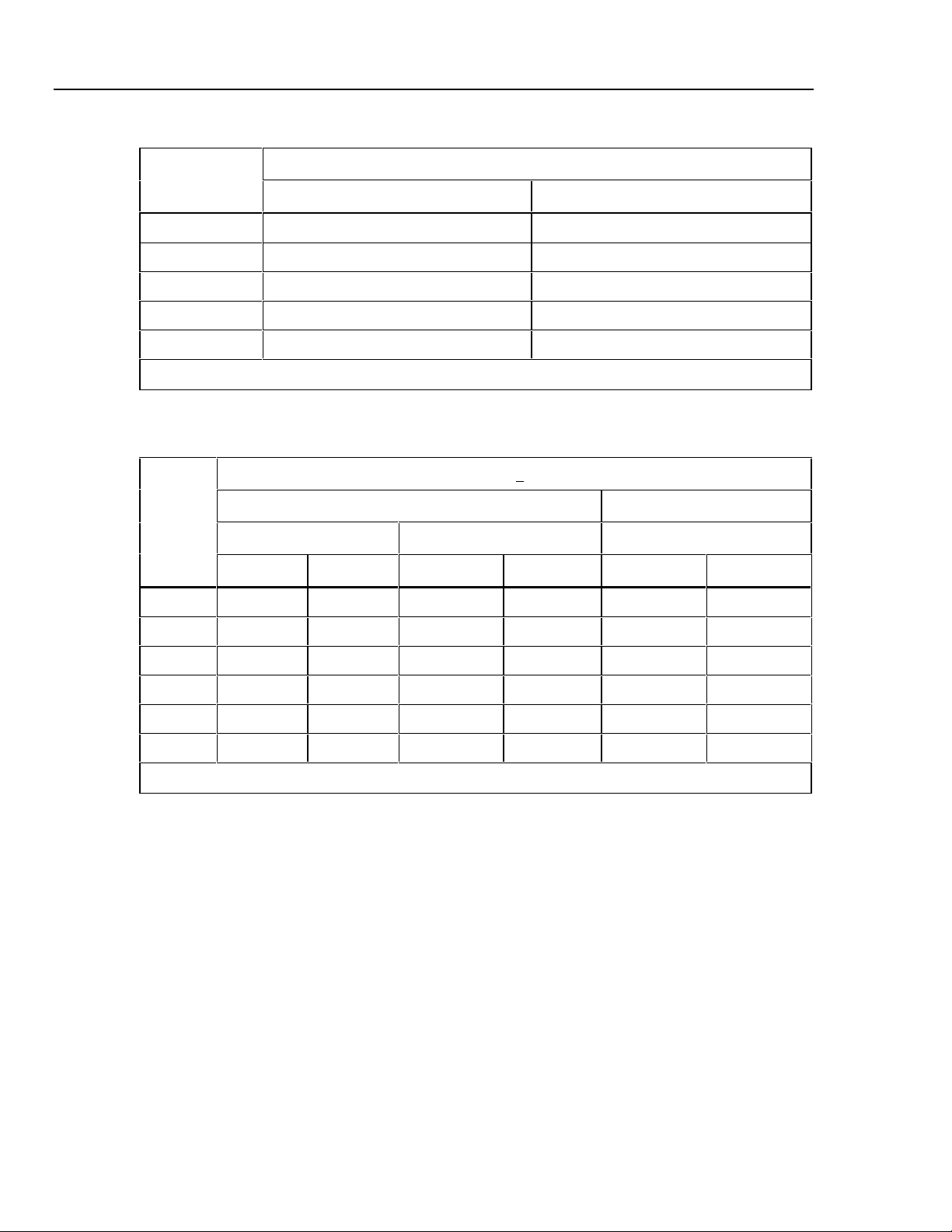

Table 1-1 provides the general specifications for the 2680A and 2686A devices.

Table 1-1. 268XA General Specifications

Specification Characteristic

Input Channel Capacity Maximum of 120 channels (Precision or Fast Analog Input) per

chassis

Optional DIO 20 digital input and outputs channels, 8 double pole-single throw

relay channels, a totalizer input, and a totalizer enable input.

Computed Channels 60

Size 473 mm (18.6 in) x 423 mm (17 in) x 237 mm (9.3 in)

Weight 2680A/2686A (empty) 8.5 kg (18.9 lb)

2680A – FAI 0.8 kg (1.8 lb)

2680A – PAI 1.2 kg (2.7 lb)

2680A – DIO 0.8 kg (1.8 lb)

Power 100 – 240 V ac (no switching required), 50 to 60 Hz, 100 VA

maximum or optional 9 V dc to 45 V dc, 35 W maximum

EMC EN50082-2

EN55022-1

EN55011 class A

EN610000-4-2,3,4,6,8

EN61326

Safety EN61010-1, CAT II (DIO is rated CAT I) CSA C22.2 No. 1010.1

Serial Interface Connector: 9 pin male (DB9)

Signals: Tx, Rx, DTR, RTS, GND

Modem Control: full duplex

Baud rates: 4800, 9600, 19200, 38400 (19,200 default)

Data format: 8 data bits, no parity, one stop bit

Flow Control: XON/XOFF

Echo: off

Common Mode Voltage Precision Analog Input: 150 (300 on channels 1 and 11) Fast

Analog Input: 50 V dc or 30 V ac rms

Operating Temperature Range -20 oC to 60 oC (-4 oF to +140 oF)

Storage Temperature Range -40 oC to 70 oC (-40 oF to +158 oF)

Relative Humidity 90% maximum for -10 oC to 28 oC (14 oF to +82 oF)

75% maximum for 28

50% maximum for 35

(3 MΩ range, reduce humidity rating by 25% for 1 hour warm-up.

3 MΩ range meets full humidity ratings with 2 hour warm-up)

o

C to 35 oC (82 oF to +95 oF)

o

C to 60 oC (95 oF to +140 oF)

1-8

Altitude Operating: 2,000 m (6,561 ft) maximum

Non-operating: 12,200 m (40,000 ft) maximum

Warm-up Time 1 hour to rated specifications -or- 15 minutes if relative humidity

(non-condensing) is 50% or less.

Page 25

Introduction and Specifications

Real-Time Clock and Calendar

Real-Time Clock and Calendar

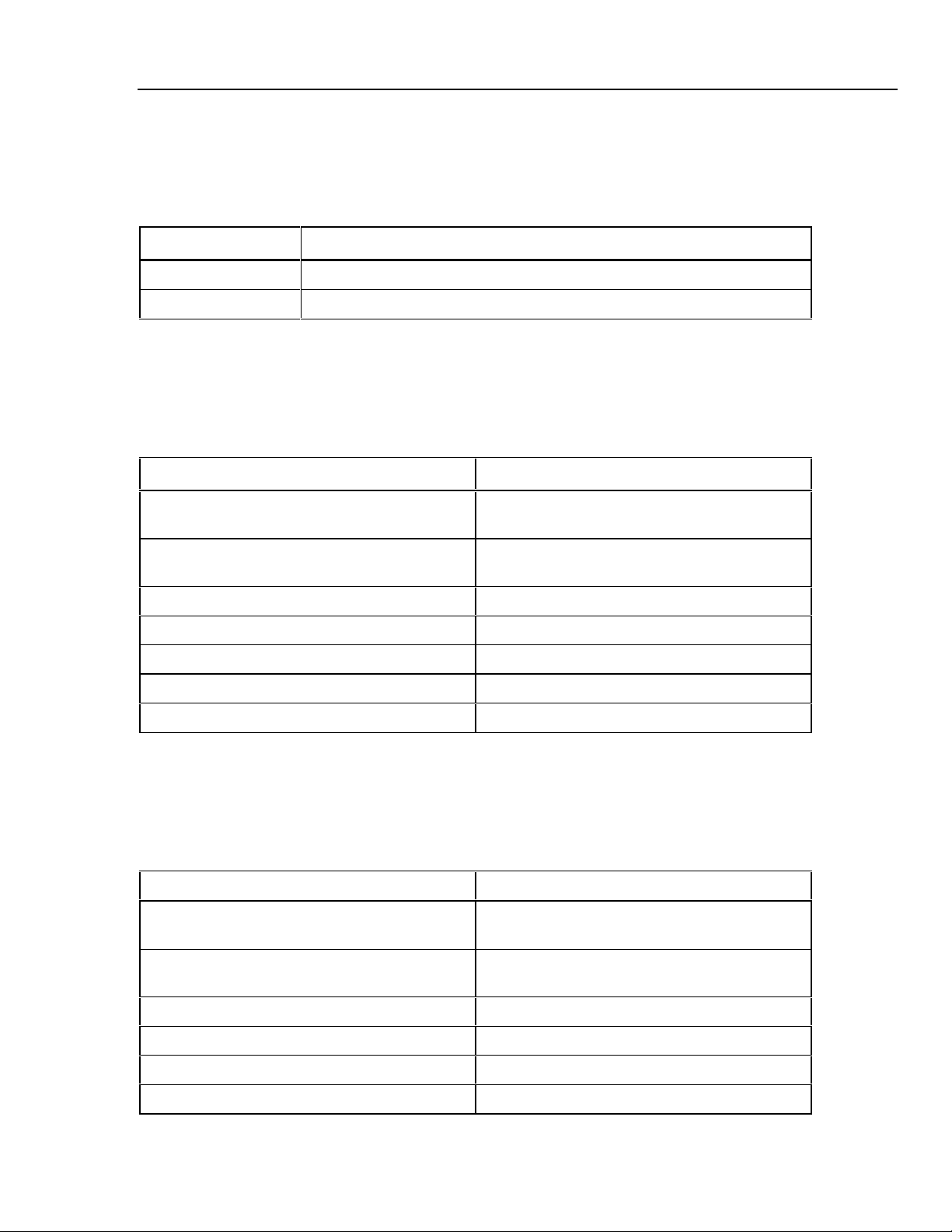

The next table provides a summary of the battery powered real-time clock and calendar.

Table 1-2. 268X Real-Time Clock and Calendar

Specification Characteristic

Accuracy 1 minute per month for 0 °C to 50 °C range

Battery Life >5 unpowered device years for 20 °C to 28 °C (68 °F to 82.4 °F).

Trigger In Specifications

The following table provides a summary of the Trigger In specifications. The Trigger In

input is located on the rear panel connector, terminals Trigger In and Signal GND.

Table 1-3. Trigger In Specification

Specification Characteristic

Logical High - Trigger not set Minimum: 2.0 V

Maximum: 7.0 V

1

Logical Low - Trigger set Minimum: -0.6 V

Maximum: +0.8 V

Compatibility TTL or Contact Closure

Isolation None (dc coupled)

Minimum Pulse Width 5 µs

Maximum Frequency Nominal 400 Hz

Repeatability 3 ms

Trigger Out Specifications

The next table provides a summary of the Trigger Out specifications. The Trigger Out

output is located on the rear panel connector, terminals Trigger Out and Signal GND.

Table 1-4. Trigger Out Specification

Specification Characteristic

TTL Logical Zero - Trigger Out Set 0.8 V maximum for an Iout of -1.0 mA (1 LSTTL

load)

TTL Logical One - Trigger Out Not Set 3.8 V minimum for an Iout of 0.05 mA (1 LSTTL

load)

Non-TTL Logical Zero - Trigger Out Set 1.8 V maximum for an Iout of -20 mA

Non-TTL Logical One - Trigger Out Not Set 3.25 V minimum for an Iout of -50 mA

Pulse Duration (Logic Low) 125 µs

Isolation None

1-9

Page 26

268XA

Service Manual

Master Alarm Output Specification

Communication I/O

The following specifications cover the Master Alarm output. The Master Alarm output is

located on the rear panel connector, terminals Master Alarm, and Signal GND.

Table 1-5. Master Alarm Output Specification

Specification Characteristic

Output Voltage - TTL Logical Zero 0.8 V maximum for an Iout of -1.0 mA (1 LSTTL

load)

Output Voltage - TTL Logical One 3.8 V minimum for an Iout of 0.05 mA (1 LSTTL

load)

Output Voltage - Non-TTL Load Zero 1.8 V maximum for an Iout of -20 mA

Output Voltage - Non-TTL Load One 3.25 V minimum for an Iout of -50 mA

Communication with 268XA devices can be accomplished through either a 10/100BaseT

interface or through an RS-232 port. The 10/100BaseT provides the primary

communication interface. The RS-232 is used for calibration and limited debug

capability.

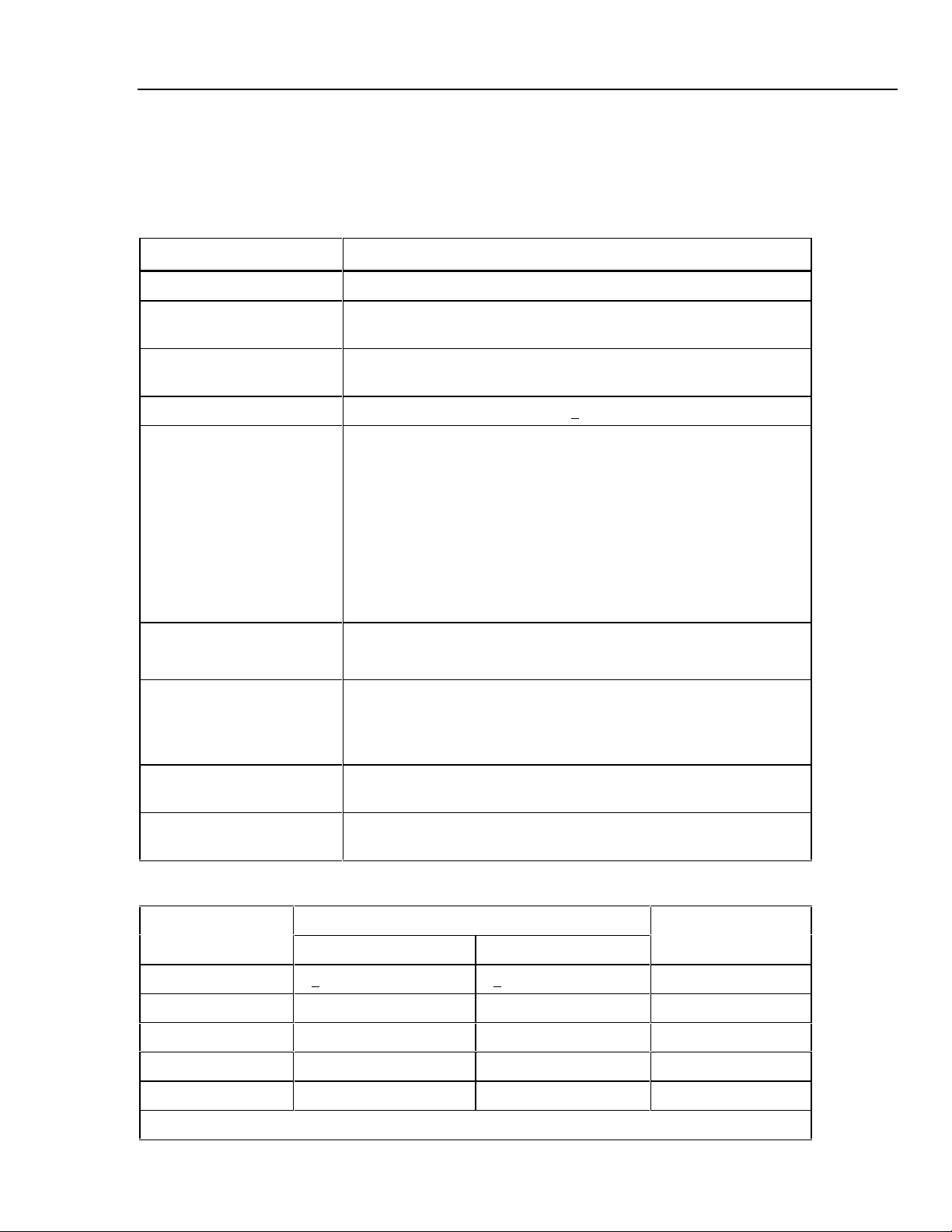

2686A PC Card Storage

The 2686A supports a non-volatile PC Card (PCMCIA ATA type card) memory module

option. This table provides a list of active channels and the number of scans to memory

card capacity. The standard Controller card will store approximately 600,000 readings.

Table 1-6. 2686A - Active Channels and Number of Scans to Card Capacity

Memory Card/

Active Channels 20 ch 40 ch 60 ch 80 ch 100 ch 120 ch

16 MB 100,548 66,765 50,074 40,059 33,382 28,613

128 MB 800,000 528,000 400,000 320,000 264,000 224,000

256 MB 1.6 M 1.056 M 800,000 640,000 528,000 448,000

512 MB 3.2 M 2.112 M 1.6 M 1.28 M 1.056 M 896,000

1 GB 6.2 M 4.224 M 3.2 M 2.56 M 2.112 M 1.792 M

Estimating space: 80 bytes/scan + 4 bytes/channel scanned (allow 4.5% overhead for card formatting)

1-10

Page 27

Introduction and Specifications

Precision Analog Input (PAI) A/D Specifications

Precision Analog Input (PAI) A/D Specifications

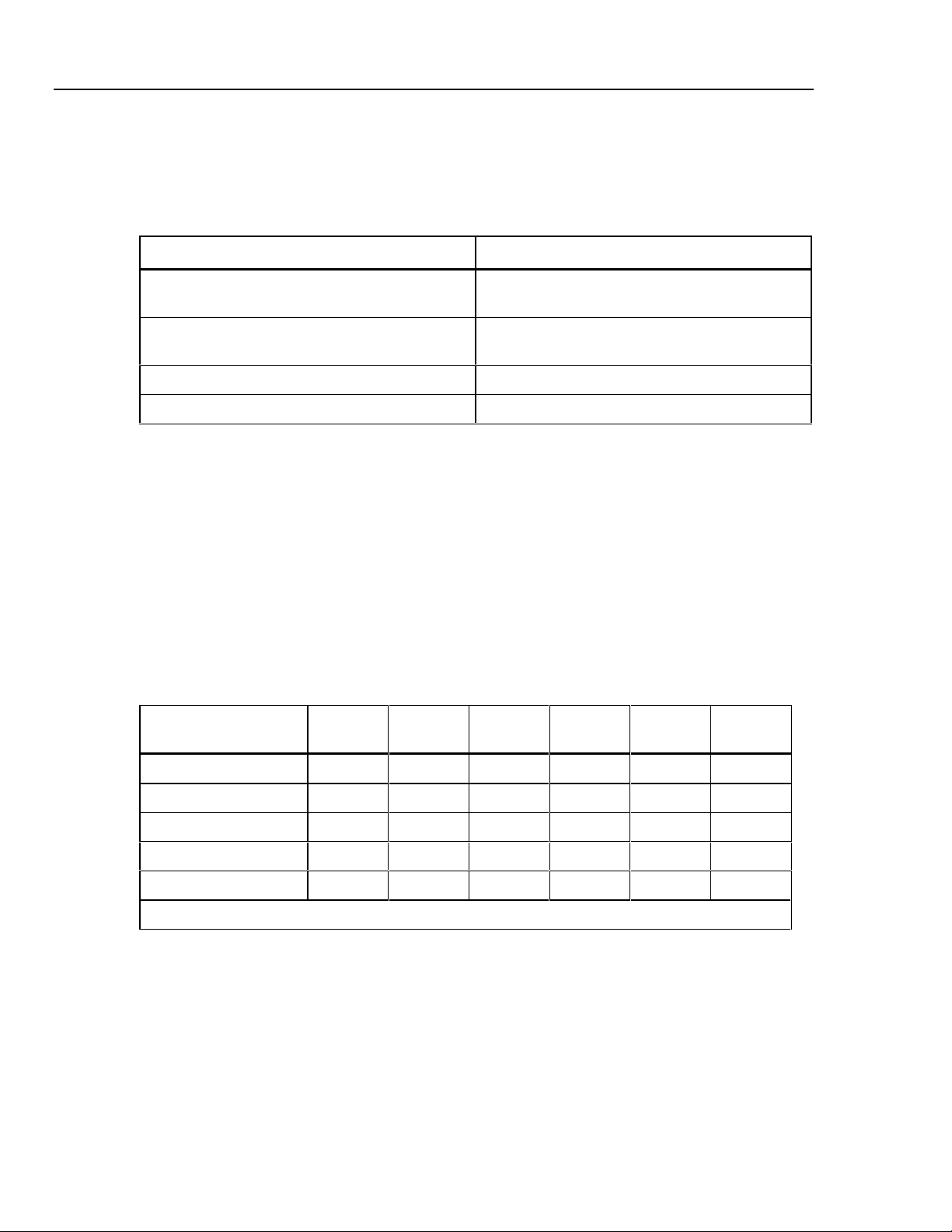

This section includes specifications specific to the PAI A/D instrument by measurement

function.

Specifications PAI A/D DC Voltage Measurement

The following tables provide PAI A/D specifications for the dc voltage measurement

function.

Table 1-7. PAI A/D DC Voltage General Specifications

Specification Characteristic

Input Impedance 100 MΩ in parallel with 300 pF maximum for ranges <=3 V

10 MΩ in parallel with 100 pF maximum for ranges >3 V

Normal Mode Rejection 50 dB minimum at 50 Hz/60 Hz +0.1%, Slow Rate

Common Mode Rejection 120 dB minimum at dc, 50 Hz/60 Hz +0.1%, 1 kΩ imbalance, Slow

Rate

80 dB minimum at dc, 50 Hz/60 Hz +0.1%, 1 kΩ imbalance, Medium

and Fast Rates

1

Channel-to-Channel Cross talk 120 dB minimum Slow Rate (e.g., 30 V dc on channel 1 may cause a

30 µV error on channel 2)

100 dB minimum Medium and Fast Rates (e.g., 1V dc on channel 1

may cause a 10 µV error on channel 2)

Temperature Coefficient For % input: Add 1/10th the 90-day specification per °C above 28 °C or

below 18 °C

For floor error (V): Add 1/20th the 90-day specification per °C above

28 °C or below 18 °C

Accuracy at -20 °C Multiply the -10 °C to +60 °C accuracy specification by 2. After 1 hour

warm-up. For accurate between -10 °C and -20 °C, interpolate linearly.

Maximum Input Voltage The lesser voltage of:

300 V from any terminal on channels 1 and 11 to earth;

150 V from any terminal on channels 2 through 10, and 12 through 20

to earth;

300 V from any terminal on channels 1 and 11 to any other terminal;

150 V from any terminal on channels 2 through 10, and 12 through 20

to any other input terminal

1-11

Page 28

268XA

Service Manual

Table 1-8. PAI A/D DC Voltage Range and Resolution Specifications

Resolution

Range

Slow Fast

90 mV 0.3 µV1 µV

300 mV 1 µV3 µV

3 V 10 µV 30 µV

30 V 100 µV 300 µV

150/300 V 1 mV 3 mV

Note 300 V range applies to channels 1 and 11 only.

Table 1-9. PAI A/D DC Voltage Accuracy Specifications

Accuracy, 3σ + (% input + V)

18 °C to 28 °C -10 °C to 60 °C

Range

90 Day 1 Year 1 Year

Slow Fast Slow Fast Slow Fast

90 mV .01%+7 µV .01%+17 µV .013%+8 µV .013%+18 µV .042%+18.2 µV .042%+44.2 µV

300 mV .01%+15 µV .01%+30 µV .013%+17 µV .013%+35 µV .042%+39 µV .042%+78 µV

750 mV* .01%+40 µV .01%+70 µV .013%+50 µV .013%+80 µV .042%+104 µV .042%+182 µV

3 V .01%+0.1 mV .01%+0.2 mV .013%+0.15 mV .013%+0.2 mV .042%+0.26 mV .042%+0.52 mV

30 V .01%+1.5 mV .02%+3 mV .013%+1.7 mV .026%+3.5 mV .042%+3.9 mV .084%+7.8 mV

150/300 V* .01%+15 mV .04%+30 mV .013%+17 mV .052%+35 mV .042%+39 mV .168%+78 mV

* 300 V range applies to channels 1 and 11 only.

1-12

Page 29

Introduction and Specifications

Precision Analog Input (PAI) A/D Specifications

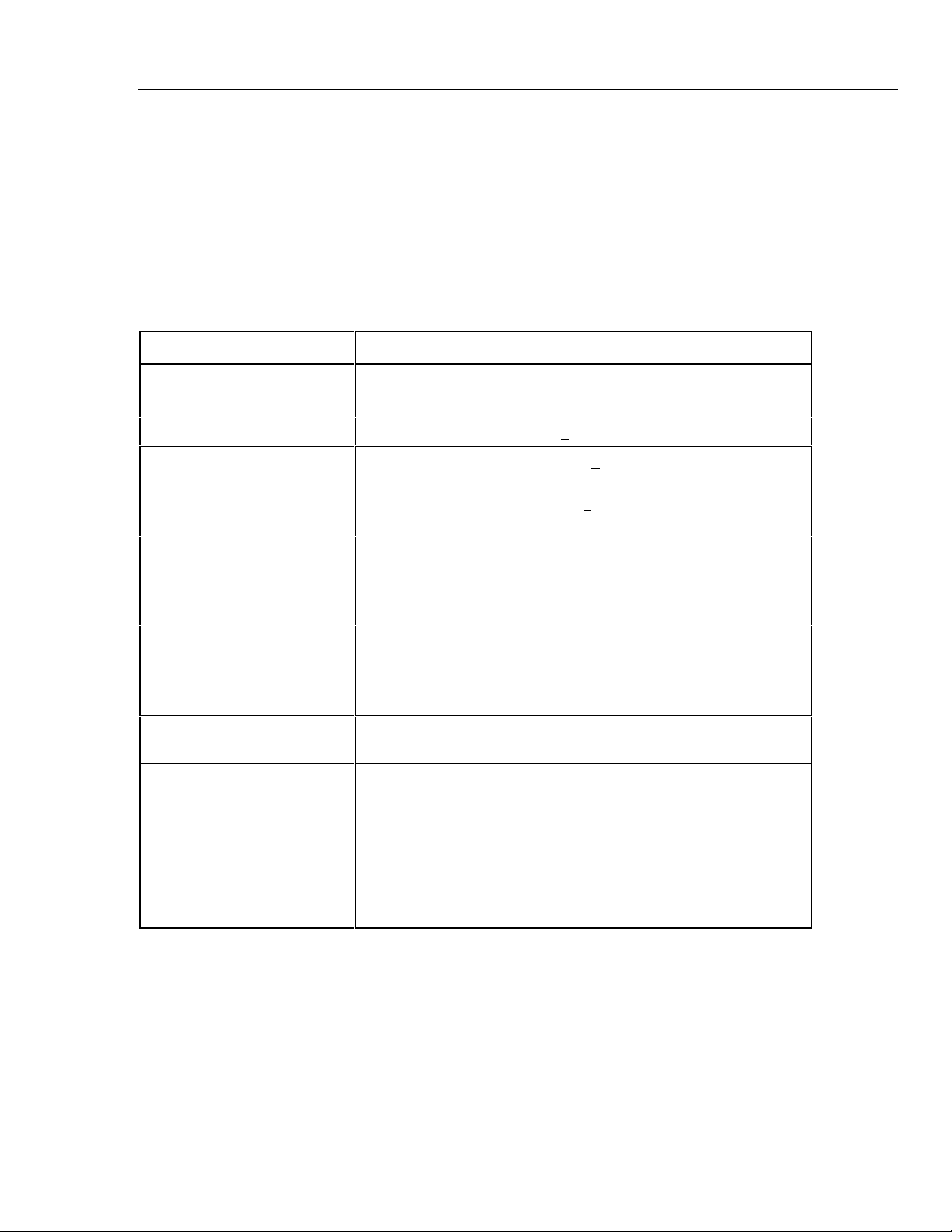

PAI A/D AC Voltage Measurement Specifications

The following tables provide PAI A/D specifications for the ac voltage measurement

function.

Table 1-10. PAI A/D AC Voltage General Specifications

Specification Characteristic

Input Impedance 1 MΩ in parallel with 100 pF

Maximum Crest Factor 3.0 Maximum

2.0 for rated accuracy

Crest Factor Error For nonsinusoidal input signals with crest factors between 2 and 3 and

pulse widths >=100 µs, add 0.2% to the accuracy specifications.

Common Mode Rejection 80 dB minimum at dc, 50 Hz/60 Hz +0.1%, 1 kΩ imbalance, Slow Rate

Maximum Input Voltage The lesser voltage of:

300 V ac rms from any terminal on channels 1 and 11 to earth.

150 V ac rms from any terminal on channels 2 through 10, and 12

through 20 to earth.

1

300 V ac rms from any terminal on channels 1 and 11 to any other

terminal.

150 V ac rms from any terminal on channels 2 through 10 and 12

through 20 to any other input terminal.

Maximum Volt-Hertz Product 2x106 Volt-Hertz product on any range, normal mode input.

1x106 Volt-Hertz product on any range, common mode input.

Temperature Coefficient Linear interpolation between 2 applicable points for temperatures

between 28 °C and 60 °C, or -10 °C and 18 °C, e.g., if the applicable

specification at 28 °C is 2% and the specification at 60 °C is 3%, then

the specification at 40 °C is (3%-2%)x(40-28)/(60-28)+2%=2.375%.

Accuracy at -20 °C Multiply the -10 °C to +60 °C accuracy specification by 2. After 1 hour

warm-up. For accuracy between -10 °C and -20 °C, interpolate lin early .

DC Component Error The presence of a dc voltage will cause an indeterminate error in the

reading of the ac voltage on the input.

Table 1-11. PAI A/D AC Voltage Range and Resolution Specifications

Range Resolution Minimum Input for

Slow Fast Rate Accuracy

Full Scale +30,000 +3,000

300 mV 10 µV 100 µV 20 mV

3 V 100 µV 1 mV 200 mV

30 V 1 mV 10 mV 2 V

150/300 V 10 mV 100 mV 20 V

Note 300 V range applies to channels 1 and 11 only.

1-13

Page 30

268XA

Service Manual

Table 1-12. PAI A/D AC Voltage Accuracy Specifications

1 Year Accuracy + (%input + V) [1]

Range Frequency 18 °C to 28 °C -10 °C to 60 °C

Slow Fast Slow Fast

300 mV 20 to 50 Hz 3%+.25 mV 6%+.5 mV 3.5%+.25 mV 7%+.5 mV

50 to 150 Hz 0.4%+.25 mV 1%+.5 mV 0.5%+.25 mV 1.5%+.5 mV

150 Hz to 10 kHz 0.3%+.25 mV 1%+.5 mV 0.4%+.25 mV 1.5%+.5 mV

10 kHz to 20 kHz 0.4%+.25 mV 1%+.5 mV 0.7%+.25 mV 1.5%+.5 mV

20 kHz to 50 kHz 2%+.3 mV 3%+.5 mV 3%+.3 mV 4%+.5 mV

50 kHz to 100 kHz 5%+.5 mV 5%+1 mV 7%+.5 mV 8%+1 mV

3 V 20 to 50 Hz 3%+2.5 mV 6%+5 mV 3.5%+2.5 mV 7%+5 mV

50 to 150 Hz 0.4%+2.5 mV 1%+5 mV 0.5%+2.5 mV 1.2%+5 mV

150 Hz to 10 kHz 0.3%+2.5 mV 1%+5 mV 0.4%+2.5 mV 1.2%+5 mV

10 kHz to 20 kHz 0.4%+2.5 mV 1%+5 mV 0.5%+2.5 mV 1.2%+5 mV

20 kHz to 50 kHz 1%+3 mV 1.5%+6 mV 1.5%+3 mV 2%+6 mV

50 kHz to 100 kHz 2%+5 mV 3%+10 mV 3%+5 mV 4%+10 mV

30 V 20 to 50 Hz 3%+25 mV 6%+50 mV 3.5%+25 mV 7%+50 mV

50 to 150 Hz 0.4%+25 mV 1%+50 mV 0.5%+25 mV 1.2%+40 mV

150 Hz to 10 kHz 0.3%+25 mV 1%+50 mV 0.5%+25 mV 1.2%+40 mV

10 kHz to 20 kHz 0.4%+25 mV 1%+50 mV 0.5%+25 mV 1.2%+40 mV

20 kHz to 50 kHz 1%+30 mV 1.5%+60 mV 1%+30 mV 2%+50 mV

50 kHz to 100 kHz, V<20V 2%+50 mV 3%+100 mV 2.5%+50 mV 4%+100 mV

150/300 V 20 to 50 Hz 3%+.25 V 6%+.5 V 3.5%+.25 V 7%+.5 V

50 to 150 Hz 0.4%+.25 V 1%+.5 V 0.5%+.25 V 1.2%+.4 V

150 Hz to 2 kHz

Vx Hz<2 x10

6

0.3%+.25 V 1 .2%+.5 V 0.5%+.25 V 1.4%+.4 V

2 kHz to 20 kHz, V<100V 0.4%+.25 V 1.6%+.5 V 0.5%+.25 V 1.8%+.4 V

20 kHz to 50 kHz, V<40V 1%+.30 V 2 .0%+.6 V 1.2%+.30 V 2.5%+.5 V

[1] Sinewave inputs>6% of scale and signals with crest factors <2.

1-14

Page 31

Introduction and Specifications

Precision Analog Input (PAI) A/D Specifications

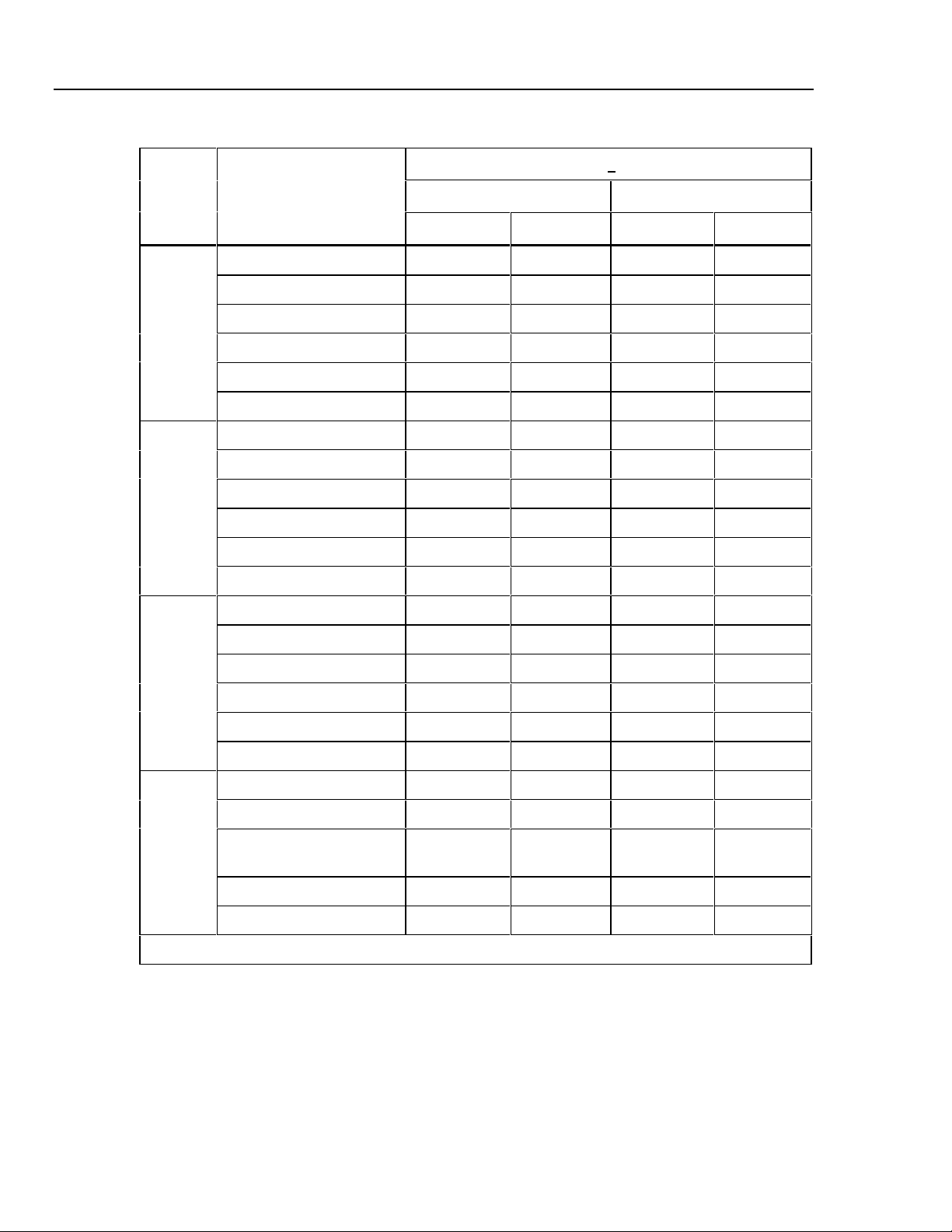

PAI A/D 4-Wire Resistance Measurement Specifications

The following tables provide PAI A/D specifications for the 4-wire resistance

measurement function. The 4-wire measurements use 2 input channels a decade apart,

e.g., channels 4 and 14.

Table 1-13. PAI A/D 4-Wire Resistance Temperature Coefficient

Specification Characteristic

Temperature Coefficient Add 1/10th the 90 day specification per °C above

28 °C or below 18 °C.

Accuracy at -20 °C Multiply the -10 °C to +60 °C accuracy

specification by 2. After 1 hour warm-up. For

accuracy between -10 °C and -20 °C, interpolate

linearly.

Table 1-14. PAI A/D 4-Wire Resistance Range and Resolution Specifications

1

Resolution

Range Slow Fast

300 Ω 1 mΩ 3mΩ 1 mA 300 mV 3.5 V

3 kΩ 10 mΩ 30 mΩ 100 µA 300 mV 3.5 V

30 kΩ 100 mΩ 300 mΩ 10 µA 300 mV 3.5 V

300 kΩ 1 Ω 3 Ω 10 µA 3.0 V 3.5 V

3 MΩ 10 Ω 30 Ω 1 µA 3.0 V 3.5 V

Table 1-15. PAI A/D 4-Wire Resistance Accuracy Specifications

Range

300 Ω .015%+20 mΩ .02%+80 mΩ .02%+50 mΩ .02%+120 mΩ .084%+126 mΩ .084%+336 mΩ

3 kΩ .02%+.3 Ω .02%+.8 Ω .02%+.5 Ω .02%+1.2 Ω .084%+1.26 Ω .084%+3.36 Ω

30 kΩ .03%+3 Ω .04%+10 Ω .03%+5 Ω .04%+15 Ω .126%+12.6 Ω .168%+42 Ω

90 Day 1 Year 1 Year

Slow Fast Slow Fast Slow Fast

Current Full Scale Maximum Voltage

Applied Voltage Applied by Instrument

Accuracy, 3σ + (% input + V)

18 °C to 28 °C -10 °C to 60 °C

300 kΩ .1%+40 Ω .2%+100 Ω .1%+60 Ω .2%+150 Ω .42%+168 Ω .84%+420 Ω

3 MΩ [1] .25%+800 Ω .5%+10 kΩ .25%+1 kΩ .5%+1.5 kΩ 1. 05%+3.36 kΩ 2.1%+4.2 kΩ

[1] The 3 MΩ range is susceptible to the absorption of humidity under extreme conditi ons. If the i nst rument is

operated normally within its specified temperat ure-hum i dity range, the 3 MΩ range meets its accuracy specifications.

However, if the instrument is “soaked” at 50 °C, 90% relative humidity, the 3 MΩ range may require 1 hour of “dryout” time at 25 °C, <40% relative humidity for each hour of soak time in order to achieve its specified accuracy.

1-15

Page 32

268XA

Service Manual

PAI A/D 2-Wire Resistance Measurement Specifications

PAI A/D 4-Wire RTD per ITS-1990 Measurement Specifications

The PAI A/D specifications for the two-wire resistance measurement function is based on

the four-wire resistance measurement specification (above) except you add a nominal 5 Ω

(10 Ω maximum) positive offset. This value varies for each channel and with temperature

(nominal +1%/ºC).

The following tables provide PAI A/D specifications for the 4-wire ResistanceTemperature Detector (RTD) measurement function. The 4-wire measurements use 2

input channels a decade apart, e.g., channels 4 and 14.

Table 1-16. PAI A/D 4-Wire RTD Temperature Coefficient

Specification Characteristic

Temperature Coefficient To calculate RTD accuracy for temperatures between 28 °C and 60 °C,

or -10 °C and 18 °C, use a linear interpolation between the two

applicable points. For example, if the applicable specification at 28 °C

is 0.2 and the specification at 60 °C is 0.75, then the specification at

40 °C is =(.75-.2)x(40-28)/(60-28)+.2=0.406.

Accuracy at -20 °C Multiply the -10 °C to +60 °C accuracy specification by 2. After 1 hour

warm-up. For accuracy between -10 °C and -20 °C, interpolate lin early .

Table 1-17. PAI A/D 4-Wire RTD Specifications

Accuracy, 3σ

Resolution

Temperature

Slow Fast Slow Fast Slow Slow Fast

-200 °C 0.003 °C 0.007 °C0.06 °C0.16 °C 0.09 °C0.33 °C0.63 °C

0 °C 0.003 °C 0.007 °C0.09 °C0.20 °C 0.13 °C0.53 °C0.86 °C

100 °C 0.003 °C 0.007 °C0.10 °C0.23 °C 0.16 °C0.63 °C0.97 °C

300 °C 0.003 °C 0.007 °C0.14 °C0.30 °C 0.21 °C0.83 °C1.20 °C

600 °C 0.003 °C 0.007 °C0.19 °C0.53 °C 0.30 °C1.20 °C1.60 °C

90 Day

18 °C to 28 °C

1 Year

18 °C to 28 °C

1 Year

–10 °C to 60 °C

PAI A/D 2-Wire RTD per ITS-1990 Measurement Specifications