Page 1

®

2640A/2645A

NetDAQ Data Acquisition Tools

Service Manual

PN 942615

March 1995

© 1995 Fluke Corporation, Inc. All rights reserved. Printed in U.S.A.

All product names are trademarks of their respective companies.

Page 2

LIMITED WARRANTY & LIMITATION OF LIABILITY

Each Fluke product is warranted to be free from defects in material and workmanship under

normal use and service. The warranty period is one year and begins on the date of shipment.

Parts, product repairs and services are warranted for 90 days. This warranty extends only to the

original buyer or end-user customer of a Fluke authorized reseller, and does not apply to fuses,

disposable batteries or to any product which, in Fluke’s opinion, has been misused, altered,

neglected or damaged by accident or abnormal conditions of operation or handling. Fluke

warrants that software will operate substantially in accordance with its functional specifications for

90 days and that it has been properly recorded on non-defective media. Fluke does not warrant

that software will be error free or operate without interruption.

Fluke authorized resellers shall extend this warranty on new and unused products to end-user

customers only but have no authority to extend a greater or different warranty on behalf of Fluke.

Warranty support is available if product is purchased through a Fluke authorized sales outlet or

Buyer has paid the applicable international price. Fluke reserves the right to invoice Buyer for

importation costs of repair/replacement parts when product purchased in one country is submitted

for repair in another country.

Fluke’s warranty obligation is limited, at Fluke’s option, to refund of the purchase price, free of

charge repair, or replacement of a defective product which is returned to a Fluke authorized

service center within the warranty period.

To obtain warranty service, contact your nearest Fluke authorized service center or send the

product, with a description of the difficulty, postage and insurance prepaid (FOB Destination), to

the nearest Fluke authorized service center. Fluke assumes no risk for damage in transit.

Following warranty repair, the product will be returned to Buyer, transportation prepaid (FOB

Destination). If Fluke determines that the failure was caused by misuse, alteration, accident or

abnormal condition of operation or handling, Fluke will provide an estimate of repair costs and

obtain authorization before commencing the work. Following repair, the product will be returned to

the Buyer transportation prepaid and the Buyer will be billed for the repair and return

transportation charges (FOB Shipping Point).

THIS WARRANTY IS BUYER’S SOLE AND EXCLUSIVE REMEDY AND IS IN LIEU OF ALL

OTHER WARRANTIES, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY

IMPLIED WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE.

FLUKE SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL OR

CONSEQUENTIAL DAMAGES OR LOSSES, INCLUDING LOSS OF DATA, WHETHER

ARISING FROM BREACH OF WARRANTY OR BASED ON CONTRACT, TORT, RELIANCE OR

ANY OTHER THEORY.

Since some countries or states do not allow limitation of the term of an implied warranty, or

exclusion or limitation of incidental or consequential damages, the limitations and exclusions of

this warranty may not apply to every buyer. If any provision of this Warranty is held invalid or

unenforceable by a court of competent jurisdiction, such holding will not affect the validity or

enforceability of any other provision.

Fluke Corporation Fluke Europe B.V.

P.O. Box 9090 P.O. Box 1186

Everett WA 5602 B.D. Eindhoven

98206-9090 The Netherlands

5/94

Page 3

SAFETY TERMS IN THIS MANUAL

This instrument has been designed and tested in accordance with IEC publicat ion

1010-1 (1992-1), Safety Requirements for Electrical Measuring, Control and Labor at ory

Equipment, and ANSI/ISA-582.01-1994, and CAN/CSA-C22.2 No. 1010.1-92. This User

Manual contains information, warning, and caut ions t hat must be followed to ensure

safe operation and to maintain the instrument in a safe condition. Use of this equipment

in a manner not specified herein may impair the pr ot ection provided by the equipment.

This instrument is designed for IEC 1010-1 Inst allation Category II use. It is not

designed for connection to circuits rated over 4800 VA.

WARNING statements identify condit ions or practices that could result in personal injury

or loss of life.

CAUTION statements identify conditions or pr act ices t hat could result in damage to

equipment.

SYMBOLS MARKED ON EQUIPMENT

WARNING Risk of electric shock. Refer to the manual.

GROUND Ground terminal to chassis (earth).

Attention Refer to the manual. This sym bol indicat es that information

about usage of a feature is contained in the manual. This sym bol

appears on the rear panel ground post and by the fuse compar tment.

AC POWER SOURCE

The instrument is intended to operate from an ac power source that will not apply more

than 264V ac rms between the supply conductors or bet ween eit her supply conductor

and ground. A protective ground connection by way of the grounding conductor in the

power cord is required for safe operation.

USE THE PROPER FUSE

To avoid fire hazard, for fuse replacement use only t he specified unit: 15/100 ampere,

250V, time delay.

GROUNDING THE INSTRUMENT

The instrument utilizes controlled overvoltage techniques that require the instrument t o

be grounded whenever normal mode or common mode ac volt ages or t r ansient voltages

may occur. The enclosure must be grounded through t he gr ounding conductor of the

power cord, or through the rear panel gr ound binding post .

Page 4

USE THE PROPER POWER CORD

Use only the power cord and connector appropriate for the voltage and plug

configuration in your country.

Use only a power cord that is in good condition.

Refer power cord and connector changes to qualified service personnel.

DO NOT OPERATE IN EXPLOSIVE ATM O SPHERES

To avoid explosion, do not operate the instrument in an atmosphere of explosive gas.

DO NOT REMOVE COVER DURING OPERATION

To avoid personal injury or death, do not remove the instrument cover without first

removing the power source connected to the rear panel. Do not operate the instrument

without the cover properly installed. Norm al calibration is accomplished with the cover

closed. Access procedures and the warnings for such procedures ar e cont ained in this

manual. Service procedures are for qualified ser v ice per sonnel only.

DO NOT ATTEMPT TO OPERATE IF PROTECTION MAY BE IMPAIRED

If the instrument appears damaged or operates abnormally, protection may be impaired.

Do not attempt to operate t he inst r um ent under these conditions. Refer all questions of

proper instrument operation to qualif ied service personnel.

Page 5

Table of Contents

Chapter Title Page

1 Introduction and Specification............................................................ 1-1

1-1. Introduction............................................................................................ 1-3

1-2. Options and Accessories ........................................................................ 1-6

1-3. Instrument Connector Set, 2620A-100.............................................. 1-6

1-4. Host Computer Ethernet Interfaces.................................................... 1-6

1-5. Interconnection Cables and Components........................................... 1-6

1-6. Operating Instructions............................................................................ 1-7

1-7. Organization of the Service Manual....................................................... 1-7

1-8. Conventions............................................................................................ 1-8

1-9. Specifications......................................................................................... 1-8

1-10. 2640A/2645A Combined Specifications ........................................... 1-8

1-11. 2640A/2645A General Specifications........................................... 1-9

1-12. 2640A/2645A Environmental Specifications................................ 1-10

1-13. 2640A/2645A Input/Output Capabilities....................................... 1-10

1-18. 2640A/2645A Totalizer................................................................. 1-12

1-19. 2640A/2645A Real-Time Clock and Calendar.............................. 1-12

1-20. 2640A Specifications......................................................................... 1-13

1-21. 2640A DC Voltage Measurement Specifications.......................... 1-13

1-22. 2640A AC Voltage Measurement Specifications.......................... 1-14

1-23. 2640A Four-Wire Resistance Measurement Specifications.......... 1-16

1-24. 2640A Two-Wire Resistance Measurement Specifications.......... 1-16

1-25. 2640A Four-Wire RTD per ITS-1990 Measurement

Specifications.............................................. .................................. 1-17

1-26. 2640A Two-Wire RTD per ITS-1990 Measurement

Specifications.............................................. .................................. 1-17

1-27. 2640A Thermocouple per ITS-1990 Measurement

Specifications.............................................. .................................. 1-18

1-28. 2640A Frequency Measurement Specifications............................ 1-19

1-29. 2645A Specifications......................................................................... 1-20

1-30. 2645A DC Voltage Measurement Specifications.......................... 1-20

1-31. 2645A AC Voltage Measurement Specifications.......................... 1-21

1-32. 2645A Four-Wire Resistance Measurement Specifications.......... 1-23

1-33. 2645A Two-Wire Resistance Measurement Specifications.......... 1-23

i

Page 6

NetDAQ

Service Manual

1-34. 2645A Four-Wire RTD per ITS-1990 Measurement

Specifications................................................................................. 1-24

1-35. 2645A Thermocouple per ITS-1990 Measurement

Specifications................................................................................. 1-24

1-36. 2645A Frequency Measurement Specifications............................ 1-26

2 Theory of Operation............................................................................. 2-1

2-1. Introduction............................................................................................ 2-5

2-2. Functional Block Description................................................................. 2-5

2-3. A1 Main PCA Block Description...................................................... 2-7

2-4. Power Supply................................................................................. 2-7

2-5. Digital Kernel................................................................................ 2-7

2-6. Serial Communication (Guard Crossing)...................................... 2-8

2-7. Digital Inputs and Outputs............................................................. 2-8

2-8. Ethernet Interface .......................................................................... 2-8

2-9. A2 Display PCA Block Description.................................................. 2-8

2-10. A3 A/D Converter PCA Block Description....................................... 2-8

2-11. Analog Measurement Processor.................................................... 2-9

2-12. Input Protection ............................................................................. 2-9

2-13. Input Signal Conditioning.............................................................. 2-9

2-14. Analog-to-Digital (a/d) Converter................................................. 2-9

2-15. Inguard Microcontroller ................................................................ 2-9

2-16. Channel Selection.......................................................................... 2-9

2-17. Open Thermocouple Check........................................................... 2-10

2-18. A4 Analog Input PCA Block Description.......................................... 2-10

2-19. 20-Channel Terminals ................................................................... 2-10

2-20. Reference Junction Temperature................................................... 2-10

2-21. Detailed Circuit Description .................................................................. 2-10

2-22. A1 Main PCA Circuit Description..................................................... 2-10

2-23. Power Supply Circuit Description................................................. 2-10

2-31. Digital Kernel................................................................................ 2-13

2-42. Digital Inputs and Outputs............................................................. 2-24

2-48. A2 Display PCA Circuit Description................................................. 2-26

2-49. Main PCA Connector .................................................................... 2-26

2-50. Front Panel Switches..................................................................... 2-27

2-51. Display........................................................................................... 2-28

2-52. Beeper Drive Circuit...................................................................... 2-28

2-53. Watchdog Timer and Reset Circuit............................................... 2-29

2-54. Display Controller ......................................................................... 2-29

2-55. A3 A/D Converter PCA Circuit Description..................................... 2-31

2-56. Stallion Chip.................................................................................. 2-33

2-57. Input Protection ............................................................................. 2-33

2-58. Input Signal Conditioning.............................................................. 2-33

2-59. Function Relays............................................................................. 2-33

2-60. Channel Selection Circuitry........................................................... 2-34

2-61. DC Volts and Thermocouples Measurement Circuitry................. 2-34

2-62. Ohms and RTD Measurement Circuitry........................................ 2-36

2-63. AC Volts Measurement Circuitry.................................................. 2-37

2-64. Frequency Measurements.............................................................. 2-37

2-65. Active Filter (ACV Filter)............................................................. 2-37

2-66. Voltage Reference Circuit............................................................. 2-38

2-67. Analog/Digital Converter Circuit.................................................. 2-39

2-73. Inguard Digital Kernel Circuitry................................................... 2-42

2-74. Open Thermocouple Detect Circuitry............................................. 2-43

ii

Page 7

Contents (continued)

2-75. A4 Analog Input PCA Circuit Description........................................ 2-43

2-76. A1 Main to A3 A/D Converter Communications................................... 2-44

2-77. Special Codes..................................................................................... 2-44

2-78. Resets................................................................................................. 2-44

2-79. Commands.......................................................................................... 2-45

2-80. Perform Scan ................................................................................. 2-45

2-81. Perform Self-Test........................................................................... 2-46

2-82. Return Main Firmware Version..................................................... 2-46

2-83. Return Boot Firmware Version ..................................................... 2-47

2-84. Set Global Configuration............................................................... 2-47

2-85. Set Channel Configuration ............................................................ 2-47

2-86. Do Housekeeping........................................................................... 2-48

2-87. Checksums......................................................................................... 2-48

2-88. Errors.................................................................................................. 2-48

2-89. Power-Up Protocol............................................................................. 2-49

2-90. Inguard Unresponsive........................................................................ 2-49

2-91. Inguard Software Description ................................................................ 2-49

2-92. Hardware Elements............................................................................ 2-49

2-93. Channel MUX.... ........................................................................... 2-49

2-94. Function Relays. ........................................................................... 2-51

2-95. Stallion Chip and Signal Conditioning.......................................... 2-51

2-96. A/D ................................................................................................ 2-53

2-101. DISCHARGE Signal. .................................................................... 2-57

2-102. Open-Thermocouple Detector....................................................... 2-57

2-103. Channel Measurements...................................................................... 2-57

2-104. Reading Rates................................................................................ 2-57

2-105. Measurement Types....................................................................... 2-58

2-112. Autoranging................................................................................... 2-60

2-113. Overload ........................................................................................ 2-61

2-114. Housekeeping Readings..................................................................... 2-61

2-115. Reading Types............................................................................... 2-61

2-118. Housekeeping Schedule................................................................. 2-62

2-119. Self-Tests ........................................................................................... 2-62

2-120. Power-Up Self-Tests...................................................................... 2-62

2-121. Self-Test Command....................................................................... 2-63

3 General Maintenance........................................................................... 3-1

3-1. Introduction............................................................................................ 3-3

3-2. Warranty Repairs and Shipping ............................................................. 3-3

3-3. General Maintenance.............................................................................. 3-3

3-4. Required Equipment .......................................................................... 3-3

3-5. Power Requirements.......................................................................... 3-3

3-6. Static-Safe Handling.......................................................................... 3-3

3-7. Servicing Surface-Mount Assemblies................................................ 3-4

3-8. Cleaning.................................................................................................. 3-4

3-9. Replacing the Line Fuse......................................................................... 3-5

3-10. Disassembly Procedures......................................................................... 3-7

3-11. Removing the Instrument Case.......................................................... 3-7

3-12. Removing the Front Panel Assembly................................................. 3-7

3-13. Disassembling the Front Panel Assembly.......................................... 3-11

3-14. Removing the A1 Main PCA............................................................. 3-11

3-15. Removing the A2 Display PCA......................................................... 3-12

3-16. Removing the A3 A/D Converter PCA.............................................. 3-12

3-17. Removing the A4 Analog Input PCA ................................................ 3-12

iii

Page 8

NetDAQ

Service Manual

3-18. Removing Miscellaneous Chassis Components................................ 3-12

3-19. Removing the Power Switch/Input Connector.............................. 3-12

3-20. Removing the Fuseholder.............................................................. 3-13

3-21. Removing the Power Transformer................................................. 3-13

3-22. Assembly Procedures............................................................................. 3-13

3-23. Installing Miscellaneous Chassis Components.................................. 3-13

3-24. Installing the Power Transformer.................................................. 3-13

3-25. Installing the Fuseholder ............................................................... 3-14

3-26. Installing the Power Switch/Input Connector................................ 3-14

3-27. Installing the A1 Main PCA............................................................... 3-15

3-28. Installing the A2 Display PCA........................................................... 3-15

3-29. Installing the A3 A/D Converter PCA............................................... 3-15

3-30. Installing the A4 Analog Input PCA.................................................. 3-15

3-31. Assembling the Front Panel Assembly.............................................. 3-16

3-32. Installing the Front Panel Assembly.................................................. 3-16

3-33. Installing the Instrument Case............................................................ 3-16

4 Performance Testing and Calibration................................................. 4-1

4-1. Introduction............................................................................................ 4-3

4-2. Performance Test ................................................................................... 4-3

4-3. Configuring the Performance Test Setup........................................... 4-3

4-4. Initializing the Performance Test Setup............................................. 4-6

4-5. Accuracy Performance Tests ............................................................. 4-7

4-6. Volts DC Accuracy Test (2640A)................................................. 4-8

4-7. Volts DC Accuracy Test (2645A)................................................. 4-9

4-8. Volts AC Accuracy Test................................................................ 4-10

4-9. Frequency Accuracy Test.............................................................. 4-10

4-10. Analog Channel Integrity Test....................................................... 4-11

4-11. Computed Channel Integrity Test.................................................. 4-11

4-12. Thermocouple Temperature Accuracy Test.................................. 4-12

4-13. Open Thermocouple Response Test.............................................. 4-12

4-14. Two-Terminal Resistance Accuracy Test (2640A)....................... 4-13

4-15. Two-Terminal Resistance Accuracy Test (2645A)....................... 4-14

4-16. Four-Terminal Resistance Accuracy Test (2640A)....................... 4-15

4-17. Four-Terminal Resistance Accuracy Test (2645A)....................... 4-17

4-18. RTD Temperature Accuracy Test (Resistance) (2640A).............. 4-18

4-19. RTD Temperature Accuracy Test (Resistance) (2645A).............. 4-19

4-20. RTD Temperature Accuracy Test (DIN/IEC 751 RTD) ............... 4-19

4-21. Digital Input/Output Tests ................................................................. 4-20

4-22. Digital I/O Output Test.................................................................. 4-20

4-23. Digital Input Test........................................................................... 4-21

4-24. Totalizer Tests........................................................................................ 4-22

4-25. Totalizer Count Test...................................................................... 4-22

4-26. Totalizer Sensitivity Test............................................................... 4-23

4-27. Master Alarm Output Test................................................................. 4-23

4-28. Trigger Input Test .............................................................................. 4-24

4-29. Trigger Output Test............................................................................ 4-24

4-30. Calibration.............................................................................................. 4-25

4-31. Methods of Calibration...................................................................... 4-25

4-32. Preparing for Calibration................................................................... 4-26

4-33. Ending Calibration............................................................................. 4-28

4-34. RS-232 Instrument Configuration Parameters................................... 4-28

4-35. Calibration Procedure (Automatic).................................................... 4-28

4-36. Calibration Procedure (Semiautomatic)............................................. 4-28

iv

Page 9

Contents (continued)

4-37. VDC Calibration Procedure........................................................... 4-31

4-38. VAC Calibration Procedure........................................................... 4-32

4-39. Resistance Calibration Procedure.................................................. 4-33

4-40. Frequency Calibration Procedure.................................................. 4-34

4-41. Calibration Procedure (Manual) ........................................................ 4-34

4-42. Manual Calibration Commands..................................................... 4-36

4-43. Manual VDC Calibration Procedure ............................................. 4-37

4-44. Manual VAC Calibration Procedure ............................................. 4-38

4-45. Manual Resistance Calibration Procedure..................................... 4-39

4-46. Manual Frequency Calibration Procedure..................................... 4-41

5 Diagnostic Testing and Troubleshooting........................................... 5-1

5-1. Introduction............................................................................................ 5-3

5-2. Servicing Surface-Mount Assemblies.................................................... 5-3

5-3. Error Detection....................................................................................... 5-4

5-4. FLASH ROM Parameter Defaults..................................................... 5-5

5-5. Background Testing........................................................................... 5-5

5-6. Internal Software Errors..................................................................... 5-6

5-7. Retrieving Error Codes using RS-232................................................5-6

5-8. Retrieving Error Codes using the Network........................................ 5-6

5-9. Selecting the Diagnostic Tools............................................................... 5-6

5-10. Diagnostic Tool dio............................................................................ 5-7

5-11. Diagnostic Tool idS ........................................................................... 5-7

5-12. Diagnostic Tool conF......................................................................... 5-8

5-13. Diagnostic Display Test..................................................................... 5-9

5-14. COMM Parameter Reset.................................................................... 5-9

5-15. Using the RS-232 Interface.................................................................... 5-9

5-16. Command Processing......................................................................... 5-10

5-17. Instrument Configuration................................................................... 5-11

5-18. Command Set......................................................................................... 5-12

5-19. Troubleshooting the Instrument............................................................. 5-19

5-20. General Troubleshooting ................................................................... 5-19

5-21. A1 Main PCA Troubleshooting......................................................... 5-27

5-22. Troubleshooting the A1 Main PCA Digital Kernel....................... 5-27

5-23. Troubleshooting the RS-232 Interface........................................... 5-28

5-24. Troubleshooting the Ethernet Interface......................................... 5-28

5-25. Troubleshooting the Digital I/O Lines and Trigger Out Lines...... 5-28

5-26. Troubleshooting the Totalizer and Trigger In Lines ..................... 5-28

5-27. Troubleshooting the Power Supply ............................................... 5-29

5-28. A2 Display PCA Troubleshooting..................................................... 5-29

5-29. Variations in the Display............................................................... 5-31

5-30. A3 A/D Converter PCA Troubleshooting.......................................... 5-31

5-31 A3 Kernel. ..................................................................................... 5-32

5-32. Break/Reset Circuit........................................................................ 5-32

5-33. Out of Tolerance Readings............................................................ 5-32

5-34. Troubleshooting Relay Problems .................................................. 5-33

5-35. A4 Analog Input PCA Troubleshooting ............................................ 5-33

5-36. Troubleshooting Calibration Failures .................................................... 5-34

5-37. Retrieving Calibration Constants....................................................... 5-34

5-38. Loading Embedded Instrument Firmware.............................................. 5-36

5-39. Firmware Diskette.............................................................................. 5-36

5-40. Loading the Main Firmware .............................................................. 5-37

5-41. Loading the A/D Firmware................................................................ 5-38

v

Page 10

NetDAQ

Service Manual

6 List of Replaceable Parts .................................................................... 6-1

6-1. Introduction............................................................................................ 6-3

6-2. How To Obtain Parts.............................................................................. 6-3

6-3. Manual Status Information..................................................................... 6-3

6-4. Newer Instruments.................................................................................. 6-4

6-5. Service Centers....................................................................................... 6-4

7 Schematic Diagrams............................................................................ 7-1

vi

Page 11

List of Tables

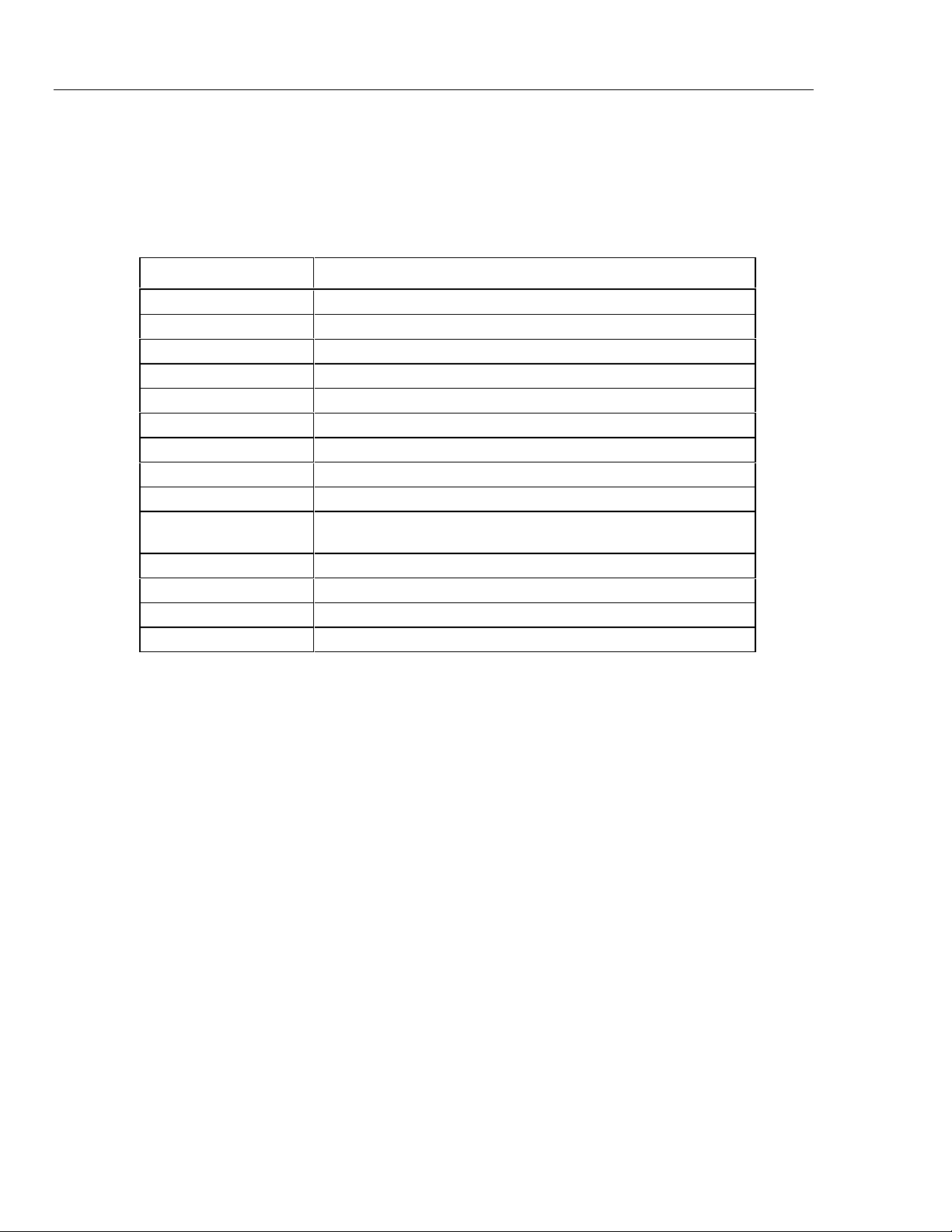

Table Title Page

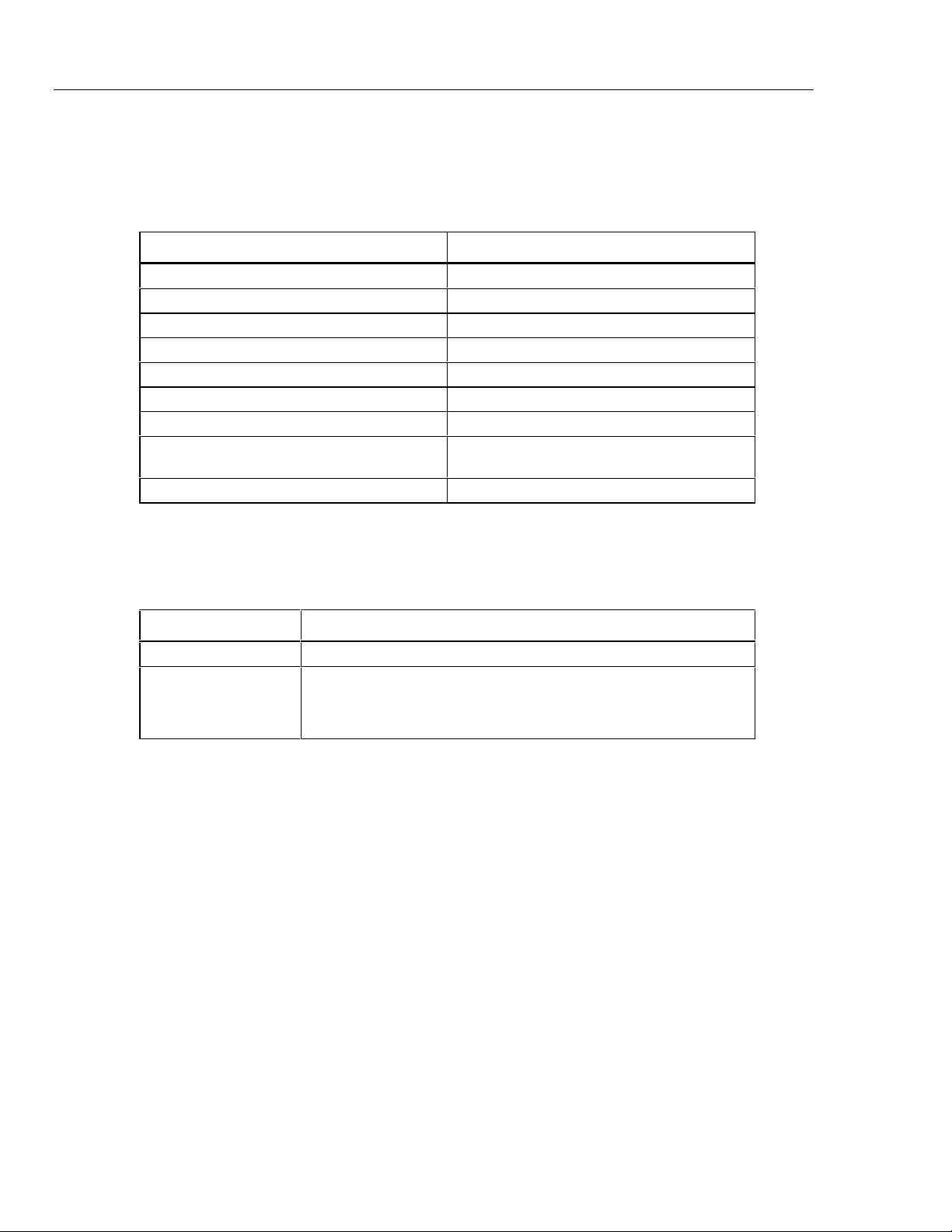

1-1. Summary of 2640A/2645A Specifications............................................. 1-4

1-2. Summary of 2640A/2645A Measurement Capabilities ......................... 1-4

1-3. Summary of 2640A/2645A Features...................................................... 1-5

1-4. Models, Options and Accessories.......................................................... 1-6

1-5. 2640A/2645A General Specifications.................................................... 1-9

1-6. Environmental Specifications ................................................................ 1-10

1-7. 2640A/2645A DIGITAL I/O Specification............................................ 1-10

1-8. 2640A/2645A Trigger In (TI) Specification.......................................... 1-11

1-9. 2640A/2645A Trigger Out (TO) Specification...................................... 1-11

1-10. 2640A/2645A Master Alarm (MA) Specification ................................. 1-11

1-11. 2640A/2645A Totalizer Specification ................................................... 1-12

1-12. 2640A/2645A Real-Time Clock and Calendar...................................... 1-12

1-13. 2640A DC Voltage General Specifications ........................................... 1-13

1-14. 2640A DC Voltage Range and Resolution Specifications..................... 1-13

1-15. 2640A DC Voltage Accuracy Specifications......................................... 1-14

1-16. 2640A AC Voltage General Specifications ........................................... 1-14

1-17. 2640A AC Voltage Range and Resolution Specifications..................... 1-15

1-18. 2640A AC Voltage Accuracy Specifications......................................... 1-15

1-19. 2640A Four-Wire Resistance Temperature Coefficient......................... 1-16

1-20. 640A Four-Wire Resistance Range and Resolution Specifications....... 1-16

1-21. 2640A Four-Wire Resistance Accuracy Specifications......................... 1-16

1-22. 2640A Four-Wire RTD Temperature Coefficient.................................. 1-17

1-23. 2640A Four-Wire RTD Specifications .................................................. 1-17

1-24. 2640A Thermocouple General Specifications ....................................... 1-18

1-25. 2640A Thermocouple Specifications..................................................... 1-18

1-26. 2640A Frequency Accuracy Specifications........................................... 1-19

1-27. 2640A Frequency Sensitivity Specifications......................................... 1-20

1-28. 2645A DC Voltage General Specifications ........................................... 1-20

1-29. 2645A DC Voltage Resolution and Repeatability Specifications.......... 1-21

1-30. 2645A DC Voltage Accuracy Specifications......................................... 1-21

1-31. 2645A AC Voltage General Specifications ........................................... 1-21

1-32. 2645A AC Voltage Range and Resolution Specifications..................... 1-22

1-33. 2645A AC Voltage Accuracy Specifications......................................... 1-22

1-34. 2645A Four-Wire Resistance Temperature Coefficient......................... 1-23

1-35. 2645A Four-Wire Resistance Range and Resolution Specifications..... 1-23

vii

Page 12

NetDAQ

Service Manual

1-36. 2645A Four-Wire Resistance Accuracy Specifications......................... 1-23

1-37. 2645A Four-Wire RTD Temperature Coefficient.................................. 1-24

1-38. 2645A Four-Wire RTD Specifications .................................................. 1-24

1-39. 2645A Thermocouple General Specifications ....................................... 1-24

1-40. 2645A Thermocouple Specifications..................................................... 1-25

1-41. 2645A Frequency Accuracy Specifications........................................... 1-26

1-42. 2645A Frequency Sensitivity Specifications......................................... 1-26

2-1. Microprocessor Interrupt Sources.......................................................... 2-16

2-2. Booting Microprocessor Memory Map.................................................. 2-17

2-3. nstrument Microprocessor Memory Map............................................... 2-17

2-4. A2 Display Power Supply Connections................................................. 2-27

2-5. Front Panel Switch Scanning ................................................................. 2-28

2-6. Display Initialization Modes.................................................................. 2-30

2-7. Range of Buffer Amplifier..................................................................... 2-34

2-8. Measurement Matrix for DC Volts........................................................ 2-35

2-9. Measurement Matrix for Ohms.............................................................. 2-36

2-10. Measurement Matrix for AC Volts........................................................ 2-37

2-11. Analog/Digital Converter Measurement Cycle...................................... 2-39

2-12. Tree Bits................................................................................................. 2-50

2-13. Channel Bits........................................................................................... 2-50

2-14. Tree and Channel Switch Settling Times............................................... 2-50

2-15. Function Relays...................................................................................... 2-51

2-16. Function Relay Settling Time................................................................. 2-51

2-17. Stallion Switch Settings ......................................................................... 2-52

2-18. Signal Conditioning Settling Time......................................................... 2-53

2-19. A/D Command Codes............................................................................. 2-55

2-20. A/D Readings to Average to Obtain a Measurement............................. 2-58

2-21. Frequency Sensitivity............................................................................. 2-60

2-22. A/D Readings to Average to Obtain a Reference

Balance Measurement ............................................................................ 2-61

4-1. Recommended Test Equipment.............................................................. 4-4

4-2. RS-232 Instrument Configuration for Calibration Procedures............... 4-28

4-3. Calibration Commands........................................................................... 4-36

4-4. Manual Calibration Command Responses............................................. 4-37

4-5. Manual VDC Calibration....................................................................... 4-37

4-6. Manual VAC Calibration....................................................................... 4-39

4-7. Manual Resistance Calibration .............................................................. 4-40

4-8. Manual Frequency Calibration............................................................... 4-41

5-1. Selftest Error Codes ............................................................................... 5-4

5-2. FLASH ROM Parameter Defaults ......................................................... 5-5

5-3. Corrective Action for Background Error Checking............................... 5-6

5-4. Instrument Firmware Descriptions......................................................... 5-8

5-5. Instrument Default COMM Parameters................................................. 5-9

5-6. Instrument Configuration....................................................................... 5-11

5-7. RS232 Command Set ............................................................................. 5-12

5-8. Power-on/Reset Instrument State........................................................... 5-14

5-9. Range Settings........................................................................................ 5-18

5-10. Selftest Error Codes ............................................................................... 5-20

5-10. Relating Selftest Errors to Instrument Problems.................................... 5-21

5-10. Relating Selftest Errors to Instrument Problems.................................... 5-22

5-10. Relating Selftest Errors to Instrument Problems.................................... 5-23

5-10. Relating Selftest Errors to Instrument Problems.................................... 5-24

5-10. Relating Selftest Errors to Instrument Problems.................................... 5-25

5-11. Hints for Troubleshooting...................................................................... 5-26

5-12. A1 Main PCA Jumper Positions ............................................................ 5-27

viii

Page 13

Tables (continued)

5-13. A2 Display PCA Initialization Routines................................................ 5-29

5-14. A3 A/D Converter PCA Jumper Positions............................................. 5-32

5-15. Calibration Constants............................................................................. 5-35

5-16. Files on the Firmware Diskette .............................................................. 5-37

6-1. 2640A/2645A Final Assembly............................................................... 6-5

6-2. A1 Main PCA Assembly........................................................................ 6-10

6-3. A2 Display PCA Assembly.................................................................... 6-15

6-4. 2640A A3 A/D Converter PCA Assembly............................................. 6-17

6-5. 2645A A3 A/D Converter PCA Assembly............................................. 6-22

6-6. A4 Analog Input PCA Assembly ........................................................... 6-27

ix

Page 14

NetDAQ

Service Manual

x

Page 15

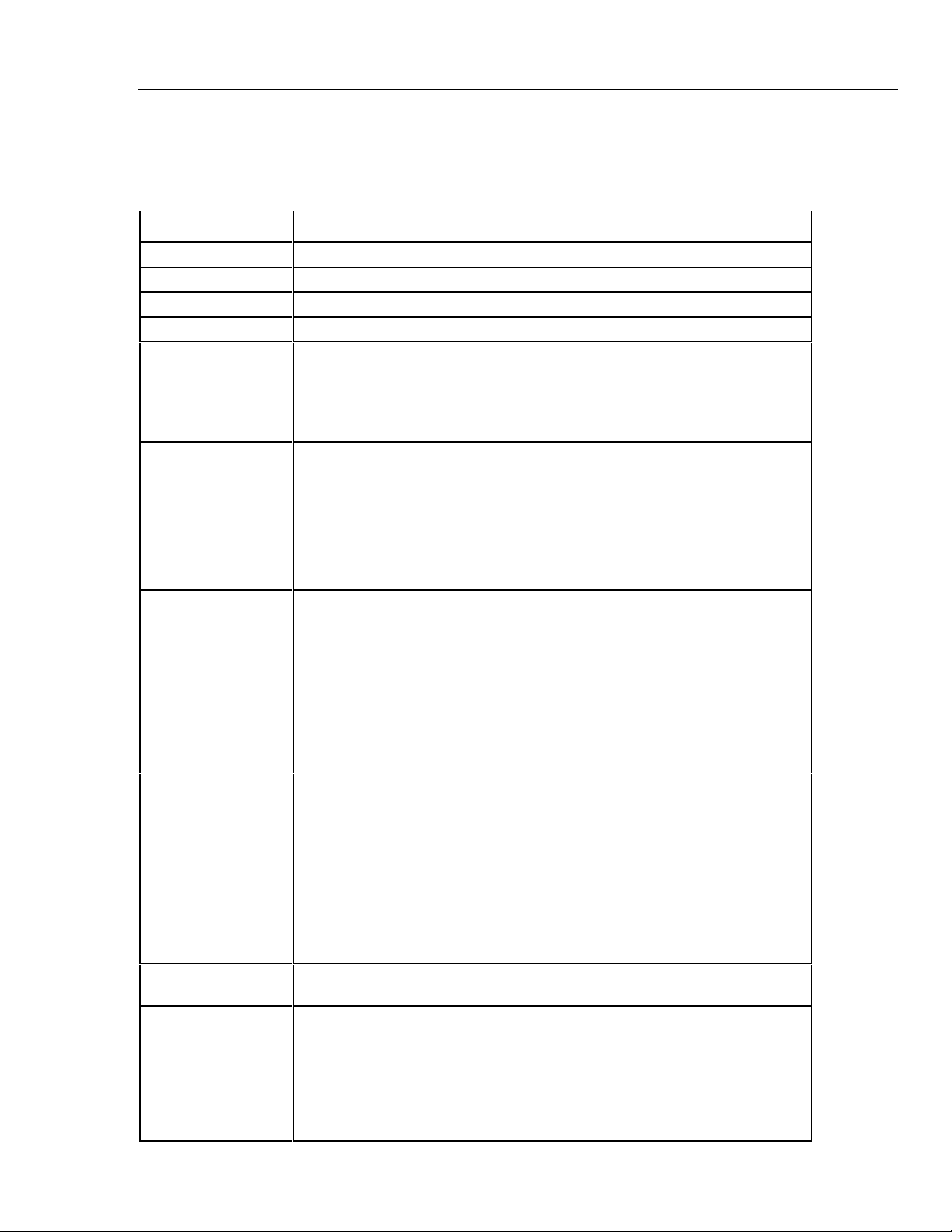

List of Figures

Figure Title Page

1-1. 2640A/2645A NetDAQ Networked Data Acquisition Units................. 1-3

2-1. Interconnection Diagram........................................................................ 2-5

2-2. Overall Functional Block Diagram........................................................ 2-6

2-3. Power Supply Block Diagram................................................................ 2-7

2-4. Command Byte Transfer Waveforms..................................................... 2-29

2-5. Grid Control Signal Timing ................................................................... 2-30

2-6. Grid-Anode Timing Relationships......................................................... 2-31

2-7. A3 A/D Converter Block Diagram......................................................... 2-32

2-8. DC Volts 300V Range Simplified Schematic........................................ 2-35

2-9. RTD Measurement Simplified Schematic.............................................. 2-36

2-10. AC Volts 3V Range Simplified Schematic............................................ 2-38

2-11. Integrator Output Waveform for Input Near 0....................................... 2-40

2-12. Integrator Output Waveform for Input Near + Full Scale...................... 2-41

2-13. Integrator Output Waveform for Input Near - Full Scale....................... 2-41

2-14. A/D Timing (2645A Normal Reading).................................................. 2-54

2-15. A/D Timing (2640A Normal Reading, 2640A and

2645A Reference Balance)..................................................................... 2-54

2-16. A/D Status Signals.................................................................................. 2-55

3-1. Replacing the Fuse ................................................................................. 3-6

3-2. 2640A and 2645A Assembly Details..................................................... 3-8

3-3. Power Input Connections at the Power Switch...................................... 3-14

4-1. Performance Test Setup ......................................................................... 4-5

4-2. Two-Terminal Connections to 5700A.................................................... 4-5

4-3. Four-Terminal Connections to the Universal Input Module (Resistor). 4-15

4-4. Four-Terminal Connections to the Universal Input Module (5700A)... 4-16

4-5. Instrument and Host Computer Calibration Setup................................. 4-27

4-6. Universal Input Module Calibration Connections ................................. 4-27

4-7. Two-Wire Calibration Connection......................................................... 4-29

4-8. Four-Wire Calibration Connection......................................................... 4-29

5-1. Display Test Pattern #1.......................................................................... 5-29

5-2. Display Test Pattern #2.......................................................................... 5-30

5-3. Connection to A3P1 for Loading A/D Firmware................................... 5-39

6-1. 2640A/264A5 Final Assembly............................................................... 6-9

6-1. 701/702 Final Assembly......................................................................... 6-9

6-2. A1 Main PCA Assembly........................................................................ 6-14

xi

Page 16

NetDAQ

Service Manual

6-2. A1 Power Supply PCA........................................................................... 6-14

6-3. A2 Display PCA Assembly.................................................................... 6-16

6-4. 2640A A3 A/D Converter PCA Assembly............................................. 6-21

6-5. 2645A A3 A/D Converter PCA Assembly............................................. 6-26

6-6. A4 Analog Input PCA Assembly ........................................................... 6-28

xii

Page 17

Chapter 1

Introduction and Specification

Title Page

1-1. Introduction............................................................................................ 1-3

1-2. Options and Accessories ........................................................................ 1-6

1-3. Instrument Connector Set, 2620A-100.............................................. 1-6

1-4. Host Computer Ethernet Interfaces................................................... 1-6

1-5. Interconnection Cables and Components.......................................... 1-6

1-6. Operating Instructions............................................................................ 1-7

1-7 Organization of the Service Manual ...................................................... 1-7

1-8. Conventions............................................................................................ 1-8

1-9. Specifications......................................................................................... 1-8

1-10. 2640A/2645A Combined Specifications........................................... 1-8

1-11. 2640A/2645A General Specifications.......................................... 1-9

1-12. 2640A/2645A Environmental Specifications............................... 1-10

1-13. 2640A/2645A Input/Output Capabilities ..................................... 1-10

1-14. Digital I/O.................................................................................1-10

1-15. Trigger In..................................................................................1-11

1-16. Trigger Out ...............................................................................1-11

1-17. Master Alarm............................................................................1-11

1-18. 2640A/2645A Totalizer................................................................ 1-12

1-19. 2640A/2645A Real-Time Clock and Calendar ............................ 1-12

1-20. 2640A Specifications ........................................................................ 1-13

1-21. 2640A DC Voltage Measurement Specifications ........................ 1-13

1-22. 2640A AC Voltage Measurement Specifications ........................ 1-14

1-23. 2640A Four-Wire Resistance Measurement Specifications......... 1-16

1-24. 2640A Two-Wire Resistance Measurement Specifications......... 1-16

1-25. 2640A Four-Wire RTD per ITS-1990 Measurement

Specifications ............................................................................... 1-17

1-26. 2640A Two-Wire RTD per ITS-1990 Measurement

Specifications ............................................................................... 1-17

1-27. 2640A Thermocouple per ITS-1990 Measurement

Specifications. .............................................................................. 1-18

1-28. 2640A Frequency Measurement Specifications........................... 1-19

1-1

Page 18

NetDAQ

Service Manual

1-29. 2645A Specifications ........................................................................ 1-20

1-30. 2645A DC Voltage Measurement Specifications ........................ 1-20

1-31. 2645A AC Voltage Measurement Specifications ........................ 1-21

1-32. 2645A Four-Wire Resistance Measurement Specifications......... 1-23

1-33. 2645A Two-Wire Resistance Measurement Specifications......... 1-23

1-34. 2645A Four-Wire RTD per ITS-1990 Measurement

Specifications ............................................................................... 1-24

1-35. 2645A Thermocouple per ITS-1990 Measurement

Specifications. .............................................................................. 1-24

1-36. 2645A Frequency Measurement Specifications........................... 1-26

1-2

Page 19

Introduction and Specification

Introduction

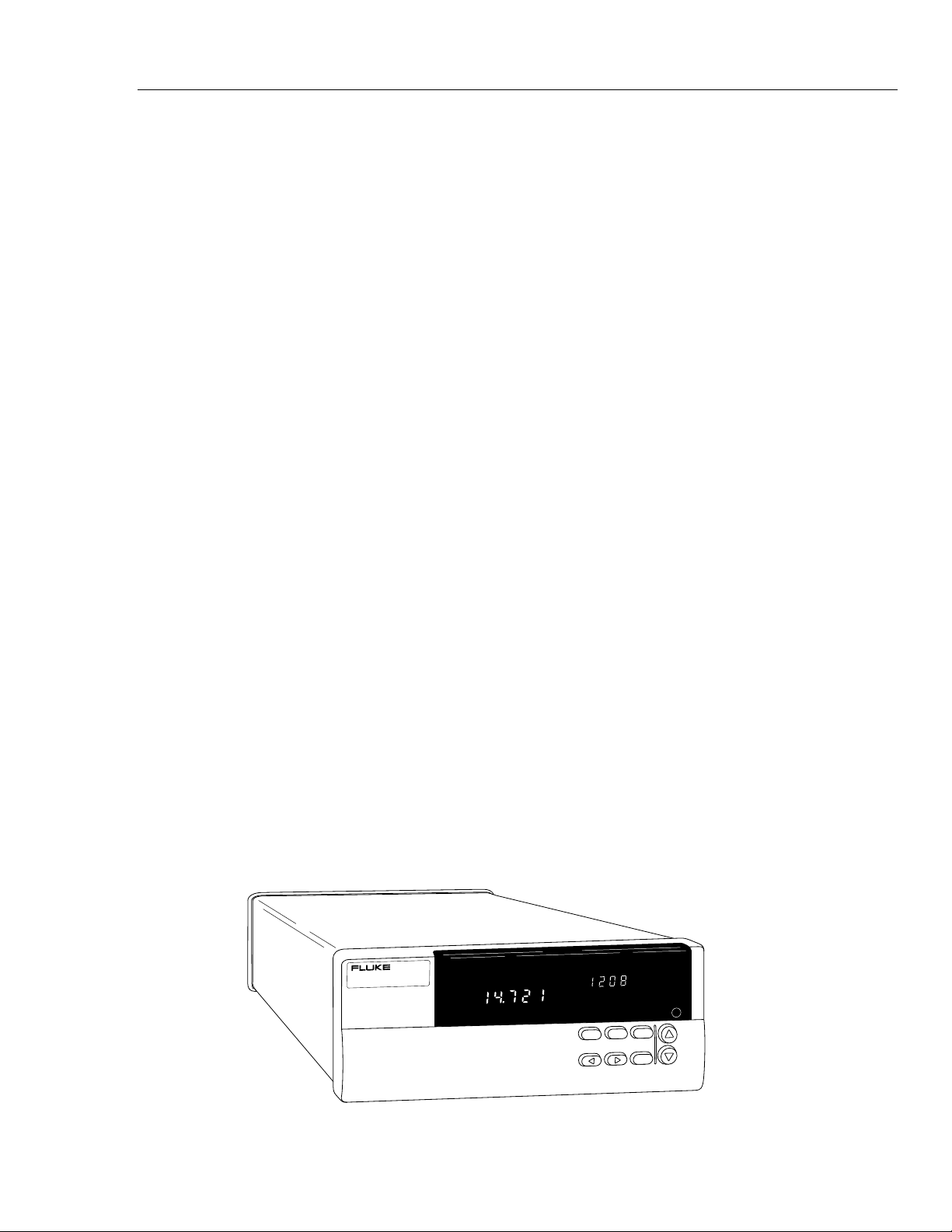

Introduction 1-1.

This Service Manual supports performance testing, calibration, servicing, and

maintenance of the 2640A NetDAQ

units (Figure 1-1). NetDAQ networked data acquisition units are 20-channel front ends

that operate in conjunction with a host computer to form a networked data acquisition

system. The host computer and instruments are interconnected using an Ethernet

network, and the host computer runs the NetDAQ Logger for Windows application to

provide an operating environment for the instruments, including testing and calibration.

The 2640A and 2645A networked data acquisition units are identical in operation and

appearance, and vary only in emphasis: The 2640A emphasizes precision and supports

up to 100 measurements per second, with 5 ½ digits of resolution, .02% accuracy, and

150-volt common mode voltage (300 volts on channels 1 and 11), while the 2645A

emphasizes increased measurement speed supporting up to 1000 measurements per

second, with 4 ½ digits of resolution, .04% accuracy, and 50-volt common mode voltage.

Refer to Table 1-1 for a summary of instrument specifications. For complete instrument

specifications, see “Specifications” later in this chapter.

The instruments measure dc volts, ac volts, ohms, temperature, frequency, and dc

current. Temperature measurements use thermocouples or resistance-temperature

detectors (RTDs). Refer to Table 1-2 for a summary of instrument measurement

capabilities. In addition, there are eight digital input/output lines, one totalizing input,

one external trigger input, one trigger output, and one master alarm output. The

instruments can be ac or dc powered. An RS-232 serial port is supplied for servicing and

maintenance procedures.

™ and 2645A NetDAQ networked data acquisition

1

The term "instrument" is used in this manual to refer to both units. The model number

(2640A or 2645A) is used when discussing characteristics unique to one instrument.

Instrument assemblies are identical except for the A3 Analog/Digital Converter printed

circuit assembly (pca), which is specific to the 2640A (mechanical switching for

measurement signals) and 2645A (solid-state switching for measurement signals).

The instrument is designed for bench-top, field service, and system applications. A dual

vacuum-fluorescent display uses combinations of alphanumeric characters and

descriptive annunciators to provide prompting and measurement information during

setup and operation modes. Some features provided by the instrument are listed in Table

1-3. For additional information regarding instrument features and capabilities, refer to

the NetDAQ Users Manual (PN 942623).

NetDAQ

NETWORKED DATA ACQUISITION UNIT

REM SCAN

MON

V DC

COMM

CH

DIO

ENTER

CAL

ENABLE

MON

Figure 1-1. 2640A/2645A NetDAQ Networked Data Acquisition Units

1-3

Page 20

NetDAQ

Service Manual

Maximum Normal Mode Voltage 150/300V [1] 50V

Maximum Common Mode

Voltage

Input (Overload) Protection 1600V 300V

Maximum Reading Rates

(Volts DC Only)

Maximum Single Channel Scan

Reading Rates [2]

Volts DC Accuracy (90 day),

1V dc input

Thermocouple Accuracy

(90 day)

Resistance-Temperature

Detectors (RTDs) Resolution

Resistance-Temperature

Detectors (RTDs) Accuracy

Time to Change Functions

(Between V dc, V ac,

Frequency, and Ohms)

[1] The 300V value is for channels 1 and 11 only; the 150V value is for all other channels.

[2] Drift Correction refers to an automatic internal measurement step performed with each

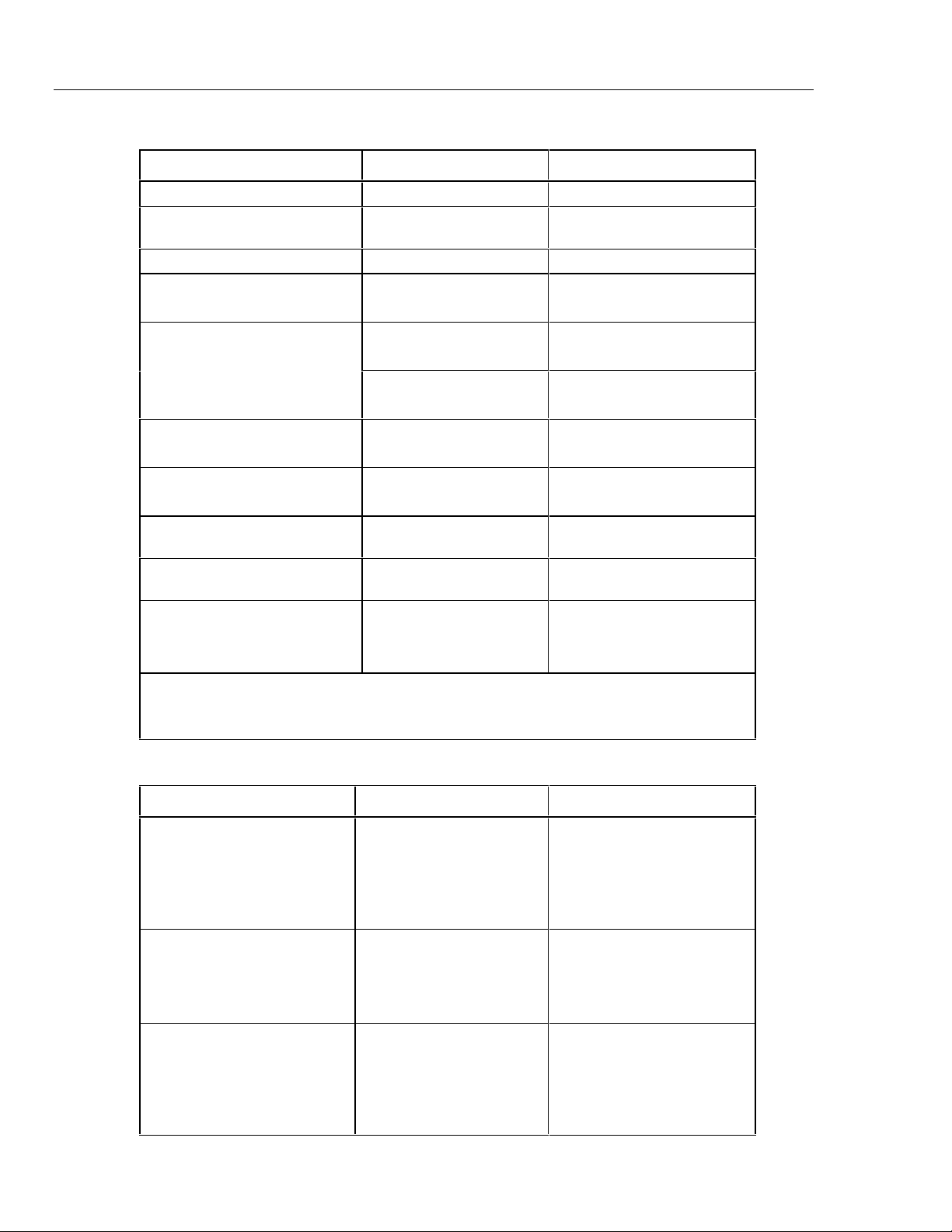

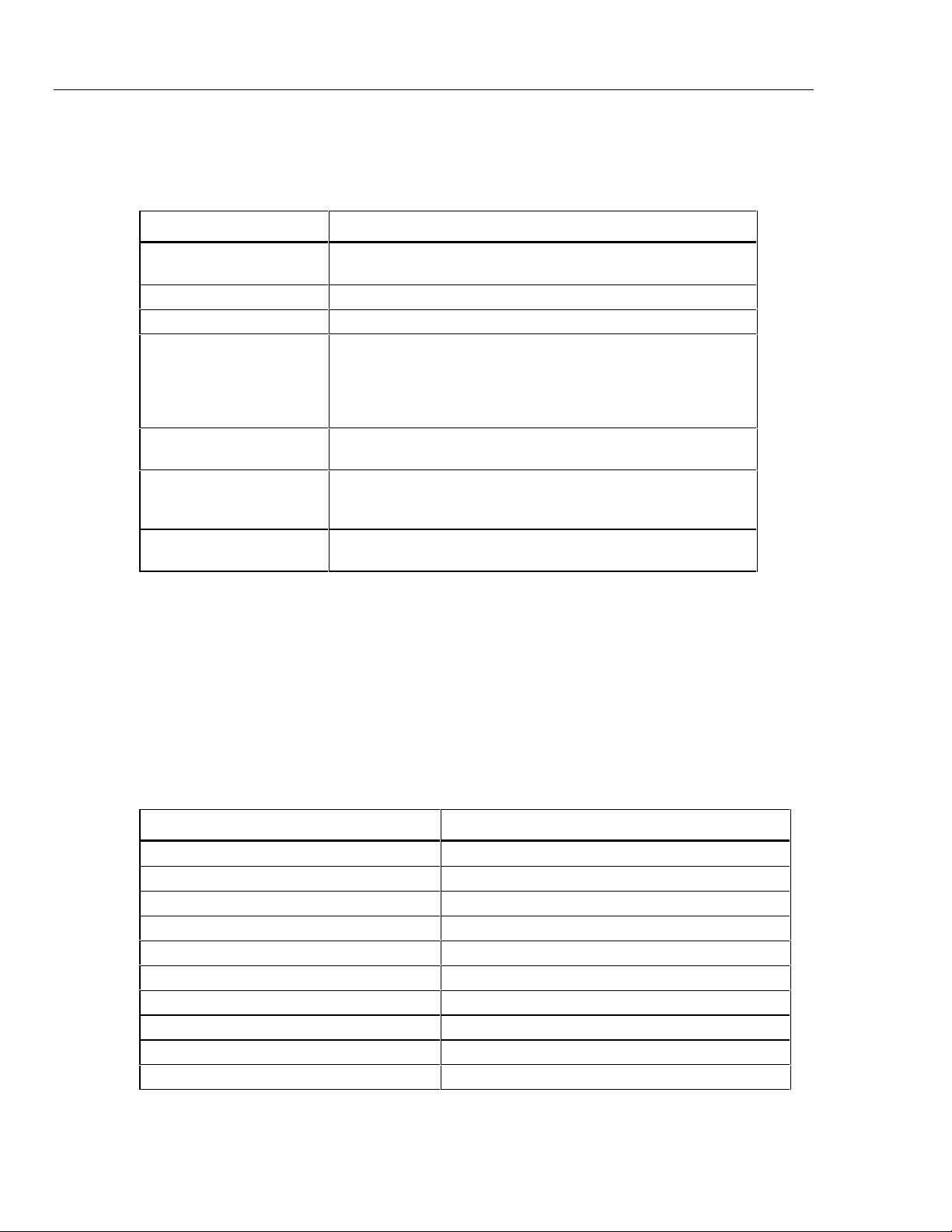

Table 1-1. Summary of 2640A/2645A Specifications

Specification 2640A 2645A

150/300V [1] 50V

143 readings/second

(scanning 20 channels)

80 readings/second

(Drift Correction enabled)

120 readings/second

(Drift Correction disabled)

0.02% 0.04%

0.3°C0.6°C

0.003°C0.03°C

0.12°C0.2°C

6 ms 6 ms

scan to correct for drift due to changes in ambient temperature and humidity.

1000 readings/second

(scanning 20 channels)

250 readings/second

(Drift Correction enabled)

400 readings/second

(Drift Correction disabled)

1-4

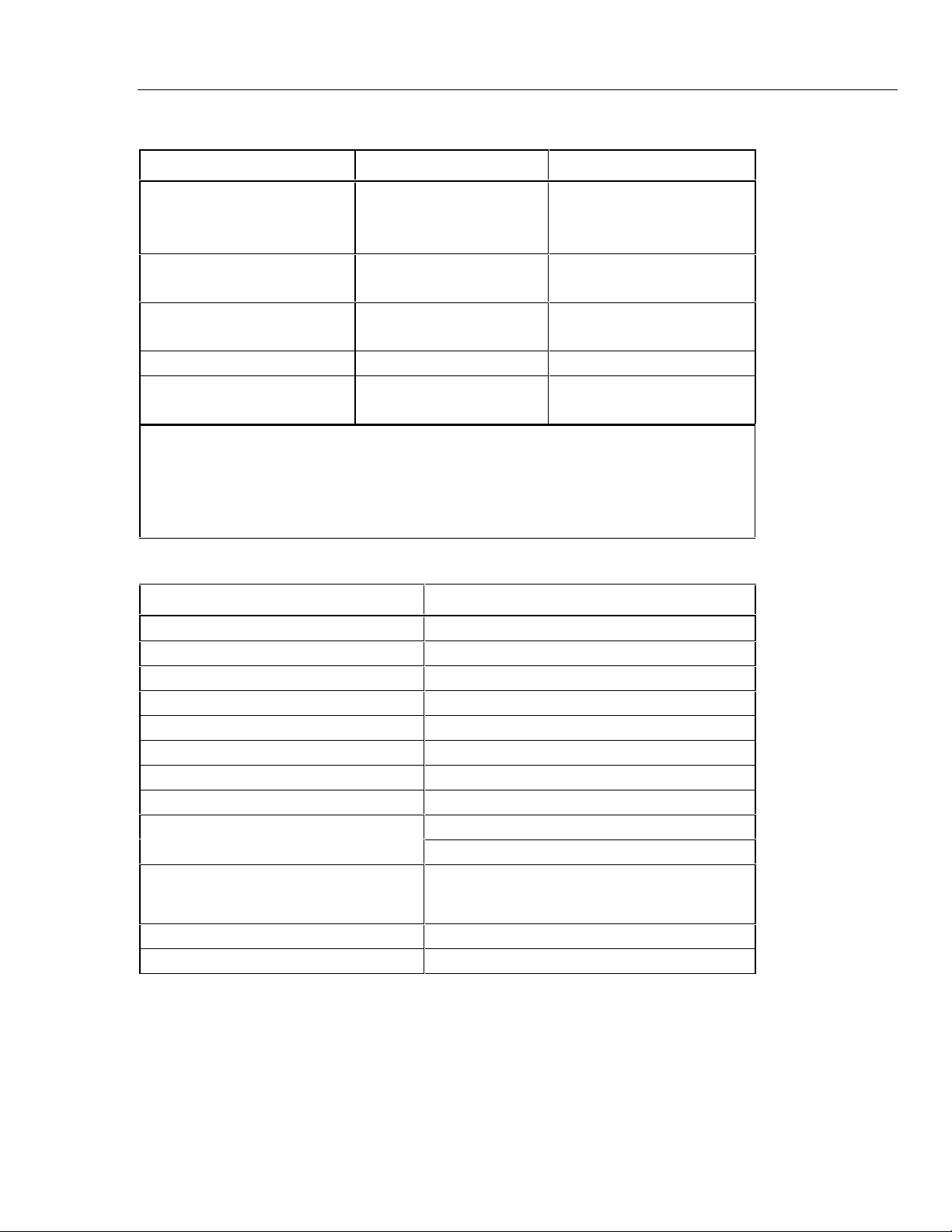

Table 1-2. Summary of 2640A/2645A Measurement Capabilities

Capability 2640A 2645A

Volts DC Measurements Ranges: 90 mV

300 mV

3V

30V

150/300V [1]

Autorange

Volts AC Measurements Ranges: 300 mV

3V

30V

150/300V [1]

Autorange

Resistance Measurements Ranges: 300 Ω

3 kΩ

30 kΩ

300 kΩ

3 MΩ

Autorange

Ranges: 90 mV

300 mV

3V

30V

50V

Autorange

Ranges: 300 mV

3V

30V

Autorange

Ranges: 30 kΩ

300 kΩ

3 MΩ

Autorange

Page 21

Introduction and Specification

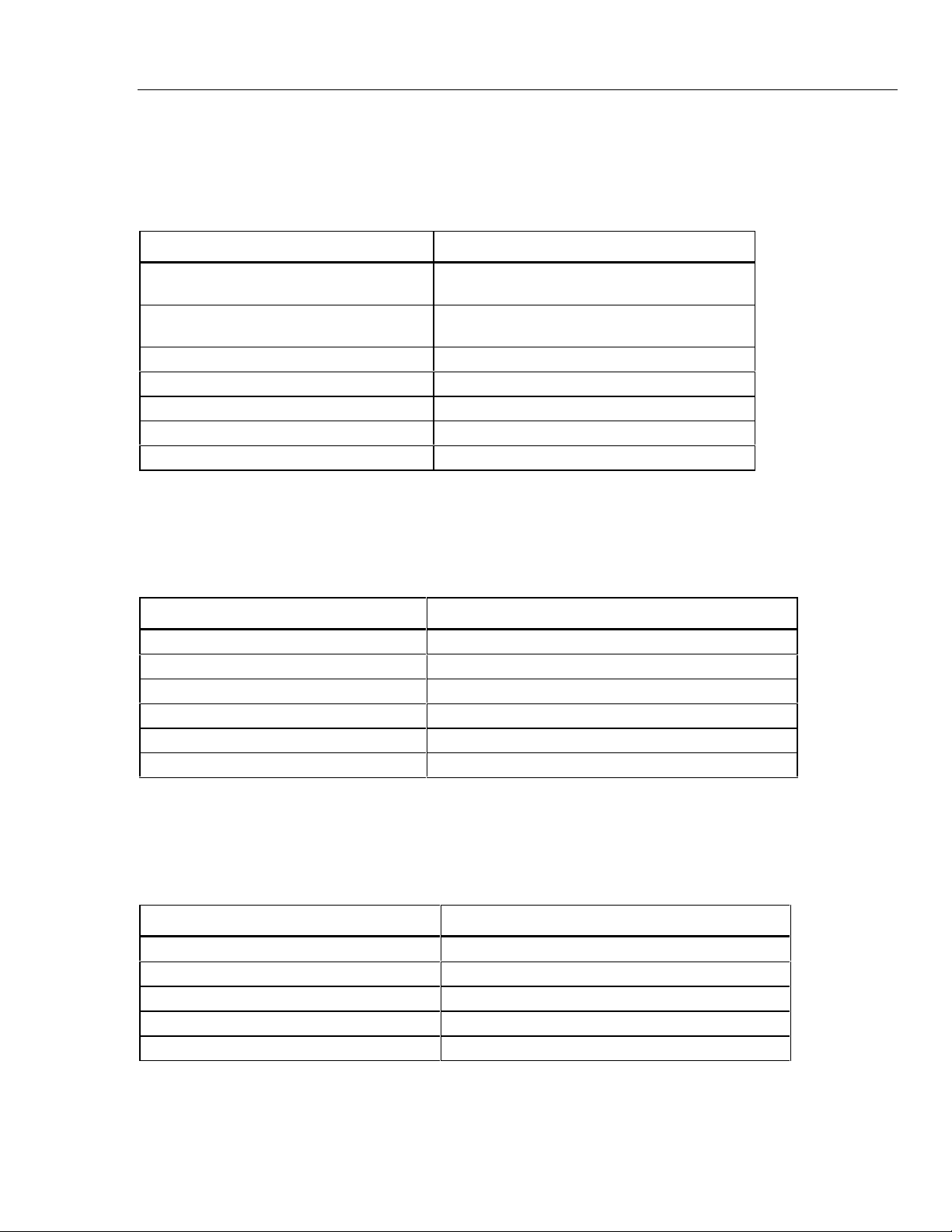

Table 1-2. Summary of 2640A/2645A Measurement Capabilities (cont)

Capability 2640A 2645A

Introduction

1

Temperature Measurements

(Thermocouple) [2]

Temperature Measurements

(RTD) (Two-wire)

Temperature Measurements

(RTD) (Four-wire)

Frequency Measurements [3] Ranges: Autorange Ranges: Autorange

Amperes DC Measurements [4] Ranges: 4 to 20 mA

[1] 300V range available only on channels 1 and 11.

[2] Open thermocouple detection is supported on a per-channel basis.

[3] Minimum frequency is 20 Hz. Signal strength must be at least 50 mV ac rms.

[4] Shunt resistor required (enter value; default is 10 ohms). The 4 to 20 mA scale displayed as

0% (4 mA) to 100% (20 mA).

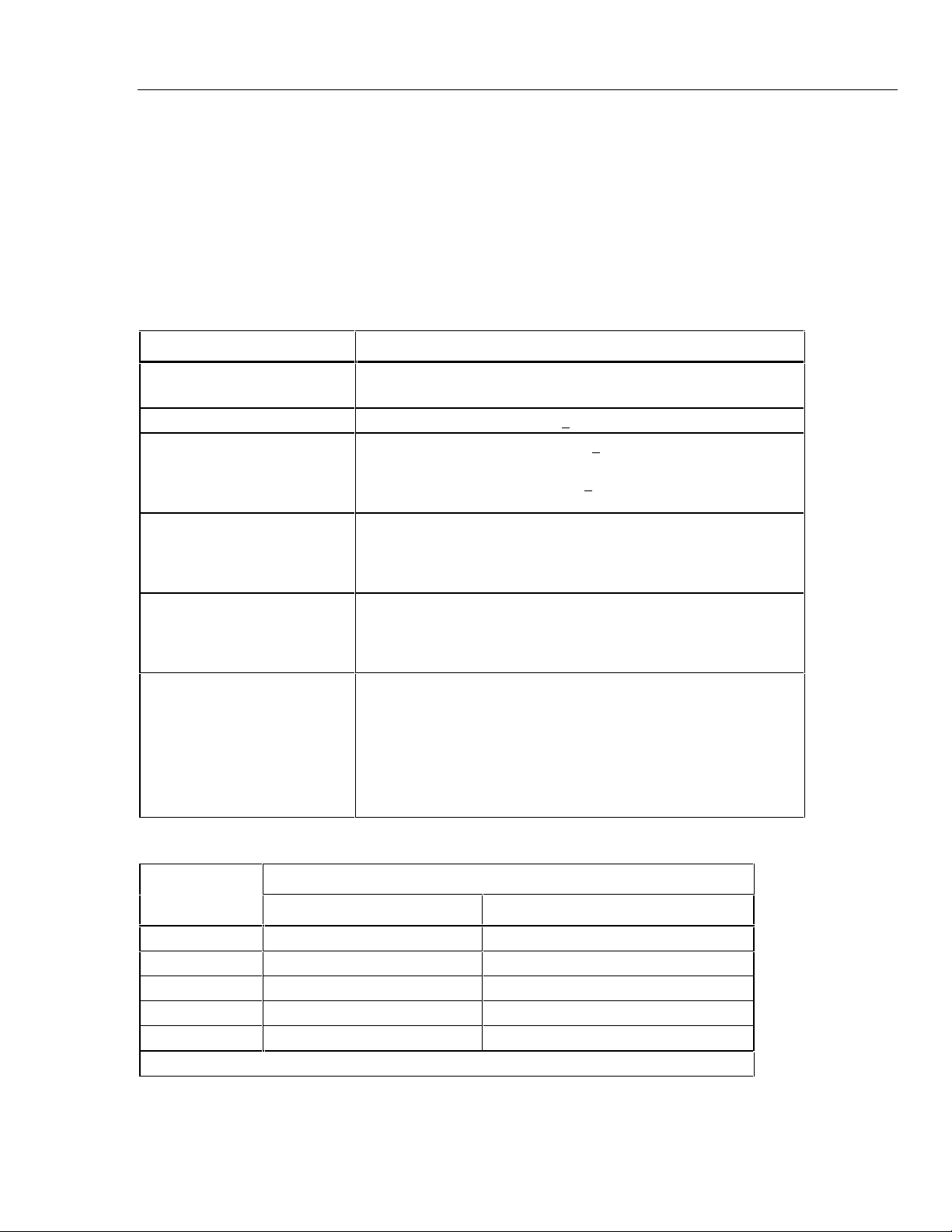

Feature Description

Analog Channels 20 (channels 1 to 20)

Computed Channels 10 (channels 21 to 30)

Alarm Limits Two per channel

Mx+B Scaling Any configured channel (1 to 30)

Scan Triggering Interval/External/Alarm Trigger

Channel Monitoring Any configured channel, scanning or not scanning

Setup and Operation Via host computer

Communications Ports Ethernet 10BASE2 and 10BASE-T

Primary Power AC - 107 to 264V ac, 50/60 Hz

Nonvolatile Memory (unaffected by cycling

instrument power)

Permanent Data Storage Via host computer

Real-Time Trend Plotting Via host computer

Thermocouples:

JKRSE

TBCN

RTD R0: 10 to 1010 (None)

RTD R0: 10 to 1010 RTD R0: 10 to 1010

0 to 100 mA

Table 1-3. Summary of 2640A/2645A Features

DC - 9 to 16V dc

Instrument parameters: Base Channel Number,

Line Frequency, Network Type, Socket Port, IP

Address, Baud Rate. (See Chapter 2.)

Thermocouples:

JKRSE

TBCN

Ranges: 4 to 20 mA

0 to 100 mA

1-5

Page 22

NetDAQ

Service Manual

Options and Accessories 1-2.

2640A NetDAQ Instrument

2645A NetDAQ Instrument

264XA-901 NetDAQ

264XA-902 NetDAQ

264XA-902U NetDAQ

264XA-801 Ethernet Card

264XA-802 Parallel-to-LAN Adapter (10BASE2)

80i-410 Clamp-On DC/AC Current Probe

80i-1010 Clamp-On DC/AC Current Probe

2620A-100 I/O connector set, including Universal Input Module, DIGITAL I/O

2620A-101 4-20 mA Current Shunt Strip

942615 NetDAQ Service Manual

Y2641 19-inch Rackmount Kit

Y2643 4-meter Cable Kit

Table 1-4 summarizes the available models, options and accessories, including

measurement transducers, software, connector sets, Ethernet interfaces, cables, and

components.

Table 1-4. Models, Options and Accessories

Model Description

Logger for Windows

Logger for Windows

Logger for Windows

and ALARM/TRIGGER I/O connectors.

(Isolated Network)

(General Network)

Network (Upgrade Kit)

Instrument Connector Set, 2620A-100 1-3.

The 2620A-100 is a complete set of input connectors: one Universal Input Module, one

ALARM/TRIGGER I/O connector, and one DIGITAL I/O connector. Each instrument

comes with a 2620A-100 Instrument Connector Set. The use of additional connector sets

allows quick equipment interface to several wiring setups.

Host Computer Ethernet Interfaces 1-4.

The 264XA-801 is the recommended Ethernet card and the 264XA-802 is the

recommended Parallel-to-LAN Adapter for host computer installations.

Interconnection Cables and Components 1-5.

Cables for equipment interconnection can be purchased as an option or fabricated.

Ethernet interconnection components such as BNC "T" and 50-ohm terminations are

available from any components supplier.

1-6

Page 23

Introduction and Specification

Operating Instructions

Operating Instructions 1-6.

Full operating instructions are provided in the NetDAQ User Manual (PN 942623). Refer

to the User Manual as necessary during the maintenance and repair procedures presented

in this Service Manual.

Organization of the Service Manual 1-7.

This manual focuses on performance tests, calibration procedures, and component-level

repair of the 2640A and 2645A networked data acquisition units. To that end, manual

chapters are often interdependent; effective troubleshooting may require not only

reference to the troubleshooting procedures in Chapter 5, but also some understanding of

the detailed Theory of Operation in Chapter 2 and some tracing of circuit operation in

the Schematic Diagrams presented in Chapter 7.

Often, scanning the table of contents yields an appropriate place to start using the

manual. A comprehensive table of contents is presented at the front of the manual; local

tables of contents are also presented at the beginning of each chapter for ease of

reference. If you know the topic name, the index at the end of the manual is probably a

good place to start.

1

The following descriptions introduce the manual:

Chapter 1 - Introduction and Specifications Introduces the instrument, describing its

features, options, and accessories. This chapter also discusses use of the Service Manual

and the various conventions used in describing the circuitry. Finally, a complete set of

specifications is presented.

Chapter 2 - Theory of Operation This chapter first categorizes the instrument’s

circuitry into functional blocks, with a description of each block’s role in overall

operation. A detailed circuit description is then given for each block. These descriptions

explore operation to the component level and fully support troubleshooting procedures

defined in Chapter 5.

Chapter 3 - General Maintenance Provides maintenance information covering

handling, cleaning, and fuse replacement. Access and reassembly procedures are also

explained in this chapter.

Chapter 4 - Performance Testing and Calibration This chapter provides performance

verification procedures, which relate to the specifications presented in Chapter 1. To

maintain these specifications, a full calibration procedure is also presented.

Chapter 5 - Diagnostic Testing and Troubleshooting The troubleshooting procedures

presented in this chapter rely closely on both the Theory of Operation presented in

Chapter 2, the Schematic Diagrams shown in Chapter 7, and the access information

provided in Chapter 3.

Chapter 6 - List of Replaceable Parts Includes parts lists for all standard assemblies.

Information on how and where to order parts is also provided.

Chapter 7 - Schematic Diagrams Includes schematic Diagrams for all standard and

optional assemblies. A list of mnemonic definitions is also included to aid in identifying

signal name abbreviations.

1-7

Page 24

NetDAQ

Service Manual

Conventions 1-8.

Throughout the manual set, certain notational conventions are used. A summary of these

conventions follows:

• Instrument Reference The term "instrument" is used in this manual to refer to both

the 2640A NetDAQ and 2645A NetDAQ networked data acquisition units. The

model number (2640A or 2645A) is used when discussing characteristics unique to

one instrument.

• Printed Circuit Assembly The term "pca" is used to represent a printed circuit

board and its attached parts.

• Signal Logic Polarity On schematic Diagrams, a signal name followed by a "*"

character is active (or asserted) low. Signals not so marked are active high.

• Circuit Nodes Individual pins or connections on a component are specified with a

dash (-) following the assembly and component reference designators. For example,

pin 19 of U30 on assembly A1 would be A1U30-19.

• Front Panel Interface User Notation For front panel operation, XXX, an

uppercase word or symbol without parentheses indicates a button to be pressed by

the user. Buttons can be pressed in four ways:

1. Press a single button to select a function or operation.

2. Press a combination of buttons, one after the other.

3. Press and hold down a button; then press another button.

4. Press multiple buttons simultaneously.

• Computer Interface User Notation For computer interface operation:

XXX An uppercase word without parentheses identifies a command by name.

<XXX> Angle brackets around all uppercase letters mean press the <XXX> key.

(xxx) A lowercase word in parentheses indicates a keyboard input.

1-8

Specifications 1-9.

Specifications are divided into three sections. The first section contains the combined

specifications that apply equally to both the 2640A and 2645A instruments. The second

section contains specifications that apply only to the 2640A instrument. The third section

contains specifications that apply only to the 2645A instrument.

2640A/2645A Combined Specifications 1-10.

The following specifications apply equally to both the 2640A and 2645A instruments.

The topics include:

• 2640A/2645A General Specifications

• 2640A/2645A Environmental Specifications

• 2640A/2645A Digital I/O and Totalizer Interface

Page 25

Introduction and Specification

Specifications

2640A/2645A General Specifications 1-11.

Table 1-5 provides the general specifications for the 2640A and 2645A instruments.

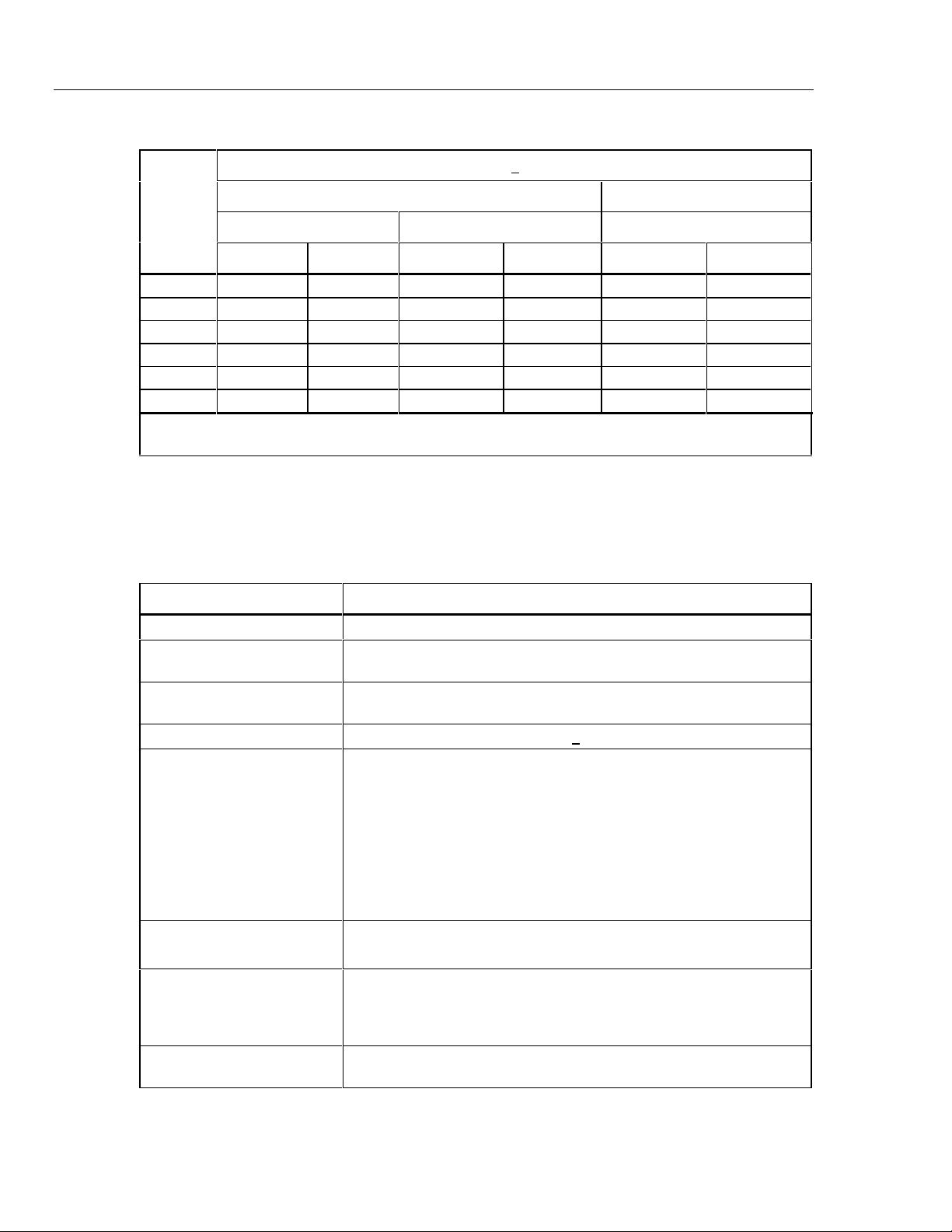

Table 1-5. 2640A/2645A General Specifications

Specification Characteristic

Channel Capacity 20

I/O Lines Total 12

Size 9.3 cm (3.67 in) high, 21.6 cm (8.5 in) wide, 36.2 cm (14.28 in) deep

Weight Net, 4 kg (8.8 lb.) Shipping, 6.0 kg (13.2 lb.)

Power 107 to 264V ac (no switching required), 45 to 65 Hz, 15 VA maximum

9V dc to 16V dc, 6W maximum. Specifications are for 50 or 60 Hz operation.

If both sources are applied simultaneously, ac voltage is used if it exceeds

approximately 8 times the dc voltage. Automatic switchover occurs between ac

and dc without interruption.

Standards Both instruments comply with:

IEC 1010-1

UL 1244

CSA Bulletin 556B

ANSI/ISA-S8201-1988

CSA C22.2 No. 101.1-92

Vfg. 243/1991 (when shielded cables are used)

FCC-15B, Class B level (when shielded cables are used)

Serial Interface

(RS-232C)

Common Mode

Voltage

Measurement Speed

(Scanning Rates)

Accuracy of Medium

Scanning Rate

Additional error if

“Automatic drift

correction” is turned

off.

Connector: 9 pin male (DB-9P)

Signals: TX, RX, DTR, RTS, GND

Modem Control: full duplex

Baud rates: 4800, 9600, 19200, 38400

Data format: 8 data bits, no parity bit, one stop bit

Flow control: XON/XOFF

Echo: Off

2640A 150V (300V on channels 1 and 11)

2645A 50V dc or 30V ac rms.

2640A

Slow - 6 readings per second

Medium - 48 readings per second (60 Hz)

Fast - 143 readings per second (20 configured channels)

Single Channel - 120 readings per second

2645A

Slow - 54 readings per second (60 Hz)

Medium - 200 readings per second

Fast - 1000 readings per second (20 configured channels)

Single Channel - 400 readings per second

Equal to (Fast Accuracy Rate + Slow Accuracy Rate)/2

If the instrument is fully warmed-up at the time drift correction was disabled, i.e.,

turned on at least 1 hour earlier: 1/10 of the 90-day specification per °C change

in ambient temperature from the temperature when drift correction was disabled.

If the instrument was not fully warmed up at the time of drift correction was

disabled: add an error equal to the 90-day specification for instrument warmup

+1/10 of the 90-day specification per °C change in ambient temperature from the

temperature when drift correction was disabled.

1

1-9

Page 26

NetDAQ

Service Manual

2640A/2645A Environmental Specifications 1-12.

Warmup Time 1 hour to rated specifications -or- 15 minutes if relative humidity

Operating Temperature -10°C to 60°C (14°F to 140°F)

Storage Temperature -40°C to +70°C (-40°F to +158F)

Relative Humidity 90% maximum for -10°C to 28°C (14°F to 82.4°F)

Altitude Operating: 2,000m (6,561 ft) maximum

Vibration 0.7g at 15 Hz

Shock 30g half-sine per Mil-T-28800

Table 1-6 provides a summary of the environmental specifications for the 2640A/2645A.

Table 1-6. Environmental Specifications

Specification Characteristic

(noncondensing) is 50% or less.

75% maximum for 28°C to 35°C (82.4°F to 95°F)

50% maximum for 35°C to 60°C (95°F to 140°F)

(3 MΩ range, reduce humidity rating by 25% for 1 hour warmup.

The 3 MΩ range meets full humidity ratings with 2-hour warmup.)

Non-operating: 12,200m (40,000 ft) maximum

1.3g at 25 Hz

3g at 55 Hz

Bench handling per Mil-T-28800

2640A/2645A Input/Output Capabilities 1-13.

The following specifications include the input/output functions, including the Digital

I/O, Trigger Out, Trigger In, and Master Alarm output.

Digital I/O 1-14.

Table 1-7 provides a summary of the Digital I/O specifications for the 8 Digital I/O lines

(0 to 7). Digital I/O is located on the DIGITAL I/O connector, terminals 0 to 7, and

GND.

Table 1-7. 2640A/2645A DIGITAL I/O Specification

Specification Characteristic

Maximum Input Voltage 30V

Minimum Input Voltage -4V

Isolation None (dc coupled)

Threshold 1.4V

Hysteresis 500 mV

Specification Characteristic

Output Voltage - TTL Logical Zero 0.8V maximum for an Iout of -1.0 mA (1 LSTTL load)

Output Voltage - TTL Logical One 3.8V minimum for an Iout of 0.05 mA (1 LSTTL load)

Output Voltage - Non-TTL Load Zero 1.8V maximum for an Iout of -20 mA

Output Voltage - Non-TTL Load One 3.25V maximum for an Iout of -50 mA

1-10

Page 27

Introduction and Specification

Specifications

Trigger In 1-15.

Table 1-8 provides a summary of the Trigger In specifications. The Trigger In input is

located on the ALARM/TRIGGER I/O connector, terminals TI and GND.

Table 1-8. 2640A/2645A Trigger In (TI) Specification

Specification Characteristic

Logical High - Trigger not set Minimum: 2.0V

Maximum: 7.0V

Logical Low - Trigger set Minimum: -0.6V

Maximum: +0.8 V

Compatibility TTL or Contact Closure

Isolation None (dc coupled)

Minimum Pulse Width 5 µs

Maximum Frequency Nominal 400 Hz

Repeatability 3 ms

Trigger Out 1-16.

1

Table 1-9 provides a summary of the Trigger Out specifications. The Trigger Out output

is located on the ALARM/TRIGGER I/O connector, terminals TO and GND.

Table 1-9. 2640A/2645A Trigger Out (TO) Specification

Specification Characteristic

TTL Logical Zero - Trigger Out Set 0.8V maximum for an Iout of -1.0 mA (1 LSTTL load)

TTL Logical One - Trigger Out Not Set 3.8V minimum for an Iout of 0.05 mA (1 LSTTL load)

Non-TTL Logical Zero - Trigger Out Set 1.8V maximum for an Iout of -20 mA

Non-TTL Logical One - Trigger Out Not Set 3.25V maximum for an Iout of -50 mA

Pulse Duration (Logic Low) 125 µs

Isolation None

Master Alarm 1-17.

Table 1-10 provides a summary of the Master Alarm specifications. The Master Alarm

output is located on the ALARM/TRIGGER I/O connector, terminals MA and GND.

Table 1-10. 2640A/2645A Master Alarm (MA) Specification

Specification Characteristic

TTL Logical Zero - Master Alarm Set 0.8V maximum for an Iout of -1.0 mA (1 LSTTL load)

TTL Logical One - Master Alarm Not Set 3.8V minimum for an Iout of 0.05 mA (1 LSTTL load)

Non-TTL Logical Zero - Master Alarm Set 1.8V maximum for an Iout of -20 mA

Non-TTL Logical One - Master Alarm Not Set 3.25V maximum for an Iout of -50 mA

Isolation None

1-11

Page 28

NetDAQ

Service Manual

2640A/2645A Totalizer 1-18.

Maximum Input Voltage 30V

Minimum Input Voltage -4V

Minimum Peak Voltage 2V

Isolation None (dc coupled)

Threshold 1.4V

Hysteresis 500 mV

Input Debouncing None or 1.75 ms (selectable)

Maximum Transition Rate 5 kHz (Debounce disabled)

Maximum Count 4,294,967,295

Table 1-11 provides a summary of the Totalizer specifications. The Totalizer input is

located on the DIGITAL I/O connector, terminals Σ and GND.

Table 1-11. 2640A/2645A Totalizer Specification

Specification Characteristic

500 Hz (Debounce enabled)

2640A/2645A Real-Time Clock and Calendar 1-19.

Table 1-12 provides a summary of the battery powered real-time clock and calendar.

Table 1-12. 2640A/2645A Real-Time Clock and Calendar

Specification Characteristic

Accuracy 1 minute per month for 0°C to 50°C range

Battery Life >15 unpowered instrument years for 0°C to 28°C (32°F to 82.4°F).

>6 unpowered instrument years for 0°C to 50°C (32°F to 122°F).

>4 unpowered instrument years for 50°C to 70°C (122°F to 158°F).

1-12

Page 29

Introduction and Specification

Specifications

2640A Specifications 1-20.

This section includes specifications specific to the 2640A instrument by measurement

function.

2640A DC Voltage Measurement Specifications 1-21.

Tables 1-13 to 1-15 provide 2640A specifications for the dc voltage measurement

function.

Table 1-13. 2640A DC Voltage General Specifications

Specification Characteristic

Input Impedance 100 MΩ in parallel with 300 pF maximum for ranges <=3V

10 MΩ in parallel with 100 pF maximum for ranges >3V

Normal Mode Rejection 50 dB minimum at 50 Hz/60 Hz +0.1%, Slow Rate

Common Mode Rejection 120 dB minimum at dc, 50 Hz/60 Hz +0.1%, 1 kΩ imbalance, Slow

Rate

80 dB minimum at dc, 50 Hz/60 Hz +0.1%, 1 kΩ imbalance, Medium

and Fast Rates

Channel-to-Channel Crosstalk 120 dB minimum Slow Rate (e.g., 30V dc on channel 1 may cause a

30 µV error on channel 2)

100 dB minimum Medium and Fast Rates (e.g., 1V dc on channel 1

may cause a 10 µV error on channel 2)

Temperature Coefficient For % input: Add 1/10th the 90-day specification per °C above 28 °C

or below 18 °C

For floor error (V): Add 1/20th the 90-day specification per °C above

28 °C or below 18 °C

Maximum Input Voltage The lesser voltage of:

300V from any terminal on channels 1 and 11 to earth;

150V from any terminal on channels 2 through 10, and 12 through 20

to earth;

300V from any terminal on channels 1 and 11 to any other terminal;

150V from any terminal on channels 2 through 10, and 12 through 20

to any other input terminal

1

Table 1-14. 2640A DC Voltage Range and Resolution Specifications

Resolution

Range

90 mV 0.3 µV1 µV

300 mV 1 µV3 µV

3V 10 µV30 µV

30V 100 µV 300 µV

150V/300V 1 mV 3 mV

Note 300V range applies to channels 1 and 11 only.

Slow Fast

1-13

Page 30

NetDAQ

Service Manual

90 mV .01%+7 µV .01%+17 µV .013%+8 µV .013%+18 µV .042%+18.2 µV .042%+44.2 µV

300 mV .01%+15 µV .01%+30 µV .013%+17 µV .013%+35 µV .042%+39 µV .042%+78 µV

750 mV* .01%+40 µV .01%+70 µV .013%+50 µV .013%+80 µV .042%+104 µV .042%+182 µV

3V .01%+0.1 mV .01%+0.2 mV .013%+0.15 mV .013%+0.2 mV .042%+0.26 mV .042%+0.52 mV

30V .01%+1.5 mV .02%+3 mV .013%+1.7 mV .026%+3.5 mV .042%+3.9 mV .084%+7.8 mV

150/300V** .01%+15 mV .04%+30 mV .013%+17 mV .052%+35 mV .042%+39 mV .168%+78 mV

* The 750 mV range is used internally to the instrument and not user selectable.

** 300V range applies to channels 1 and 11 only.

2640A AC Voltage Measurement Specifications 1-22.

Range

Table 1-15. 2640A DC Voltage Accuracy Specifications

Accuracy, 3σ + (% input + V)

18°C to 28°C-10°C to 60°C

90 Day 1 Year 1 Year

Slow Fast Slow Fast Slow Fast

Tables 1-16 to 1-18 provide 2640A specifications for the ac voltage measurement

function.

Table 1-16. 2640A AC Voltage General Specifications

Specification Characteristic

Input Impedance 1 MΩ in parallel with 100 pF

Maximum Crest Factor 3.0 Maximum

2.0 for rated accuracy

Crest Factor Error For nonsinusoidal input signals with crest factors between 2 and 3 and

pulse widths >=100 µs, add 0.2% to the accuracy specifications.

Common Mode Rejection 80 dB minimum at dc, 50 Hz/60 Hz +0.1%, 1 kΩ imbalance, Slow Rate

Maximum Input Voltage The lesser voltage of:

300V ac rms from any terminal on channels 1 and 11 to earth.

150V ac rms from any terminal on channels 2 through 10, and 12

through 20 to earth.

300V ac rms from any terminal on channels 1 and 11 to any other

terminal.

150V ac rms from any terminal on channels 2 through 10 and 12

through 20 to any other input terminal.

Maximum Volt-Hertz Product 2x106 Volt-Hertz product on any range, normal mode input.

6

1x10

Volt-Hertz product on any range, common mode input.

Temperature Coefficient Linear interpolation between 2 applicable points for temperatures

between 28°C and 60°C, or -10°C and 18°C, e.g., if the applicable

specification at 28°C is 2% and the specification at 60°C is 3%, then the

specification at 40°C is (3%-2%)x(40-28)/(60-28)+2%=2.375%.

DC Component Error The presence of a dc voltage will cause an indeterminate error in the

reading of the ac voltage on the input.

1-14

Page 31

Introduction and Specification

Table 1-17. 2640A AC Voltage Range and Resolution Specifications

Specifications

1

Range

Slow Fast

Full Scale +30,000 +3,000

300 mV 10 µV 100 µV 20 mV

3V 100 µV 1 mV 200 mV

30V 1 mV 10 mV 2V