Fairchild Semiconductor NC7WZ07 Datasheet

NC7WZ07

NC7WZ07 TinyLogic

March 1999

Revised May 2003

TinyLogic

General Description

The NC7WZ07 is a dual buffer with open drain outputs

from Fairchild’s Ultra High Speed Series of TinyLogic

the space saving SC70 6-lead packag e. The dev ice is fabricated with advanced CM OS technology to achieve ultra

high speed with high output drive while maintaining low

static power dissipati on over a very broad V

range. The device is s pecified to operate over the 1.6 5V to

5.5V V

range. The inputs and outputs are high im ped-

CC

ance when V

independent of V

UHS Dual Buffer (Open Drain Outputs)

Features

■ Space saving SC70 6-lead package

operating

CC

is 0V. Inputs tolerate voltages up to 7V

CC

operating voltage.

CC

in

■ Ultra small MicroPak

■ Ultra High Speed: t

■ High IOL Output Drive: +24 mA at 3V V

■ Broad VCC Operating Range: 1.65V to 5.5V

■ Matches the performance of LCX when operated at

3.3V V

CC

■ Power down high impedance inputs/outputs

■ Overvoltage tolerant inputs facilitate 5V to 3V translation

■ Patented noise/EMI reduction circuitry implemented

leadless package

2.3 ns Typ into 50 pF at 5V V

PZL

CC

CC

Ordering Code:

Order Package Product Code

Number Number Top Mark

NC7WZ07P6X MAA06A Z07 6-Lead SC70, EIAJ SC88, 1.25mm Wide 3k Units on Tape and Reel

NC7WZ07L6X MAC06A D3 6-Lead MicroPak, 1.0mm Wide 5k Units on Tape and Reel

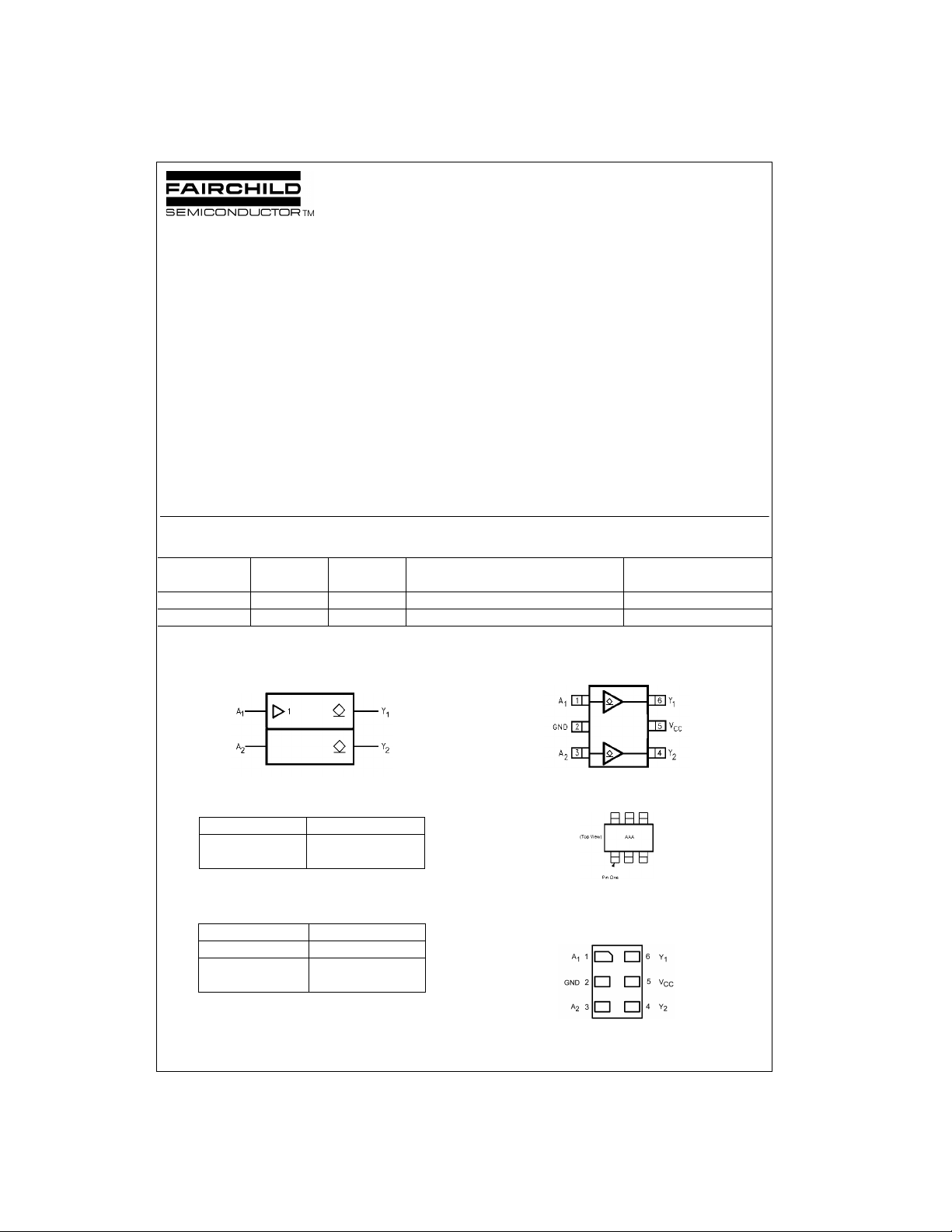

Logic Symbol

IEEE/IEC

Package Descript ion Supplied As

Connection Diagrams

Pin Assignments for SC 70

UHS Dual Buffer (Open Drain Outputs)

(Top View)

Pin Descriptions

Pin Names Description

A

, A

1

2

Y

, Y

1

2

Function Table

Input Output

AY

LL

HZ

H = HIGH Logic Le v el

L = LOW Logic Level

TinyLogic is a registered trademark of F airc hild Semiconduct or Corporation.

MicroPak is a tradem ark of Fairchild Semiconductor Corporation.

© 2003 Fairchild Semiconductor Corporation DS500218 www.fairchildsemi.com

Y = A

Data Inputs

Output

AAA represents Product Code Top Mark - see ordering code

Note: Orientation of Top Mark determines Pin One location. Read the top

product code mark lef t to right, Pin One is the lower left pin (see diagram ).

Pin One Orientation Diagram

Pad Assignments for MicroPak

(Top Thru View)

Absolute Maximum Ratings(Note 1) Recommended Operating

Supply Voltage (VCC) −0.5V to +7V

DC Input Voltage (V

NC7WZ07

DC Output Voltage (V

DC Input Diode Current (I

@ V

< −0.5V −50 mA

IN

DC Output Diode Current (I

< −0.5V −50 mA

@ V

OUT

DC Output Current (I

DC V

/GND Current (ICC/I

CC

Storage Temperature (T

Junction Temperature under Bias (T

Junction Lead Temperature (T

) −0.5V to +7V

IN

) −0.5V to +7V

OUT

)

IK

)

OK

) +50 mA

OUT

) ±100 mA

GND

) −65°C to +150°C

STG

) 150°C

J

)

L

(Soldering, 10 seconds) 260

Power Dissipation (P

) @ +85°C 180 mW

D

Conditions

Supply Voltage Operating (V

Supply Voltage Data Retention (V

Input Voltage (V

Output Voltage (V

Operating Temperature (T

Input Rise and Fall Time (t

= 1.8V, 2.5V ± 0.2V 0 ns/V to 20 ns/V

V

CC

V

= 3.3V ± 0.3V 0 ns/V to 10 ns/V

CC

V

= 5.0V ± 0.5V 0 ns/V to 5 ns/V

CC

Thermal Resistance (

°C

Note 1: Absolute maximum ratings are DC values beyond which the devi ce

may be damage d or h ave its us eful life im pai red. Th e dat as heet sp ecific ations should be met, without exception, to ensure that the system design is

reliable over its power supply, temperature, and output/input loading variables. Fairchild does no t recommend operation outsid e datasheet spec ifications.

Note 2: Unused inputs must be held HIGH or LOW. They may not float.

(Note 2)

) 1.65V to 5.5V

CC

)0V to 5.5V

IN

)0V to 5.5V

OUT

) −40°C to +85°C

A

, tf)

r

θ

) 350° C/W

JA

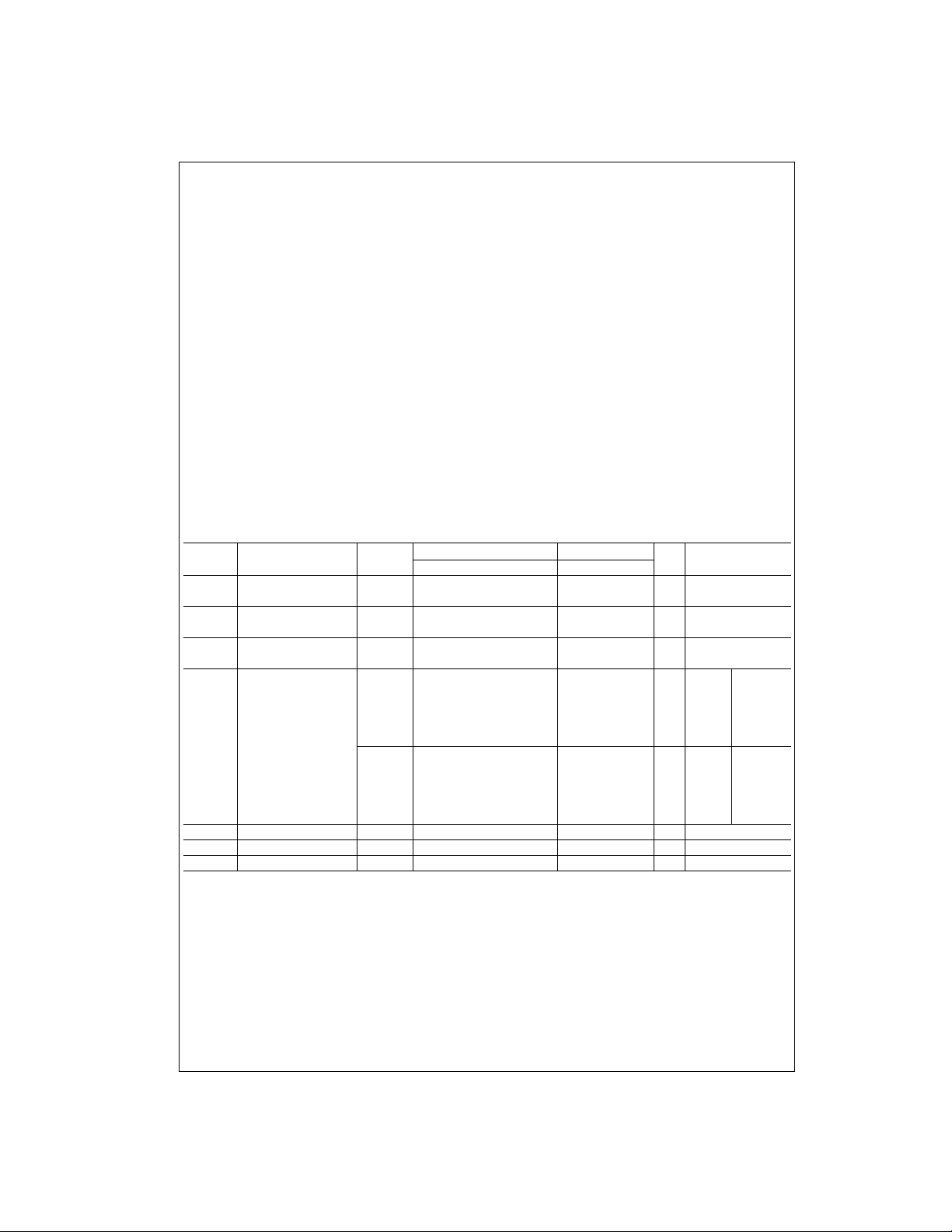

DC Electrical Characteristics

Symbol Parameter

V

IH

V

IL

I

LKG

V

OL

I

IN

I

OFF

I

CC

HIGH Level Input Voltage 1.65 to 1.95 0.75 V

LOW Level Input Voltage 1.65 to 1.95 0.25 V

HIGH Level Output

Leakage Current V

LOW Level Output Voltage 1.65 0.0 0.1 0.0

Input Leakage Current 0 to 5.5 ±0.1 ±1.0 µA0 ≤ VIN ≤ 5.5V

Power Off Leakage Current 0.0 1 10 µAVIN or V

Quiescent Supply Current 1.65 to 5.5 1.0 10 µAVIN = 5.5V, GND

V

CC

(V) MinTypMaxMinMax

2.3 to 5.5 0.7 V

2.3 to 5.5 0.3 V

1.65 to 5.5 ±5 ±10 µA

1.8 0.0 0.1 0.1

2.3 0.0 0.1 0.1

3.0 0.0 0.1 0.1

4.5 0.0 0.1 0.1

1.65 0.08 0.24 0.24

2.3 0.10 0.3 0.3 I

3.0 0.16 0.4 0.4 IOL = 16 mA

3.0 0.24 0.55 0.55 IOL = 24 mA

4.5 0.25 0.55 0.55 IOL = 32 mA

TA = +25°CT

CC

CC

A

0.75 V

0.7 V

CC

CC

= −40°C to +85°C

CC

CC

0.25 V

0.3 V

CC

CC

) 1.5V to 5.5V

CC

Units Conditions

V

V

VIN = V

IH

= VCC or GND

OUT

VV

= VILIOL = 100 µA

IN

IOL = 4 mA

= 8 mA

OUT

OL

= 5.5V

V

www.fairchildsemi.com 2

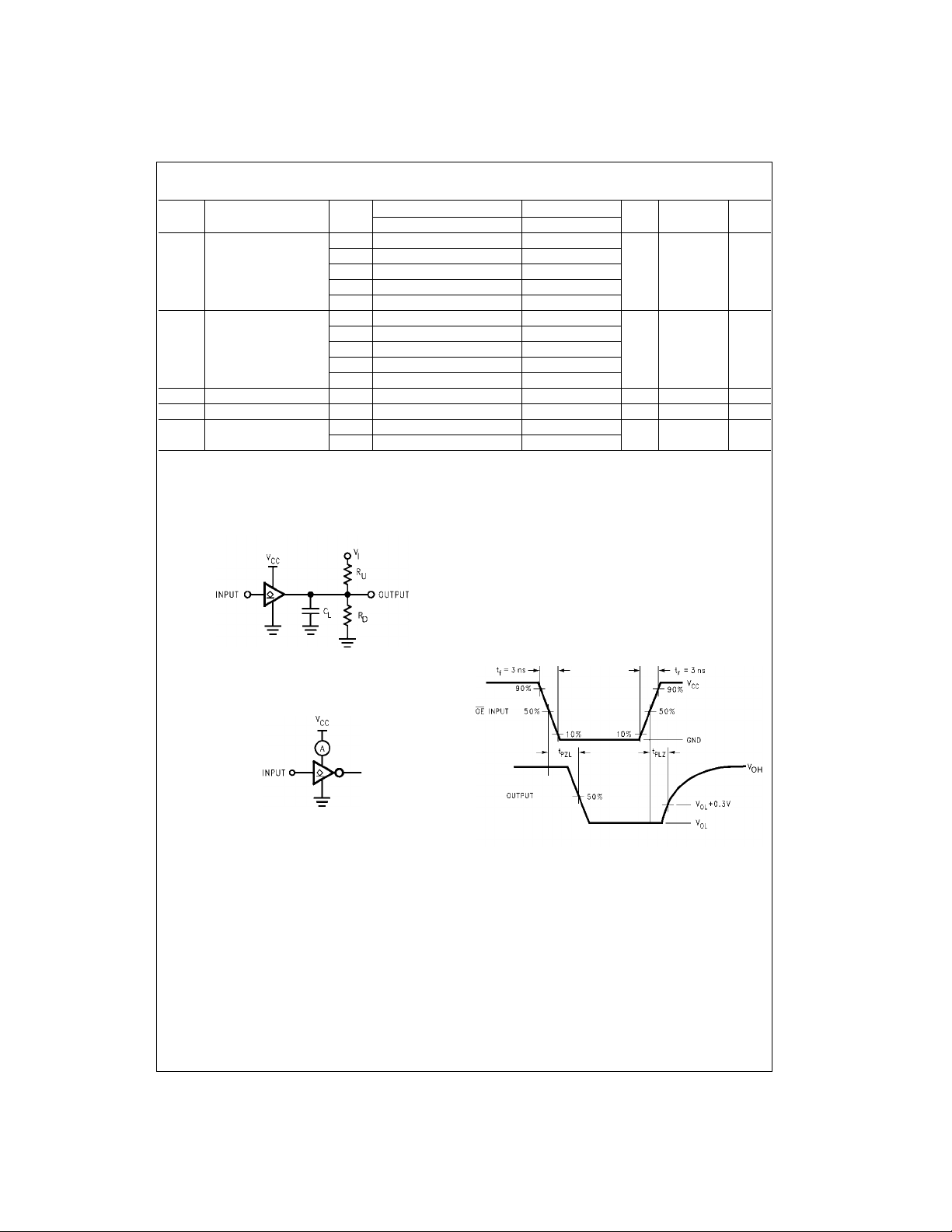

AC Electrical Characteristics

V

Symbol Parameter

t

Propagation Delay 1.65 1.8 6.6 11.5 1.8 12.6

PZL

CC

(V) Min Typ Max Min Max Number

1.8 1.8 5.5 9.5 1.8 10.5 CL = 50 pF

2.5 ± 0.2 1.2 3.7 5.8 1.2 6.4 RU = 500Ω

3.3 ± 0.3 0.8 2.9 4.4 0.8 4.8 RD = 500Ω

5.0 ± 0.5 0.5 2.3 3.5 0.5 3.9 VI = 2 x V

t

Propagation Delay 1.65 1.8 5.5 11.5 1.8 12.6

PLZ

1.8 1.8 4.3 9.5 1.8 10.5 C

2.5 ± 0.2 1.2 2.8 5.8 1.2 6.4 RU = 500Ω

3.3 ± 0.3 0.8 2.1 4.4 0.8 4.8 RD = 500Ω

5.0 ± 0.5 0.5 1.4 3.5 0.5 3.9 VI = 2 x V

C

C

C

Input Capacitance 0 2.5 pF

IN

Output Capacitance 0 4.0 pF

OUT

Power Dissipation 3.3 3

PD

Capacitance 5.0 4

Note 3: CPD is defined as the value of the internal equivalent capacitance which is derived from dynamic operating current consumption (I

loading and operating at 50% duty cycle. (See Figure 2.) C

= (CPD)(VCC)(fIN) + (ICCstatic).

I

CCD

TA = +25°CT

is related to I

PD

dynamic operating current by the express ion:

CCD

= −40°C to +85°C

A

Units Conditions

ns

ns

pF (Note 3) Figure 2

AC Loading and Waveforms

= 50 pF

L

CC

CC

) at no output

CCD

Figure

Figures

1, 3

Figures

1, 3

NC7WZ07

CL includes load and s tr ay c apacitance

Input PR R = 1.0 MHz; t

= 500 ns

W

FIGURE 1. AC Test Circuit

Input = AC Wavefor m; tr = tf = 1.8 ns;

PRR = 10 MHz; Duty Cycle = 50%

FIGURE 2. I

CCD

Test Circuit

FIGURE 3. AC Waveforms

3 www.fairchildsemi.com

Loading...

Loading...