Fairchild Semiconductor MM74HC259M, MM74HC259N, MM74HC259MTC, MM74HC259MTCX, MM74HC259SJX Datasheet

...

September 1983

Revised February 1999

MM74HC259 8-Bit Addressable Latch/3-to-8 Line Decoder

© 1999 Fairchild Semiconductor Corporation DS005006.prf www.fairchildsemi.com

MM74HC259

8-Bit Addressable Latch/3-to-8 Line Decoder

General Description

The MM74HC259 device utilizes advanced silicon-gate

CMOS technology to implement an 8-bit addressable latch,

designed for general purpose storage applications in digital

systems.

The MM74HC259 has a single data in put (D), 8 latch out-

puts (Q1–Q8), 3 addres s inputs (A, B, and C), a co mmon

enable input (G

), and a common CLEAR input. To operate

this device as an addres sable latch, d ata is held on th e D

input, and the add ress of the la tch i nto whic h th e dat a is to

be entered is held on the A, B, and C inputs. When

ENABLE is taken LOW the data flows through to the

addressed ou tpu t. The data i s stor ed wh en ENABL E tr ansi tions from LOW-to-HIGH. All unaddressed latches will

remain unaffected. With enable in the HIGH state the

device is deselected, and all latches remain in their previous state, unaffected by changes on the data or a ddress

inputs. To eliminate the possibility of entering erroneous

data into the latches, the enable should be held HIGH

(inactive) while the address lines are changing.

If enable is held HIGH and CLEAR is taken LOW all eight

latches are cleared to a LOW state. If enable is LOW all

latches except the addressed latch will be cleared. The

addressed latch will instead follow the D input, effectively

implementing a 3-to-8 line decoder.

All inputs are protected from damage due to static discharge by diodes to V

CC

and ground.

Features

■ Typical propagation delay: 18 ns

■ Wide supply range: 2–6V

■ Low input current: 1 µA maximum

■ Low quiescent current: 80 µA maximum (74HC Series)

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering cod e.

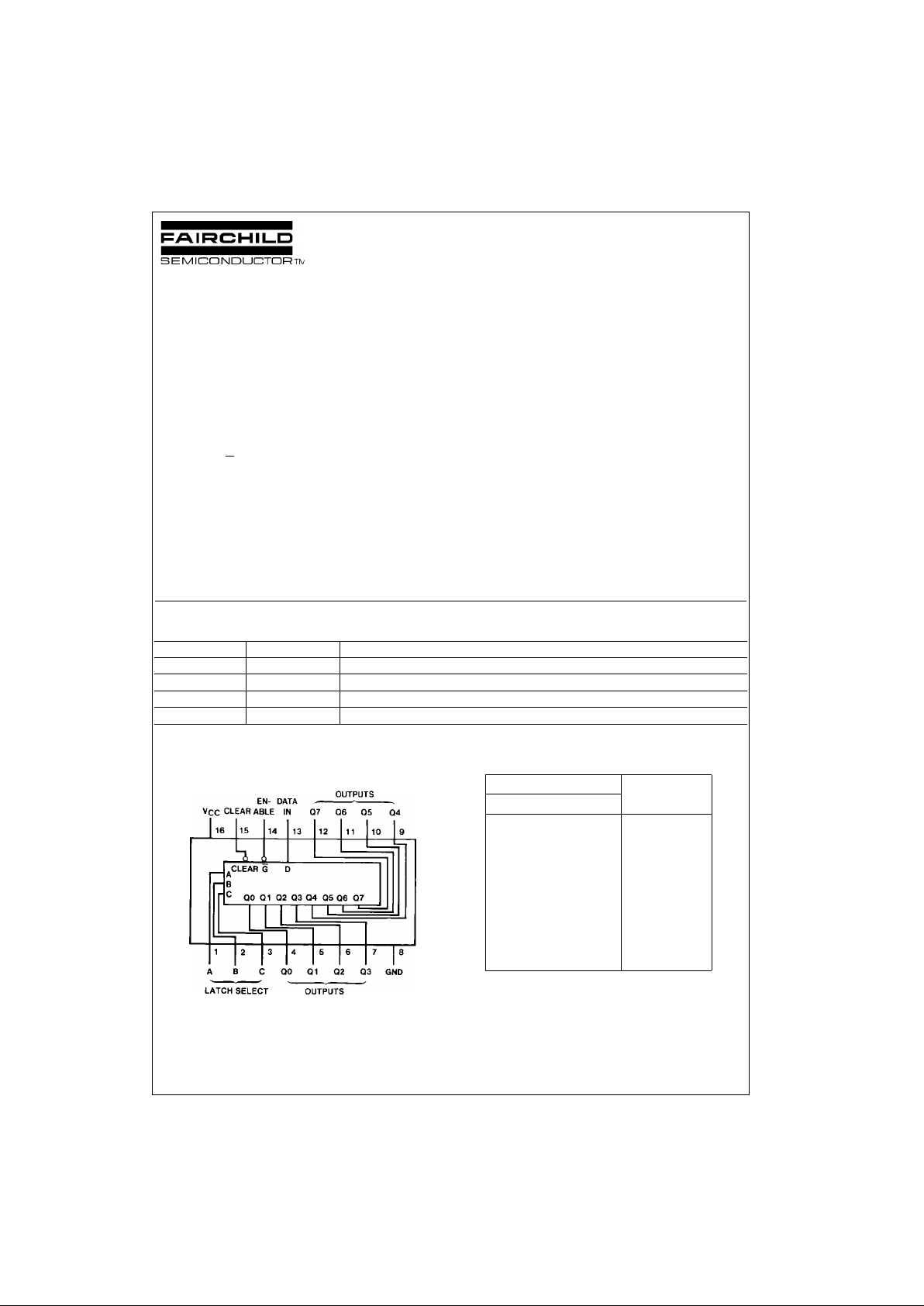

Connection Diagram

Pin Assignments f or DIP, SOIC, SOP and TSSOP

Top View

Latch Selection Table

H = HIGH level, L = LOW level

D = the level at the d at a input

Q

i0

the level of Qi (i = 0, 1...7, as appropriate)

before the indicate d s te ady-state input

conditions were est ablished.

Order Number Package Number Package Description

MM74HC259M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150” Narrow

MM74HC259SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

MM74HC259MTC MTC16 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

MM74HC259N N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

Select Inputs Latch

C B A Addressed

LLL 0

LLH 1

LHL 2

LHH 3

HLL 4

HLH 5

HHL 6

HHH 7

www.fairchildsemi.com 2

MM74HC259

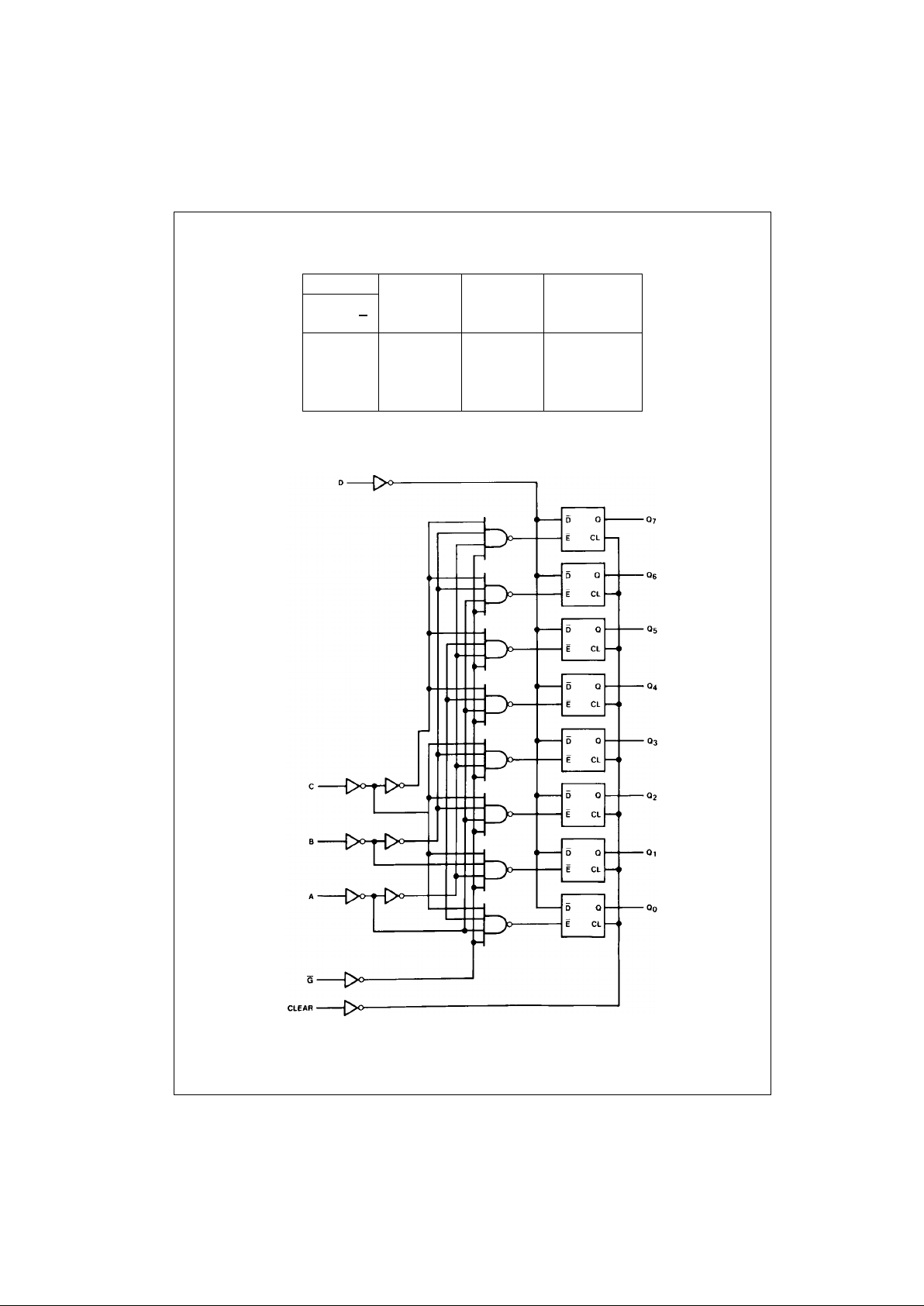

Truth Table

Logic Diagram

Inputs Outputs of Each

Addressed Other Function

Clear G

Latch Output

HL D Q

i0

Addressable Latch

HH Q

i0

Q

i0

Memory

L L D L 8-Line Decoder

L H L L Clear

3 www.fairchildsemi.com

MM74HC259

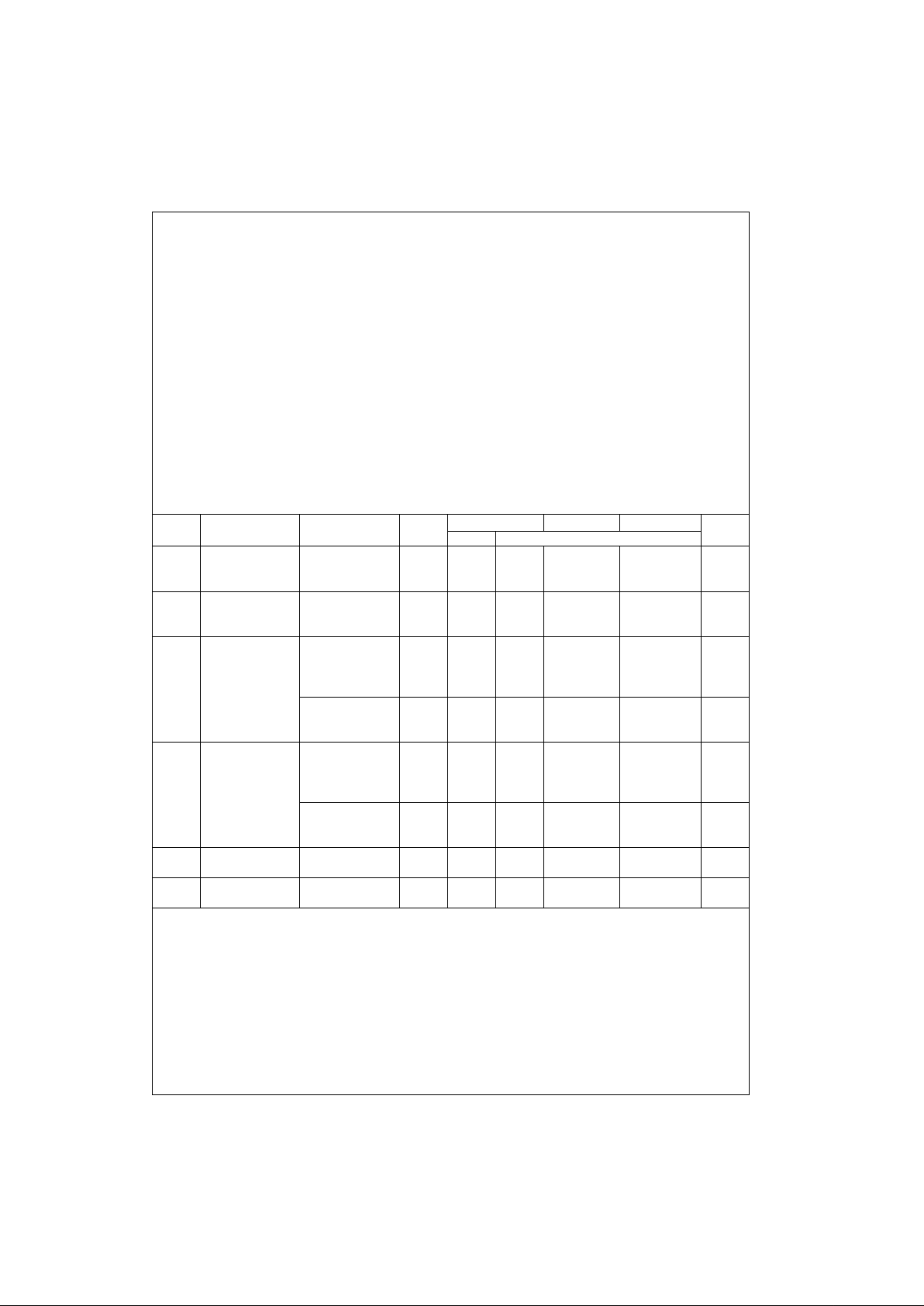

Absolute Maximum Ratings(Note 1)

(Note 2)

Recommended Operating

Conditions

Note 1: Absolute Maximum Ra tings are those valu es beyond w hich dam-

age to the device may occur.

Note 2: Unless otherwise specified all voltages are referenced to ground.

Note 3: Power Dissipation te mperature d erating — pl astic “N” pa ckage: −

12 mW/°C from 65°C to 85°C

DC Electrical Characteristics (Note 4)

Note 4: For a powe r supply o f 5V ±10% the worst case output voltages (VOH, and VOL) occur for HC at 4.5V. Thus the 4. 5V valu es shou ld be u sed when

designing with this supply. Worst case V

IH

and VIL occur at VCC=5.5V and 4.5V respectively. (The VIH value at 5.5V is 3. 85V.) The worst case leak ag e cur ren t

(I

IN

, ICC, and IOZ) occur for CMOS at the higher voltage and s o t he 6.0V values should be used.

Supply Voltage (VCC) −0.5 to +7.0V

DC Input Voltage (V

IN

) −1.5 to VCC+1.5V

DC Output Voltage (V

OUT

) −0.5 to VCC+0.5V

Clamp Diode Current (I

IK

, IOK) ±20 mA

DC Output Current, per pin (I

OUT

) ±25 mA

DC V

CC

or GND Current, per pin (ICC) ±50 mA

Storage Temperature Range (T

STG

) −65°C to +150°C

Power Dissipation (P

D

)

(Note 3) 600 mW

S.O. Package only 500 mW

Lead Temperature (T

L

)

(Soldering 10 seconds) 260°C

Min Max Units

Supply Voltage (V

CC

)26V

DC Input or Output Voltage 0 V

CC

V

(V

IN

, V

OUT

)

Operating Temperature Range (T

A

) −40 +85 °C

Input Rise or Fall Times

(t

r

, tf) V

CC

= 2.0V 1000 ns

V

CC

= 4.5V 500 ns

V

CC

= 6.0V 400 ns

Symbol Parameter Conditions

V

CC

TA= 25°CTA = −40 to 85°CTA = −55 to 125°C

Units

Typ Guaranteed Limits

V

IH

Minimum HIGH Level 2.0V 1.5 1.5 1.5 V

Input Voltage 4.5V 3.15 3.15 3.15 V

6.0V 4.2 4.2 4.2 V

V

IL

Maximum LOW Level 2.0V 0.5 0.5 0.5 V

Input Voltage 4.5V 1.35 1.35 1.35 V

6.0V 1.8 1.8 1.8 V

V

OH

Minimum HIGH Level V

IN

= VIH or V

IL

Output Voltage |I

OUT

| ≤ 20 µA 2.0V 2.0 1.9 1.9 1.9 V

4.5V 4.5 4.4 4.4 4.4 V

6.0V 6.0 5.9 5.9 5.9 V

V

IN

= VIH or V

IL

|I

OUT

| ≤ 4.0 mA 4.5V 4.2 3.98 3.84 3.7 V

|I

OUT

| ≤ 5.2 mA 6.0V 5.7 5.48 5.34 5.2 V

V

OL

Maximum LOW Level V

IN

= VIH or V

IL

Output Voltage |I

OUT

| ≤ 20 µA 2.0V 0 0.1 0.1 0.1 V

4.5V 0 0.1 0.1 0.1 V

6.0V 0 0.1 0.1 0.1 V

V

IN

= VIH or V

IL

|I

OUT

| ≤ 4.0 mA 4.5V 0.2 0.26 0.33 0.4 V

|I

OUT

| ≤ 5.2 mA 6.0V 0.2 0.26 0.33 0.4 V

I

IN

Maximum Input V

IN

= VCC or GND 6 .0V ±0.1 ±1.0 ±1.0 µA

Current

I

CC

Maximum Quiescent V

IN

= VCC or GND 6.0V 8.0 80 160 µA

Supply Current I

OUT

= 0 µA

Loading...

Loading...