Fairchild Semiconductor ML4425 Datasheet

www.fairchildsemi.com

ML4425

Sensorless BLDC Motor Controller

Features

• Stand-alone operation

• Motor starts and stops with power to IC

• On-board start sequence: Align ♦ Ramp ♦ Set Speed

• Patented Back-EMF commutation technique provides

jitterless torque for minimum “spin-up” time

• Onboard speed control loop

• PLL used for commutation provides noise immunity from

PWM spikes, compared to noise sensitive zero crossing

technique

• PWM control for maximum efficiency

• Direct FET drive for 12V motors; drives high voltage

motors with IC buffers

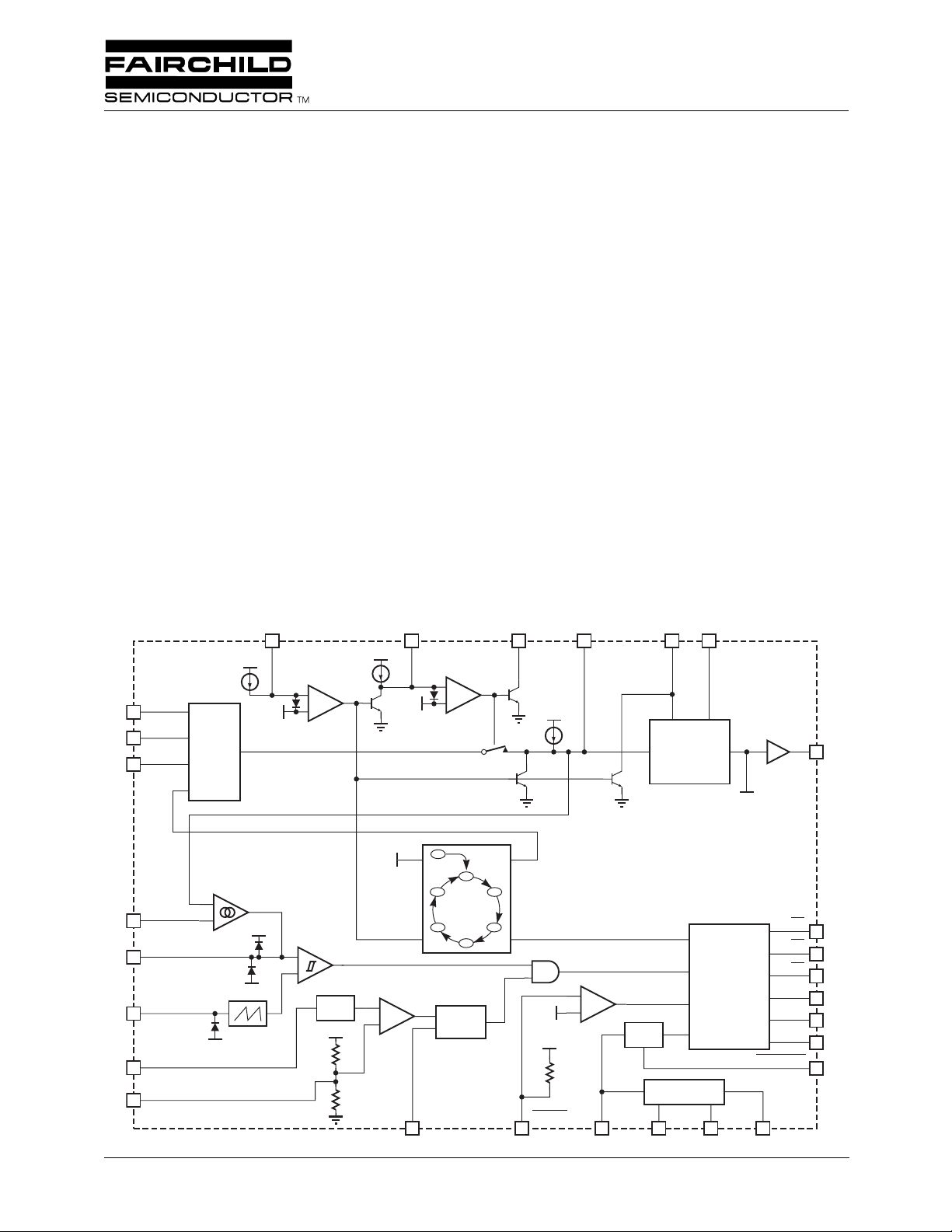

Block Diagram

17

C

DD

1.5V

AT

750nA

–

+

V

750nA

FB A

22

FB B

23

FB C

24

BACK

EMF

SAMPLER

19

V

DD

C

RT

–

1.5V

+

General Description

The ML4425 PWM motor controller provides all of the

functions necessary for starting and controlling the speed of

delta or wye wound Brushless DC (BLDC) motors without

Hall Effect sensors. Back EMF voltage is sensed from the

motor windings to determine the proper commutation phase

sequence using a PLL. This patented sensing technique will

commutate a wide range of 3-Phase BLDC motors and is

insensitive to PWM noise and motor snubbing circuitry.

The ML4425 limits the motor current using a constant offtime PWM control loop. The velocity loop is controlled with

an onboard amplifier. The ML4425 has circuitry to ensure

that there is no shoot-through in directly driven external

power MOSFETs.

The timing of the start-up sequence is determined by the

selection of three timing capacitors. This allows optimization

for a wide range of motors and loads.

21

C

500nA

RR

20

SPEED

FB

V

DD

15 16

C

VCO

VOLTAGE

CONTROLLED

OSCILLATOR

R

VCO

VCO/TACH

13

8

SPEED SET

5

SPEED COMP

C

T

6

I

SENSE

1

I

LIMIT

12

1.7V

VCO

OUT

VCO

OUT

+

–

3.9V

–

+

1.7V

–

+

8kΩ

20kHz

16kΩ

V

× 5

REF

R

A

I

LIMIT

B

COMMUTATION

STATE MACHINE

C

D

GATING

LOGIC

&

OUTPUT

DRIVERS

REF

25

1.4V

V

DD

BRAKE

4kΩ

–

+

UVLO

REFERENCE

V

DD

14

GND27R

28

HA

HB

HC

LA

LB

LC

UV FAULT

V

REF

7

2

3

4

9

10

11

18

F

E

1-SHOT

C

IOS

26

REV. 1.0.2 7/2/01

ML4425 PRODUCT SPECIFICATION

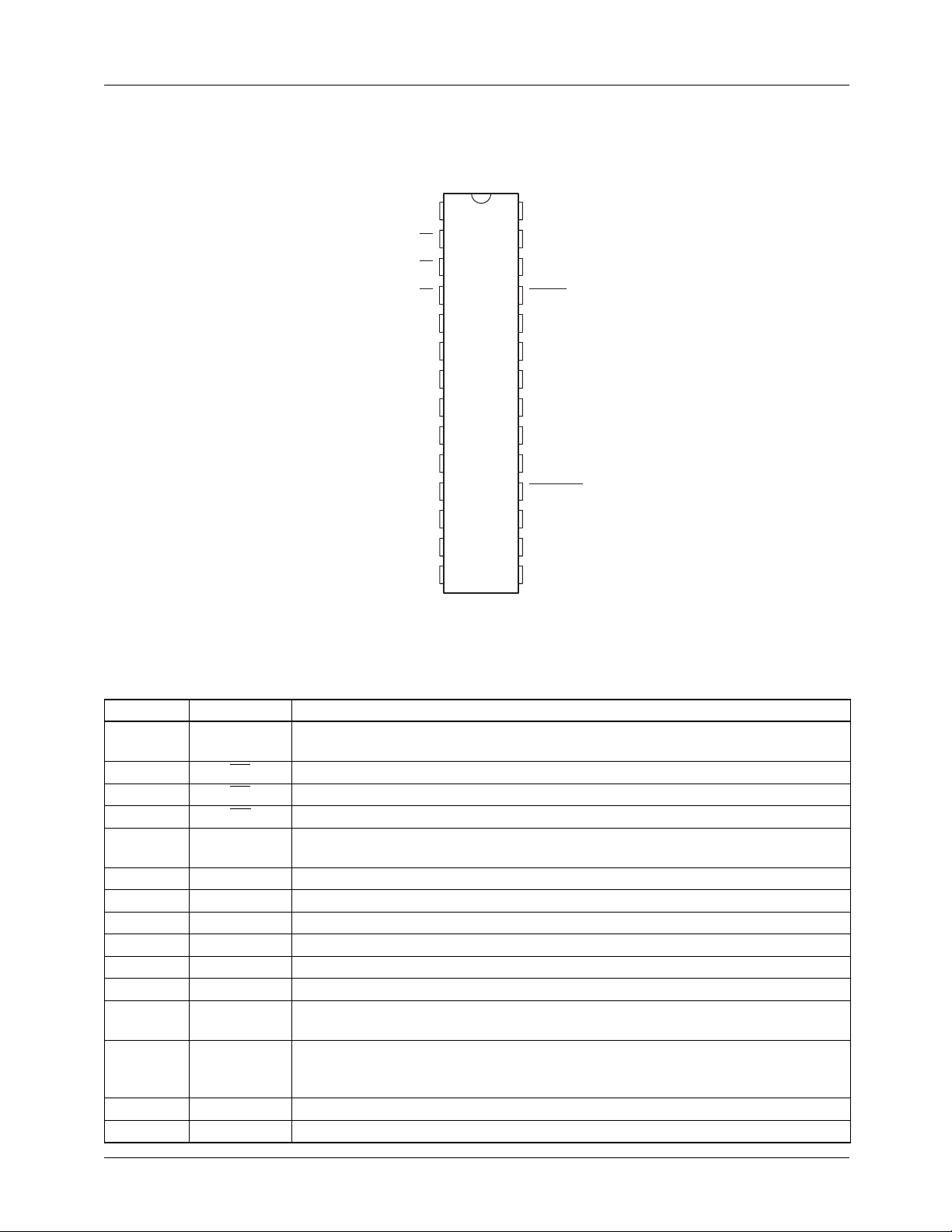

Pin Configuration

28-Pin Narrow PDIP (P28N)

I

SENSE

SPEED COMP

V

SPEED SET

I

LIMIT

VCO/TACH

ML4425

28-Pin SOIC (S28)

1

HA

2

HB

3

HC

4

5

C

6

T

7

REF

8

LA

9

LB

10

LC

11

12

13

V

14

DD

TOP VIEW

GND

28

R

27

REF

C

26

IOS

BRAKE

25

FB C

24

FB B

23

FB A

22

C

21

RR

SPEED FB

20

C

19

RT

UV FAULT

18

C

17

AT

R

16

VCO

C

15

VCO

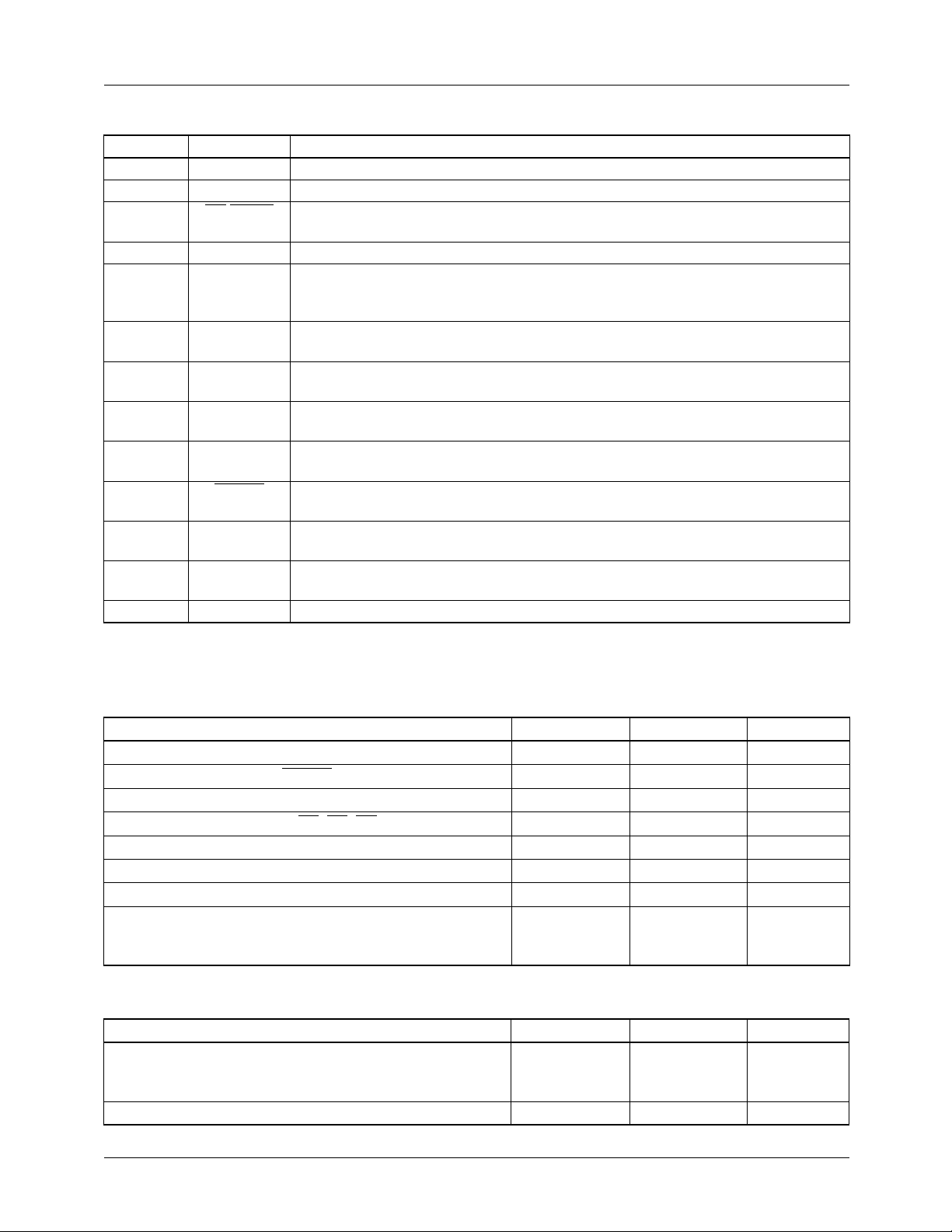

Pin Description

Pin Name Function

1I

SENSE

2HA

3HBActive low output driver for the phase B high-side switch.

4HCActive low output driver for the phase C high-side switch.

5 SPEED

COMP

6C

V

T

REF

8 SPEED SET Speed loop input which ranges from 0 (stopped) to V

9 LA Active high output driver for the phase A low-side switch.

10 LB Active high output driver for the phase B low-side switch.

11 LC Active high output driver for the phase C low-side switch.

12 I

LIMIT

13 VCO/TACH This TTL level output corresponds to the signal used to clock the commutation state

14 V

15 C

DD

VCO

Motor current sense input. When I

LB, and LC are shut off for a fixed time determined by C

exceeds 0.2 ↔ I

SENSE

the output drivers LA,

LIMIT,

.

IOS

Active low output driver for the phase A high-side switch.

Speed control loop compensation is set by a series resistor and capacitor from

SPEED COMP to GND.

A capacitor from C

to GND sets the PWM oscillator frequency.

T

6.9V reference voltage output.

(maximum speed).

REF

Voltage on this pin sets the I

threshold voltage at 0.2 ↔ I

SENSE

, leaving this pin

LIMIT

unconnected selects an internally set threshold.

machine. The output frequency is proportional to the motor speed when the backEMF sensing loop is locked onto the rotor position.

12V power supply input.

A capacitor to GND sets the voltage-to-frequency ratio of the VCO.

2

REV. 1.0.2 7/2/01

)

PRODUCT SPECIFICATION ML4425

Pin Description

(continued)

Pin Name Function

16 R

17 C

18 UV

FAULT This output goes low when V

VCO

AT

An resistor to GND sets up a current proportional to the input voltage of the VCO.

A capacitor to GND sets the time that the controller stays in the align mode.

drops below the UVLO threshold, and indicates that

DD

all output drivers have been disabled.

19 C

RT

A capacitor to GND sets the time that the controller stays in the ramp mode.

20 SPEED FB Output of the back-EMF sampling circuit and input to the VCO. An RC network

connected to SPEED FB sets the compensation for the PLL loop formed by the

back-EMF sampling circuit, the VCO, and the commutation state machine.

21 C

RR

A capacitor to between C

and SPEED FB sets the ramp rate (acceleration) of the

RR

motor when the controller is in ramp mode.

22 FB A The motor feedback voltage from phase A is monitored through a resistor divider for

back-EMF sensing at this pin.

23 FB B The motor feedback voltage from phase B is monitored through a resistor divider for

back-EMF sensing at this pin.

24 FB C The motor feedback voltage from phase C is monitored through a resistor divider for

back-EMF sensing at this pin.

25 BRAKE A logic low input activates motor braking by shutting off the high-side output drivers

and turning on the low-side output drivers.

26 C

27 R

IOS

REF

A capacitor to GND sets the time that the low-side output drivers remain off after

I

exceeds its threshold .

SENSE

An 137k Ω resistor to GND sets a current proportional to V

that is used to set all

REF

the internal bias currents except for the VCO.

28 GND Signal and power ground.

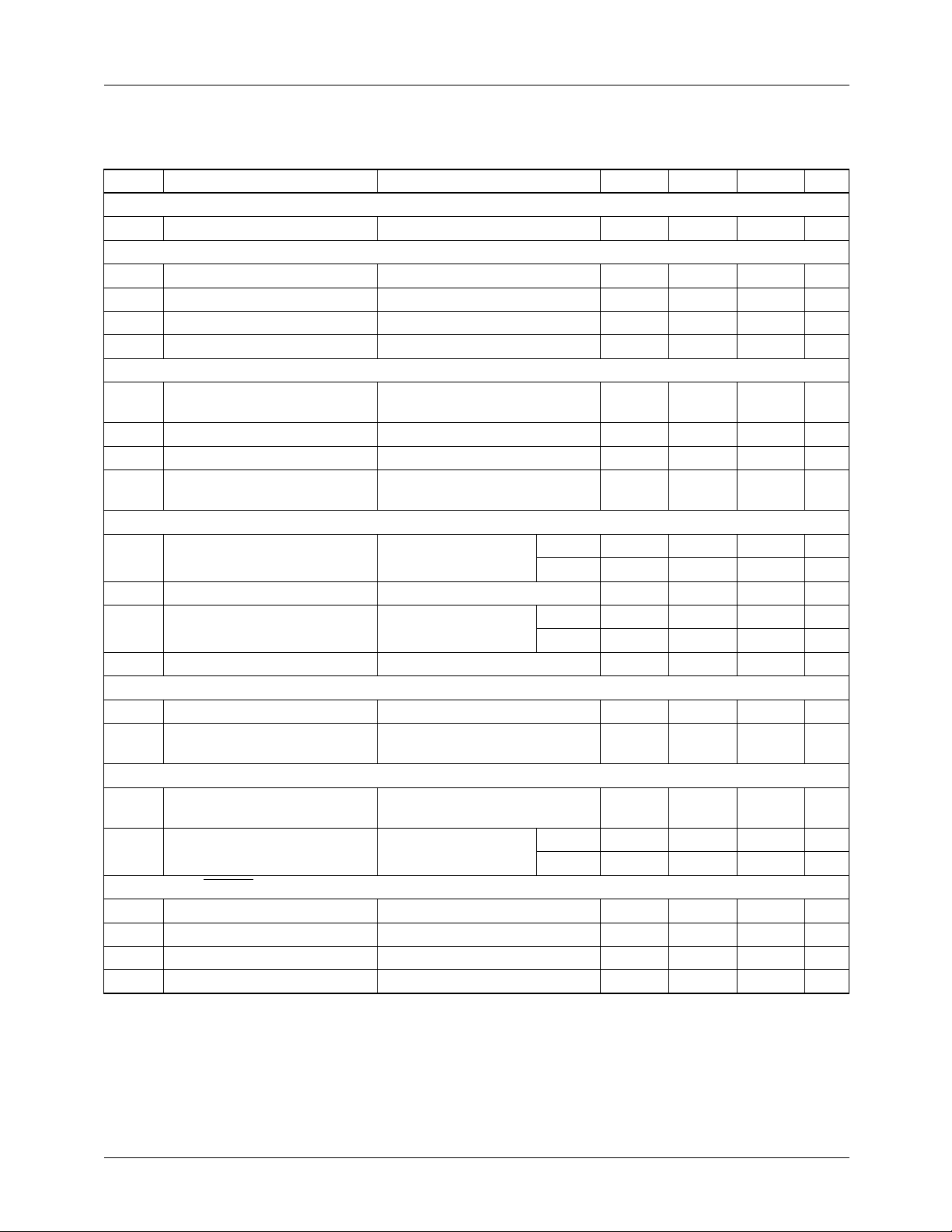

Absolute Maximum Ratings

Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum

ratings are stress ratings only and functional device operation is not implied.

Parameter Min. Max. Units

V

DD

14 V

Logic Inputs (SPEED FB, BRAKE) GND – 0.3 7 V

All Other Inputs and Outputs GND – 0.3 V

Output Current (LA, LB, LC, HA

, HB, HC

+ 0.3 V

DD

±50 mA

Junction Temperature 150 °C

Storage Temperature Range -65 150 °C

Lead Temperature (Soldering 10 sec.) 260 °C

Thermal Resistance ( θ

28-Pin Narrow PDIP

28-Pin SOIC

JA

)

48

75

°C/W

°C/W

Operating Conditions

Parameter Min. Max. Units

Temperature Range

ML4425CX

ML4425IX

V

DD

0

–40

70

85

°C

°C

10.8 13.2 V

REV. 1.0.2 7/2/01

3

) ≤

ML4425 PRODUCT SPECIFICATION

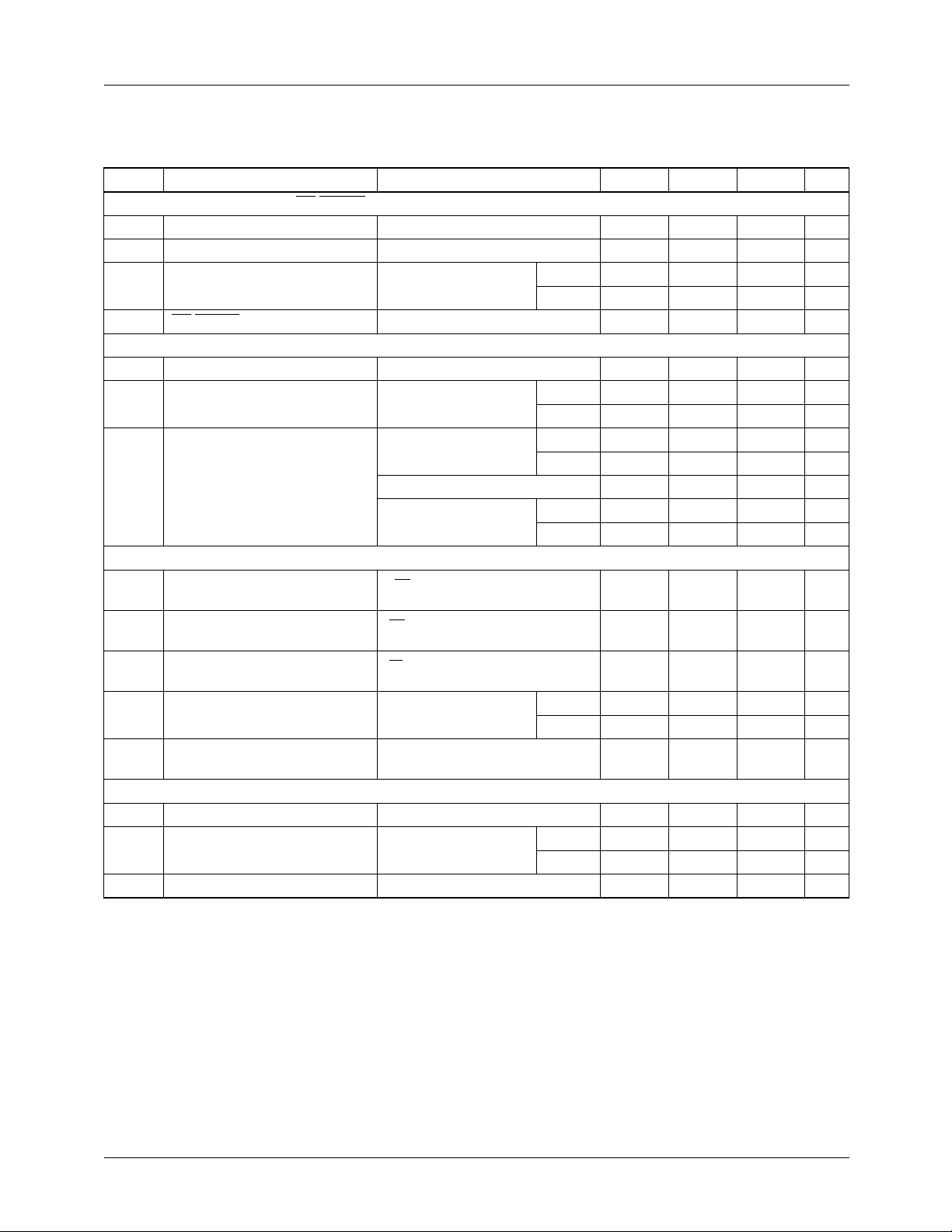

Electrical Characteristics

Unless otherwise specified, V

T

= Operating Temperature Range (Notes 1, 2) .

A

Symbol Parameter Conditions Min. Typ. Max. Units

Reference

V

Total Variation Line, Temp 6.5 6.9 7.5 V

REF

PWM Oscillator

Total Variation C

Ramp Peak 3.9 V

Ramp Valley 1.7 V

Ramp Charging Current µA

Speed Control Loop

SPEED SET Input Voltage

Range

SPEED FB Input Voltage Range 0 V

SPEED COMP Output Current ±5 ±20 µA

SPEED SET Error Amp

Transconductance

Start-up

C

Charging Current C Suffix 0.68 0.98 µA

AT

C

Threshold Voltage 1.4 1.7 V

AT

C

Charging Current C Suffix 0.68 0.98 µA

RT

C

Threshold Voltage 1.4 1.7 V

RT

Voltage Controlled Oscillator

Frequency Range R

Frequency vs. SPEED FB R

Current Limit

I

Gain V(I

SENSE

= 12V ± 10%, R

DD

= 1 Ω , C

SENSE

= 1nF 28 kHz

T

V

SPEED SET

V

SPEED FB

= xV,

= yV

VCO

= 10nF, C

= 100pF, R

IOS

= 137k Ω ,

REF

0V

REF

REF

144 µ

I Suffix 0.5 1.1 µA

I Suffix 0.5 1.1 µA

= 5V, SPEED FB = 6V 1.5 1.85 2.2 kHz

VCO

= 5V, 0.5V ≤ SPEED FB ≤

VCO

300 Hz/V

7V

2.5V 4.5 5.0 5.5 V/V

LIMIT

V

V

Ω

One Shot OFF-Time C

Logic Inputs (BRAKE) (Note 3)

V

V

Input High Voltage 2 V

IH

Input Low Voltage 0.8 V

IL

Input High Current V

I

IH

I

Input Low Current V

IL

4

= 100pF C Suffix 9 18 µs

IOS

I Suffix 9 20 µs

= 2.4V 2.4 mA

IH

= 0.4V 2.9 mA

IL

REV. 1.0.2 7/2/01

PRODUCT SPECIFICATION ML4425

Electrical Characteristics (continued)

Unless otherwise specified, V

TA = Operating Temperature Range (Notes 1, 2).

Symbol Parameter Conditions Min. Typ. Max. Units

Logic Outputs (VCO/TACH, UV FAULT) (Note 3)

VCO/TACH Output High Voltage I

VCO/TACH Output Low Voltage I

UV FAULT Output High Voltage I

UV

FAULT Output Low Voltage I

Back-EMF Sampler

SPEED FB Align Mode Voltage 125 250 mV

SPEED FB Ramp Mode Current C Suffix 500 720 nA

SPEED FB Run Mode Current State A, C

Output Drivers

High Side Driver Output Low

Current

High Side Driver Output High

Voltage

Low Side Driver Output Low

Voltage

Low Side Driver Output High

Voltage

Phase C Cross-conduction

Lockout Threshold

Supply

I

DD

VDD Current 32 50 mA

UVLO Threshold C Suffix 8.8 9.5 10.2 V

UVLO Hysteresis 150 mV

Notes:

1. Limits are guaranteed by 100% testing, sampling, or correlation with worst case test conditions.

2. For explanation of states, see Figure 4 and Table 1.

3. The BRAKE and UV FAULT pins each have an internal 4k Ω resistor to the internal reference.

= 12V ± 10%, R

DD

= 1Ω, C

SENSE

= –100µA 2.2 V

OUT

= 400µA 0.6 V

OUT

= –10µA C Suffix 3.4 4.5 5.4 V

OUT

VCO

= 10nF, C

= 100pF, R

IOS

= 137kΩ,

REF

I Suffix 3.2 5.6 V

= 400µA 0.6 V

OUT

I Suffix 500 750 nA

= 5V,

V

PHB

State A, C

State A, C

V

PHB

V

HX

I

HX

I

LX

V(I

RT

= V

/3

DD

= 5V, V

RT

= 5V,

RT

= 2 ↔ V

DD

/3

= 2 V 0.5 1.2 mA

= –10µ AV

= 1mA 0.2 0.7 V

) = 0V C Suffix VDD – 2.2 V

SENSE

C Suffix 30 90 µA

I Suffix 27 90 µA

= V

PHB

/2 –15 15 µA

DD

C Suffix –90 –30 µA

I Suffix –90 –27 µA

– 1.3 V

CC

I Suffix V

– 2.9 V

DD

V

– 3.0 V

DD

I Suffix 8.6 10.3 V

REV. 1.0.2 7/2/01

5

Loading...

Loading...