Fairchild Semiconductor ML2036IP, ML2036CP Datasheet

www.fairchildsemi.com

ML2036

Serial Input Programmable Sine Wave Generator

with Digital Gain Control

Features

• Programmable output frequency – DC to 50kHz

• Low gain error and total harmonic distortion

• 3-wire SPI compatible serial microprocessor interface

with double buffered data latch

• Fully integrated solution – no external components

required

• Frequency resolution of 1.5Hz (±0.75Hz) with a 12MHz

clock input

• Onboard 3 to 12MHz crystal oscillator

• Clock outputs of 1/2 or 1/8 of the input clock frequency

• Synchronous or asynchronous data loading capability

• Compatible with ML2004 logarithmic gain/attenuator

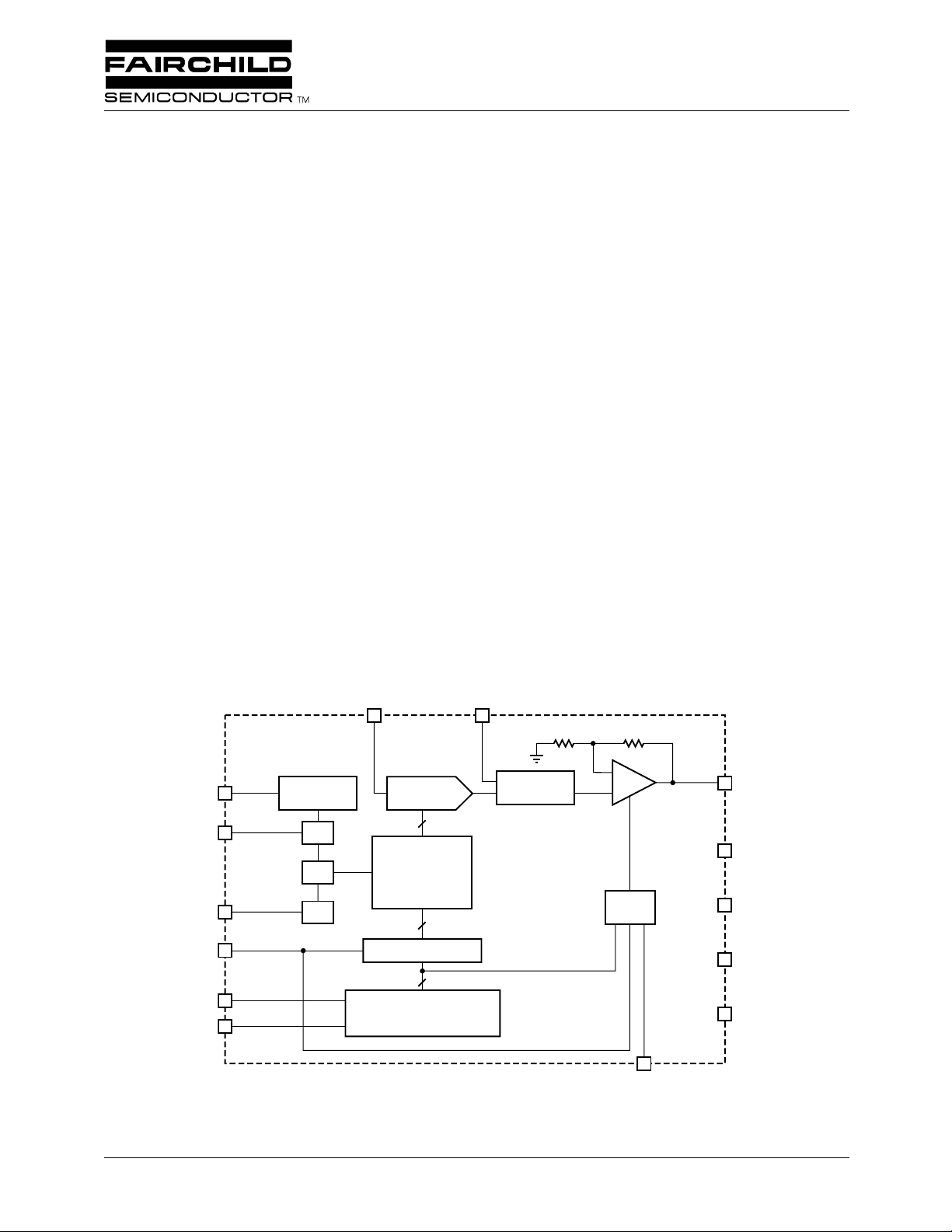

Block Diagram

(Pin configuration shown for 14-Pin PDIP Version)

9

V

REF

General Description

The ML2036 is a monolithic sine wave generator whose

output is programmable from DC to 50kHz. No external

components are required. The frequency of the sinewave

output is derived from either an external crystal or clock

input, providing a stable and accurate frequency reference.

The frequency is programmed by a 16-bit serial data word.

The ML2036 provides for a V

or ±V

/2. Also included with the ML2036 is an inhibit

REF

function which allows the sinewave output to be held at zero

volts after completing the last half cycle of the sine wave in

progress. Two digital clock outputs are provided to drive

other devices with one half or one eighth of the input clock

frequency.

The ML2036 is intended for telecommunications and

modem applications that need low cost and accurate generation of precise test tones, call progress tones, and signaling

tones.

13

GAIN

5kΩ 5kΩ

amplitude of either ±V

OUT

REF

CLK IN

14

CLK OUT 1

3

CLK OUT 2

4

LATI

7

SCK

5

SID

3

CRYSTAL

OSCILLATOR

÷2

÷2

÷2

8-BIT

DAC

8

PHASE

ACCUMULATOR

& 512 POINT

SINE LOOK-UP

TABLE

16

16-BIT DATA LATCH

16

16-BIT SHIFT REGISTER

SMOOTHING

FILTER

-

+

ZERO

DETECT

2

V

OUT

10

V

CC

8

AGND

11

DGND

12

V

SS

1

-INH

P

DN

REV. 1.0.2 7/26/01

ML2036 PRODUCT SPECIFICATION

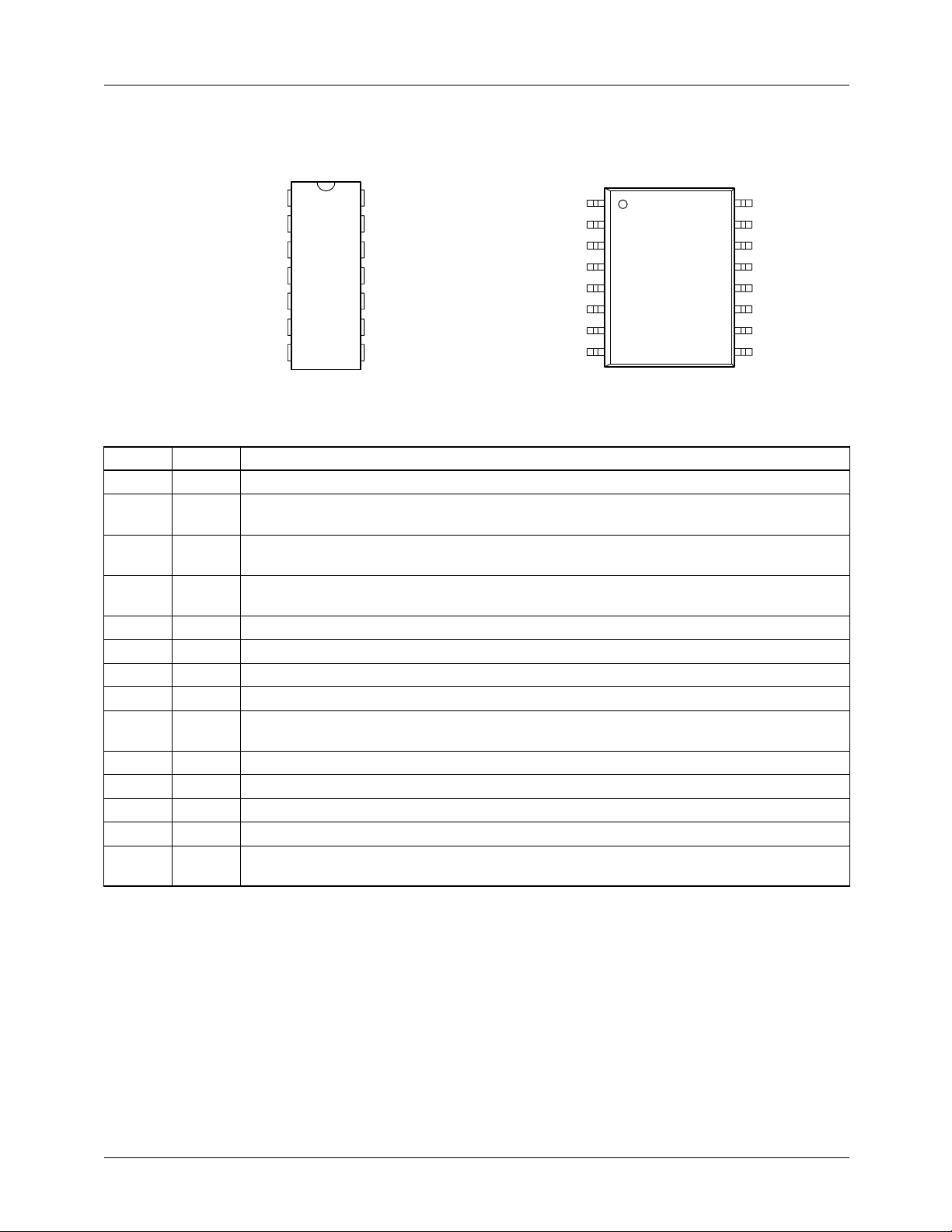

Pin Configuration

1

2

3

4

5

6

7

8

ML2036

TOP VIEW

16

15

14

13

12

11

10

CLK IN

GAIN

NC

DGND

AGND

V

OUT

V

REF

9

V

CC

PDN-INH

CLK OUT 1

CLK OUT 2

Pin Description

ML2036

14-Pin PDIP (P14)

V

SS

SCK

SID

LATI

1

2

3

4

5

6

7

TOP VIEW

14

13

12

11

10

9

8

CLK IN

GAIN

DGND

AGND

V

OUT

V

REF

V

CC

V

PDN-INH

CLK OUT 1

CLK OUT 2

SCK

LATI

(Pin Number in Paranthesis is for SOIC Version)

16-Pin Wide SOIC (S16W)

NC

SS

SID

PIN NAME FUNCTION

1 (2) V

2 (3) P

DN

3 (4) CLK

OUT 1

4 (5) CLK

OUT 2

Negative supply (-5V).

SS

-INH Three level input which controls the inhibit and power down modes. Current source pull-up

to V

.

CC

Digital clock output from the internal clock generator that can drive other devices at f

1

= f

CLK IN

/2.

Digital clock output from the internal clock generator that can drive other devices at f

2

= f

CLK IN

/8.

CLK OUT

CLK OUT

5 (6) SCK Serial clock. Digital input which clocks in serial data on its rising edges.

6 (7) SID Serial input data which programs the frequency of V

OUT

.

7 (8) LATI Digital input which latches serial data into the internal data latch on falling edges.

8 (9) V

9 (10) V

10 (11) V

REF

OUT

Positive supply (5V).

CC

Reference input. The voltage on this pin determines the peak-to-peak swing of V

can be tied to V

CC

.

Analog output.

OUT

. V

11 (12) AGND Analog ground. All analog inputs and outputs are referenced to this point.

12 (13) DGND Digital ground. All digital inputs and outputs are referenced to this point.

13 (15) GAIN Sets V

peak amplitude to V

OUT

REF

or V

/2. Current source pull-down to DGND.

REF

14 (16) CLK IN Clock input. The internal clock can be generated by tying a 3 to 12MHz crystal from this pin

to DGND, or by applying a digital clock signal directly to the pin.

REF

2

REV. 1.0.2 7/26/01

PRODUCT SPECIFICATION ML2036

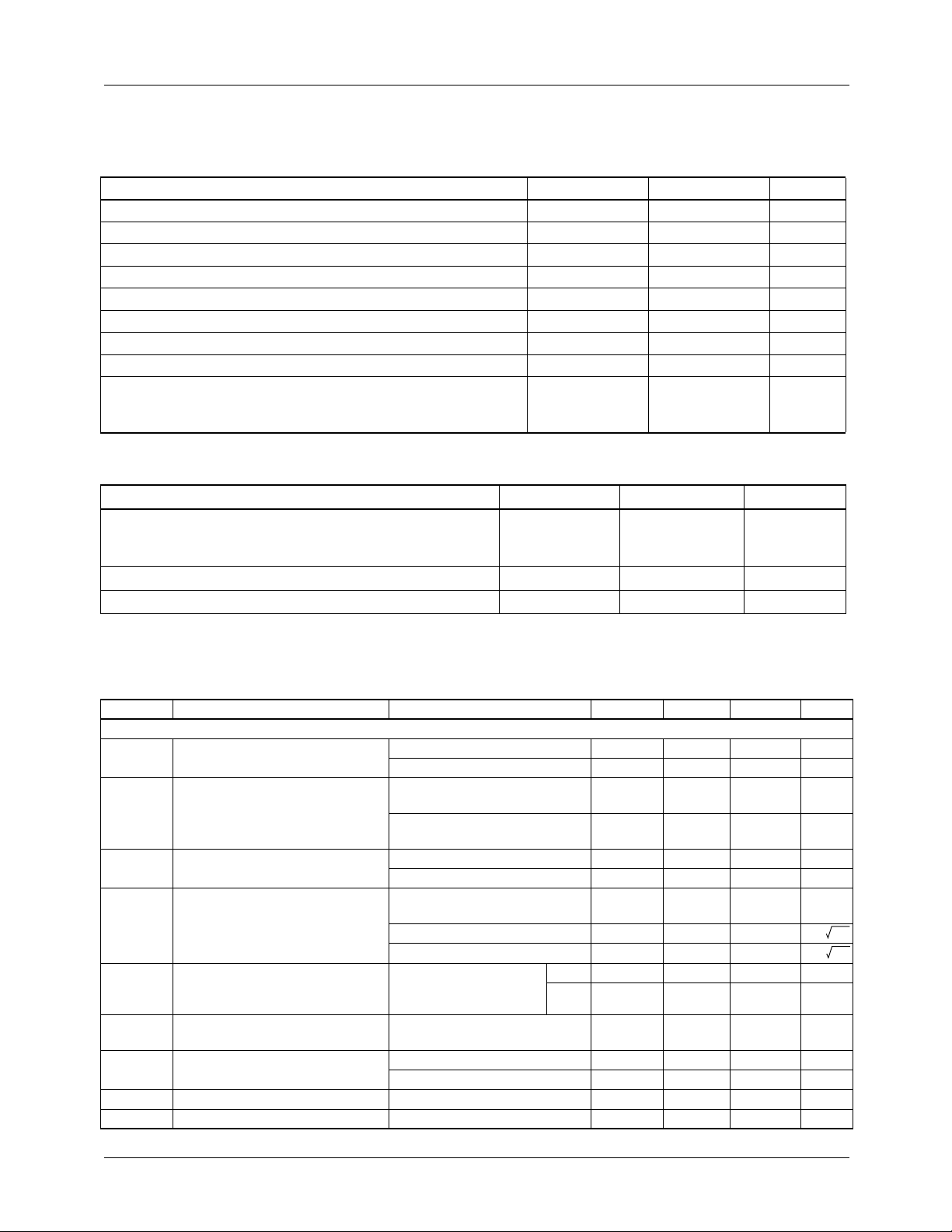

Absolute Maximum Ratings

Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum

ratings are stress ratings only and functional device operation is not implied.

Parameter Min. Max. Units

V

CC

V

SS

V

OUT

V

- 0.3 V

SS

Voltage on any other pin GND - 0.3 V

6.5 V

-6.5 V

+ 0.3 V

CC

+ 0.3 V

CC

Input Current ±25 mA

Junction Temperature 150 °C

Storage Temperature Range –65 150 °C

Lead Temperature (Soldering, 10 sec) 260 °C

Thermal Resistance ( θ

14-Pin PDIP

16-Pin Wide SOIC

)

JA

88

105

°C/W

°C/W

Operating Conditions

Parameter Min. Max. Units

Temperature Range

ML2036CX

ML2036IX

V

Range 4.5 5.5 V

CC

V

Range -4.5 -5.5 V

SS

0

-40

70

85

°C

°C

Electrical Characteristics

Unless otherwise specified, V

C

= 100pF, R

L

= 1k Ω , T

L

Symbol Parameter Conditions Min. Typ. Max. Units

Output

HD Harmonic Distortion (Note 2)

(2nd and 3rd Harmonic)

SND Signal to Noise + Distortion

(Note 2)

V

GN

Gain Error (Note 2) 20Hz < f

ICN Idle Channel Noise Power Down Mode, Cmsg

PSRR Power Supply Rejection Ratio 200mV

V

V

V

OS

P-P

Offset Voltage (Note 3) ±(2.5+

OUT

Peak-to-Peak Output Voltage

(Note 2)

V

Swing GAIN = V

OUT

R

REF

Reference Input Resistance 1 6 M Ω

= 4.5V to 5.5V, V

CC

= Operating Temperature Range (Note 1)

A

= -4.5V to -5.5V, V

SS

20Hz to 5kHz -45 dB

5kHz to 50kHz -40 dB

200Hz to 3.4kHz,

f

BW = 200Hz to 4kHz

OUT

20Hz to 50kHz,

BW = 20 Hz to 150kHz

f

OUT

OUT

5kHz < f

OUT

Weighted

Power Down Mode, 1kHz 50 nV/ Hz

Inhibit Mode, 1kHz 500 nV/ Hz

, 0 - 10kHz

P-P

Sine, Measured on

V

OUT

GAIN = V

CC

GAIN = DGND ±V

CC

= 2.5V to V

REF

, CLK IN = 12.352MHz,

CC

-45 dB

-40 dB

< 5kHz ±0.15 dB

< 50kHz ±0.3 dB

-20 0 dBrnc

V

CC

V

SS

±V

REF

REF

V

+1.5 V

SS

-40 dB

-40 dB

V

)/100

P-P

/2 V

-1.5 V

CC

V

V

REV. 1.0.2 7/26/01

3

≤

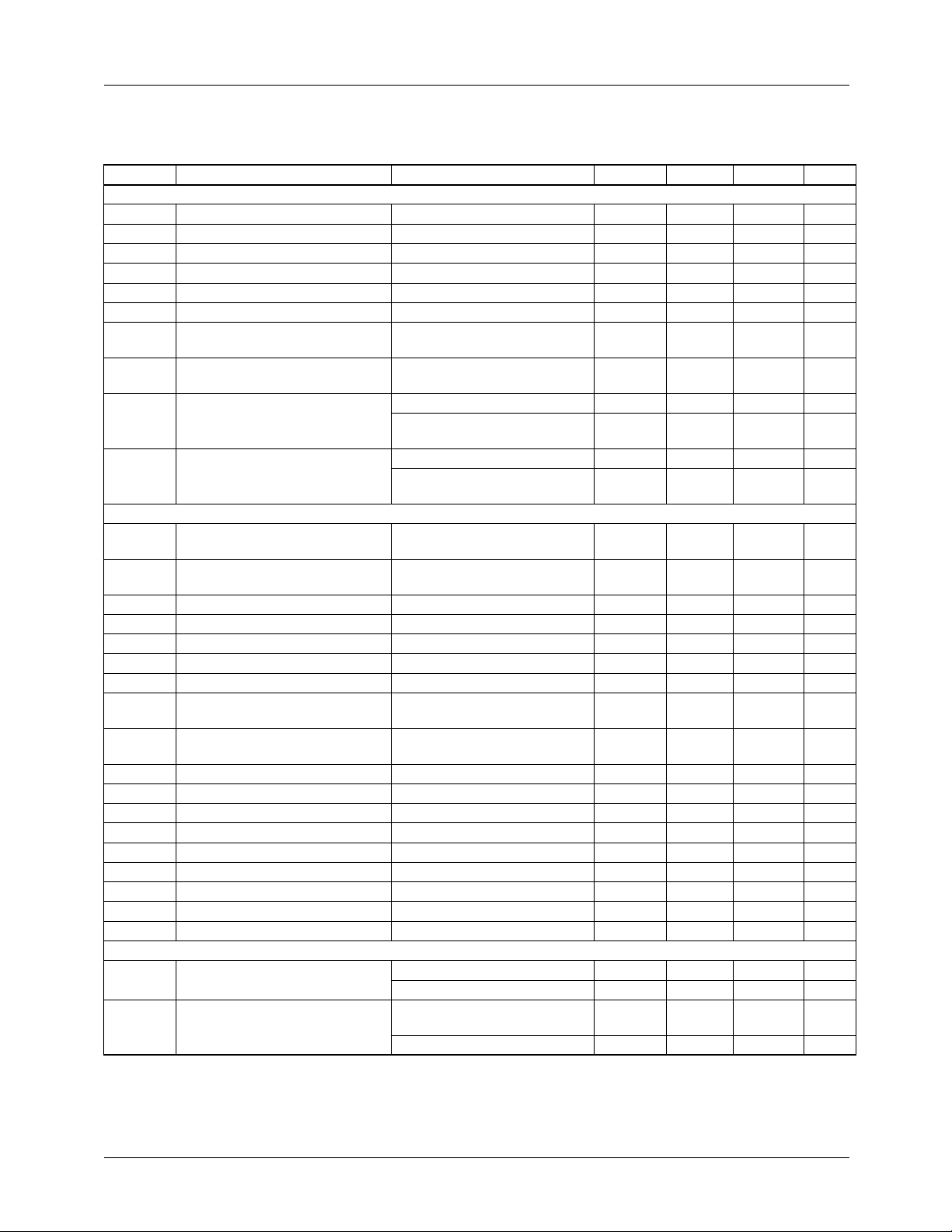

ML2036 PRODUCT SPECIFICATION

Electrical Characteristics (continued)

Unless otherwise specified, VCC = 4.5V to 5.5V, VSS = -4.5V to -5.5V, V

CL = 100pF, RL = 1kΩ, TA = Operating Temperature Range (Note 1)

Symbol Parameter Conditions Min. Typ. Max. Units

Oscillator

V

CLK CLK IN Input Low Voltage 1.5 V

IL

V

CLK CLK IN Input High Voltage 3.5 V

IH

I

CLK CLK IN Input Low Current -250 µA

IL

I

CLK CLK IN Input High Current 250 µA

IH

C

CLK CLK IN Input Capacitance 12 pF

IN

t

CKI

CLK IN On/Off Period t

CLK OUT 1/CLK IN Frequency

= t

= 10ns, 2.5V Midpoint 30 ns

R

F

See Figure 2 0.49 0.51

Ratio

CLK OUT 2/CLK IN Frequency

See Figure 2 0.122 0.128

Ratio

t

1R

, t

CLK OUT 1, CLK OUT 2 Rise

2R

Time

C

= 40pF, 10% to 90% 20 ns

L

C

= 100pF, 0.8V to 2.0V

L

Transition

, t

t

1F

CLK OUT 1, CLK OUT 2 Fall

2F

Time

C

= 40pF, 90% to 10% 20 ns

L

C

= 100pF, 2.0V to 0.8V

L

Transition

Logic

V

IL

Input Low Voltage (LATI, SCK,

SID, GAIN)

V

IH

Input High Voltage (LATI, SCK,

SID, GAIN)

V

I1

V

I2

V

I3

I

-P

IL

I

-GAIN GAIN Input High Current GAIN = V

IH

I

IL

Input Low Voltage - P

Inhibit Stage Voltage - P

Input High Voltage - P

P

DN

-INH Input Low Current P

DN

Input Low Current (LATI, SCK,

-INH -0.5 0.8 V

DN

-INH V

DN

-INH 2.0 V

DN

-INH = 0V -70 -20 -5 µA

DN

CC

VIN = 0V -1 µA

SID, GAIN)

I

IH

Input High Current (LATI, SCK,

VIN = V

CC

SID, GAIN)

C

V

OL

V

OH

t

SCK

t

DS

t

DH

t

LPW

t

LH

t

LS

IN

Input Capacitance 5 pF

Output Low Voltage IOL = -2mA 0.4 V

Output High Voltage IOH = 2mA 4.0 V

Serial Clock On/Off Period 100 ns

SID Data Setup Time 50 ns

SID Data Hold Time 50 ns

LATI Pulse Width 50 ns

LATI Hold Time 50 ns

LATI Setup Time 50 ns

Supply

I

CC

VCC Current No Load, VCC = V

No Load, Power Down Mode 2 mA

I

SS

VSS Current No Load, VCC = V

5.5V, V

= -5.5V

SS

No Load, Power Down Mode -100 µA

Notes:

1. Limits are guaranteed by 100% testing, sampling, or correlation with worst case test conditions.

2. Maximum peak-to-peak voltage for the output sine wave is: V

the maximum output voltage swing is 2.5V

3. Offset voltage is a function of the peak-to-peak output voltage. For example, if V

P-P

.

OUT(P-P)

= 2.5V to VCC, CLK IN = 12.352MHz,

REF

20 ns

20 ns

0.8 V

2.0 V

+ 0.5 V

SS

5 20 70 µA

1µA

= 5.5V 5.5 mA

REF

=

REF

(125kV x Hz)/f

OUT

OUT(P-P)

. For example, at 50kHz,

= 2.5V, V

-3.5 mA

= ±50mV max.

OS

4

REV. 1.0.2 7/26/01

Loading...

Loading...