Fairchild Semiconductor KSB1151 Datasheet

Feature

• Low Collector-Emitter Saturation Voltage

• Large Collector Current

• High Power Dissipation : P

• Complement to KSD 1691

=1.3W (Ta=25°C)

C

KSB1151

KSB1151

1

TO-126

1. Emitter 2.Collector 3.Base

PNP Epitaxial Silicon Transistor

Absolute Maximum Ratings

Symbol Parameter Value Units

V

CBO

V

CEO

V

EBO

I

C

I

CP

I

B

P

C

Collector-Base Voltage - 60 V

Collector-Emitter Voltage - 60 V

Emitter-Base Voltage - 7 V

Collector Current (DC) - 5 A

*Collector Current (Pulse) - 8 A

Base Current - 1 A

Collector Dissipation (Ta=25°C) 1.3 W

Collector Dissipation (T

T

J

T

STG

* PW≤10ms, Duty Cycle≤50%

Junction Temperature 150 °C

Storage Temperature - 55 ~ 150 °C

Electrical Characteristics

Symbol Parameter Test Condition Min. Typ. Max. Units

I

CBO

I

EBO

h

FE1

h

FE2

h

FE3

V

CE

V

BE

t

ON

t

STG

t

F

* Pulse test: PW≤350µs, Duty Cycle≤2% Pulsed

Collector Cut-off Current V

Emitter Cut-off Current V

* DC Current Gain V

(sat) * Collector-Emitter Saturation Voltage IC = - 2A, IB = - 0.2A - 0.14 - 0.3 V

(sat) * Base-Em itter Sat uration Voltage IC = - 2A, IB = - 0.2A - 0.9 - 1.2 V

Turn On Time V

Storage Time 0.78 2.5 µs

Fall Time 0.18 1 µs

TC=25°C unless otherwise noted

=25°C) 20 W

C

TC=25°C unless otherwise noted

= - 50V, IE = 0 - 10 µA

CB

= - 7V, IC = 0 - 10 µA

EB

= - 1V, IC = - 0.1A

CE

= - 1V, IC = - 2A

V

CE

= - 2V, IC = - 5A

V

CE

= - 10V, IC = - 2A

CC

I

= - IB2 =0.2A

B1

60

100

50

200 400

0.15 1 µs

RL = 5Ω

hFE Classification

Classification O Y G

h

FE2

©2003 Fairchild Semiconductor Corporation Rev. B, May 2003

100 ~ 200 160 ~ 320 200 ~ 400

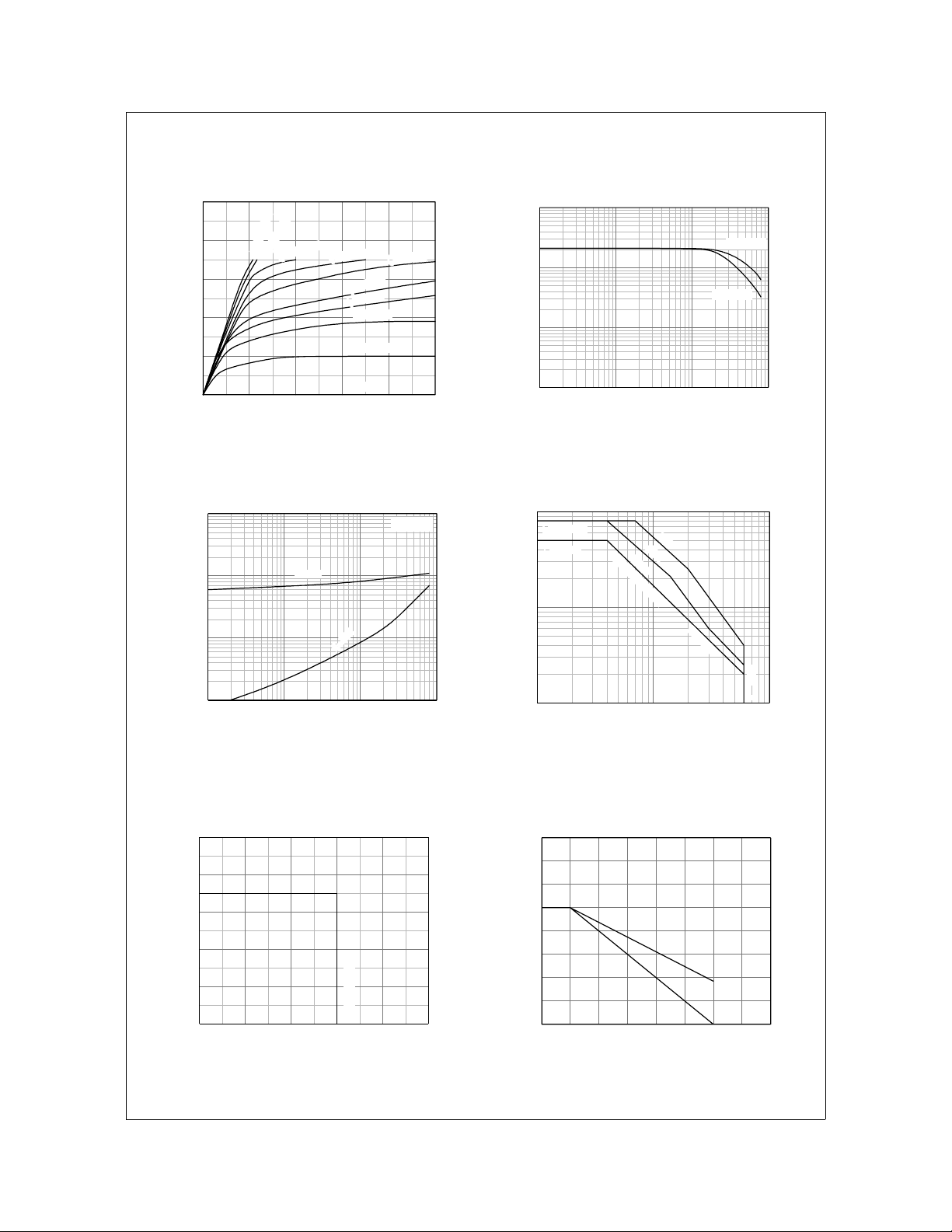

Typical Characteristics

KSB1151

[A], COLLECTOR CURRENT

C

I

(sat)[V], SATURATION VOLTAGE

CE

(sat), V

BE

V

= -150mA

B

= -100mA

I

B

= -80mA

I

B

= -40mA

I

B

= -30mA

I

B

IB = -20mA

IB = -10mA

IB = 0

= -60mA

I

B

-1000

-100

-10

, DC CURRENT GAIN

FE

h

-1

-0.01 -0.1 -1 -10

IC[A], COLLECTOR CURRENT

-10

-8

-6

-4

-2

-0

= -200mA

B

I

I

-0.4 -0.8 -1.2 -1.6 -2.0

VCE[V], COLLECTOR-EMITTER VOLTAGE

Figure 1. Static Characteristic Figure 2. DC current Gain

-0.01

VBE(sat)

IC = 10 I

B

-10

-1

-0.1

-0.1 -1 -10

(sat)

CE

V

IC[A], COLLECTOR CURRENT

-10

IC(Pulse)MAX

IC(DC)MAX

-1

[A], COLLECTOR CURRENT

C

I

-0.1

-1 -10 -100

Dissipation Limited

200mS

VCE[V], COLLECTOR-EMITTER VOLTAGE

10mS

VCE = -2V

VCE = -1V

2mS

s/b Limited

(MAX)

CEO

V

Figure 3. Collector-Emitter Saturation Voltage

Base-Emitter Saturation Voltage

-10

-8

-6

-4

-2

[A], COLLECTOR CURRENT

C

I

-0

-20 -40 -60 -80 -100

VCE[V], COLLECTOR-EMITTER VOLTAGE

Figure 5. Reverse Bias Safe Operating Area Figure 6. Derating Curve of Safe Operating Areas

©2003 Fairchild Semiconductor Corporation

Figure 4. Forward Bias Operating Area

(SUS)

CEO

V

[%], Ic DERATING

T

d

160

140

120

100

80

60

40

20

0

0

25 50 75 100 125 150 175 200

TC[oC], CASE TEMPERATURE

s/b LIMITED

DISSIPATION LIMITED

Rev. B, May 2003

Loading...

Loading...