Fairchild Semiconductor FIN1001 Datasheet

December 2001

Revised January 2002

FIN1001

3.3V LVDS 1-Bit High Speed Differential Driver

FIN1001 3.3V LVDS 1-Bit High Speed Differential Driver

General Description

This single driver is designed for high speed interconnects

utilizing Low Voltage Differential Signaling (LVDS) technology. The driver translates LVTTL signal levels to LVDS levels with a typical differen tial o utput swin g of 350 mV w hich

provides low EMI at ultra low power dissipation even at

high frequencies. Th is device is ideal for hi gh spe ed tran sfer of clock or data.

The FIN1001 can be paired with its companion receiver,

the FIN1002, or with any other LVDS receiver.

Features

■ Greater than 600Mbs data rate

■ 3.3V power supply operation

■ 0.5ns maximum differential pulse skew

■ 1.5ns maximum propagation delay

■ Low power dissipation

■ Power-Off protection

■ Meets or exceeds the TIA/EIA-644 LVDS standard

■ Flow-through pinout simpli f ies PCB layout

■ 5-Lead SOT23 package saves space

Ordering Code:

Order Number Package Number Package Description

FIN1001M5 MA05B 5-Lead SOT23, JEDEC MO-178, 1.6mm [250 Units on Tape and Reel]

FIN1001M5X MA05B 5-Lead SOT23, JEDEC MO-178, 1.6mm [3000 Units on Tape and Reel]

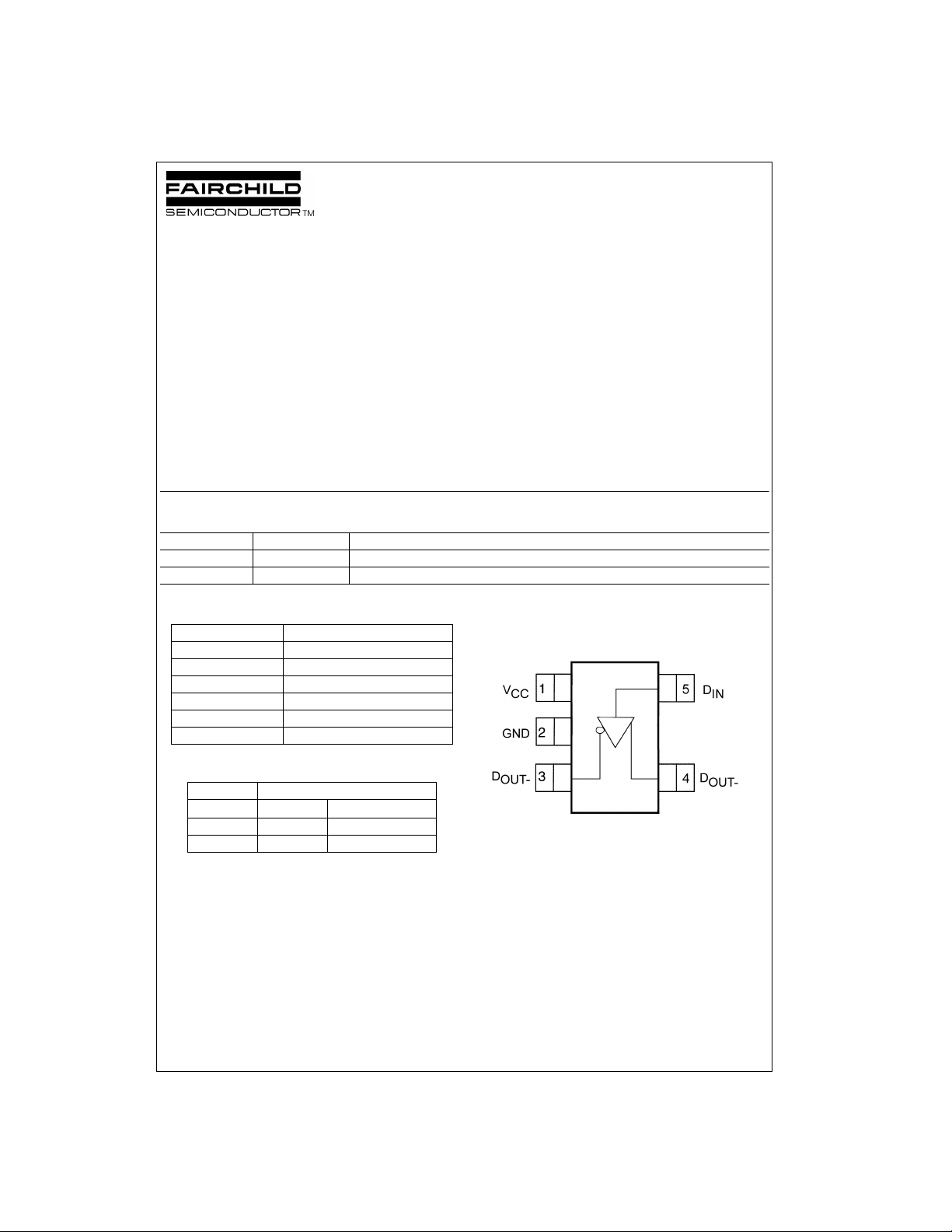

Pin Descriptions

Pin Name Description

D

IN

D

OUT+

D

OUT−

V

CC

GND Ground

NC No Connect

LVTTL Data Input

Non-inverting LVDS Driver Output

Inverting LVDS Driver Output

Power Supply

Connection Diagram

Pin Assignment for SOT23

Function Table

Input Outputs

D

IN

LL H

H = HIGH Logic Le v el L = LOW Logic Level

HH L

D

OUT+

D

OUT−

(Top View)

© 2002 Fairchild Semiconductor Corporation DS500721 www.fairchildsemi.com

Absolute Maximum Ratings(Note 1) Recommended Operating

Supply Voltage ( VCC) −0.5V to +4.6V

DC Input Voltage (D

FIN1001

DC Output Voltage (D

Driver Short Circuit Current (I

Storage Temperature Range (T

Max Junction Temperature (T

Lead Temperature (T

) −0.5V to +6V

IN

) − 0.5V to +4.6V

L

OUT

)

) Continuous

OSD

) −65°C to +150°C

STG

)150°C

J

(Soldering, 10 seconds) 260

ESD (Human Body Model)

ESD (Machine Model)

≥ 7500V

≥ 500V

Conditions

Supply Voltage (V

Input Voltage (V

Operating Temperature (TA) −40°C to +85°C

Note 1: The “Absolute Maximum Ratings”: are those values beyond which

damage to the device may occur. The databook specifications should be

°C

met, without exception, to ensure that the system design is reliable over its

power supply, temperatur e and output/input loading va riables. Fairchild

does not recommend operation of circu it s o ut s ide databook specific ation.

) 3.0V to 3.6V

CC

) 0 to V

IN

DC Electrical Characteristics

Over supply voltage and operating temperature ranges, unless otherwise specified

Symbol Parameter Test Conditions

V

OD

∆V

V

OS

∆V

I

OFF

I

OS

V

IH

V

IL

I

IN

I

I(OFF)

V

IK

I

CC

C

IN

C

OUT

Note 2: All typical values are at TA = 25°C and with VCC = 3.3V .

Output Differential Voltage

VOD Magnitude Change from

OD

Differential LOW-to-HIGH

Offset Voltage 1.125 1.25 1.375 V

Offset Magnitude Change from

OS

Differential LOW-to-HIGH

Power-Off Output Current VCC = 0V, V

Short Circuit Output Current V

Input HIGH Voltage 2.0 V

Input LOW Voltage GND 0.8 V

Input Current VIN = 0V or V

Power-Off Input Current VCC = 0V, VIN = 0V or 3.6V ±20 µA

Input Clamp Voltage IIK = −18 mA −1.5 −0.8 V

Power Supply Current No Load, VIN = 0V or V

Input Capacitance VCC = 3.3V 3.2 pF

Output Capacitance VCC = 0V 3.3 pF

RL = 100 Ω, See Figure 1

= 0V or 3.6V ±20 µA

OUT

= 0V −5.5 −8

OUT

VOD = 0V ±4 ±8

CC

R

= 100 Ω, VIN = 0V or V

L

CC

CC

Min Typ Max

(Note 2)

250 350 450 mV

4.5 8

6.5 10

Units

25 mV

25 mV

mA

CC

±20 µA

mA

CC

V

AC Electrical Characteristics

Over supply voltage and operating temperature ranges, unless otherwise specified

Symbol Parameter Test Conditions

t

PLHD

t

PHLD

t

TLHD

t

THLD

t

SK(P)

t

SK(PP)

Note 3: All typical values are at TA = 25°C and with VCC = 3.3V .

Note 4: t

(either LOW-to-HI GH or HIGH-to-LOW) w hen both devices operate with the same supply voltage, same te m perature, and have id ent ic al test circuits.

Differential Propagation Delay

LOW-to-HIGH

Differential Propagation Delay

HIGH-to-LOW RL = 100 Ω, CL = 10pF,

Differential Output Rise Time (20% to 80%) See Figure 2 and Figure 3 0.4 0.5 1.0 ns

Differential Output Fall Time (80% to 20%) 0.4 0.5 1.0 ns

Pulse Skew |t

Part-to-Part Skew (Note 4) 1.0 ns

is the magnitude of t he difference in propagation delay tim es between any spec ified terminals of t w o devices switching in the sam e di re c ti on

SK(PP)

- t

| 0.05 0.5 ns

PLH

PHL

www.fairchildsemi.com 2

Min Typ Max

(Note 3)

0.50.981.5 ns

0.50.931.5 ns

Units

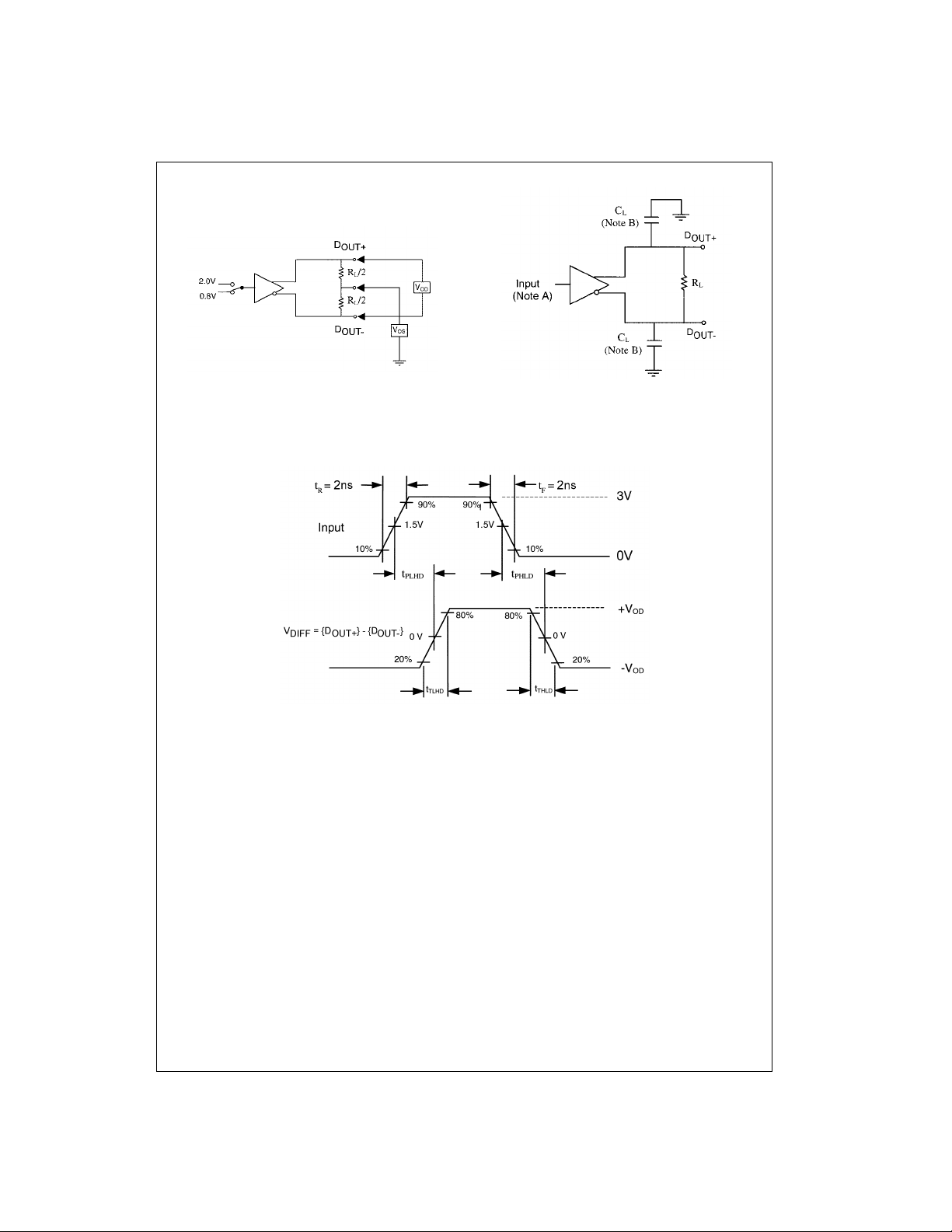

FIGURE 1. Differential Driver DC Test Circuit

Note A: All input pulses have f requency = 10 MHz, tR or tF = 2 ns

includes all probe and fixture capacitances

Note B: C

L

FIGURE 2. Differential Driver Propagation Delay and

Transition Time Test Circuit

FIN1001

FIGURE 3. AC Waveforms

3 www.fairchildsemi.com

Loading...

Loading...