Fairchild Semiconductor FAN5067 Datasheet

www.fairchildsemi.com

FAN5067

ACPI Dual Switch Controller

Features

• Implements ACPI control with PWROK, SLP_S3

SLP_S5

• Switch and linear regulator controller for 3.3V or 5V Dual

• Linear regulator controller and linear regulator for VADJ

Dual output adjustable from 2.5V to 3.5V

• Break-before-Make

• Drives all N-Channel MOSFETs plus NPN

• Latched overcurrent protection for outputs

• Power-up softstarts for the linear regulators

• UVLO guarantees correct operation for all conditions

• 16 pin SOIC package

and

Applications

• Willamette Platform ACPI Controller

• Northnwood Platform ACPI Controller

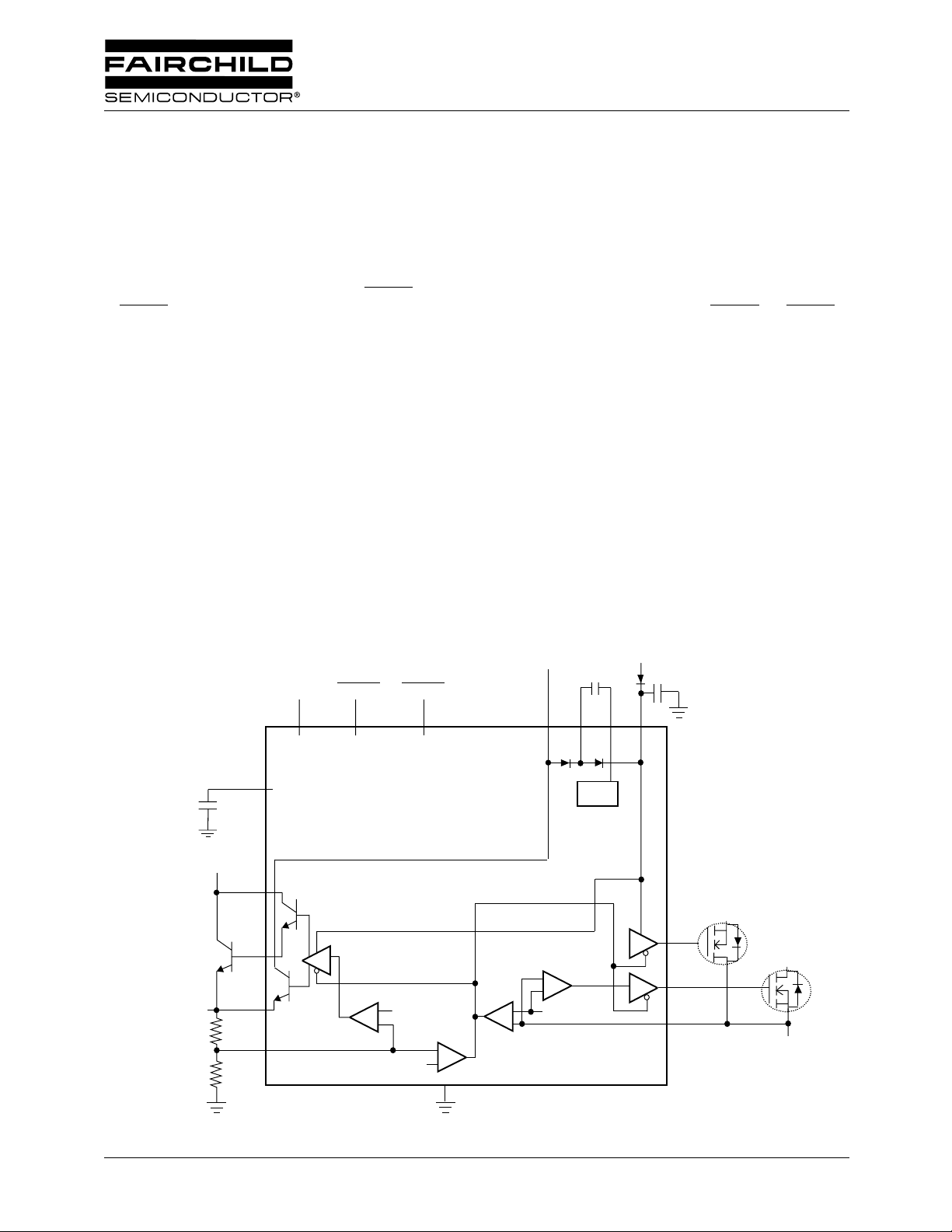

Block Diagram

PWR_OK

9

SLP_S3

SLP_S5

7

8

Description

The FAN5067 is an ACPI Switch Controller for Pentium IV

Platforms. It is controlled by PWROK, SLP_S3

and provides 3.3V or 5V Dual and VADJ Dual output for

SDRAM or DDR with 200mA minimum base current for an

external NPN transistor. An on-board precision low TC

reference achieves tight tolerance voltage regulation without

expensive external components. The FAN5067 also offers

integrated Current Limiting that protects each output, and

softstart for the linear regulators. The FAN5067 is available in

a 16 pin SOIC.

+5V Standby

321

+12V

16

and SLP_S5,

VADJ Dual

(SDRAM or DDR)

+5V Main

10

15

14

13

12

Softstart

Osc

Over Current

Main

4

-

+

REF

REF

+

-

+

REF

11

+

-

5

6

+5V Standby

+3.3V or 5V Dual

REV. 1.0.1 5/2/02

2

FAN5067 PRODUCT SPECIFICATION

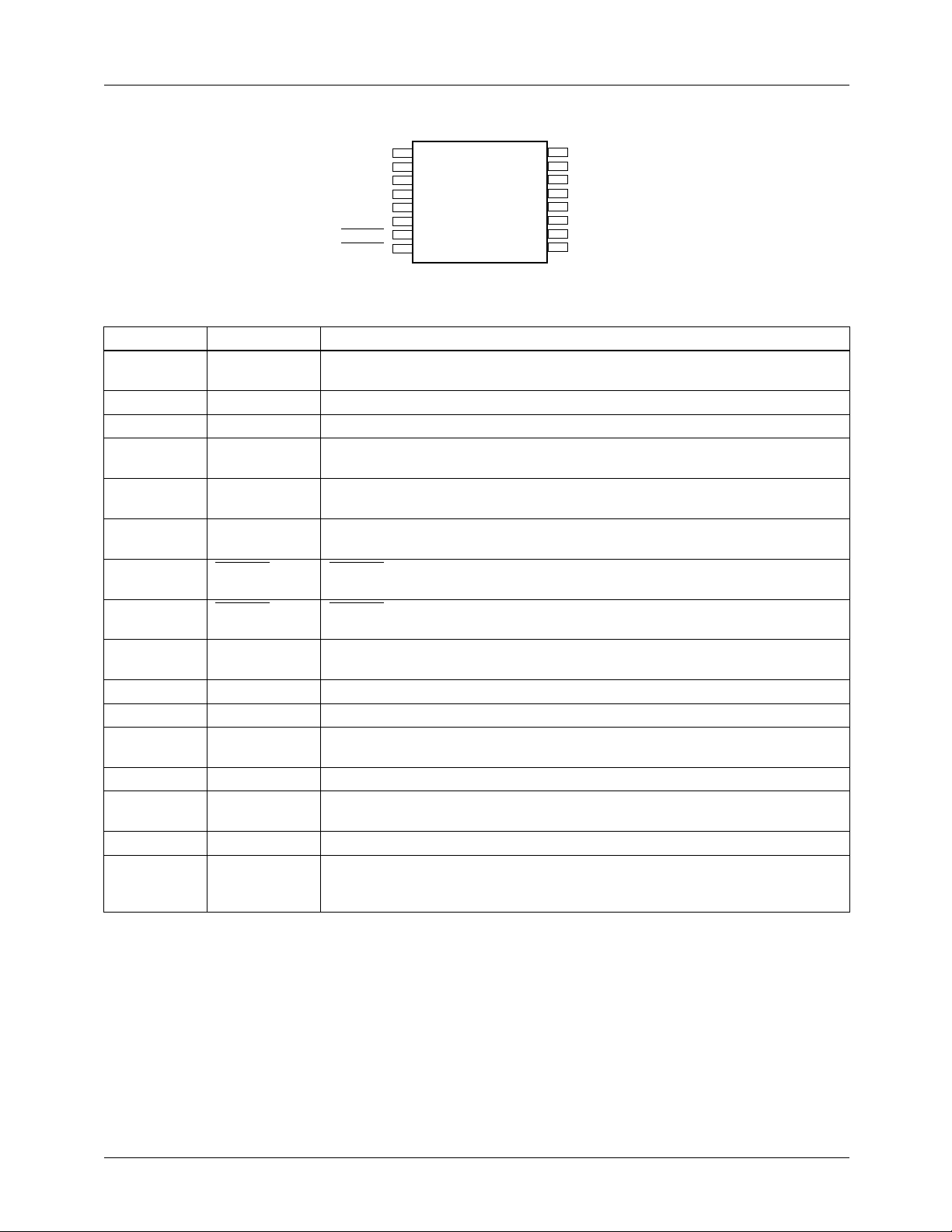

Pin Assignments

16

QCAP

PUMP

5VSTBY

DUALOUT1

DUALOUT2

DUALVFB

SLP_S3

SLP_S5

1

2

3

4

FAN5067

5

6

7

8

15

14

13

12

11

10

9

VCCP

5VMAIN

VADJOUT

VADJ

VADJFB

GND

SS

PWR_OK

Pin Definitions

Pin Number Pin Name Pin Function Description

1 QCAP

2 PUMP

3 5VSTBY

4 DUALOUT1

5 DUALOUT2

6 DUALFB

7 SLP_S3

8 SLP_S5

9 PWR_OK

10 SS

11 GND

12 VADJFB

13 VADJ

14 VADJOUT

15 5VMAIN

16 VCCP

Charge pump cap. Attach flying capacitor between this pin and PUMP to

generate high voltage from standby power.

Charge pump switcher.

5V Standby. Apply +5V standby on this pin to run the circuit in standby mode.

Dual output main gate control. Attach this pin to a transistor powering 3.3V or

5V dual from the main supply.

Dual output standby gate control. Attach this pin to a transistor powering 3.3V

or 5V dual from the 5V standby supply.

Dual output voltage Feedback. Pin 6 is used as the input for the voltage

feedback control loop for 3.3V or 5V dual.

SLP_S3. Control signal governing the Soft Off state S3. Internal current source

pulls this line high if left open.

SLP_S5. Control signal governing the Soft Off state S5. Internal current source

pulls this line high if left open.

PWR_OK. Control signal for switches. Internal current source pulls this line high if

left open.

Softstart. Attach a capacitor to this pin to determine the softstart rate.

Ground. Connect this pin to ground.

Adjustable Dual Voltage Feedback. Pin 12 is used as the input for the voltage

feedback loop for the adjustable dual voltage.

Adjustable Dual Voltage . Pin 13 sources VADJ during standby.

Adjustable Dual Voltage Base Control. Attach this pin to an NPN transistor

powering VADJ from the 5V Main.

5V Main. Apply +5V Main on this pin to run the VADJ base drive.

Main Power. Apply +12V through a diode on this pin to run the circuit in normal

mode. Bypass with a 0.1µF capacitor. When 12V is not present, this pin produces

voltage doubled 5V standby.

REV. 1.0.1 5/2/02

PRODUCT SPECIFICATION FAN5067

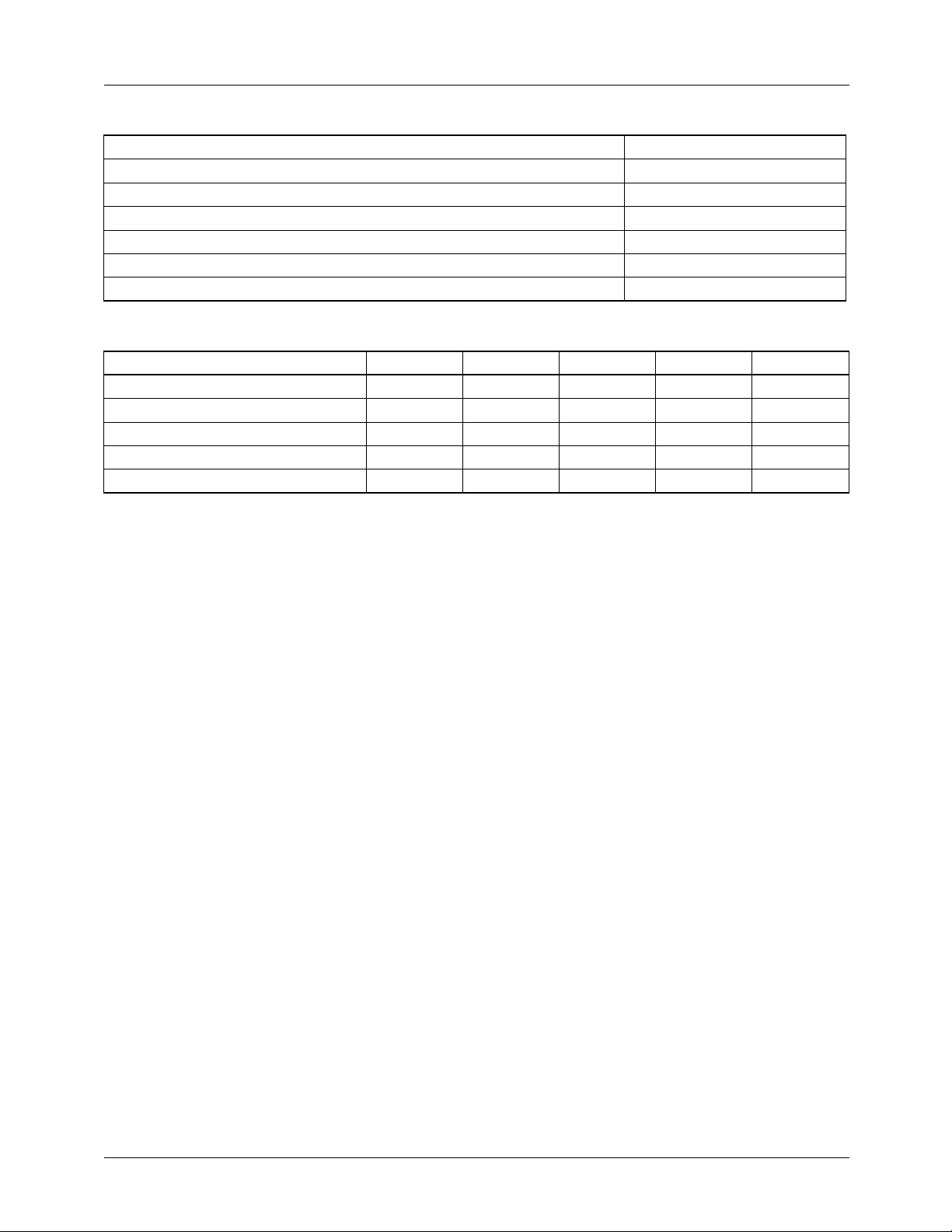

Absolute Maximum Ratings

V

CCP

15V

All Other Pins 13.5V

Junction Temperature, T

J

150°C

Storage Temperature -65 to 150°C

Lead Soldering Temperature, 10 seconds 300°C

Thermal Resistance Junction to Ambient Θ

Thermal Resistance Junction-to-case, Θ

JC

JA

85°C/W

24°C/W

Recommended Operating Conditions

Parameter Conditions Min. Typ. Max. Units

+3.3VMAIN 3.135 3.3 3.465 V

+5VMAIN 4.75 5 5.25 V

+5VSTBY 4.75 5 5.25 V

+12V 11.4 12 12.6 V

Ambient Operating Temperature 0 70 °C

REV. 1.0.1 5/2/02

3

4

≤

FAN5067 PRODUCT SPECIFICATION

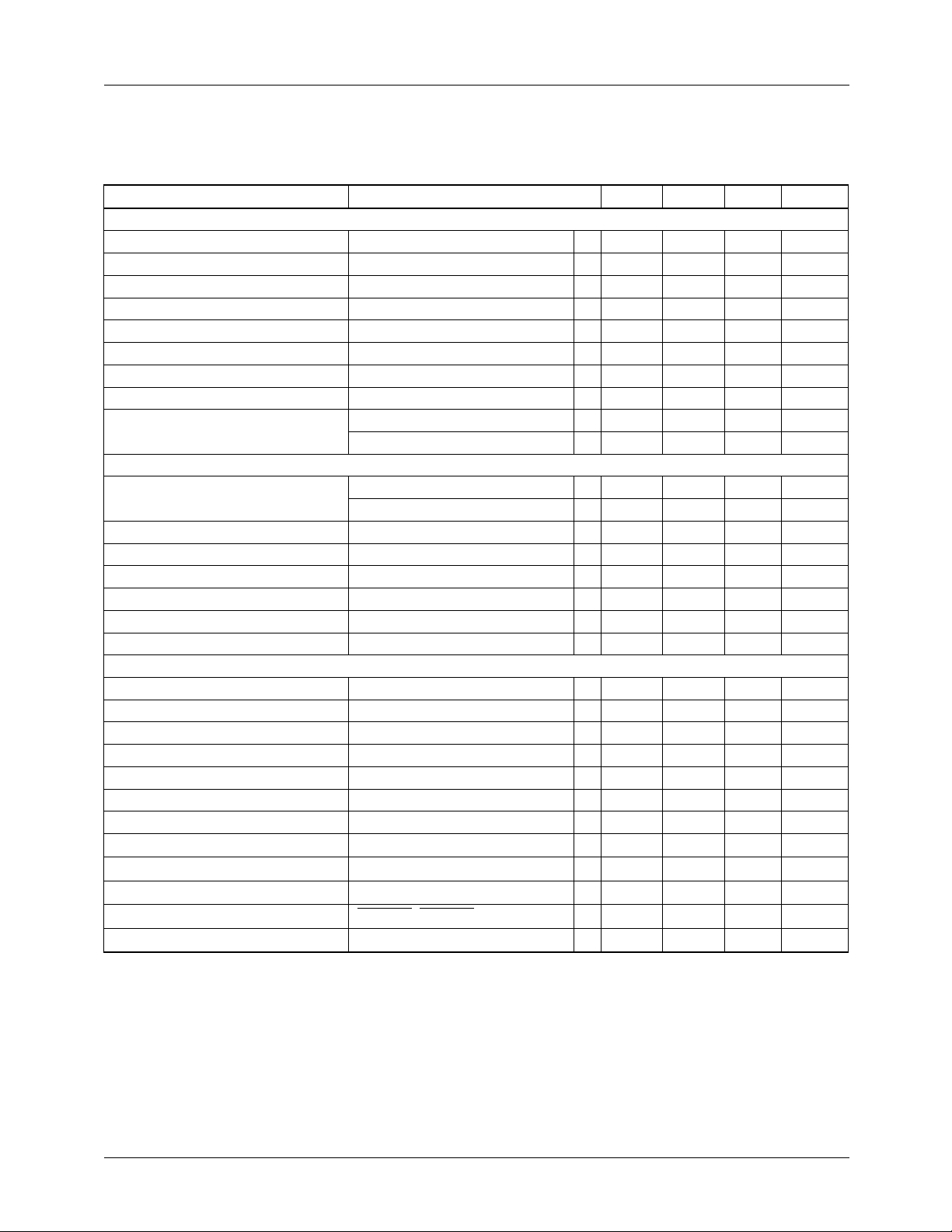

Electrical Specifications

(V

+5VSTBY

The • denotes specifications which apply over the full operating temperature range.

Parameter Conditions Min. Typ. Max. Units

DUAL Output

V

Out1

V

Out1

V

Out2

Total Output Voltage Variation

Maximum Drive Current DUALOUT1 On • 100 mA

Minimum Load Current DUALOUT2 On • 50 mA

Overcurrent Limit: Undervoltage 80 %Vout

Overcurrent Delay Time 150 µsec

Output Driver Deadtime See Figure 2: Main → Standby • 2 6 µsec

VADJ DUAL

I

B

Total Voltage Variation

VADJ Output Voltage Range 1.25 3.5 V

VADJ Current • 365 400 mA

Overcurrent Limit 80 %Vref

Overcurrent Delay Time 150 µsec

Output Driver Overlap Time See Figure 2 • 1 5 µsec

Common Functions

Charge Pump Frequency 250 KHz

+5VSTBY UVLO 4.5 V

+5VSTBY UVLO Hysteresis 0.5 V

+12V UVLO 7.5 V

+12V UVLO Hysteresis 800 mV

+5VSTBY Current MAIN Power Present 10 25 mA

+12V Current 2.5 10 mA

Input Logic HIGH • 2.0 V

Input Logic LOW • 0.8 V

Softstart Current 6 µA

Control Line Input Current SLP_S5, SLP_S3, PWROK • 100 µA

Over Temperature Shutdown 150 °C

= V

+5VMAIN

=5V, V

+3.3V

= 3.3V, V

= 12V and T

+12V

= +25°C using circuit in Figure 4, unless otherwise noted.)

A

, On • 10 V

, Off I = 10µA • 200 mV

, On Standby • 5 mA

1

DUALOUT2 On • 3.135 3.3 3.465 V

See Figure 2: Standby → Main • 200 1000 nsec

V

> 3.3V • 100 mA

O

V

3.3V • 150 mA

1

O

R

= R

= 10K Ω

1

2

• 2.375 2.5 2.625 V

Note:

1. Voltage Regulation includes Initial Voltage Setpoint and Output Temperature Drift.

REV. 1.0.1 5/2/02

PRODUCT SPECIFICATION FAN5067

→

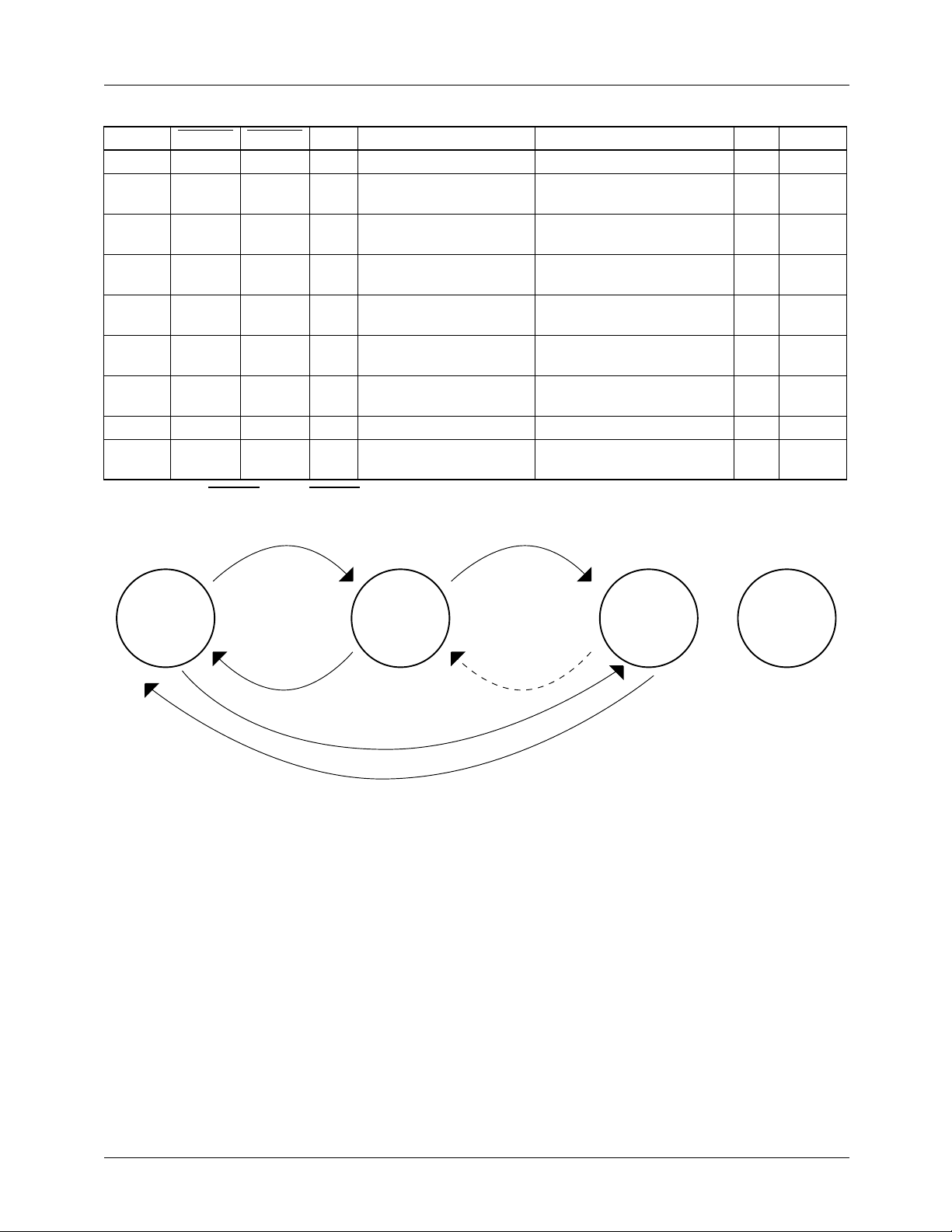

Table 1. Power Descriptors

PWROK SLP_S3

1 1 1 ON ON, Powered from MAIN ON, Powered from MAIN S0 S0

1 0 1 OFF ON, Powered from

0 0 1 OFF ON, Powered from

0 1 1 OFF ON, Powered from

1 0 0 OFF ON, Powered from

0 0 0 OFF ON, Powered from

0 1 0 OFF ON, Powered from

1 1 0 ON ON, Powered from MAIN OFF S5 Not Used

000

SLP_S5 Main Dual Output VADJ State Usage

STANDBY

STANDBY

STANDBY

ON, Powered from

STANDBY

ON, Powered from

STANDBY

ON, Powered from

STANDBY

S3 S0 → S3

S3 S3

S3 S3 → S0

OFF S5 S0 → S5

STANDBY

OFF S5 S5

STANDBY

OFF S5 S5 → S0

STANDBY

1 OFF ON, Powered from

OFF S5* *

STANDBY

*When PWROK =

111

S0

SLP_S3

= 0 and

101

011

SLP_S5

transitions from 0 to 1, the FAN5067 remains in the S5 state. See Table 2.

001

S3

Blocked

100

010

Figure 1. Power State Usage Diagram

000 110

S5

Not

Used

REV. 1.0.1 5/2/02

5

Loading...

Loading...