Fairchild Semiconductor FAN1654 Datasheet

www.fairchildsemi.com

FAN1654

1.5A LDO, DDR Bus Termination Regulator

Features

• Sinks and sources 1A continuous, 1.5A peak

• -40°C to +125°C Operating Range

• Load regulation: (VDDQ/2) ± 40mV

• 5mA VREF buffer tracks VTT

• On-chip thermal limiting

• Power-enhanced eTSSOP™-16 package

• Low Current Shutdown Mode

• Output Short Circuit Protection

Applications

• DDR terminators

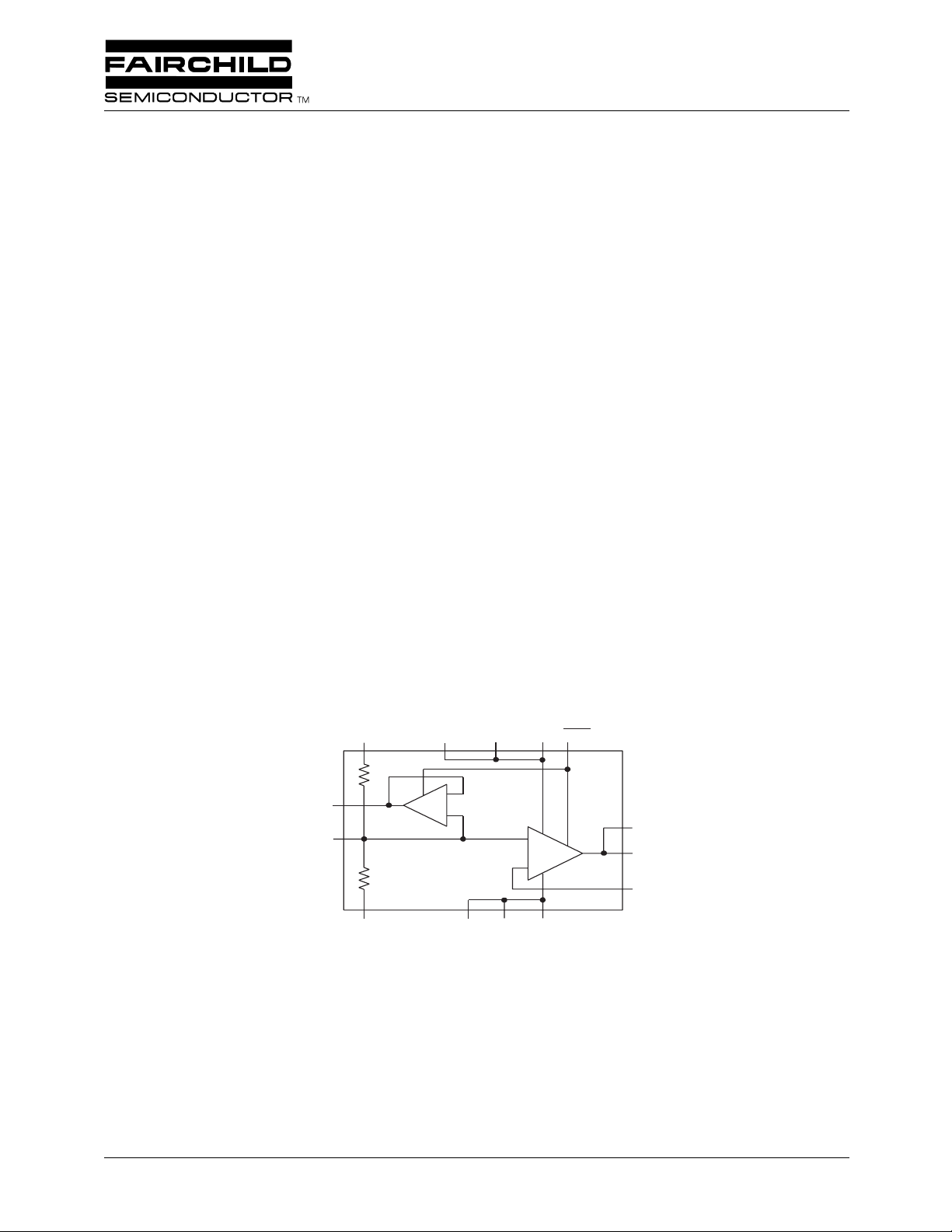

Block Diagram

Description

The FAN1654 is a low-cost bi-directional LDO specifically

designed for terminating DDR memory bus. It can both sink

and source up to 1A continuous, 1.5A peak, providing

enough current for most DDR applications. Load regulation

meets the JEDEC spec, VTT = (VDDQ/2) ± 40mV.

The FAN1654 includes a buffered reference voltage capable

of supplying up to 5mA current. On-chip thermal limiting

provides protection against a combination of power overload

and ambient temperature that would create an excessive

junction temperature. A shutdown input puts the FAN1654

into a low power mode for laptop computer applications.

The FAN1654 regulator is available in a power-enhanced

eTSSOP™-16 package, and the standard SOIC-14

VREFOUT

VREFIN

VDDQ

VSSQ

200k

200k

FAN1655

VDD VDD VDD

-

+

+

-

VSS VSS

VSS

SHDN

VTTFORCE

VTTFORCE

VTTSENSE

REV. 1.0.5 4/17/02

3

0

9

8

3

5

6

654

S

SE

SS

CE

SS

Q

OUT

Q

CE

SS

6

5

3

0

9

3

5

6

8

654

C

Q

Q

SHDN

SE

C

CE

SS

SS

CE

SS

PRODUCT SPECIFICATION FAN1654

Pin Assignments

1

VTTFOR

VTTFOR

N

VDD

1

VREFOUT

V

V

V

FAN1

VSS

1

1

VTTSEN

N

VSS

VREF

VDD

VTTFOR

HDN

1

FAN1

V

VTTSEN

V

1

VTTFOR

V

16-Lead Plastic eTSSOP-16

θJC = 4˚C/W*

*With package power slug soldered to 0.5 square inch

copper area over backside ground plane of internal

power plane

θJC = 37˚C/W, θ

Pin Definitions

Pin Number* Pin Name Pin Function Description

1, 2, 7 (4, 5, 10) VDD

3, 6 (6, 9) VTTFORCE VTT Force Output.

4, 5, 8 (7, 8, 11) VSS

10 (12) VTTSENSE VTT Sense . Feedback for remote sense of the VTT voltage.

11 (13) VREFIN

12 (14) SHDN

13 (1) VSSQ

14 (2) VREFOUT Buffered Voltage Reference Output.

15 (3) VDDQ

9,16 NC No Internal Connection

VDD. Input power for the LDO.

Power Ground.

VREFIN . Alternative input for direct control of VTTOUT and VREFOUT.

Shutdown. This active low shutdown turns off both VTT and VREFOUT. This

pin has an internal pull-down, and must be externally driven high for the IC to be

on.

Signal Ground.

VDDQ Input. Attach this pin to the VDDQ supply to generate VTT and

VREFOUT.

14-Lead Plastic SOIC

= 88˚C/W

JA

* Pin Numbers in brackets are for the SOIC-14 package

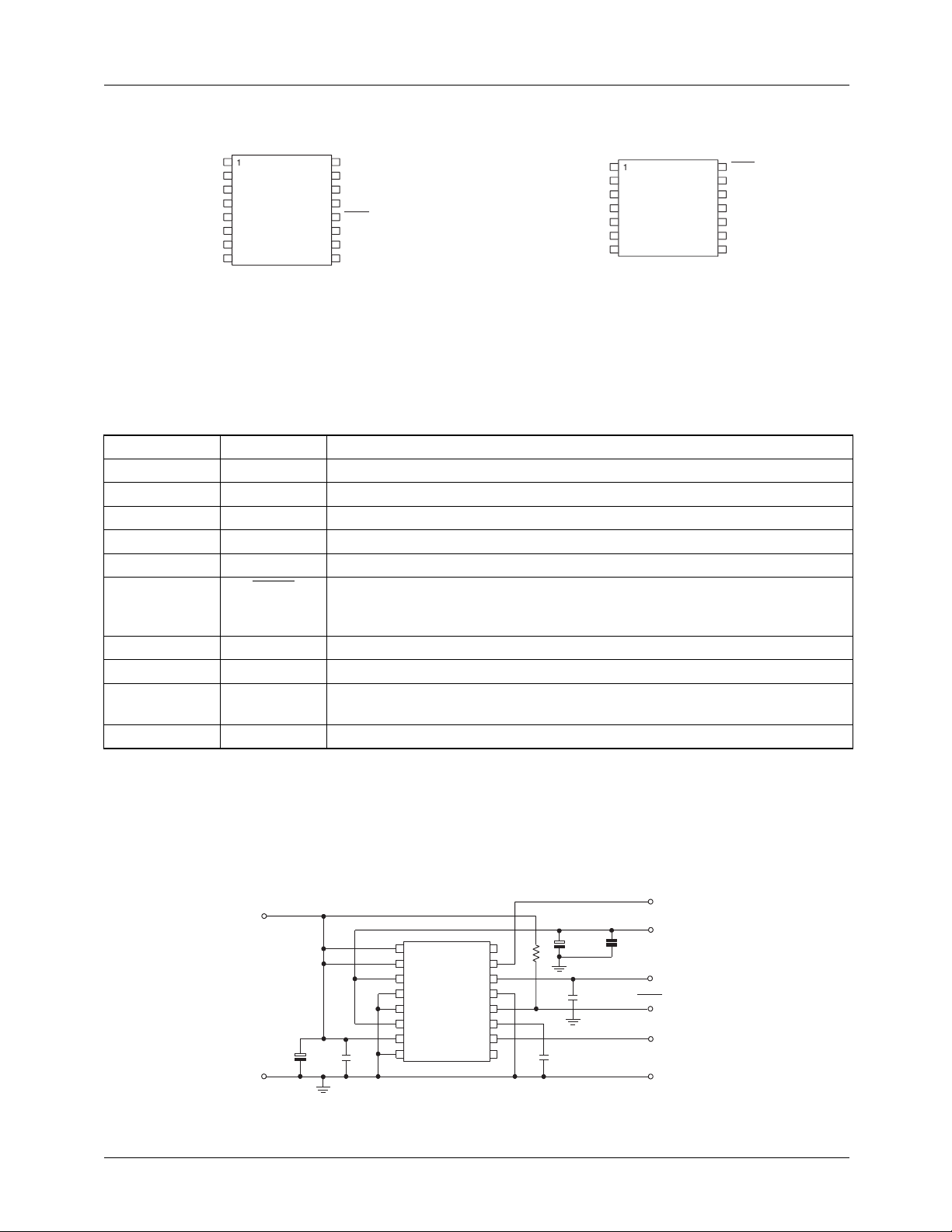

Typical Application

VDD

1

2

3

4

FAN1654

5

6

100µF

6V

GND

10µF

2

7

8

Figure 1. (eTSSOP pinout shown)

VDDQ

16

15

14

13

12

11

10

9

470µF

10k

1nF

VTTFORCE

10µF

VREFOUT

1nF

(connect to VTTFORCE

SHDN

VTTSENSE

at the load)

GND

REV. 1.0.5 4/17/02

FAN1654 PRODUCT SPECIFICATION

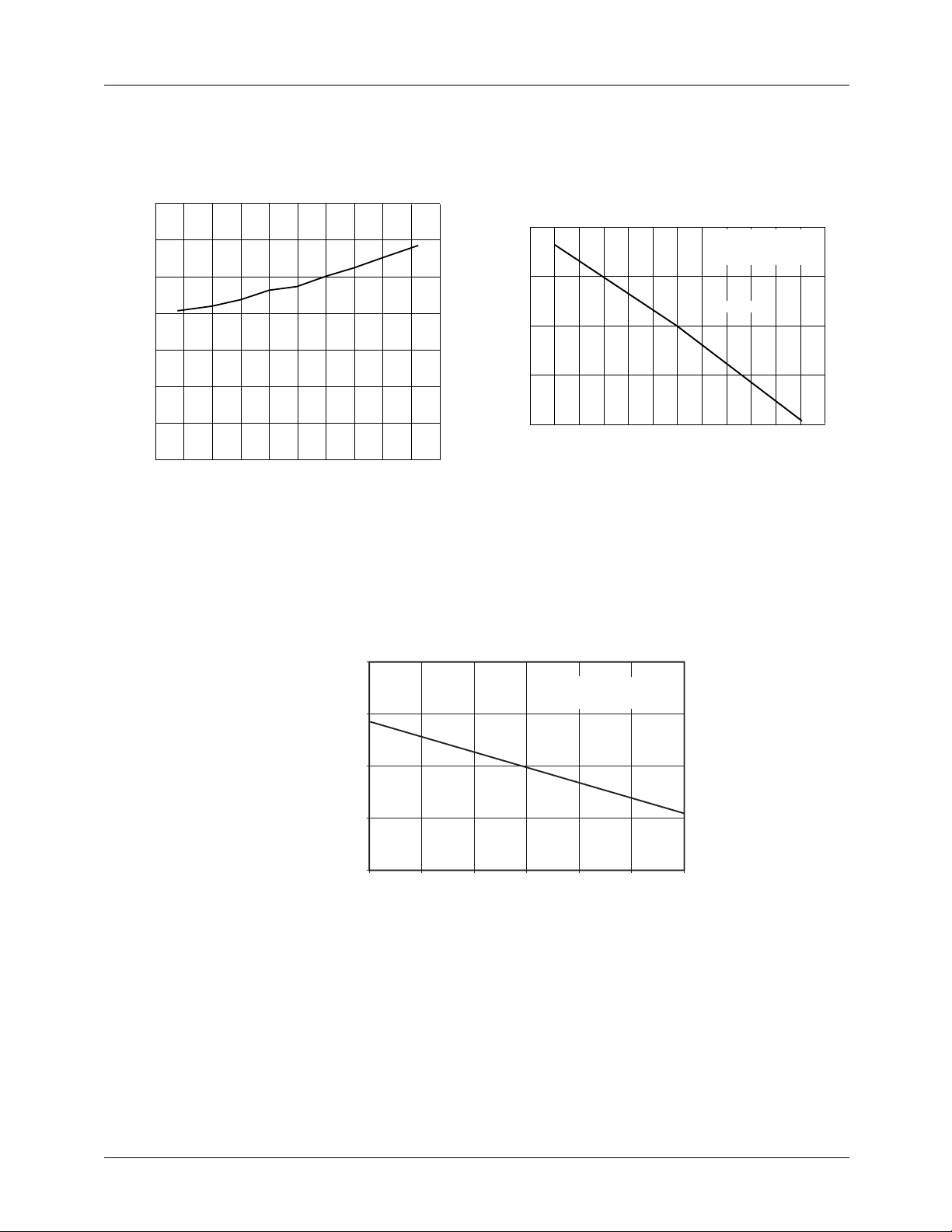

Typical Performance Characteristics

Quiescent Current vs. Temperature

3.5

3

2.5

2

1.5

1

QUIESCENT CURRENT (mA)

.5

0

-60

-20 0

-40

AMBIENT TEMPERATURE (˚C)

Figure 2 Figure 3

20

40 60 80

1.260

1.255

100

120

(mV)

REFOUT

∆ V

140

VTT Load Current

1.0

0.5

-0.5

-1.0

V

REF

Output Change vs. I

R

0

-5

-6

-4 -3

-1 0

-2

V

REF

LOAD CURRENT (mA)

1

VDD = V

TA = 25˚C

OUT

= 0.2Ω

2

3

REF

DDQ

= 2.5V

4

56

= V

DDQ

= 2.5V

V

DD

TA = 25°C

REV. 1.0.5 4/17/02

1.250

OUTPUT (V)

TT

V

1.245

1.240

-1500 -1000 -500 0 500 1000 1500

Load Current (mA)

V

TT

Figure 4

3

Loading...

Loading...