Fairchild Semiconductor 74ALVCH162244 Datasheet

September 2001

Revised February 2002

74ALVCH162244

Low Voltage 16-Bit Buffer/Line Driver with Bushold

and 26

Ω Series Resistor in Outputs

74ALVCH162244 Low Voltage 16-Bit Buffer/Line Driver with Bushold and 26

General Description

The ALVCH162244 contains sixteen non-inverting buffers

with 3-STATE outputs to be empl oyed as a memory and

address driver, clock driver, or bus oriented transmitter/

receiver. The device is nibble (4-bit) controlled. Each nibble

has separate 3-STATE control inputs which can be shorted

together for full 16-bit operation.

The ALVCH162244 data inputs incl ude active b ushold circuitry, eliminating the need for external pull-up resistors to

hold unused or floating data inputs at a valid logic level

The 74ALVCH162244 is also designed with 26

resistors in the outputs. This design reduces l ine noise in

applications such as memory address drivers, cl ock drivers, and bus transceivers/transmitters.

The 74ALVCH162244 is designed for low voltage (1.65V to

3.6V) V

The 74ALVCH162244 is fabricated with an advanced

CMOS technology to achieve high speed operation while

maintaining low CMOS power dissipation.

applications with output capability up to 3.6V.

CC

Ω series

Features

■ 1.65V to 3.6V VCC supply operation

■ 3.6V tolerant control inputs and outputs

■ Bushold on data inputs eliminates the need for external

pull-up/pull-down resistors

■ 26

Ω series resistors in outputs

■ t

PD

4.2 ns max for 3.0V to 3.6V V

4.9 ns max for 2.3V to 2.7V V

7.6 ns max for 1.65V to 1.95V V

■ Uses patented noise/EMI reductio n circuitr y

■ Latch-up conforms to JEDEC JED78

■ ESD performance:

Human body model

Machine model

> 200V

CC

CC

CC

> 2000V

Ordering Code:

Order Number

74ALVCH162244T MTD48 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

Devices also availab l e in Tape and Reel. Specify by appending su ffix let te r “X” to the ordering code.

Package

Number

Package Description

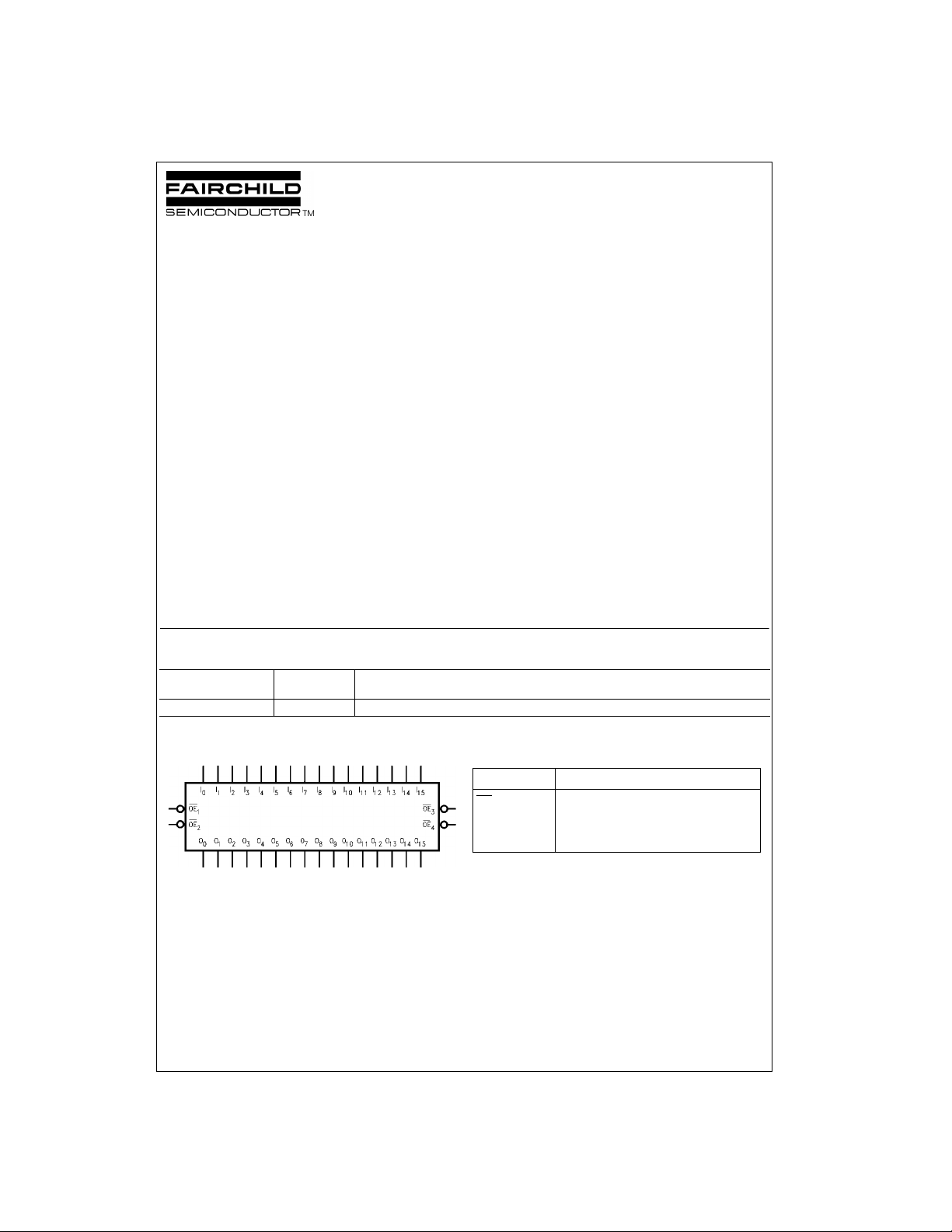

Logic Symbol Pin Descriptions

Pin Names Description

OE

I

0–I15

O

0–O15

n

Output Enable Input (Active LOW)

Bushold Inputs

Outputs

Ω

Series Resistor in Outputs

© 2002 Fairchild Semiconductor Corporation DS500632 www.fairchildsemi.com

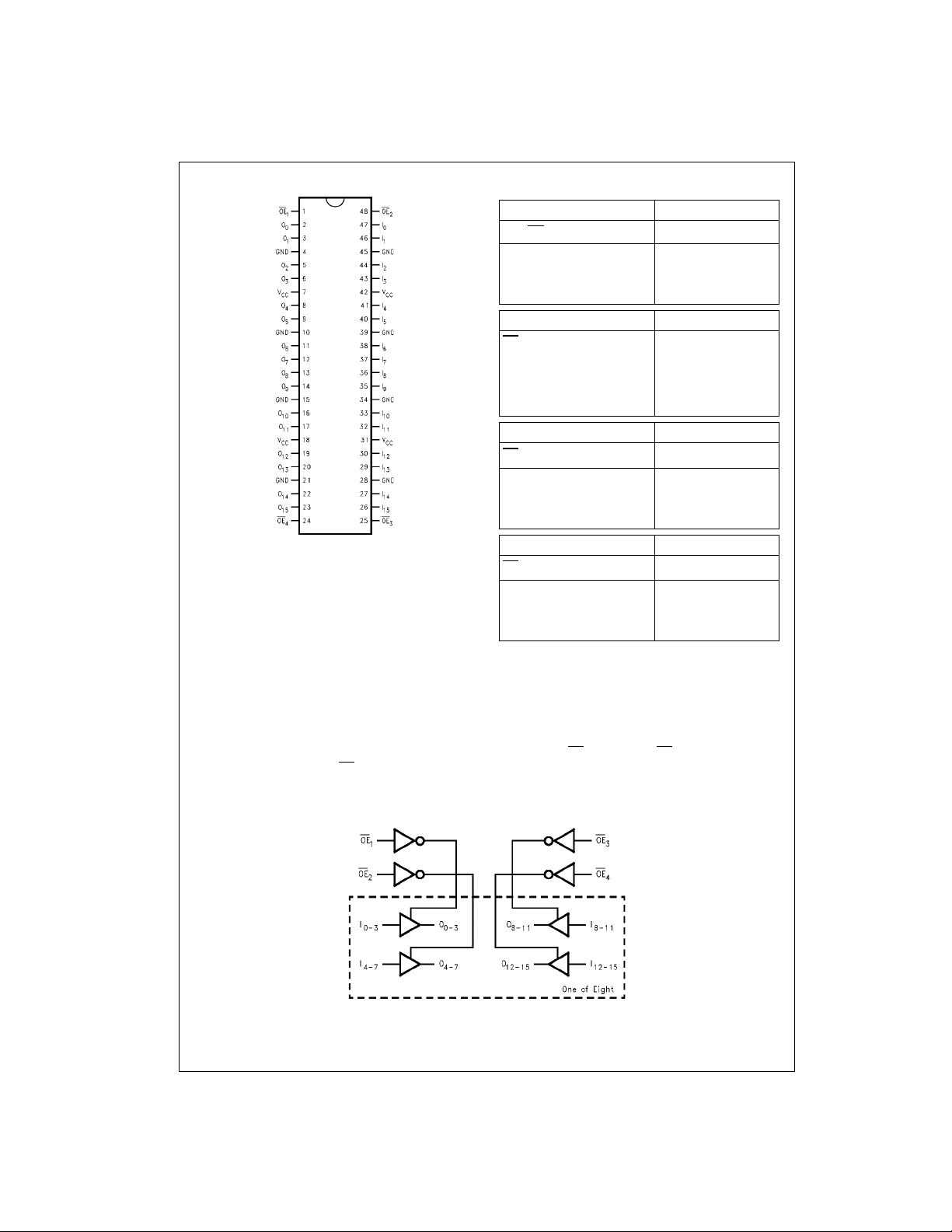

Connection Diagram Truth Tables

OE

LL L

LH H

74ALVCH162244

HX Z

Inputs Outputs

OE

2

LLL

LHH

HXZ

Inputs Outputs

OE

3

LLL

LHH

HXZ

Inputs Outputs

OE

4

LLL

LHH

HXZ

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial (HIGH or LOW, inputs may not float)

Z = High Impedance

Inputs Outputs

1

I0–I

I4–I

I8–I

I12–I

3

7

11

15

O0–O

O4–O

O8–O

O12–O

3

7

11

15

Functional Description

The 74ALVCH162244 contains sixteen non-inverting buffers with 3-STATE outputs. The device is nibble (4 bits) controlled

with each nibble funct ionin g identical ly, but independent of ea ch other. The contro l pins m ay be sho rted tog ether to obtain

full 16-bit operation .The 3-S TATE outputs are controlled by an Output Enabl e (OE

are in the 2-state mo de. When OE

is HIGH, the standard out put s are in th e hi g h imp ed ance mo de b ut th i s do es no t inte r-

n

) input. When OEn is LOW, the outputs

n

fere with entering new data into the inputs.

Logic Diagram

www.fairchildsemi.com 2

Loading...

Loading...