Fairchild Semiconductor 74ABT652CMTC, 74ABT652CMSAX, 74ABT652CMSA, 74ABT652CSPC, 74ABT652CSCX Datasheet

...

November 1992

Revised January 1999

74ABT652 Octal Transceivers and Registers with 3-STATE Outputs

© 1999 Fairchild Semiconductor Corporation DS011512.prf www.fairchildsemi.com

74ABT652

Octal Transceiver s and Registe rs with 3-STATE Output s

General Description

The ABT652 consists of bus transceiver circuits with Dtype flip-flops and cont rol circu itr y arrang ed for multip lexed

transmission of data directl y from th e input bus or fr om the

internal registers. Data on the A or B bus will be clocked

into the registers as the appropriate clock pin goes to HIGH

logic level. Output Enable pins (OEAB, OEBA

) are pro-

vided to control the transceiver function.

Features

■ Independent registers for A and B buses

■ Multiplexed real-time and stored data

■ A and B output sink capability of 64 mA, source

capability of 32 mA

■ Guaranteed output skew

■ Guaranteed multiple output switching specifications

■ Output switching specified for both 50 pF and

250 pF loads

■ Guaranteed simultaneous switching noise level and

dynamic threshold performance

■ Guaranteed latchup protection

■ High impedance glitch free bus loading during entire

power up and power down cycle

■ Nondestructive hot insertion capability

Ordering Code:

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to t he ordering code.

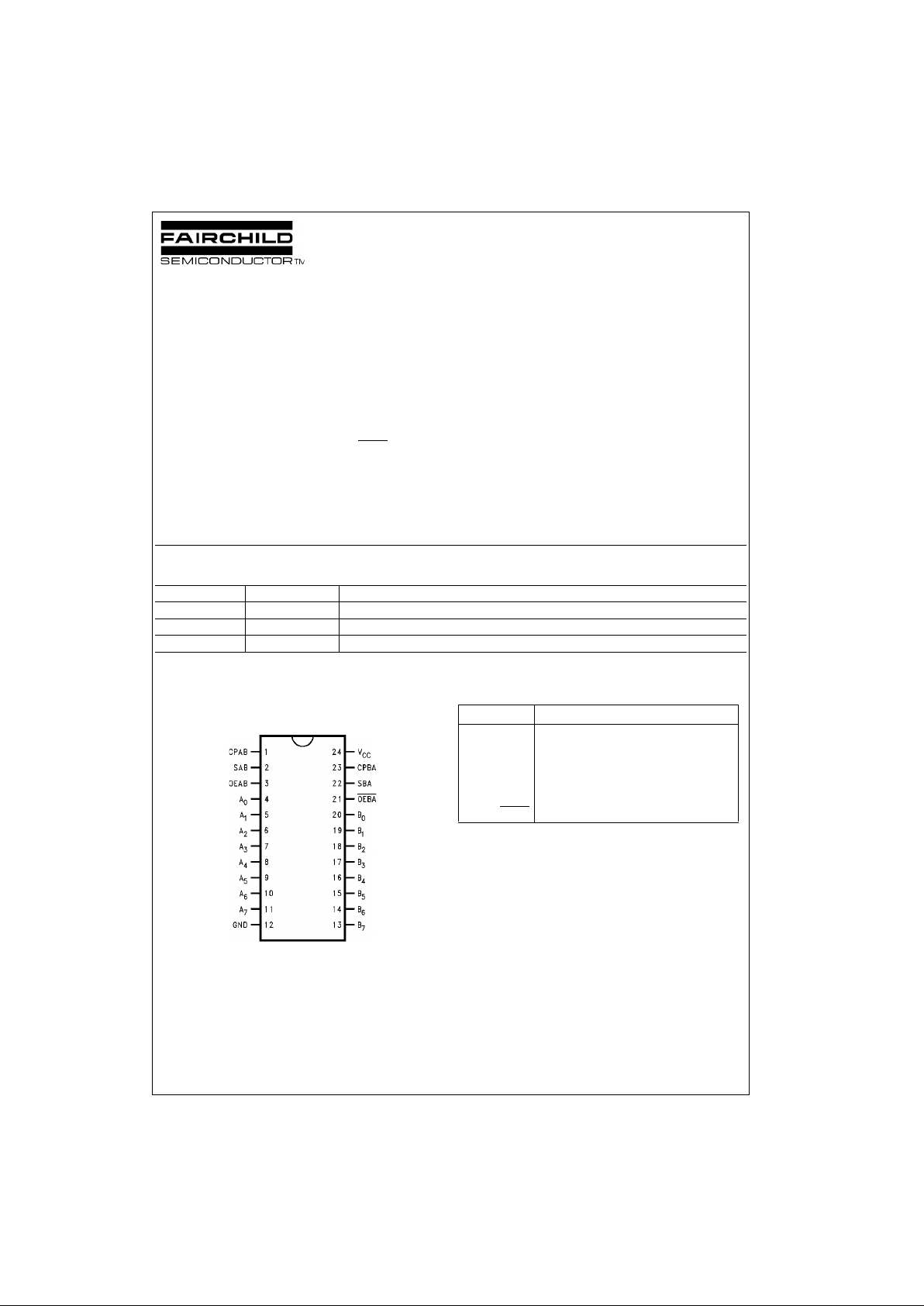

Connection Diagram

Pin Assignment for

SOIC, SSOP and TSSOP

Pin Descriptions

Order Number Package Number Package Description

74ABT652CSC M24B 24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300” Wide Body

74ABT652CMSA MSA24 24-Lead Shrink Small Outline Package (SSOP), EIAJ TYPE II, 5.3mm Wide

74ABT652CMTC MTC24 24-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

Pin Names Description

A

0–A7

Data Register A Inputs/3-STATE Outputs

B

0–B7

Data Register B Inputs/3-STATE Outputs

CPAB, CPBA Clock Pulse Inputs

SAB, SBA Select Inputs

OEAB, OEBA

Output Enable Inputs

www.fairchildsemi.com 2

74ABT652

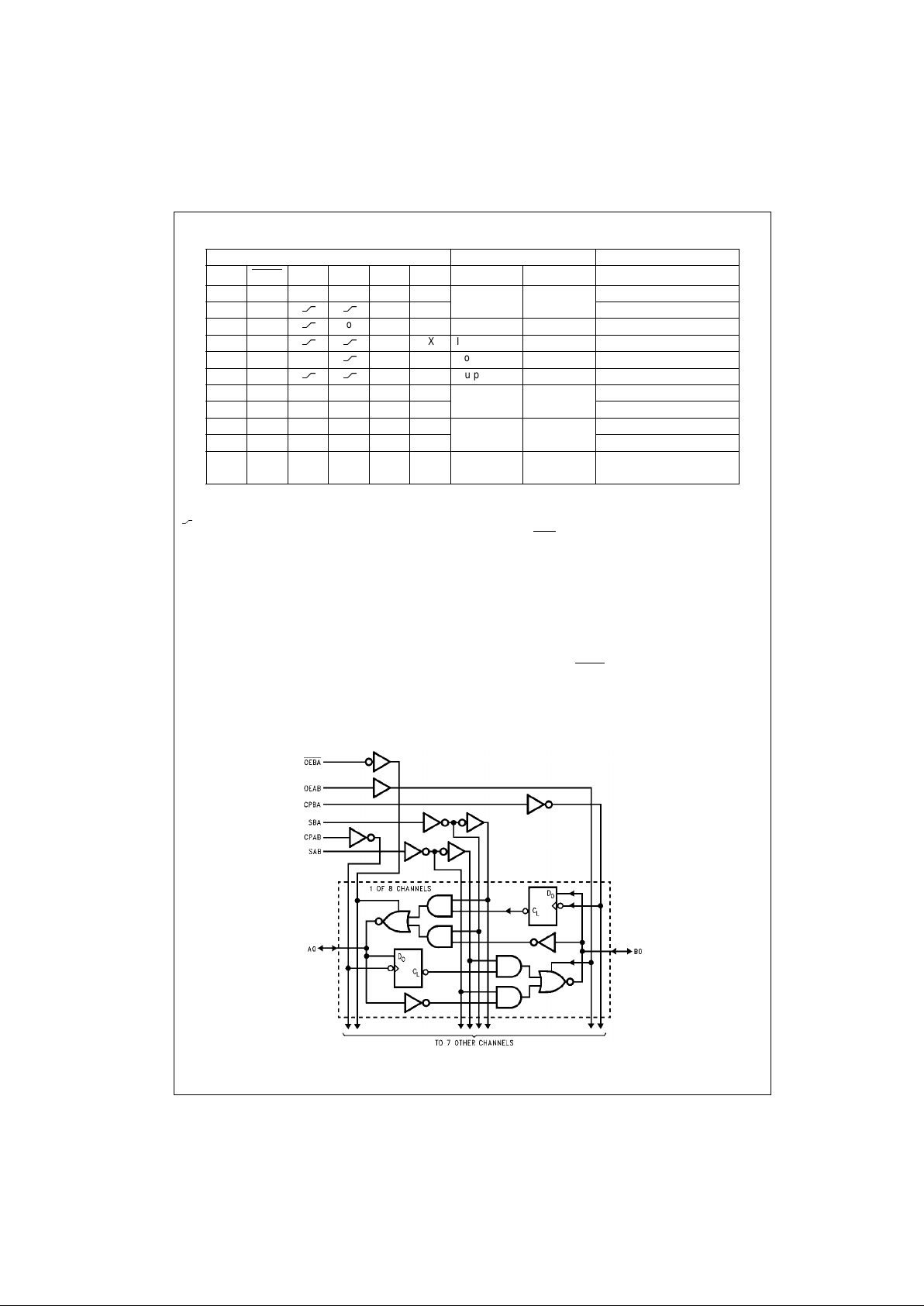

Truth Table

H = HIGH Voltage Level

L = LOW V oltage Leve l

X = Immaterial

= LOW to HIGH Clock Transition

Note 1: The data output f unction s may be enabled or dis abled by vario us si gnals a t OEA B or OE BA

inputs. Data input functions are always enabled, i.e.,

data at the bus pins will b e s to red on every LOW to HIGH transition on the clock inputs.

Functional Description

In the transceiver mo de, data presen t at the HI GH impedance port may be stored in either the A or B register or

both.

The select (SAB, SBA) controls can multiplex stored and

real-time.

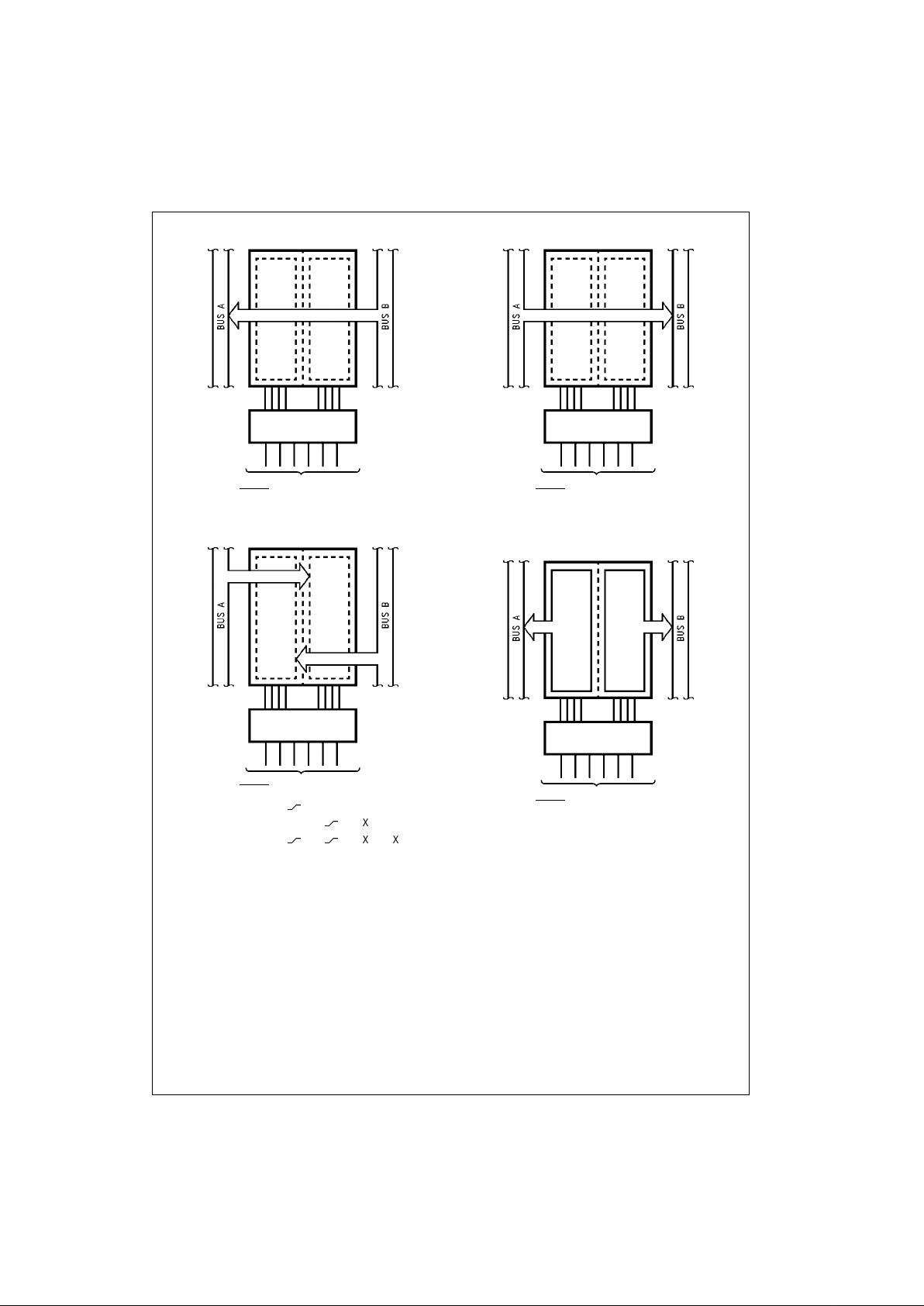

The examples in Figure 1 demon strate th e four fundamen tal bus-management func tions that can be perfor med with

the ABT652.

Data on the A or B data bus, or both, can be stored in the

internal D flip-flop by LOW to HIGH transitions at the

appropriate Clock Inpu ts (CPAB, CPBA) regardless o f the

Select or Output Enable Inputs. When SAB and SBA are in

the real time transfer mod e, it is also possible to store data

without using the internal D flip-flops by simultaneously

enabling OEAB and OEBA

. In this configuration each Output reinforces its Input. Thus when all other data sources to

the two sets of bus lines are i n a HIGH impedance sta te,

each set of bus lines will remain at its last state.

Logic Diagram

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

Inputs Inputs/Outputs (Note 1) Operating Mode

OEAB

OEBA

CP AB CPBA SAB SBA

A

0

thru A7 B0 thru B

7

L H H or L H or L X X Input Input Isolation

L H

X X Store A and B Data

X H

H or L X X Input Not Specified Store A, Hold B

H H

X X Input Output Store A in Both Registers

L X H or L

X X Not Specified Input Hold A, Store B

L L

X X Output Input Store B in Both Registers

L L X X X L Output Input Real-Time B Data to A Bus

L L X H or L X H Store B Data to A Bus

H H X X L X Input Output Real-Time A Data to B Bus

H H H or L X H X Stored A Data to B Bus

H L H or L H or L H H Output Output Stored A Data to B Bus and

Stored B Data to A Bus

3 www.fairchildsemi.com

74ABT652

Note A: Real-Time

Transfer Bus B to Bus A

Note C: Storage

Note B: Real-Time

Transfer Bus A to Bus B

Note D: Transfer Storage

Data to A or B

FIGURE 1.

OEAB OEBA

CPAB CPBA SAB SBA

L L X X X L

OEAB OEBA

CPAB CPBA SAB SBA

X H

X X X

L X X

X X

L H

X X

OEAB OEBA CPAB CPBA SAB SBA

H H X X L X

OEAB OEBA

CPAB CPBA SAB SBA

H L H or L H or L H H

Loading...

Loading...