Fairchild Semiconductor 29F52SPC, 29F52SCX, 29F52SC Datasheet

© 1999 Fairchild Semiconductor Corporation DS009606 www.fairchildsemi.com

April 1988

Revised August 1999

29F52•29F53 8-Bit Registered Transceiver

29F52•29F53

8-Bit Registered Transceiver

General Description

The 29F52 and 29F53 are 8-bit registered transceivers.

Two 8-bit back to back registers store data flowing i n both

directions between two bidirectional buses. Separate clock,

clock enable and 3-STATE output enable signals are provided for each reg ister. The A

0–A7

output pins are guara n-

teed to sink 24 mA while the B

0–B7

output pins are

designed for 64 mA.

The 29F53 is an inverting op tion of the 29F5 2. Both tran s-

ceivers are AMD Am2952/2953 functional equivalents.

Features

■ 8-bit registered transceivers

■ Separate clock, clock enable and 3-STATE output

enable provided for each register

■ AMD Am2952/2953 functional equivalents

■ Both inverting and non-inverting options available

■ 24-Pin slimline package

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

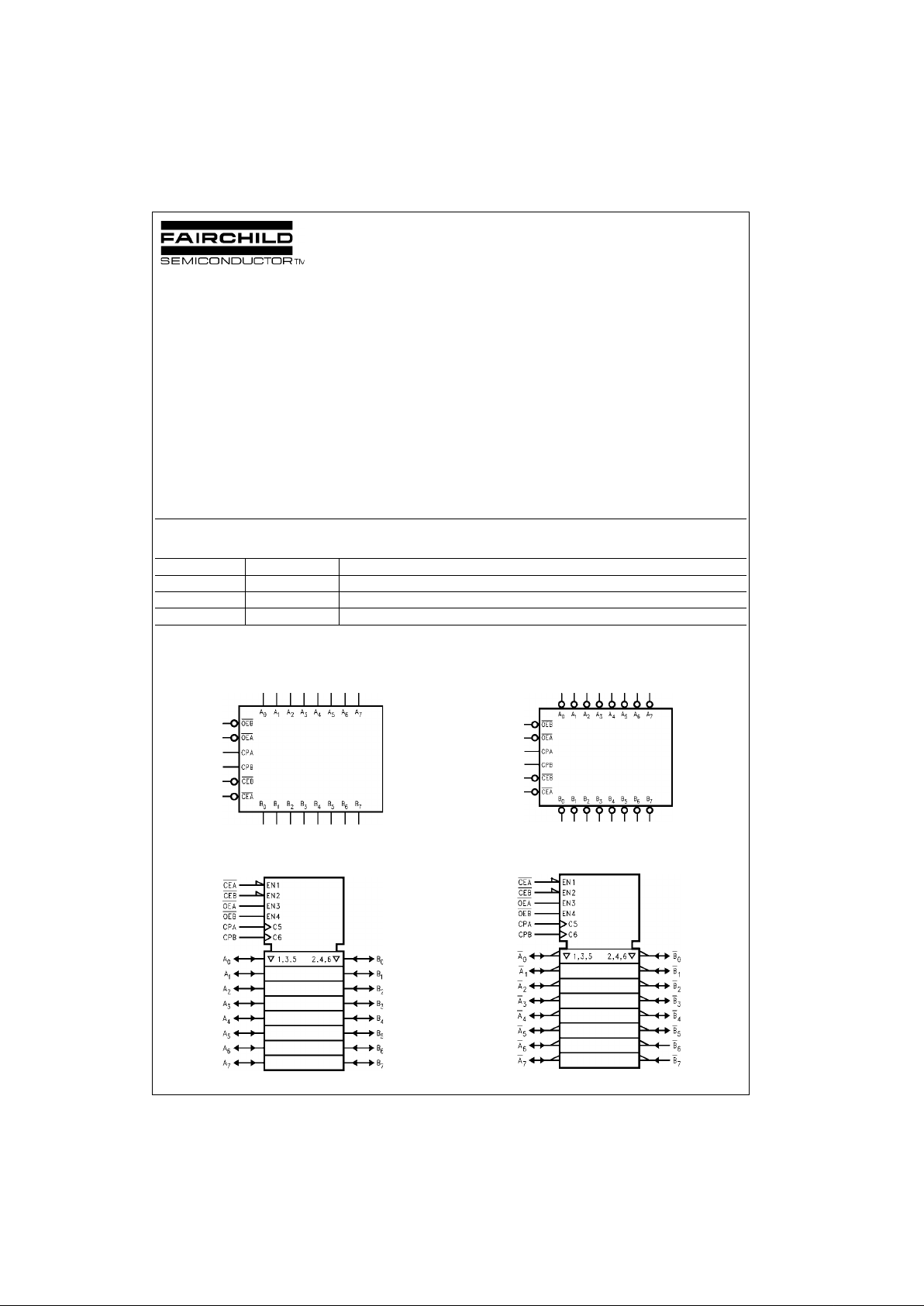

Logic Symbols

29F52

IEEE/IEC

29F52

29F53

IEEE/IEC

29F53

Order Number Package Number Package Description

29F52SC M24B 24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

29F52SPC N24C 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-100, 0.300 Wide

29F53SPC N24C 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-100, 0.300 Wide

www.fairchildsemi.com 2

29F52•29F53

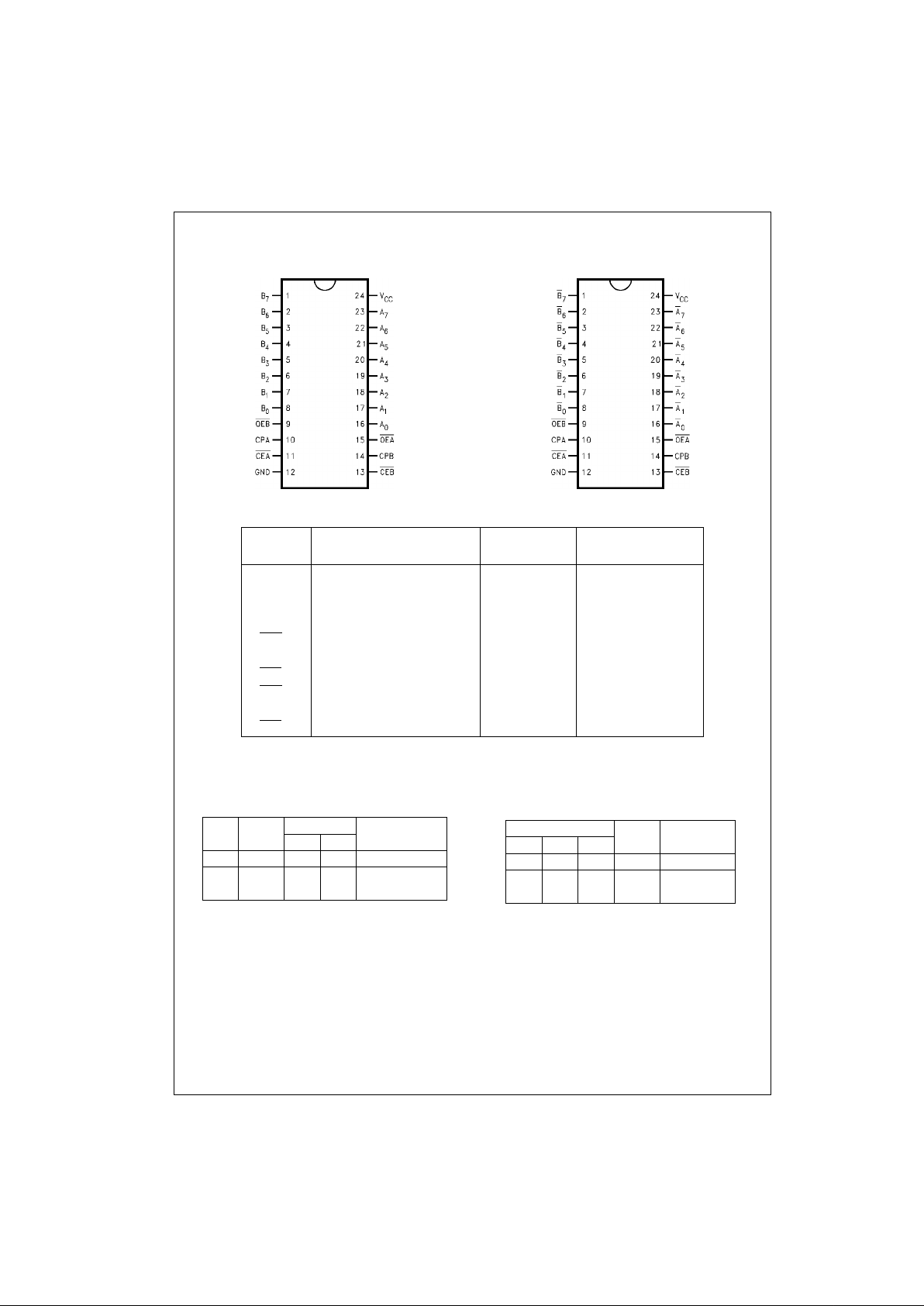

Connection Diagrams

Pin Assignment for DIP and SOIC

29F52

Pin Assignment for DIP

29F53

Unit Loading/Fan Out

Output Control

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

Z = HIGH Impedance

N = LOW-to-HIGH Transition

NC = No Change

Register Function Table

(Applies to A or B Register)

Pin Names Description

U.L.

Input I

IH/IIL

HIGH/LOW

Output I

OH/IOL

A0–A

7

A-Register Inputs/ 3.5/1.083 70 µA/0.65 mA

B-Register 3-STATE Outputs 150/40 (33.3) −3 mA/24 mA (20 mA)

B

0–B7

B Register Inputs/ 3.5/1.083 70 µA/0.65 mA

A-Register 3-STATE Outputs 600/106.6 (80) −12 mA/64 mA (48 mA)

OEA

Output Enable A-Register 1.0/1.0 20 µA/−0.6 mA

CPA A-Register Clock 1.0/1.0 20 µA/−0.6 mA

CEA

A-Register Clock Enable 1.0/1.0 20 µA/−0.6 mA

OEB

Output Enable B-Register 1.0/1.0 20 µA/−0.6 mA

CPB B-Register Clock 1.0/1.0 20 µA/−0.6 mA

CEB

B-Register Clock Enable 1.0/1.0 20 µA/−0.6 mA

OE

Internal Y-Output

Function

Q 29F52 29F53

H X Z Z Disable Outputs

LLLH

Enable Outputs

LHHL

Inputs Internal

Function

DCPCE Q

X X H NC Hold Data

LNL L

Load Data

HNL H

3 www.fairchildsemi.com

29F52•29F53

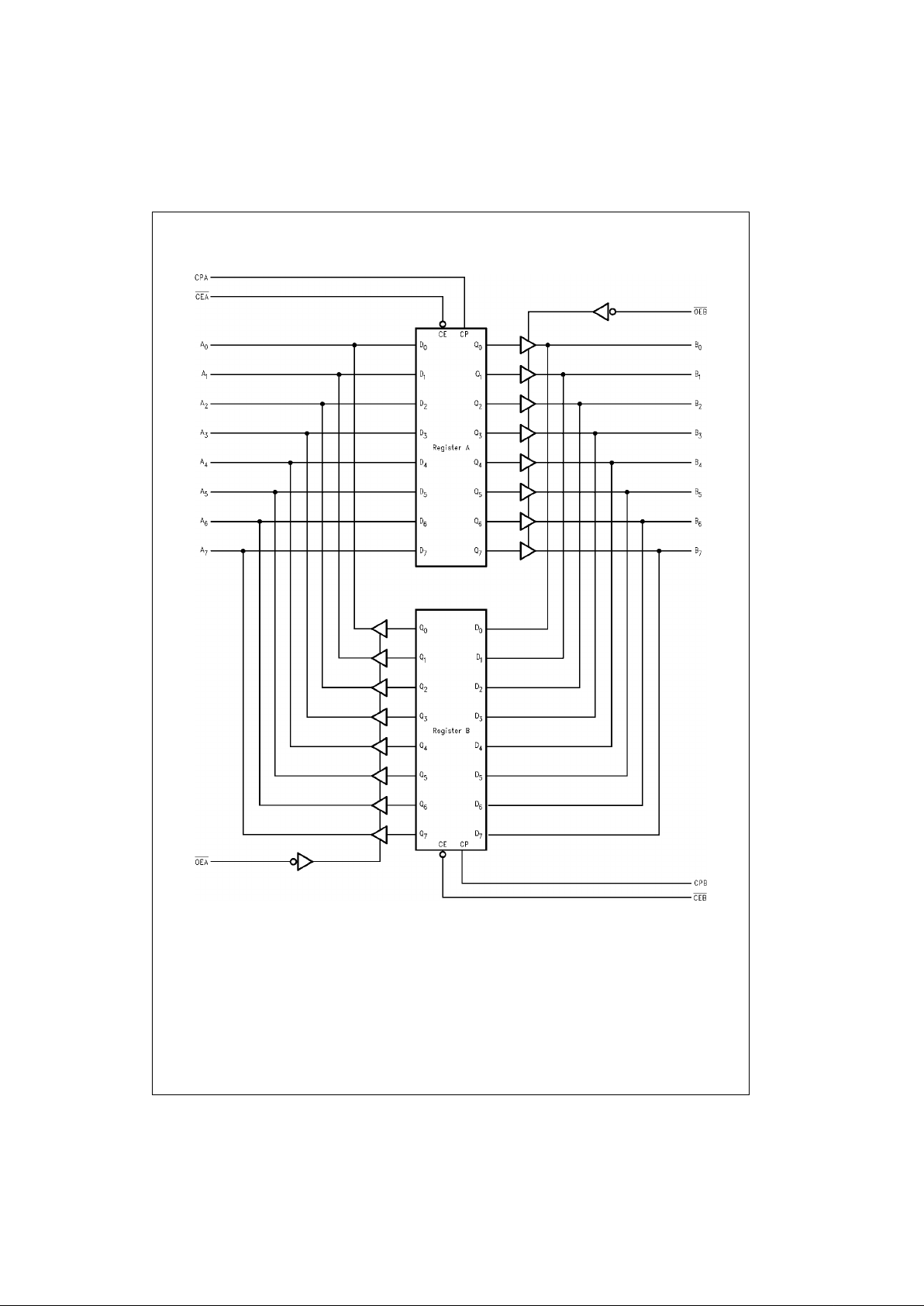

Block Diagrams

29F52

Loading...

Loading...