Fairchild FSTU32160 service manual

May 1999

Revised

October 2006

FSTU32160

16-Bit to 32-Bit Multiplexer/Demultiplexer Bus Switch

with

−2V Undershoot Protection

FSTU32160 16-Bit to 32-Bit Multiplexer/Demultipl exer Bus Switch with

General Description

The Fairchild Sw itch F STU3 2160 is a 16-b it t o 32- bit hi ghspeed CMOS TTL-compatible multiplexer/demultiplexer

bus switch. The low on resistance of the switch allows

inputs to be connect ed to out puts wi thout adding prop agation delay or generating additional ground bounce noise.

The device can be used in app lications where two buses

need to be addresse d simultaneously. The FSTU3 2160 is

designed so that the A Port de multiplexe s into B

both. The A and B Ports have “ undershoot har dened” circuit protection to suppor t an ext end ed range to 2.0V below

ground. Fairchild’s integrated Undershoot Hardened Circuit

(UHC

®) senses undershoot at the I/O’s, and responds by

preventing voltage differentials from developing and turning on the switch.

Two select (S

When S

to a selectable bias voltage (Bi as V) to mini mize li ve inser-

tion noise.

, S2) inputs provide switch enable control.

1

, S2 are HIGH, the device precharge s the B Port

1

or B2 or

1

Features

■ Undershoot hardened to −2V (A and B Ports).

■ Slower Output Enable times prevent signal disruption

■ 4

Ω switch connection between two ports.

■ Minimal propagation delay through the switch.

■ Low l

■ Zero bounce in flow-through mode.

■ Control inputs compatible with TTL level.

■ See Applications Note AN-5008 for details

.

CC

Ordering Code:

Order Number Package Number Package Description

FSTU32160MTD MTD56 56-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

−

2V Undershoot Protection

UHC

® is a registered trademark of Fairchild Semiconductor Corporation.

© 2000 Fairchild Semiconductor Corporation DS500244 www.fairchildsemi.com

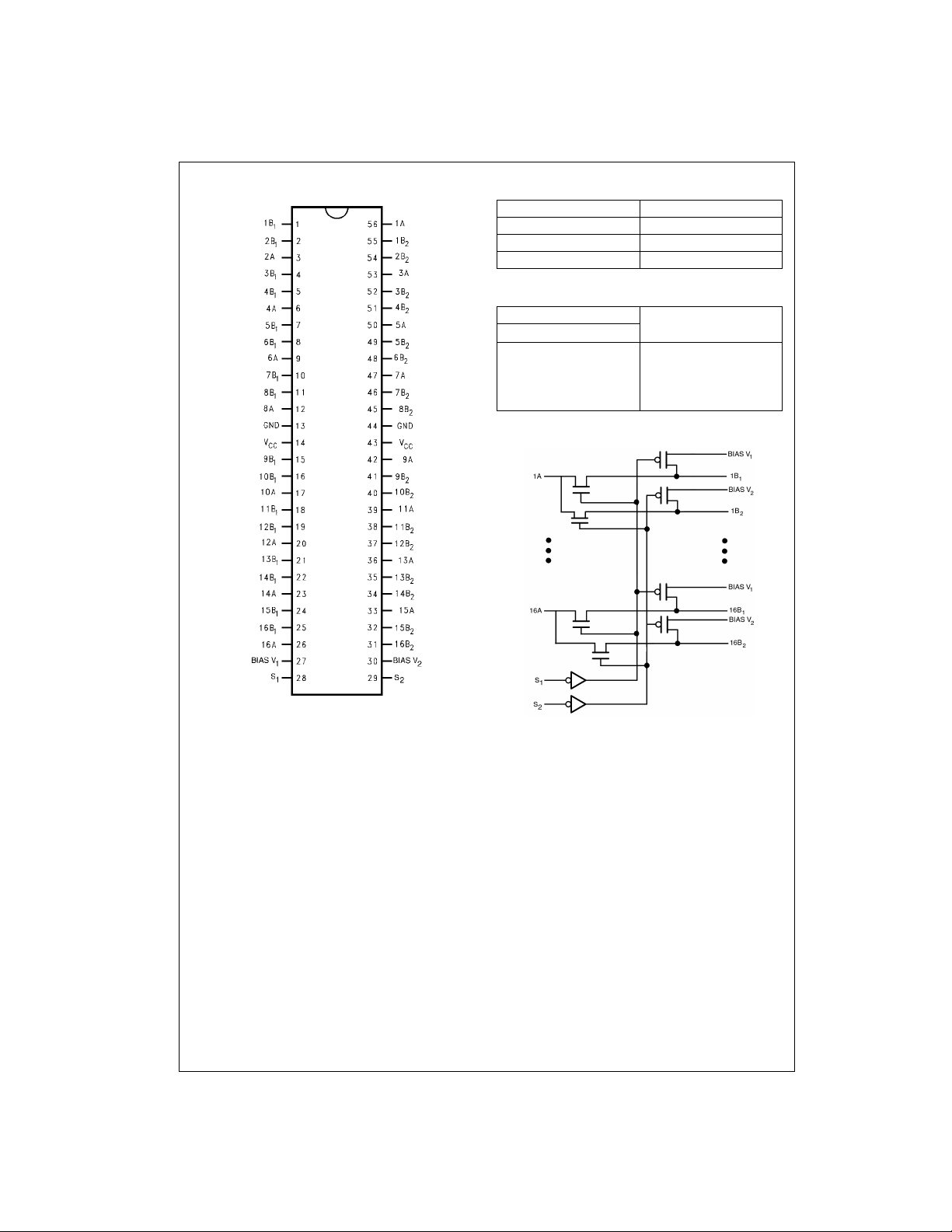

Connection Diagram Pin Descriptions

Pin Name Description

S

, S

1

FSTU32160

ABus A

B

, B

1

Truth Table

Inputs

S

1

LH x A = x B

HL x A = x B

LLx A = x B1 and x B

H H x B1, x B2 = BiasV

Logic Diagram

2

2

S

2

Select Inputs

Bus B

Function

1

2

2

www.fairchildsemi.com 2

Loading...

Loading...