FSFM260N / FSFM261N / FSFM300N

Green-Mode Fairchild Power Switch (FPS™)

FSFM260N / FSFM261N / FSFM300N — Green-Mode Farichild Power Switch (FPS™)

August 2009

Features

! Internal Avalanche-Rugged SenseFET

! Advanced Burst-Mode Operation Consumes Under

1W at 240VAC and 0.5W Load

! Precision Fixed Operating Frequency: 67kHz

! Internal Startup Circuit

! Over-Voltage Protection (OVP)

! Overload Protection (OLP)

! Internal Thermal Shutdown Function (TSD)

! Abnormal Over-Current Protection (AOCP)

! Auto-Restart Mode

! Under-Voltage Lockout (UVLO) with Hysteresis

! Low Operating Current: 2.5mA

! Built-in Soft-Start: 15ms

Applications

! Power Supply for LCD TV and Monitor, VCR, SVR,

STB, DVD, and DVD Recorder

! Adapter

Related Resources

Visit: http://www.fairchildsemi.com/apnotes/ for:

! AN-4134: Design Guidelines for Offline Forward

Converters Using Fairchild Power Switch (FPS

! AN-4137: Design Guidelines for Offline Flyback

Converters Using Fairchild Power Switch (FPS

! AN-4140: Transformer Design Consideration for

Offline Flyback Converters Using Fairchild Power

Switch (FPS

! AN-4141: Troubleshooting and Design Tips for

Fairchild Power Switch (FPS

! AN-4145: Electromagnetic Compatibility for Power

™

)

™

) Flyback Applications

Converters

! AN-4147: Design Guidelines for RCD Snubber of

Flyback Converters

! AN-4148: Audible Noise Reduction Techniques for

Fairchild Power Switch (FPS

™)

Applications

™

)

™

)

Description

The FSFM260/261/300 is an integrated Pulse Width

Modulator (PWM) and SenseFET specifically designed

for high-performance offline Switch Mode Power

Supplies (SMPS) with minimal external components.

This device is an integrated high-voltage powerswitching regulator that combines an avalanche-rugged

SenseFET with a current-mode PWM control block. The

PWM controller includes an integrated fixed-frequency

oscillator, under-voltage lockout, leading-edge blanking

(LEB), optimized gate driver, internal soft-start,

temperature-compensated precise-current sources for a

loop compensation, and self-protection circuitry.

Compared with discrete MOSFET and PWM controller

solutions, it can reduce total cost, component count, size,

and weight while simultaneously increasing efficiency,

productivity, and system reliability. This device is a basic

platform for cost-effective designs of flyback converters.

© 2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSFM260N / FSFM261N / FSFM300N • Rev. 1.0.1

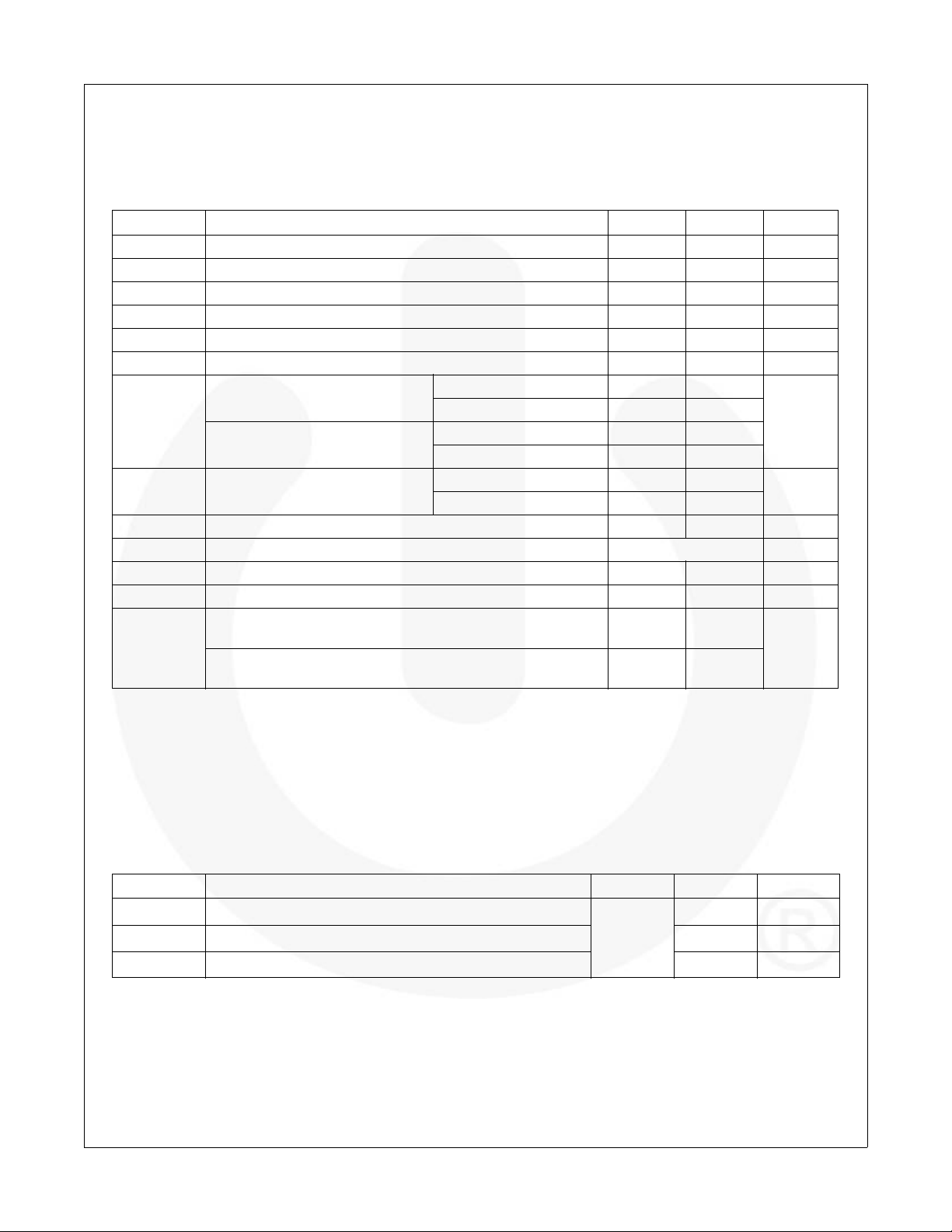

Ordering Information

Maximum Output Power

Product

Number

FSFM260N 8-DIP -25 to +85°C 1.5A 2.6Ω 23W 35W 17W 26W

FSFM261N 8-DIP -25 to +85°C 1.5A 2.7Ω 23W 35W 17W 26W

FSFM300N 8-DIP -25 to +85°C 1.6A 2.2Ω 26W 40W 20W 30W

PKG.

(5)

Operating

Temp.

Current

Limit

R

DS(ON)

Max.

230VAC±15%

Adapter

(3)

(2)

Open

Frame

(4)

Adapter

Notes:

1. The junction temperature can limit the maximum output power.

2. 230V

or 100/115VAC with doubler.

AC

3. Typical continuous power in a non-ventilated enclosed adapter measured at 50°C ambient temperature.

4. Maximum practical continuous power in an open-frame design at 50°C ambient.

5. Eco status for all the FSFM260N, FSFM261N and FSFM300NS is RoHS.

For Fairchild’s definition of Eco Status, please visit:

http://www.fairchildsemi.com/company/green/rohs_green.html. Eco Status: RoHS.

(1)

85-265V

(3)

AC

Open

Frame

Replaces

Devices

(4)

FSDM0465RS

FSQ0465RS

FSFM260N / FSFM261N / FSFM300N — Green-Mode Farichild Power Switch (FPS™)

© 2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSFM260N / FSFM261N / FSFM300N • Rev. 1.0.1 2

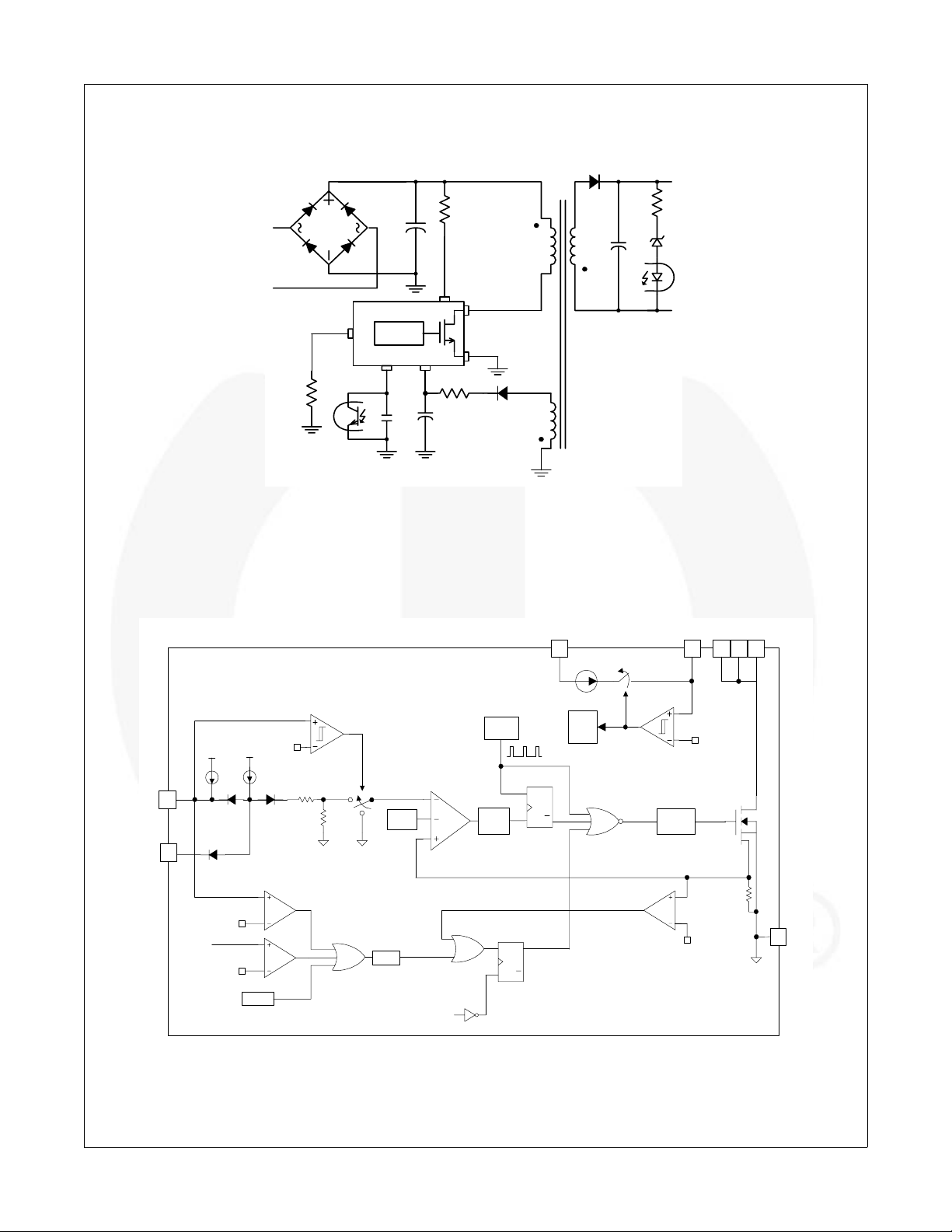

Application Diagram

AC

IN

V

STR

Drain

I

LIM

PWM

GND

FB

V

CC

Figure 1. Typical Flyback Application

V

FSFM260 Rev. 00

FSFM260N / FSFM261N / FSFM300N — Green-Mode Farichild Power Switch (FPS™)

O

Internal Block Diagram

V

BURL/VBURH

V

V

CC

CC

I

FB

I

3

LIM

4

delayIFB

V

SD

V

CC

V

OVP

2.5R

TSD

R

Normal

Burst

LPF

SoftStart

PWM

VCC good

OSC

LEB

250ns

SQQ

R

V

V

str

V

ref

good

V

CC

S

Q

QR

Gate

driver

CC

2 85

V

CC

8V/12V

Drain

76

1

V

OCP

GND

FSFM260 Rev.00

Figure 2. Internal Block Diagram

© 2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSFM260N / FSFM261N / FSFM300N • Rev. 1.0.1 3

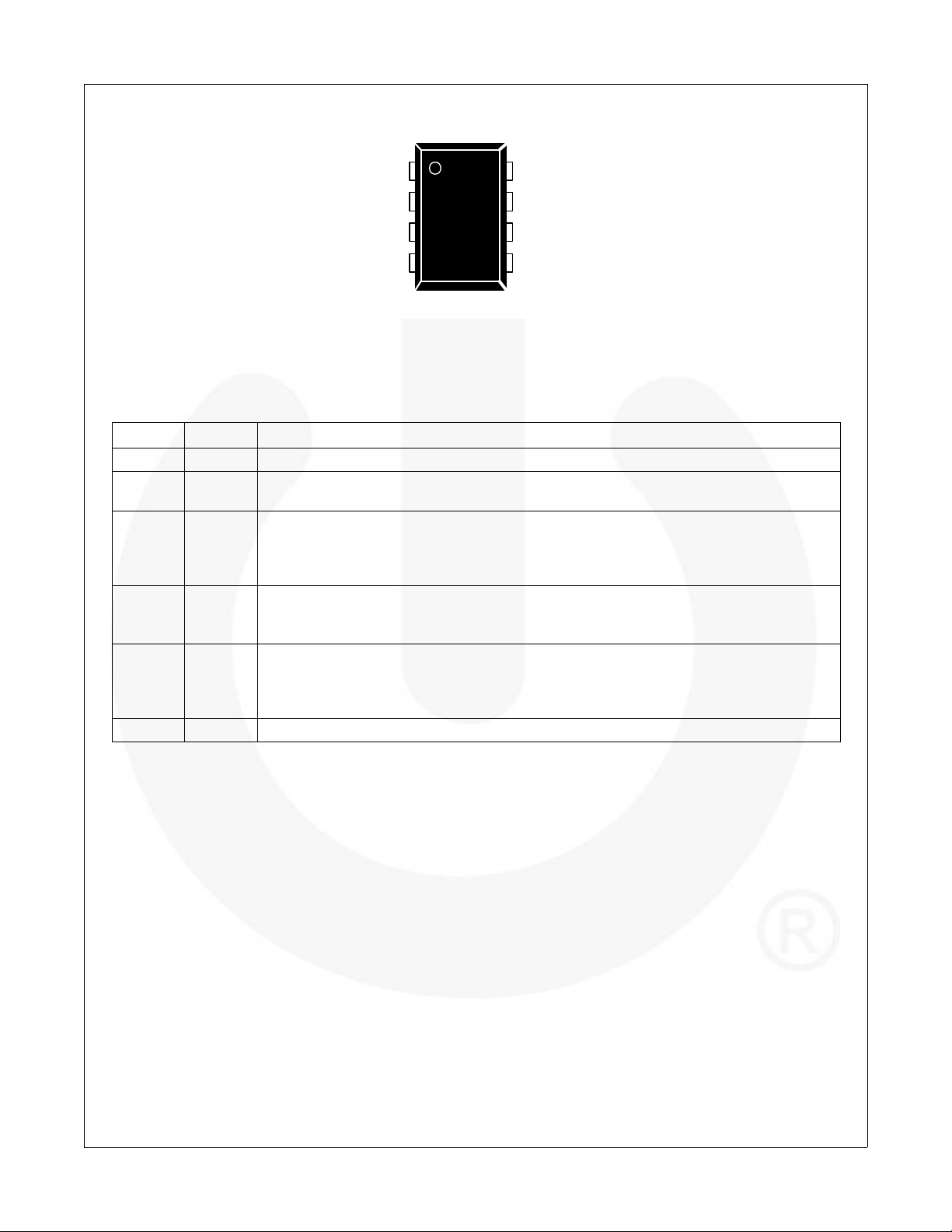

Pin Configuration

FSFM260N / FSFM261N / FSFM300N — Green-Mode Farichild Power Switch (FPS™)

GND

V

FB

I

LIM

CC

FSFM260 Rev.1.0.0

8-DIP

Drain

Drain

Drain

V

STR

Figure 3. Pin Configuration (Top View)

Pin Definitions

Pin # Name Description

1GNDGround. This pin is the control ground and the SenseFET source.

2V

3FB

4I

5V

LIM

STR

6,7,8 Drain SenseFET Drain. High-voltage power SenseFET drain connection.

Power Supply. This pin is the positive supply input, providing internal operating current for

CC

both startup and steady-state operation.

Feedback. This pin is internally connected to the inverting input of the PWM comparator. The

collector of an opto-coupler is typically tied to this pin. For stable operation, a capacitor should

be placed between this pin and GND. If the voltage of this pin reaches 6V, the overload protection triggers, which shuts down the FPS.

Peak Current Limit. Adjusts the peak current limit of the Sense FET. The feedback 0.9mA

current source is diverted to the parallel combination of an internal 2.8kΩ resistor and any external resistor to GND on this pin to determine the peak current limit.

Startup. This pin is connected directly, or through a resistor, to the high-voltage DC link. At

startup, the internal high-voltage current source supplies internal bias and charges the external capacitor connected to the VCC pin. Once VCC reaches 12V, the internal current source is

disabled. It is not recommended to connect V

and drain together.

STR

© 2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSFM260N / FSFM261N / FSFM300N • Rev. 1.0.1 4

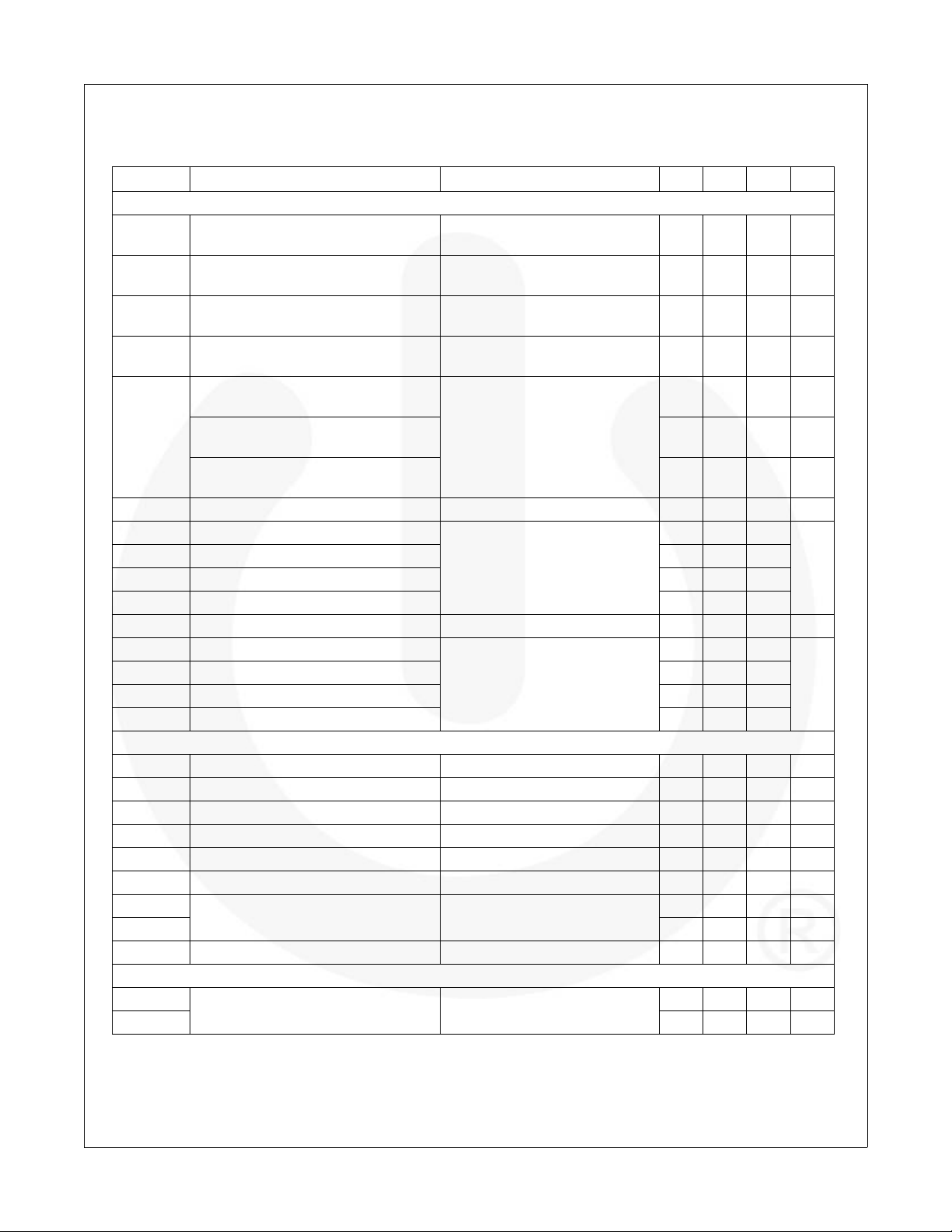

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The

absolute maximum ratings are stress ratings only. T

Symbol Parameter Min. Max. Unit

V

STR

V

DS

V

DS

V

CC

V

FB

I

DM

I

D

E

AS

P

T

T

T

STG

ESD

D

J

A

V

Pin Voltage 650 V

STR

1 Drain Pin Voltage of FSFM260N and FSFM300N 650 V

2 Drain Pin Voltage of FSFM261N 700 V

Supply Voltage 21 V

Feedback Voltage Range

(6)

Drain Current Pulsed 9.6 A

Continuous Drain Current of

FSFM260 and FSFM261

Continuous Drain Current of

FSFM300

(7)

(7)

Single Pulsed Avalanche Energy

Total Power Dissipation (TC=25°C) 1.5 W

Operating Junction Temperature Internally Limited °C

Operating Ambient Temperature -25 +85 °C

Storage Temperature -55 +150 °C

Electrostatic Discharge Capability

Human Body Model, JESD22-A114

Electrostatic Discharge Capability,

Charged Device Model, JESD22-C110

= 25°C, unless otherwise specified.

A

-0.3 8.0 V

TC = 25°C 2.2

= 100°C 1.4

T

C

TC = 25°C 2.8

= 100°C 1.7

T

C

FSFM260 and FSFM261 120

(8)

FSFM300 190

2.0

2.0

A

mJ

kV

FSFM260N / FSFM261N / FSFM300N — Green-Mode Farichild Power Switch (FPS™)

Notes:

6. VFB is internally clamped and its maximum clamping current capability is 100μA.

7. Repetitive rating: pulse-width limited by maximum junction temperature.

8. L=14mH, starting T

=25°C.

J

Thermal Impedance

TA = 25°C unless otherwise specified.

Symbol Parameter Package Value Unit

(11)

(10)

(9)

8-DIP

80

20

35

θ

JA

θ

JC

Ψ

JT

Junction-to-Ambient Thermal Resistance

Junction-to-Case Thermal Resistance

Junction-to-Top Thermal Resistance

Notes:

9. Free standing with no heat-sink under natural convection.

10. Infinite cooling condition - refer to the SEMI G30-88.

11. Measured on the package top surface.

© 2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSFM260N / FSFM261N / FSFM300N • Rev. 1.0.1 5

°

C/W

°

C/W

°

C/W

FSFM260N / FSFM261N / FSFM300N — Green-Mode Farichild Power Switch (FPS™)

Electrical Characteristics

TA = 25°C unless otherwise specified.

Symbol Parameter Condition Min. Typ. Max. Unit

SenseFET Section

BV

DSS

BV

DSS

I

DSS1

I

DSS2

R

DS(ON)

C

OSS

t

d(on)

t

t

d(off)

t

C

OSS

t

d(on)

t

t

d(off)

t

Control Section

f

OSC

Δf

STABLE

Δf

OSC

I

FB

D

MAX

D

MIN

V

START

V

STOP

t

S/S

Burst Mode Section

V

BURH

V

BURL

Drain Source Breakdown Voltage of

1

FSFM260 and FSFM300

Drain Source Breakdown Voltage of

2

FSFM261

Zero Gate Voltage Drain Current1

Zero Gate Voltage Drain Current2

Static Drain Source on Resistance of

FSFM260

Static Drain Source on Resistance of

FSFM261

Static Drain Source on Resistance of

FSFM300

(12)

(12)

(12)

VCC = 0V, ID = 250µA 650 V

VCC = 0V, ID = 250µA 700 V

= 650V, VGS = 0V,

V

DS

= 25°C

T

C

V

= 520V, VGS = 0V,

DS

TC = 125°C

2.20 2.60 Ω

VGS = 10V, ID = 2.5A

2.30 2.70 Ω

1.76 2.20 Ω

Output Capacitance of FSFM260/261 VGS = 0V, VDS = 25V, f = 1MHz 60 pF

Turn-On Delay Time of FSFM260/261

Rise Time of FSFM260/261 20

r

Turn-Off Delay Time of FSFM260/261 30

Fall Time of FSFM260/261 16

f

VDD = 325V, ID = 5A

12

Output Capacitance of FSFM300 VGS = 0V, VDS = 25V, f = 1MHz 75 pF

Turn-On Delay Time of FSFM300

Rise Time of FSFM300 26

r

Turn-Off Delay Time of FSFM300 32

Fall Time of FSFM300 25

f

VDD = 325V, ID = 5A

14

Switching Frequency VFB = 3V 61 67 73 kHz

Switching Frequency Stability 13V ≤ VCC ≤ 18V 0 1 3 %

Switching Frequency Variation

(13)

-25°C ≤ TA ≤ 85°C 0 ±5 ±10 %

Feedback Source Current VFB = GND 0.7 0.9 1.1 mA

Maximum Duty Cycle 71 77 83 %

Minimum Duty Cycle 0 %

UVLO Threshold Voltage VFB = GND

11 12 13 V

789V

Internal Soft-Start Time VFB = 3V 10 15 20 ms

Burst Mode Voltages VCC = 14V

0.50 V

0.35 V

250 µA

250 µA

ns

ns

© 2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FSFM260N / FSFM261N / FSFM300N • Rev. 1.0.1 6

Loading...

Loading...