Fairchild FAN7888 service manual

FAN7888

3 Half-Bridge Gate-Drive IC

FAN7888 — 3 Half-Bridge Gate-Drive IC

May 2008

Features

Floating Channel for Bootstrap Operation to +200V

Typically 350mA/650mA Sourcing/Sinking Current

Driving Capability for All Channels

3 Half-Bridge Gate Driver

Extended Allowable Negative V

Signal Propagation at V

Matched Propagation Delay Time Maximum 50ns

3.3V and 5V Input Logic Compatible

Built-in Shoot-Through Prevention Circuit for All

Channels with Typically 270ns Dead Time

Built-in Common Mode dv/dt Noise Canceling Circuit

Built-in UVLO Functions for All Channels

BS

Swing to -9.8V for

S

=15V

Applications

3-Phase Motor Inverter Driver

Description

The FAN7888 is a monolithic three half-bridge gate-drive

IC designed for high-voltage, high-speed driving MOSFETs and IGBTs operating up to +200V.

Fairchild’s high-voltage process and common-mode

noise canceling technique provide stable operation of

high-side drivers under high-dv/dt noise circumstances.

An advanced level-shift circuit allows high-side gate

driver operation up to V

The UVLO circuits prevent malfunction when VDD and

VBS are lower than the specified threshold voltage.

Output drivers typically source/sink 350mA/650mA,

respectively, which is suitable for three-phase half-bridge

applications in motor drive systems.

= -9.8V (typical) for VBS =15V.

S

20-SOIC

Ordering Information

Part Number Package Operating Temperature Range Packing Method

FAN7888M

FAN7888MX Tape & Reel

All packages are lead free per JEDEC: J-STD-020B standard.

© 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7888 • Rev. 1.0.0

20-SOIC -40°C to +125°C

Tube

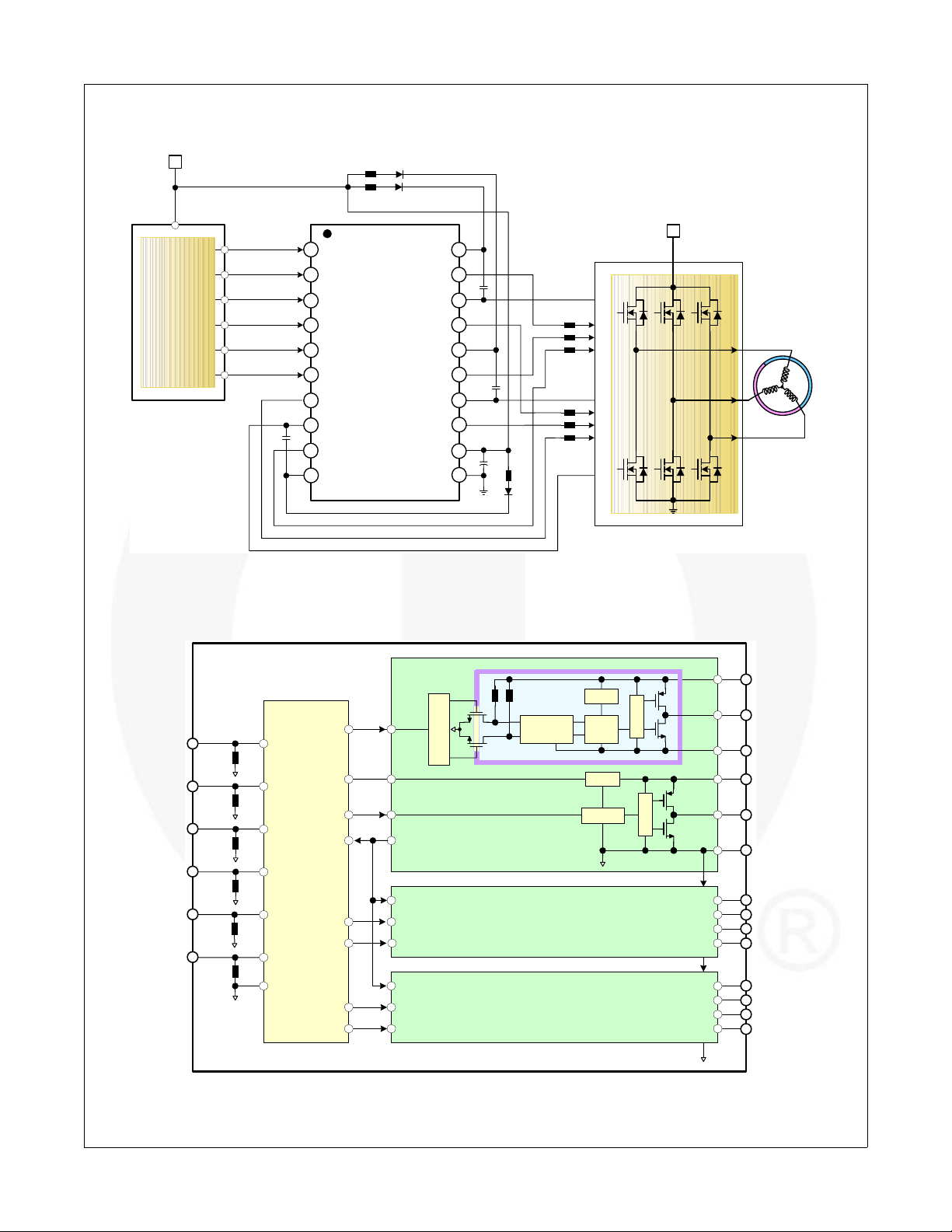

Typical Application Circuit

+15V

FAN7888 — 3 Half-Bridge Gate-Drive IC

Up to 200V

UU

UL

3-Phase

BLDC Motor

Controller

VU

VL

WU

WL

Internal Block Diagram

HIN1

1

HIN1

2

LIN1

3

HIN2

4

LIN2

5

HIN3

6

LIN3

7

LO3

8

V

S3

9

HO3

10

V

B3

FAN7888

HO1

LO1

HO2

LO2

GND

20

V

B1

19

V

S1

18

17

V

16

B2

15

V

14

S2

13

V

12

DD

11

V

S1

Q1

Q3

Q5

V

S2

Q4

Q6

Q2

V

S3

Figure 1. 3-Phase BLDC Motor Drive Application

UVLO

R

S

R

UHIN

GENERATOR

PULSE

NOISE

CANCELLER

Q1 Q3 Q5

V

S1

3-Phase Inverter

V

S2

Q4 Q6 Q2

DRIVER

Q

I

U

I

V

I

W

V

S3

FAN7888 Rev.00

V

B1

HO1

V

S1

U

V

W

HIN2

HIN3

LIN1

LIN2

LIN3

SCHMITT

TRIGGER INPUT

SHOOT-THOUGH

PREVENTION

CONTROL LOGIC

VDD_UVLO

ULIN

VDD

U Phase Driver

V

DD

VHIN

VLIN

V

DD

WHIN

WLIN

UVLO

DRIVER

DELAY

V Phase Driver

W Phase Driver

V

LO1

GND

V

HO2

V

LO2

V

HO3

V

LO3

DD

B2

S2

B3

S3

FAN7888 Rev.01

Figure 2. Functional Block Diagram

© 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7888 • Rev.1.0.0 2

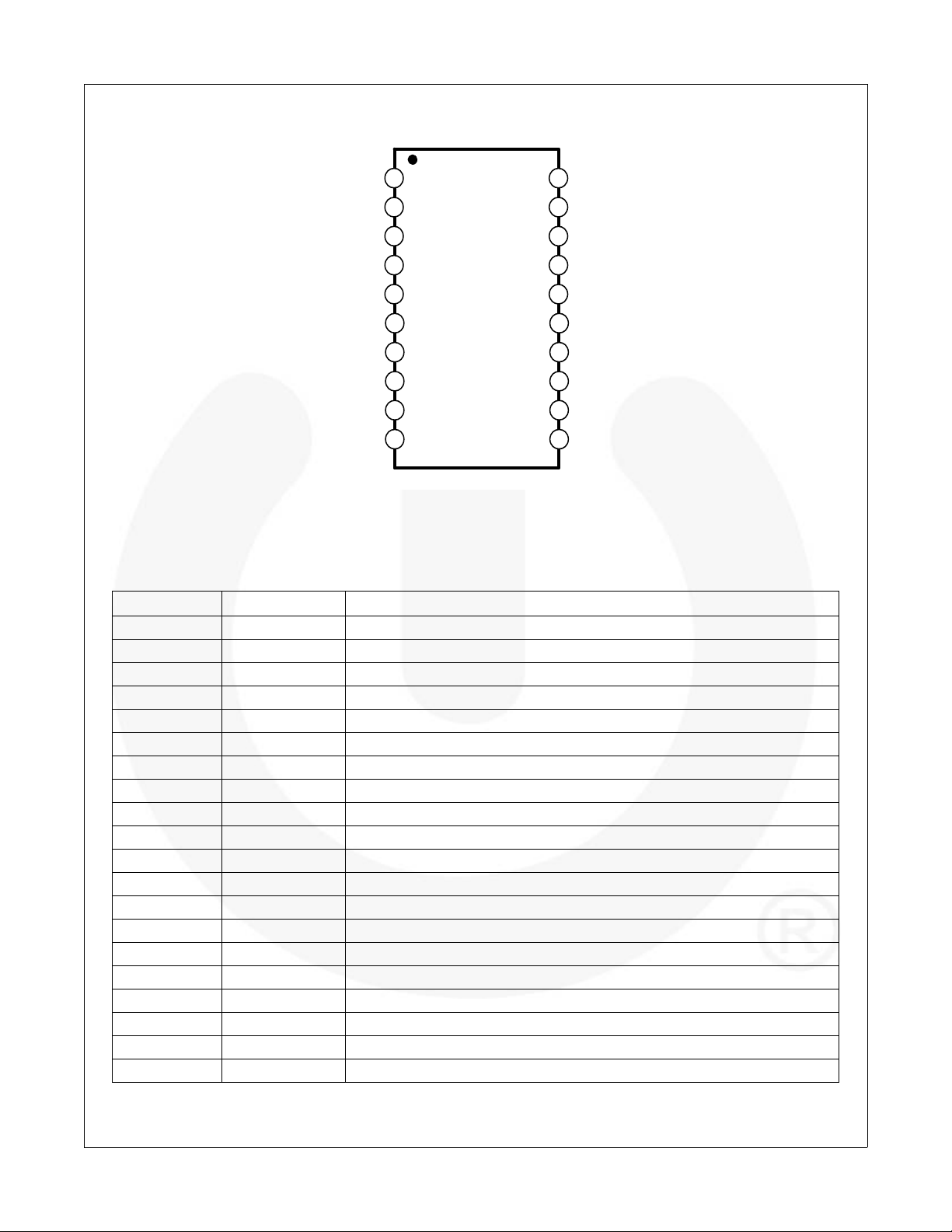

Pin Configuration

FAN7888 — 3 Half-Bridge Gate-Drive IC

1

HIN1

LIN1

2

HIN2

LIN2

HIN3

LIN3

LO3

V

HO3

V

3

4

5

6

7

8

S3

9

10

B3

FAN7888

FAN7888 Rev.00

Figure 3. Pin Configuration (Top View)

Pin Definitions

Pin # Name Description

1 HIN1 Logic input 1 for high-side gate 1 driver

2 LIN1 Logic input 1 for low-side gate 1 driver

3 HIN2 Logic input 2 for high-side gate 2 driver

4 LIN2 Logic input 2 for low-side gate 2 driver

5 HIN3 Logic input 3 for high-side gate 3 driver

6 LIN3 Logic input 3 for low-side gate 3 driver

7 LO3 Low-side gate driver 3 output

8V

S3

9 HO3 High-side driver 3 gate driver output

10 V

B3

11 GND Ground

12 V

DD

13 LO2 Low-side gate driver 2 output

14 V

S2

15 HO2 High-side driver 2 gate driver output

16 V

B2

17 LO1 Low-side gate driver 1 output

18 V

S1

19 HO1 High-side driver 1 gate driver output

20 V

B1

High-side driver 3 floating supply offset voltage

High-side driver 3 floating supply voltage

Logic and all low-side gate drivers power supply voltage

High-side driver 2 floating supply offset voltage

High-side driver 2 floating supply voltage

High-side driver 1 floating supply offset voltage

High-side driver 1 floating supply voltage

20

V

B1

19

HO1

V

18

S1

LO1

17

V

16

B2

HO2

15

V

14

S2

LO2

13

V

12

DD

GND

11

© 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7888 • Rev.1.0.0 3

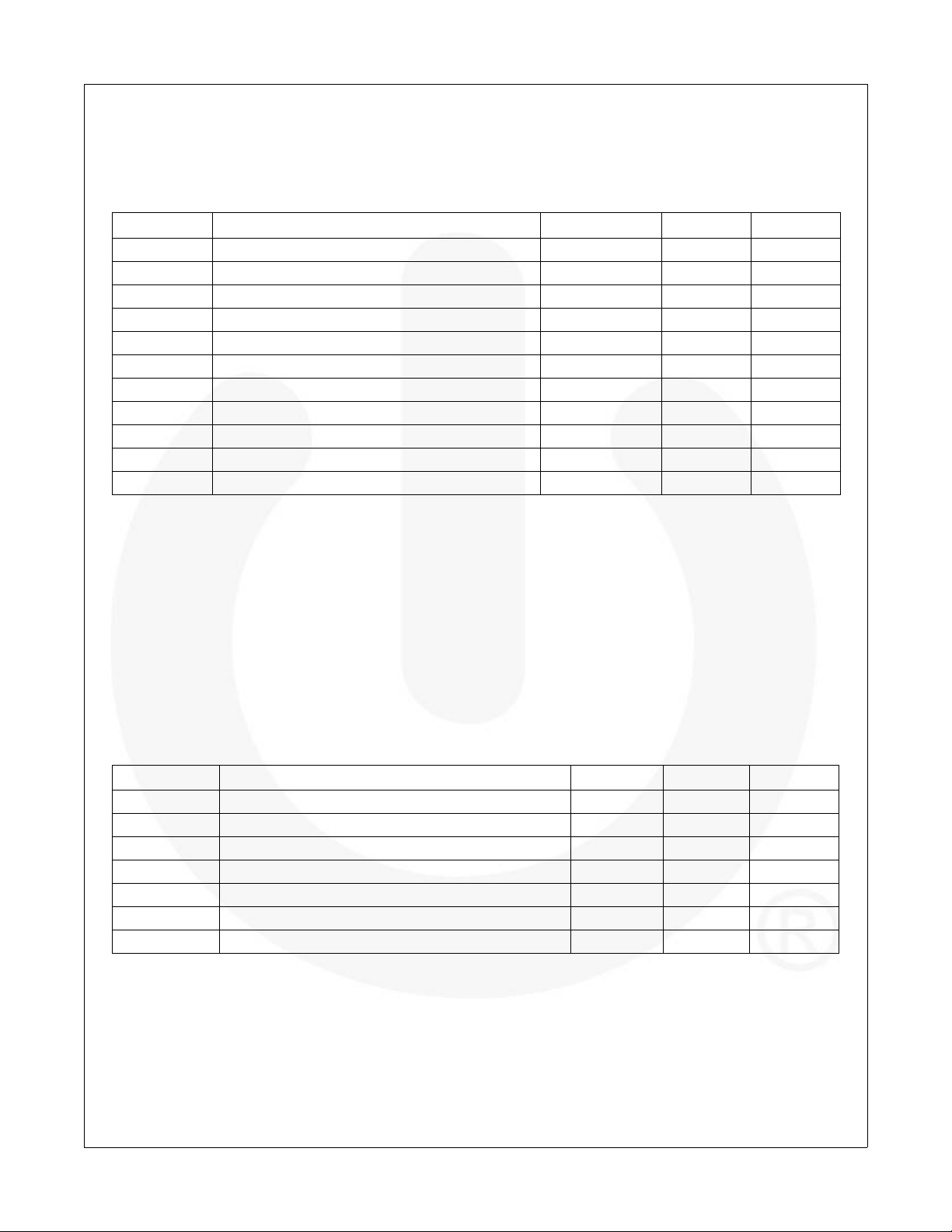

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating cond itions may affect device reliability. The

absolute maximum ratings are stress ratings only. T

Symbol Parameter Min. Max. Unit

V

B

V

S

V

HO1,2,3

V

DD

V

LO1,2,3

V

IN

/dt Allowable Offset Voltage Slew Rate 50 V/ns

dV

S

P

D

θ

JA

T

J

T

S

Notes:

1. Mounted on 76.2 x 114.3 x 1.6mm PCB (FR-4 glass epoxy material).

2. Refer to the following standards:

JESD51-2: Integral circuits thermal test method environmental conditions - natural convection

JESD51-3: Low effective thermal conductivity test board for leaded surface-mount packages.

3. Do not exceed P

High-side Floating Supply Voltage of V

High-side Floating Supply Offset Voltage of V

High-side Floating Output Voltage V

Low-side and Logic-fixed Supply Voltage -0.3 25.0 V

Low-side Output Voltage -0.3 VDD+0.3 V

Logic Input Voltage (HIN1,2,3 and LIN1,2,3) -0.3 VDD+0.3 V

Power Dissipation

(1)(2)(3)

Thermal Resistance, Junction-to-ambient 80 °C/W

Junction Temperature +150 °C

Storage Temperature -55 +150 °C

under any circumstances.

D

=25°C, unless otherwise specified.

A

B1,2,3

S1,2,3

-0.3 225.0 V

V

-25 V

B1,2,3

-0.3 V

S1,2,3

+0.3 V

B1,2,3

+0.3 V

B1,2,3

1.8 W

FAN7888 — 3 Half-Bridge Gate-Drive IC

Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended

operating conditions are specified to ensure optimal perfor mance to the datasheet specifications. Fairchild does not

recommend exceeding them or designing to Absolute Maximum Ratings.

Symbol Parameter Min. Max. Unit

V

B1,2,3

V

S1,2,3

V

V

HO1,2,3

V

LO1,2,3

V

T

DD

IN

A

High-side Floating Supply Voltage V

High-side Floating Supply Offset Voltage 6-V

S1,2,3

+10 V

DD

+20 V

S1,2,3

200 V

Supply Voltage 10 20 V

High-side Output Voltage V

Low-side Output Voltage GND V

Logic Input Voltage (HIN1,2,3 and LIN1,2,3) GND V

V

S1,2,3

B1,2,3

DD

DD

V

V

V

Ambient Temperature -40 +1 2 5 °C

© 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7888 • Rev.1.0.0 4

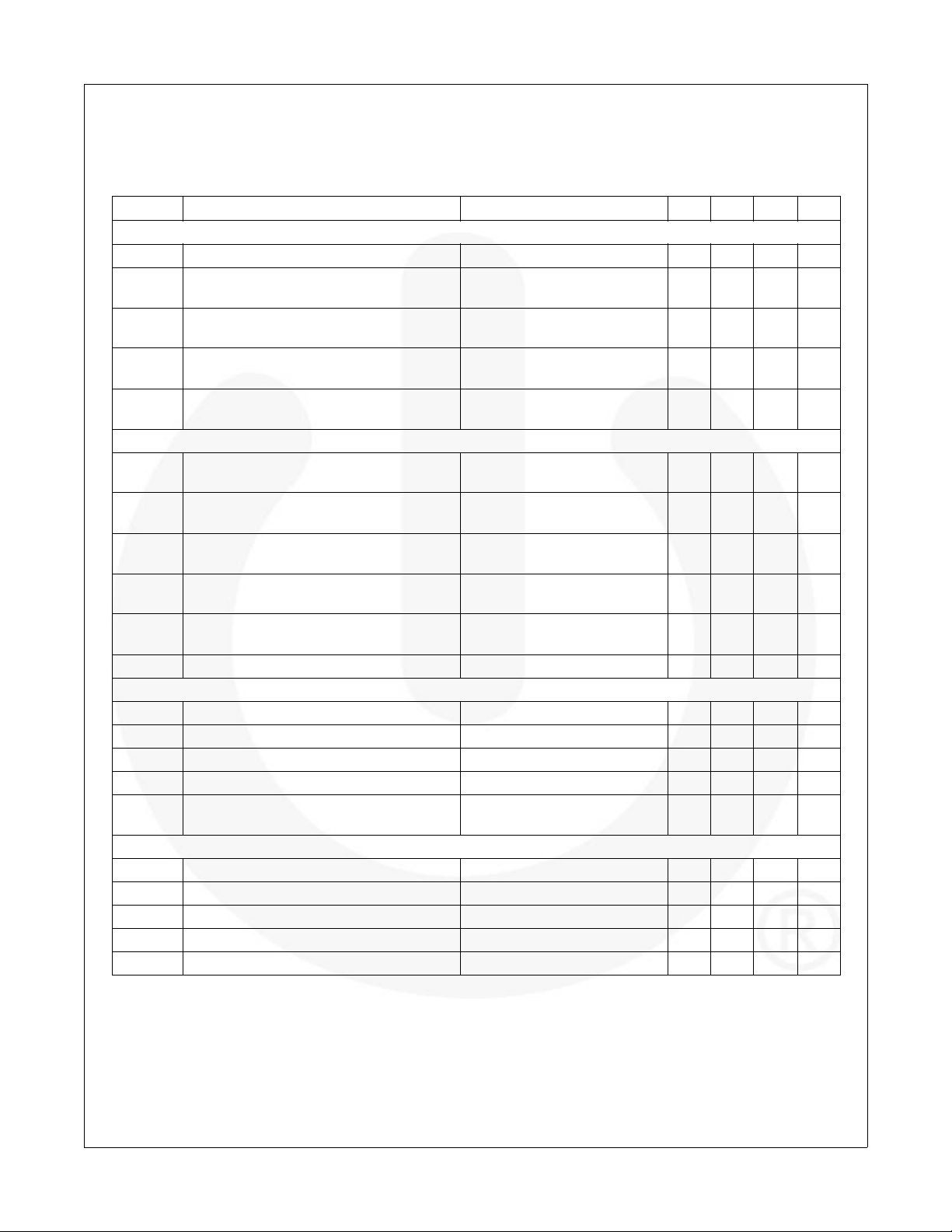

Electrical Characteristics

V

BIAS (VDD

GND. The VO and IO parameters are referenced to GND and V

LO1,2,3 and HO1,2,3.

Symbol Characteristics Condition Min. Typ. Max. Unit

LOW SIDE POWER SUPPLY SECTION

I

PDD1,2,3

V

V

V

DDHYS

BOOTSTRAPPED POWER SUPPLY SECTION

I

QBS1,2,3

I

PBS1,2,3

V

BSUV+

V

V

BSHYS

GATE DRIVER OUTPUT SECTION

LOGIC INPUT SECTION (HIN, LIN)

Note:

4. This parameter is guaranteed by design.

I

QDD

DDUV+

DDUV-

BSUV-

I

LK

V

OH

V

OL

I

O+

I

O-

V

S

V

IH

V

IL

I

IN+

I

IN-

R

IN

, V

Quiescent VDD Supply Current V

Operating VDD Supply Current for each

Channel

V

Threshold

V

Threshold

V

Hysteresis

Quiescent VBS Supply Current for each

Channel

Operating VBS Supply Current for each

Channel

VBS Supply Under-Voltage Positive-going

Threshold

VBS Supply Under-Voltage Negative-going

Threshold

VBS Supply Under-Voltage Lockout

Hysteresis

Offset Supply Leakage Current V

High-level Output Voltage, V

Low-level Output Voltage, V

Output HIGH Short-circuit Pulsed Current

Output LOW Short-circuit Pulsed Current

Allowable Negative VS Pin Voltage for IN

Signal Propagation to H

) = 15.0V, TA = 25°C, unless otherwise specified. The VIN and IIN parameters are referenced to

BS1,2,3

Supply Under-Voltage Positive-going

DD

Supply Under-Voltage Negative-going

DD

Supply Under-Voltage Lockout

DD

BIAS-VO

O

O

LIN1,2,3

f

LIN1,2,3

=Sweep, VBS=15V 7.2 8.2 9.0 V

V

DD

V

=Sweep, VBS=15V 6.8 7.8 8.5 V

DD

=Sweep, VBS=15V 0.4 V

V

DD

V

HIN1,2,3

f

HIN1,2,3

=15V, VBS=Sweep 7.2 8.2 9.0 V

V

DD

=15V, VBS=Sweep 6.8 7.8 8.5 V

V

DD

V

=15V, VBS=Sweep 0.4 V

DD

B1,2,3=VS1.2.3

IO=20mA 1.0 V

IO=20mA 0.6 V

(4)

VO=0V, VIN=5V with PW<10µs 250 350 mA

(4)

VO=15V, VIN=0V with PW<10µs 500 650 mA

and are applicable to the respective outputs

S1,2,3

=0V or 5V 160 350 µA

=20kHz, rms Value 500 900 µA

=0V or 5V 50 120 µA

=20kHz, rms Value 400 800 µA

=200V 10 µA

-9.8 -7.0 V

Logic "1" Input Voltage 2.5 V

Logic "0" Input Voltage 1.0 V

Logic "1" Input Bias Current VIN=5V 25 50 µA

Logic "0" Input Bias Current

(4)

VIN=0V 2.0 µA

Input Pull-down Resistance 100 200 300 KΩ

FAN7888 — 3 Half-Bridge Gate-Drive IC

© 2008 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN7888 • Rev.1.0.0 5

Loading...

Loading...