Fairchild FAN6300, FAN6300A, FAN6300H service manual

www.fairchildsemi.com

AN-6300

FAN6300 / FA N6300A / FAN6300H

Highly Integrated Quasi-Resona nt PWM Controller

Abstract

This application note describes a detailed design strategy for

higher-power conversion efficiency and better EMI using a

Quasi-Resonant PWM controller compared to the

conventional, hard-switched converter with a fixed

switching frequency. Based on the proposed design

guideline, a design example with detailed parameters

demonstrates the performance of the controller.

Introduction

The highly integrated FAN6300/A/H PWM controller

provides several features to enhance the performance of

flyback converters. FAN6300/A are applied on QuasiResonant flyback converter where maximum operating

frequency is below 100kHz and FAN6300H is suitable for

high frequency operation that is around 190kHz. A built-in

High Voltage (HV) startup circuit can provide more startup

current to reduce the startup time of the controller. Once the

VDD voltage exceeds the turn-on threshold voltage, the HV

startup function is disabled immediately to reduce power

consumption. An internal valley voltage detector ensures

power system operates in quasi-resonant operation in wide-

range line voltage and reduces switching loss to minimize

switching voltage on drain of the power MOSFET.

To minimize standby power consumption and improve lightload efficiency, a proprietary green-mode function provides

off-time modulation to decrease switching frequency and

perform extended valley voltage switching to keep to a

minimum switching voltage.

FAN6300/A/H controller provides many protection

functions. Pulse-by-pulse current limiting ensures the fixed

peak current limit level, even when short-circuit occurs.

Once an open-circuit failure occurs in the feedback loop, the

internal protection circuit disables PWM output

immediately. As long as V

threshold voltage, the controller also disables the PWM

output. The gate output is clamped at 18V to protect the

power MOS from high gate-source voltage conditions. The

minimum t

being too high. If the DET pin reaches OVP level, internal

OTP is triggered, and the power system enters latch-mode

until AC power is removed.

time limit prevents the system frequency from

OFF

drops below the turn-off

DD

© 2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

Rev. 1.0.2 • 5/21/10

AN-6300 APPLICATION NOTE

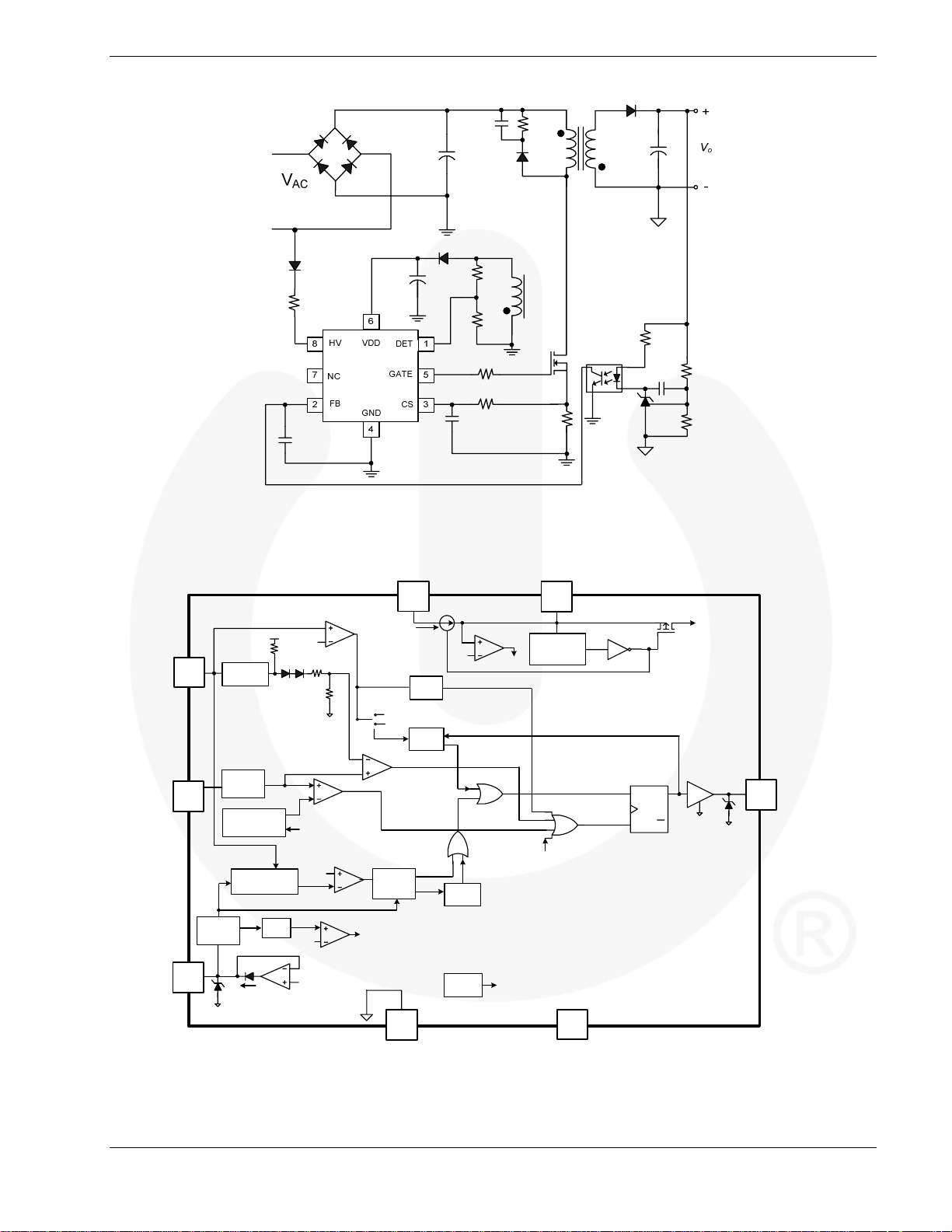

Figure 1. Basic Quasi-Resonant Converter

FB

CS

DET

2

3

1

Soft-Start

5ms

Blanking

Circuit

Over-Power

Compensation

(3µs/13µs)

for H version

t

OFF

Blanking

(4µs)

(1.5µs) for H version

5V

t

OFF-MIN

(8µs/38µs)

I

DET

S/H

V

4.2V

V

DET

2.5V

2R

I

DET

DET

0.3V

0.3V

R

PWM

Current Limit

DET OVP

Latched

2ms

30µs

Valley

Detector

HV

8

I

HV

Timer

55ms

Starter

1st

Valley

27V

FB OLP

t

OFF-MIN

+9µs

Internal

OTP

OVP

t

OFF-MIN

for H version

Latched

+5µs

Latched

VDD

6

Two Steps

UVLO

16V/10V/8V

Latched

Internal

Bias

SET

S

CLR

R

DRV

Q

Q

18V

5

GATE

4

GND

7

NC

Figure 2. Functional Block Diagram

© 2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

Rev. 1.0.2 • 5/21/10 2

AN-6300 APPLICATION NOTE

Design Procedure for the Primary-Side Inductance of Transformer

In this section, a design procedure is described using the

schematic of Figure 1 as a reference.

[a] Define the System Specifications

Line voltage range (V

Maximum output power (P

Output voltage (V

o

in,min

and V

).

o

in,max

)

) and maximum output current (Io)

Estimated efficiency (η)

The power conversion efficiency must be estimated to

calculate the maximum input power. In the case of NB

adaptor applications, the typical efficiency is 85%~90%.

With the estimated efficiency, the maximum input power

is given by:

P

P=

in

o

η

(1)

designed to turn on the MOSFET when V

minimum voltage V

-n(Vo+Vd).

in

n:1

+

V

in

-

n(Vo+Vd)

C

oss

-

+

+-

+

V

ds

-

V

d

reaches its

ds

+

V

o

-

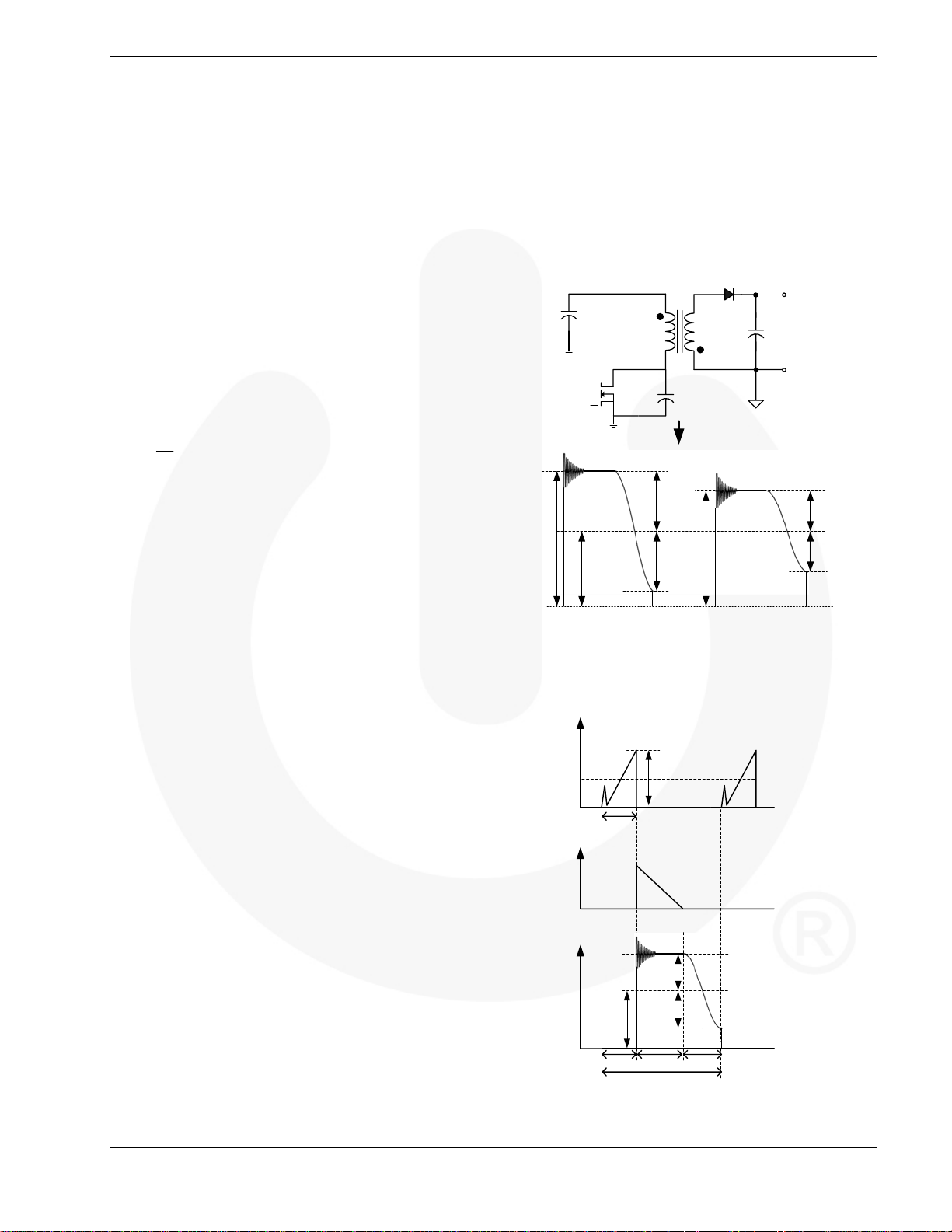

[b] Estimate Reflected Output Voltage

Figure 3 shows the typical waveforms of the drain voltage

of quasi-resonant flyback converter. When the MOSFET

is turned off, the DC link voltage (V

output voltage (V

Schottky diode (V

) and the forward voltage drop of the

o

) reflected to the primary, are imposed

d

on the MOSFET. The maximum nominal voltage across

the MOSFET (V

VV+nV+V=()

ds,max in,max o d

ds

) is:

where the turns ratio of primary to secondary side of

transformer is defined as n and V

), together with the

o

is as specified in

ds

(2)

V

ds

V

in,max

0V

n(Vo+Vd)

n(Vo+Vd)

n(V

)

n(V

o+Vd

o+Vd

)

V

ds

Figure 3. Typical Waveform of MOSFET Drain Voltage

for QR Operation

I

ds

Equation 2.

pk

I

By increasing n, the capacitive switching loss and

I

in

ds

conduction loss of the MOSFET is reduced. However, this

increases the voltage stress on the MOSFET as shown in

Figure 3. Therefore, determine n by a trade-off between

I

DT

d

s

the voltage margin of the MOSFET and the efficiency.

Typically, a turn-off voltage spike of V

100V, thus V

is designed around 490~550V

ds,max

is considered as

ds

(75~85% of MOSFET rated voltage).

V

[c] Determine the Transformer Primary-side

Inductance (L

)

P

ds

Vin+n(Vo+Vd)

n(Vo+Vd)

Figure 4 shows the typical waveforms of MOSFET drain

current (I

MOSFET drain voltage (V

t

, the current flows through the secondary side rectifier

OFF

diode. When I

resonance between the effective output capacitor of the

MOSFET and the primary-side inductance (L

minimize the switching loss, the FAN6300/A/H is

), secondary diode current (Id), and the

ds

) of a QR converter. During

ds

reduces to zero, Vds begins to drop by the

d

). To

P

n(Vo+Vd)

V

in

t

t

ON

OFF

T

S

t

F

Vin-n(Vo+Vd)

Figure 4. Typical Waveform of QR Operation

© 2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

Rev. 1.0.2 • 5/21/10 3

AN-6300 APPLICATION NOTE

p

To determine the primary-side inductance (LP), the

following variables should be determined beforehand:

The minimum switching frequency (f

s,min

): The

maximum average input current occurs at the

minimum input voltage and full-load condition.

Meanwhile, the switching frequency is at minimum

value during QR operation.

The falling time of the MOSFET drain voltage (t

):

f

As shown in Figure 4, the falling time of MOSFET

drain voltage is half of the resonant period of the

MOSFET effective output capacitance and primaryside inductance. If a resonant capacitor is added to be

paralleled with C

, tf can be increased and EMI can

oss

be reduced. However, this forces a switching loss

increase.

application is about 0.5~1μs.

After determining f

The typical value of t

and t

s,min

, the maximum duty cycle is

f

for NB adaptor

f

calculated as:

nV+V

()

D(1-ft)

=

max s,min f

where V

od

n V +V +V

()

od in

is specified at low-line and full-load.

in,min

××

(3)

According to Equation 1, the maximum average input

current I

I

in,max

According to Figure 3, I

IDI

in,max max d s,max

I

ds,max

I

ds,max

In Equation 5, replace I

combine Equations 4 and 5 to obtain L

L

=

P

where P

respectively, and f

is determined as

in,max

VI

oo

=

V η

in,min

in,max

1

=

k

(5)

2

pk

can be determined as:

VD

pk

in,min max

=

Lf

(V D

in,min max

2P f

in s, min

, and D

in

ms,min

2

)

are specified in Equations 1 and 3,

max

s,min

(4)

can be obtained as:

(6)

pk

by Equation 6, then

ds,max

P:

(7)

is the minimum switching

frequency.

Once L

is determined, the RMS current of the MOSFET

P

in normal operation are obtained as:

D

rms peak

II

ds,max ds,max

max

=

3

(8)

[d] Determine the Proper Core and the

Minimum Primary Turns

When designing the transformer, consider the maximum

flux density swing in normal operation (B

). The

max

maximum flux density swing in normal operation is

related to the hysteresis loss in the core, while the

maximum flux density in transient is related to the core

saturation.

From Faraday’s law, the minimum number of turns for the

transformer primary side is given by:

pk

LI

N10

P,min

Pds,max

=

BA

max e

6

×

(9)

where:

L

is specified in Equation 7;

P

pk

I

is the peak drain current specified in Equation 6;

ds,max

A

is the cross-sectional area of the core in mm2; and

e

B

is the maximum flux density swing in tesla.

max

Generally, it is possible to use B

=0.25~0.30 T.

max

Determine the Number of Turns for Auxiliary

Winding

The number of turns for auxiliary winding (Na) can be

obtained by:

V+V

DD D1

N=

a

V+V

od

(10)

where:

V

is the operating voltage for VDD pin;

DD

V

is the forward voltage drop of D1 in Figure 5; and

D1

V

and Vd as determined in Equation 2.

o

© 2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

Rev. 1.0.2 • 5/21/10 4

Loading...

Loading...