Page 1

S1D13708 Embedded Memory LCD Controller

S1D13708

TECHNICAL MANUAL

Document Number: X39A-Q-001-01

Copyright © 2001 Epson Research and Development, Inc. All Rights Reserved.

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in

evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any

representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain

material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. All other trademarks are the property of their respective owners.

Page 2

Page 2 Epson Research and Development

Vancouver Design Center

THIS PA GE LEFT BLANK

S1D13708 TECHNICAL MANUAL

X39A-Q-001-01 Issue Date: 01/10/09

Page 3

Epson Research and Development Page 3

Vancouver Design Center

COMPREHENSIVE SUPPORT TOOLS

EPSON provides the designer and manufacturer a complete set of resources and tools for the development of LCD

Graphics Systems.

Documentation

• Technical manuals

• Evaluation/Demonstration board manual

Evaluation/Demonstration Board

• Assembled and fully tested Graphics Evaluation/Demonstration board

• Schematic of Evaluation/Demonstration board

• Parts List

• Installation Guide

• CPU Independent Software Utilities

• Evaluation Software

•Display Drivers

Application Engineering Support

EPSON offers the following services through their Sales and Marketing Network:

• Sales Technical Suppo rt

• Customer Training

• Design Assi stance

Application Engineering Support

Engineering and Sales Support is provided by:

Japan

Seiko Epson Corporation

Electronic Devices Marketing Division

421-8, Hino, Hino-shi

Tokyo 191-8501, Japan

Tel: 042-587-5812

Fax: 042-587-5564

http://www.epson.co.jp/

Hong Kong

Epson Hong Kong Ltd.

20/F., Harbour Centre

25 Harbour Road

Wanchai, Hong Kong

Tel: 2585-4600

Fax: 2827-4346

http://www.epson.com.hk/

North America

Epson Electronics America, Inc.

150 River Oaks Parkway

San Jose, CA 95134, USA

Tel: (408) 922-0200

Fax: (408) 922-0238

http://www.eea.epson.com/

Europe

Epson Europe Electronics GmbH

Riesstrasse 15

80992 Munich, Germany

Tel: 089-14005-0

Fax: 089-14005-110

http://www.epson-electronics.de/

Taiwan

Epson Taiwan T echnology

& Trading Ltd.

10F, No. 287

Nanking East Road

Sec. 3, Taipei, Taiwan

Tel: 02-2717-7360

Fax: 02-2712-9164

http://www.epson.com.tw/

Singapore

Epson Singapore Pte., Ltd.

No. 1

Temasek Avenue #36-00

Millenia Tower

Singapore, 039192

Tel: 337-7911

Fax: 334-2716

http://www.epson.com.sg/

TECHNICAL MANUAL S1D13708

Issue Date: 01/10/09 X39A-Q-001-01

Page 4

Page 4 Epson Research and Development

Vancouver Design Center

THIS PA GE LEFT BLANK

S1D13708 TECHNICAL MANUAL

X39A-Q-001-01 Issue Date: 01/10/09

Page 5

ENERGY

SAVING

EPSON

GRAPHICS

S1D13708

S1D13708 Embedded Memory LCD Controller

July 20 01

The S1D13708 is a color/monochrome LCD graphics controller with an embedded memory / display

buffer. Targeted at PDA and Cell Phone applications, the S1D13708 ‘directly’ interfaces to numerous

TFT panels and incorporates a minimum pin-count CPU inter face thereby making it an ideal solut ion for

an LCD Module.

This high level of integration combined wit h a 1.8V Core, provides a low cost, low power, single chip

solution to meet the demands of embedded markets such as Mobile Communications devices and

Palm-size PCs, where board size and battery life are major concerns.

The embedded display buffer greatly improves overall system perfor ma nce as the S1D13708 handles

all of the display functions directly with very little interaction from the processor.

The S1D13708 provides very flexible display features, from our patented SwivelView

TM

technology

which provides hardware rotation of the displa yed image, to our Ink Layer with transparency, to our

“Picture-in-Picture Plus” feature which allows two active variable size display ‘windows’.

The S1D13708 provides impressive support for Mobile Communicati on devices and Palm OS

handhelds, however its impar tiality to CPU type or operating system makes it an ideal display solution

for a wide variet y of appl ications.

■

FEATURES

Embedded Display Buffer.

•

Low Operating Voltage.

•

Low-latency CPU interface.

•

Direct support for the multiple CPU types.

•

Programmable Resoluti ons and Color depths.

•

STN LCD support.

•

Active Matrix LCD support.

•

Reflective Active Matrix support.

•

SwivelView

•

• (Patent # 5,734,875 - Patent # 5,956,049)

“Picture-in-Picture Plus ”.

•

Ink Layer.

•

Software Initiated Power Save Mode.

•

Hardware or Software Video Invert.

•

120-pin PFBGA package.

•

TM

(hardware rotation of displayed image)

.

■

SYSTEM BLOCK DIAGRAM

CPU

X39A-C-001-01 1

Data and

Control Signals

S1D13708

Digital Out

Flat Panel

Page 6

GRAPHICS

S1D13708

■

DESCRIPTION

Memory Interface

• Embedded 80K byte SRAM display buffer.

CPU Interface

• ‘Fixed’ low-latenc y CP U acces s times .

• Direct support for:

• InDirect Interface

Display Support

• 4/8-bit monochrome LCD interface.

• 4/8/16-bit color STN LCD interface.

• Single-panel, single-drive passive displays.

• 9/12/18-bit Active matrix TFT interface.

• ‘Direct’ support for multi ple TFT interfaces (Eps on, Sharp,

• Typical resolutions supported (Ink Layer disabled):

Power Down Modes

• Software Initiated Power Save Mode.

• BCLK can be switched off while maintaining LCD refresh.

Hitachi SH-4 / SH-3.

Motorola M68xxx

(DragonBall, ColdFire,REDCAP2)

MPU bus interface with programmable READY.

provides a minimum 15-pin interface (as compared to

42-pin max implementation).

Type 2,3,4 external timing control IC not required).

- 320x240 @ 8bpp

- 160x160 @ 16bpp

- 160x240 @ 16bpp

Display Modes

• 1/2/4/8/16 bit-per-pixel (bpp ) support.

• Up to 64 gray shades using FRM and dithering on

monochrome passive LCD panels.

• Up to 64K colors on passive STN panels.

• Up to 64K colors on active matrix panels.

.

• SwivelView: direct hard ware ro tati on of display image

by 90°, 180°, 270°.

• “Picture-in-Picture Plus”: displays a variable size

window overlaid over background image.

• Ink Layer.

• Partial Display Support (available on Type 3 TFT).

• Double Buffering/multi-pages: provides smooth

animation and instantaneous screen update.

Clock Source

• Two clock inputs (single c lock possible).

• Clock source can be internally divided down for a

higher frequency clock input.

• 12MHz Crystal Input.

Operating Voltage

•CORE

•IO

1.8 to 2.2 volts.

VDD

3.0 to 3.6volts.

VDD

Package

• 120-pin PFBGA.

CONTACT YOUR SALES REPRESENTATIVE FOR THESE COMPREHENSIVE DESIGN TOOLS

• S1D13708 Technical

Manual

•Palm OS

Abstraction Layer

• S5U13708 Evaluation Boards • Windows

• CPU Independent Software

Utilities

Japan

Seiko Epson Corporation

Electronic Devices Marketing Division

421-8, Hino, Hino-shi

Tokyo 191-8501, Japan

Tel: 042-587-5812

Fax: 042-587-5564

http://www.epson.co.jp

Hong Kong

Epson Hong Kong Ltd.

20/F., Harbour Centre

25 Harbour Road

Wanchai, Hong Kong

Tel: 2585-4600

Fax: 2827-4346

http://www.epson.com.hk/

Copyright © 2001 Epson Research and Development, Inc. All rights reserved.

Information in this document is subject to cha nge wi thou t notice. Y ou ma y download and use thi s do cumen t, but only fo r your own us e in evaluat ing Se iko Epso n/

EPSON products. You may not modify the document. Epson Resear ch and Development, Inc. di sclaims any repre sentation that the contents of this document are

accurate or current. The Programs/Technologies described in this document may contain material protected under U.S. and/or International Patent laws.

EPSON is a registered tra dema rk of Sei ko Epson C orp orat ion. Palm Com puting i s a re gister ed tra dem ark an d the Palm OS platfor m Pl atinu m l ogo is a trademark

of Palm Computing, Inc., 3Com or its subsidiaries. Microsoft, Windows, and the Window s Embedde d Partner Logo are registered trademarks of Microsoft Corporation. All other trademarks are the property of their respective owners.

•VXWorks

Driver

Hardware

CE Display Driver

TornadoTM Display

North America

Epson Electronics America, Inc.

150 River Oaks Parkway

San Jose, CA 95134, USA

Tel: (408) 922-0200

Fax: (408) 922-0238

http://www.eea.epson.com

Europe

Epson Europe Electronics GmbH

Riesstrasse 15

80992 Munich, Germany

Tel: 089-14005-0

Fax: 089-14005-110

http://www.epson-electronics.de

Taiwan

Epson Taiwan Technology & Trading Ltd.

10F, No. 287

Nanking East Road

Sec. 3, Taipei, Taiwan

Tel: 02-2717-7360

Fax: 02-2712-9164

http://www.epson.com.tw/

Singapore

Epson Singapore Pte., Ltd.

No. 1

Temasek Avenue #36-00

Millenia Tower

Singapore, 039192

Tel: 337-7911

Fax: 334-2716

http://www.epson.com.sg/

X39A-C-001-01 2

Page 7

S1D13708 Embedded Memory LCD Controller

Hardware Functional Specification

Document Number: X39A-A-001-02

Copyright © 2001, 2002 Epson Research and Development, Inc. All Rights Reser ved.

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in

evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any

representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain

material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. All other Trademarks are the property of their respective owners

Page 8

Page 2 Epson Research and Development

Vancouver Design Center

THIS PA GE LEFT BLANK

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

Page 9

Epson Research and Development Page 3

Vancouver Design Center

Table of Contents

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.1 Scope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.2 Overview Description . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.1 Integrated Frame Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.2 CPU Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.3 Display Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.4 Display Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.5 Display Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.6 Clock Source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.7 Operating Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.8 Miscellaneous . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3 Typical System Implementation Diagrams . . . . . . . . . . . . . . . . . . . . . . 19

4 Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4.1 Pinout Diagram - PFBGA - 120pin . . . . . . . . . . . . . . . . . . . . . . 27

4.2 Pinout Diagram - Die Form . . . . . . . . . . . . . . . . . . . . . . . . . 28

4.3 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

4.3.1 Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

4.3.2 LCD Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

4.3.3 Clock Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4.3.4 Miscellaneous . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4.3.5 Power And Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

4.4 Summary of Configuration Options . . . . . . . . . . . . . . . . . . . . . . 38

4.5 Host Bus Interface Pin Mapping . . . . . . . . . . . . . . . . . . . . . . . 39

4.6 LCD Interface Pin Mapping . . . . . . . . . . . . . . . . . . . . . . . . . 40

5 D.C. Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

6 A.C. Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

6.1 Clock Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

6.1.1 Input Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

6.1.2 Internal Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

6.2 CPU Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

6.2.1 Generic #1 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

6.2.2 Generic #2 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

6.2.3 Hitachi SH-4 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

6.2.4 Hitachi SH-3 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

6.2.5 Motorola MC68K #1 Interface Timing (e.g. MC68000) . . . . . . . . . . . . . . . 52

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

Page 10

Page 4 Epson Research and Development

Vancouver Design Center

6.2.6 Motorola MC68K #2 Interface Timing (e.g. MC68030) . . . . . . . . . . . . . . . 54

6.2.7 Motorola REDCAP2 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . 56

6.2.8 Motorola DragonBall Interface Timing with DTACK

(e.g. MC68EZ328/MC68VZ328) . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

6.2.9 Motorola DragonBall Interface Timing w/o DTACK

(e.g. MC68EZ328/MC68VZ328) . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

6.2.10 Indirect Interface Timing (Mode 68) . . . . . . . . . . . . . . . . . . . . . . . . . 62

6.2.11 Indirect Interface Timing (Mode 80) . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.3 LCD Power Sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . .66

6.3.1 Passive/TFT Power-On Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

6.3.2 Passive/TFT Power-Off Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

6.4 Display Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

6.4.1 Generic STN Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

6.4.2 Single Monochrome 4-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . 72

6.4.3 Single Monochrome 8-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . 74

6.4.4 Single Color 4-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

6.4.5 Single Color 8-Bit Panel Timing (Format 1) . . . . . . . . . . . . . . . . . . . . . 78

6.4.6 Single Color 8-Bit Panel Timing (Format 2) . . . . . . . . . . . . . . . . . . . . . 80

6.4.7 Single Color 16-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

6.4.8 Generic TFT Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

6.4.9 9/12/18-Bit TFT Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

6.4.10 160x160 Sharp ‘Direct’ HR-TFT Panel Timing (e.g. LQ031B1DDxx) . . . . . . . 88

6.4.11 320x240 Sharp ‘Direct’ HR-TFT Panel Timing (e.g. LQ039Q2DS01) . . . . . . . . 92

6.4.12 160x240 Epson D-TFD Panel Timing (e.g. LF26SCR) . . . . . . . . . . . . . . . . 94

6.4.13 320x240 Epson D-TFD Panel Timing (e.g. LF37SQR) . . . . . . . . . . . . . . . . 98

6.4.14 TFT Type 2 Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102

6.4.15 TFT Type 3 Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

6.4.16 TFT Type 4 Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .109

7 Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

7.1 Clock Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

7.1.1 BCLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112

7.1.2 MCLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112

7.1.3 PCLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

7.1.4 PWMCLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115

7.2 Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

7.3 Clocks versus Functions . . . . . . . . . . . . . . . . . . . . . . . . . . 117

8 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

8.1 Register Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

8.2 Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

8.3 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

Page 11

Epson Research and Development Page 5

Vancouver Design Center

8.3.1 Read-Only Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . .121

8.3.2 Clock Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . .122

8.3.3 Look-Up Table Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

8.3.4 Panel Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

8.3.5 Display Mode Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

8.3.6 Picture-in-Picture Plus Registers . . . . . . . . . . . . . . . . . . . . . . . . . . .138

8.3.7 Miscellaneous Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143

8.3.8 General IO Pins Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .145

8.3.9 Pulse Width Modulation (PWM) Clock and Contrast Voltage (CV)

Pulse Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . .150

8.3.10 Extended Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .154

9 Frame Rate Calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

10 Display Data Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

11 Look-Up Table Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

11.1 Monochrome Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

11.2 Color Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175

12 SwivelView™ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

12.1 Concept . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

12.2 90° SwivelView™ . . . . . . . . . . . . . . . . . . . . . . . . . . . .179

12.2.1 Register Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .180

12.3 180° SwivelView™ . . . . . . . . . . . . . . . . . . . . . . . . . . . .181

12.3.1 Register Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .181

12.4 270° SwivelView™ . . . . . . . . . . . . . . . . . . . . . . . . . . . .182

12.4.1 Register Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .183

13 Picture-in-Picture Plus (PIP+) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

13.1 Concept . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

13.2 With SwivelView Enabled . . . . . . . . . . . . . . . . . . . . . . . . .185

13.2.1 SwivelView 90° . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .185

13.2.2 SwivelView 180° . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .185

13.2.3 SwivelView 270° . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .186

14 Ink Layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .187

14.1 Memory Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . .187

14.2 Controlling the Ink Layer . . . . . . . . . . . . . . . . . . . . . . . . . . 187

14.3 Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .188

15 Indirect Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

15.1 Mode 68 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .190

15.2 Mode 80 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .200

15.3 Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

Page 12

Page 6 Epson Research and Development

Vancouver Design Center

16 Embedded Crystal Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

16.1 Oscillator Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

17 Big-Endian Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 211

17.1 Byte Swapping Bus Data . . . . . . . . . . . . . . . . . . . . . . . . . . 211

17.1.1 16 Bpp Color Depth . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .212

17.1.2 1/2/4/8 Bpp Color Depth . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .213

18 Power Save Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

19 Mechanical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

20 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

21 Technical Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 217

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

Page 13

Epson Research and Development Page 7

Vancouver Design Center

List of Tables

Table 4-1: PFBGA 120-pin Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 4-2: S1D13708 Pad Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 4-3: Host Interface Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 4-4: LCD Interface Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 4-5: Clock Input Pin Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 4-6: Miscellaneous Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 4-7: Power And Ground Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 4-8: Summary of Power-On/Reset Options . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 4-9: Host Bus Interface Pin Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 4-10: LCD Interface Pin Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 5-1: Absolute Maximum Ratings (Preliminary - Subject to Change). . . . . . . . . . . . . . 41

Table 5-2: Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 5-3: Electrical Characteristics for VDD = 3.3V typical. . . . . . . . . . . . . . . . . . . . . 41

Table 6-1: Clock Input Requirements for CLKI when CLKI to BCLK divide > 1 . . . . . . . . . . 42

Table 6-2: Clock Input Requirements for CLKI when CLKI to BCLK divide = 1 . . . . . . . . . . 43

Table 6-3: Clock Input Requirements for CLKI2 . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 6-4: Internal Clock Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 6-5: Generic #1 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 6-6: Generic #2 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 6-7: Hitachi SH-4 Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 6-8: Hitachi SH-3 Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 6-9: Motorola MC68K #1 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 6-10: Motorola MC68K #2 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 6-11: Motorola REDCAP2 Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 6-12: Motorola DragonBall Interface with DTACK Timing. . . . . . . . . . . . . . . . . . . 59

Table 6-13: Motorola DragonBall Interface without DTACK Timing . . . . . . . . . . . . . . . . . 61

Table 6-14: Indirect Interface Timing (Mode 68). . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 6-15: Indirect Interface Timing (Mode 80). . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 6-16: Passive/TFT Power-On Sequence Timing . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 6-17: Passive/TFT Power-Off Sequence Timing. . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 6-18: Panel Timing Parameter Definition and Register Summary . . . . . . . . . . . . . . . . 69

Table 6-19: Single Monochrome 4-Bit Panel A.C. Timing. . . . . . . . . . . . . . . . . . . . . . . 73

Table 6-20: Single Monochrome 8-Bit Panel A.C. Timing. . . . . . . . . . . . . . . . . . . . . . . 75

Table 6-21: Single Color 4-Bit Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Table 6-22: Single Color 8-Bit Panel A.C. Timing (Format 1) . . . . . . . . . . . . . . . . . . . . . 79

Table 6-23: Single Color 8-Bit Panel A.C. Timing (Format 2) . . . . . . . . . . . . . . . . . . . . . 81

Table 6-24: Single Color 16-Bit Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

Page 14

Page 8 Epson Research and Development

Vancouver Design Center

Table 6-25: TFT A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Table 6-26: 160x160 Sharp ‘Direct’ HR-TFT Horizontal Timing . . . . . . . . . . . . . . . . . . . 89

Table 6-27: 160x160 Sharp ‘Direct’ HR-TFT Panel Vertical Timing . . . . . . . . . . . . . . . . . 91

Table 6-28: 320x240 Sharp ‘Direct’ HR-TFT Panel Horizontal Timing . . . . . . . . . . . . . . . . 93

Table 6-29: 320x240 Sharp ‘Direct’ HR-TFT Panel Vertical Timing . . . . . . . . . . . . . . . . . 93

Table 6-30: 160x240 Epson D-TFD Panel Horizontal Timing . . . . . . . . . . . . . . . . . . . . . 95

Table 6-31: 160x240 Epson D-TFD Panel GCP Horizontal Timing . . . . . . . . . . . . . . . . . . 96

Table 6-32: 160x240 Epson D-TFD Panel Vertical Timing . . . . . . . . . . . . . . . . . . . . . . 97

Table 6-33: 320x240 Epson D-TFD Panel Horizontal Timing . . . . . . . . . . . . . . . . . . . . . 99

Table 6-34: 320x240 Epson D-TFD Panel GCP Horizontal Timing . . . . . . . . . . . . . . . . . .100

Table 6-35: 320x240 Epson D-TFD Panel Vertical Timing . . . . . . . . . . . . . . . . . . . . . .101

Table 6-36: TFT Type 2 Horizontal Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103

Table 6-37: TFT Type 2 Vertical Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104

Table 6-38: TFT Type 3 Horizontal Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .106

Table 6-39: TFT Type 3 Vertical Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

Table 6-40: TFT Type 4 A.C. Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

Table 7-1: BCLK Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112

Table 7-2: MCLK Clock Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

Table 7-3: PCLK Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113

Table 7-4: Relationship between MCLK and PCLK. . . . . . . . . . . . . . . . . . . . . . . . . .115

Table 7-5: PWMCLK Clock Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115

Table 7-6: S1D13708 Internal Clock Requirements . . . . . . . . . . . . . . . . . . . . . . . . . .117

Table 8-1: S1D13708 Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

Table 8-2: MCLK Divide Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Table 8-3: PCLK Divide Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122

Table 8-4: PCLK Source Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

Table 8-5: Panel Data Width Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

Table 8-6: HRTFT/D-TFD Panel Resolution Selection . . . . . . . . . . . . . . . . . . . . . . . .126

Table 8-7: LCD Panel Type Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

Table 8-8: Inverse Video Mode Select Options . . . . . . . . . . . . . . . . . . . . . . . . . . . .134

Table 8-9: LCD Bit-per-pixel Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Table 8-10: SwivelViewTM Mode Select Options . . . . . . . . . . . . . . . . . . . . . . . . . . .136

Table 8-11: 32-bit Address Increments for Color Depth . . . . . . . . . . . . . . . . . . . . . . . .139

Table 8-12: 32-bit Address Increments for Color Depth . . . . . . . . . . . . . . . . . . . . . . . .140

Table 8-13: 32-bit Address Increments for Color Depth . . . . . . . . . . . . . . . . . . . . . . . .141

Table 8-14: 32-bit Address Increments for Color Depth . . . . . . . . . . . . . . . . . . . . . . . .142

Table 8-15: PWM Clock Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .150

Table 8-16: CV Pulse Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Table 8-17: PWM Clock Divide Select Options . . . . . . . . . . . . . . . . . . . . . . . . . . . .152

Table 8-18: CV Pulse Divide Select Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .152

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

Page 15

Epson Research and Development Page 9

Vancouver Design Center

Table 8-19: PWMOUT Duty Cycle Select Options. . . . . . . . . . . . . . . . . . . . . . . . . . .153

Table 8-20: Extended Panel Type Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .155

Table 8-21: VCLK Hold . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .159

Table 8-22: VCLK Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .159

Table 8-23: AP Pulse Width. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .160

Table 8-24: AP Rising Position . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .160

Table 8-25: GPO2 PCLK2 Divide Rate. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164

Table 8-26: GPO1 PCLK1 Divide Rate. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164

Table 8-27: Number of Source Driver ICs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .170

Table 18-1: Power Save Mode Function Summary. . . . . . . . . . . . . . . . . . . . . . . . . . .214

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

Page 16

Page 10 Epson Research and Development

Vancouver Design Center

THIS PA GE LEFT BLANK

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

Page 17

Epson Research and Development Page 11

Vancouver Design Center

List of Figures

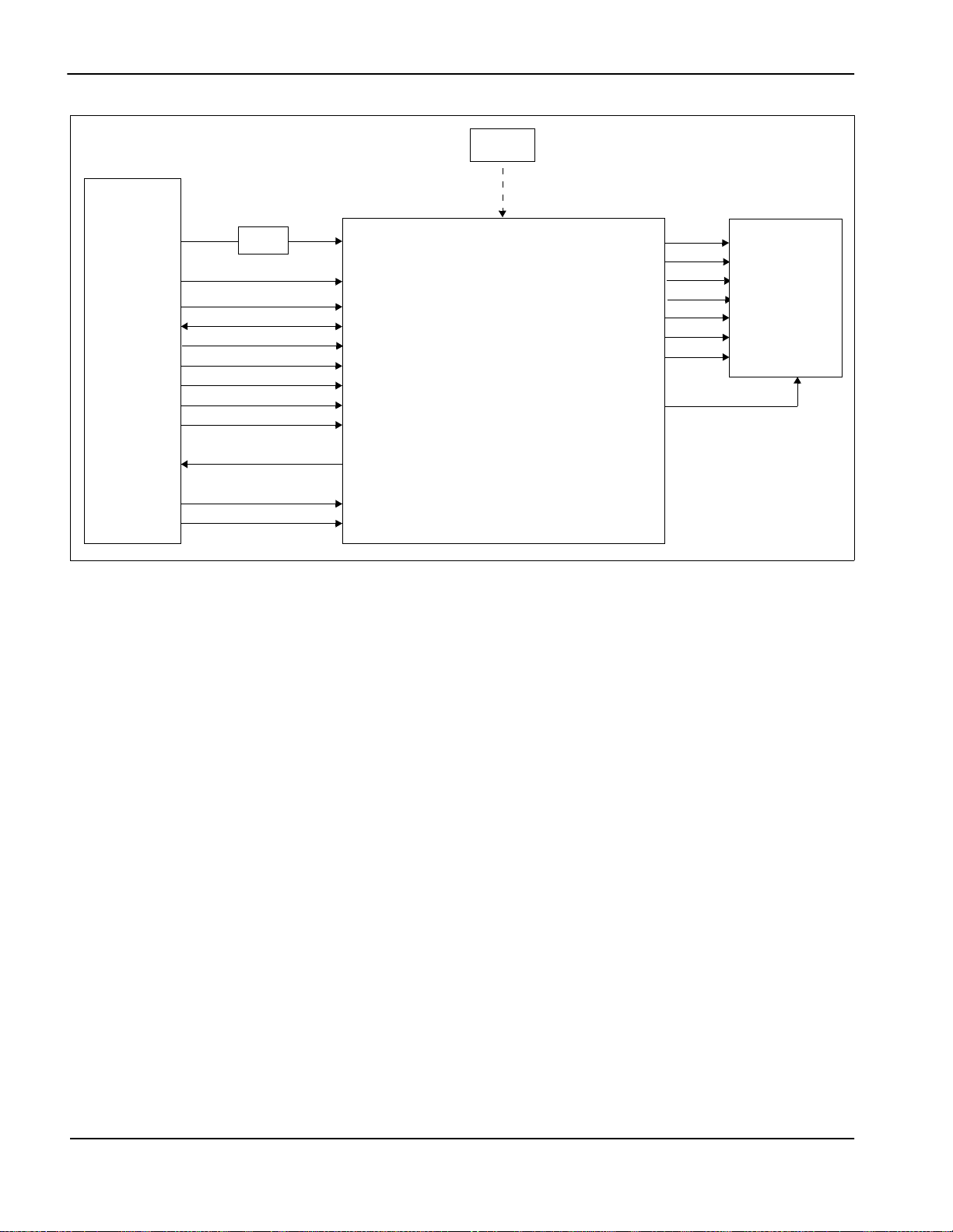

Figure 3-1 Typical System Diagram (Generic #1 Bus) . . . . . . . . . . . . . . . . . . . . . . . .19

Figure 3-2 Typical System Diagram (Generic #2 Bus) . . . . . . . . . . . . . . . . . . . . . . . .19

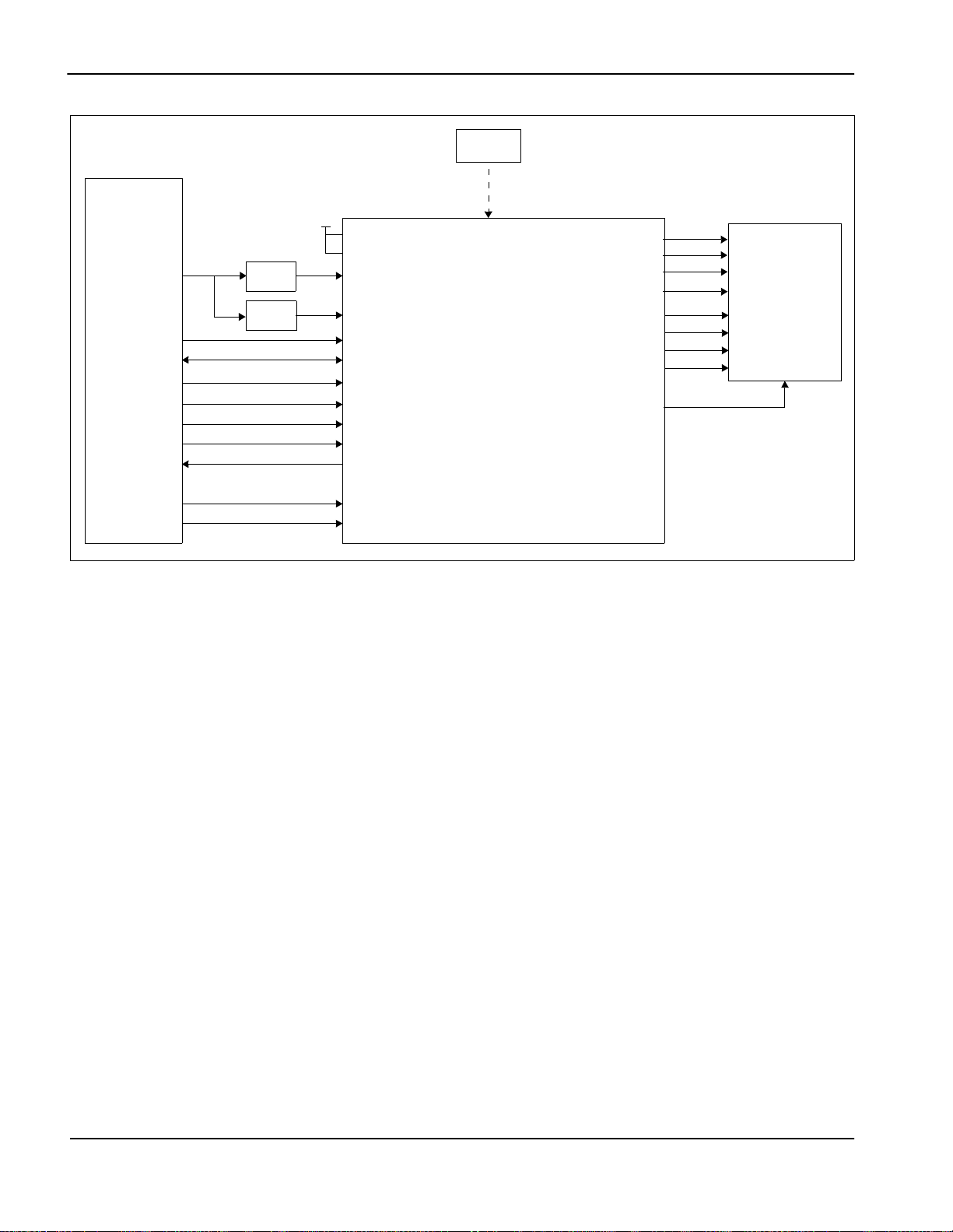

Figure 3-3 Typical System Diagram (Hitachi SH-4 Bus) . . . . . . . . . . . . . . . . . . . . . . .20

Figure 3-4 Typical System Diagram (Hitachi SH-3 Bus) . . . . . . . . . . . . . . . . . . . . . . .21

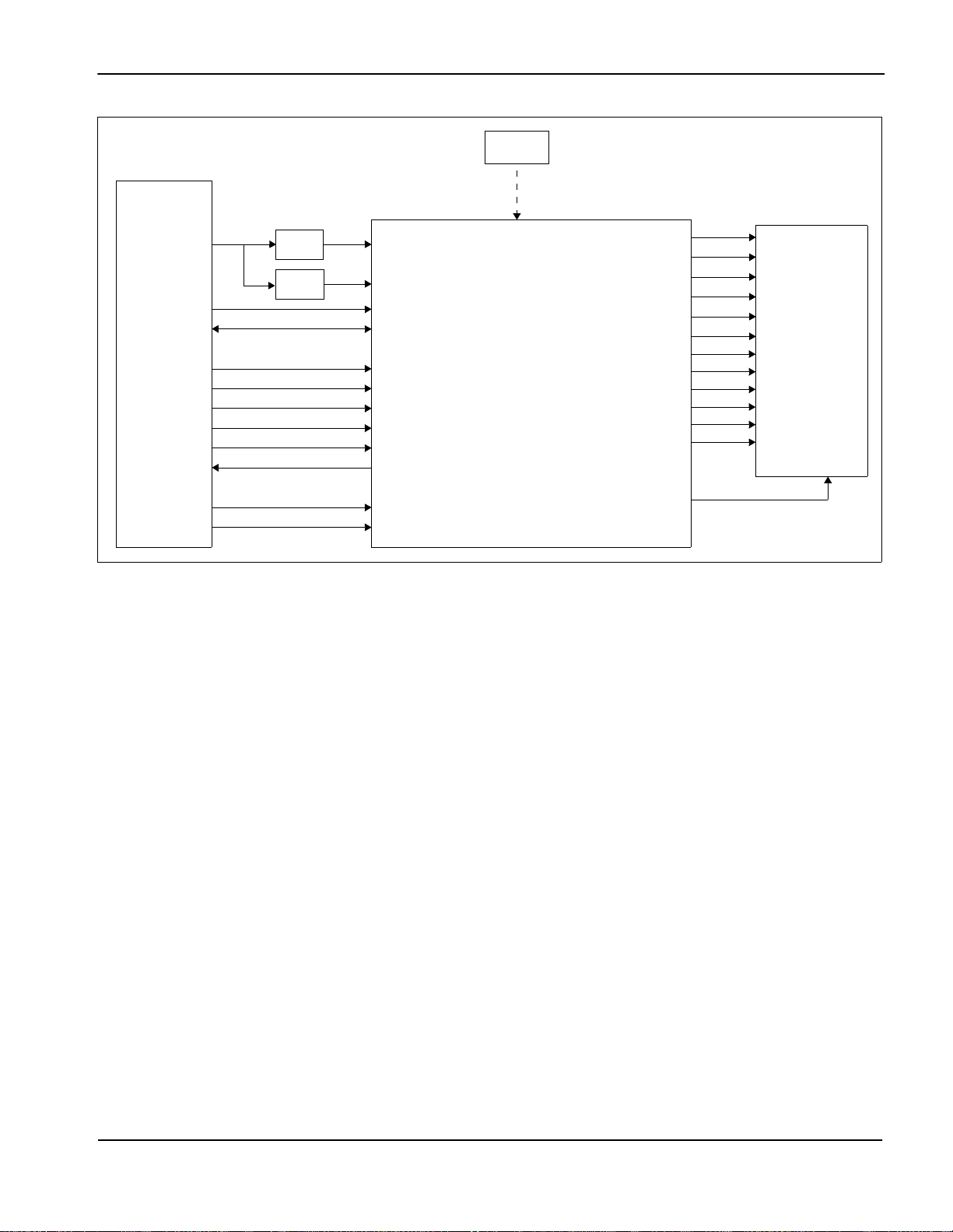

Figure 3-5 Typical System Diagram (MC68K # 1, Motorola 16-Bit 68000) . . . . . . . . . . . . .22

Figure 3-6 Typical System Diagram (MC68K #2, Motorola 32-Bit 68030). . . . . . . . . . . . . .2 3

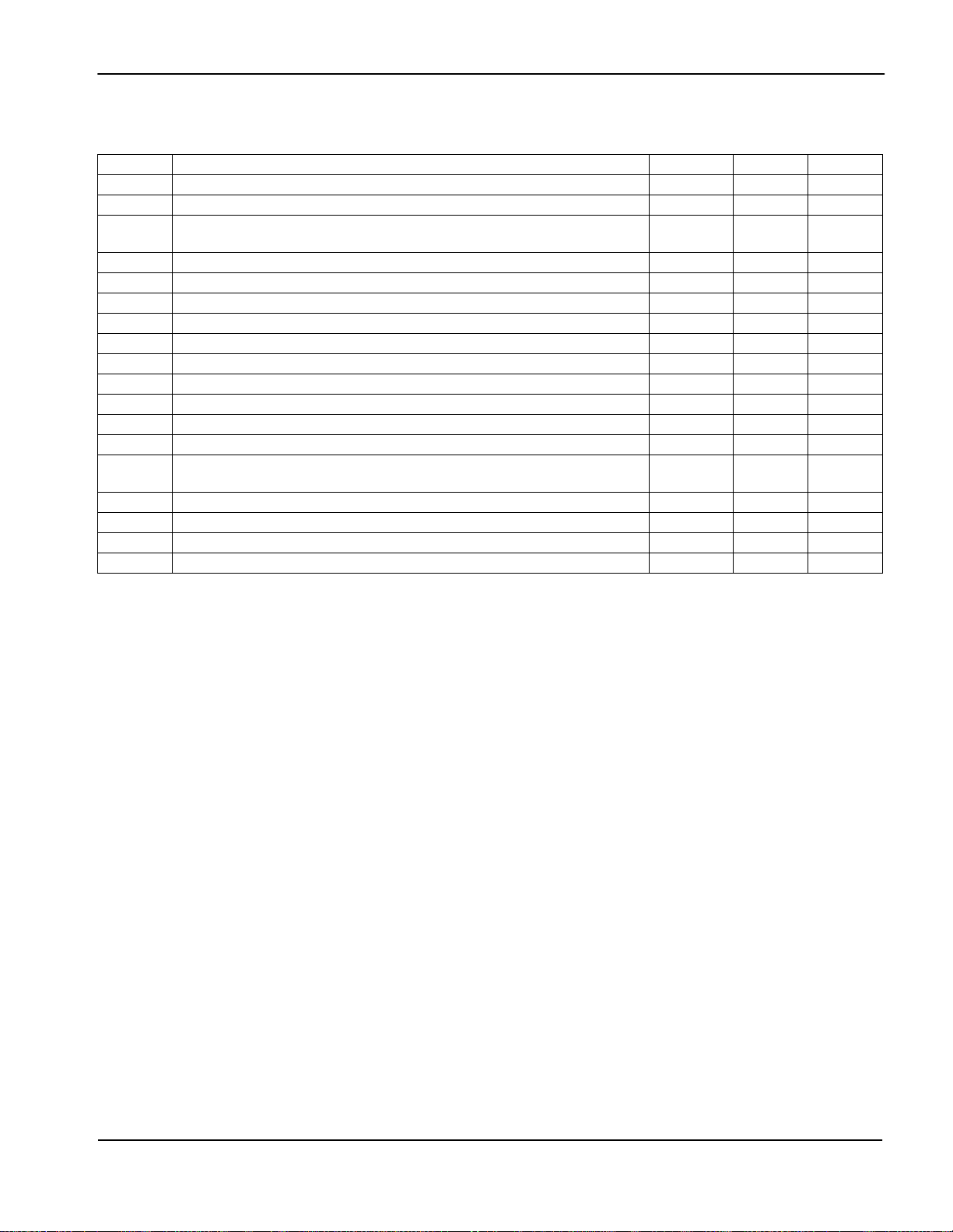

Figure 3-7 Typical System Diagram (Motorola REDCAP2 Bus) . . . . . . . . . . . . . . . . . . .24

Figure 3-8 Typical System Diagram (Motorola MC68EZ328/MC68VZ328 “DragonBall” Bus). . .25

Figure 3-9 Typical System Diagram (Indirect Interface, Mode 68) . . . . . . . . . . . . . . . . . . 25

Figure 3-10 Typical System Diagram (Indirect Interface, Mode 80) . . . . . . . . . . . . . . . . . .26

Figure 4-1 Pinout Diagram - PFBGA 120-pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Figure 6-1 Clock Input Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Figure 6-2 Generic #1 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Figure 6-3 Generic #2 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

Figure 6-4 Hitachi SH-4 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 8

Figure 6-5 Hitachi SH-3 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 0

Figure 6-6 Motorola MC68K #1 Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . .52

Figure 6-7 Motorola MC68K #2 Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . .54

Figure 6-8 Motorola REDCAP2 Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . .56

Figure 6-9 Motorola DragonBall Interface with DTACK Timing . . . . . . . . . . . . . . . . . . . 5 8

Figure 6-10 Motorola DragonBall Interface without DTACK# Timing . . . . . . . . . . . . . . . .60

Figure 6-11 Indirect Interface Timing (Mode 68) . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

Figure 6-12 Indirect Interface Timing (Mode 80) . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

Figure 6-13 Passive/TFT Power-On Sequence Timing . . . . . . . . . . . . . . . . . . . . . . . . .66

Figure 6-14 Passive/TFT Power-Off Sequence Timing . . . . . . . . . . . . . . . . . . . . . . . . .67

Figure 6-15 Panel Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

Figure 6-16 Generic STN Panel Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

Figure 6-17 Single Monochrome 4-Bit Panel Timing. . . . . . . . . . . . . . . . . . . . . . . . . .72

Figure 6-18 Single Monochrome 4-Bit Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . .73

Figure 6-19 Single Monochrome 8-Bit Panel Timing. . . . . . . . . . . . . . . . . . . . . . . . . .74

Figure 6-20 Single Monochrome 8-Bit Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . .75

Figure 6-21 Single Color 4-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

Figure 6-22 Single Color 4-Bit Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . . .77

Figure 6-23 Single Color 8-Bit Panel Timing (Format 1) . . . . . . . . . . . . . . . . . . . . . . . .78

Figure 6-24 Single Color 8-Bit Panel A.C. Timing (Format 1) . . . . . . . . . . . . . . . . . . . . .79

Figure 6-25 Single Color 8-Bit Panel Timing (Format 2) . . . . . . . . . . . . . . . . . . . . . . . .80

Figure 6-26 Single Color 8-Bit Panel A.C. Timing (Format 2) . . . . . . . . . . . . . . . . . . . . .81

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

Page 18

Page 12 Epson Research and Development

Vancouver Design Center

Figure 6-27 Single Color 16-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 2

Figure 6-28 Single Color 16-Bit Panel A.C. Timing. . . . . . . . . . . . . . . . . . . . . . . . . . .83

Figure 6-29 Generic TFT Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

Figure 6-30 18-Bit TFT Panel Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

Figure 6-31 TFT A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

Figure 6-32 160x160 Sharp ‘Direct’ HR-TFT Panel Horizontal Timing . . . . . . . . . . . . . . . .88

Figure 6-33 160x160 Sharp ‘Direct’ HR-TFT Panel Vertical Timing. . . . . . . . . . . . . . . . . .90

Figure 6-34 320x240 Sharp ‘Direct’ HR-TFT Panel Horizontal Timing . . . . . . . . . . . . . . . .92

Figure 6-35 320x240 Sharp ‘Direct’ HR-TFT Panel Vertical Timing. . . . . . . . . . . . . . . . . .93

Figure 6-36 160x240 Epson D-TFD Panel Horizontal Timing . . . . . . . . . . . . . . . . . . . . .94

Figure 6-37 160x240 Epson D-TFD Panel GCP Horizontal Timing . . . . . . . . . . . . . . . . . .96

Figure 6-38 160x240 Epson D-TFD Panel Vertical Timing. . . . . . . . . . . . . . . . . . . . . . .97

Figure 6-39 320x240 Epson D-TFD Panel Horizontal Timing . . . . . . . . . . . . . . . . . . . . .98

Figure 6-40 320x240 Epson D-TFD Panel GCP Horizontal Timing . . . . . . . . . . . . . . . . . 100

Figure 6-41 320x240 Epson D-TFD Panel Vertical Timing. . . . . . . . . . . . . . . . . . . . . . 101

Figure 6-42 TFT Type 2 Horizontal Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Figure 6-43 TFT Type 2 Vertical Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Figure 6-44 TFT Type 3 Horizontal Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Figure 6-45 TFT Type 3 Vertical Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Figure 6-46 TFT Type 4 Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Figure 6-47 TFT Type 4 A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Figure 7-1 Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Figure 8-1 Display Data Byte/Word Swap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Figure 8-2 PWM Clock/CV Pulse Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . 150

Figure 10-1 4/8/16 Bit-Per-Pixel Display Data Memory Organization . . . . . . . . . . . . . . . . 172

Figure 11-1 1 Bit-per-pixel Monochrome Mode Data Output Path . . . . . . . . . . . . . . . . . . 173

Figure 11-2 2 Bit-per-pixel Monochrome Mode Data Output Path . . . . . . . . . . . . . . . . . . 173

Figure 11-3 4 Bit-per-pixel Monochrome Mode Data Output Path . . . . . . . . . . . . . . . . . . 174

Figure 11-4 8 Bit-per-pixel Monochrome Mode Data Output Path . . . . . . . . . . . . . . . . . . 174

Figure 11-5 1 Bit-Per-Pixel Color Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . 175

Figure 11-6 2 Bit-Per-Pixel Color Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . 176

Figure 11-7 4 Bit-Per-Pixel Color Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . 177

Figure 11-8 8 Bit-per-pixel Color Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . 178

Figure 12-1 Relationship Between The Screen Image and the Image Refreshed in 90× SwivelView.179

Figure 12-2 Relationship Between The Screen Image and the Image Refreshed in 180× SwivelView.181

Figure 12-3 Relationship Between The Screen Image and the Image Refreshed in 270× SwivelView.182

Figure 13-1 Picture-in-Picture Plus with SwivelView disabled . . . . . . . . . . . . . . . . . . . . 184

Figure 13-2 Picture-in-Picture Plus with SwivelView 90° enabled . . . . . . . . . . . . . . . . . . 185

Figure 13-3 Picture-in-Picture Plus with SwivelView 180° enabled . . . . . . . . . . . . . . . . . 185

Figure 13-4 Picture-in-Picture Plus with SwivelView 270° enabled . . . . . . . . . . . . . . . . . 186

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

Page 19

Epson Research and Development Page 13

Vancouver Design Center

Figure 14-1 Memory Mapping for Ink Layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

Figure 14-2 Transparent Color Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

Figure 15-1 Sample timing of “register write” with Mode 68. . . . . . . . . . . . . . . . . . . . . 190

Figure 15-2 Sample timing of “register read” with Mode 68 . . . . . . . . . . . . . . . . . . . . . 191

Figure 15-3 Sample timing of “memory write” with Mode 68, Big Endian . . . . . . . . . . . . . 192

Figure 15-4 Sample timing of “memory read” with Mode 68, Big Endian . . . . . . . . . . . . . . 194

Figure 15-5 Sample timing of “register writ e” for Mode 68 when Memory Access Select Enabled . 196

Figure 15-6 Sample timing of “register read” for Mode 68 when Memory Access Select Enabled . 198

Figure 15-7 Sample timing of “register write” with Mode 80. . . . . . . . . . . . . . . . . . . . . 200

Figure 15-8 Sample timing of “register read” with Mode 80 . . . . . . . . . . . . . . . . . . . . . 201

Figure 15-9 Sample timing of “memory write” with mode 80, little endian . . . . . . . . . . . . . 202

Figure 15-10Sample timing of “memory read” with mode 80, Little endian . . . . . . . . . . . . . 204

Figure 15-11Sample timing of “memory write” for Mode 80 when Memory Access Select Enabled 206

Figure 15-12Sample timing of “memory read” for Mode 80 when Memory Access Select Enabled . 208

Figure 16-1 Recommended Crystal Oscillator Circuit . . . . . . . . . . . . . . . . . . . . . . . . 210

Figure 17-1 Byte-swapping for 16 Bpp . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 212

Figure 17-2 Byte-swapping for 1/2/4/8 Bpp. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

Figure 19-1 Mechanical Data PFBGA 120-pin Package . . . . . . . . . . . . . . . . . . . . . . . 215

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

Page 20

Page 14 Epson Research and Development

Vancouver Design Center

THIS PA GE LEFT BLANK

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

Page 21

Epson Research and Development Page 15

Vancouver Design Center

1 Introduction

1.1 Scope

This is the Hardware Functi onal Specifica tion for the S1 D13708 Embedded Memory LCD

Controller. Included in this document are timing diagrams, AC and DC characteristics,

register descriptions, and power management descriptions. This document is intended for

two audiences: Video Subsystem Designers and Software Developers.

For additional documentation related to the S1D13708 see Section 20, “References” on

page 217.

This document is updated as appropriate. Please check the Epson Research and

Development Website at www.erd.epson.com for the latest revision of this doc ument

before beginning any development.

We appreciate your comments on our documentation. Please contact us via email at

documentation@erd.epson.com.

1.2 Overview Description

The S1D13708 is a color/monochrome LCD graphics controller with an embedded 80K

byte SRAM display buffer. While supporting all other panel types, the S1D13708 also

directly interfaces to a variety of TFT products, thus removing the requirement of an

external Timing Control IC. Thi s high level of int egrat ion pr ovides a low c ost, low powe r,

single chip solution to meet the demands of embedded markets such as Mobile Communications devices, and Palm-size PCs where board size and battery life are major concerns.

The S1D13708 utilizes a guaranteed low-latency CPU architecture providing support for

microprocessors without READY/WAIT# handshaking signals. The 32-bit internal data

path provides high performance bandwidth into display memory allowing for fast screen

updates.

Products requiring a rotat ed display image can take advantage of the SwivelView

which provides har dware rotation of the display me mo ry transparent to the software a ppl ication. The S1D13708 also provides support for Virtual screen sizes and Pictu re-in-Picture

Plus (variable size Overlay window).

The S1D13708’s impartiality to CPU type or operating system makes it an ideal display

solution for a wide variety of applications.

TM

feature

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

Page 22

Page 16 Epson Research and Development

Vancouver Design Center

2 Features

2.1 Integrated Frame Buffer

• Embedded 80K byte SRAM display buffer.

2.2 CPU Interface

• Direct support of the following interfaces:

Generic MPU bus interface using WAIT# signal.

Hitachi SH-3.

Hitachi SH-4.

Motorola M68K.

Motorola MC68EZ328/MC68VZ328 DragonBall.

Motorola “REDCAP2” - no WAIT# signal.

Indirect Interface (Mode 68/Mode 80).

• 8-bit processor support with “glue logic”.

• “Fixed” low-latency CPU access times.

• Registers are memory-mapped - M/R# input selects between memory and register

address space.

• The complete 80K byte display buffer is di rectly and con tiguously available through the

17-bit address bus.

• Single level CPU write buffer.

2.3 Display Support

• 4/8-bit monochrome LCD interface.

• 4/8/16-bit color LCD interface.

• Single-panel, single-drive passive displays.

• 9/12/18-bit Active Matrix TFT interface.

• Direct support for 18-bit Epson D-TFD interface.

• Direct support for 18-bit Sharp HR-TFT interface.

• Direct support for 18-bit Type 2, 3, and 4 TFT interfaces.

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

Page 23

Epson Research and Development Page 17

Vancouver Design Center

2.4 Display Modes

• 1/2/4/8/16 bit-per-pixel (bpp) color depths.

• Up to 64 gray shades on monochrome passive LCD panels or 262144 colors on color

passive LCD panels using Frame Rate Modulation (FRM) and dithering.

• Up to 64 gray shades or 262144 colors on active matrix LCD panels.

• Up to 64 gray shades or 256 colors can be simultaneously displayed in 8 bpp mode.

• Up to 64 gray shades or 65536 colors can be simultaneously displayed in 16 bpp mode.

• Example resolutions:

320x240 at a color depth of 8 bpp

160x160 at a color depth of 16 bpp

160x240 at a color depth of 16 bpp

• Example resolutions with Ink Layer enabled.

640x240 at a color depth of 2 bpp

320x240 at a color depth of 4 bpp

160x120 at a color depth of 16 bpp

2.5 Display Features

• SwivelView™: 90°, 180°, 270° counter-clockwise hardware rotation of display image.

• Virtual display support: displays images larger than the panel size through the use of

panning and scrolling.

• Picture-in-Picture Plus: displays a variable size window overlaid over background

image.

• Ink Layer.

• Double Buffering/Multi-pages: provides smooth animation and instantaneous screen

updates.

2.6 Clock Source

• Three clock inputs: CLKI, CLKI2 and XTAL. It is possible to use one clock input only.

• Bus clock can be internally divided by 2, 3, or 4.

• Memory clock is derived from bus clock, CLKI2 or XTAL (XTAL is only available

when configured for Indirect Interface). It can be internally divided by 2, 3, or 4.

• Pixel clock can be derived from CLKI, CLKI2, XTAL, bus clock, or memory clock. It

can be internally divided by 2, 3, 4, or 8.

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

Page 24

Page 18 Epson Research and Development

Vancouver Design Center

2.7 Operating Voltage

• CORE VDD 1.62 to 1.98 volts.

•IO V

2.8 Miscellaneous

• Hardware/Software Video Invert.

• Software Power Save mode.

• General Purpose Input/Output pins are available.

• BCLK can be switche d off while still maintaining LCD refresh, offering power savings.

• 120-pin PFBGA package (also available in die form).

• 12MHz m aximum crystal oscillator (XTAL) available for Indirect Interface.

3.0 to 3.6 volts.

DD

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

Page 25

Epson Research and Development Page 19

Vancouver Design Center

3 Typical System Implementation Diagrams

.

Oscillator

Generic #1

BUS

A[27:17]

A[16:0]

D[15:0]

WE0#

WE1#

RD0#

RD1#

WAIT#

BUSCLK

RESET#

CS#

IO V

DD

Decoder

BS#

M/R#

CS#

AB[16:0]

DB[15:0]

WE0#

WE1#

RD#

RD/WR#

WAIT#

CLKI

RESET#

S1D13708

CLKI2

Figure 3-1 Typical System Diagram (Generic #1 Bus)

.

Oscillator

FPDAT[15:0]

FPFRAME

FPLINE

FPSHIFT

DRDY

GPO0

D[15:0]

FPFRAME

FPLINE

FPSHIFT

MOD

16-bit

Single

LCD

Display

Bias Power

Generic #2

BUS

A[27:17]

CS#

A[16:0]

D[15:0]

WE#

BHE#

RD#

WAIT#

BUSCLK

RESET#

Decoder

IO V

DD

BS#

RD/WR#

M/R#

CS#

AB[16:0]

DB[15:0]

WE0#

WE1#

RD#

WAIT#

CLKI

RESET#

CLKI2

S1D13708

FPDAT[8:0]

FPFRAME

FPLINE

FPSHIFT

DRDY

GPO0

D[8:0]

FPFRAME

FPLINE

FPSHIFT

DRDY

9-bit

TFT

Display

Bias Power

Figure 3-2 Typical System Diagram (Generic #2 Bus)

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

Page 26

Page 20 Epson Research and Development

Vancouver Design Center

.

Oscillator

SH-4

BUS

A[25:17]

CSn#

A[16:0]

D[15:0]

WE0#

WE1#

BS#

RD/WR#

RD#

RDY#

CKIO

RESET#

Decoder

M/R#

CS#

AB[16:0]

DB[15:0]

WE0#

WE1#

BS#

RD/WR#

RD#

WAIT#

CLKI

RESET#

CLKI2

S1D13708

Figure 3-3 Typical System Diagram (Hitachi SH-4 Bus)

FPDAT15

FPDAT12

FPDAT[9:0]

FPFRAME

FPLINE

FPSHIFT

DRDY

GPO0

D11

D10

D[9:0]

FPFRAME

FPLINE

FPSHIFT

DRDY

12-bit

TFT

Display

Bias Power

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

Page 27

Epson Research and Development Page 21

Vancouver Design Center

.

Oscillator

SH-3

BUS

A[25:17]

CSn#

A[16:0]

D[15:0]

WE0#

WE1#

BS#

RD/WR#

RD#

WAIT#

CKIO

RESET#

Decoder

M/R#

CS#

AB[16:0]

DB[15:0]

WE0#

WE1#

BS#

RD/WR#

RD#

WAIT#

CLKI

RESET#

CLKI2

S1D13708

Figure 3-4 Typical System Diagram (Hitachi SH-3 Bus)

FPDAT[17:0]

FPFRAME

FPLINE

FPSHIFT

DRDY

GPO0

D[17:0]

FPFRAME

FPLINE

FPSHIFT

DRDY

18-bit

TFT

Display

Bias Power

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

Page 28

Page 22 Epson Research and Development

Vancouver Design Center

.

Oscillator

MC68K #1

BUS

A[23:17]

FC0, FC1

A[16:1]

D[15:0]

LDS#

UDS#

AS#

R/W#

DTACK#

Decoder

Decoder

IO V

DD

RD#

WE0#

M/R#

CS#

AB[16:1]

DB[15:0]

AB0

WE1#

BS#

RD/WR#

WAIT#

CLKI2

S1D13708

FPDAT[17:0]

FPFRAME

FPLINE

FPSHIFT

GPIO0

GPIO1

GPIO2

GPIO3

GPO0

D[17:0]

SPS

LP

CLK

PS

CLS

REV

SPL

18-bit

HR-TFT

Display

Bias Power

CLK

RESET#

CLKI

RESET#

Figure 3-5 Typical System Diagram (MC68K # 1, Motorola 16-Bit 68000)

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

Page 29

Epson Research and Development Page 23

Vancouver Design Center

.

Oscillator

MC68K #2

BUS

A[31:17]

FC0, FC1

A[16:0]

D[31:16]

DS#

AS#

R/W#

SIZ1

SIZ0

DSACK1#

Decoder

Decoder

M/R#

CS#

AB[16:0]

DB[15:0]

WE1#

BS#

RD/WR#

RD#

WE0#

WAIT#

CLKI2

S1D13708

FPDAT[17:0]

FPFRAME

FPLINE

FPSHIFT

DRDY

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

D[17:0]

DY

LP

XSCL

GCP

XINH

YSCL

FR

FRS

RES

DD_P1

YSCLD

18-bit

D-TFD

Display

XSET (Bias Power)

CLK

RESET#

CLKI

RESET#

GPO0

Figure 3-6 Typical System Diagram (MC68K #2, Motorola 32-Bit 68030)

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

Page 30

Page 24 Epson Research and Development

Vancouver Design Center

.

Oscillator

REDCAP2

BUS

A[21:17]

CSn

A[16:0]

D[15:0]

R/W

OE

EB1

EB0

CLK

RESET_OUT

*Note: CSn# can be any of CS0-CS4

Decoder

Figure 3-7 Typical System Diagram (Motorola REDCAP2 Bus)

IO V

DD

BS#

M/R#

CS#

AB[16:0]

DB[15:0]

RD/WR#

RD#

WE0#

WE1#

CLKI

RESET#

CLKI2

S1D13708

FPDAT[7:4]

FPSHIFT

FPFRAME

FPLINE

DRDY

GPO0

D[3:0]

FPSHIFT

FPFRAME

FPLINE

MOD

4-bit

Single

LCD

Display

Bias Power

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

Page 31

Epson Research and Development Page 25

Vancouver Design Center

.

Oscillator

MC68EZ328/

MC68VZ328

DragonBall

BUS

A[25:17]

Decoder

IO V

DD

BS#

RD/WR#

M/R#

CLKI2

FPDAT[7:0]

FPSHIFT

D[7:0]

FPSHIFT

8-bit

Single

LCD

Display

CS

A[16:0]

D[15:0]

n

CS#

AB[16:0]

DB[15:0]

FPFRAME

FPLINE

DRDY

S1D13708

LWE

UWE

OE

DTACK

CLKO

RESET

WE0#

WE1#

RD#

WAIT#

CLKI

RESET#

Figure 3-8 Typical System Diagram (Motorola MC68EZ328/MC68VZ328 “DragonBall” Bus)

Indirect

Interface

Mode 68

A[23:17]

FC0, FC1

BUSCLK

RESET#

VSS

Decoder

A0

D[15:0]

EBL

EBU

R/W#

AB[16:0]

RD#

BS#

CS#

M/R#

DB[15:0]

WE0#

WE1#

RD/WR#

CLKI

RESET#

XTAL0

XTAL1

S1D13708

GPO0

FPDAT[7:4]

FPSHIFT

FPFRAME

FPLINE

DRDY

GPO0

FPFRAME

FPLINE

MOD

D[3:0]

FPSHIFT

FPFRAME

FPLINE

MOD

Bias Power

4-bit

Single

LCD

Display

Bias Power

Figure 3-9 Typical System Diagram (Indirect Interface, Mode 68)

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

Page 32

Page 26 Epson Research and Development

Vancouver Design Center

Indirect

Interface

Mode 80

BUSCLK

RESET#

A[23:17]

A0

D[15:0]

RDU#

WRL#

WRU#

Decoder

IO V

VSS

DD

BS#

AB[16:0]

CS#

M/R#

DB[15:0]

RD/WR#RDL#

RD#

WE0#

WE1#

CLKI

RESET#

XTAL0

XTAL1

S1D13708

FPDAT[7:4]

FPSHIFT

FPFRAME

FPLINE

DRDY

GPO0

D[3:0]

FPSHIFT

FPFRAME

FPLINE

MOD

4-bit

Single

LCD

Display

Bias Power

Figure 3-10 Typical System Diagram (Indirect Interface, Mode 80)

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

Page 33

Epson Research and Development Page 27

Vancouver Design Center

4 Pins

4.1 Pinout Diagram - PFBGA - 120pin

L

K

J

H

G

F

E

D

C

B

A

1234567891011

BOTTOM VIEW

Figure 4-1 Pinout Diagram - PFBGA 120-pin

Table 4-1: PFBGA 120-pin Mapping

COREVDD IOVDD AB6 AB2 DB7 DB4 DB0 WAIT# FPLINE GPIO5 IOVDD

L

K

J

H

G

F

E

D

C

B

A

AB7 AB5 AB4 AB3 COREVDD DB3 M/R# IOVDD GPIO6 GPIO4 COREVDD

AB10 AB9 AB8 AB1 DB6 DB2 BS# FPFRAME GPIO1 GPIO2 GPIO3

AB14 AB13 AB11 AB0 DB5 DB1 RD# COREVDD PWMOUT GPIO0 DRDY

XTAL0 IOVDD AB15 AB12 VSS VSS VSS GPO6 CLKI2 FPSHIFT CVOUT

COREVDD CLKI XTAL1 AB16 VSS VSS GPO2 GPO5 GPO7 IOVDD

DB11 DB10 DB8 VSS VSS VSS VSS CNF7 GPO1 G PO3 GPO4

DB15 DB14 DB12 DB9 FPDAT0 FPDAT6 FPDAT12 FPDAT16 CNF6 TESTEN GPO0

WE0# CS# DB13 FPDAT1 FPDAT4 FPDAT7 IOVDD FPDAT13 FPDAT17 CNF4 CNF5

COREVDD WE1# RD/WR# FPDAT2 COREVDD FPDAT8 FPDAT10 FPDAT14 CNF0 CNF2 CNF3

IOVDD RESET# IOVDD FPDAT3 FPDAT5 FPDAT9 FPDAT11 FPDAT15 CNF1 COREVDD IOVDD

1234567891011

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

Page 34

Page 28 Epson Research and Development

Vancouver Design Center

4.2 Pinout Diagram - Die Form

Table 4-2: S1D13708 Pad Layout

VSS

IOVDD

CNF3

CNF4

CNF5

CNF6

CNF7

TESTEN

GPO0

GPO1

GPO2

GPO3

GPO4

GPO5

GPO6

GPO7

VSS

CLKI2

IOVDD

FPSHIFT

VSS

COREVDD

CVOUT

PWMOUT

GPO0

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

VSS

COREVDD

989796959493929190898887868584838281807978777675747372717069686766

COREVDD

VSS

CNF2

CNF1

CNF0

FPDAT17

FPDAT16

FPDAT15

FPDAT14

FPDAT13

FPDAT12

FPDAT11

FPDAT10

IOVDD

VSS

FPDAT9

FPDAT8

FPDAT7

FPDAT6

FPDAT5

COREVDD

VSS

FPDAT4

FPDAT3

FPDAT2

FPDAT1

FPDAT0

IOVDD

VSS

*CUT

IOVDD

VSS

99 65

100

101 87 57 63

102 88 56 62

103 89 55 61

104 90 54 60

105 91 53 59

106 92 52 58

107 93 51 57

108 94 50 56

109 95 49 55

110 96 48 54

111 97 47 53

112 98 46 52

113 99 45 51

114 100 44 50

115 101 43 49

116 102 42 48

117 103 41 47

118 104 40 46

119 105 39 45

120 106 38 44

121 107 37 43

122 108 36 42

123 109 35 41

124 110 34 40

125 111 33 39

126 112 32 38

127 113 31 37

128 114 30 36

129 35

130

8685848382818079787776757473727170696867666564636261605958

S1D13708

123456789

10111213141516171819202122232425262728

29

64

34

VSS

IOVDD

GPIO6

FPLINE

FPFRAME

*CUT

VSS

IOVDD

WAIT#

RD#

BS#

M/R#

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

VSS

COREVDD

AB0

AB1

AB2

AB3

AB4

AB5

AB6

AB7

VSS

COREVDD

123456789

VSS

WE1#

WE0#

RESET#

COREVDD

RD/WR#

1011121314151617181920212223242526272829303132

CS#

VSS

DB15

DB14

DB13

DB12

DB9

DB8

DB11

DB10

CLKI

VSS

AB16

AB15

XTAL1

XTAL0

IOVDD

AB14

COREVDD

33

AB9

AB8

AB13

AB12

AB11

AB10

VSS

IOVDD

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

Page 35

Epson Research and Development Page 29

Vancouver Design Center

4.3 Pin Descriptions

Key:

I = Input

O=Output

IO = Bi-Directional (Input/Output)

P=Power pin

PCLKI1 = CMOS/LVTTL schmitt input clock buffer

PIC = CMOS/LVTTL input buffer

PICS = CMOS/LVTTL input buffer with Schmitt input

POC8 = CMOS/LVTTL 8mA low noise output buffer

PBCC8 = CMOS/LVTTL bi-directional low noise buffer with 8mA CMOS output

PBCC8C = CMOS/LVTTL high-speed bi-directional low noise buffer with 8mA CMOS output

Hi-Z = High Impedance

POSC1 = Crystal oscillator IO cell

4.3.1 Host Interface

Table 4-3: Host Interface Pin Descriptions

Pin Name Type

AB0 I H4 PIC IOVDD 0

AB[16:1] I

PFBGA

Pin #

F4,G3,

G4,H1,

H2,H3,

J1,J2,

J3,J4,

K1,K2,

K3,K4,

L3,L4

Cell

PIC IOVDD 0

IO

Voltage

RESET

# State

Description

This input pin has multiple functions.

• For Generic #1, this pin inputs system address bit 0 (A0).

• For Generic #2, this pin inputs system address bit 0 (A0).

• For SH-3/SH-4, this pin inputs system address bit 0 (A0).

• For MC68K #1, this pin inputs the lower data strobe (LDS#).

• For MC68K #2, this pin inputs system address bit 0 (A0).

• For REDCAP2, this pin inputs system address bit 0 (A0).

• For DragonBall, this pin inputs system address bit 0 (A0).

• For Indirect (Mode 68), this pin is tied to V

• For Indirect (Mode 80), this pin is tied to VSS.

See Table 4-9: “Host Bus Interface Pin Mapping,” on page 39

summary.

System address bus bits 16-1.

• For Generic #1, these pins input system address bits 16-1.

• For Generic #2, these pins input system address bits 16-1.

• For SH-3/SH-4, these pins input system address bits 16-1.

• For MC68K #1, these pins input system address bits 16-1.

• For MC68K #2, these pins input system address bits 16-1.

• For REDCAP2, these pins input system address bits 16-1.

• For DragonBall, these pins input system address bits 16-1.

• For Indirect (Mode 68), these pins are tied to V

• For Indirect (Mode 80), these pins are tied to VSS.

SS

.

.

SS

for

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

Page 36

Page 30 Epson Research and Development

Vancouver Design Center

Table 4-3: Host Interface Pin Descriptions

IO

Pin Name Type

PFBGA

Pin #

Cell

Voltage

C3,D1,

D2,D3,

D4,E1,

DB[15:0] IO

E2,E3,

H5,H6,

PBCC8 IOVDD Hi-Z

J5,J6,

K6,L5,

L6,L7

WE0# I C1 PIC IOVDD 1

RESET

# State

Description

Input data from the system data bus.

• For Generic #1, these pins are connected to D[15:0].

• For Generic #2, these pins are connected to D[15:0].

• For SH-3/SH-4, these pins are connected to D[15:0].

• For MC68K #1, these pins are connected to D[15:0].

• For MC68K #2, these pins are connected to D[31:16] for a 32bit device (e.g. MC68030) or D[15:0] for a 16-bit device (e.g.

MC68340).

• For REDCAP2, these pins are connected to D[15:0].

• For DragonBall, these pins are connected to D[15:0].

• For Indirect (Mode 68), these pins are connected to D[15:0].

• For Indirect (Mode 80), these pins are connected to D[15:0].

Unused pins should be tied to VSS. See Table 4-9: “Host Bus

Interface Pin Mapping,” on page 39

for summary.

This input pin has multiple functions.

• For Generic #1, this pin inputs the write enable signal for the

lower data byte (WE0#).

• For Generic #2, this pin inputs the write enable signal (WE#)

• For SH-3/SH-4, this pin inputs the write enable signal for data

byte 0 (WE0#).

• For MC68K #1, this pin must be tied to IO V

DD

• For MC68K #2, this pin inputs the bus size bit 0 (SIZ0).

• For REDCAP2, this pin inputs the byte enable signal for the

D[7:0] data byte (EB1

).

• For DragonBall, this pin inputs the byte enable signal for the

D[7:0] data byte (LWE).

• For Indirect (Mode 68), thi s pin inputs the byte enable signal for

the D[7:0] data byte (EBL).

• For Indirect (Mode 80), this pin inputs the write enable signal for

data byte 0 (WRL#).

See Table 4-9: “Host Bus Interface Pin Mapping,” on page 39

summary.

for

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

Page 37

Epson Research and Development Page 31

Vancouver Design Center

Table 4-3: Host Interface Pin Descriptions

IO

Pin Name Type

PFBGA

Pin #

Cell

Voltage

WE1# I B2 PIC IOVDD 1

CS# I C2 PIC IOVDD 1

M/R# I K7 PIC IOVDD 0

BS# I J7 PIC IOVDD 1

RESET

# State

Description

This input pin has multiple functions.

• For Generic #1, this pin inputs the write enable signal for the

upper data byte (WE1#).

• For Generic #2, this pin inputs the byte enable signal for the

high data byte (BHE#).

• For SH-3/SH-4, this pin inputs the write enable signal for data

byte 1 (WE1#).

• For MC68K #1, this pin inputs the upper data strobe (UDS#).

• For MC68K #2, this pin inputs the data strobe (DS#).

• For REDCAP2, this pin inputs the byte enable signal for the

D[15:8] data byte (EB0

).

• For DragonBall, this pin inputs the byte enable signal for the

D[15:8] data byte (UWE).

• For Indirect (Mode 68), this pi n in put s the byte enable signal for

the D[15:8] data byte (EBU).

• For Indirect (Mode 80), this pin inp uts the write enab le sig nal f or

data byte 1 (WRU#).

See Table 4-9: “Host Bus Interface Pin Mapping,” on page 39

for

summary.

Chip select input. See Table 4-9: “Host Bus Interface Pin Mapping,”

on page 39

for summary.

This input pin is used to select between the display buffer and

register address spaces of the S1D13708. M/R# is set high to

access the displa y b u ffer and low to access the registers. See Table

4-9: “Host Bus Interface Pin Mapping,” on page 39

for summary.

This input pin has multiple functions.

• For Generic #1, this pin must be tied to IO V

DD

.

• For Generic #2, this pin must be tied to IO VDD.

• For SH-3/SH-4, this pin inputs the bus start signal (BS#).

• For MC68K #1, this pin inputs the address strobe (AS#).

• For MC68K #2, this pin inputs the address strobe (AS#).

• For REDCAP2, this pin must be tied to IO V

DD

.

• For DragonBall, this pin must be tied to IO VDD.

• For Indirect (Mode 68), th is p in se lects the I ndirec t Interface For

Mode 68, this pin is tied to VSS.

• For Indirect (Mode 80), th is p in se lects the I ndirec t Interface For

Mode 80, this pin is tied to IO V

See Table 4-9: “Host Bus Interface Pin Mapping,” on page 39

DD

.

for

summary.

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

Page 38

Page 32 Epson Research and Development

Vancouver Design Center

Table 4-3: Host Interface Pin Descriptions

IO

Pin Name Type

PFBGA

Pin #

Cell

Voltage

RD/WR# I B3 PIC IOVDD 1

RD# I H7 PIC IOVDD 1

RESET

# State

Description

This input pin has multiple functions.

• For Generic #1, this pin inputs th e rea d co mm an d for the upper

data byte (RD1#).

• For Generic #2, this pin must be tied to IO V

DD

.

• For SH-3/SH-4, this pin inputs the RD/WR# signal. The

S1D13708 needs this signal for early decode of the bus cycle.

• For MC68K #1, this pin inputs the R/W# signal.

• For MC68K #2, this pin inputs the R/W# signal.

• For REDCAP2, this pin inputs the R/W signal.

• For DragonBall, this pin must be tied to IO V

DD

.

• For Indirect (Mode 68), this pin inputs the R/W# signal.

• For Indirect (Mode 80, this pin inputs the read enable signal for

data byte 0 (RDL#).

See Table 4-9: “Host Bus Interface Pin Mapping,” on page 39

summary.

This input pin has multiple functions.

• For Generic #1, this pin inputs the read command for the lower

data byte (RD0#).

• For Generic #2, this pin inputs the read command (RD#).

• For SH-3/SH-4, this pin inputs the read signal (RD#).

• For MC68K #1, this pin must be tied to IO VDD.

• For MC68K #2, this pin inputs the bus size bit 1 (SIZ1).

• For REDCAP2, this pin inputs the output enable (OE

).

• For DragonBall, this pin inputs the output enable (OE).

• For Indirect (Mode 68), this pin is tied to V

SS

.

• For Indirect (Mode 80), this pin inp uts the read ena b le signal f or

data byte 1 (RDU#).

See Table 4-9: “Host Bus Interface Pin Mapping,” on page 39

summary.

for

for

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

Page 39

Epson Research and Development Page 33

Vancouver Design Center

Table 4-3: Host Interface Pin Descriptions

IO

Pin Name Type

PFBGA

Pin #

Cell

Voltage

WAIT# O L8 PBCC8C IOVDD Hi-Z

RESET# I A2 PICS IOVDD 0

RESET

# State

Description

During a data transfer, this output pin is driven active to force the

system to insert wait states. It is driven inactive to indicate the

completion of a data transfer. WAIT# is released to the high

impedance state af ter the data transfe r is complete. Its active polarit y

is configurable. See Table 4-8: “Summary of Power-On/Reset

Options,” on page 38.

• For Generic #1, this pin outputs the wait signal (WAIT#).

• For Generic #2, this pin outputs the wait signal (WAIT#).

• For SH-3 mode, this pin outputs the wait request signal

(WAIT#).

• For SH-4 mode, this pin outputs the device ready signal

(RDY#).

• For MC68K #1, this pin outputs the data transfer acknowledge

signal (DTACK#).

• For MC68K #2, this pin outputs the data transfer and size

acknowledge bit 1 (DSACK1#).

• For REDCAP2, this pin is unused (Hi-Z).

• For DragonBall, this pin outputs the data transfer acknowledge

signal (DTACK

).

• For Indirect (Mode 68), this pin is unused (Hi-Z).

• For Indirect (Mode 80), this pin is unused (Hi-Z).

See Table 4-9: “Host Bus Interface Pin Mapping,” on page 39 for

summary.

Active low input to set all internal registers to the default state and to

force all signals to their inactive states.

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

Page 40

Page 34 Epson Research and Development

Vancouver Design Center

4.3.2 LCD Interface

Table 4-4: LCD Interface Pin Descriptions

IO

Pin Name Type

FPDAT[17:0] O

FPFRAME O J8 PBCC8 IOVDD 0

FPLINE O L9 PBCC8 IOVDD 0

FPSHIFT O G10 PBCC8 IOVDD 0

DRDY O H11 POC8 IOVDD 0

PFBGA

Pin #

A4,A5,

A6,A7,

A8,B4,

B6,B7,

B8,C4,

C5,C6,

C8,C9,

D5,D6,

D7,D8

Cell

PBCC8 IOVDD 0 Panel Data bits 17-0.

Voltage

RESET#

State

Description

This output pin has multiple functions.

•Frame Pulse

• SPS for Sharp HR-TFT

• DY for Epson D-TFD

• STV for TFT Type 2

•STV for Type 3

See Table 4-10: “LCD Interface Pin Mapping,” on page 40

summary.

This output pin has multiple functions.

•Line Pulse

• LP for Sharp HR-TFT

• LP for Epson D-TFD

• STB for TFT Type 2

• LP for Type 3

See Table 4-10: “LCD Interface Pin Mapping,” on page 40 for

summary.

This output pin has multiple functions.

• Shift Clock

• CLK for Sharp HR-TFT

• XSCL for Epson D-TFD

• CLK for TFT Type 2

•CPH for Type 3

See Table 4-10: “LCD Interface Pin Mapping,” on page 40

summary.

This output pin has multiple functions.

• Display enable (DRDY) for TFT panels

• 2nd shift clock (FPSHIFT2) for passive LCD with Format 1

interface

• GCP for Epson D-TFD

• INV for TFT T ype 2

• INV for TFT Type 3

• LCD backplane bias signal (MOD) for all other LCD panels

See Table 4-10: “LCD Interface Pin Mapping,” on page 40 for

summary.

for

for

S1D13708 Hardware Functional Specification

X39A-A-001-02 Issue Date: 02/03/07

Page 41

Epson Research and Development Page 35

Vancouver Design Center

Table 4-4: LCD Interface Pin Descriptions

IO

Pin Name Type

PFBGA

Pin #

Cell

Voltage

GPIO0 IO H10 PBCC8 IOVDD 0

GPIO1 IO J9 PBCC8 IOVDD 0

GPIO2 IO J10 PBCC8 IOVDD 0

GPIO3 IO J11 PBCC8 IOVDD 0

GPIO4 IO K10 PBCC8 IOVDD 0

RESET#

State

Description

This pin has multiple functions.

• PS for Sharp HR-TFT

• XINH for Epson D-TFD

• VCLK for TFT Type 2

• CPV for Type 3

• General purpose IO pin 0 (GPIO0)

• Hardware Video Invert

See Table 4-10: “LCD Interface Pin Mapping,” on page 40

for

summary.

This pin has multiple functions.

• CLS for Sharp HR-TFT

• YSCL for Epson D-TFD

• AP for TFT Type 2

•OE for Type 3

• General purpose IO pin 1 (GPIO1)

See Table 4-10: “LCD Interface Pin Mapping,” on page 40 for

summary.

This pin has multiple functions.

• REV for Sharp HR-TFT

• FR for Epson D-TFD

• POL for TFT Type 2

• POL for Type 3

• General purpose IO pin 2 (GPIO2)

See Table 4-10: “LCD Interface Pin Mapping,” on page 40

for

summary.

This pin has multiple functions.

• SPL for Sharp HR-TFT

• FRS for Epson D-TFD

• STH for TFT Type 2

• EIO for Type 3

• General purpose IO pin 3 (GPIO3)

See Table 4-10: “LCD Interface Pin Mapping,” on page 40

for

summary.

This pin has multiple functions.

• RES for Epson D-TFD

•VCOM for Type 3

• General purpose IO pin 4 (GPIO4)

See Table 4-10: “LCD Interface Pin Mapping,” on page 40

for

summary.

Hardware Functional Specification S1D13708

Issue Date: 02/03/07 X39A-A-001-02

Page 42

Page 36 Epson Research and Development

Vancouver Design Center