Page 1

查询S1D13706供应商

S1D13706 Embedded Memory LCD Controller

Hardware Functional Specification

Document Number: X31B-A-001-09

Copyright © 1999, 2004 Epson Research and Development, Inc. All Rights Reserved.

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in

evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any

representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain

material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. All other Trademarks are the property of their respective owners

Page 2

Page 2 Epson Research and Development

Vancouver Design Center

THIS PAGE LEFT BLANK

S1D13706 Hardware Functional Specification

X31B-A-001-09 Issue Date: 2004/02/09

Page 3

Epson Research and Development Page 3

Vancouver Design Center

Table of Contents

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.1 Scope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.2 Overview Description . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.1 Integrated Frame Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.2 CPU Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.3 Display Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.4 Display Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.5 Display Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.6 Clock Source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.7 Miscellaneous . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3 Typical System Implementation Diagrams . . . . . . . . . . . . . . . . . . . . . . 14

4 Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

4.1 Pinout Diagram - TQFP15 - 100pin . . . . . . . . . . . . . . . . . . . . . . 18

4.2 Pinout Diagram - Die Form . . . . . . . . . . . . . . . . . . . . . . . . . 19

4.3 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.3.1 Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.3.2 LCD Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.3.3 Clock Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4.3.4 Miscellaneous . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4.3.5 Power And Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4.4 Summary of Configuration Options . . . . . . . . . . . . . . . . . . . . . . 28

4.5 Host Bus Interface Pin Mapping . . . . . . . . . . . . . . . . . . . . . . . 29

4.6 LCD Interface Pin Mapping . . . . . . . . . . . . . . . . . . . . . . . . . 30

5 D.C. Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

6 A.C. Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

6.1 Clock Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

6.1.1 Input Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

6.1.2 Internal Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

6.2 CPU Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

6.2.1 Generic #1 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

6.2.2 Generic #2 Interface Timing (e.g. ISA) . . . . . . . . . . . . . . . . . . . . . . . . 37

6.2.3 Hitachi SH-4 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

6.2.4 Hitachi SH-3 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

6.2.5 Motorola MC68K #1 Interface Timing (e.g. MC68000) . . . . . . . . . . . . . . . 43

6.2.6 Motorola MC68K #2 Interface Timing (e.g. MC68030) . . . . . . . . . . . . . . . 45

Hardware Functional Specification S1D13706

Issue Date: 2004/02/09 X31B-A-001-09

Page 4

Page 4 Epson Research and Development

Vancouver Design Center

6.2.7 Motorola REDCAP2 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . 47

6.2.8 Motorola DragonBall Interface Timing with DTACK (e.g. MC68EZ328/MC68VZ328) 49

6.2.9 Motorola DragonBall Interface Timing w/o DTACK (e.g. MC68EZ328/MC68VZ328) 51

6.3 LCD Power Sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . .54

6.3.1 Passive/TFT Power-On Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

6.3.2 Passive/TFT Power-Off Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

6.4 Display Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

6.4.1 Generic STN Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

6.4.2 Single Monochrome 4-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . 60

6.4.3 Single Monochrome 8-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . 62

6.4.4 Single Color 4-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.4.5 Single Color 8-Bit Panel Timing (Format 1) . . . . . . . . . . . . . . . . . . . . . 66

6.4.6 Single Color 8-Bit Panel Timing (Format 2) . . . . . . . . . . . . . . . . . . . . . 68

6.4.7 Single Color 16-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

6.4.8 Generic TFT Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

6.4.9 9/12/18-Bit TFT Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

6.4.10 160x160 Sharp ‘Direct’ HR-TFT Panel Timing (e.g. LQ031B1DDxx) . . . . . . . 76

6.4.11 320x240 Sharp ‘Direct’ HR-TFT Panel Timing (e.g. LQ039Q2DS01) . . . . . . . . 80

6.4.12 160x240 Epson D-TFD Panel Timing (e.g. LF26SCR) . . . . . . . . . . . . . . . . 82

6.4.13 320x240 Epson D-TFD Panel Timing (e.g. LF37SQR) . . . . . . . . . . . . . . . . 86

7 Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

7.1 Clock Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

7.1.1 BCLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

7.1.2 MCLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

7.1.3 PCLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

7.1.4 PWMCLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

7.2 Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .93

7.3 Clocks versus Functions . . . . . . . . . . . . . . . . . . . . . . . . . . .94

8 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .95

8.1 Register Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . .95

8.2 Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .95

8.3 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

8.3.1 Read-Only Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . 96

8.3.2 Clock Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

8.3.3 Look-Up Table Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

8.3.4 Panel Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

8.3.5 Display Mode Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .109

8.3.6 Picture-in-Picture Plus (PIP+) Registers . . . . . . . . . . . . . . . . . . . . . . .115

8.3.7 Miscellaneous Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .120

S1D13706 Hardware Functional Specification

X31B-A-001-09 Issue Date: 2004/02/09

Page 5

Epson Research and Development Page 5

Vancouver Design Center

8.3.8 General IO Pins Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122

8.3.9 Pulse Width Modulation (PWM) Clock and Contrast Voltage (CV) Pulse Configuration

Registers 126

9 Frame Rate Calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

10 Display Data Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

11 Look-Up Table Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

11.1 Monochrome Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

11.2 Color Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134

12 SwivelView™ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

12.1 Concept . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

12.2 90° SwivelView™ . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

12.2.1 Register Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

12.3 180° SwivelView™ . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

12.3.1 Register Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

12.4 270° SwivelView™ . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

12.4.1 Register Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

13 Picture-in-Picture Plus (PIP+) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

13.1 Concept . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

13.2 With SwivelView Enabled . . . . . . . . . . . . . . . . . . . . . . . . .144

13.2.1 SwivelView 90° . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .144

13.2.2 SwivelView 180° . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

13.2.3 SwivelView 270° . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

14 Big-Endian Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

14.1 Byte Swapping Bus Data . . . . . . . . . . . . . . . . . . . . . . . . . .146

14.1.1 16 Bpp Color Depth . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

14.1.2 1/2/4/8 Bpp Color Depth . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .148

15 Power Save Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

16 Mechanical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

17 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

18 Sales and Technical Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Hardware Functional Specification S1D13706

Issue Date: 2004/02/09 X31B-A-001-09

Page 6

Page 6 Epson Research and Development

Vancouver Design Center

THIS PAGE LEFT BLANK

S1D13706 Hardware Functional Specification

X31B-A-001-09 Issue Date: 2004/02/09

Page 7

Epson Research and Development Page 7

Vancouver Design Center

List of Tables

Table 4-1: Pinout Assignments - Die Form (S1D13706D00A) . . . . . . . . . . . . . . . . . . . . 20

Table 4-2: Host Interface Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 4-3: LCD Interface Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 4-4: Clock Input Pin Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 4-5: Miscellaneous Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 4-6: Power And Ground Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 4-7: Summary of Power-On/Reset Options . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 4-8: Host Bus Interface Pin Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 4-9: LCD Interface Pin Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 5-1: Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 5-2: Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 5-3: Electrical Characteristics for VDD = 3.3V typical. . . . . . . . . . . . . . . . . . . . . 31

Table 6-1: Clock Input Requirements for CLKI when CLKI to BCLK divide > 1 . . . . . . . . . . 32

Table 6-2: Clock Input Requirements for CLKI when CLKI to BCLK divide = 1 . . . . . . . . . . 33

Table 6-3: Clock Input Requirements for CLKI2 . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 6-4: Internal Clock Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 6-5: Generic #1 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 6-6: Generic #2 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 6-7: Hitachi SH-4 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 6-8: Hitachi SH-3 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 6-9: Motorola MC68K #1 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 6-10: Motorola MC68K #2 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 6-11: Motorola REDCAP2 Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 6-12: Motorola DragonBall Interface with DTACK Timing. . . . . . . . . . . . . . . . . . . 50

Table 6-13: Motorola DragonBall Interface without DTACK Timing . . . . . . . . . . . . . . . . . 52

Table 6-14: Passive/TFT Power-On Sequence Timing . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 6-15: Passive/TFT Power-Off Sequence Timing. . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 6-16: Panel Timing Parameter Definition and Register Summary . . . . . . . . . . . . . . . . 57

Table 6-17: Single Monochrome 4-Bit Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . 61

Table 6-18: Single Monochrome 8-Bit Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . 63

Table 6-19: Single Color 4-Bit Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 6-20: Single Color 8-Bit Panel A.C. Timing (Format 1) . . . . . . . . . . . . . . . . . . . . . 67

Table 6-21: Single Color 8-Bit Panel A.C. Timing (Format 2) . . . . . . . . . . . . . . . . . . . . . 69

Table 6-22: Single Color 16-Bit Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 6-23: TFT A.C. Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Table 6-24: 160x160 Sharp ‘Direct’ HR-TFT Horizontal Timing . . . . . . . . . . . . . . . . . . . 77

Table 6-25: 160x160 Sharp ‘Direct’ HR-TFT Panel Vertical Timing . . . . . . . . . . . . . . . . . 79

Hardware Functional Specification S1D13706

Issue Date: 2004/02/09 X31B-A-001-09

Page 8

Page 8 Epson Research and Development

Vancouver Design Center

Table 6-26: 320x240 Sharp ‘Direct’ HR-TFT Panel Horizontal Timing . . . . . . . . . . . . . . . . 81

Table 6-27: 320x240 Sharp ‘Direct’ HR-TFT Panel Vertical Timing . . . . . . . . . . . . . . . . . 81

Table 6-28: 160x240 Epson D-TFD Panel Horizontal Timing . . . . . . . . . . . . . . . . . . . . . 83

Table 6-29: 160x240 Epson D-TFD Panel GCP Horizontal Timing . . . . . . . . . . . . . . . . . . 84

Table 6-30: 160x240 Epson D-TFD Panel Vertical Timing . . . . . . . . . . . . . . . . . . . . . . 85

Table 6-31: 320x240 Epson D-TFD Panel Horizontal Timing . . . . . . . . . . . . . . . . . . . . . 87

Table 6-32: 320x240 Epson D-TFD Panel GCP Horizontal Timing . . . . . . . . . . . . . . . . . . 88

Table 6-33: 320x240 Epson D-TFD Panel Vertical Timing . . . . . . . . . . . . . . . . . . . . . . 89

Table 7-1: BCLK Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Table 7-2: MCLK Clock Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Table 7-3: PCLK Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Table 7-4: Relationship between MCLK and PCLK. . . . . . . . . . . . . . . . . . . . . . . . . . 92

Table 7-5: PWMCLK Clock Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Table 7-6: S1D13706 Internal Clock Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Table 8-1: S1D13706 Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Table 8-2: MCLK Divide Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Table 8-3: PCLK Divide Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 8-4: PCLK Source Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 8-5: Panel Data Width Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102

Table 8-6: Active Panel Resolution Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102

Table 8-7: LCD Panel Type Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102

Table 8-8: Inverse Video Mode Select Options . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

Table 8-9: LCD Bit-per-pixel Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111

Table 8-10: SwivelViewTM Mode Select Options . . . . . . . . . . . . . . . . . . . . . . . . . . .112

Table 8-11: 32-bit Address Increments for Color Depth . . . . . . . . . . . . . . . . . . . . . . . .116

Table 8-12: 32-bit Address Increments for Color Depth . . . . . . . . . . . . . . . . . . . . . . . .117

Table 8-13: 32-bit Address Increments for Color Depth . . . . . . . . . . . . . . . . . . . . . . . .118

Table 8-14: 32-bit Address Increments for Color Depth . . . . . . . . . . . . . . . . . . . . . . . .119

Table 8-15: PWM Clock Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

Table 8-16: CV Pulse Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

Table 8-17: PWM Clock Divide Select Options . . . . . . . . . . . . . . . . . . . . . . . . . . . .128

Table 8-18: CV Pulse Divide Select Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .128

Table 8-19: PWMOUT Duty Cycle Select Options . . . . . . . . . . . . . . . . . . . . . . . . . . .129

Table 15-1: Power Save Mode Function Summary . . . . . . . . . . . . . . . . . . . . . . . . . . .149

S1D13706 Hardware Functional Specification

X31B-A-001-09 Issue Date: 2004/02/09

Page 9

Epson Research and Development Page 9

Vancouver Design Center

List of Figures

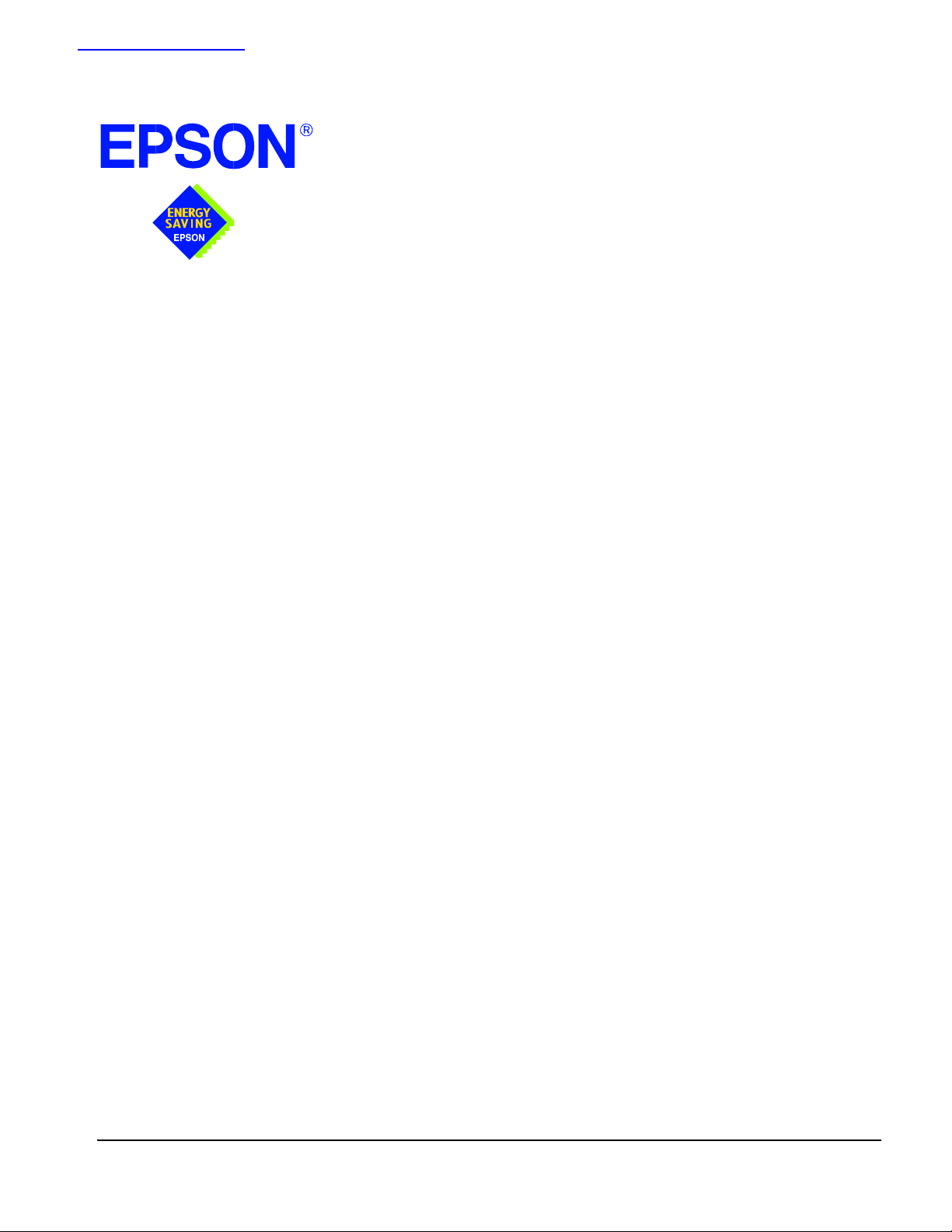

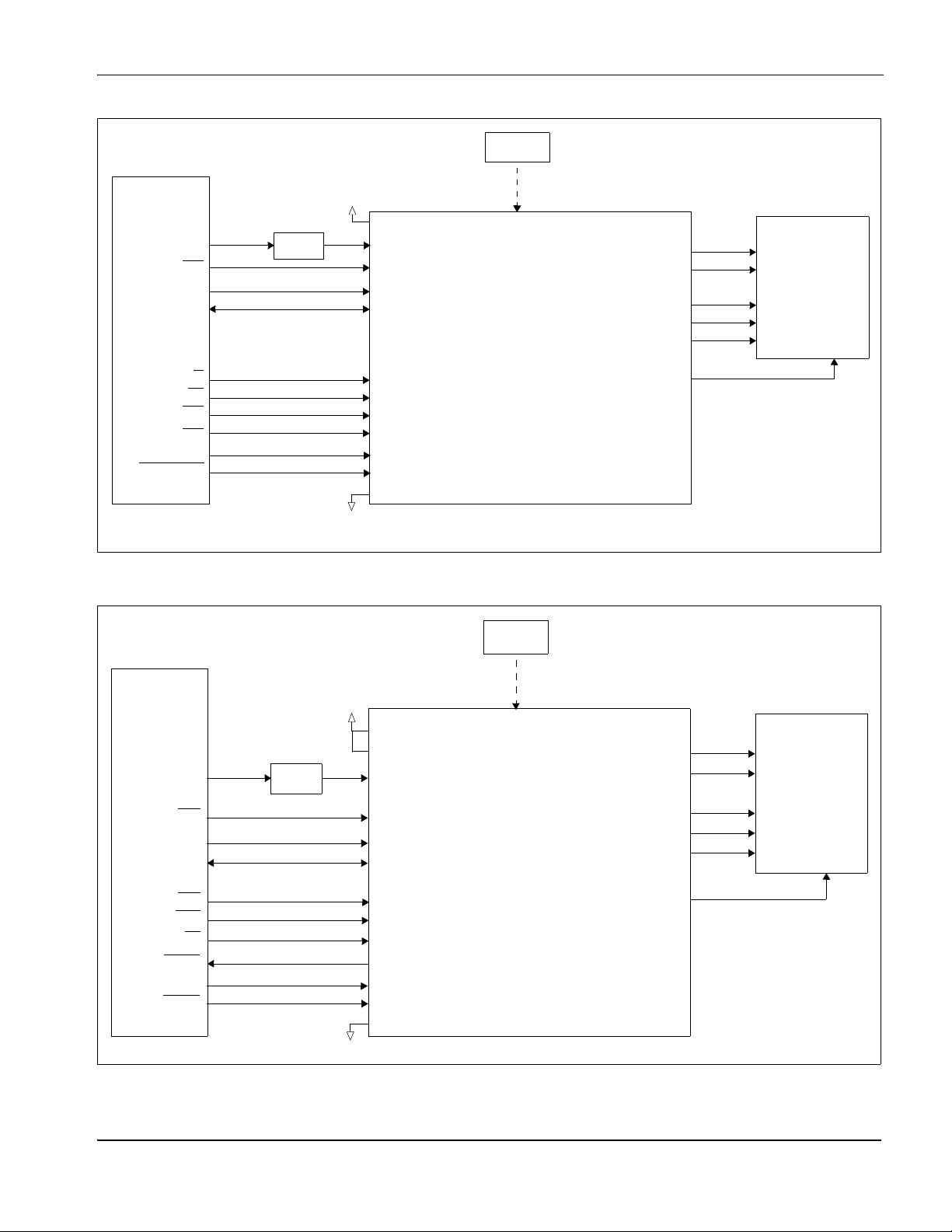

Figure 3-1: Typical System Diagram (Generic #1 Bus) . . . . . . . . . . . . . . . . . . . . . . . .14

Figure 3-2: Typical System Diagram (Generic #2 Bus) . . . . . . . . . . . . . . . . . . . . . . . .14

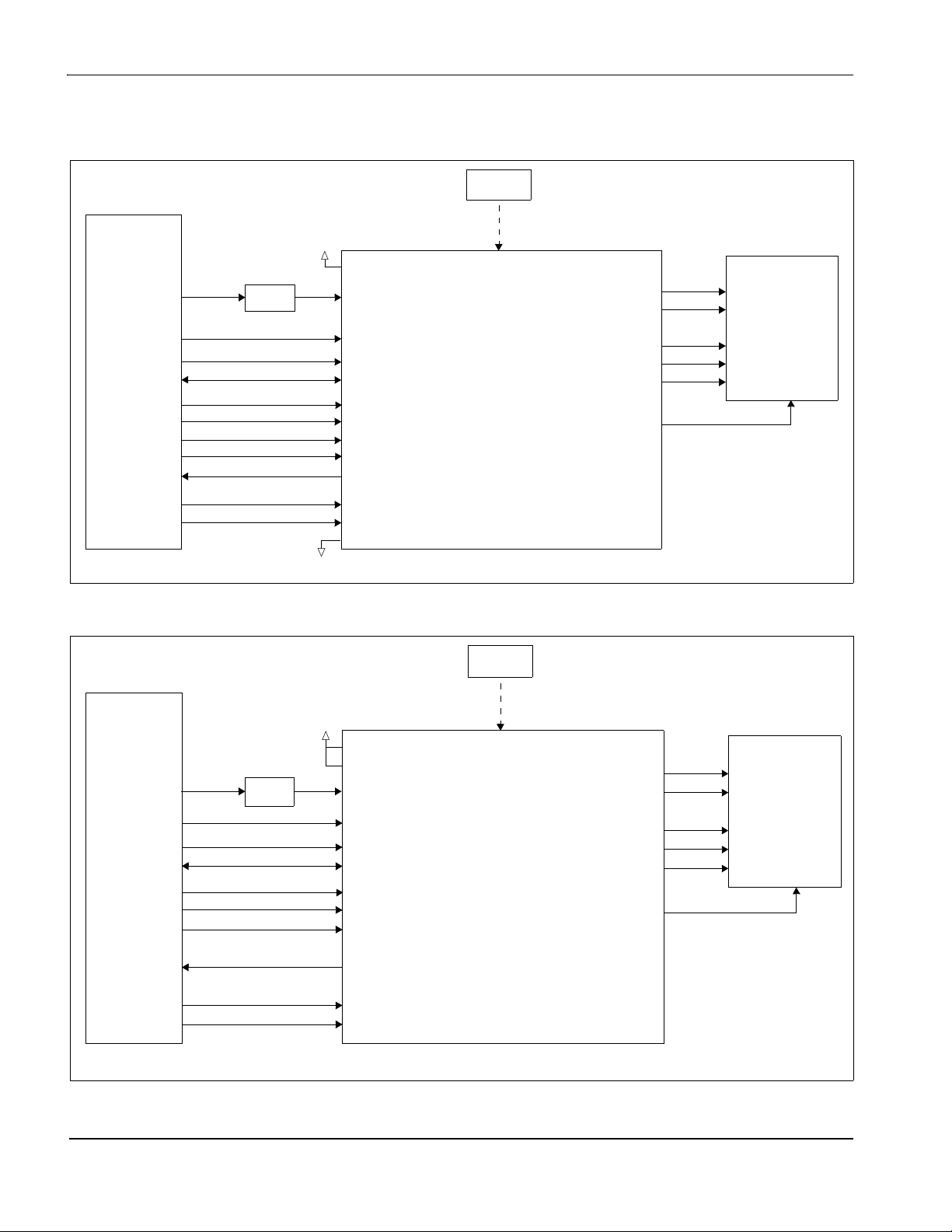

Figure 3-3: Typical System Diagram (Hitachi SH-4 Bus) . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 3-4: Typical System Diagram (Hitachi SH-3 Bus) . . . . . . . . . . . . . . . . . . . . . . . 15

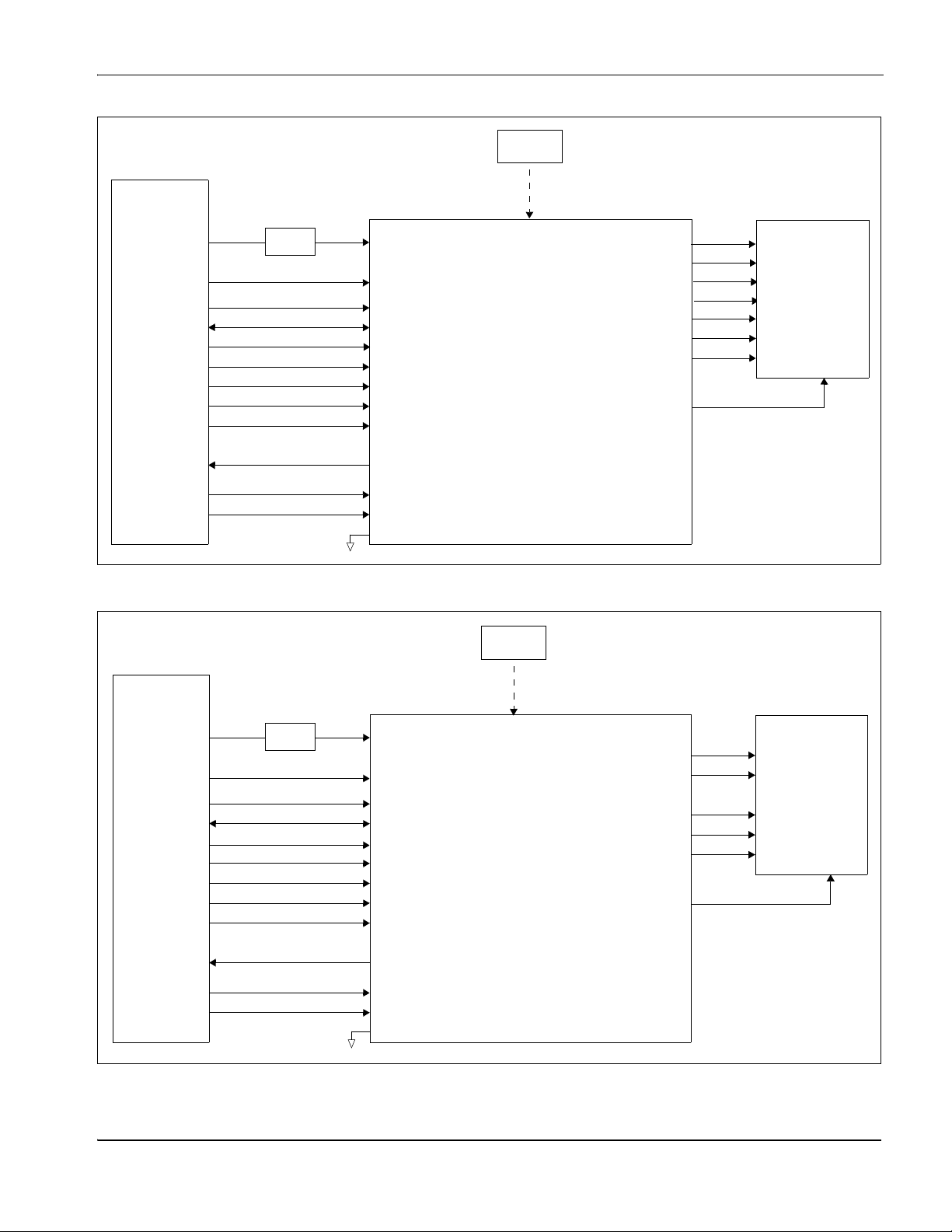

Figure 3-5: Typical System Diagram (MC68K # 1, Motorola 16-Bit 68000) . . . . . . . . . . . . . 16

Figure 3-6: Typical System Diagram (MC68K #2, Motorola 32-Bit 68030). . . . . . . . . . . . . .16

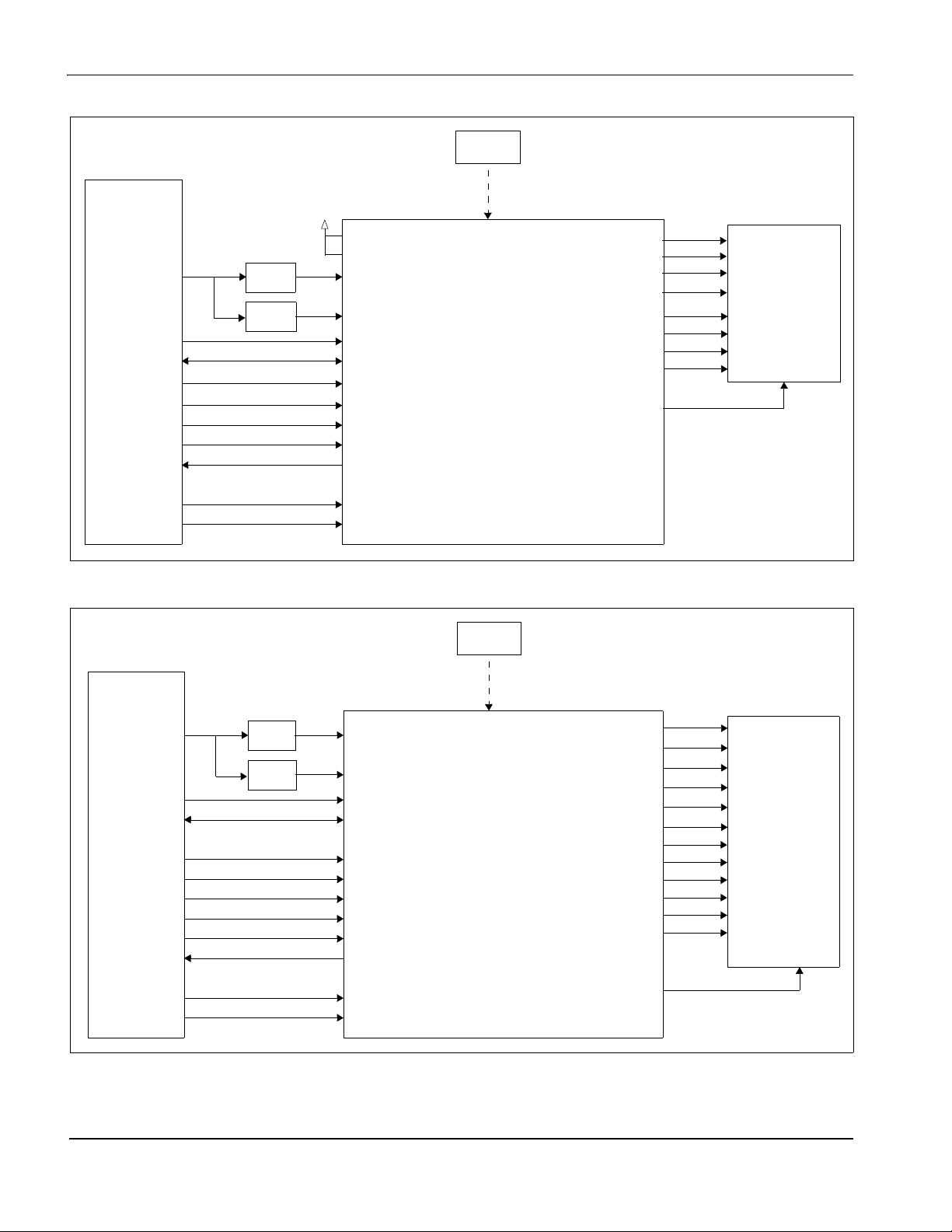

Figure 3-7: Typical System Diagram (Motorola REDCAP2 Bus) . . . . . . . . . . . . . . . . . . .17

Figure 3-8: Typical System Diagram (Motorola MC68EZ328/MC68VZ328 “DragonBall” Bus). . . 17

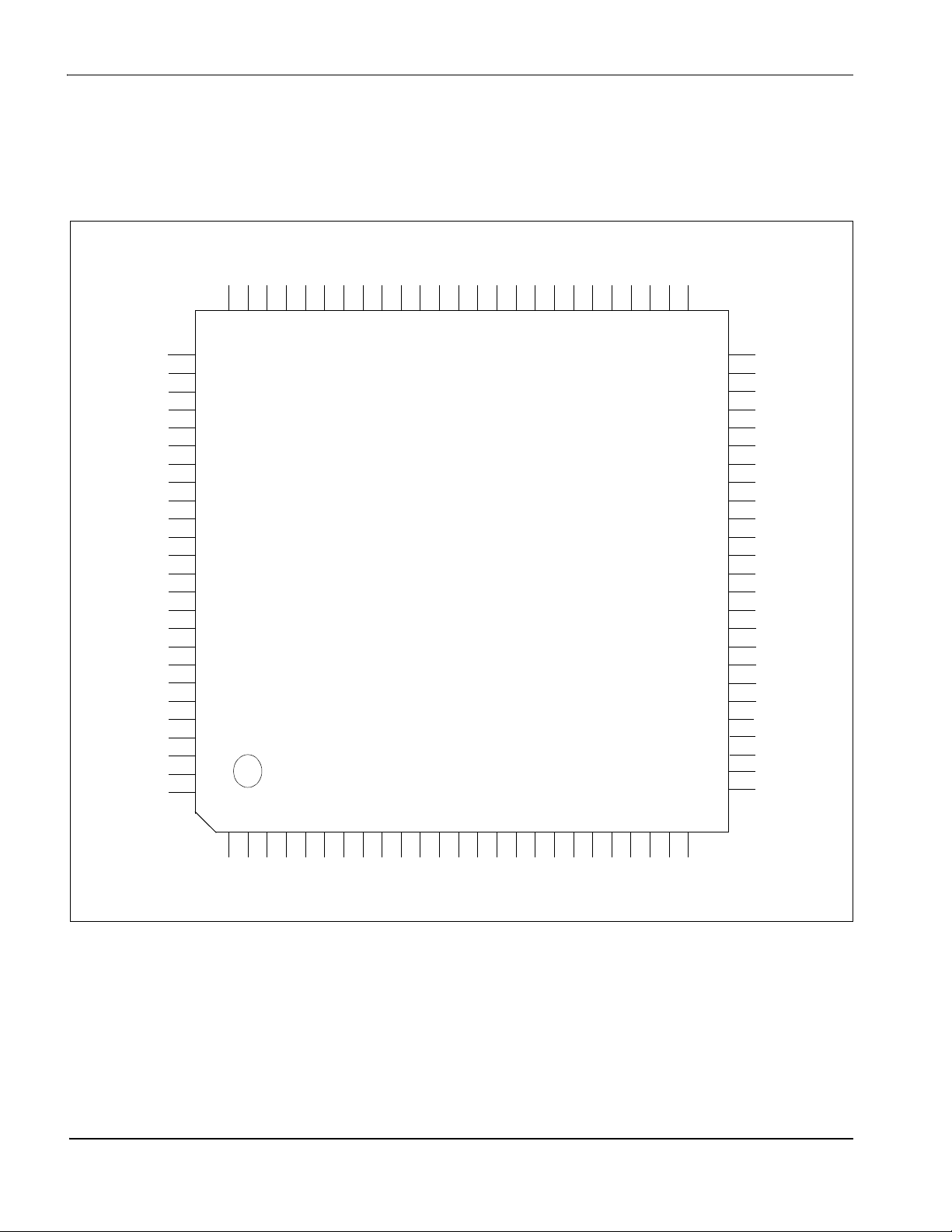

Figure 4-1: Pinout Diagram - TQFP15 - 100pin (S1D13706F00A) . . . . . . . . . . . . . . . . . .18

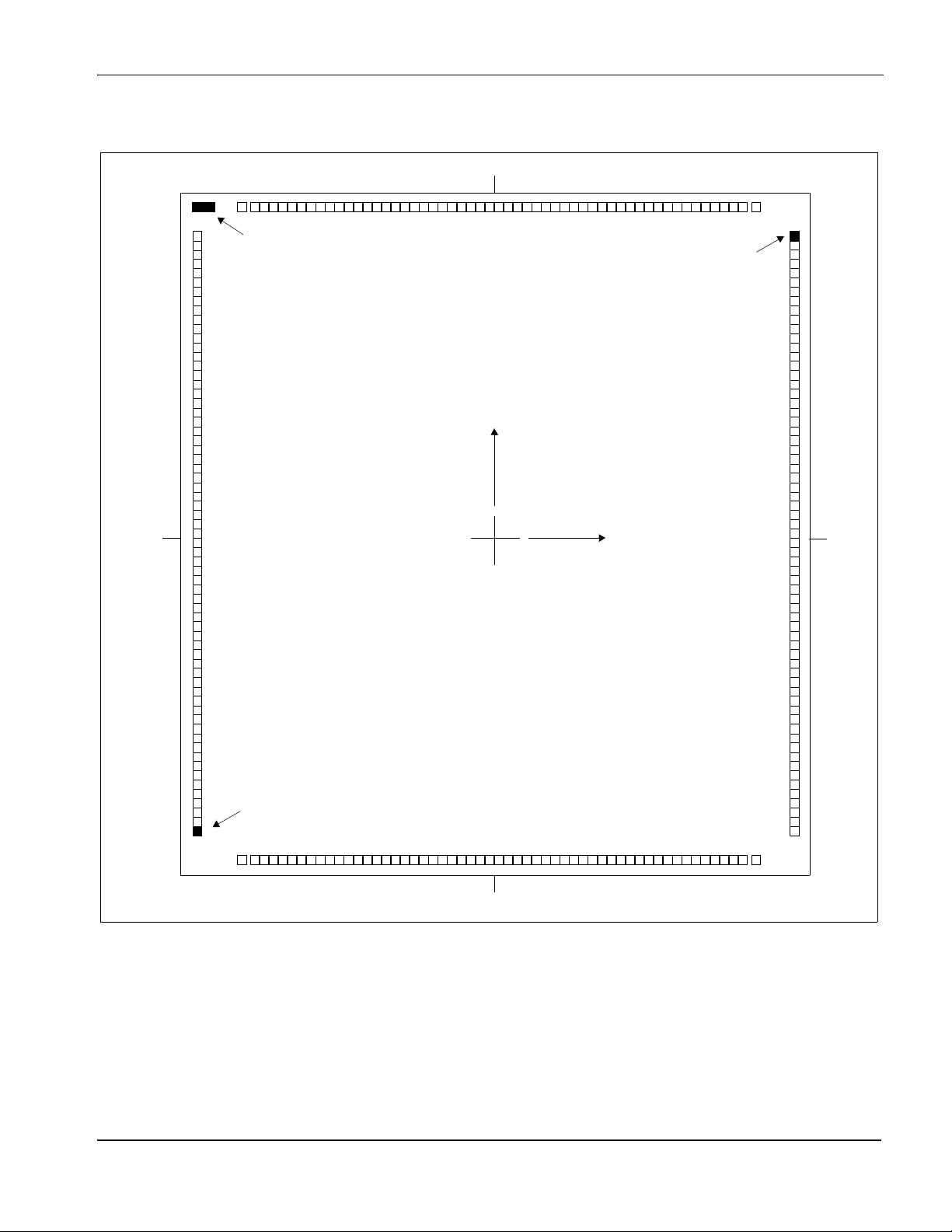

Figure 4-2: Pinout Diagram - Die Form (S1D13706D00A) . . . . . . . . . . . . . . . . . . . . . .19

Figure 6-1: Clock Input Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

Figure 6-2: Generic #1 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 6-3: Generic #2 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Figure 6-4: Hitachi SH-4 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

Figure 6-5: Hitachi SH-3 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .41

Figure 6-6: Motorola MC68K #1 Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . .43

Figure 6-7: Motorola MC68K #2 Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . .45

Figure 6-8: Motorola REDCAP2 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Figure 6-9: Motorola DragonBall Interface with DTACK Timing . . . . . . . . . . . . . . . . . . .49

Figure 6-10: Motorola DragonBall Interface without DTACK# Timing . . . . . . . . . . . . . . . .51

Figure 6-11: Passive/TFT Power-On Sequence Timing . . . . . . . . . . . . . . . . . . . . . . . . .54

Figure 6-12: Passive/TFT Power-Off Sequence Timing . . . . . . . . . . . . . . . . . . . . . . . . .55

Figure 6-13: Panel Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

Figure 6-14: Generic STN Panel Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Figure 6-15: Single Monochrome 4-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . .60

Figure 6-16: Single Monochrome 4-Bit Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . .61

Figure 6-17: Single Monochrome 8-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . .62

Figure 6-18: Single Monochrome 8-Bit Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . .63

Figure 6-19: Single Color 4-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Figure 6-20: Single Color 4-Bit Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . . .65

Figure 6-21: Single Color 8-Bit Panel Timing (Format 1) . . . . . . . . . . . . . . . . . . . . . . . . 66

Figure 6-22: Single Color 8-Bit Panel A.C. Timing (Format 1) . . . . . . . . . . . . . . . . . . . . .67

Figure 6-23: Single Color 8-Bit Panel Timing (Format 2) . . . . . . . . . . . . . . . . . . . . . . . . 68

Figure 6-24: Single Color 8-Bit Panel A.C. Timing (Format 2) . . . . . . . . . . . . . . . . . . . . .69

Figure 6-25: Single Color 16-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Figure 6-26: Single Color 16-Bit Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . .71

Figure 6-27: Generic TFT Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Hardware Functional Specification S1D13706

Issue Date: 2004/02/09 X31B-A-001-09

Page 10

Page 10 Epson Research and Development

Vancouver Design Center

Figure 6-28: 18-Bit TFT Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

Figure 6-29: TFT A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

Figure 6-30: 160x160 Sharp ‘Direct’ HR-TFT Panel Horizontal Timing . . . . . . . . . . . . . . . .76

Figure 6-31: 160x160 Sharp ‘Direct’ HR-TFT Panel Vertical Timing. . . . . . . . . . . . . . . . . .78

Figure 6-32: 320x240 Sharp ‘Direct’ HR-TFT Panel Horizontal Timing . . . . . . . . . . . . . . . .80

Figure 6-33: 320x240 Sharp ‘Direct’ HR-TFT Panel Vertical Timing. . . . . . . . . . . . . . . . . .81

Figure 6-34: 160x240 Epson D-TFD Panel Horizontal Timing . . . . . . . . . . . . . . . . . . . . .82

Figure 6-35: 160x240 Epson D-TFD Panel GCP Horizontal Timing . . . . . . . . . . . . . . . . . .84

Figure 6-36: 160x240 Epson D-TFD Panel Vertical Timing . . . . . . . . . . . . . . . . . . . . . . .85

Figure 6-37: 320x240 Epson D-TFD Panel Horizontal Timing . . . . . . . . . . . . . . . . . . . . .86

Figure 6-38: 320x240 Epson D-TFD Panel GCP Horizontal Timing . . . . . . . . . . . . . . . . . .88

Figure 6-39: 320x240 Epson D-TFD Panel Vertical Timing . . . . . . . . . . . . . . . . . . . . . . .89

Figure 7-1: Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .93

Figure 8-1: Display Data Byte/Word Swap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Figure 8-2: PWM Clock/CV Pulse Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Figure 10-1: 4/8/16 Bit-Per-Pixel Display Data Memory Organization . . . . . . . . . . . . . . . . 131

Figure 11-1: 1 Bit-per-pixel Monochrome Mode Data Output Path . . . . . . . . . . . . . . . . . . 132

Figure 11-2: 2 Bit-per-pixel Monochrome Mode Data Output Path . . . . . . . . . . . . . . . . . . 132

Figure 11-3: 4 Bit-per-pixel Monochrome Mode Data Output Path . . . . . . . . . . . . . . . . . . 133

Figure 11-4: 8 Bit-per-pixel Monochrome Mode Data Output Path . . . . . . . . . . . . . . . . . . 133

Figure 11-5: 1 Bit-Per-Pixel Color Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . 134

Figure 11-6: 2 Bit-Per-Pixel Color Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . 135

Figure 11-7: 4 Bit-Per-Pixel Color Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . 136

Figure 11-8: 8 Bit-per-pixel Color Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . 137

Figure 12-1: Relationship Between The Screen Image and the Image Refreshed in 90× SwivelView.138

Figure 12-2: Relationship Between The Screen Image and the Image Refreshed in 180× SwivelView.140

Figure 12-3: Relationship Between The Screen Image and the Image Refreshed in 270× SwivelView.141

Figure 13-1: Picture-in-Picture Plus with SwivelView disabled . . . . . . . . . . . . . . . . . . . . 143

Figure 13-2: Picture-in-Picture Plus with SwivelView 90° enabled . . . . . . . . . . . . . . . . . . 144

Figure 13-3: Picture-in-Picture Plus with SwivelView 180° enabled . . . . . . . . . . . . . . . . . 144

Figure 13-4: Picture-in-Picture Plus with SwivelView 270° enabled . . . . . . . . . . . . . . . . . 145

Figure 14-1: Byte-swapping for 16 Bpp . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Figure 14-2: Byte-swapping for 1/2/4/8 Bpp . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Figure 16-1: Mechanical Data 100pin TQFP15 (S1D13706F00A) . . . . . . . . . . . . . . . . . . 150

S1D13706 Hardware Functional Specification

X31B-A-001-09 Issue Date: 2004/02/09

Page 11

Epson Research and Development Page 11

Vancouver Design Center

1 Introduction

1.1 Scope

This is the Hardware Functional Specification for the S1D13706 Embedded Memory LCD

Controller. Included in this document are timing diagrams, AC and DC characteristics,

register descriptions, and power management descriptions. This document is intended for

two audiences: Video Subsystem Designers and Software Developers.

For additional documentation related to the S1D13706 see Section 17, “References” on

page 151.

This document is updated as appropriate. Please check the Epson Research and Development Website at www.erd.epson.com for the latest revision of this document before

beginning any development.

We appreciate your comments on our documentation. Please contact us via email at

documentation@erd.epson.com.

1.2 Overview Description

The S1D13706 is a color/monochrome LCD graphics controller with an embedded 80K

byte SRAM display buffer. While supporting all other panel types, the S1D13706 is the

only LCD controller to directly interface to both the Epson D-TFD and the Sharp HR-TFT

family of products thus removing the requirement of an external Timing Control IC. This

high level of integration provides a low cost, low power, single chip solution to meet the

demands of embedded markets such as Mobile Communications devices and Palm-size

PCs, where board size and battery life are major concerns.

The S1D13706 utilizes a guaranteed low-latency CPU architecture providing support for

microprocessors without READY/WAIT# handshaking signals. The 32-bit internal data

path provides high performance bandwidth into display memory allowing for fast screen

updates.

Products requiring a rotated display image can take advantage of the SwivelView

which provides hardware rotation of the display memory transparent to the software application. The S1D13706 also provides support for “Picture-in-Picture Plus” (a variable size

Overlay window).

The S1D13706 provides impressive support for Palm OS

tiality to CPU type or operating system makes it an ideal display solution for a wide variety

of applications.

TM

feature

handhelds, however its impar-

Hardware Functional Specification S1D13706

Issue Date: 2004/02/09 X31B-A-001-09

Page 12

Page 12 Epson Research and Development

Vancouver Design Center

2 Features

2.1 Integrated Frame Buffer

• Embedded 80K byte SRAM display buffer.

2.2 CPU Interface

• Direct support of the following interfaces:

Generic MPU bus interface using WAIT# signal.

Hitachi SH-3.

Hitachi SH-4.

Motorola M68K.

Motorola MC68EZ328/MC68VZ328 DragonBall.

Motorola “REDCAP2” - no WAIT# signal.

• 8-bit processor support with “glue logic”.

• “Fixed” low-latency CPU access times.

• Registers are memory-mapped - M/R# input selects between memory and register

address space.

• The complete 80K byte display buffer is directly and contiguously available through the

17-bit address bus.

• Single level CPU write buffer.

2.3 Display Support

• Single-panel, single-drive passive displays.

• 4/8-bit monochrome LCD interface.

• 4/8/16-bit color LCD interface.

• Active Matrix TFT interface.

• 9/12/18-bit interface.

• ‘Direct’ support for 18-bit Epson D-TFD interface.

• ‘Direct’ support for 18-bit Sharp HR-TFT interface.

S1D13706 Hardware Functional Specification

X31B-A-001-09 Issue Date: 2004/02/09

Page 13

Epson Research and Development Page 13

Vancouver Design Center

2.4 Display Modes

• 1/2/4/8/16 bit-per-pixel (bpp) color depths.

• Up to 64 gray shades using Frame Rate Modulation (FRM) and dithering on monochrome passive LCD panels.

• Up to 64K colors on passive STN panels.

• Up to 64K colors on active matrix LCD panels.

• Example resolutions:

320x240 at a color depth of 8 bpp

160x160 at a color depth of 16 bpp

160x240 at a color depth of 16 bpp

2.5 Display Features

• SwivelView™: 90°, 180°, 270° counter-clockwise hardware rotation of display image.

• “Picture-in-Picture Plus”: displays a variable size window overlaid over background

image.

• Double Buffering/Multi-pages: provides smooth animation and instantaneous screen

2.6 Clock Source

• Two clock inputs: CLKI and CLKI2. It is possible to use one clock input only.

• Bus clock is derived from CLKI and can be internally divided by 2, 3, or 4.

• Memory clock is derived from bus clock. It can be internally divided by 2, 3, or 4.

• Pixel clock can be derived from CLKI, CLKI2, bus clock, or memory clock. It can be

2.7 Miscellaneous

• Hardware/Software Video Invert.

• Software Power Save mode.

• General Purpose Input/Output pins are available.

• 100-pin TQFP15 package.

• 104-pin CFLGA package.

updates.

internally divided by 2, 3, 4, or 8.

• Die form available.

Hardware Functional Specification S1D13706

Issue Date: 2004/02/09 X31B-A-001-09

Page 14

Page 14 Epson Research and Development

Vancouver Design Center

3 Typical System Implementation Diagrams

.

Oscillator

Generic #1

BUS

A[27:17]

CSn#

A[16:1]

D[15:0]

WE0#

WE1#

RD0#

RD1#

WAIT#

BUSCLK

RESET#

HIOVDD

Decoder

VSS

BS#

M/R#

CS#

AB[16:1]

DB[15:0]

WE0#

WE1#

RD#

RD/WR#

WAIT#

CLKI

RESET#

AB0

CLKI2

S1D13706

FPDAT[15:0]

FPFRAME

FPLINE

FPSHIFT

DRDY

GPO

D[15:0]

FPFRAME

FPLINE

FPSHIFT

MOD

16-bit

Single

LCD

Display

Bias Power

Generic #2

BUS

A[27:17]

CSn#

A[16:0]

D[15:0]

BHE#

WAIT#

BUSCLK

RESET#

WE#

RD#

Figure 3-1: Typical System Diagram (Generic #1 Bus)

.

Oscillator

VDD

Decoder

BS#

RD/WR#

M/R#

CS#

AB[16:0]

DB[15:0]

WE0#

WE1#

RD#

WAIT#

CLKI

RESET#

S1D13706

CLKI2

FPDAT[8:0]

FPFRAME

FPLINE

FPSHIFT

DRDY

GPO

D[8:0]

FPFRAME

FPLINE

FPSHIFT

DRDY

9-bit

TFT

Display

Bias Power

Figure 3-2: Typical System Diagram (Generic #2 Bus)

S1D13706 Hardware Functional Specification

X31B-A-001-09 Issue Date: 2004/02/09

Page 15

Epson Research and Development Page 15

Vancouver Design Center

.

Oscillator

SH-4

BUS

A[25:17]

CSn#

A[16:1]

D[15:0]

WE0#

WE1#

BS#

RD/WR#

RD#

RDY#

CKIO

RESET#

Decoder

VSS

M/R#

CS#

AB[16:1]

DB[15:0]

WE0#

WE1#

BS#

RD/WR#

RD#

WAIT#

CLKI

RESET#

AB0

CLKI2

S1D13706

Figure 3-3: Typical System Diagram (Hitachi SH-4 Bus)

.

Oscillator

FPDAT15

FPDAT12

FPDAT[9:0]

FPFRAME

FPLINE

FPSHIFT

DRDY

GPO

D11

D10

D[9:0]

FPFRAME

FPLINE

FPSHIFT

DRDY

12-bit

TFT

Display

Bias Power

SH-3

BUS

A[25:17]

CSn#

A[16:1]

D[15:0]

WE0#

WE1#

BS#

RD/WR#

RD#

WAIT#

CKIO

RESET#

Decoder

VSS

M/R#

CS#

AB[16:1]

DB[15:0]

WE0#

WE1#

BS#

RD/WR#

RD#

WAIT#

CLKI

RESET#

AB0

CLKI2

S1D13706

Figure 3-4: Typical System Diagram (Hitachi SH-3 Bus)

FPDAT[17:0]

FPFRAME

FPLINE

FPSHIFT

DRDY

GPO

D[17:0]

FPFRAME

FPLINE

FPSHIFT

DRDY

18-bit

TFT

Display

Bias Power

Hardware Functional Specification S1D13706

Issue Date: 2004/02/09 X31B-A-001-09

Page 16

Page 16 Epson Research and Development

Vancouver Design Center

.

Oscillator

MC68K #1

BUS

A[23:17]

FC0, FC1

A[16:1]

D[15:0]

LDS#

UDS#

AS#

R/W#

DTACK#

HIOVDD

Decoder

Decoder

RD#

WE0#

M/R#

CS#

AB[16:1]

DB[15:0]

AB0

WE1#

BS#

RD/WR#

WAIT#

CLKI2

S1D13706

FPDAT[17:0]

FPFRAME

FPLINE

FPSHIFT

GPIO0

GPIO1

GPIO2

GPIO3

GPO

D[17:0]

SPS

LP

CLK

PS

CLS

REV

SPL

18-bit

HR-TFT

Display

Bias Power

RESET#

MC68K #2

BUS

A[31:17]

FC0, FC1

A[16:0]

D[31:16]

R/W#

DSACK1#

CLK

DS#

AS#

SIZ1

SIZ0

CLKI

RESET#

Figure 3-5: Typical System Diagram (MC68K # 1, Motorola 16-Bit 68000)

.

Oscillator

Decoder

Decoder

M/R#

CS#

AB[16:0]

DB[15:0]

WE1#

BS#

RD/WR#

RD#

WE0#

WAIT#

CLKI2

S1D13706

FPDAT[17:0]

FPFRAME

FPLINE

FPSHIFT

DRDY

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

D[17:0]

DY

LP

XSCL

GCP

XINH

YSCL

FR

FRS

RES

DD_P1

YSCLD

18-bit

D-TFD

Display

XSET (Bias Power)

CLK

RESET#

CLKI

RESET#

GPO

Figure 3-6: Typical System Diagram (MC68K #2, Motorola 32-Bit 68030)

S1D13706 Hardware Functional Specification

X31B-A-001-09 Issue Date: 2004/02/09

Page 17

Epson Research and Development Page 17

Vancouver Design Center

.

Oscillator

REDCAP2

BUS

A[21:17]

CSn

A[16:1]

D[15:0]

R/W

OE

EB1

EB0

CLK

RESET_OUT

Decoder

HIOVDD

VSS

BS#

M/R#

CS#

AB[16:1]

DB[15:0]

RD/WR#

RD#

WE0#

WE1#

CLKI

RESET#

AB0

CLKI2

S1D13706

FPDAT[7:4]

FPSHIFT

FPFRAME

FPLINE

DRDY

GPO

D[3:0]

FPSHIFT

FPFRAME

FPLINE

MOD

4-bit

Single

LCD

Display

Bias Power

*Note: CSn# can be any of CS0-CS4

Figure 3-7: Typical System Diagram (Motorola REDCAP2 Bus)

MC68EZ328/

MC68VZ328

DragonBall

BUS

A[25:17]

CS

A[16:1]

D[15:0]

LWE

UWE

OE

DTACK

CLKO

RESET

X

Decoder

HIOVDD

VSS

BS#

RD/WR#

M/R#

CS#

AB[16:1]

DB[15:0]

WE0#

WE1#

RD#

WAIT#

CLKI

RESET#

AB0

.

Oscillator

CLKI2

S1D13706

FPDAT[7:0]

FPSHIFT

FPFRAME

FPLINE

DRDY

GPO

D[7:0]

FPSHIFT

FPFRAME

FPLINE

MOD

8-bit

Single

LCD

Display

Bias Power

Figure 3-8: Typical System Diagram (Motorola MC68EZ328/MC68VZ328 “DragonBall” Bus)

Hardware Functional Specification S1D13706

Issue Date: 2004/02/09 X31B-A-001-09

Page 18

Page 18 Epson Research and Development

Vancouver Design Center

4 Pins

4.1 Pinout Diagram - TQFP15 - 100pin

75747372717069686766656463626160595857565554535251

VSS

FPDAT17

FPDAT16

FPDAT15

FPDAT14

FPDAT13

FPDAT12

FPDAT11

FPDAT10

FPDAT9

FPDAT8

FPDAT7

NIOVDD

VSS

FPDAT6

FPDAT5

FPDAT4

FPDAT3

FPDAT2

FPDAT1

FPDAT0

FPSHIFT

FPLINE

FPFRAME

COREVDD

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

NIOVDD

CLKI2

CNF7

CNF6

CNF5

CNF4

CNF3

CNF2

CNF1

CNF0

TESTEN

AB16

AB15

AB14

AB13

AB12

AB11

AB10

AB9

AB8

AB7

AB6

AB5

COREVDD

AB4

VSS

AB3

AB2

AB1

AB0

CS#

50

VSS

DRDY

GPO

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

VSS

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

DB8

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

NIOVDD

CVOUT

DB10

PWMOUT

NIOVDD

HIOVDD

VSS

DB9

S1D13706

RD/WR#

RESET#

WE1#

BS#

RD#

WE0#

M/R#

VSS

HIOVDD

WAIT#

DB15

DB14

DB13

DB12

CLKI

DB11

1

2

3

4

5

6

7

101112131415161718192021222324

8

9

25

Figure 4-1: Pinout Diagram - TQFP15 - 100pin (S1D13706F00A)

Note

Package type: 100 pin surface mount TQFP15

S1D13706 Hardware Functional Specification

X31B-A-001-09 Issue Date: 2004/02/09

Page 19

Epson Research and Development Page 19

Vancouver Design Center

4.2 Pinout Diagram - Die Form

120125130135140145150155160165170

175

DIE No. X5534D

180

Unusable Pad

115

185

190

195

200

205

210

215

220

225

230

Y

(0,0)

110

105

100

95

90

X

85

80

75

70

65

235

Unusable Pad

15 10 403530252015

555045

60

Figure 4-2: Pinout Diagram - Die Form (S1D13706D00A)

Chip Size: 5.88 x 6.55 mm

PAD size: 68 x 68

Hardware Functional Specification S1D13706

Issue Date: 2004/02/09 X31B-A-001-09

µm

Page 20

Page 20 Epson Research and Development

Vancouver Design Center

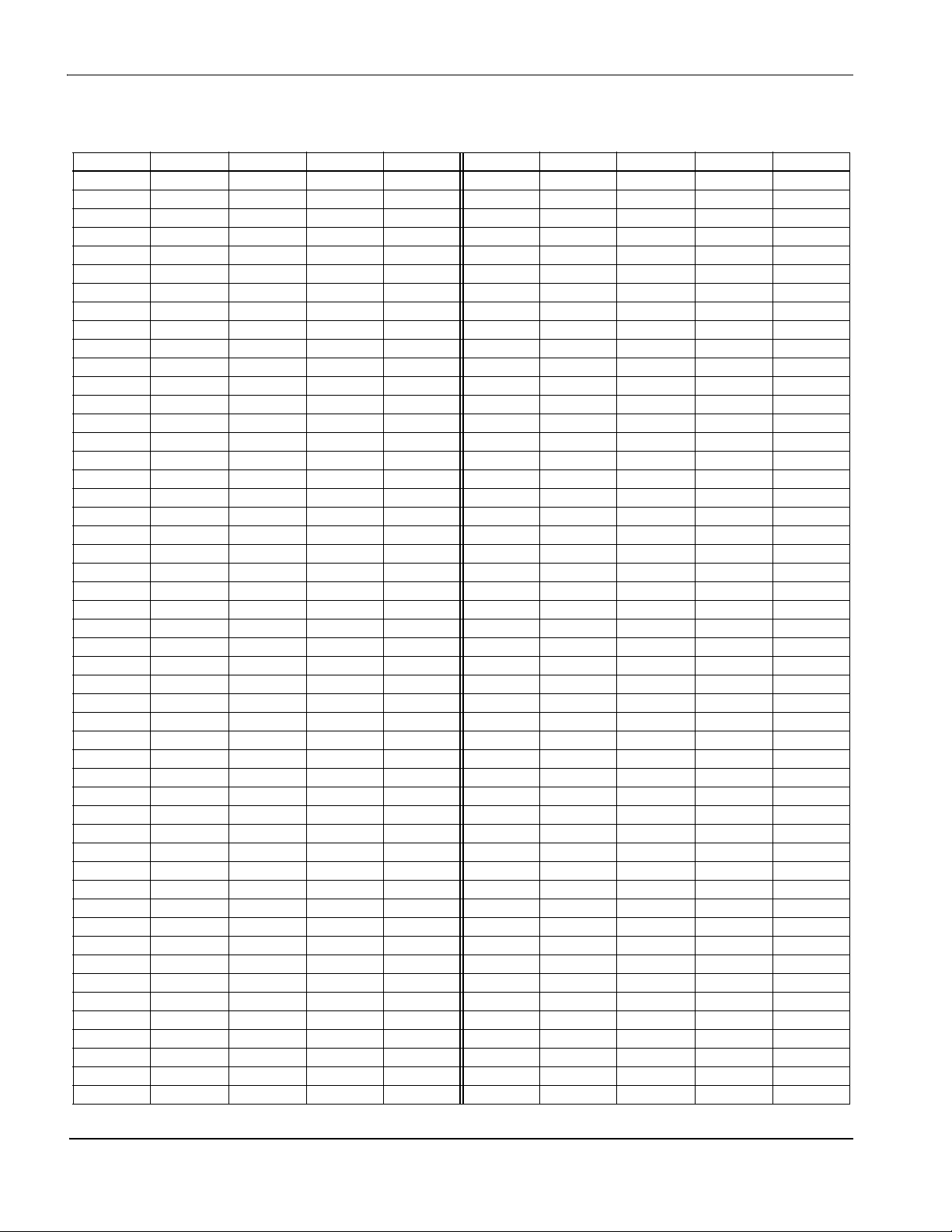

Table 4-1: Pinout Assignments - Die Form (S1D13706D00A)

Pin No. Pad No. Pin Name X (µm) Y (µm) Pin No. Pad No. Pin Name X (µm) Y (µm)

1 1 LVDD -2331 -3149 51 119 LVDD 2813 2667

2 3 AB3 -2100 -3149 52 122 FPFRAME 2100 3149

3 5 AB2 -1932 -3149 53 124 FPLINE 1932 3149

4 8 AB1 -1680 -3149 54 127 FPSHIFT 1680 3149

5 10 AB0 -1512 -3149 55 129 FPDAT0 1512 3149

6 12 CS# -1344 -3149 56 131 FPDAT1 1344 3149

7 15 M/R# -1092 -3149 57 134 FPDAT2 1092 3149

8 17 BS# -924 -3149 58 136 FPDAT3 924 3149

9 20 RD# -672 -3149 59 139 FPDAT4 672 3149

10 22 WE0# -504 -3149 60 141 FPDAT5 504 3149

11 24 WE1# -336 -3149 61 143 FPDAT6 336 3149

12 27 RD/WR# -84 -3149 62 146 VSS 84 3149

13 29 RESET# 84 -3149 63 148 HVDD -84 3149

14 31 VSS 252 -3149 64 150 FPDAT7 -252 3149

15 34 CLKI 504 -3149 65 153 FPDAT8 -504 3149

16 36 HVDD 672 -3149 66 155 FPDAT9 -672 3149

17 39 WAIT# 924 -3149 67 158 FPDAT10 -924 3149

18 41 DB15 1092 -3149 68 160 FPDAT11 -1092 3149

19 43 DB14 1260 -3149 69 162 FPDAT12 -1260 3149

20 46 DB13 1512 -3149 70 165 FPDAT13 -1512 3149

21 48 DB12 1680 -3149 71 167 FPDAT14 -1680 3149

22 50 DB11 1848 -3149 72 169 FPDAT15 -1848 3149

23 53 DB10 2100 -3149 73 172 FPDAT16 -2100 3149

24 55 DB9 2331 -3149 74 174 FPDAT17 -2331 3149

25 58 VSS 2813 -2478 75 177 VSS -2813 2478

26 60 HVDD 2813 -2310 76 179 HVDD -2813 2310

27 62 DB8 2813 -2142 77 181 CLKI2 -2813 2142

28 65 DB7 2813 -1890 78 184 CNF7 -2813 1890

29 67 DB6 2813 -1722 79 186 CNF6 -2813 1722

30 70 DB5 2813 -1470 80 189 CNF5 -2813 1470

31 72 DB4 2813 -1302 81 191 CNF4 -2813 1302

32 74 DB3 2813 -1134 82 193 CNF3 -2813 1134

33 77 DB2 2813 -882 83 196 CNF2 -2813 882

34 79 DB1 2813 -714 84 198 CNF1 -2813 714

35 81 DB0 2813 -546 85 200 CNF0 -2813 546

36 84 VSS 2813 -294 86 203 TESTEN -2813 294

37 86 HVDD 2813 -126 87 205 AB16 -2813 126

38 89 PWMOUT 2813 126 88 208 AB15 -2813 -126

39 91 GPIO6 2813 294 89 210 AB14 -2813 -294

40 93 GPIO5 2813 462 90 212 AB13 -2813 -462

41 96 GPIO4 2813 714 91 215 AB12 -2813 -714

42 98 GPIO3 2813 882 92 217 AB11 -2813 -882

43 100 GPIO2 2813 1050 93 219 AB10 -2813 -1050

44 103 GPIO1 2813 1302 94 222 AB9 -2813 -1302

45 105 GPIO0 2813 1470 95 224 AB8 -2813 -1470

46 108 CVOUT 2813 1722 96 227 AB7 -2813 -1722

47 110 GPO 2813 1890 97 229 AB6 -2813 -1890

48 112 DRDY 2813 2058 98 231 AB5 -2813 -2058

49 115 HVDD 2813 2310 99 234 AB4 -2813 -2310

50 117 VSS 2813 2478 100 236 VSS -2813 -2478

S1D13706 Hardware Functional Specification

X31B-A-001-09 Issue Date: 2004/02/09

Page 21

Epson Research and Development Page 21

Vancouver Design Center

4.3 Pin Descriptions

Key:

I = Input

O=Output

IO = Bi-Directional (Input/Output)

P=Power pin

LIS = LVTTL

LI = LVTTL input

LB2A = LVTTL IO buffer (6mA/-6mA@3.3V)

LB3P = Low noise LVTTL IO buffer (12mA/-12mA@3.3V)

LO3 = Low noise LVTTL Output buffer (12mA/-12mA@3.3V)

LB3M = Low noise LVTTL IO buffer with input mask (12mA/-12mA@3.3V)

T1 = Test mode control input with pull-down resistor (typical value of 50Ω at 3.3V)

Hi-Z = High Impedance

a

Schmitt input

a

LVTTL is Low Voltage TTL (see Section 5, “D.C. Characteristics” on page 31).

4.3.1 Host Interface

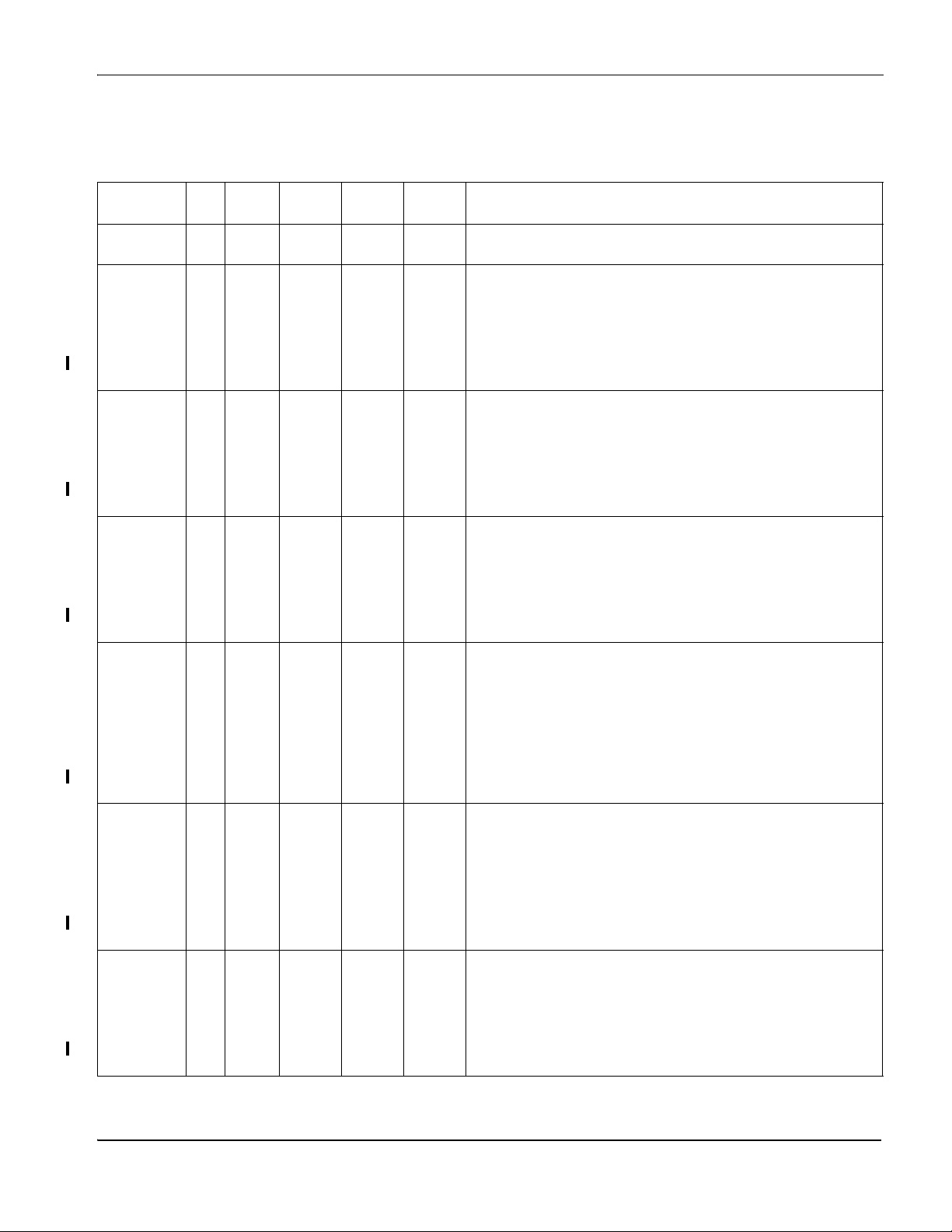

Table 4-2: Host Interface Pin Descriptions

Pin Name Type Pin # Cell

AB0 I 5 LIS HIOVDD 0

AB[16:1] I

87-99,

2-4

LI HIOVDD 0 System address bus bits 16-1.

IO

Vol tage

RESET#

State

Description

This input pin has multiple functions.

• For Generic #1, this pin is not used and should be connected

to VSS.

• For Generic #2, this pin inputs system address bit 0 (A0).

• For SH-3/SH-4, this pin is not used and should be connected

to VSS.

• For MC68K #1, this pin inputs the lower data strobe (LDS#).

• For MC68K #2, this pin inputs system address bit 0 (A0).

• For REDCAP2, this pin is not used and should be connected

to VSS.

• For DragonBall, this pin is not used and should be connected

to VSS.

See Table 4-8: “Host Bus Interface Pin Mapping,” on page 29 for

summary.

Hardware Functional Specification S1D13706

Issue Date: 2004/02/09 X31B-A-001-09

Page 22

Page 22 Epson Research and Development

Vancouver Design Center

Table 4-2: Host Interface Pin Descriptions

IO

Pin Name Type Pin # Cell

DB[15:0] IO

18-24,

27-35

LB2A HIOVDD Hi-Z

Volta ge

WE0# I 10 LIS HIOVDD 1

WE1# I 11 LIS HIOVDD 1

CS# I 6 LI HIOVDD 1

M/R# I 7 LIS HIOVDD 0

RESET#

State

Input data from the system data bus.

• For Generic #1, these pins are connected to D[15:0].

• For Generic #2, these pins are connected to D[15:0].

• For SH-3/SH-4, these pins are connected to D[15:0].

• For MC68K #1, these pins are connected to D[15:0].

• For MC68K #2, these pins are connected to D[31:16] for a 32bit device (e.g. MC68030) or D[15:0] for a 16-bit device (e.g.

MC68340).

• For REDCAP2, these pins are connected to D[15:0].

• For DragonBall, these pins are connected to D[15:0].

See Table 4-8: “Host Bus Interface Pin Mapping,” on page 29 for

summary.

This input pin has multiple functions.

• For Generic #1, this pin inputs the write enable signal for the

lower data byte (WE0#).

• For Generic #2, this pin inputs the write enable signal (WE#)

• For SH-3/SH-4, this pin inputs the write enable signal for data

byte 0 (WE0#).

• For MC68K #1, this pin must be tied to HIO V

• For MC68K #2, this pin inputs the bus size bit 0 (SIZ0).

• For REDCAP2, this pin inputs the byte enable signal for the

D[7:0] data byte (EB1).

• For DragonBall, this pin inputs the byte enable signal for the

D[7:0] data byte (LWE

See Table 4-8: “Host Bus Interface Pin Mapping,” on page 29 for

summary.

This input pin has multiple functions.

• For Generic #1, this pin inputs the write enable signal for the

upper data byte (WE1#).

• For Generic #2, this pin inputs the byte enable signal for the

high data byte (BHE#).

• For SH-3/SH-4, this pin inputs the write enable signal for data

byte 1 (WE1#).

• For MC68K #1, this pin inputs the upper data strobe (UDS#).

• For MC68K #2, this pin inputs the data strobe (DS#).

• For REDCAP2, this pin inputs the byte enable signal for the

D[15:8] data byte (EB0

• For DragonBall, this pin inputs the byte enable signal for the

D[15:8] data byte (UWE

See Table 4-8: “Host Bus Interface Pin Mapping,” on page 29 for

summary.

Chip select input. See Table 4-8: “Host Bus Interface Pin Mapping,”

on page 29 for summary.

This input pin is used to select between the display buffer and

register address spaces of the S1D13706. M/R# is set high to

access the display buffer and low to access the registers. See

Table 4-8: “Host Bus Interface Pin Mapping,” on page 29 for

summary.

Description

DD

).

).

).

S1D13706 Hardware Functional Specification

X31B-A-001-09 Issue Date: 2004/02/09

Page 23

Epson Research and Development Page 23

Vancouver Design Center

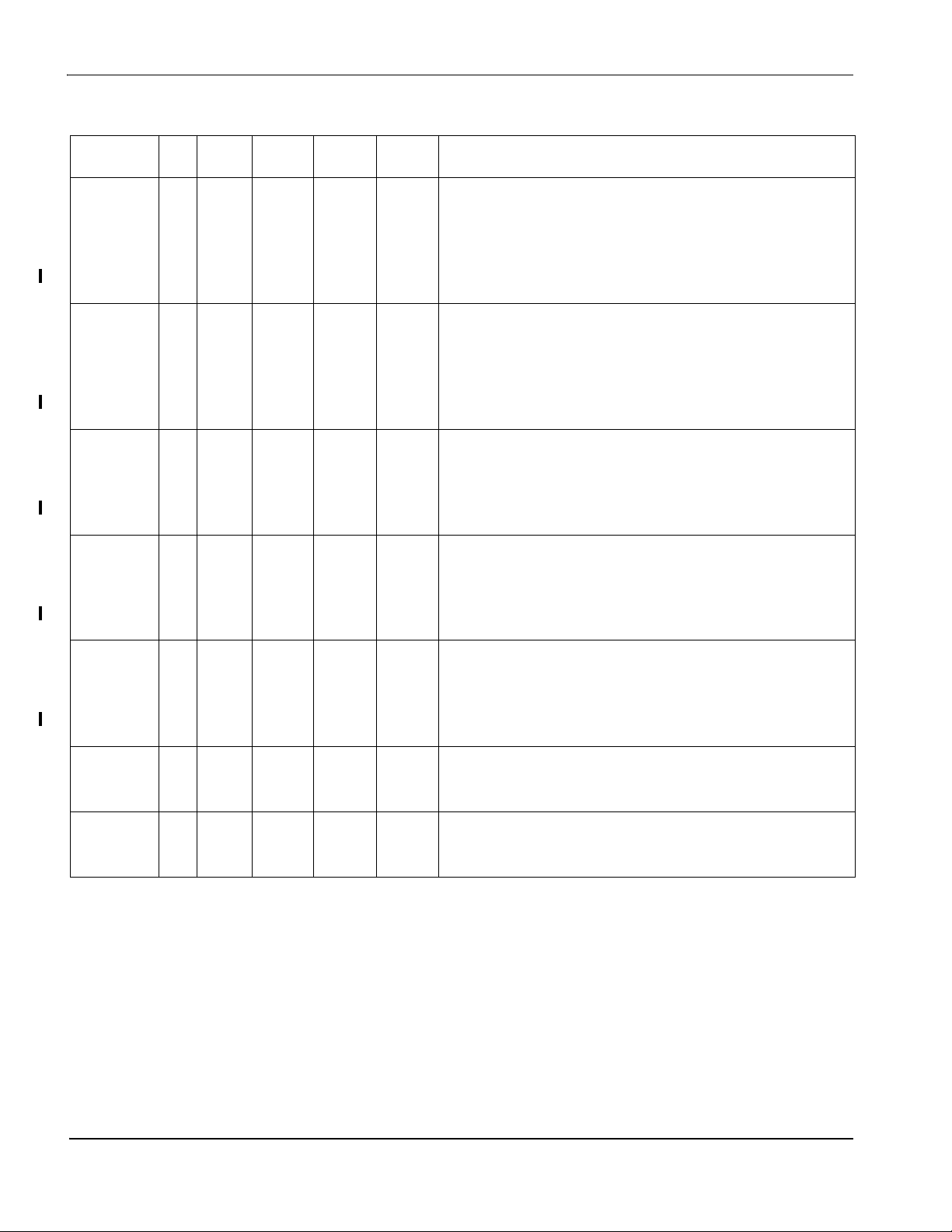

Table 4-2: Host Interface Pin Descriptions

IO

Pin Name Type Pin # Cell

Vol tage

RESET#

BS# I 8 LIS HIOVDD 1

RD/WR# I 12 LIS HIOVDD 1

RD# I 9 LIS HIOVDD 1

State

This input pin has multiple functions.

• For Generic #1, this pin must be tied to HIO VDD.

• For Generic #2, this pin must be tied to HIO VDD.

• For SH-3/SH-4, this pin inputs the bus start signal (BS#).

• For MC68K #1, this pin inputs the address strobe (AS#).

• For MC68K #2, this pin inputs the address strobe (AS#).

• For REDCAP2, this pin must be tied to HIO V

• For DragonBall, this pin must be tied to HIO VDD.

See Table 4-8: “Host Bus Interface Pin Mapping,” on page 29 for

summary.

This input pin has multiple functions.

• For Generic #1, this pin inputs the read command for the

upper data byte (RD1#).

• For Generic #2, this pin must be tied to HIO V

• For SH-3/SH-4, this pin inputs the RD/WR# signal. The

S1D13706 needs this signal for early decode of the bus cycle.

• For MC68K #1, this pin inputs the R/W# signal.

• For MC68K #2, this pin inputs the R/W# signal.

• For REDCAP2, this pin inputs the R/W

• For DragonBall, this pin must be tied to HIO VDD.

See Table 4-8: “Host Bus Interface Pin Mapping,” on page 29 for

summary.

This input pin has multiple functions.

• For Generic #1, this pin inputs the read command for the

lower data byte (RD0#).

• For Generic #2, this pin inputs the read command (RD#).

• For SH-3/SH-4, this pin inputs the read signal (RD#).

• For MC68K #1, this pin must be tied to HIO VDD.

• For MC68K #2, this pin inputs the bus size bit 1 (SIZ1).

• For REDCAP2, this pin inputs the output enable (OE).

• For DragonBall, this pin inputs the output enable (OE

See Table 4-8: “Host Bus Interface Pin Mapping,” on page 29 for

summary.

Description

signal.

DD

DD

.

.

).

Hardware Functional Specification S1D13706

Issue Date: 2004/02/09 X31B-A-001-09

Page 24

Page 24 Epson Research and Development

Vancouver Design Center

Table 4-2: Host Interface Pin Descriptions

IO

Pin Name Type Pin # Cell

Volta ge

RESET#

WAIT# O 17 LB2A HIOVDD Hi-Z

RESET# I 13 LIS HIOVDD 0

State

During a data transfer, this output pin is driven active to force the

system to insert wait states. It is driven inactive to indicate the

completion of a data transfer. WAIT# is released to the high

impedance state after the data transfer is complete. Its active

polarity is configurable. See Table 4-7: “Summary of PowerOn/Reset Options,” on page 28.

• For Generic #1, this pin outputs the wait signal (WAIT#).

• For Generic #2, this pin outputs the wait signal (WAIT#).

• For SH-3 mode, this pin outputs the wait request signal

(WAIT#).

• For SH-4 mode, this pin outputs the device ready signal

(RDY#).

• For MC68K #1, this pin outputs the data transfer acknowledge

signal (DTACK#).

• For MC68K #2, this pin outputs the data transfer and size

acknowledge bit 1 (DSACK1#).

• For REDCAP2, this pin is unused (Hi-Z).

• For DragonBall, this pin outputs the data transfer

acknowledge signal (DTACK

See Table 4-8: “Host Bus Interface Pin Mapping,” on page 29 for

summary.

Active low input to set all internal registers to the default state and

to force all signals to their inactive states.

Description

).

S1D13706 Hardware Functional Specification

X31B-A-001-09 Issue Date: 2004/02/09

Page 25

Epson Research and Development Page 25

Vancouver Design Center

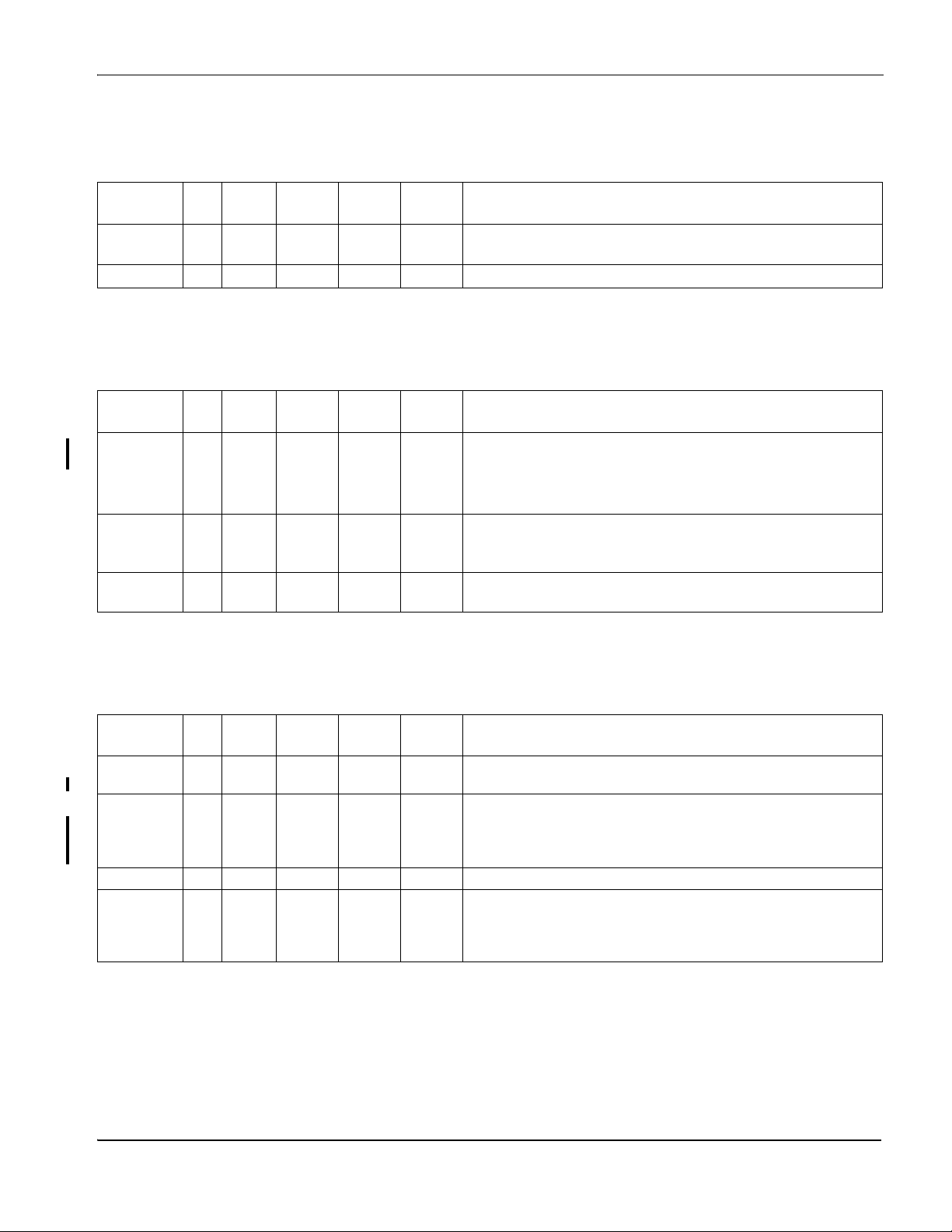

4.3.2 LCD Interface

Table 4-3: LCD Interface Pin Descriptions

IO

Pin Name Type Pin # Cell

FPDAT[17:0] O

FPFRAME O 52 LB3P NIOVDD 0

FPLINE O 53 LB3P NIOVDD 0

FPSHIFT O 54 LB3P NIOVDD 0

DRDY O 48 LO3 NIOVDD 0

GPIO0 IO 45 LB3M NIOVDD 0

GPIO1 IO 44 LB3M NIOVDD 0

74-64,

61-55

LB3P NIOVDD 0 Panel Data bits 17-0.

Volta ge

RESET#

State

This output pin has multiple functions.

•Frame Pulse

• SPS for Sharp HR-TFT

• DY for Epson D-TFD

See Table 4-9: “LCD Interface Pin Mapping,” on page 30 for

summary.

This output pin has multiple functions.

•Line Pulse

• LP for Sharp HR-TFT

• LP for Epson D-TFD

See Table 4-9: “LCD Interface Pin Mapping,” on page 30 for

summary.

This output pin has multiple functions.

• Shift Clock

• CLK for Sharp HR-TFT

• XSCL for Epson D-TFD

See Table 4-9: “LCD Interface Pin Mapping,” on page 30 for

summary.

This output pin has multiple functions.

• Display enable (DRDY) for TFT panels

• 2nd shift clock (FPSHIFT2) for passive LCD with Format 1

interface

• GCP for Epson D-TFD

• LCD backplane bias signal (MOD) for all other LCD panels

See Table 4-9: “LCD Interface Pin Mapping,” on page 30 for

summary.

This pin has multiple functions.

• PS for Sharp HR-TFT

• XINH for Epson D-TFD

• General purpose IO pin 0 (GPIO0)

• Hardware Video Invert

See Table 4-9: “LCD Interface Pin Mapping,” on page 30 for

summary.

This pin has multiple functions.

• CLS for Sharp HR-TFT

• YSCL for Epson D-TFD

• General purpose IO pin 1 (GPIO1)

See Table 4-9: “LCD Interface Pin Mapping,” on page 30 for

summary.

Description

Hardware Functional Specification S1D13706

Issue Date: 2004/02/09 X31B-A-001-09

Page 26

Page 26 Epson Research and Development

Vancouver Design Center

Table 4-3: LCD Interface Pin Descriptions

IO

Pin Name Type Pin # Cell

Vol tage

RESET#

State

GPIO2 IO 43 LB3M NIOVDD 0

GPIO3 IO 42 LB3M NIOVDD 0

GPIO4 IO 41 LB3M NIOVDD 0

GPIO5 IO 40 LB3M NIOVDD 0

GPIO6 IO 39 LB3M NIOVDD 0

PWMOUT O 38 LB3P NIOVDD 0

CVOUT O 46 LB3P NIOVDD 0

This pin has multiple functions.

• REV for Sharp HR-TFT

• FR for Epson D-TFD

• General purpose IO pin 2 (GPIO2)

See Table 4-9: “LCD Interface Pin Mapping,” on page 30 for

summary.

This pin has multiple functions.

• SPL for Sharp HR-TFT

• FRS for Epson D-TFD

• General purpose IO pin 3 (GPIO3)

See Table 4-9: “LCD Interface Pin Mapping,” on page 30 for

summary.

This pin has multiple functions.

• RES for Epson D-TFD

• General purpose IO pin 4 (GPIO4)

See Table 4-9: “LCD Interface Pin Mapping,” on page 30 for

summary.

This pin has multiple functions.

• DD_P1 for Epson D-TFD

• General purpose IO pin 5 (GPIO5)

See Table 4-9: “LCD Interface Pin Mapping,” on page 30 for

summary.

This pin has multiple functions.

• YSCLD for Epson D-TFD

• General purpose IO pin 6 (GPIO6)

See Table 4-9: “LCD Interface Pin Mapping,” on page 30 for

summary.

This output pin has multiple functions.

• PWM Clock output

• General purpose output

This output pin has multiple functions.

• CV Pulse Output

• General purpose output

Description

S1D13706 Hardware Functional Specification

X31B-A-001-09 Issue Date: 2004/02/09

Page 27

Epson Research and Development Page 27

Vancouver Design Center

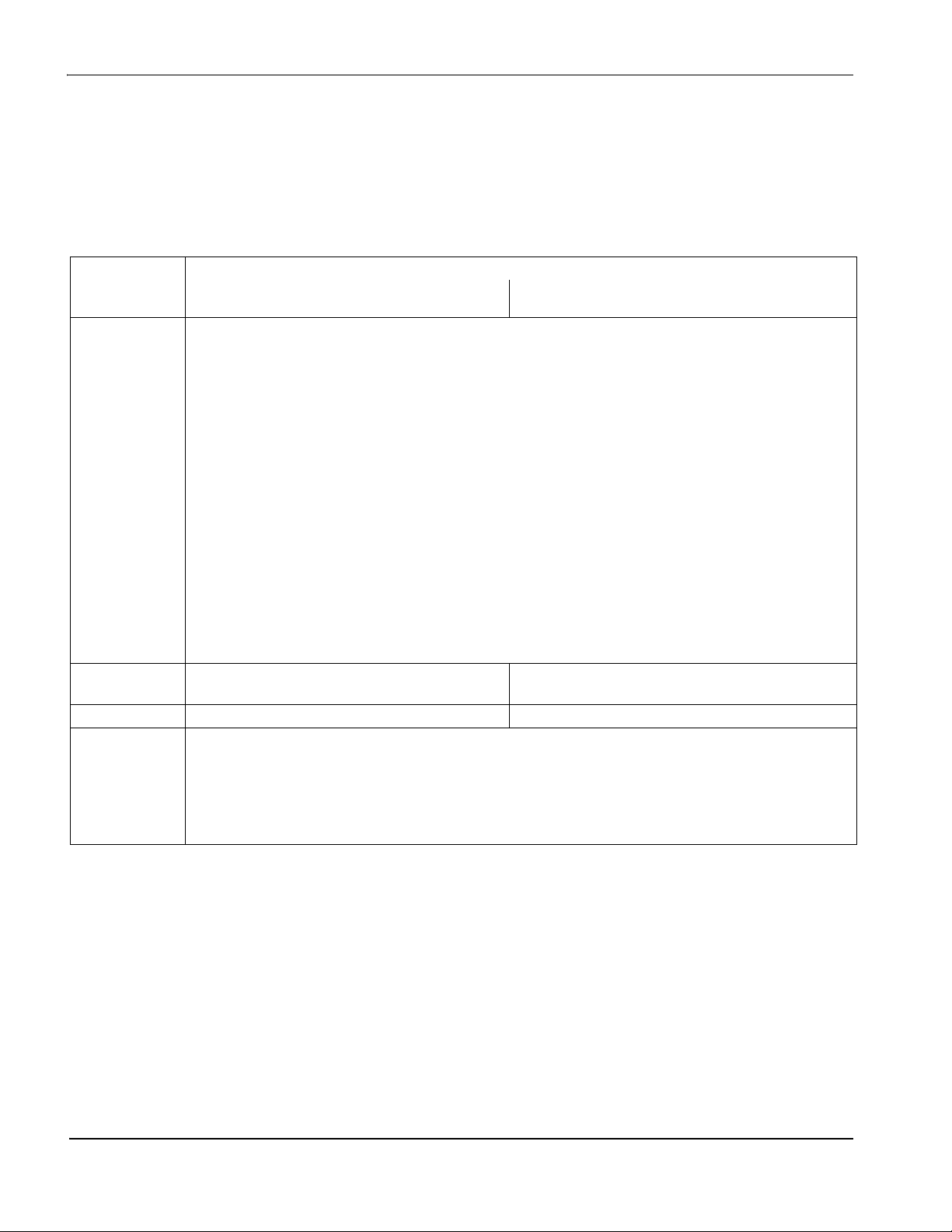

4.3.3 Clock Input

Table 4-4: Clock Input Pin Descriptions

IO

Pin Name Type Pin # Cell

CLKI I 15 LI NIOVDD —

CLKI2 I 77 LI NIOVDD — Typically used as input clock source for pixel clock

Vol tage

RESET#

State

Typically used as input clock source for bus clock and memory

clock

Description

4.3.4 Miscellaneous

Table 4-5: Miscellaneous Pin Descriptions

IO

Pin Name Type Pin # Cell

CNF[7:0] I 78-85 LI NIOVDD —

GPO O 47 LO3 NIOVDD 0

TESTEN I 86 T1 NIOVDD 0

Vol tage

RESET#

State

These inputs are used to configure the S1D13706 - see Table 4-7:

“Summary of Power-On/Reset Options,” on page 28.

Note: These pins are used for configuration of the S1D13706

and must be connected directly to IO V

General Purpose Output (possibly used for controlling the LCD

power). It may also be used for the MOD control signal of the Sharp

HR-TFT panel.

Test Enable input used for production test only (has type 1 pull-

down resistor with a typical value of 50Ω at 3.3V).

Description

or VSS.

DD

4.3.5 Power And Ground

Table 4-6: Power And Ground Pin Descriptions

IO

Pin Name Type Pin # Cell

HIOVDD P 16, 26 P — —

NIOVDD P

COREVDD P 1, 51 P — — 2 Core V

VSS P

37, 49,

63, 76

14, 25,

36, 50,

62, 75,

100

Vol tage

P——

P——7 V

RESET#

State

IO V

Section 4.3.1, “Host Interface” on page 21.

IO V

described in Section 4.3.2, “LCD Interface” on page 25, Section

4.3.3, “Clock Input” on page 27, and Section 4.3.4, “Miscellaneous”

on page 27.

SS

Description

pins associated with the host interface pins as described in

DD

pins associated with the non-host interface pins as

DD

pins.

DD.

pins.

Hardware Functional Specification S1D13706

Issue Date: 2004/02/09 X31B-A-001-09

Page 28

Page 28 Epson Research and Development

Vancouver Design Center

4.4 Summary of Configuration Options

These pins are used for configuration of the S1D13706 and must be connected directly to

NIOV

state at any other time has no effect.

S1D13706

Configuration

Input

Select host bus interface as follows:

CNF4,CNF[2:0]

or VSS. The state of CNF[6:0] is latched on the rising edge of RESET#. Changing

DD

Table 4-7: Summary of Power-On/Reset Options

Power-On/Reset State

1 (connected to NIOV

CNF4 CNF2 CNF1 CNF0 Host Bus

1000 SH-4/SH-3 interface, Big Endian

0000 SH-4/SH-3 interface, Little Endian

1001 MC68K #1, Big Endian

0001 Reserved

1010 MC68K #2, Big Endian

0010 Reserved

1011 Generic #1, Big Endian

0011 Generic #1, Little Endian

1100 Reserved

0100 Generic #2, Little Endian

1101 REDCAP2, Big Endian

0101 Reserved

1110 DragonBall (MC68EZ328/MC68VZ328), Big Endian

0110 Reserved

X111 Reserved

) 0 (Connected to VSS)

DD

Note: The host bus interface is 16-bit only.

CNF3 Configure GPIO pins as inputs at power-on

CNF5 WAIT# is active high WAIT# is active low

CLKI to BCLK divide select:

CNF7 CNF6 CLKI to BCLK Divide Ratio

CNF[7:6]

00 1 : 1

01 2 : 1

10 3 : 1

11 4 : 1

Configure GPIO pins as outputs at power-on (for use

by HR-TFT/D-TFD when selected)

S1D13706 Hardware Functional Specification

X31B-A-001-09 Issue Date: 2004/02/09

Page 29

Epson Research and Development Page 29

Vancouver Design Center

4.5 Host Bus Interface Pin Mapping

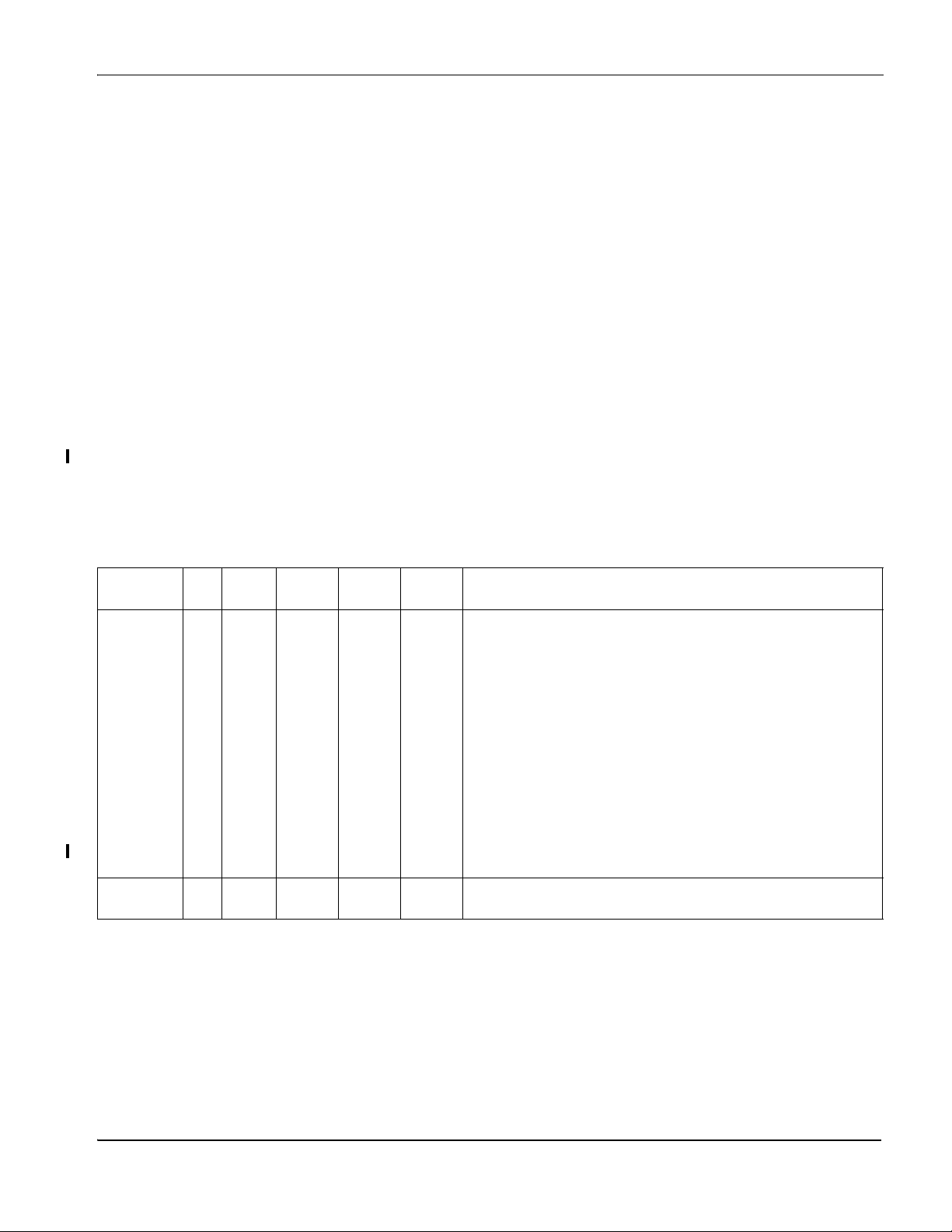

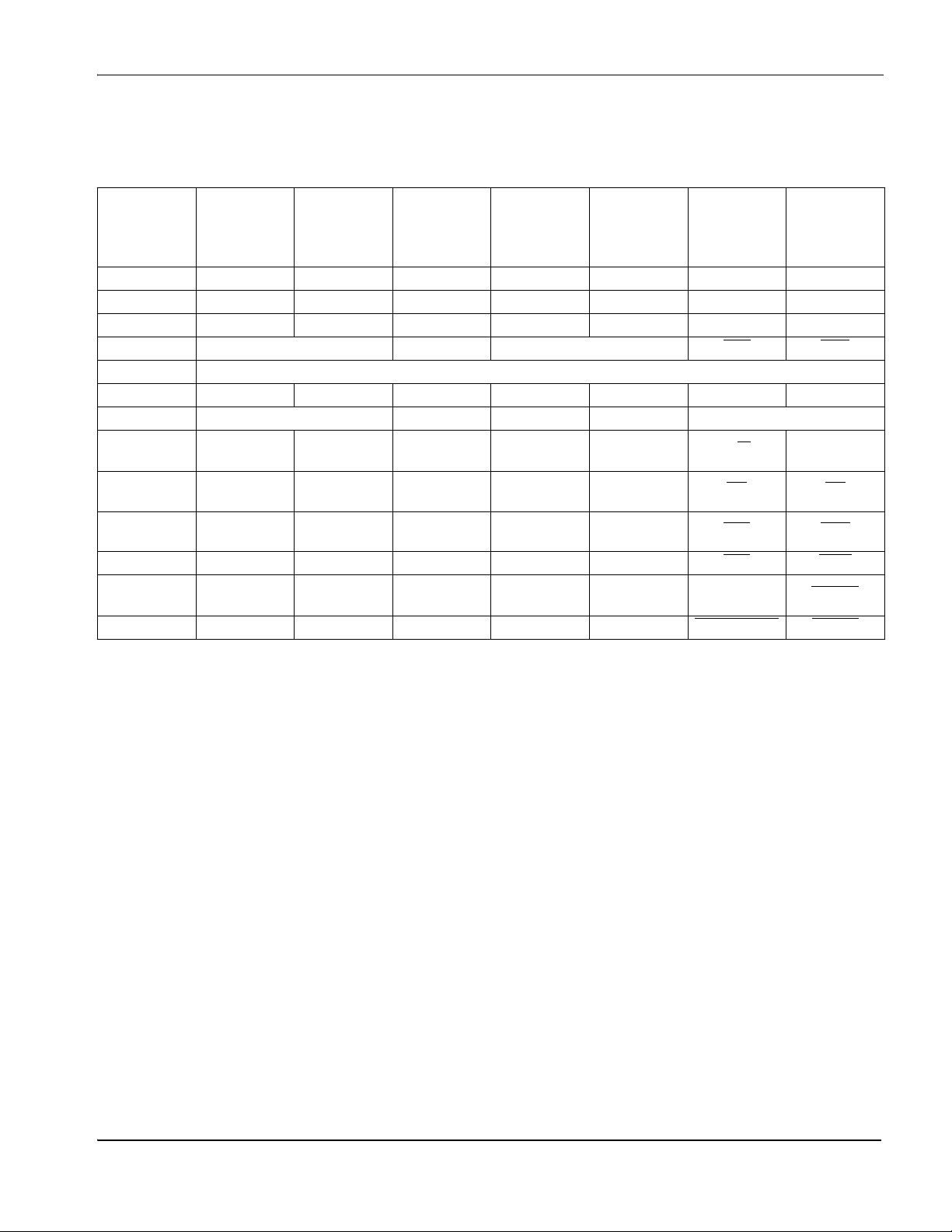

Table 4-8: Host Bus Interface Pin Mapping

Motorola

S1D13706

Pin Name

Generic #1 Generic #2

Hitachi

SH-3 /SH-4

Motorola

MC68K #1

Motorola

MC68K #2

Motorola

REDCAP2

AB[16:1] A[16:1] A[16:1] A[16:1] A[16:1] A[16:1] A[16:1] A[16:1]

AB0 A0

1

A0 A0

DB[15:0] D[15:0] D[15:0] D[15:0] D[15:0] D[15:0]

1

LDS# A0 A0

2

1

D[15:0] D[15:0]

CS# External Decode CSn# External Decode CSn

M/R# External Decode

CLKI BUSCLK BUSCLK CKIO CLK CLK CLK CLKO

BS# Connected to V

RD/WR# RD1#

DD

Connected to

V

DD

RD# RD0# RD# RD#

WE0# WE0# WE# WE0#

BS# AS# AS# Connected to V

RD/WR# R/W# R/W# R/W

Connected to

V

DD

Connected to

V

DD

SIZ1 OE OE

SIZ0 EB1 LWE

WE1# WE1# BHE# WE1# UDS# DS# EB0 UWE

WAIT# WAIT# WAIT#

WAIT#/

RDY#

DTACK# DSACK1# N/A DTACK

RESET# RESET# RESET# RESET# RESET# RESET# RESET_OUT RESET

MC68EZ328/

MC68VZ328

DragonBall

1

A0

CSX

DD

Connected to

V

DD

Note

1

A0 for these busses is not used internally by the S1D13706 and should be connected to VSS.

2

If the target MC68K bus is 32-bit, then these signals should be connected to D[31:16].

Hardware Functional Specification S1D13706

Issue Date: 2004/02/09 X31B-A-001-09

Page 30

Page 30 Epson Research and Development

Vancouver Design Center

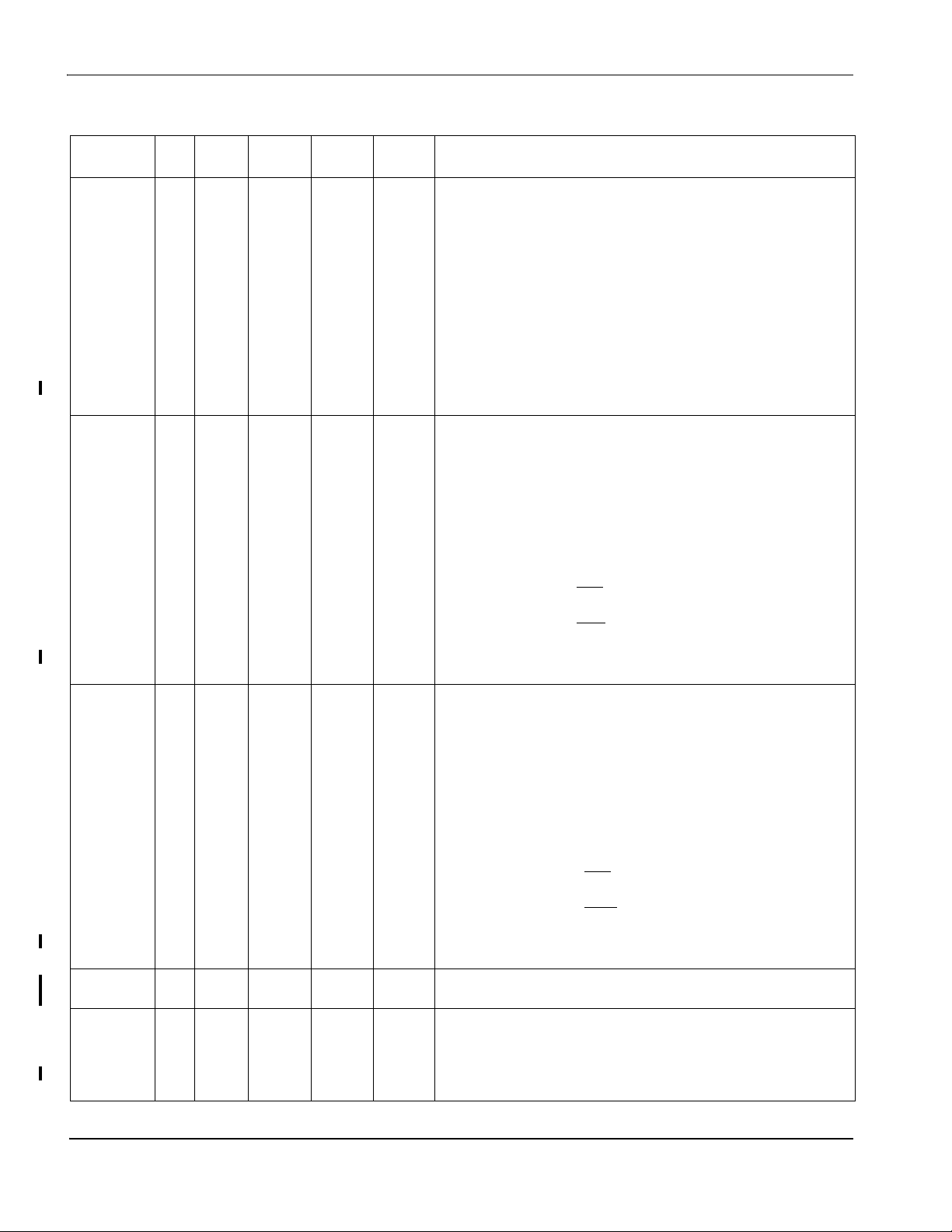

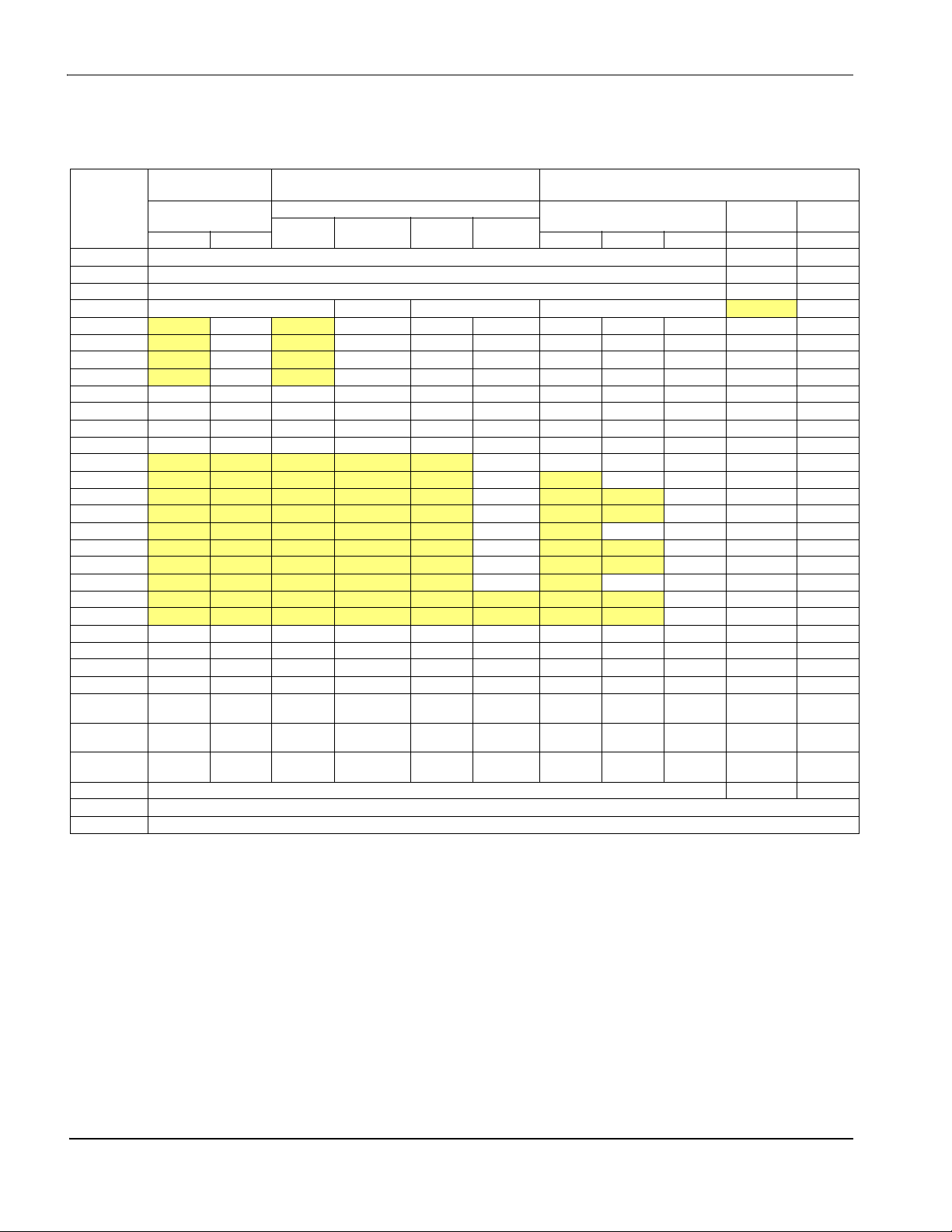

4.6 LCD Interface Pin Mapping

Table 4-9: LCD Interface Pin Mapping

Monochrome Passive

Panel

Pin Name

FPFRAME FPFRAME SPS DY

FPLINE FPLINE LP LP

FPSHIFT FPSHIFT DCLK XSCL

DRDY MOD FPSHIFT2 MOD DRDY

FPDAT0

FPDAT1

FPDAT2

FPDAT3

FPDAT4 D0 D4 D0 (R2)

FPDAT5 D1 D5 D1 (B1)

FPDAT6 D2 D6 D2 (G1)

FPDAT7 D3 D7 D3 (R1)

FPDAT8

FPDAT9

FPDAT10

FPDAT11

FPDAT12

FPDAT13

FPDAT14

FPDAT15

FPDAT16

FPDAT17

GPIO0 GPIO0 GPIO0 GPIO0 GPIO0 GPIO0 GPIO0 GPIO0 GPIO0 GPIO0 PS XINH

GPIO1 GPIO1 GPIO1 GPIO1 GPIO1 GPIO1 GPIO1 GPIO1 GPIO1 GPIO1 CLS YSCL

GPIO2 GPIO2 GPIO2 GPIO2 GPIO2 GPIO2 GPIO2 GPIO2 GPIO2 GPIO2 REV FR

GPIO3 GPIO3 GPIO3 GPIO3 GPIO3 GPIO3 GPIO3 GPIO3 GPIO3 GPIO3 SPL FRS

GPIO4 GPIO4 GPIO4 GPIO4 GPIO4 GPIO4 GPIO4 GPIO4 GPIO4 GPIO4

GPIO5 GPIO5 GPIO5 GPIO5 GPIO5 GPIO5 GPIO5 GPIO5 GPIO5 GPIO5

GPIO6 GPIO6 GPIO6 GPIO6 GPIO6 GPIO6 GPIO6 GPIO6 GPIO6 GPIO6

GPO GPO (General Purpose Output) MOD

CVOUT CVOUT

PWMOUT PWMOUT

Single

4-bit 8-bit 9-bit 12-bit 18-bit 18-bit 18-bit

driven 0 D0 driven 0 D0 (B5)2D0 (G3)2D0 (R6)

driven 0 D1 driven 0 D1 (R5)2D1 (R3)2D1 (G5)

driven 0 D2 driven 0 D2 (G4)2D2 (B2)2D2 (B4)

driven 0 D3 driven 0 D3 (B3)2D3 (G2)2D3 (R4)

driven 0 driven 0 driven 0 driven 0 driven 0 D4 (G3)

driven 0 driven 0 driven 0 driven 0 driven 0 D5 (B2)2driven 0R0R2R2R2

driven 0 driven 0 driven 0 driven 0 driven 0 D6 (R2)2driven 0 driven 0R1R1R1

driven 0 driven 0 driven 0 driven 0 driven 0 D7 (G1)2driven 0 driven 0R0R0R0

driven 0 driven 0 driven 0 driven 0 driven 0 D12 (R3)2driven 0G0G2G2G2

driven 0 driven 0 driven 0 driven 0 driven 0 D13 (G2)2driven 0 driven 0G1G1G1

driven 0 driven 0 driven 0 driven 0 driven 0 D14 (B1)2driven 0 driven 0G0G0G0

driven 0 driven 0 driven 0 driven 0 driven 0 D15 (R1)2driven 0B0B2B2B2

driven 0 driven 0 driven 0 driven 0 driven 0 driven 0 driven 0 driven 0B1B1B1

driven 0 driven 0 driven 0 driven 0 driven 0 driven 0 driven 0 driven 0B0B0B0

4-bit

Color Passive Panel Color TFT Panel

Single

Format 1

8-bit

2

D4 (R3)

2

D5 (G2)

2

D6 (B1)2D6 (G1)2D10 (G4)

2

D7 (R1)

Format 2

8-bit

2

D4 (R2)2D8 (B5)

2

D5 (B1)2D9 (R5)

2

D7 (R1)2D11 (B3)

16-Bit

2

R2 R3 R5 R5 R5

2

R1 R2 R4 R4 R4

2

R0 R1 R3 R3 R3

2

G2 G3 G5 G5 G5

2

G1 G2 G4 G4 G4

2

G0 G1 G3 G3 G3

2

B2 B3 B5 B5 B5

2

B1 B2 B4 B4 B4

2

B0 B1 B3 B3 B3

Others

Sharp HR-

TFT

no connect GCP

GPIO4

(output only)

GPIO5

(output only)

GPIO6

(output only)

Epson

1

D-TFD

RES

DD_P1

YSCLD

3

GPO

1

Note

1

GPIO pins must be configured as outputs (CNF3 = 0 at RESET#) when the HR-TFT or

D-TFD interface is selected.

2

These pin mappings use signal names commonly used for each panel type, however

signal names may differ between panel manufacturers. The values shown in brackets

represent the color components as mapped to the corresponding FPDATxx signals at

the first valid edge of FPSHIFT. For further FPDATxx to LCD interface mapping, see

Section 6.4, “Display Interface” on page 56.

3

When the HR-TFT interface is selected (REG[10h] bits 1-0 = 10), this GPO can be

used to control the HR-TFT MOD signal. Note this is not the same signal as the

S1D13706 DRDY(MOD) signal used for passive panels.

S1D13706 Hardware Functional Specification

X31B-A-001-09 Issue Date: 2004/02/09

Page 31

Epson Research and Development Page 31

Vancouver Design Center

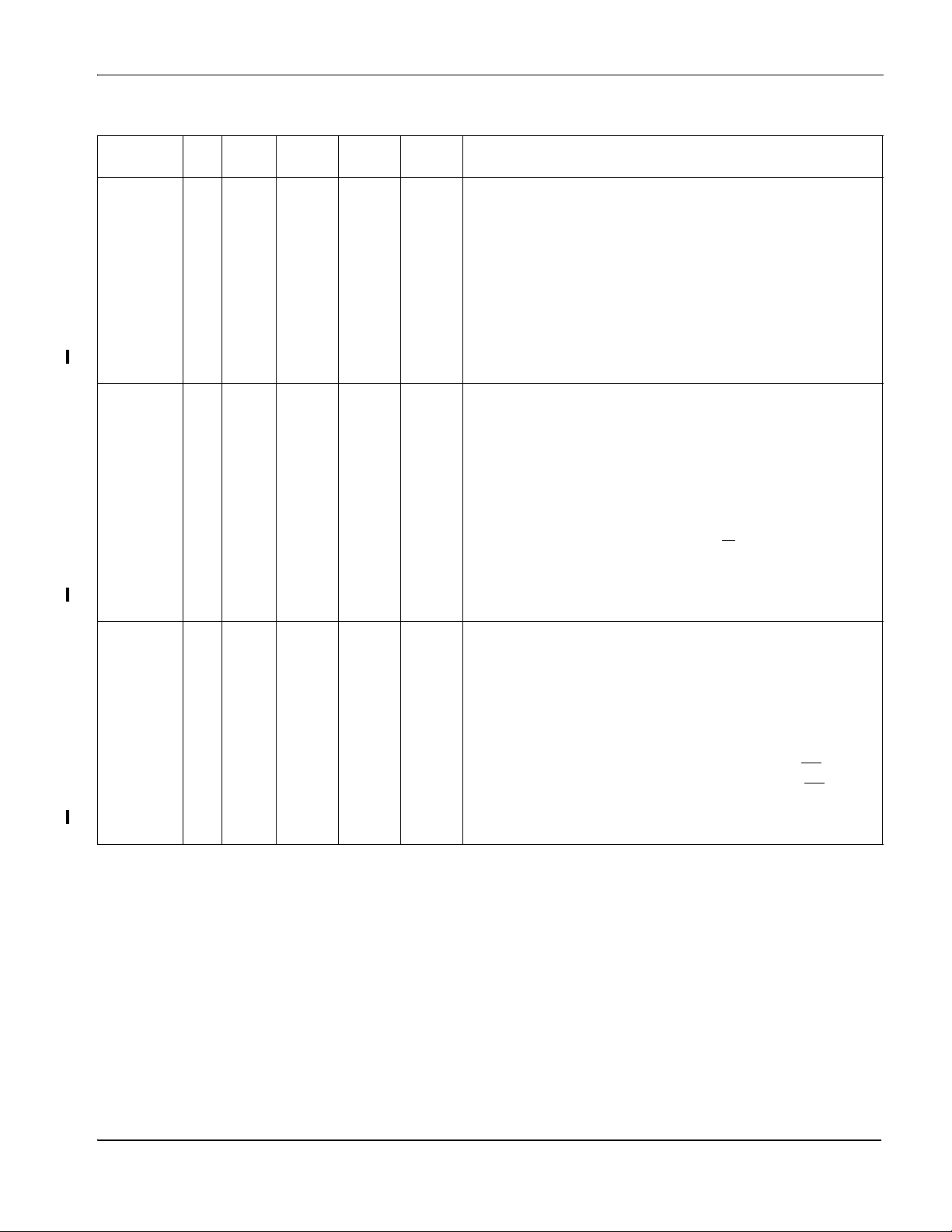

5 D.C. Characteristics

Table 5-1: Absolute Maximum Ratings

Symbol Parameter Rating Units

Core V

DD

IO V

DD

V

IN

V

OUT

T

STG

T

SOL

Symbol Parameter Condition Min Typ Max Units

Core V

DD

HIO V

DD

NIO V

DD

V

IN

T

OPR

Supply Voltage VSS - 0.3 to 4.0 V

Supply Voltage VSS - 0.3 to 4.0 V

Input Voltage VSS - 0.3 to IO VDD + 0.5 V

Output Voltage VSS - 0.3 to IO VDD + 0.5 V

Storage Temperature -65 to 150 ° C

Solder Temperature/Time 260 for 10 sec. max at lead ° C

Table 5-2: Recommended Operating Conditions

Supply Voltage VSS = 0 V

Supply Voltage VSS = 0 V

Supply Voltage VSS = 0 V 3.0 3.3 3.6 V

Input Voltage V

Operating Temperature -40 25 85 ° C

1.8 2.0 2.2 V

3.0 3.3 3.6 V

1.8 2.0 2.2 V

3.0 3.3 3.6 V

SS

IO V

DD

V

Note

The S1D13706 requires that Core VDD ≤ HIO VDD and Core VDD ≤ NIO VDD.

Table 5-3: Electrical Characteristics for VDD = 3.3V typical

Symbol Parameter Condition Min Typ Max Units

I

DDS

I

IZ

I

OZ

V

V

V

V

V

V

V

R

C

C

C

OH

OL

IH

IL

T+

T-

H1

PD

I

O

IO

Quiescent Current Quiescent Conditions 170 µA

Input Leakage Current -1 1 µA

Output Leakage Current -1 1 µA

VDD = min

High Level Output Voltage

IOH = -6mA (Type 2)

VDD - 0.4 V

-12mA (Type 3)

VDD = min

Low Level Output Voltage

IOL = 6mA (Type 2)

0.4 V

12mA (Type 3)

High Level Input Voltage LVTTL Level, VDD = max 2.0 V

Low Level Input Voltage LVTTL Level, VDD = min 0.8 V

High Level Input Voltage LVTTL Schmitt 1.1 2.4 V

Low Level Input Voltage LVTTL Schmitt 0.6 1.8 V

Hysteresis Voltage LVTTL Schmitt 0.1 V

Pull Down Resistance VI = V

DD

20 50 120 kΩ

Input Pin Capacitance 10 pF

Output Pin Capacitance 10 pF

Bi-Directional Pin Capacitance 10 pF

Hardware Functional Specification S1D13706

Issue Date: 2004/02/09 X31B-A-001-09

Page 32

Page 32 Epson Research and Development

Vancouver Design Center

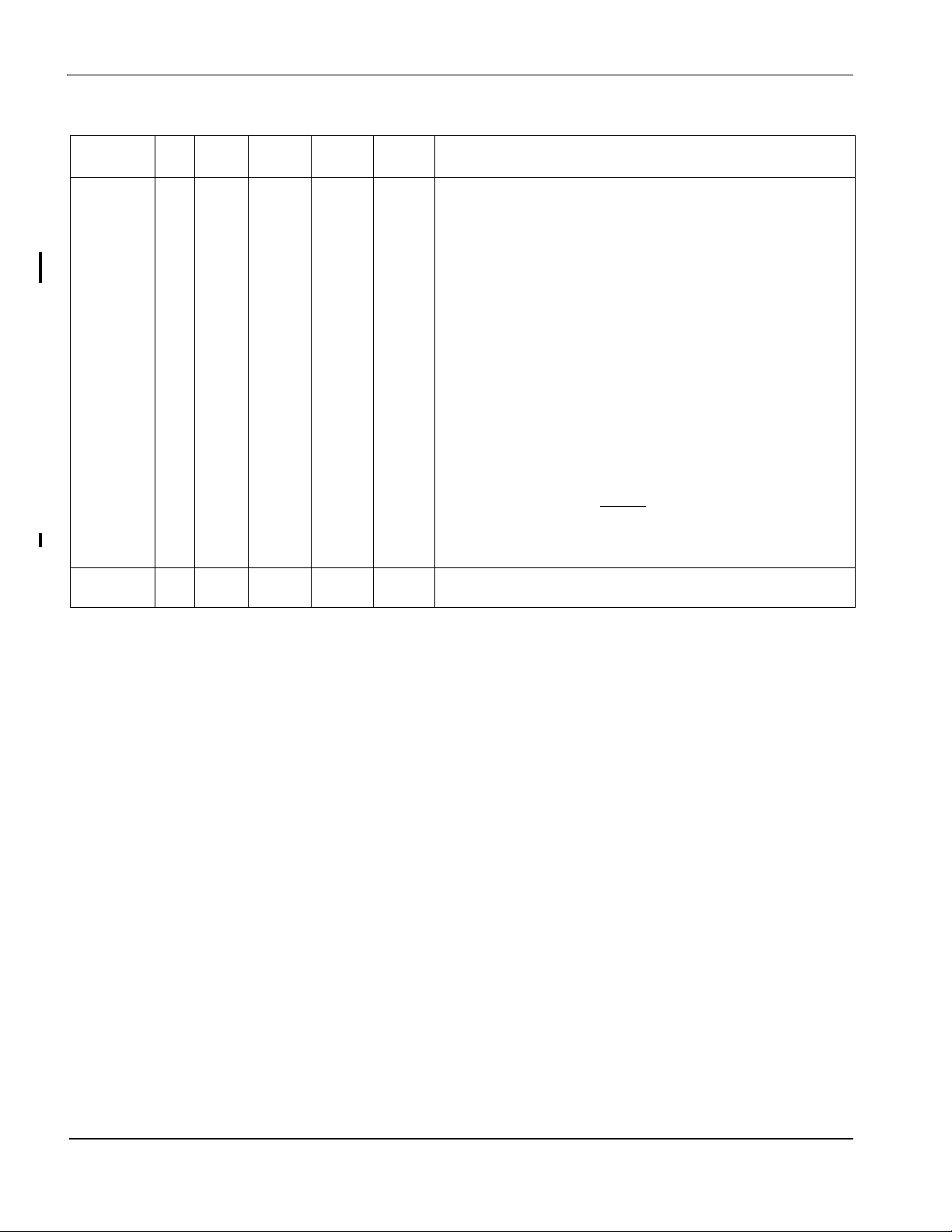

6 A.C. Characteristics

Conditions: HIO VDD = 2.0V ± 10% and HIO VDD = 3.3V ± 10%

= 3.3V ± 10%

DD

and T

fall

for all inputs must be < 5 nsec (10% ~ 90%)

6.1 Clock Timing

6.1.1 Input Clocks

Clock Input Waveform

NIO V

T

= -40° C to 85° C

A

T

rise

C

= 50pF (Bus/MPU Interface)

L

C

= 0pF (LCD Panel Interface)

L

t

PWH

90%

V

IH

V

IL

10%

t

r

Figure 6-1: Clock Input Requirements

Table 6-1: Clock Input Requirements for CLKI when CLKI to BCLK divide > 1

Symbol Parameter

Input Clock Frequency (CLKI) 40 100 MHz

f

OSC

T

t

Input Clock period (CLKI) 1/f

OSC

Input Clock Pulse Width High (CLKI) 4.5 4.5 ns

PWH

Input Clock Pulse Width Low (CLKI) 4.5 4.5 ns

t

PWL

Input Clock Fall Time (10% - 90%) 5 5 ns

t

f

Input Clock Rise Time (10% - 90%) 5 5 ns

t

r

T

OSC

t

PWL

t

f

2.0V 3.3V

MinMaxMinMax

OSC

1/f

OSC

Units

ns

Note

Maximum internal requirements for clocks derived from CLKI must be considered

when determining the frequency of CLKI. See Section 6.1.2, “Internal Clocks” on page

34 for internal clock requirements.

S1D13706 Hardware Functional Specification

X31B-A-001-09 Issue Date: 2004/02/09

Page 33

Epson Research and Development Page 33

Vancouver Design Center

Table 6-2: Clock Input Requirements for CLKI when CLKI to BCLK divide = 1

Symbol Parameter

f

T

t

t

Input Clock Frequency (CLKI) 20 66 MHz

OSC

Input Clock period (CLKI) 1/f

OSC

Input Clock Pulse Width High (CLKI) 3 3 ns

PWH

Input Clock Pulse Width Low (CLKI) 3 3 ns

PWL

Input Clock Fall Time (10% - 90%) 5 5 ns

t

f

Input Clock Rise Time (10% - 90%) 5 5 ns

t

r

Note

Maximum internal requirements for clocks derived from CLKI must be considered

when determining the frequency of CLKI. See Section 6.1.2, “Internal Clocks” on page

34 for internal clock requirements.

Table 6-3: Clock Input Requirements for CLKI2

Symbol Parameter

f

T

t

t

Input Clock Frequency (CLKI2) 20 66 MHz

OSC

Input Clock period (CLKI2) 1/f

OSC

Input Clock Pulse Width High (CLKI2) 3 3 ns

PWH

Input Clock Pulse Width Low (CLKI2) 3 3 ns

PWL

Input Clock Fall Time (10% - 90%) 5 5 ns

t

f

Input Clock Rise Time (10% - 90%) 5 5 ns

t

r

2.0V 3.3V

MinMaxMinMax

OSC

1/f

OSC

2.0V 3.3V

MinMaxMinMax

OSC

1/f

OSC

Units

ns

Units

ns

Note

Maximum internal requirements for clocks derived from CLKI2 must be considered

when determining the frequency of CLKI2. See Section 6.1.2, “Internal Clocks” on page

34 for internal clock requirements.

Hardware Functional Specification S1D13706

Issue Date: 2004/02/09 X31B-A-001-09

Page 34

Page 34 Epson Research and Development

Vancouver Design Center

6.1.2 Internal Clocks

Table 6-4: Internal Clock Requirements

Symbol Parameter

f

f

f

f

PWMCLK

Bus Clock frequency 20 66 MHz

BCLK

Memory Clock frequency 20 50 MHz

MCLK

Pixel Clock frequency 20 50 MHz

PCLK

PWM Clock frequency 20 66 MHz

Note

For further information on internal clocks, refer to Section 7, “Clocks” on page 90.

2.0V 3.3V

MinMaxMinMax

Units

S1D13706 Hardware Functional Specification

X31B-A-001-09 Issue Date: 2004/02/09

Page 35

Epson Research and Development Page 35

Vancouver Design Center

6.2 CPU Interface Timing

The following section includes CPU interface AC Timing for both 2.0V and 3.3V. The

2.0V timings are based on HIO V

HIO V

= Core VDD = 3.3V.

DD

6.2.1 Generic #1 Interface Timing

= Core VDD = 2.0V. The 3.3V timings are based on

DD

CLK

A[16:1]

M/R#

CS#

RD0#,RD1#

WE0#,WE1#

WAIT#

D[15:0](write)

D[15:0](read)

T

CLK

t1 t2

t3

t5

t4

t6

t7

t8

t9

t13

t11

t12

t14

VALID

t10

t15

Figure 6-2: Generic #1 Interface Timing

Hardware Functional Specification S1D13706

Issue Date: 2004/02/09 X31B-A-001-09

Page 36

Page 36 Epson Research and Development

Vancouver Design Center

Table 6-5: Generic #1 Interface Timing

Symbol Parameter

f

Bus Clock frequency 20 50 MHz

CLK

T

Bus Clock period 1/f

CLK

2.0V 3.3V

Min Max Min Max

CLK

1/f

CLK

t1 Clock pulse width high 22.5 9 ns

t2 Clock pulse width low 22.5 9 ns

A[16:1], M/R# setup to first CLK rising edge where CS# = 0 and

t3

either RD0#, RD1# = 0 or WE0#, WE1# = 0

A[16:1], M/R# hold from either RD0#, RD1# or WE0#, WE1#

t4

rising edge

11ns

00ns

t5 CS# setup to CLK rising edge 0 1 ns

t6 CS# hold from either RD0#, RD1# or WE0#, WE1# rising edge 0 0 ns

t7a RD0#, RD1#, WE0#, WE1# asserted for MCLK = BCLK 8.5 8.5 T

t7b RD0#, RD1#, WE0#, WE1# asserted for MCLK = BCLK ÷ 2 11.5 11.5 T

t7c RD0#, RD1#, WE0#, WE1# asserted for MCLK = BCLK ÷ 3 13.5 13.5 T

t7d RD0#, RD1#, WE0#, WE1# asserted for MCLK = BCLK ÷ 4 17.5 17.5 T

t8 RD0#, RD1#, WE0#, WE1# setup to CLK rising edge 2 1 ns

Falling edge of either RD0#, RD1# or WE0#, WE1# to WAIT#

t9

driven low

Rising edge of either RD0#, RD1# or WE0#, WE1# to WAIT#

t10

high impedance

D[15:0] setup to third CLK rising edge where CS# = 0 and

t11

WE0#, WE1# = 0 (write cycle) (see note 1)

5 31 3 15 ns

5 34 3 13 ns

10ns

t12 D[15:0] hold from WAIT# rising edge (write cycle) 1 0 ns

t13 RD0#, RD1# falling edge to D[15:0] driven (read cycle) 4 27 3 14 ns

t14 WAIT# rising edge to D[15:0] valid (read cycle) 0 2 ns

t15 RD0#, RD1# rising edge to D[15:0] high impedance (read cycle) 3 29 3 11 ns

1. t11 is the delay from when data is placed on the bus until the data is latched into the write buffer.

Unit

ns

CLK

CLK

CLK

CLK

S1D13706 Hardware Functional Specification

X31B-A-001-09 Issue Date: 2004/02/09

Page 37

Epson Research and Development Page 37

Vancouver Design Center

6.2.2 Generic #2 Interface Timing (e.g. ISA)

BUSCLK

SA[16:0]

M/R#, SBHE#

CS#

MEMR#

MEMW#

IOCHRDY

SD[15:0] (write)

SD[15:0] (read)

T

BUSCLK

t1 t2

t3

t5

t4

t6

t7

t8

t9

t13

t11

t14

t10

t12

t15

VAL ID

Figure 6-3: Generic #2 Interface Timing

Hardware Functional Specification S1D13706

Issue Date: 2004/02/09 X31B-A-001-09

Page 38

Page 38 Epson Research and Development

Vancouver Design Center

Table 6-6: Generic #2 Interface Timing

Symbol Parameter

f

BUSCLK

T

BUSCLK

Bus Clock frequency 20 50 MHz

Bus Clock period 1/f

2.0V 3.3V

MinMaxMinMax

BUSCLK

1/f

BUSCLK

Unit

ns

t1 Clock pulse width high 22.5 9 ns

t2 Clock pulse width low 22.5 9 ns

SA[16:0], M/R#, SBHE# setup to first BUSCLK rising edge

t3

where CS# = 0 and either MEMR# = 0 or MEMW# = 0

SA[16:0], M/R#, SBHE# hold from either MEMR# or MEMW#

t4

rising edge

11ns

00ns

t5 CS# setup to BUSCLK rising edge 0 1 ns

t6 CS# hold from either MEMR# or MEMW# rising edge 0 0 ns

t7a MEMR#/MEMW# asserted for MCLK = BCLK 8.5 8 T

t7b MEMR#/MEMW# asserted for MCLK = BCLK ÷ 211.511T

t7c MEMR#/MEMW# asserted for MCLK = BCLK ÷ 313.513T

t7d MEMR#/MEMW# asserted for MCLK = BCLK ÷ 417.517T

BUSCLK

BUSCLK

BUSCLK

BUSCLK

t8 MEMR# or MEMW# setup to BUSCLK rising edge 2 1 ns

Falling edge of either MEMR# or MEMW# to IOCHRDY driven

t9

low

Rising edge of either MEMR# or MEMW# to IOCHRDY high

t10

impedance

SD[15:0] setup to third BUSCLK rising edge where CS# = 0 and

t11

MEMW# = 0 (write cycle) (see note 1)

5 3 15 ns

5 3 13 ns

10ns

t12 SD[15:0] hold from IOCHRDY rising edge (write cycle) 1 0 ns