Page 1

S1D13705 Embedded Memory LCD Controller

S1D13705

TECHNICAL MANUAL

Document No. X27A-Q -001-04

Copyright © 2001 Epson Research and Development, Inc. All Rights Reserved.

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in

evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any

representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain

material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. All other Trademarks are the property of their respective owners

Page 2

Page 2 Epson Research and Development

Vancouver Design Center

THIS PAGE LEFT BLANK

S1D13705 TECHNICAL MANUAL

X27A-Q-001-04 Issue Date: 01/04/18

Page 3

Epson Research and Development Page 3

Vancouver Design Center

Customer Support Information

Comprehensive Support Tools

Seiko Epson Corp. provides to the system designer and computer OEM manufacturer a

complete set of resources and tools for the dev elopment of graphics sy stems.

Evaluation / Demonstration Board

• Assembled and fully tested graphics evaluation board with installation guide and schematics.

• To borrow an evaluation board, pl ease cont act your local Seiko Epson Corp. sal es repr esentative.

Chip Documentation

• Technical manual includes Data Sheet, Application Notes, and Programmer’s Reference.

Software

• OEM Utilities.

• User Utilit ies.

• Evaluation Software.

• To obtain these programs, contact Application Engineering Support.

Application Engineering Support

Engineering and Sales Support is provided by:

Japan

Seiko Epson Corporation

Electronic Devices Marketing Division

421-8, Hino, Hino-shi

Tokyo 191-8501, Japan

Tel: 042-587-5812

Fax: 042-587-5564

http://www.epson.co.jp

Hong Kong

Epson Hong Kong Ltd.

20/F., Harbour Centre

25 Harbour Road

Wanchai, Hong Kong

Tel: 2585-4600

Fax: 2827-4346

North America

Epson Electronics America, Inc.

150 River Oaks Parkway

San Jose, CA 95134, USA

Tel: (408) 922-0200

Fax: (408) 922-0238

http://www.eea.epson.com

Europe

Epson Europe Electronics GmbH

Riesstrasse 15

80992 Munich, Germany

Tel: 089-14005-0

Fax: 089-14005-110

Taiwan

Epson Taiwan T echnology

& Trading Ltd.

10F, No. 287

Nanking East Road

Sec. 3, Taipei, Taiwan

Tel: 02-2717-7360

Fax: 02-2712-9164

Singapore

Epson Singapore Pte., Ltd.

No. 1

Temasek Avenue #36-00

Millenia Tower

Singapore, 039192

Tel: 337-7911

Fax: 334-2716

TECHNICAL MANUAL S1D13705

Issue Date: 01/04/18 X27A-Q-001-04

Page 4

Page 4 Epson Research and Development

Vancouver Design Center

THIS PAGE LEFT BLANK

S1D13705 TECHNICAL MANUAL

X27A-Q-001-04 Issue Date: 01/04/18

Page 5

ENERGY

SAVING

EPSON

GRAPHICS

S1D13705

February 2001

S1D13705 Embedded Memory LCD Controller

The S1D13705 is a color/monochrome LCD graphics controller with an embedded 80K Byte SRAM

display buffer. The high integr ation of the S1D13705 provides a low c ost, low power, single chip solution

to meet the requirements of e mbedded markets such as Office Automati on equipment, Mobile Communications devices, and Palm-size PCs where board size and batter y li fe are major concerns.

Products requiring a “Portr ait” display can take advantage of th e Hardware Portrai t Mode feature of the

S1D13705. Virtual and Split Screen are just some of the displ ay mo des supported. While focusing on

devices targeted b y the Micros oft Windows CE Oper ating System, t he S1D13705’s impartiality to CPU

type or operating system makes it an ideal display solution for a wide variety of applications.

■ FEATURES

• Embedded 80K byte SRAM display buffer.

• Direct support for the following CPU’s:

Hitachi SH-3.

Hitachi SH-4.

Motorola M68xxx.

MPU bus interface with programmable

READY.

• Resolutions up to:

640x480 at a color depth of 2 bpp.

640x240 at a color depth of 4 bpp.

320x240 at a color depth of 8 bpp.

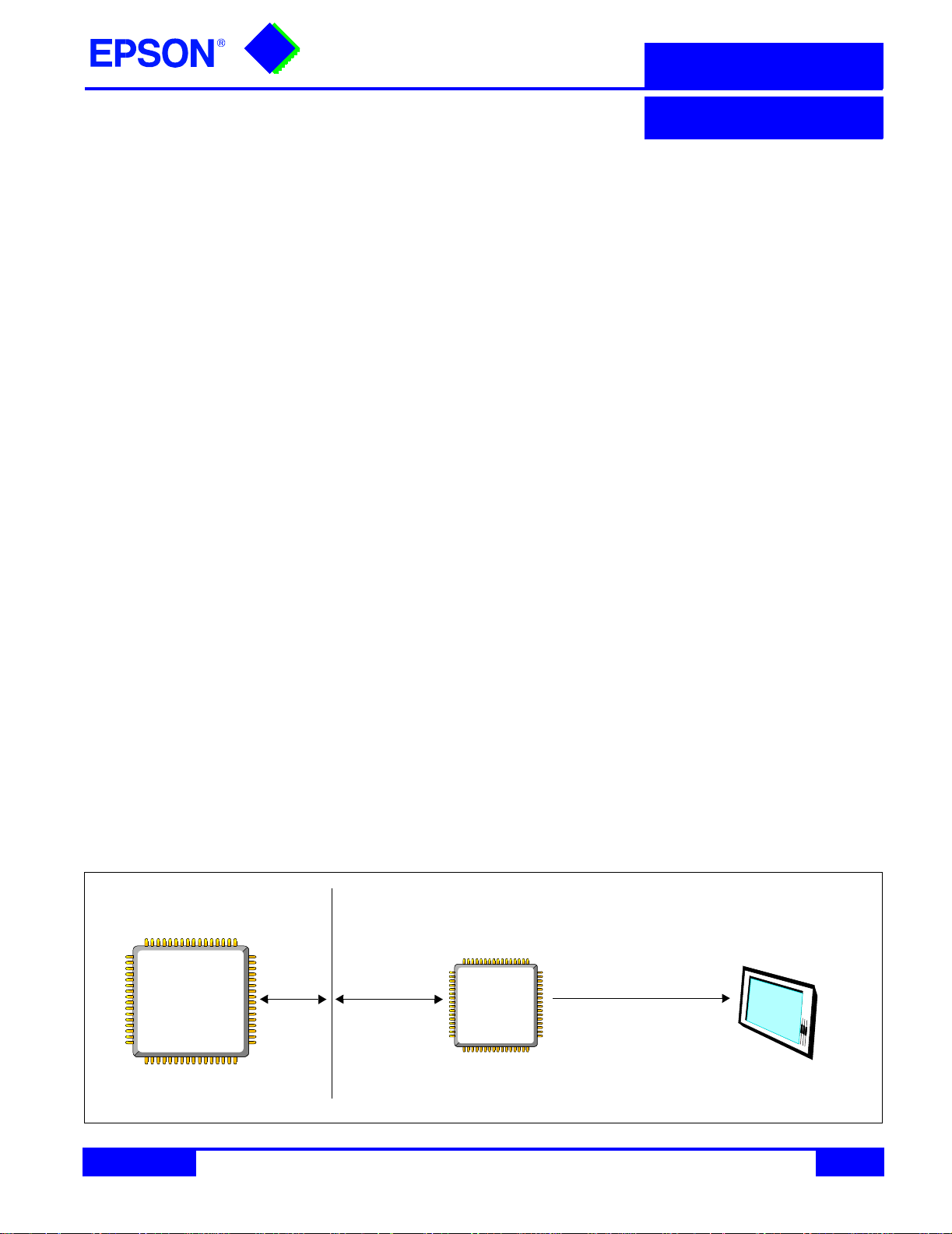

■ SYSTEM BLOCK DIAGRAM

• Up to 256 simultaneous colors from a possible

4096 colors on passive LCD panels and active

matrix TFT/D-TFD LCD panels.

• Register level support for EL panels.

• Hardware Portrait Mode

• Split Screen Display

• Virtual Display Support

• LCD power-down sequencing.

CPU

X27A-C-001-04 1

Data and

Control Signals

S1D13705

Digital Out

Flat Panel

Page 6

GRAPHICS

S1D13705

■ DESCRIPTION

Memory Interface

• Embedded 80K byte SRAM display buffer.

CPU Interface

• Direct support for:

Hitachi SH-3.

Hitachi SH-4.

Motorola M68xxx.

MPU bus interface with programmable READY.

• CPU write buffer.

Display Support

• 4/8-bit monochrome LCD interface.

• 4/8-bit color LCD interface.

• Single-panel, single-drive passive displays.

• Dual-panel, dual-drive passive displays.

• Active matrix TFT / D-TFD interface.

• Example resolutio ns:

640x480 at a color depth of 2 bpp.

640x240 at a color depth of 4 bpp.

320x240 at a color depth of 8 bpp.

Clock Source

• Single clock input for both pixel and memory clocks.

• The S1D13705 clock source can be internally divided

down for a higher frequency clock input.

• Dynamic switching of m emory clocks in portrait mode.

Display Modes

• 1/2/4/8 bit-per-pixel (bpp) support on LCD.

• Up to 16 shades of gray using FRM on

monochrome passive LCD panels.

• Up to 256 simultaneous colors from a possible 4096

colors on passive STN and active matrix TFT/D-TFD

LCD panels.

• Split Screen Display: a llows two differen t images to be

simultaneously viewed on the same display.

• Virtual Display Support: displays images larger than

the display size through the use of panning.

• Double Buffering/multi-pages: provides smooth

animation and instantaneous screen update.

• Hardware Portrait Mode: direct hardware 90°

rotation of display image for portrait mode dis play.

Power Down Modes

• Software Suspend mode.

• LCD power-down sequencing.

Operating Voltage

• CORE

2.7 to 3.6 volts; IO

VDD

2.7 to 5.5 volts.

VDD

Package

• 80-pin QFP 14.

CONTACT YOUR SALES REPRESENTATIVE FOR THESE

COMPREHENSIVE DESIGN TOOLS:

• S1D13705 Technical Manual

• S5U13705 Evaluation Boards

• Windows

CE Display Driver

• CPU Independent Software Utilities

Japan

Seiko Epson Corporation

Electronic Devices Marketing Division

421-8, Hino, Hino-shi

Tokyo 191-8501, Japan

Tel: 042-587-5812

Fax: 042-587-5564

http://www.epson.co.jp

Hong Kong

Epson Hong Kong Ltd.

20/F., Harbour Centre

25 Harbour Road

Wanchai, Hong Kong

Tel: 2585-4600

Fax: 2827-4346

Copyright © 2001 Epson Research and Development, Inc. All rights reserved. VDC

Information in this document is subject to chang e w ithout no tice. Y ou may do wnl oad an d use this docu ment, but only for your ow n use in evaluating Seiko Epson/

EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any re presentati on that the contents of this document are

accurate or current. The Programs/Technologies described in this document may contain material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. Microsoft, Windows, and the Windows CE Logo are registere d trademarks of Microsoft Corporation.

North America

Epson Electronics America, Inc.

150 River Oaks Parkway

San Jose, CA 95134, USA

Tel: (408) 922-0200

Fax: (408) 922-0238

http://www.eea.epson.com

Europe

Epson Europe Electronics GmbH

Riesstrasse 15

80992 Munich, Germany

Tel: 089-14005-0

Fax: 089-14005-110

FOR SYSTEM INTEGRATION SERVICES

FOR WINDOWS® CE CONTACT:

Epson Research & Development, Inc.

Suite #320 - 11120 Horseshoe Way

Richmond, B.C., Canada V7A 5H7

Tel: (604) 275-5151

Fax: (604) 275-2167

Email: wince@erd.epson.com

http://www.erd.epson.com

Taiwan

Epson Taiwan Technology

& Trading Ltd.

10F, No. 287

Nanking East Road

Sec. 3, Taipei, Taiwan

Tel: 02-2717-7360

Fax: 02-2712-9164

Singapore

Epson Singapore Pte., Ltd.

No. 1

Temasek Avenue #36-00

Millenia Tower

Singapore, 039192

Tel: 337-7911

Fax: 334-2716

X27A-C-001-04 2

Page 7

S1D13705 Embedded Memory LCD Controller

Hardware Functional Specification

Document Number: X27A-A-001-10

Copyright © 1999, 2002 Epson Research and Development, Inc. All Rights Reser ved.

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in

evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any

representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain

material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. All other Trademarks are the property of their respective owners

Page 8

Page 2 Epson Research and Development

Vancouver Design Center

THIS PA GE LEFT BLANK

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 9

Epson Research and Development Page 3

Vancouver Design Center

Table of Contents

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.1 Scope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

1.2 Overview Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.1 Integrated Frame Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.2 CPU Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.3 Display Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.4 Display Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.5 Clock Source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.6 Miscellaneous . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.7 Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3 Typical System Implementation Diagrams . . . . . . . . . . . . . . . . . . . . . . 12

4 Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

4.1 Functional Block Descriptions . . . . . . . . . . . . . . . . . . . . . . . . 15

4.1.1 Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

4.1.2 Memory Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

4.1.3 Sequence Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

4.1.4 Look-Up Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

4.1.5 LCD Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

4.1.6 Power Save . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

5 Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5.1 Pinout Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5.2 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.2.1 Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.2.2 LCD Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

5.2.3 Clock Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

5.2.4 Miscellaneous . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

5.2.5 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

5.3 Summary of Configuration Options . . . . . . . . . . . . . . . . . . . . . . 22

5.4 Host Bus Interface Pin Mapping . . . . . . . . . . . . . . . . . . . . . . . 22

5.5 LCD Interface Pin Mapping . . . . . . . . . . . . . . . . . . . . . . . . . 23

6 D.C. Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

7 A.C. Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

7.1 Bus Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

7.1.1 SH-4 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

7.1.2 SH-3 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

7.1.3 Motorola MC68K #1 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . 30

7.1.4 Motorola MC68K #2 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . 31

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

Page 10

Page 4 Epson Research and Development

Vancouver Design Center

7.1.5 Generic #1 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

7.1.6 Generic #2 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

7.2 Clock Input Requirements . . . . . . . . . . . . . . . . . . . . . . . . . .34

7.3 Display Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

7.3.1 Power On/Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

7.3.2 Power Down/Up Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

7.3.3 Single Monochrome 4-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . 38

7.3.4 Single Monochrome 8-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . 40

7.3.5 Single Color 4-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

7.3.6 Single Color 8-Bit Panel Timing (Format 1) . . . . . . . . . . . . . . . . . . . . . 44

7.3.7 Single Color 8-Bit Panel Timing (Format 2) . . . . . . . . . . . . . . . . . . . . . 46

7.3.8 Dual Monochrome 8-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . 48

7.3.9 Dual Color 8-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

7.3.10 9/12-Bit TFT/D-TFD Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . 52

8 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

8.1 Register Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

8.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

9 Frame Rate Calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

10 Display Data Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

11 Look-Up Table Architectur e . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

11.1 Monochrome Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

11.2 Color Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

12 SwivelView™ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

12.1 Default SwivelView Mode . . . . . . . . . . . . . . . . . . . . . . . . . .77

12.1.1 How to Set Up Default SwivelView Mode . . . . . . . . . . . . . . . . . . . . . . 78

12.2 Alternate SwivelView Mode . . . . . . . . . . . . . . . . . . . . . . . . .79

12.2.1 How to Set Up Alternate SwivelView Mode . . . . . . . . . . . . . . . . . . . . . 80

12.3 Comparison Between Default and Alternate SwivelView Modes . . . . . . . . . . .81

12.4 SwivelView Mode Limitations . . . . . . . . . . . . . . . . . . . . . . . .81

13 Power Save Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82

13.1 Software Power Save Mode . . . . . . . . . . . . . . . . . . . . . . . . .82

13.2 Hardware Power Save Mode . . . . . . . . . . . . . . . . . . . . . . . . .82

13.3 Power Save Mode Function Summary . . . . . . . . . . . . . . . . . . . . .83

13.4 Panel Power Up/Down Sequence . . . . . . . . . . . . . . . . . . . . . . .83

13.5 Turning Off BCLK Between Accesses . . . . . . . . . . . . . . . . . . . . .84

13.6 Clock Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

14 Mechanical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

15 Sales and Technical Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 11

Epson Research and Development Page 5

Vancouver Design Center

List of Tables

Table 5-1: Summary of Power On/Reset Options . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 5-2: Host Bus Interface Pin Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 5-3: LCD Interface Pin Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 6-1: Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 6-2: Recommended Operating Conditions for Core VDD = 3.3V ± 10% . . . . . . . . . . . 24

Table 6-3: Input Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 6-4: Output Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 7-1: SH-4 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 7-2: SH-3 Bus Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 7-3: MC68K #1 Bus Timing (MC68000) . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 7-4: MC68K #2 Timing (MC68030) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 7-5: Generic #1 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 7-6: Generic #2 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 7-7: Clock Input Requirements for CLKI. . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 7-8: Clock Input Requirements for BCLK . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 7-9: LCD Panel Power On/Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 7-10: Power Down/Up Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 7-11: Single Monochrome 4-Bit Panel A.C. Timing. . . . . . . . . . . . . . . . . . . . . . . 39

Table 7-12: Single Monochrome 8-Bit Panel A.C. Timing. . . . . . . . . . . . . . . . . . . . . . . 41

Table 7-13: Single Color 4-Bit Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 7-14: Single Color 8-Bit Panel A.C. Timing (Format 1) . . . . . . . . . . . . . . . . . . . . . 45

Table 7-15: Single Color 8-Bit Panel A.C. Timing (Format 2) . . . . . . . . . . . . . . . . . . . . . 47

Table 7-16: Dual Monochrome 8-Bit Panel A.C. Timing. . . . . . . . . . . . . . . . . . . . . . . . 49

Table 7-17: Dual Color 8-Bit Panel A.C. Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 7-18: TFT/D-TFD A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 8-1: Panel Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 8-2: Gray Scale/Color Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 8-3: High Performance Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 8-4: Inverse Video Mode Select Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 8-5: Hardware Power Save/GPIO0 Operation . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 8-6: Software Power Save Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 8-7: Selection of SwivelView Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 8-8: Selection of PCLK and MCLK in SwivelView Mode. . . . . . . . . . . . . . . . . . . 68

Table 12-1: Default and Alternate SwivelView Mode Comparison . . . . . . . . . . . . . . . . . . 81

Table 13-1: Power Save Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 13-2: Software Power Save Mode Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 13-3: Hardware Power Save Mode Summary . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 13-4: Power Save Mode Function Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 13-5: S1D13705 Internal Clock Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . 85

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

Page 12

Page 6 Epson Research and Development

Vancouver Design Center

THIS PA GE LEFT BLANK

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 13

Epson Research and Development Page 7

Vancouver Design Center

List of Figures

Figure 3-1: Typical System Diagram (SH-4 Bus). . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Figure 3-2: Typical System Diagram (SH-3 Bus). . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Figure 3-3: Typical System Diagram (M68K #1 Bus) . . . . . . . . . . . . . . . . . . . . . . . . .13

Figure 3-4: Typical System Diagram (M68K #2 Bus) . . . . . . . . . . . . . . . . . . . . . . . . .13

Figure 3-5: Typical System Diagram (Generic #1 Bus) . . . . . . . . . . . . . . . . . . . . . . . .14

Figure 3-6: Typical System Diagram (Generic #2 Bus - e.g. ISA Bus). . . . . . . . . . . . . . . . .14

Figure 4-1: System Block Diagram Showing Data Paths. . . . . . . . . . . . . . . . . . . . . . . .15

Figure 5-1: Pinout Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Figure 7-1: SH-4 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Figure 7-2: SH-3 Bus Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Figure 7-3: MC68K #1 Bus Timing (MC68000) . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Figure 7-4: MC68K #2 Timing (MC68030) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Figure 7-5: Generic #1 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

Figure 7-6: Generic #2 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Figure 7-7: Clock Input Requirements for CLKI . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

Figure 7-8: Clock Input Requirements for BCLK . . . . . . . . . . . . . . . . . . . . . . . . . . .35

Figure 7-9: LCD Panel Power On/Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

Figure 7-10: Power Down/Up Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Figure 7-11: Single Monochrome 4-Bit Panel Timing. . . . . . . . . . . . . . . . . . . . . . . . . .38

Figure 7-12: Single Monochrome 4-Bit Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . .39

Figure 7-13: Single Monochrome 8-Bit Panel Timing. . . . . . . . . . . . . . . . . . . . . . . . . .40

Figure 7-14: Single Monochrome 8-Bit Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . .41

Figure 7-15: Single Color 4-Bit Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Figure 7-16: Single Color 4-Bit Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . . .43

Figure 7-17: Single Color 8-Bit Panel Timing (Format 1). . . . . . . . . . . . . . . . . . . . . . . .44

Figure 7-18: Single Color 8-Bit Panel A.C. Timing (Format 1) . . . . . . . . . . . . . . . . . . . . .45

Figure 7-19: Single Color 8-Bit Panel Timing (Format 2). . . . . . . . . . . . . . . . . . . . . . . .46

Figure 7-20: Single Color 8-Bit Panel A.C. Timing (Format 2) . . . . . . . . . . . . . . . . . . . . .47

Figure 7-21: Dual Monochrome 8-Bit Panel Timing. . . . . . . . . . . . . . . . . . . . . . . . . . .48

Figure 7-22: Dual Monochrome 8-Bit Panel A.C. Timing. . . . . . . . . . . . . . . . . . . . . . . .49

Figure 7-23: Dual Color 8-Bit Panel Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

Figure 7-24: Dual Color 8-Bit Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

Figure 7-25: 12-Bit TFT/D-TFD Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

Figure 7-26: TFT/D-TFD A.C. Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

Figure 8-1: Screen-Register Relationship, Split Screen . . . . . . . . . . . . . . . . . . . . . . . . .65

Figure 10-1: 1/2/4/8 Bit-Per-Pixel Display Data Memory Organization. . . . . . . . . . . . . . . . .70

Figure 11-1: 1 Bit-per-pixel Monochrome Mode Data Output Path . . . . . . . . . . . . . . . . . . .71

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

Page 14

Page 8 Epson Research and Development

Vancouver Design Center

Figure 11-2: 2 Bit-per-pixel Monochrome Mode Data Output Path . . . . . . . . . . . . . . . . . . .71

Figure 11-3: 4 Bit-per-pixel Monochrome Mode Data Output Path . . . . . . . . . . . . . . . . . . .72

Figure 11-4: 1 Bit-per-pixel Color Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . .73

Figure 11-5: 2 Bit-per-pixel Color Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . .74

Figure 11-6: 4 Bit-per-pixel Color Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . .75

Figure 11-7: 8 Bit-per-pixel Color Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . .76

Figure 12-1: Relationship Between The Screen Image and the Image Refreshed by

S1D13705 in Default Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

Figure 12-2: Relationship Between The Screen Image and the Image Refreshed by

S1D13705 in Alternate Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

Figure 13-1: Panel On/Off Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

Figure 14-1: Mechanical Drawing QFP14 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .86

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 15

Epson Research and Development Page 9

Vancouver Design Center

1 Introduction

1.1 Scope

This is the Hardware Functi onal Specifi cation for the S1 D13705 Embedded Memor y LCD

Controller Chip. Included in this document are timing diagrams, AC and DC characteristics, register descriptions, and power management descriptions. This document is

intended for two audiences: Video Subsystem Designers and Software Developers.

This document is updated as appropriate. Please check for the latest revision of this

document before beginning any development. The latest revision can be downloaded at

www.erd.epson.com.

We appreciate your comments on our documentation. Please contact us via email at

documentation@erd.epson.com.

1.2 Overview Description

The S1D13705 is a color / monochrome LCD graphics controller with an embedded 80K

byte SRAM display buffer. The high int egration of the S1D13 705 provides a low cos t, low

power, single chip solution to meet the requirements of embedded markets such as Office

Automation equipment, Mobile Communications devices, and Hand-Held PCs where

board size and battery life are major concerns.

Products requiring a “Portrait” display can take advantage of the SwivelView™ Mode

feature of the S1D13705. Virtual and Split Screen are just some of the display modes

supported. The above features, combined with the Operating System independence of the

S1D13705, make it the ideal solution for a wide variety of applications.

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

Page 16

Page 10 Epson Research and Development

Vancouver Design Center

2 Features

2.1 Integrated Frame Buffer

• Embedded 80K byte SRAM display buffer.

2.2 CPU Interface

• Direct support of the following interfaces:

Hitachi SH-3.

Hitachi SH-4.

Motorola M68 K.

MPU bus interface using WAIT# signal.

• Direct mem ory mapping of internal r egisters.

• Single level CPU write buffer.

• Registers are mapped into upper 32 bytes of 128K byte address space.

• The complete 80K byte display buffe r is directl y and contiguou sly avai lable throu gh the

17-bit address bus.

2.3 Display Support

• 4/8-bit monochrome LCD interface.

• 4/8-bit color LCD interface.

• Single-panel, single-drive passive displays.

• Dual-panel, dual-drive passive displays.

• Active Matrix TFT / D-TFD interface

• Register level support for EL panels.

• Example resolutions:

640x480 at a color depth of 2 bpp

640x240 at a color depth of 4 bpp

320x240 at a color depth of 8 bpp

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 17

Epson Research and Development Page 11

Vancouver Design Center

2.4 Display Modes

• SwivelView™: direct 90° hardware rotation of display image for portrait mode display

• 1/2/4 bit-per-pixel (bpp), 2/4/16-level grayscale display.

• 1/2/4/8 bit-per-pixel, 2/4/16/256-level color display.

• Up to 16 shades of gray by FRM on monochrome passive LCD panels; a 256x4 LookUp Table is used to map 1/2/4 bpp modes into these shades.

• 256 simultaneous of 4096 colors on color passive and active matrix LCD panels; three

256x4 Look-Up Tables are used to map 1/2/4/8 bpp modes into these colors.

• Split screen display for all landscape panel modes allows two different images to be

simultaneously displa yed.

• Virtual display support (displays images larger than the panel size through the use of

panning).

2.5 Clock Source

• Maximum operating clock (CLK) frequency of 25MHz.

• Operating clock (CLK) is derived from CLKI input.

• Pixel Clock (PCLK) and Memory Clock (MCLK) are derived from CLK.

2.6 Miscellaneous

• Hardware/Software Video Invert.

• Softwar e Power Save mode.

• Hardware Power Save mode.

• LCD power-down sequencing.

• 5 General Purpose Input/Output pins are available.

• Core operates from 2.7 volts to 3.6 volts.

CLK = CLKI

or

CLK = CLKI/2

• GPIO0 is available if Hardware Power Save is not required.

• GPIO[4:1] are available if upper LCD data pins (FPDAT[11:8]) are not required for

TFT/D-TFD support or hardware inverse video.

• IO Operates from the core voltag e up to 5.5 volts.

2.7 Package

• 80 pin QFP14 package.

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

Page 18

Page 12 Epson Research and Development

Vancouver Design Center

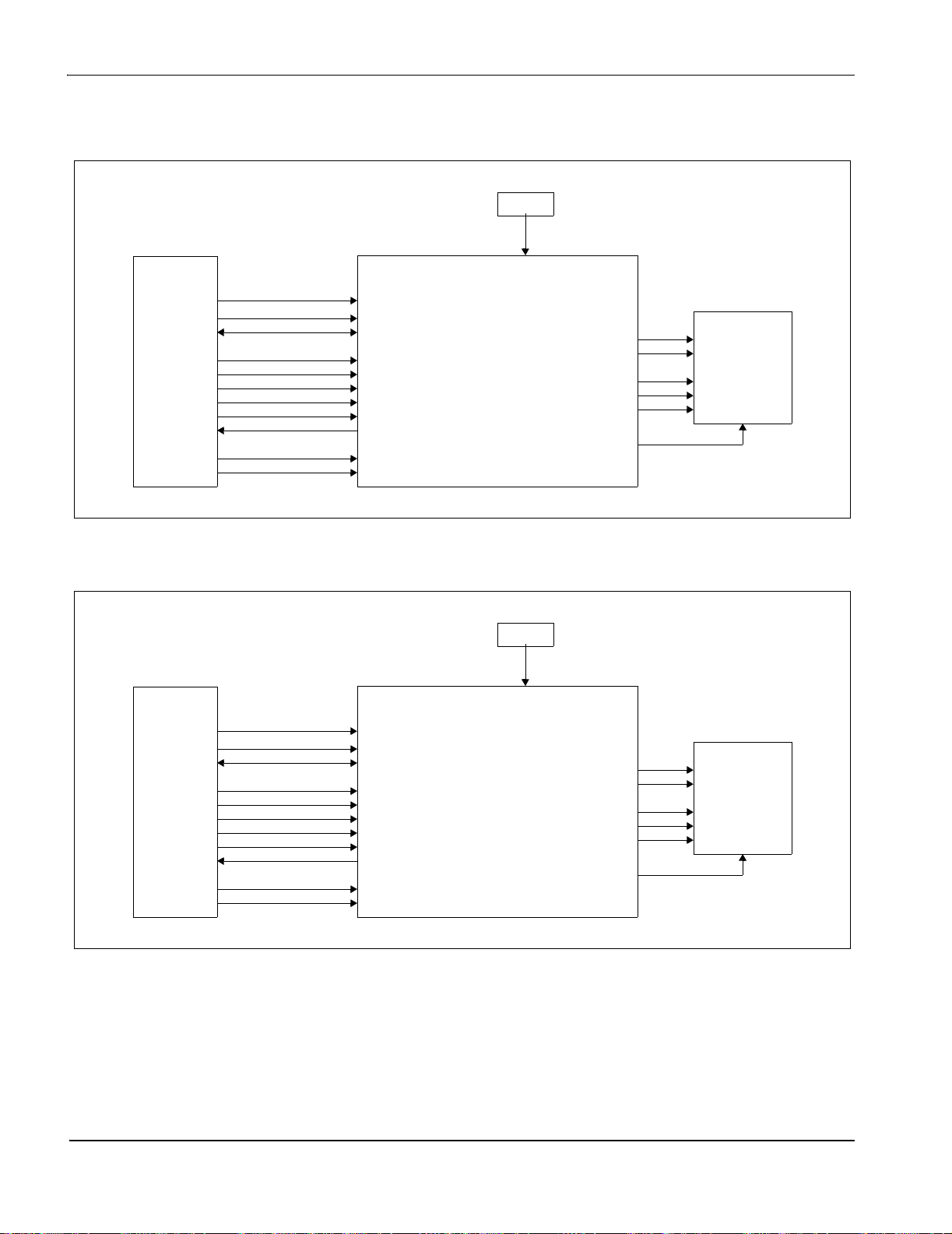

3 Typical System Implementation Diagrams

.

Oscillator

SH-4

BUS

SH-3

BUS

CSn#

A[16:0]

D[15:0]

WE1#

BS#

RD/WR#

RD#

WE0#

RDY#

CKIO

RESET#

CSn#

A[16:0]

D[15:0]

WE1#

BS#

RD/WR#

RD#

WE0#

WAIT#

CKIO

RESET#

CLKI

CS#

AB[16:0]

DB[15:0]

WE1#

BS#

RD/WR#

RD#

WE0#

WAIT#

BCLK

RESET#

S1D13705

FPDAT[7:0]

FPSHIFT

FPFRAME

FPLINE

DRDY

LCDPWR

Figure 3-1: Typical System Diagram (SH-4 Bus)

.

Oscillator

CLKI

CS#

AB[16:0]

DB[15:0]

WE1#

BS#

RD/WR#

RD#

WE0#

WAIT#

BCLK

RESET#

S1D13705

FPDAT[7:4]

FPSHIFT

FPFRAME

FPLINE

DRDY

LCDPWR

D[7:0]

FPSHIFT

FPFRAME

FPLINE

MOD

D[3:0]

FPSHIFT

FPFRAME

FPLINE

MOD

8-bit

LCD

Display

4-bit

LCD

Display

Figure 3-2: Typical System Diagram (SH-3 Bus)

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 19

Epson Research and Development Page 13

Vancouver Design Center

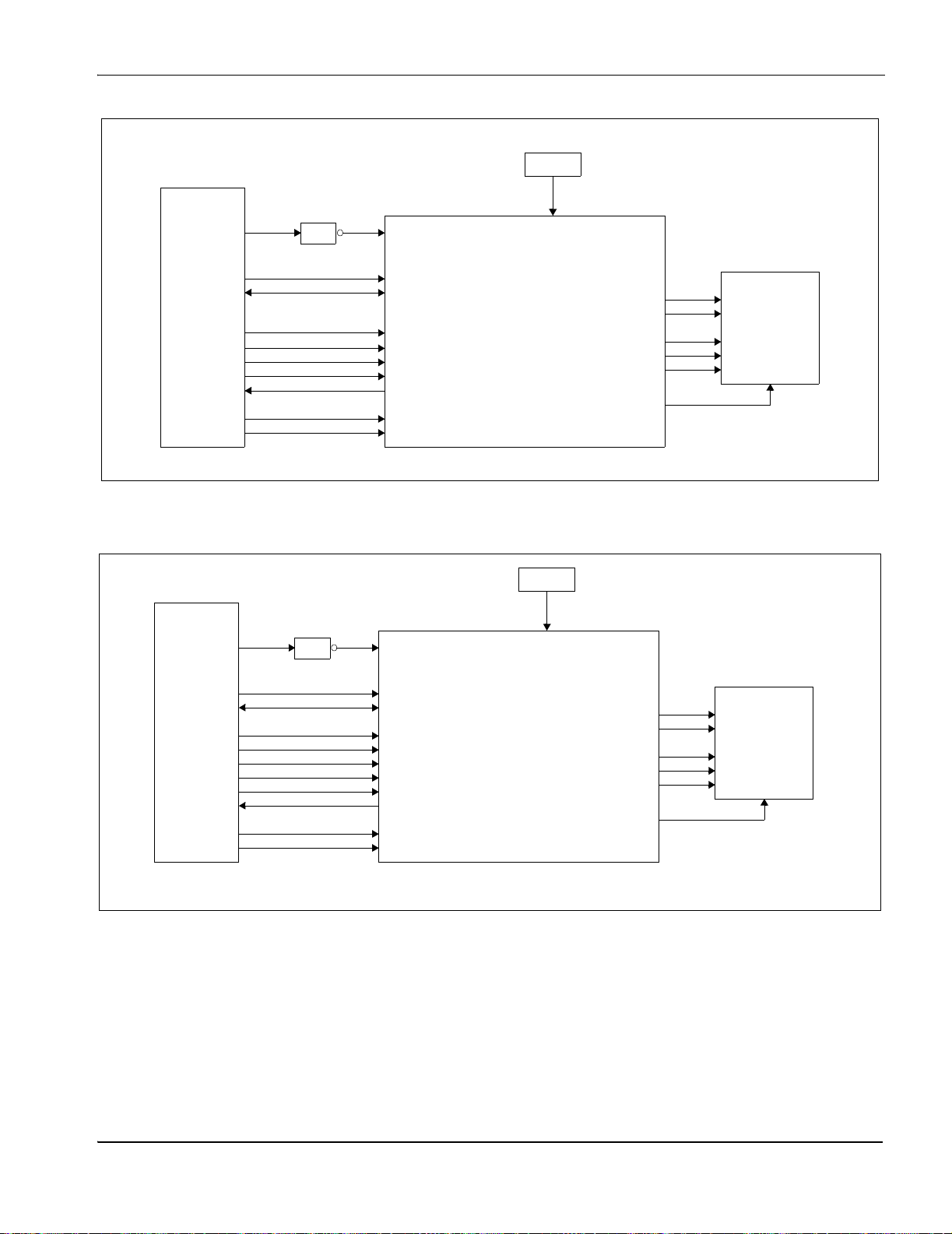

.

Oscillator

MC68000

BUS

A[23:17]

FC0, FC1, FC2

Decoder

CS#

CLKI

MC68030

BUS

A[31:17]

FC0, FC1, FC2

D[31:16]

DSACK1#

RESET#

A[16:1]

D[15:0]

LDS#

UDS#

AS#

R/W#

DTACK#

CLK

RESET#

A[16:0]

DS#

AS#

R/W#

SIZ1

SIZ0

CLK

AB[16:1]

DB[15:0]

AB0

WE1#

BS#

RD/WR#

WAIT#

BCLK

RESET#

S1D13705

FPDAT[7:4]

FPSHIFT

FPFRAME

FPLINE

LCDPWR

Figure 3-3: Typical System Diagram (M68K #1 Bus)

.

Oscillator

Decoder

CS#

AB[16:0]

DB[15:0]

WE1#

BS#

RD/WR#

RD#

WE0#

WAIT#

BCLK

RESET#

S1D13705

CLKI

FPDAT[7:0]

FPSHIFT

FPFRAME

FPLINE

DRDY

LCDPWR

DRDY

D[3:0]

FPSHIFT

FPFRAME

FPLINE

MOD

D[7:0]

FPSHIFT

FPFRAME

FPLINE

MOD

4-bit

LCD

Display

8-bit

LCD

Display

Figure 3-4: Typical System Diagram (M68K #2 Bus)

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

Page 20

Page 14 Epson Research and Development

Vancouver Design Center

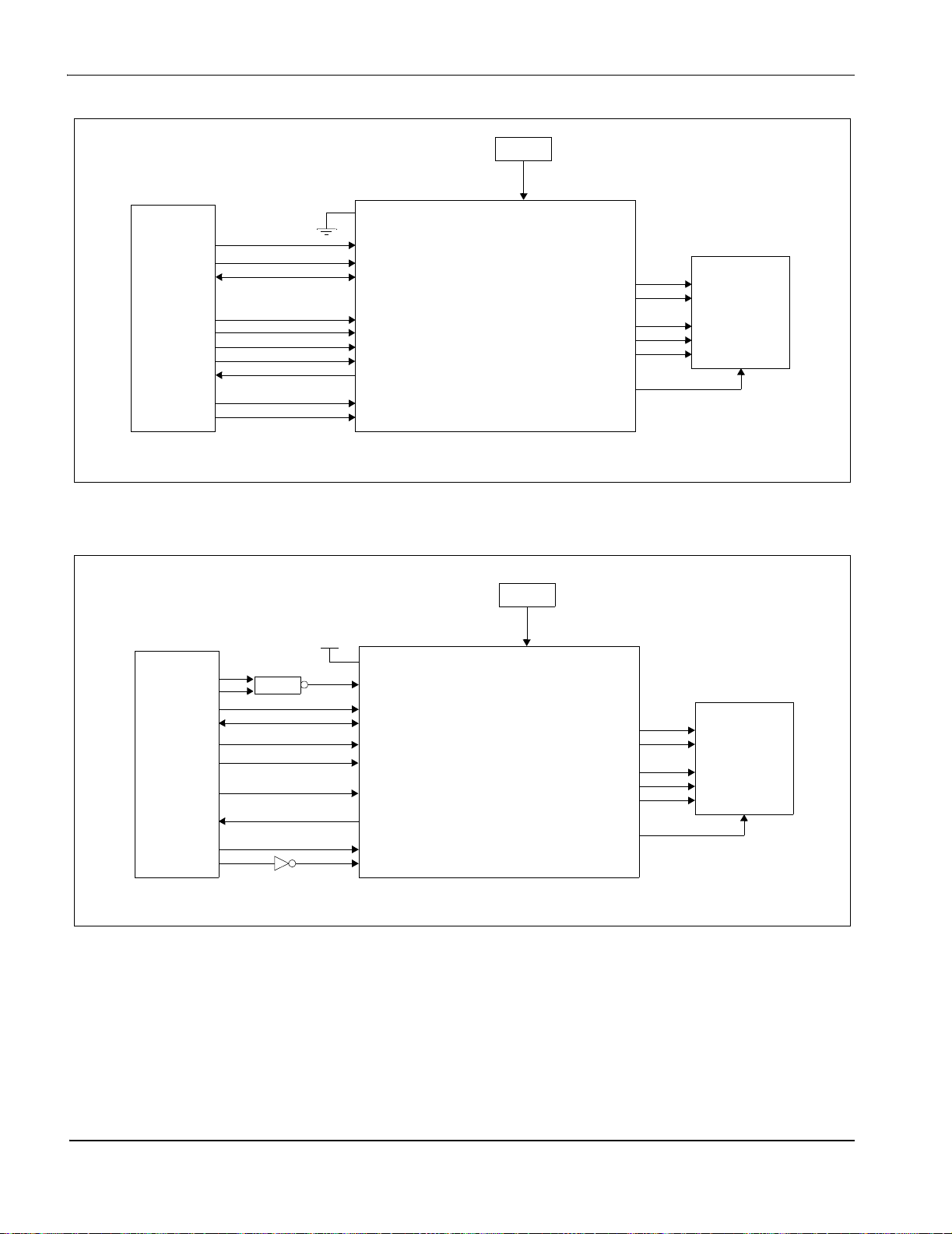

.

Oscillator

GENERIC #1

BUS

ISA

BUS

CSn#

A[16:0]

D[15:0]

WE0#

WE1#

RD0#

RD1#

WAIT#

BCLK

RESET#

REFRESH

SA[19:17]

SA[16:0]

SD[15:0]

SMEMW#

SMEMR#

SBHE#

IOCHRDY

BCLK

RESET

BS#

CS#

AB[16:0]

DB[15:0]

WE0#

WE1#

RD

RD/WR#

WAIT#

BCLK

RESET#

S1D13705

CLKI

FPDAT[11:0]

FPSHIFT

FPFRAME

FPLINE

LCDPWR

Figure 3-5: Typical System Diagram (Generic #1 Bus)

.

Oscillator

Decoder

BS#

CS#

AB[16:0]

DB[15:0]

WE0#

RD#

WE1#

WAIT#

BCLK

RESET#

S1D13705

CLKI

FPDAT[8:0]

FPSHIFT

FPFRAME

FPLINE

LCDPWR

DRDY

DRDY

D[11:0]

FPSHIFT

FPFRAME

FPLINE

DRDY

D[8:0]

FPSHIFT

FPFRAME

FPLINE

DRDY

12-bit

TFT

Display

9-bit

TFT

Display

Figure 3-6: Typical System Diagram (Generic #2 Bus - e.g. ISA Bus)

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 21

Epson Research and Development Page 15

Vancouver Design Center

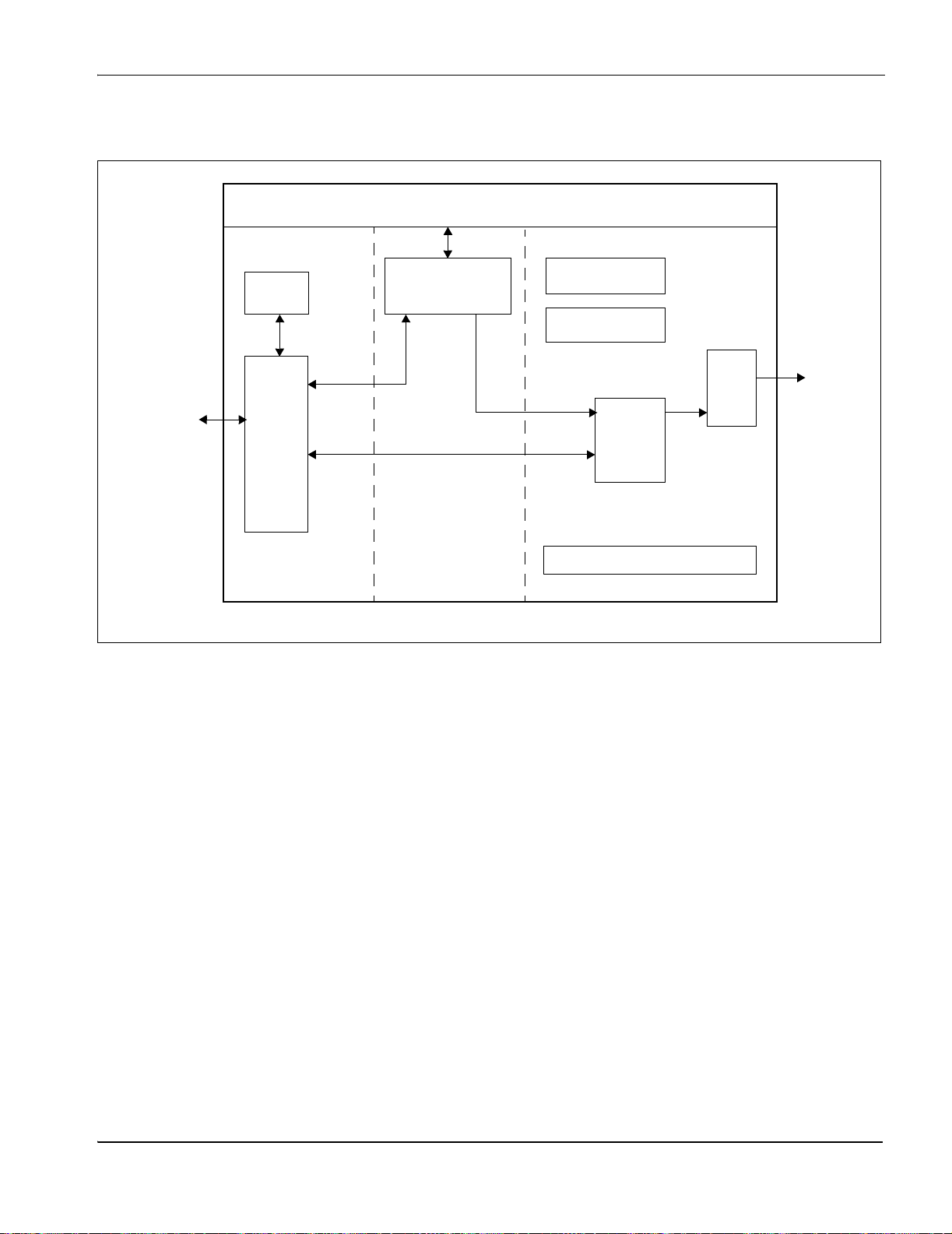

4 Functional Block Diagram

40k x 16-bit SRAM

Memory

Controller

Generic MPU

MC68K

SH-3

SH-4

Register

Host

I/F

Bus Clock Memory Clock Pixel Clock

Figure 4-1: System Block Diagram Showing Data Paths

4.1 Functional Block Descriptions

Power Save

Clocks

Look-Up

Table

Sequence Controller

LCD

I/F

LCD

4.1.1 Host Interface

The Host Interface p rovides t he mean s for the CPU/MPU to c ommunicate wi th the displ ay

buffer and internal registers.

4.1.2 Memory Contro ll er

The Memory Controller arbitrates between CPU accesses and display refresh accesses. It

also gene rates the necessary signa ls to control the SRAM fr ame buffer.

4.1.3 Sequence Controller

The Sequence Controller controls data flow from the Memory Controller throug h the LookUp Table and to the LCD Interf ace. It als o genera tes memory addresses for displa y refres h

accesses.

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

Page 22

Page 16 Epson Research and Development

Vancouver Design Center

4.1.4 Look-Up Table

The Look-Up Table contains thr ee 256x4 Look-Up Tables or pal ettes, one for each primary

color. In monochrome mode only the green Look-Up Table is used.

4.1.5 LCD Interface

The LCD Interface performs frame rate modulation for passive LCD panels. It also

generates the correct data format and timing control signals for various LCD and

TFT/D-TFD panels.

4.1.6 Power Save

Power Save contains the power save mode circuitry.

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 23

Epson Research and Development Page 17

Vancouver Design Center

5 Pins

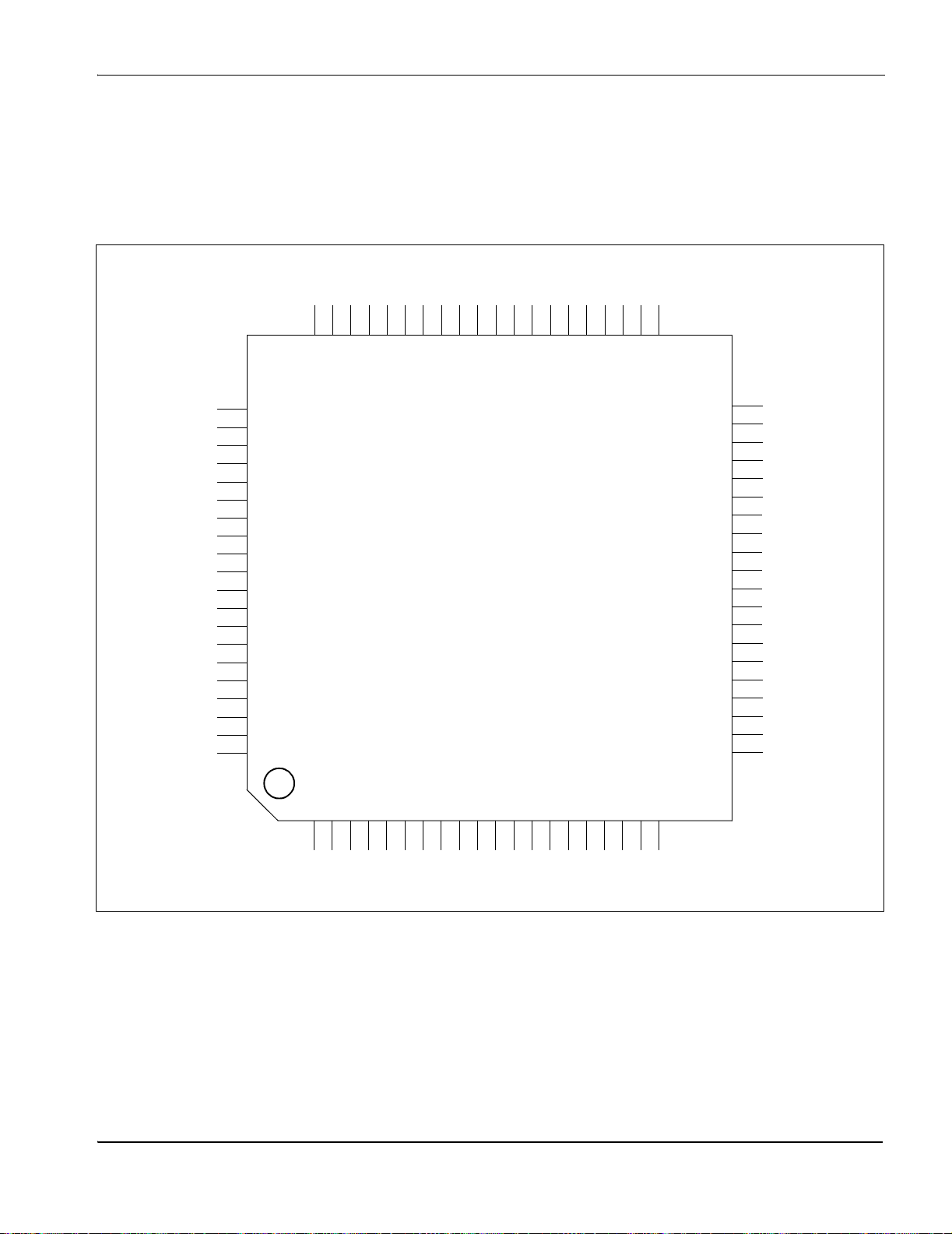

5.1 Pinout Diagram

60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41

AB11

AB9

AB10

VSS

AB12

AB13

AB14

AB15

VSS

CLKI

IOVDD

CNF1

CNF0

CNF2

CNF3

AB16

TESTEN

COREVDD

LCDPWR

DRDY

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

COREVDD

AB8

AB7

AB6

AB5

AB4

AB3

AB2

AB1

AB0

BCLK

VSS

RESET#

CS#

BS#

RD#

WE0#

WE1#

RD/WR#

VSS

S1D13705

COREVDD

WAIT#

DB15

1234567891011121314151617181920

DB14

DB13

DB12

DB11

DB10

IOVDD

DB9

DB7

DB6

DB5

DB4

DB3

DB8

DB2

VSS

DB0

DB1

VSS

FPFRAME

FPLINE

FPDAT0

FPDAT1

FPDAT2

FPDAT3

FPDAT4

FPDAT5

FPDAT6

FPDAT7

IOVDD

FPSHIFT

VSS

FPDAT8

FPDAT9

FPDAT10

FPDAT11

GPIO0

COREVDD

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

Figure 5-1: Pinout Diagram

Note

Package type: 80 pin surface mount QFP14

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

Page 24

Page 18 Epson Research and Development

Vancouver Design Center

5.2 Pin Description

Key:

I=Input

O=Output

IO = Bi-Directional (Input/Output)

P=Power pin

C = CMOS level input

CS = CMOS level Schmitt input

COx = CMOS output driver, x denotes driver type (see I

TSx =

CNx =

TEST = CMOS level test input with pull down resistor

Tri-state CMOS output driver, x denotes driver type (see IOL/IOH in Table 6-4: “Output Specifications,” on

page 25)

CMOS low-noise outp ut dri ver, x de not es dri ve r ty pe (s ee I

page 25)

5.2.1 Host Interface

in Table 6-4: “Output Specifications,” on page 25)

OL/IOH

in Table 6-4: “Ou tpu t Sp eci fic ati on s ,” on

OL/IOH

Pin NamesTypePin #Cell

AB0 I 70 CS Input

45, 53, 54,

55, 56, 57,

AB[16:1] I

DB[15:0] IO

58, 59, 62,

63, 64, 65,

66, 67, 68,

69

3, 4, 5, 6, 7,

8, 9, 11, 12,

13, 14, 15,

16, 17, 18,

19

C/TS2 Hi-Z

RESET#

C Input These pins input the system address bits 16 through 1 (A[16:1]).

State

Description

This pin has multiple functions.

• For SH-3/SH-4 mode, this pin inputs system address bit 0

(A0).

• For MC68K #1, this pin inputs the lower data strobe (LDS#).

• For MC68K #2, this pin inputs system address bit 0 (A0).

• For Generic #1, this pin inputs system address bit 0 (A0).

• For Generic #2, this pin inputs system address bit 0 (A0).

See Table 5-2: “Host Bus Interface Pin Mapping,” on page 22

summary.

These pins have multiple functions.

• For SH-3/SH-4 mode, these pins are connected to [D15:0].

• For MC68K #1, these pins are connected to D[15:0].

• For MC68K #2, these pins are connected to D[31:16] for a

32-bit device (e.g. MC68030) or D[15:0] for a 16-bit device

(e.g. MC68340).

• For Generic #1, these pins are connected to D[15:0].

• For Generic #2, these pins are connected to D[15:0].

See Table 5-2: “Host Bus Interface Pin Mapping,” on page 22

summary.

for

for

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 25

Epson Research and Development Page 19

Vancouver Design Center

Pin NamesTypePin #Cell

RESET#

State

Description

This pin has multiple functions.

• For SH-3/SH-4 mode, this pin inputs the write enable signal

for the lower data byte (WE0#).

• For MC68K #1, this pin must be tied to IO V

WE0# I 77 CS Input

• For MC68K #2, this pin inputs the bus size bit 0 (SIZ0).

• For Generic #1, this pin input s th e w rite enable signal for the

lower data byte (WE0#).

• For Generic #2, this pin inputs the write enable signal (WE#)

See Table 5-2: “Host Bus Interface Pin Mapping,” on page 22

summary.

This pin has multiple functions.

• For SH-3/SH-4 mode, this pin inputs the write enable signal

for the upper data byte (WE1#).

• For MC68K #1, this pin inputs the upper data strobe (UDS#).

• For MC68K #2, this pin inputs the data strobe (DS#).

WE1# I 78 CS Input

• For Generic #1, this pin input s th e w rite enable signal for the

upper data byte (WE1#).

• For Generic #2, this pin inputs the byte enable signal for the

high data byte (BHE#).

See Table 5-2: “Host Bus Interface Pin Mapping,” on page 22

summary.

CS# I 74 C Input This pin inputs the chip select signal.

BCLK I 71 C Input This pin inputs the system bus clock.

This pin has multiple functions.

• For SH-3/SH-4 mode, this pin inputs the bus start signal

(BS#).

• For MC68K #1, this pin inputs the address strobe (AS#).

BS# I 75 CS Input

• For MC68K #2, this pin inputs the address strobe (AS#).

• For Generic #1, this pin must be tied to V

• For Generic #2, this pin must be tied to IO V

See Table 5-2: “Host Bus Interface Pin Mapping,” on page 22

summary.

This pin has multiple functions.

• For SH-3/SH-4 mode, this pin inputs the RD/WR# signal.

The S1D13705 needs this signal for early decode of the bus

cycle.

• For MC68K #1, this pin inputs the R/W# signal.

RD/WR# I 79 CS Input

• For MC68K #2, this pin inputs the R/W# signal.

• For Generic #1, this pin inputs the read command for the

upper data byte (RD1#).

• For Generic #2, this pin must be tied to IO V

See Table 5-2: “Host Bus Interface Pin Mapping,” on page 22

summary.

SS

.

DD

DD

DD

for

for

.

for

.

for

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

Page 26

Page 20 Epson Research and Development

Vancouver Design Center

Pin NamesTypePin #Cell

RESET#

RD# I 76 CS Input

WAIT# O 2 TS2 Hi-Z

RESET# I 73 CS 0

State

Description

This pin has multiple functions.

• For SH-3/SH-4 mode, this pin inputs the read signal (RD#).

• For MC68K #1, this pin must be tied to IO V

DD

.

• For MC68K #2, this pin inputs the bus size bit 1 (SIZ1).

• For Generic #1, this pin inputs the read command for the

lower data byte (RD0#).

• For Generic #2, this pin inputs the read command (RD#).

See Table 5-2: “Host Bus Interface Pin Mapping,” on page 22 for

summary.

This pin has multiple functions.

• For SH-3 mode, this pin outputs the wait request signal

(WAIT#).

• For SH-4 mode, this pin outputs the device ready signal

(RDY#).

• For MC68K #1, this pin outputs the data transfer

acknowled ge sig nal (DTACK#).

• For MC68K #2, this pin outputs the data transfer and size

acknowledge bit 1 (DSACK1#).

• For Generic #1, this pin outputs the wait signal (WAIT#).

• For Generic #2, this pin outputs the wait signal (WAIT#).

See Table 5-2: “Host Bus Interface Pin Mapping,” on page 22

for

summary.

Active low input to s et all inter nal registe rs t o the def aul t state a nd

to force all signals to their inactive states.

5.2.2 LCD Interface

Pin Name Type Pin # Cell

30, 31, 32,

FPDAT[7:0] O

33, 34, 35,

CN3 0 Panel Data

36, 37

FPDAT[10:8]

FPDAT11

O,

IO

O,

IO

24, 25, 26 CN3 Input

23 CN3 Input

FPFRAME O 39 CN3 0 Frame Pulse

RESET#

State

These pins have multiple functions.

• Panel Data bits [10:8] for TFT/D-TFD panels.

• General Purpose Input/Output pins GPIO[3:1].

These pins should be connected to IO V

See Table 5-3: “LCD Interface Pin Mapping,” on page 23

summary.

This pin has multiple functions.

• Panel Data bit 11 for TFT/D-TFD panels.

• General Purpose Input/Output pin GPIO4.

• Inverse Video select pin.

This pin should be connected to IO V

Table 5-3: “LCD Interface Pin Mapping,” on page 23

summary.

Description

when unused.

DD

when unused. See

DD

for

for

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 27

Epson Research and Development Page 21

Vancouver Design Center

Pin Name Type Pin # Cell

RESET#

State

Description

FPLINE O 38 CN3 0 Line Pulse

FPSHIFT O 28 C N3 0 Shift Clock

LCDPWR O 43 CO1 0 Active high LCD Power Control

This pin has multiple functions.

• TFT/D-TFD Display Enable (DRDY).

DRDY O 42 CN3 0

• LCD Backplane Bias (MOD).

• Second Shift Clock (FPSHIFT2).

See Table 5-3: “LCD Interface Pin Mapping,” on page 23 for

summary.

5.2.3 Clock Input

Pin Name Type Pin # Driver Description

CLKI I 51 C Input Clock

5.2.4 Miscella neous

Pin Name Type Pin # Cell

RESET#

State

These inputs ar e used to c onfigure the S1D1 3705 - s ee Table

CNF[3:0] I

46, 47,

48, 49

C

As set by

hardware

5-1: “Summary of Power On/Reset Options,” on page 22.

Must be connected directly to IO V

This pin has multiple functions - see REG[03h] bit 2.

GPIO0

IO,

I

22

CS/

TS1

Input

• General Purpose Input/Output pin.

• Hardware Po we r Sa ve.

TESTEN I 44 TEST pulled low Test Enable input. This input must be connected to V

Description

DD

or VSS.

SS

.

5.2.5 P o w er Suppl y

Pin Name Type Pin # Driver Description

COREVDD P

IOVDD P 10, 29, 52 P IO VDD

VSS P

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

1, 21, 41,

61

20, 27, 40,

50, 60, 72,

80

PCore V

DD

P Common VSS

Page 28

Page 22 Epson Research and Development

Vancouver Design Center

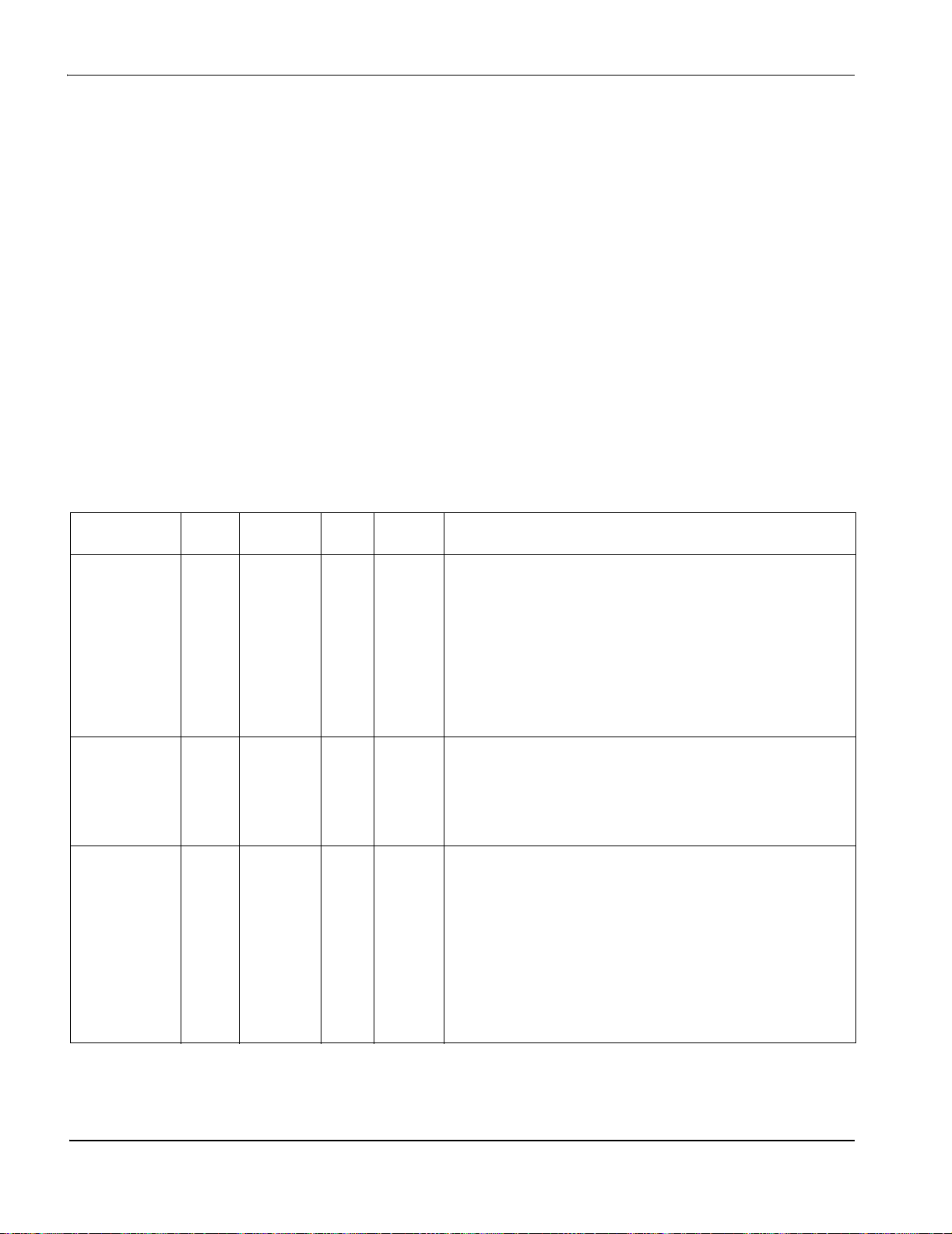

5.3 Summary of Configuration Options

Table 5-1: Summary of Power On/Reset Options

Configuration

Pin

CNF[3:0]

Select host bus interface as follows:

CNF3 CNF2 CNF1 CNF0 BS# Host Bus

1000XSH-4 interface Big Endian

0000XSH-4 interface Little Endian

1001XSH-3 interface Big Endian

0001XSH-3 interface Little Endian

X010X reserved

1011XMC68K #1, 16-bit Big Endian

0011Xreserved

X 1 0 0 X reserved

1101XMC68K #2, 16-bit Big Endian

0101Xreserved

X1100 reserved

X1101 reserved

11110 Generic #1, 16-bit Big Endian

01110 Generic #1, 16-bit Little Endian

11111 reserved

01111 Generic #2, 16-bit Little Endian

Power On/Reset State

5.4 Host Bus Interface Pin Mapping

Table 5-2: Host Bus Interface Pin Mapping

S1D13705

Pin Names

AB[16:1] A[16:1] A[16:1] A[16:1] A[16:1] A[16:1] A[16:1]

AB0 A0 A0 LDS# A0 A0 A0

DB[15:0] D[15:0] D[15:0] D[15:0] D[31:16] D[15:0] D[15:0]

WE1# WE1# WE1# UDS# DS# WE1# BHE#

CS# CSn# CSn# External Decode External Decode External Decode External Decode

BCLK CKIO CKIO CLK CLK BCLK BCLK

BS# B S# BS# AS# AS# connect to V

RD/WR# RD/WR# RD/WR# R/W# R/W# RD1# connect to IO V

RD# RD# RD# connect to IO V

WE0# WE0# WE0# connect to IO V

WAIT# WAIT# RDY# DTACK# DSACK1# WAIT# WAIT#

SH-3 SH-4 MC68K #1 MC68K #2 Generic #1 Generic #2

connect to IO V

SS

DD

DD

SIZ1 RD0# RD#

SIZ0 WE0# WE#

DD

DD

RESET# RESET# RESET# RESET# RESET# RESET# RESET#

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 29

Epson Research and Development Page 23

Vancouver Design Center

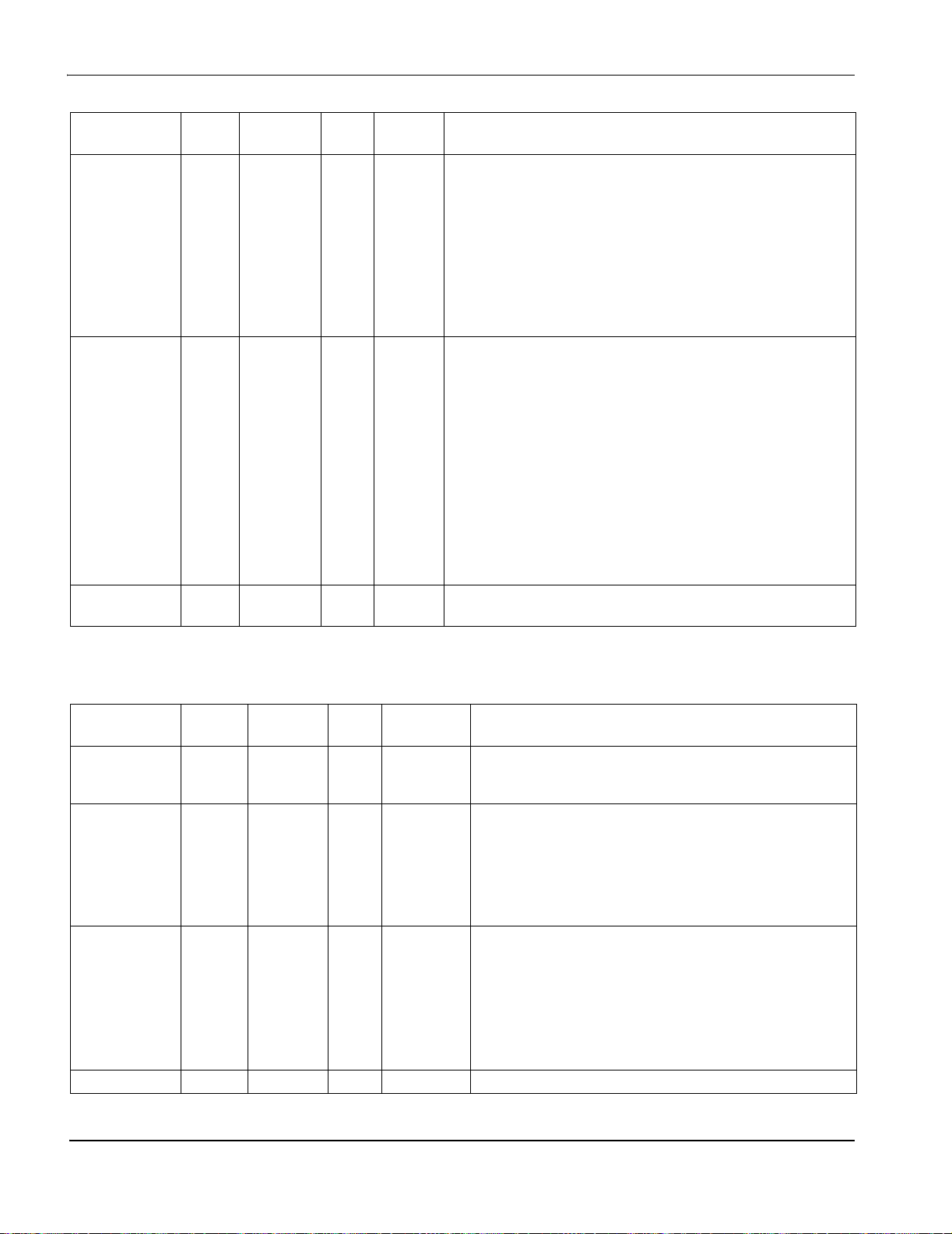

5.5 LCD Interface Pin Mapping

Table 5-3: LCD Interface Pin Mapping

Monochrome Passive Panel Color Passive Panel Color TFT/D-TFD

S1D13705

Pin Name

FPFRAME FPFRAME

FPLINE FPLINE

FPSHIFT FPSHIFT

DRDY MOD MOD MOD MOD FPSHIFT2 MOD MOD DRDY

FPDAT0 driven 0 D0 LD0 driven 0 D0 D0 LD0 R2 R3

FPDAT1 driven 0 D1 LD1 driven 0 D1 D1 LD1 R1 R2

FPDAT2 driven 0 D2 LD2 driven 0 D2 D2 LD2 R0 R1

FPDAT3 driven 0 D3 LD3 driven 0 D3 D3 LD3 G2 G3

FPDAT4 D0 D4 UD0 D0 D4 D4 UD0 G1 G2

FPDAT5 D1 D5 UD1 D1 D5 D5 UD1 G0 G1

FPDAT6 D2 D6 UD2 D2 D6 D6 UD2 B2 B3

FPDAT7 D3 D7 UD3 D3 D7 D7 UD3 B1 B2

FPDAT8 GPIO1 GPIO1 GPIO1 GPIO1 GPIO1 GPIO1 GPIO1 B0 B1

FPDAT9 GPIO2 GPIO2 GPIO2 GPIO2 GPIO2 GPIO2 GPIO2 GPIO2 R0

FPDAT10 GPIO3 GPIO3 GPIO3 GPIO3 GPIO3 GPIO3 GPIO3 GPIO3 G0

FPDAT11

4-bit

Single

GPIO4/

Hardware

Video

Invert

8-bit

Single

GPIO4/

Hardware

Video

Invert

8-bit Dual

GPIO4/

Hardware

Video

Invert

4-bit

Single

GPIO4/

Hardware

Video

Invert

8-bit

Single

Format 1

GPIO4/

Hardware

Video

Invert

8-bit

Single

Format 2

GPIO4/

Hardware

Video

Invert

8-bit Dual 9-bit 12-bit

GPIO4/

Hardware

Video

Invert

GPIO4 B0

Note

1. Unused GPIO pins must be connected to IO VDD.

2. Hardware Video Invert is enabled on FPDAT11 by REG[02h] bit 1.

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

Page 30

Page 24 Epson Research and Development

Vancouver Design Center

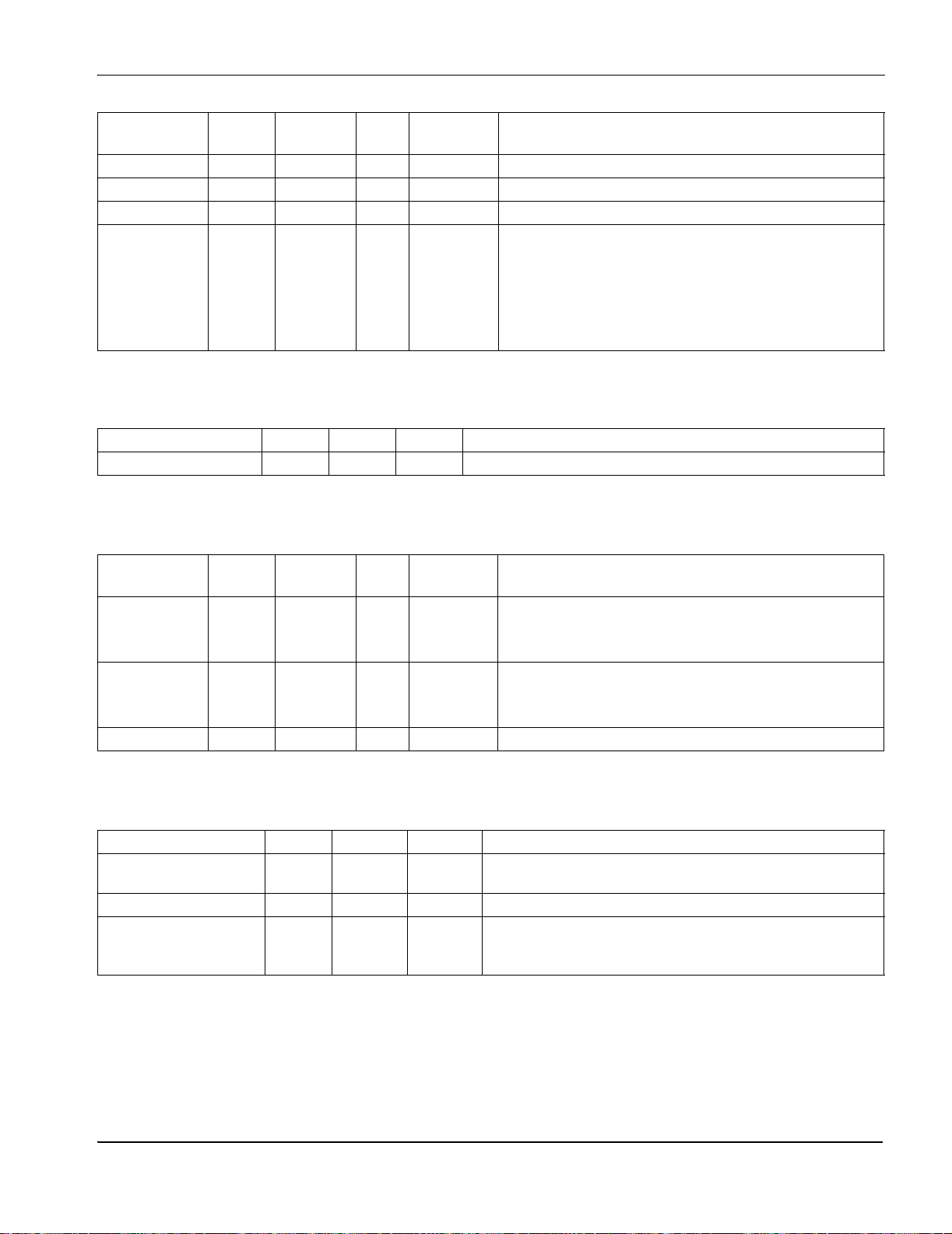

6 D.C. Characteristics

Table 6-1: Absolute Maximum Ratings

Symbol Parameter Rating Units

Core V

DD

IO V

DD

V

IN

V

OUT

T

STG

T

SOL

Symbol Parameter Condition Min Typ Max Units

Core V

DD

IO V

DD

V

IN

T

OPR

Supply Voltage VSS - 0.3 to 4.0 V

Supply Voltage Core VDD to 7.0 V

Input Voltage VSS - 0.3 to IO VDD + 0.5 V

Output Voltage VSS - 0.3 to IO VDD + 0.5 V

Storage Temperature -65 to 150 ° C

Solder Temperature/Time 260 for 10 sec. max at lead ° C

Table 6-2: Recommended Operating Conditions for Core VDD = 3.3V ± 10%

Supply Voltage VSS = 0 V 2.7 3.0/3.3 3.6 V

Supply Voltage VSS = 0 V, IO VDD ≥ Core V

Input Voltage V

Operating Temperature -40 25 85 ° C

2.7 3.0/3.3/5.0 5.5 V

DD

SS

IO V

DD

V

Table 6-3: Input Specifications

Symbol Parameter Condition Min Typ Max Units

= 3.0

IO V

IO V

IO V

IO V

V

DD

V

IH

V

IL

DD

DD

DD

DD

= Max

= V

= V

3.3

5.0

= 3.0

3.3

5.0

= 3.0

3.3

5.0

= 3.0

3.3

5.0

DD

SS

1.9

2.0

3.5

1.0

1.1

2.0

0.5

0.6

0.8

-1 1 µA

V

IL

V

IH

V

T+

V

T-

I

IZ

C

IN

Low Level Input Voltage

CMOS inputs

High Level Input Voltage

CMOS inputs

Positive-going Threshold

CMOS Schmitt inputs

Negative-going Threshold

CMOS Schmitt inputs

Input Leakage Current

Input Pin Capacitance 10 pF

0.8

0.8

1.0

2.3

2.4

4.0

1.7

1.8

3.1

V

V

V

V

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 31

Epson Research and Development Page 25

Vancouver Design Center

Table 6-4: Output Specifications

Symbol Parameter Condition Min Typ Max Units

IO V

= 3.0V

DD

V

I

(3.0V) Low Level Output Current

OL

I

(3.3V) Low Level Output Current

OL

I

(5.0V) Low Level Output Current

OL

(3.0V) High Level Output Current

I

OH

I

(3.3V) High Level Output Current

OH

I

(5.0V) High Level Output Current

OH

V

V

I

C

C

OL

OH

OZ

OUT

BID

Low Level Output Voltage I = I

High Level Output Voltage I = I

Output Leakage Current

Output Pin Capacitance 10 pF

Bidirectional Pin Capacitance 10 pF

= 0.4V, Type = 1

O

IO VDD = 3.3V

= 0.4V, Type = 1

V

O

IO V

= 5.0V

DD

V

= 0.4V, Type = 1

O

IO V

= 3.0V

DD

V

= IO VDD-0.4V, Type = 1

O

IO VDD = 3.3V

= IO VDD-0.4V, Type = 1

V

O

IO V

= 5.0V

DD

V

= IO VDD-0.4V, Type = 1

O

OL

OH

= MAX

V

DD

V

= V

OH

OL

= V

DD

SS

V

2

3

2

3

2

3

2

3

2

3

2

3

IO VDD - 0.4 V

-1 1 µA

1.8

5

10

2

6

12

3

8

12

-1.8

-5

-10

-2

-6

-12

-3

-8

-12

mA

mA

mA

mA

mA

mA

0.4 V

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

Page 32

Page 26 Epson Research and Development

Vancouver Design Center

7 A.C. Characteristics

Conditions: IO VDD = 2.7 V to 5.0 V

= -40° C to 85° C

T

A

T

and T

rise

C

= 60pF (Bus/MPU Interface)

L

C

= 60pF (LCD Panel Interface)

L

7.1 Bus Interface Timing

7.1.1 SH-4 Interface Timing

T

CKIO

CKIO

t4

for all inputs must be < 5 nsec (10% ~ 90%)

fall

t2

t3

t5

A[16:0], M/R#

RD/WR#

BS#

CSn#

WEn#

RD#

RDY#

D[15:0]

(write)

D[15:0]

(read)

Hi-Z

Hi-Z

t6 t7

t8

t12

t9

t13

t15

t10

t16

t17

VALID

t11

t14

Hi-Z

t18

Hi-Z

Figure 7-1: SH-4 Timing

Note

The SH-4 Wait State Control Register for the area in which the S1D13705 resides must be set to

a non-zero value. The SH-4 read-to-write cycle transition must be set to a non-zero value

(with reference to BUSCLK).

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 33

Epson Research and Development Page 27

Vancouver Design Center

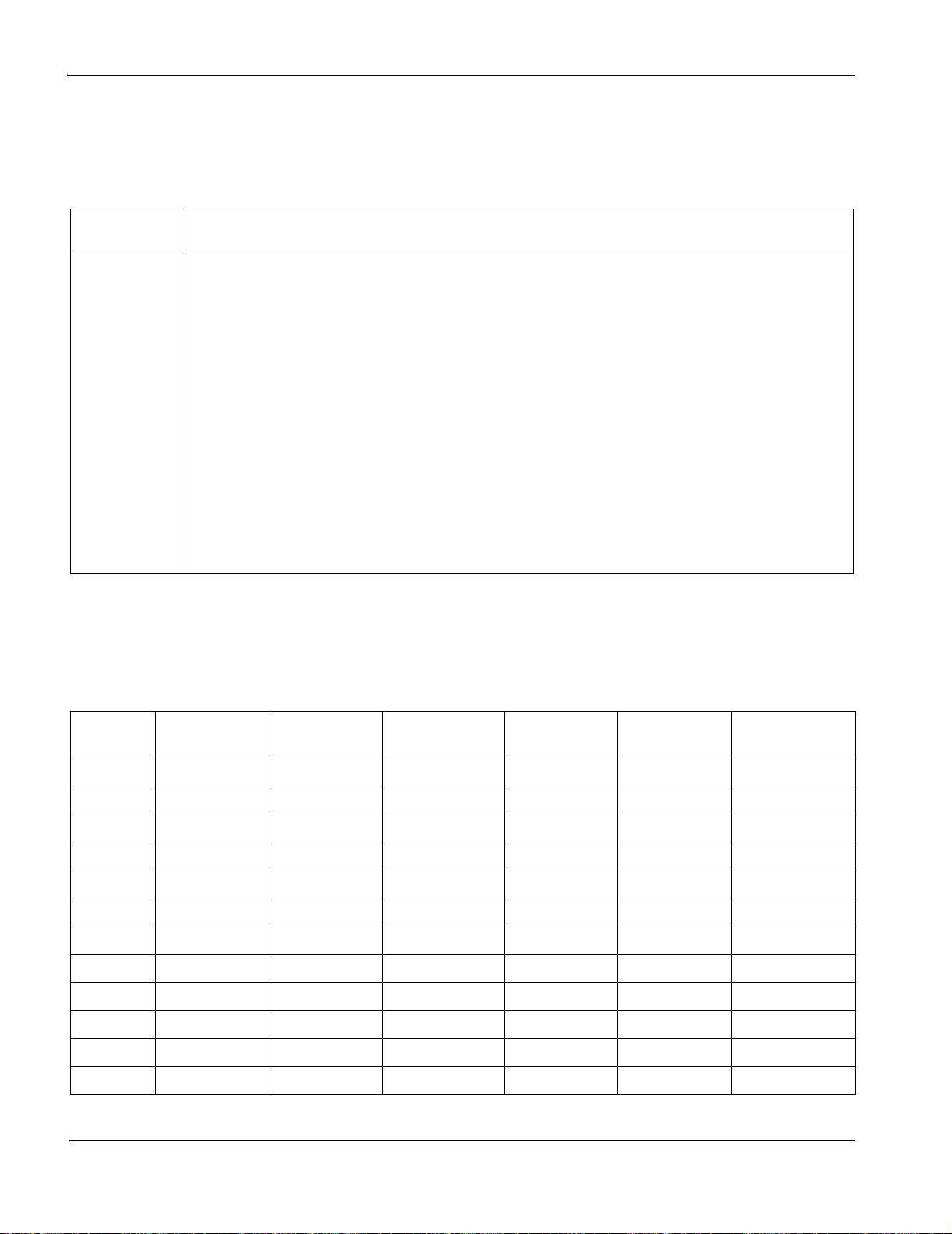

Table 7-1: SH-4 Timing

Symbol Parameter Min Max Units

f

CKIO

T

CKIO

t2

t3

t4

t5

t6

t7

t8

t9

t10

t11

t12

t13

t14

t15

t16

t17

t18

Bus Clock frequency

Bus Clock perio d

Bus Clock pulse width low

Bus Clock pulse width high

A[16:0], RD/WR# setup to CKIO

A[16:0], RD/WR# hold from CS#

BS# setup

BS# hold

CSn# setup

Falling edge RD# to DB[15:0] driven

CKIO to WE#, RD# high

Rising edge CSn# to RDY# high impedance

Falling edge CSn# to RDY# driven

CKIO to RDY# low

Rising edge CSn# to RDY# high

nd

DB[15:0] setup to 2

CKIO after BS# (write cycle)

DB[15:0] hold (write cycle)

RDY# falling edge to DB[15:0] valid (read cycle)

Rising edge RD# to DB[15:0] high impedance (read cycle)

1/f

CKIO

8ns

8ns

0ns

0ns

5ns

5ns

0ns

1.5T

CKIO

0ns

0ns

50 MHz

25 ns

T

CKIO

20 ns

20 ns

16 ns

7ns

10 ns

Note

CKIO may be turned off (held low) between accesses - see Section 13.5, “Turning Off

BCLK Between Accesses” on page 84

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

Page 34

Page 28 Epson Research and Development

Vancouver Design Center

7.1.2 SH-3 Interface Timing

T

CKIO

t2

t3

CKIO

A[16:0], M/R#

RD/WR#

BS#

CSn#

WEn#

RD#

WAIT#

D[15:0]

(write)

D[15:0]

(read)

Hi-Z

Hi-Z

Hi-Z

t4

t6 t7

t8

t12

t5

t9

t10

t11

t13

Hi-Z

t14

t16

VALID

t15

Hi-Z

t17

Hi-Z

Figure 7-2: SH-3 Bus Timing

Note

The SH-3 Wait State Control Register for the are a in whic h the S1D13 705 resides must

be set to a non-zero value.

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 35

Epson Research and Development Page 29

Vancouver Design Center

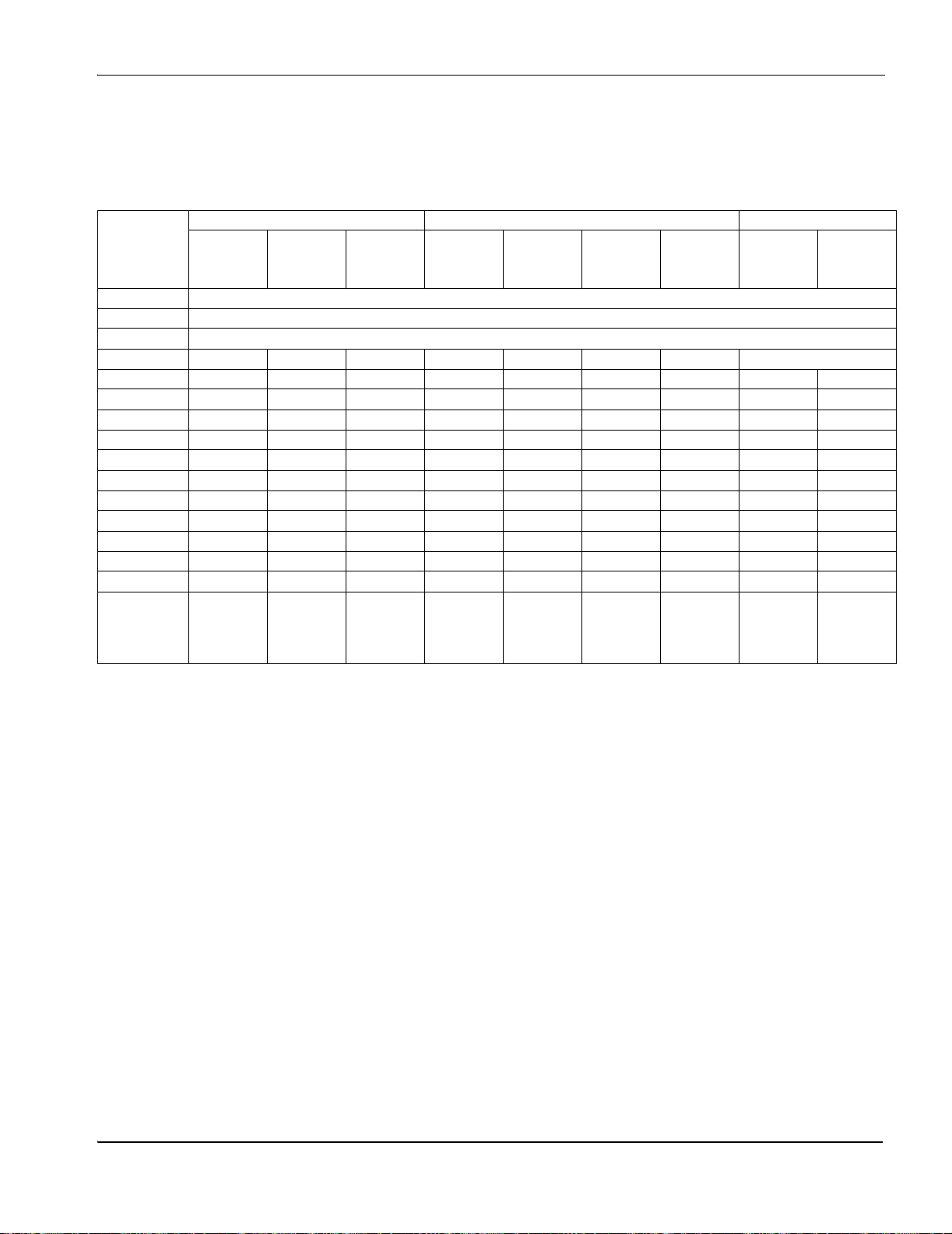

Table 7-2: SH-3 Bus Timing

Symbol Parameter Min Max

f

CKIO

T

CKIO

t2

t3

t4

t5

t6

t7

t8

t9

t10

t11

t12

t13

t14

t15

t16

t17

Bus Clock frequency

Bus Clock perio d

Bus Clock pulse width low

Bus Clock pulse width high

A[16:0], RD/WR# setup to CKIO

A[16:0], RD/WR# hold from CS#

BS# setup

BS# hold

CSn# setup

Falling edge RD# to DB[15:0] driven

CKIO to WEn#, RD# high

Rising edge CSn# to WAIT# high impedance

Falling edge CSn# to WAIT# driven

CKIO to WAIT# delay

nd

DB[15:0] setup to 2

CKIO after BS# (write cycle)

DB[15:0] hold from rising edge of WEn# (write cycle)

WAIT# rising edge to DB[15:0] valid (read cycle)

Rising edge RD# to DB[15:0] high impedance (read cycle)

a

One Software WAIT State Required

1/f

CKIO

8ns

8ns

0ns

0ns

5ns

5ns

0ns

1.5T

CKIO

0ns

0ns

a

Units

50 MHz

25 ns

10 ns

15 ns

20 ns

6ns

10 ns

Note

CKIO may be turned off (held low) between accesses - see Section 13.5, “Turning Off

BCLK Between Accesses” on page 84

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

Page 36

Page 30 Epson Research and Development

Vancouver Design Center

7.1.3 Motorola MC68K #1 Interface Timing

T

CLK

CLK

A[16:1]

CS#

R/W#

AS#

UDS#, LDS#

DTACK#

D[15:0]

(write

D[15:0]

(read)

t1

INVALID

t3

Hi-Z

Hi-Z

Hi-Z

t10

t8

VALID

t4

t11

t5

VALID

VALID

t2

t7

t6

t9

t12

Hi-Z

Hi-Z

Hi-Z

Figure 7-3: MC68K #1 Bus Timing (MC68000)

Table 7-3: MC68K #1 Bus Timing (MC68000)

Symbol Parameter Min Max Units

f

CLK

T

CLK

t1 A[16:1], CS# valid before AS# falling edge 0 ns

t2 A[16:1], CS# hold from AS# rising edge 0 ns

t3 AS# low to DTACK# driven high 16 ns

t4 CLK to DTACK# low 15 ns

t5 CLK to AS#, UDS#, LDS# high 1T

t6 AS# high to DTACK# high 20 ns

t7 AS# high to DTACK# high impedance T

t8 UDS#, LDS# falling edge to D[15:0] valid (write cycle) T

t9 D[15:0] hold from AS# rising edge (write cycle) 0 ns

t10 UDS#, LDS# falling edge to D[15:0] driven (read cycle) 15 ns

t11 D[15:0] valid to DTACK# falling edge (read cycle) 0 ns

t12 UDS#, LDS# rising edge to D[15:0] high impedance 10 ns

Bus Clock Frequency 33 MHz

Bus Clock period 1/f

CLK

CLK

CLK

CLK

Note

CLK may be turned off (held low) between accesses - see Section 13.5, “Turning Off

BCLK Between Accesses” on page 84

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 37

Epson Research and Development Page 31

Vancouver Design Center

7.1.4 Motorola MC68K #2 Interface Timing

T

CLK

CLK

A[16:0]

CS#

SIZ0, SIZ1

R/W#

AS#

DS#

DSACK1#

D[31:16]

(write)

D[31:16]

(read)

t1

t3

Hi-Z

t8

Hi-Z

Hi-Z

t10

VALID

t4

t2

t5

VALID

VALID

t7

t6

t9

t11

Hi-Z

Hi-Z

Hi-Z

Figure 7-4: MC68K #2 Timing (MC68030)

Table 7-4: MC68K #2 Timing (MC68030)

Symbol Parameter Min Max Units

f

CLK

T

CLK

t1 A[16:0], CS#, SIZ0, SIZ1 valid before AS# falling edge 0 ns

t2 A[16:0], CS#, SIZ0, SIZ1 hold from AS#, DS# rising edge 0 ns

t3 AS# low to DSACK1# driven high 22 ns

t4 CLK to DSACK1# low 18 ns

t5 CLK to AS#, DS# high 1T

t6 AS# high to DSACK1# high 20 ns

t7 AS# high to DSACK1# high impedance T

t8 DS# falling edge to D[31:16] valid (write cycle) T

t9 AS#, DS# rising edge to D[31:16] invalid (write cycle) 0 ns

t10 D[31:16] valid to DSACK1# low (read cycle) 0 ns

t11 AS#, DS# rising edge to D[31:16] high impedance 20 ns

Bus Clock frequency 33 MHz

Bus Clock peri od 1/f

CLK

CLK

CLK

CLK

ns

/2

Note

CLK may be turned off (held low) between accesses - see Section 13.5, “Turning Off

BCLK Between Accesses” on page 84

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

Page 38

Page 32 Epson Research and Development

Vancouver Design Center

7.1.5 Generic #1 Interface Timing

T

BCLK

BCLK

A[16:0]

CS#

WE0#,WE1#

RD0#, RD1#

D[15:0]

(write)

D[15:0]

(read)

WAIT#

Hi-Z

Hi-Z

Hi-Z

VALID

t1

t3

VALID

t4

t8

t6

VALID

t9

t11

t2

t5

t7

Hi-Z

t10

Hi-Z

Figure 7-5: Generic #1 Timing

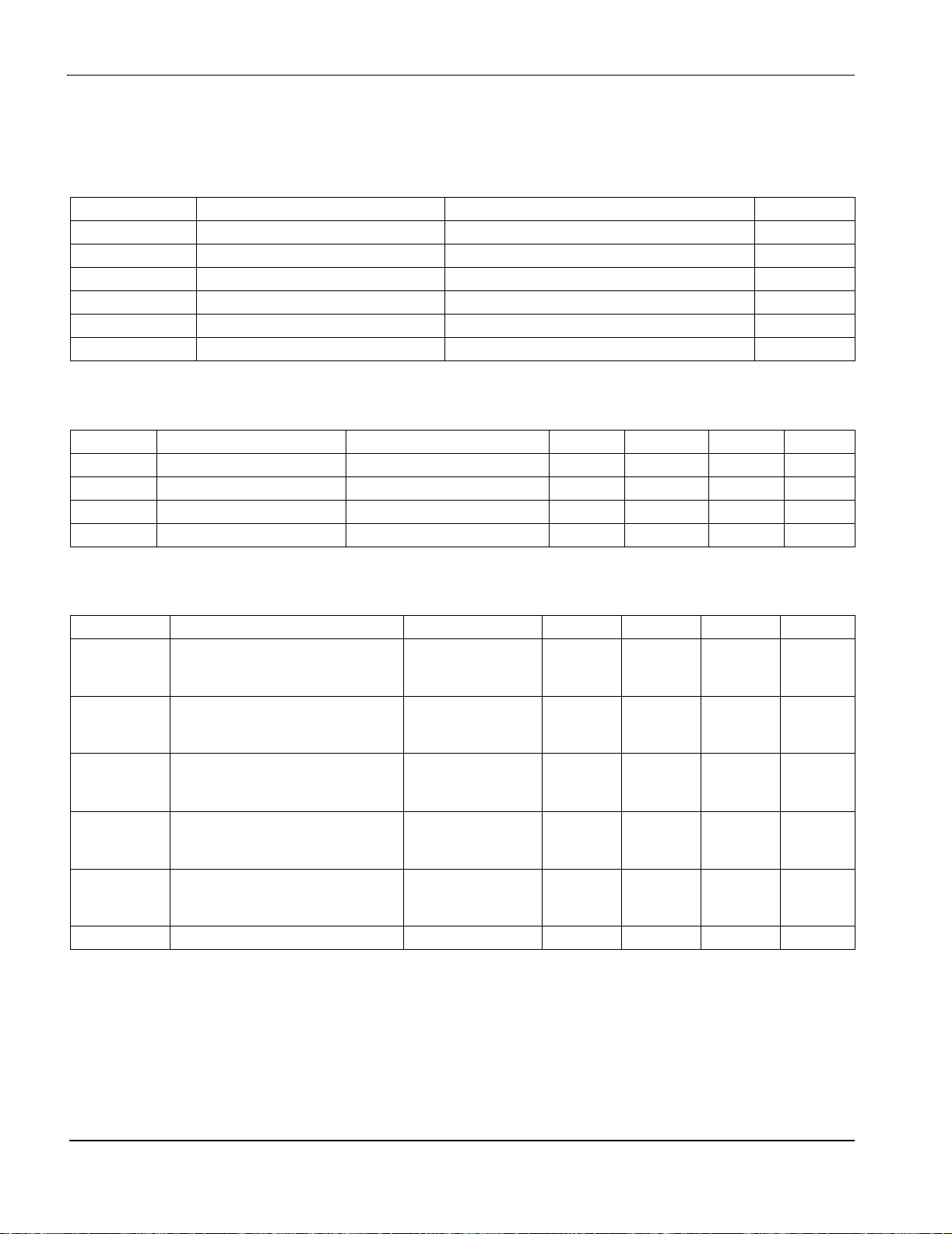

Table 7-5: Generic #1 Timing

Symbol Parameter Min Max Units

f

BCLK

T

BCLK

Bus Clock frequency 50 MHz

Bus Clock period 1/f

A[16:0], CS# valid to WE0#, WE1# low (write cycle) or RD0#, RD1#

t1

low (read cycle)

WE0#, WE1# high (write cycle) or RD0#, RD1# high (read cycle) to

t2

A[16:0], CS# invalid

BCLK

0ns

0ns

t3 WE0#, WE1# low to D[15:0] valid (write cycle) T

MHz

BCLK

t4 RD0#, RD1# low to D[15:0] driven (read cycle) 17 ns

t5 WE0#, WE1# high to D[15:0] invalid (write cycle) 0 ns

t6 D[15:0] valid to WAIT# high (read cycle) 0 ns

t7 RD0#, RD1# high to D[15:0] high impedance (read cycle) 10 ns

WE0#, WE1# low (write cycle) or RD0#, RD1# low (read cycle) to

t8

WAIT# driven low

16 ns

t9 BCLK to WAIT# high 16 ns

t10

t11 WAIT# high to WE0#, WE1#, RD0#, RD1# high 1T

WE0#, WE1# high (write cycle) or RD0#, RD1# high (read cycle) to

WAIT# high impedance

16 ns

BCLK

Note

BCLK may be turned off (held low) between accesses - see Section 13.5, “Turning Off

BCLK Between Accesses” on page 84

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 39

Epson Research and Development Page 33

Vancouver Design Center

7.1.6 Generic #2 Interface Timing

T

BCLK

BCLK

A[16:0]

BHE#

CS#

WE#,RD#

D[15:0]

(write)

D[15:0]

(read)

WAIT#

Hi-Z

Hi-Z

Hi-Z

VALID

t1

t3

VALID

t5

t8

t6

VALID

t9

t11

t2

t4

t7

Hi-Z

t10

Hi-Z

Figure 7-6: Generic #2 Timing

Table 7-6: Generic #2 Timing

Symbol Parameter Min Max Units

f

BCLK

T

BCLK

Bus Clock frequency 50 MHz

Bus Clock period 1/f

BCLK

t1 A[16:0], BHE#, CS# valid to WE#, RD# low 0 ns

t2 WE#, RD# high to A[16:0], BHE#, CS# invalid 0 ns

t3 WE# low to D[15:0] valid (write cycle) T

BCLK

t4 WE# high to D[15:0] invalid (write cycle) 0 ns

t5 RD# low to D[15:0] driven (read cycle) 16 ns

t6 D[15:0] valid to WAIT# high (read cycle) 0 ns

t7 RD# high to D[15:0] high impedance (read cycle) 10 ns

t8 WE#, RD# low to WAIT# driven low 14 ns

t9 BCLK to WAIT# high 10 ns

t10 WE#, RD# high to WAIT# high impedance 11 ns

t11 WAIT# high to WE#, RD# high 1T

BCLK

Note

BCLK may be turned off (held low) between accesses - see Section 13.5, “Turning Off

BCLK Between Accesses” on page 84

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

Page 40

Page 34 Epson Research and Development

Vancouver Design Center

7.2 Clock Input Requirements

Clock Input Waveform

t

PWL

90%

V

V

10%

t

PWH

IH

IL

T

CLKI

t

f

t

r

Figure 7-7: Clock Input Requirements for CLKI

Table 7-7: Clock Input Requirements for CLKI

Symbol Parameter Min Max Units

f

CLKI

T

CLKI

t

PWH

t

PWL

t

f

t

r

Input Clock Frequency (CLKI) 50 MHz

Input Clock period (CLKI) 1/f

CLKI

ns

Input Clock Pulse Width High (CLKI) 8 ns

Input Clock Pulse Width Low (CLKI) 8 ns

Input Clock Fall Time (10% - 90%) 5 ns

Input Clock Rise Time (10% - 90%) 5 ns

Note

When CLKI is > 25MHz the Input Clock Divide bit (REG[02h] bit 4) must be set to 1.

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 41

Epson Research and Development Page 35

Vancouver Design Center

Clock Input Waveform

t

PWL

90%

V

V

10%

t

PWH

IH

IL

T

BCLK

t

f

t

r

Figure 7-8: Clock Input Requirements for BCLK

Table 7-8: Clock Input Requirements for BCLK

Symbol Parameter Min Max Units

f

BCLK

T

BCLK

t

PWH

t

PWL

t

f

t

r

Input Clock Frequency (BCLK) 50 MHz

Input Clock period (BCLK) 1/f

CLKI

Input Clock Pulse Width High (BCLK) 8 ns

Input Clock Pulse Width Low (BCLK) 8 ns

Input Clock Fall Time (10% - 90%) 5 ns

Input Clock Rise Time (10% - 90%) 5 ns

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

Page 42

Page 36 Epson Research and Development

Vancouver Design Center

7.3 Display Interface

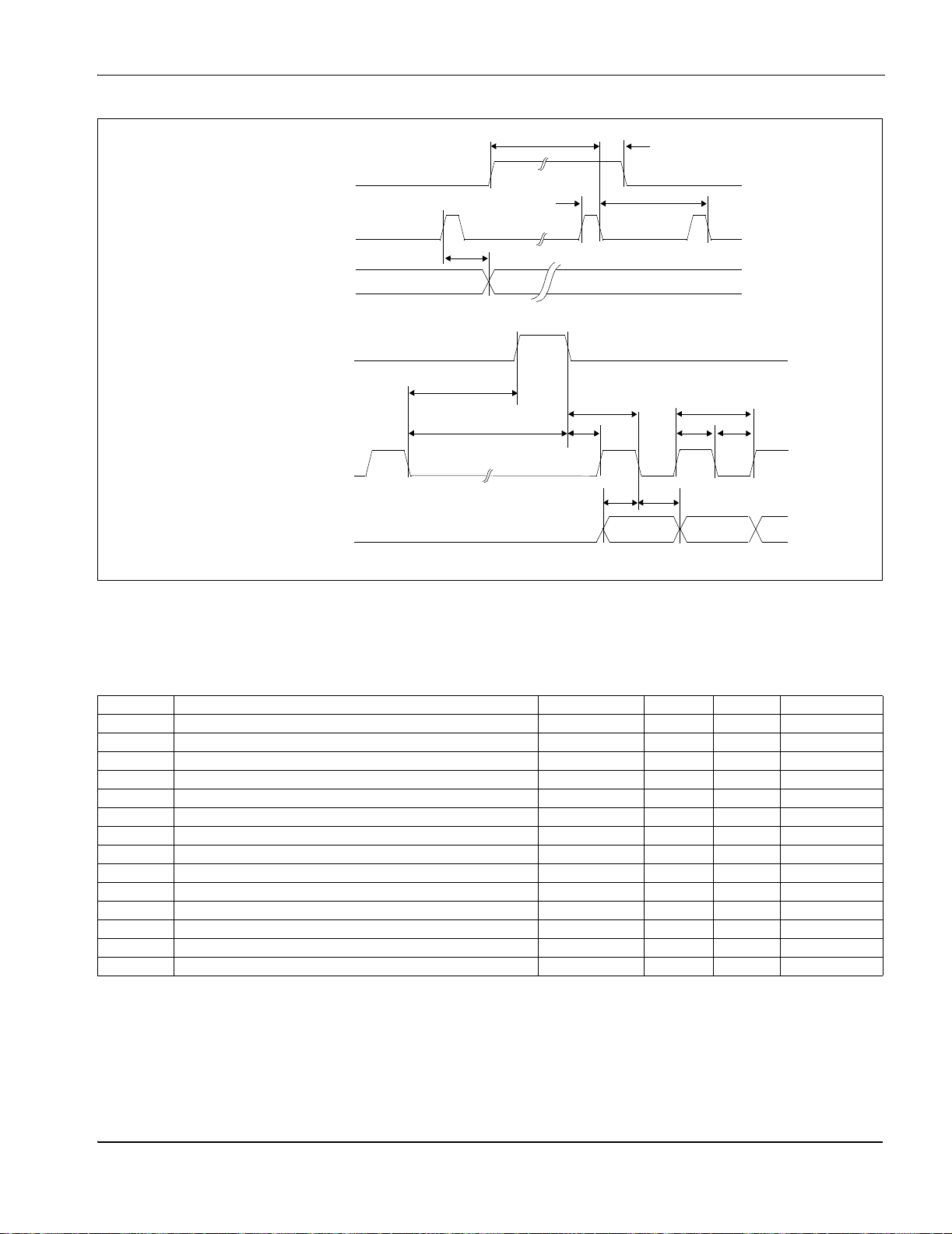

7.3.1 Power On/Reset Timing

RESET#

REG[03h] bits [1:0]

LCDPWR

FPLINE

FPSHIFT

FPDAT

FPFRAME

DRDY

00 11

t1

ACTIVE

t2

Figure 7-9: LCD Panel Power On/Reset Timing

Table 7-9: LCD Panel Power On/Reset Timing

Symbol Parameter Min Typ Max Units

t1

t2

REG[03h] to FPLINE, FPFRAME, FPSHIFT, FPDAT, DRDY

active

FPLINE, FPFRAME, FPSHIFT, FPDAT, DRDY active to

LCDPWR

T

FPFRAME

0Frames

ns

Note

Where T

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

FPFRAME

is the period of FPFRAME and T

is the period of t he pixe l cloc k.

PCLK

Page 43

Epson Research and Development Page 37

Vancouver Design Center

7.3.2 Power Down/Up Timing

LCDPWR Overri d e

(REG[03h] bit 3)

HW Power Save

or

Software Power Save

REG[03h] bits [1:0]

11 00 11 00 11

t1

t2

FP Signals

LCDPWR

Active Inactive Active Inactive Active

t3

t4

t5

t6

t7

Figure 7-10: Power Down/Up Timing

Table 7-10: Power Down/Up Timing

Symbol Parameter Min Typ Max Units

HW Power Save active to FPLINE, FPFRAME, FPSHIFT, FPDAT, DRDY

t1

inactive - LCDPWR Override = 1

HW Power Save inactive to FPLINE, FPFRAME, FPSHIFT, FPDAT, DRDY

t2

active - LCDPWR Override = 1

HW Power Save active to FPLINE, FPFRAME, FPSHIFT, FPDAT, DRDY

t3

inactive - LCDPWR Override = 0

LCDPWR low to FPLINE, FPFRAME, FPSHIFT, FPDAT, DRDY inactive

t4

- LCDPWR Override = 0

HW Power Save inactive to FPLINE, FPFRAME, FPSHIFT, FPDAT, DRDY,

t5

LCDPWR active - LCDPWR Override = 0

t6 LCDPWR Override active (1) to LCDPWR inactive 1 Frame

t7 LCDPWR Override inactive (1) to LCDPWR active 1 Frame

127 Frame

0Frame

1Frame

1Frame

1Frame

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

Page 44

Page 38 Epson Research and Development

Vancouver Design Center

7.3.3 Single Monochrome 4-Bit Panel Timing

FPFRAME

FPLINE

DRDY (MOD)

FPDAT[7:4]]

LINE1 LINE2 LINE3 LINE4 LINE239 LINE240

FPLINE

DRDY (MOD)

FPSHIFT

FPDAT7

FPDAT6

FPDAT5

FPDAT4

* Diagram drawn with 2 FPLINE vertical blank per iod

Example timing for a 320x240 panel

1-1 1-5

1-2 1-6 1-318

1-3

1-7

1-4 1-8

For this timing diagram Mask FPSHIFT, REG[01h] bit 3, is set to 1

VDP

HDP HNDP

VNDP

1-317

1-319

1-320

LINE1 LINE2

Figure 7-11: Single Monochrome 4-Bit Panel Timing

VDP = Vertical Display Period = (REG[06h] bits 1-0, REG[05h] bits 7-0) + 1 Lines

VNDP = Vertical Non-Display Period = REG[0Ah] bits 5-0 Lines

HDP = Horizontal Display Period = ((REG[04h] bits 6-0) + 1) x 8Ts

HNDP = Horizontal Non-Display Period = (REG[08h] + 4) x 8Ts

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 45

Epson Research and Development Page 39

Vancouver Design Center

Sync Timing

Frame Pulse

Line Pulse

t5

DRDY (MOD)

Data Timing

Line Pulse

t6

Shift Pulse

FPDAT[7:4]

Note: For this timing diagram Mask FPSHIFT, REG[01h] bit 3, is set to 1

t1

t4

t7

t14 t10t11

t2

t3

t8 t9

t12 t13

12

Figure 7-12: Single Monochrome 4-Bit Panel A.C. Timing

Table 7-11: Single Monochrome 4-Bit Panel A.C. Timing

Symbol Parameter Min Typ Max Units

t1 Frame Pulse setup to Line Pulse falling edge note 2 (note 1)

t2 Frame Pulse hold from Line Pulse falling edge 9 Ts

t3 Line Pulse period note 3

t4 Line Pulse pulse width 9 Ts

t5 MOD delay from Line Pu lse rising edge 1 Ts

t6 Shift Pulse falling edge to Line Pulse rising edge note 4

t7 Shift Pulse falling edge to Line Pulse falling edge note 5

t8 Line Pulse falling edge to Shift Pulse falling edge t14 + 2 Ts

t9 Shift Pulse period 4 Ts

t10 Shift Pulse pulse width low 2 Ts

t11 Shift Pulse pulse width high 2 Ts

t12 FPDAT[7:4] setup to Shift Pulse falling edge 2 Ts

t13 FPDAT[7:4] hold to Shift Pulse falling edge 2 Ts

t14 Line Pulse falling edge to Shift Pulse rising edge 23 Ts

1. Ts = pixel clock period

2. t1

3. t3

4. t6

5. t7

= t3

min

= [((REG[04h] bits 6-0)+1) x 8 + ((REG[08h] bits 4-0) + 4) x 8]Ts

min

= [(REG[08h] bits 4-0) x 8 + 2]Ts

min

= [(REG[08h] bits 4-0) x 8 + 11]Ts

min

min

- 9Ts

Hardware Functional Specification S1D13705

Issue Date: 02/02/01 X27A-A-001-10

Page 46

Page 40 Epson Research and Development

Vancouver Design Center

7.3.4 Single Monochrome 8-Bit Panel Timing

FPFRAME

FPLINE

DRDY (MOD)

FPDAT[7:0]

FPLINE

DRDY (MOD)

FPSHIFT

FPDAT7

FPDAT6

FPDAT5

FPDAT4

FPDAT3

FPDAT2

FPDAT1

FPDAT0

VDP

LINE1 LINE2 LINE3 LINE4 LINE479 LINE480

HDP

1-1 1-9

1-2 1-10 1-634

1-3

1-11

1-4 1-12

1-5 1-13

1-6 1-14

1-7 1-15 1-639

1-8 1-16

VNDP

1-633

1-635

1-636

1-637

1-638

1-640

LINE1 LINE2

HNDP

* Diagram drawn with 2 FPLINE vertical blank period

Example timing for a 640x480 panel

For this timing diagram Mask FPSHIFT, REG[01h] bit 3, is set to 1

Figure 7-13: Single Monochrome 8-Bit Panel Timing

VDP = Vertical Display Period = (REG[06h] bits 1-0, REG[05h] bits 7-0) + 1 Lines

VNDP = Vertical Non-Display Period = REG[0Ah] bits 5-0 Lines

HDP = Horizontal Display Period = ((REG[04h] bits 6-0) + 1) x 8Ts

HNDP = Horizontal Non-Display Period = (REG[08h] + 4) x 8Ts

S1D13705 Hardware Functional Specification

X27A-A-001-10 Issue Date: 02/02/01

Page 47

Epson Research and Development Page 41

Vancouver Design Center

Sync Timing

Frame Pulse

Line Pulse

t5

DRDY (MOD)

Data Timing

Line Pulse

t6

Shift Pulse

FPDAT[7:0]

Note: For this timing diagram Mask FPSHIFT, REG[01h] bit 3, is set to 1

t1

t7

t2

t4

t8 t9

t14

t3

t12 t13

12

t10t11

Figure 7-14: Single Monochrome 8-Bit Panel A.C. Timing

Table 7-12: Single Monochrome 8-Bit Panel A.C. Timing

Symbol Parameter Min Typ Max Units

t1 Frame Pulse setup to Line Pulse falling edge note 2 (note 1)

t2 Frame Pulse hold from Line Pulse falling edge 9 Ts

t3 Line Pulse period note 3

t4 Line Pulse pulse width 9 Ts

t5 MOD delay from Line Pulse rising edge 1 Ts

t6 Shift Pulse falling edge to Line Pulse rising edge note 4

t7 Shift Pulse falling edge to Line Pulse falling edge note 5

t8 Line Pulse falling edge to Shift Pulse falling edge t14 + 4 Ts

t9 Shift Pulse period 8 Ts

t10 Shift Pulse pulse width low 4 Ts

t11 Shift Pulse pulse width high 4 Ts

t12 FPDAT[7:0] setup to Shift Pulse falling edge 4 Ts