Page 1

查询S1D13505供应商

Page 2

Epson Research and Development

Page 3

Vancouver Design Center

TECHNICAL MANUAL S1D13505

Issue Date: 01/04/18 X23A-Q-001-12

Customer Support Information

Comprehensive Support Tools

Seiko Epson Corp. provides to the system designer and computer OEM manufacturer a complete set

of resources and tools for the development of graphics systems.

Evaluation / Demonstration Board

• Assembled and fully tested graphics evaluation board with installation guide and schematics.

• To borrow an evaluation board, pleas e co ntact yo ur local Seiko Eps on Corp . s ales representative.

Chip Documentation

• Technical manual includes Data Sheet, Application Notes, and Programmer’s Reference.

Software

• OEM Utilities.

• User Utilities.

• Evaluation Software.

• To obtain these programs, contact Application Engineering Support.

Application Engineering Support

Engineering and Sales Support is provided by:

Japan

Seiko Epson Corporation

Electronic Devices Marketing Division

421-8, Hino, Hino-shi

Tokyo 191-8501, Japan

Tel: 042-587-5812

Fax: 042-587-5564

http://www.epson.co.jp

Hong Kong

Epson Hong Kong Ltd.

20/F., Harbour Centre

25 Harbour Road

Wanchai, Hong Kong

Tel: 2585-4600

Fax: 2827-4346

Taiwan

Epson Taiwan Technology

& Trading Ltd.

10F, No. 287

Nanking East Road

Sec. 3, Taipei, Taiwan

Tel: 02-2717-7360

Fax: 02-2712-9164

Singapore

Epson Singapore Pte., Ltd.

No. 1

Temasek Avenue #36-00

Millenia Tower

Singapore, 039192

Tel: 337-7911

Fax: 334-2716

Europe

Epson Europe Electronics GmbH

Riesstrasse 15

80992 Munich, Germany

Tel: 089-14005-0

Fax: 089-14005-110

North America

Epson Electronics America, Inc.

150 River Oaks Parkway

San Jose, CA 95134, USA

Tel: (408) 922-0200

Fax: (408) 922-0238

http://www.eea.epson.com

Page 3

Page 4

Epson Research and Development

Vancouver Design Center

S1D13505 TECHNICAL MANUAL

X23A-Q-001-12 Issue Date: 01/04/18

THIS PAGE LEFT BLANK

Page 4

X23A-C-002-15 1

GRAPHICS

S1D13505

ENERGY

SAVING

EPSON

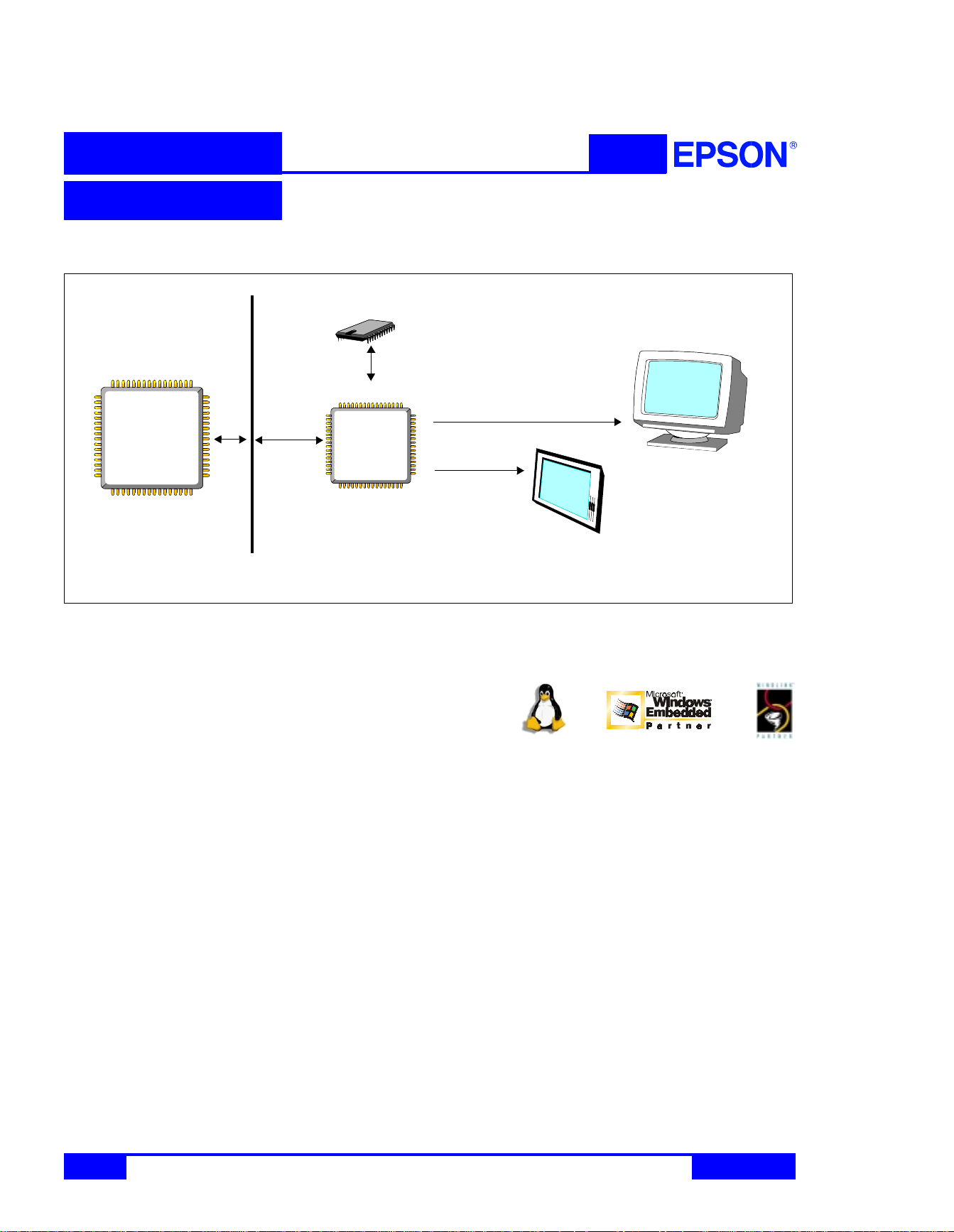

S1D13505 EMBEDDED RAMDAC LCD/CRT CONTROLLER October 2001

■

DESCRIPTION

The S1D13505 is a color/monochrome LCD/CRT graphics controller interfacing to a wide range of CPUs and display

devices. The S1D13505 architecture is designed to meet the low cost, low power requirements of the embedded

markets, such as Mobile Communications, Hand-Held PCs, and Office Automation.

The S1D13505 supports multiple CPUs, all LCD panel types, CRT, and additionally provides a number of

differentiating features. Products requiring a “Portrait” mode display can take advantage of the SwivelView feature.

Simultaneous, Virtual and Split Screen Display are just some of the display modes supported, while the Hardware

Cursor, Ink Lay er, and the Memory Enhancement Registers offer substantial performance benefits. These features,

combined with the S1D13505’s Operating System independence, make it an ideal display solution for a wide variety

of applications.

■

FEATURES

Memory Interface

•

16-bit EDO-DRAM or FPM-DRAM interface.

•

Memory size options:

512K bytes using one 256K×16 device.

2M bytes using one 1M×16 device.

•

Addressable as a single linear address space.

CPU Interface

•

Supports the following interfaces:

Hitachi SH-4.

Hitachi SH-3.

Motorola M68K.

Philips MIPS PR31500/PR31700.

Toshiba MIPS TX3912.

Motorola Power PC MPC821.

NEC MIPS VR4102/VR4111.

Epson E0C33.

PC Card (PCMCIA).

StrongARM (PC Card).

ISA bus.

MPU bus interface with programmable READY.

•

CPU write buffer.

Display Support

•

4/8-bit monochrome passive LCD interface.

•

4/8/16-bit color passive LCD interface.

•

Single-panel, single-drive displays.

•

Dual-panel, dual-drive displays.

•

Direct support for 9/12-bit TF T/D-TFD; 18-bit T FT/D-TFD

is supported up to 64K color depth (16-bit data).

•

Embedded RAMDAC with direct analog CRT drive.

•

Simultaneous dis play of CRT and passiv e or T FT/D -TF D

panels.

•

Maximum resolution of 800x600 pixels at a color

depth of 16 bpp.

Display Modes

•

1/2/4/8/16 bit-per-pixel (bpp) support on LCD/CRT.

•

Up to 16 shades of gray using FRM on monochrome

passive LCD panels.

•

Up to 4096 colors on passive LCD panels.

•

Up to 64K colors on active matrix TFT/D-TFD LCD

panels and CRT in 16 bpp modes.

•

Split Screen Display: allows two different images to be

simultaneously viewed on the same display.

•

Virtual Display Support: displays images larger than the

display size through the use of panning.

•

Double Buffering/multi-pages: provides smooth

animation and instantaneous screen update.

•

SwivelView: direct hardware 90° rotation of

display image for portrait mode display.

•

Acceleration of screen updates by allocating full

display memory bandwidth to CPU.

•

Hardware 64x64 pixel 2-bit cursor or full screen

2-bit ink layer.

Clock Source

•

Single clock input for both pixel and memory clocks.

•

Memory clock can be input clock or (input clock/2),

providing flexibility to use CPU bus clock as input.

•

Pixel clock can be memory clock or (memory clock/2) or

(memory clock/3) or (memory clock/4).

Power Down Mod es

•

Software power save mode.

•

LCD power sequencing.

General Purpose IO Pins

•

Up to 3 General Purpose IO pins are available.

Operating Voltage

•

2.7 volts to 5.5 volts.

Package

•

128-pin QFP15 surface mount package.

Page 5

X23A-C-002-15 2

GRAPHICS

S1D13505

■

SYSTEM BLOCK DIAGRAM

S1D13505

Flat Panel

Digital Out

CPU

CRT

EDO-DRAM

FPM-DRAM

Analog Out

Data and

Control Signals

CONTACT YOUR SALES REPRESENTATIVE FOR THESE COMPREHENSIVE DESIGN TOOLS

• S1D13505 Technical

Manual

• Linux Console Driver

• S5U13505 Evaluation Boards • Windows

CE Display Driver

• CPU Independent Software

Utilities

•VXWorks

TornadoTM Display

Driver

Copyright © 2001 Epson Research and Development, Inc. All Rights Reserved.

Information in this document is subject t o change without not ice . You may dow n load and use this docum ent, bu t only for you r own use in eva luati ng Sei ko Epson/

EPSON products. You may not modify the document. Epson Research and Devel opment, Inc. disclaims any repr esentati on that the contents of this document are

accurate or current. The Programs/Technologies described in this document may contain material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. Microsoft, Windows, and the Windows Embedded Partner Logo are registered trademarks of Microsoft Corporation. All other trademarks are the property of their respective owners.

Japan

Seiko Epson Corporation

Electronic Devices Marketing Division

421-8, Hino, Hino-shi

Tokyo 191-8501, Japan

Tel: 042-587-5812

Fax: 042-587-5564

http://www.epson.co.jp/

Hong Kong

Epson Hong Kong Ltd.

20/F., Harbour Centre

25 Harbour Road

Wanchai, Hong Kong

Tel: 2585-4600

Fax: 2827-4346

http://www.epson.com.hk/

Taiwan

Epson Taiwan Technology & Trading Ltd.

10F, No. 287

Nanking East Road

Sec. 3, Taipei, Taiwan

Tel: 02-2717-7360

Fax: 02-2712-9164

http://www.epson.com.tw/

Singapore

Epson Singapore Pte., Ltd.

No. 1

Temasek Avenue #36-00

Millenia Tower

Singapore, 039192

Tel: 337-7911

Fax: 334-2716

http://www.epson.com.sg/

Europe

Epson Europe Electronics GmbH

Riesstrasse 15

80992 Munich, Germany

Tel: 089-14005-0

Fax: 089-14005-110

http://www.epson-electronics.de/

North Amer ica

Epson Electronics America, Inc.

150 River Oaks Parkway

San Jose, CA 95134, USA

Tel: (408) 922-0200

Fax: (408) 922-0238

http://www.eea.epson.com/

Page 6

S1D13505 Embedded RAMDAC LCD/CRT Controller

Hardware Functional Specification

Document Number: X23A-A-001-14

Copyright © 1998, 2001 Epson Research and Development, Inc. All Rights Reserved.

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in

evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any

representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain

material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. All other trademarks are the property of their respective owners.

Page 7

Page 2

Epson Research and Development

Vancouver Design Center

S1D13505 Hardware Functional Specification

X23A-A-001-14 Issue Date: 01/02/02

THIS PAGE LEFT BLANK

Page 8

Epson Research and Development

Page 3

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

Table of Contents

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.1 Scope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

1.2 Overview Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.1 Memory Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.2 CPU Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.3 Display Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.4 Display Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.5 Display Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.6 Clock Source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.7 Miscellaneous . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3 Typical System Implementation Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

4 Internal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

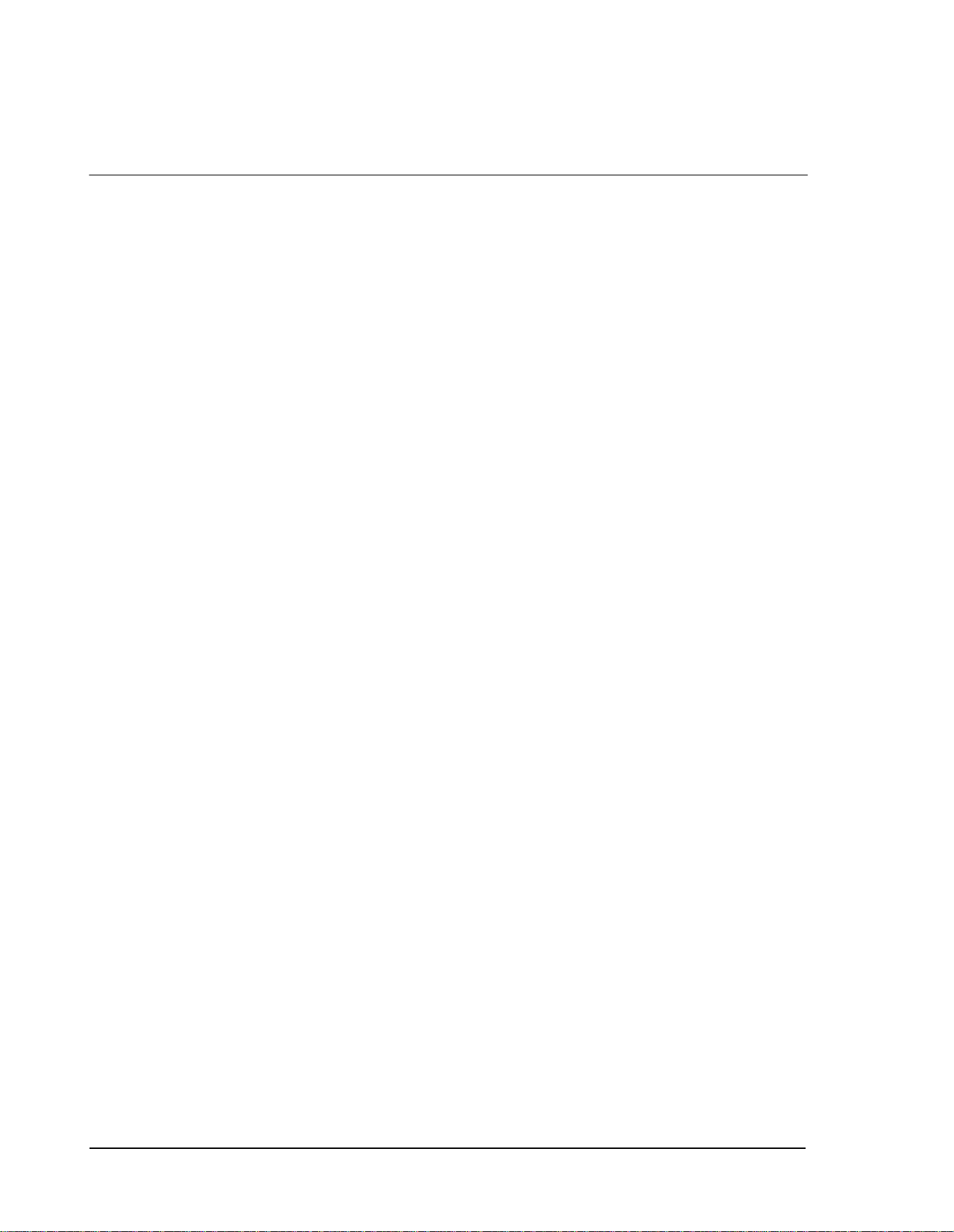

4.1 Block Diagram Showing Datapaths . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.2 Block Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.2.1 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.2.2 Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.2.3 CPU R/W . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.2.4 Memory Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.2.5 Display FIFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.2.6 Cursor FIFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.2.7 Look-Up Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.2.8 CRTC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.2.9 LCD Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.2.10 DAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.2.11 Power Save . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.2.12 Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

5 Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

5.1 Pinout Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

5.2 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5.2.1 Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5.2.2 Memory Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

5.2.3 LCD Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

5.2.4 CRT Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

5.2.5 Miscellaneous . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

5.3 Summary of Configuration Options . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5.4 Multiple Function Pin Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

5.5 CRT Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

6 D.C. Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Page 9

Page 4

Epson Research and Development

Vancouver Design Center

S1D13505 Hardware Functional Specification

X23A-A-001-14 Issue Date: 01/02/02

7 A.C. Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

7.1 CPU Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

7.1.1 SH-4 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

7.1.2 SH-3 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

7.1.3 MC68K Bus 1 Interface Timing (e.g. MC68000) . . . . . . . . . . . . . . . . . . . . . . . .46

7.1.4 MC68K Bus 2 Interface Timing (e.g. MC68030) . . . . . . . . . . . . . . . . . . . . . . . .48

7.1.5 PC Card Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

7.1.6 Generic Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

7.1.7 MIPS/ISA Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

7.1.8 Philips Interface Timing (e.g. PR31500/PR31700) . . . . . . . . . . . . . . . . . . . . . . .56

7.1.9 Toshiba Interface Timing (e.g. TX3912) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

7.1.10 Power PC Interface Timing (e.g. MPC8xx, MC68040, Coldfire) . . . . . . . . . . . . . . . .60

7.2 Clock Input Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

7.3 Memory Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

7.3.1 EDO-DRAM Read/Write/Read-Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . .63

7.3.2 EDO-DRAM CAS Before RAS Refresh Timing . . . . . . . . . . . . . . . . . . . . . . . .66

7.3.3 EDO-DRAM Self-Refresh Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

7.3.4 FPM-DRAM Read/Write/Read-Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . .69

7.3.5 FPM-DRAM CAS Before RAS Refresh Timing . . . . . . . . . . . . . . . . . . . . . . . .72

7.3.6 FPM-DRAM Self-Refresh Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

7.4 Power Sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

7.4.1 LCD Power Sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74

7.4.2 Power Save Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

7.5 Display Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

7.5.1 4-Bit Single Monochrome Passive LCD Panel Timing . . . . . . . . . . . . . . . . . . . . .76

7.5.2 8-Bit Single Monochrome Passive LCD Panel Timing . . . . . . . . . . . . . . . . . . . . .78

7.5.3 4-Bit Single Color Passive LCD Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . .80

7.5.4 8-Bit Single Color Passive LCD Panel Timing (Format 1) . . . . . . . . . . . . . . . . . . .82

7.5.5 8-Bit Single Color Passive LCD Panel Timing (Format 2) . . . . . . . . . . . . . . . . . . .84

7.5.6 16-Bit Single Color Passive LCD Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . .86

7.5.7 8-Bit Dual Monochrome Passive LCD Panel Timing . . . . . . . . . . . . . . . . . . . . . .88

7.5.8 8-Bit Dual Color Passive LCD Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . .90

7.5.9 16-Bit Dual Color Passive LCD Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . .92

7.5.10 16-Bit TFT/D-TFD Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .94

7.5.11 CRT Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .97

8 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

8.1 Register Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

8.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

8.2.1 Revision Code Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

8.2.2 Memory Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

8.2.3 Panel/Monitor Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

8.2.4 Display Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Page 10

Epson Research and Development

Page 5

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

8.2.5 Clock Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

8.2.6 Power Save Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

8.2.7 Miscellaneous Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

8.2.8 Look-Up Table Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

8.2.9 Ink/Cursor Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

9 Display Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122

9.1 Image Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

9.2 Ink/Cursor Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

9.3 Half Frame Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

10 Display Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .124

10.1 Display Mode Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . .124

10.2 Image Manipulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

11 Look-Up Table Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

11.1 Monochrome Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

11.2 Color Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .129

12 Ink/Cursor Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

12.1 Ink/Cursor Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

12.2 Ink/Cursor Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133

12.3 Ink/Cursor Image Manipulation . . . . . . . . . . . . . . . . . . . . . . . . . . .134

12.3.1 Ink Image . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

12.3.2 Cursor Image . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

13 SwivelView™ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .135

13.1 Concept . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .135

13.2 Image Manipulation in SwivelView . . . . . . . . . . . . . . . . . . . . . . . . . .136

13.3 Physical Memory Requirement . . . . . . . . . . . . . . . . . . . . . . . . . . .137

13.4 Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .138

14 Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .139

14.1 Maximum MCLK: PCLK Ratios . . . . . . . . . . . . . . . . . . . . . . . . . . .139

14.2 Frame Rate Calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .141

14.3 Bandwidth Calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .143

15 Power Save Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

16 Mechanical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .148

Page 11

Page 6

Epson Research and Development

Vancouver Design Center

S1D13505 Hardware Functional Specification

X23A-A-001-14 Issue Date: 01/02/02

THIS PAGE LEFT BLANK

Page 12

Epson Research and Development

Page 7

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

List of Tables

Table 5-1: Host Interface Pin Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 5-2: Memory Interface Pin Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 5-2: LCD Interface Pin Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 5-3: CRT Interface Pin Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 5-4: Miscellaneous Interface Pin Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 5-5: Summary of Power On/Reset Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 5-6: CPU Interface Pin Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 5-7: Memory Interface Pin Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 5-8: LCD Interface Pin Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 6-1: Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 6-2: Recommended Operating Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 6-3: Electrical Characteristics for VDD = 5.0V typical . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 6-4: Electrical Characteristics for VDD = 3.3V typical . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 6-5: Electrical Characteristics for VDD = 3.0V typical . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 7-1: SH-4 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 7-2: SH-3 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 7-3: MC68000 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 7-4: MC68030 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 7-5: PC Card Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 7-6: Generic Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 7-7: MIPS/ISA Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 7-8: Philips Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 7-9: Clock Input Requirements for BUSCLK using Philips local bus. . . . . . . . . . . . . . . . . . . 57

Table 7-10: Toshiba Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 7-11: Clock Input Requirements for BUSCLK using Toshiba local bus . . . . . . . . . . . . . . . . . . 59

Table 7-12: Power PC Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 7-13: Clock Input Requirements for CLKI divided down internally (MCLK = CLKI/2) . . . . . . . . . 62

Table 7-14: Clock Input Requirements for CLKI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 7-15: EDO-DRAM Read/Write/Read-Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 7-16: EDO-DRAM CAS Before RAS Refresh Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 7-17: EDO-DRAM Self-Refresh Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 7-18: FPM-DRAM Read/Write/Read-Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Table 7-19: FPM-DRAM CAS Before RAS Refresh Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 7-20: FPM-DRAM CBR Self-Refresh Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Table 7-21: LCD Panel Power Off/ Power On. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Table 7-22: Power Save Status and Local Bus Memory Access Relative to Power Save Mode . . . . . . . . . 75

Table 7-23: 4-Bit Single Monochrome Passive LCD Panel A.C. Timing. . . . . . . . . . . . . . . . . . . . . 77

Table 7-24: 8-Bit Single Monochrome Passive LCD Panel A.C. Timing. . . . . . . . . . . . . . . . . . . . . 79

Table 7-25: 4-Bit Single Color Passive LCD Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . 81

Table 7-26: 8-Bit Single Color Passive LCD Panel A.C. Timing (Format 1) . . . . . . . . . . . . . . . . . . . 83

Page 13

Page 8

Epson Research and Development

Vancouver Design Center

S1D13505 Hardware Functional Specification

X23A-A-001-14 Issue Date: 01/02/02

Table 7-27: 8-Bit Single Color Passive LCD Panel A.C. Timing (Format 2) . . . . . . . . . . . . . . . . . . .85

Table 7-28: 16-Bit Single Color Passive LCD Panel A.C. Timing. . . . . . . . . . . . . . . . . . . . . . . . .87

Table 7-29: 8-Bit Dual Monochrome Passive LCD Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . .89

Table 7-30: 8-Bit Dual Color Passive LCD Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . .91

Table 7-31: 16-Bit Dual Color Passive LCD Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . .93

Table 7-32: TFT/D-TFD A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

Table 8-1: S1D13505 Addressing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

Table 8-2: DRAM Refresh Rate Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Table 8-3: Panel Data Width Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Table 8-4: FPLINE Polarity Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 8-5: FPFRAME Polarity Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Table 8-6: Simultaneous Display Option Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Table 8-7: Bit-per-pixel Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Table 8-8: Pixel Panning Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Table 8-9: PCLK Divide Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Table 8-10: Suspend Refresh Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Table 8-11: MA/GPIO Pin Functionality. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Table 8-12: Minimum Memory Timing Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Table 8-13: RAS#-to-CAS# Delay Timing Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Table 8-14: RAS Precharge Timing Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Table 8-15: Optimal NRC, NRP, and NRCD values at maximum MCLK frequency . . . . . . . . . . . . . . 116

Table 8-16: Minimum Memory Timing Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Table 8-17: Ink/Cursor Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 8-18: Ink/Cursor Start Address Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Table 8-19: Recommended Alternate FRM Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Table 9-1: S1D13505 Addressing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Table 12-1: Ink/Cursor Start Address Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Table 12-2: Ink/Cursor Color Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Table 13-2 Minimum DRAM Size Required for SwivelView. . . . . . . . . . . . . . . . . . . . . . . . . . 138

Table 14-1: Maximum PCLK Frequency with EDO-DRAM . . . . . . . . . . . . . . . . . . . . . . . . . . 139

Table 14-2: Maximum PCLK Frequency with FPM-DRAM . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Table 14-3: Example Frame Rates with Ink Disabled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Table 14-4: Number of MCLKs required for various memory access . . . . . . . . . . . . . . . . . . . . . . 143

Table 14-5: Total # MCLKs taken for Display refresh. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

Table 14-6: Theoretical Maximum Bandwidth M byte/sec, Cursor/Ink disabled . . . . . . . . . . . . . . . . 145

Table 15-1: Power Save Mode Function Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Table 15-2: Pin States in Power-save Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Page 14

Epson Research and Development

Page 9

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

List of Figures

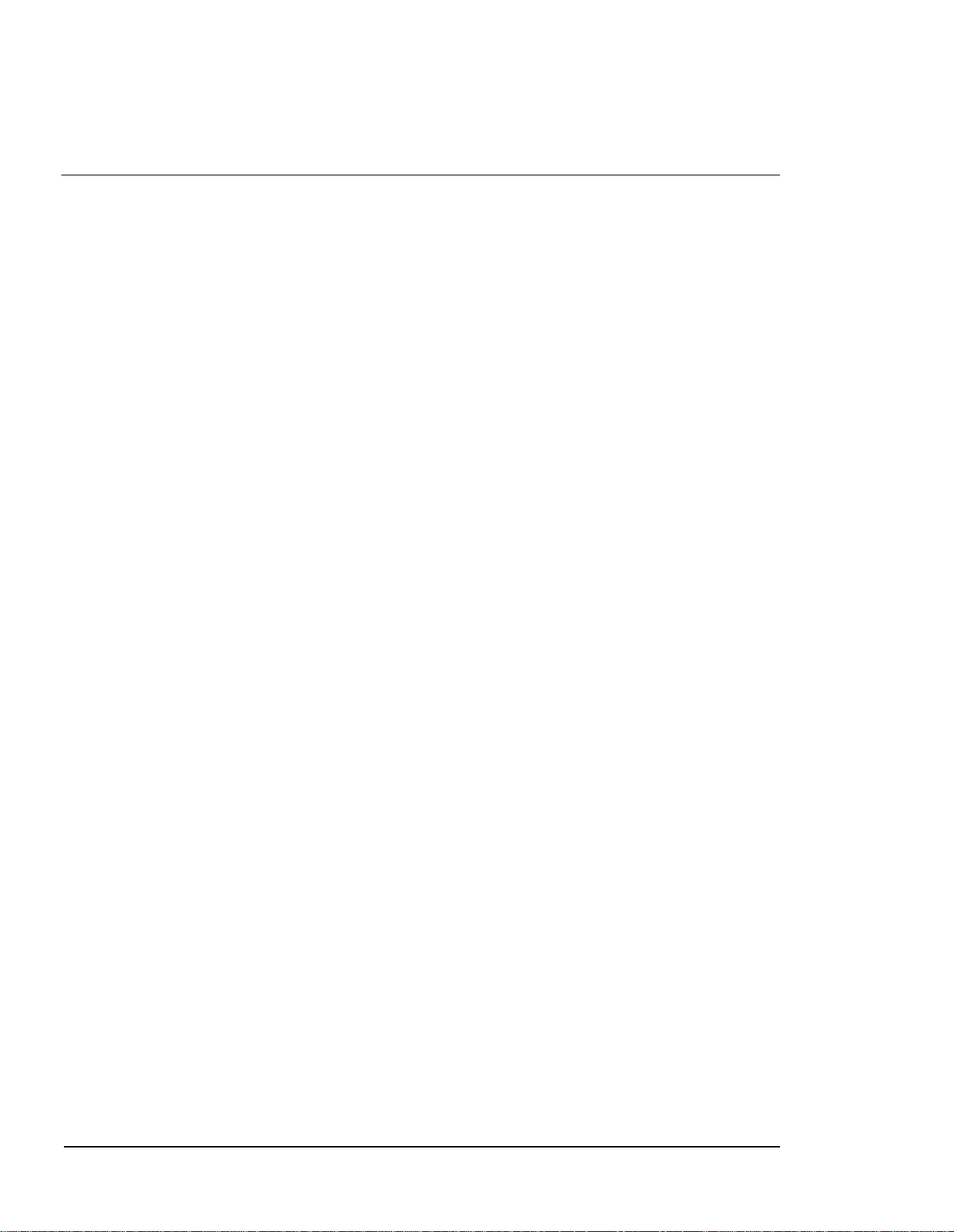

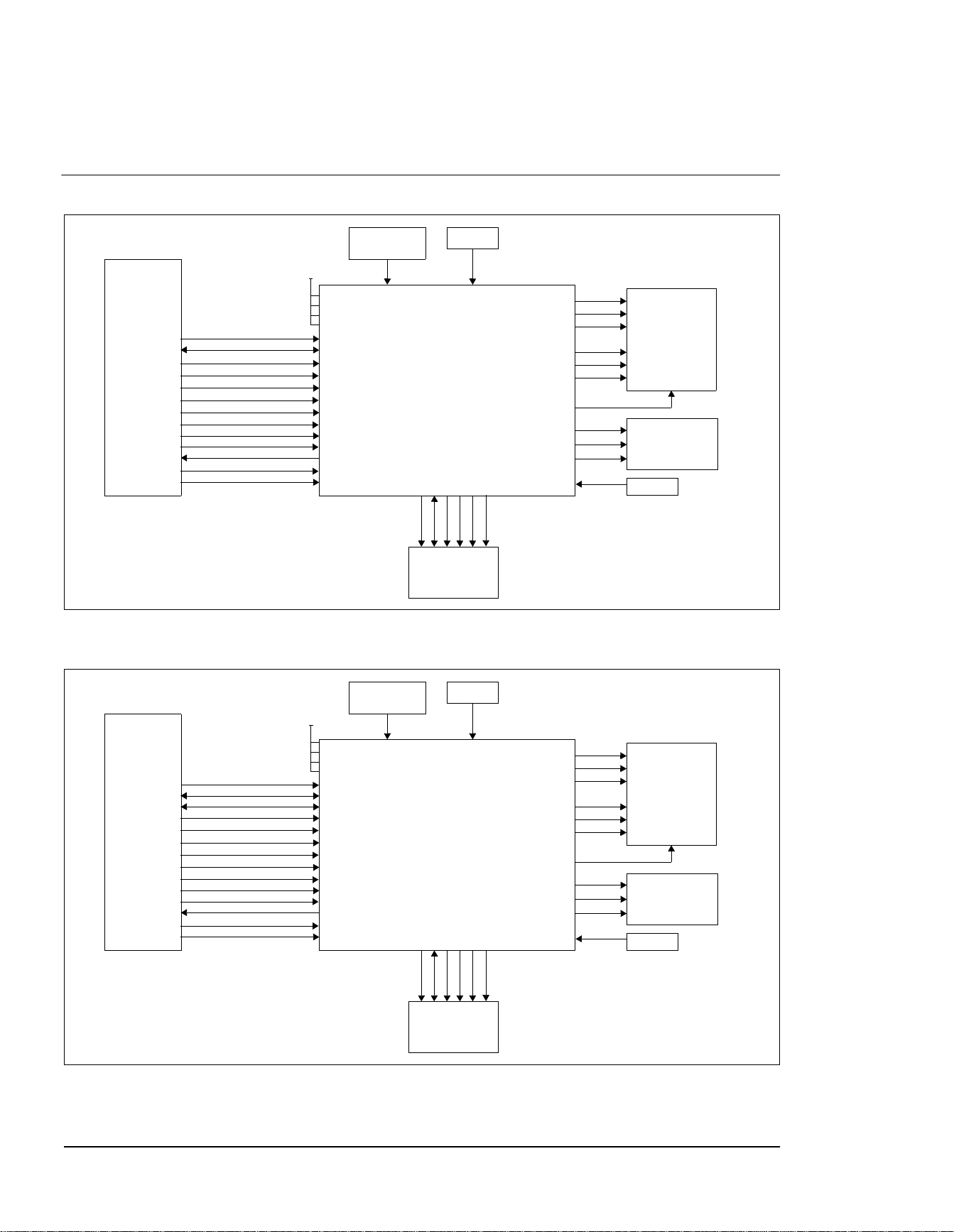

Figure 3-1: Typical System Diagram (SH-4 Bus) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 3-2: Typical System Diagram (SH-3 Bus) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

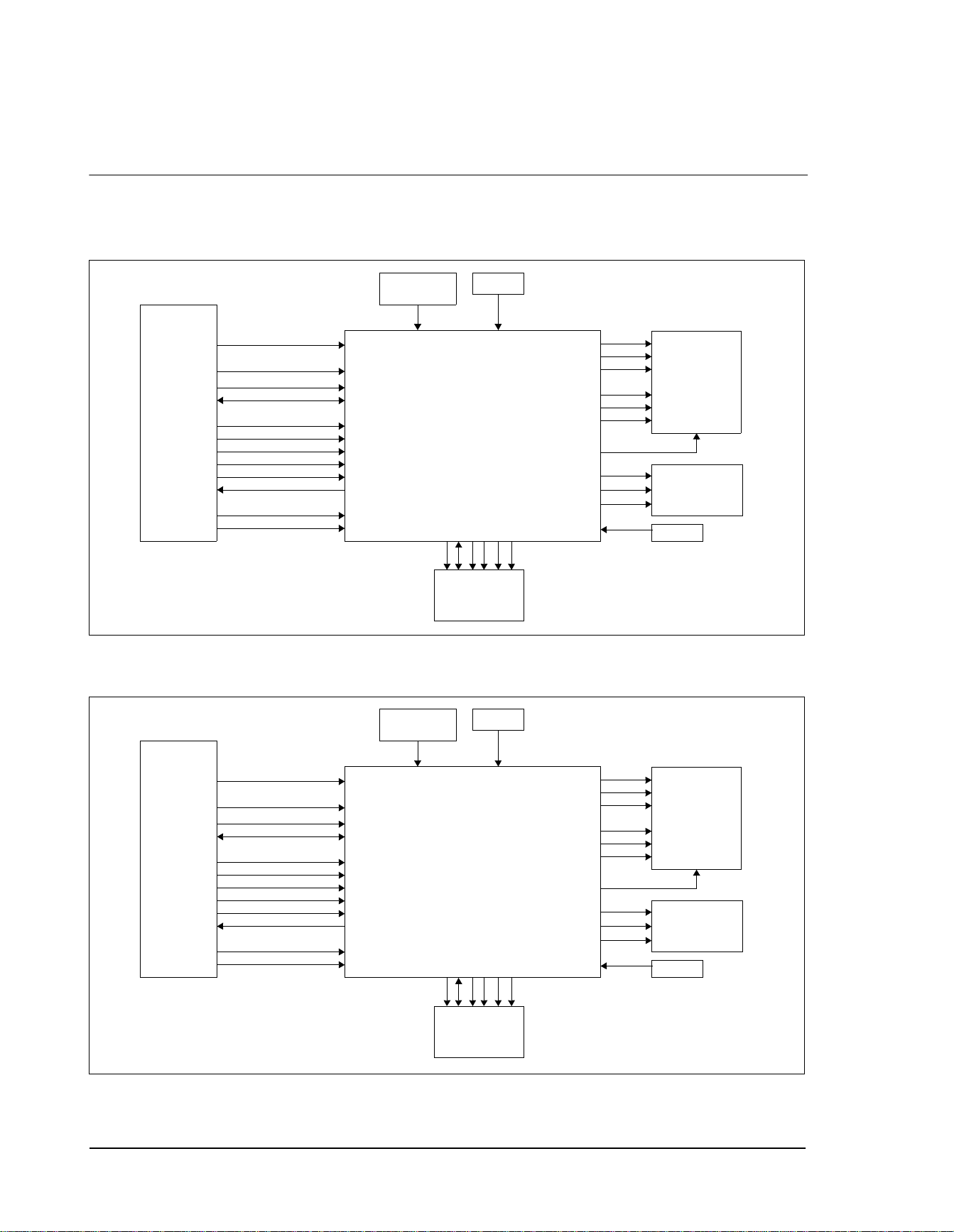

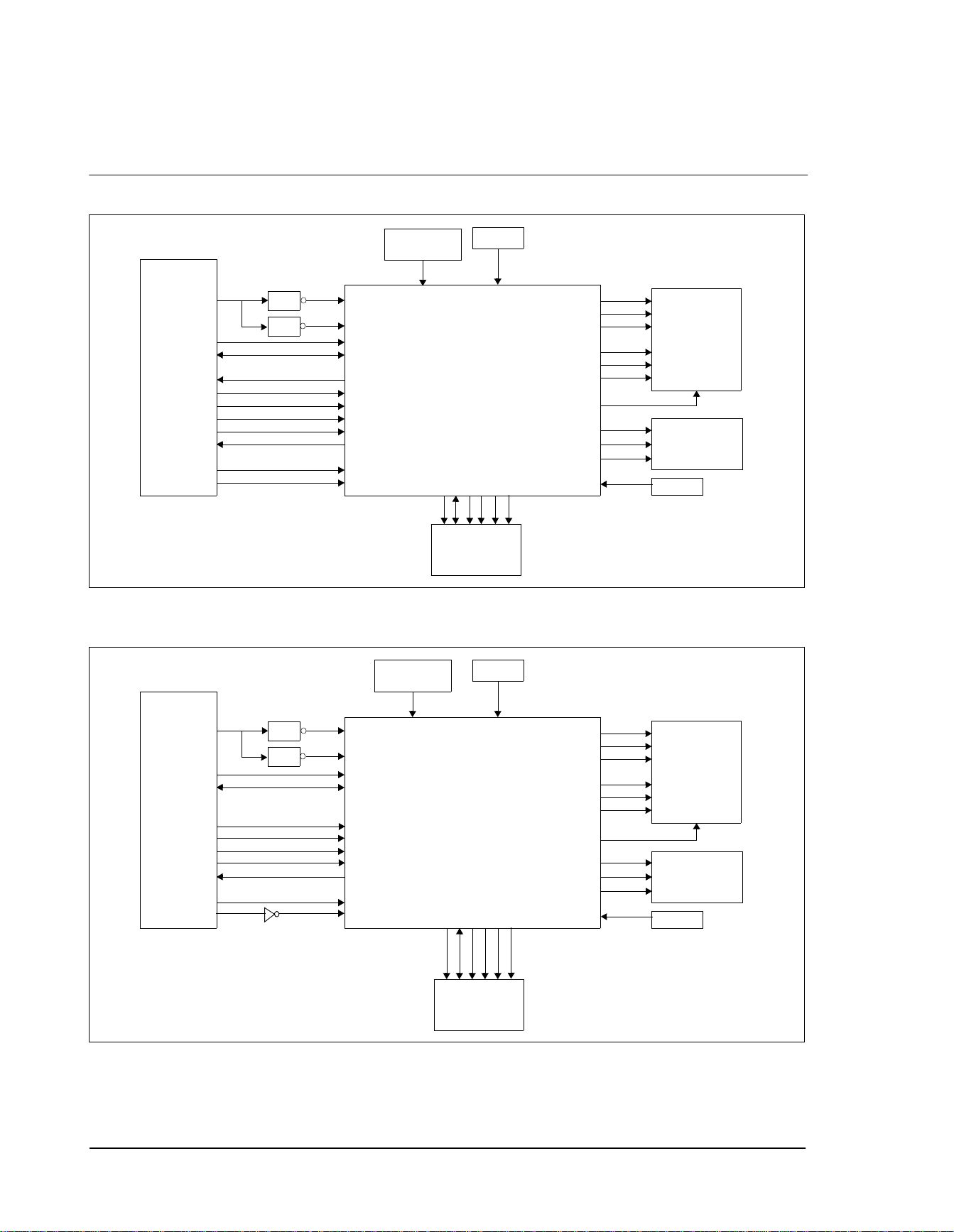

Figure 3-3: Typical System Diagram (MC68K Bus 1, 16-Bit 68000) . . . . . . . . . . . . . . . . . . . . . 16

Figure 3-4: Typical System Diagram (MC68K Bus 2, 32-Bit 68030) . . . . . . . . . . . . . . . . . . . . . 16

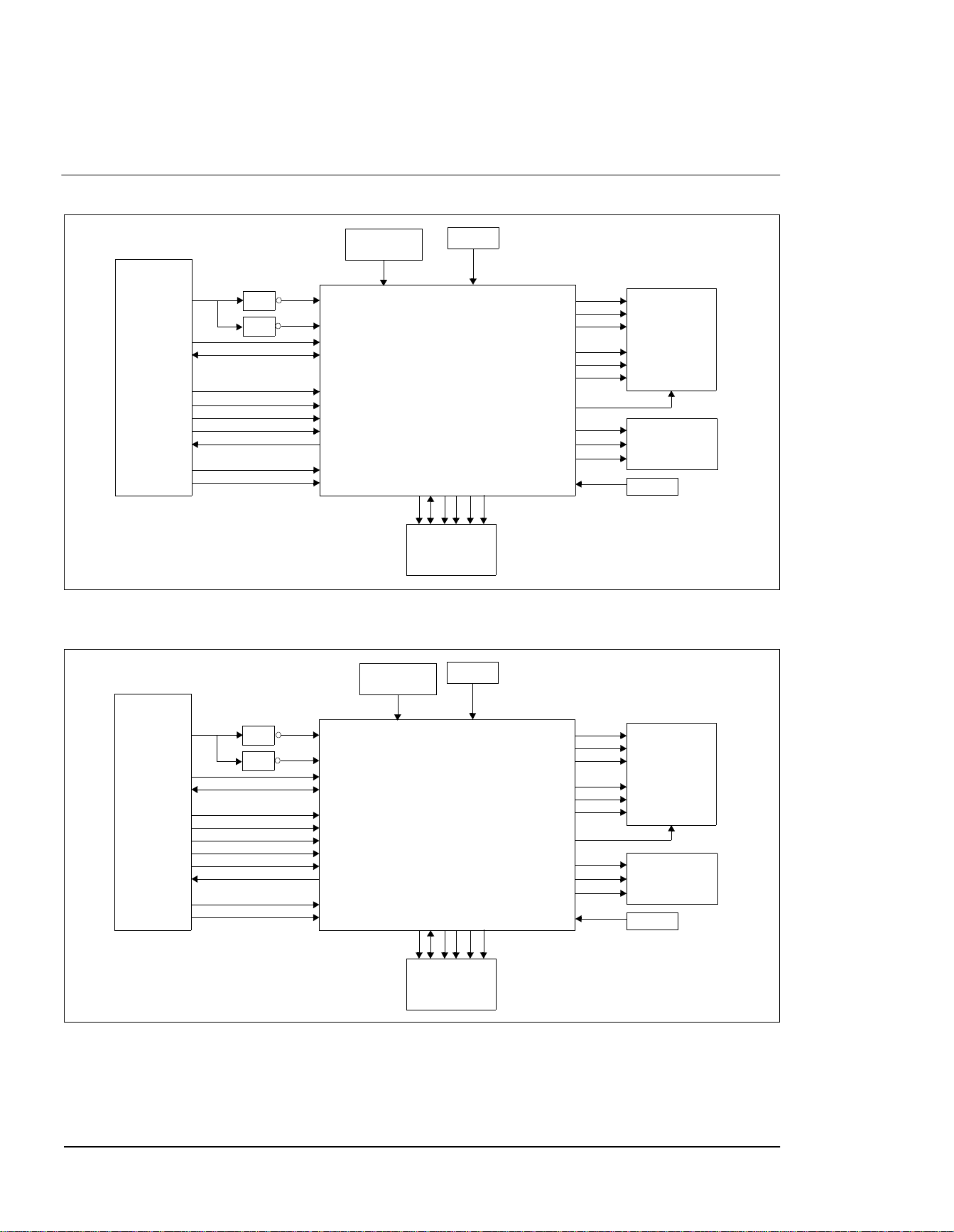

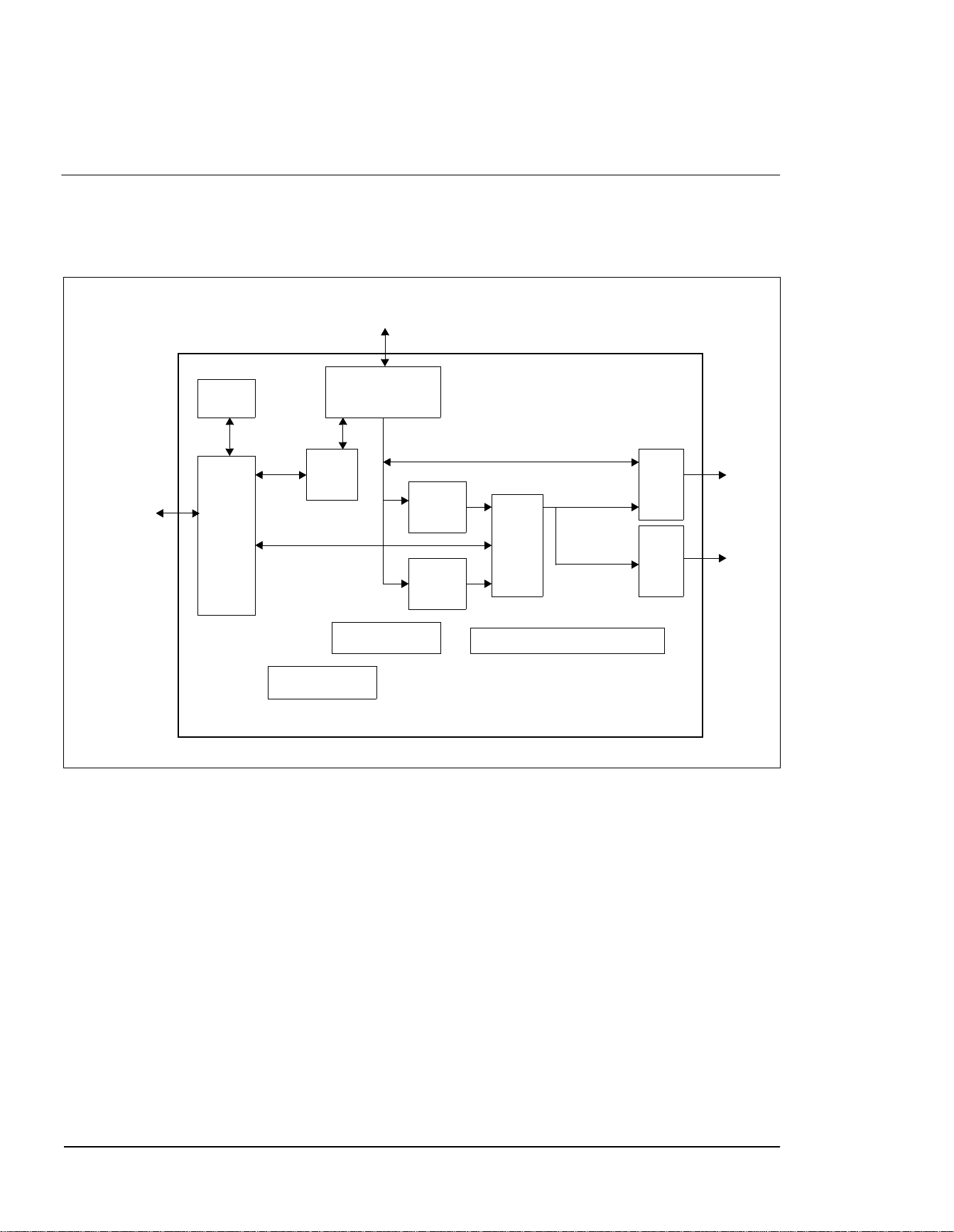

Figure 3-5: Typical System Diagram (Generic Bus) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 3-6: Typical System Diagram (NEC VR41xx (MIPS) Bus) . . . . . . . . . . . . . . . . . . . . . . 17

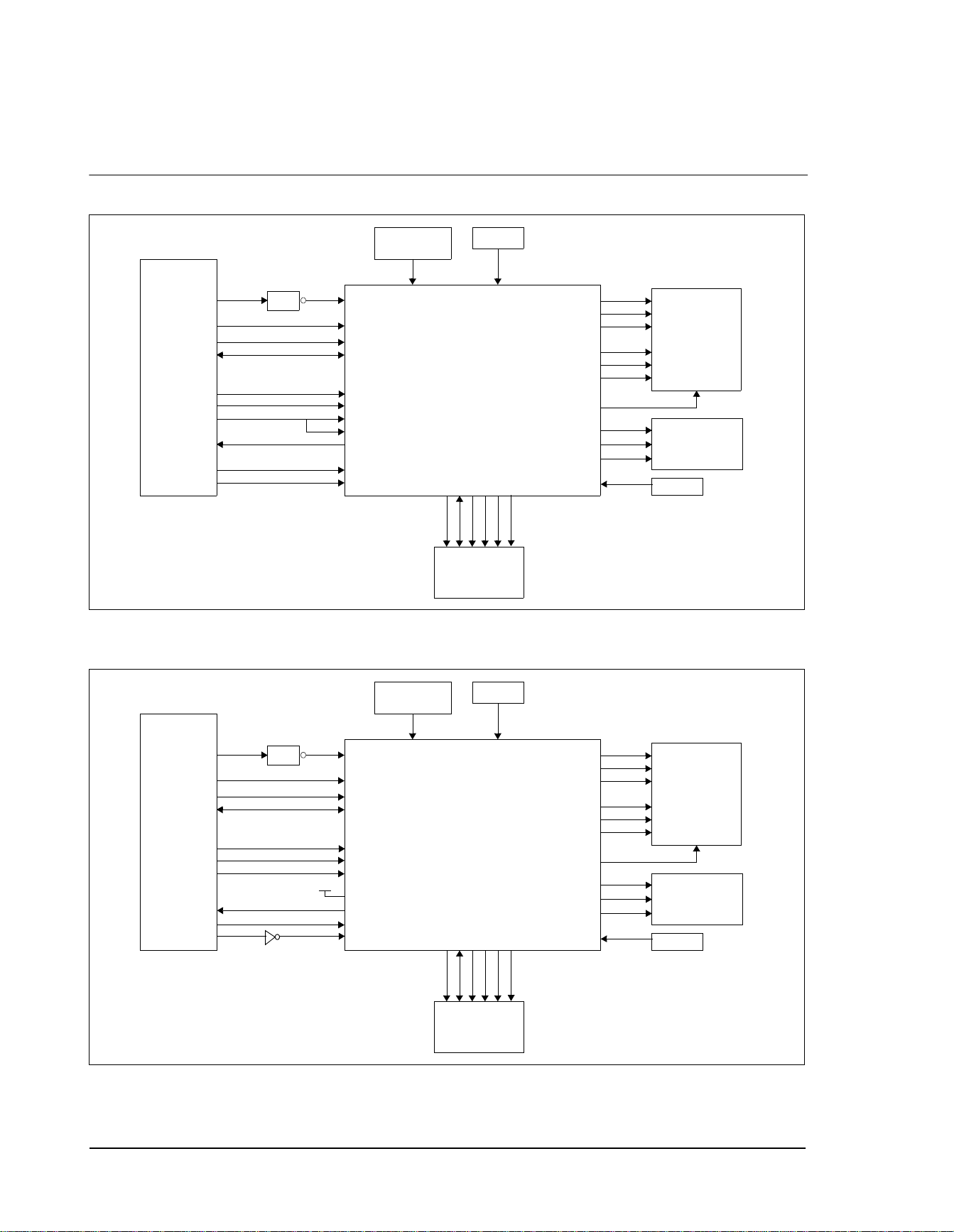

Figure 3-7: Typical System Diagram (Philips PR31500/PR31700 Bus). . . . . . . . . . . . . . . . . . . . 18

Figure 3-8: Typical System Diagram (Toshiba TX3912 Bus) . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 3-9: Typical System Diagram (Power PC Bus). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 3-10: Typical System Diagram (PC Card (PCMCIA) Bus) . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 5-1: Pinout Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 5-3: External Circuitry for CRT Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Figure 7-1: SH-4 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 7-2: SH-3 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 7-3: MC68000 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 7-4: MC68030 Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 7-5: PC Card Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 7-6: Generic Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 7-7: MIPS/ISA Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 7-8: Philips Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 7-9: Clock Input Requirement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Figure 7-10: Toshiba Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Figure 7-11: Clock Input Requirement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Figure 7-12: Power PC Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Figure 7-13: Clock Input Requirement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Figure 7-14: EDO-DRAM Read/Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Figure 7-15: EDO-DRAM Read-Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Figure 7-16: EDO-DRAM CAS Before RAS Refresh Timing . . . . . . . . . . . . . . . . . . . . . . . . . 66

Figure 7-17: EDO-DRAM Self-Refresh Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Figure 7-18: FPM-DRAM Read/Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure 7-19: FPM-DRAM Read-Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Figure 7-20: FPM-DRAM CAS Before RAS Refresh Timing . . . . . . . . . . . . . . . . . . . . . . . . . 72

Figure 7-21: FPM-DRAM Self-Refresh Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Figure 7-22: LCD Panel Power Off / Power On Timing. Drawn with LCDPWR set to active high polarity. . 74

Figure 7-23: Power Save Status and Local Bus Memory Access Relative to Power Save Mode. . . . . . . . 75

Figure 7-24: 4-Bit Single Monochrome Passive LCD Panel Timing . . . . . . . . . . . . . . . . . . . . . . 76

Figure 7-25: 4-Bit Single Monochrome Passive LCD Panel A.C. Timing . . . . . . . . . . . . . . . . . . . 77

Figure 7-26: 8-Bit Single Monochrome Passive LCD Panel Timing . . . . . . . . . . . . . . . . . . . . . . 78

Figure 7-27: 8-Bit Single Monochrome Passive LCD Panel A.C. Timing . . . . . . . . . . . . . . . . . . . 79

Figure 7-28: 4-Bit Single Color Passive LCD Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Figure 7-29: 4-Bit Single Color Passive LCD Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . 81

Page 15

Page 10

Epson Research and Development

Vancouver Design Center

S1D13505 Hardware Functional Specification

X23A-A-001-14 Issue Date: 01/02/02

Figure 7-30: 8-Bit Single Color Passive LCD Panel Timing (Format 1). . . . . . . . . . . . . . . . . . . . . 82

Figure 7-31: 8-Bit Single Color Passive LCD Panel A.C. Timing (Format 1). . . . . . . . . . . . . . . . . . 83

Figure 7-32: 8-Bit Single Color Passive LCD Panel Timing (Format 2). . . . . . . . . . . . . . . . . . . . . 84

Figure 7-33: 8-Bit Single Color Passive LCD Panel A.C. Timing (Format 2). . . . . . . . . . . . . . . . . . 85

Figure 7-34: 16-Bit Single Color Passive LCD Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . .86

Figure 7-35: 16-Bit Single Color Passive LCD Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . .87

Figure 7-36: 8-Bit Dual Monochrome Passive LCD Panel Timing . . . . . . . . . . . . . . . . . . . . . . .88

Figure 7-37: 8-Bit Dual Monochrome Passive LCD Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . 89

Figure 7-38: 8-Bit Dual Color Passive LCD Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Figure 7-39: 8-Bit Dual Color Passive LCD Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . . 91

Figure 7-40: 16-Bit Dual Color Passive LCD Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Figure 7-41: 16-Bit Dual Color Passive LCD Panel A.C. Timing . . . . . . . . . . . . . . . . . . . . . . . . 93

Figure 7-42: 16-Bit TFT/D-TFD Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Figure 7-43: TFT/D-TFD A.C. Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .95

Figure 7-44: CRT Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .97

Figure 7-45: CRT A.C. Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Figure 9-1: Display Buffer Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Figure 10-1: 1/2/4/8 Bit-per-pixel Format Memory Organization . . . . . . . . . . . . . . . . . . . . . . . 124

Figure 10-2: 15/16 Bit-per-pixel Format Memory Organization. . . . . . . . . . . . . . . . . . . . . . . . 125

Figure 10-3: Image Manipulation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Figure 11-1: 1 Bit-per-pixel Monochrome Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . 127

Figure 11-2: 2 Bit-per-pixel Monochrome Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . 127

Figure 11-3: 4 Bit-per-pixel Monochrome Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . 128

Figure 11-4: 1 Bit-per-pixel Color Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Figure 11-5: 2 Bit-per-pixel Color Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Figure 11-6: 4 Bit-per-pixel Color Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Figure 11-7: 8 Bit-per-pixel Color Mode Data Output Path . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Figure 12-1: Ink/Cursor Data Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Figure 12-2: Cursor Positioning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Figure 13-1: Relationship Between The Screen Image and the Image Residing in the Display Buffer . . . . 135

Figure 16-1: Mechanical Drawing QFP15 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Page 16

Epson Research and Development

Page 11

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

1 Introduction

1.1 Scope

This is the Hardware Functional Specification for the S1D13505 Embedded RAMDAC LCD/CRT

Controller. Included in this document are timing diagrams, AC and DC characteristics, register

descriptions, and power management descriptions. This document is intended for two audiences:

Video Subsystem Designers and Soft w are Develop e rs .

This specification will be updated as appropriate. Please check the Epson Electronics America

Website at http://www.eea.epson.com or the Epson Research and Development website at

http://www.erd.epson.com for the latest revision of this document bef ore beginning any development.

We appreciate your comments on our documentation. Please contact us via email at

documentation@erd.epson.com.

1.2 Overview Description

The S1D13505 is a color/monochrome LCD/CRT graphics con troller interfacing to a wide range of

CPUs and display devices. The S1D13505 architecture is designed to meet the low cost, lo w power

requirements of the embedded markets, such as Mobile Communications, Hand-Held PCs, and

Office Automation.

The S1D13505 supports multiple CPUs, all LCD panel types, CRT, and additionally provides a

number of differentiating featur es. Products requi ring a “Portrait” mode display can take advan tage

of the SwivelView™ feature. Simultaneous, Virtual and Split Screen Display are just some of the

display modes supported, while the Hardware Cursor, Ink Layer, and the Memory Enhancement

Registers offer substantial performance benefits. These features, combined with the S1D13505’s

Operating System independence, make it an ideal display solution for a wide variety of applications.

Page 17

Page 12

Epson Research and Development

Vancouver Design Center

S1D13505 Hardware Functional Specification

X23A-A-001-14 Issue Date: 01/02/02

2 Features

2.1 Memory Interface

• 16-bit DRAM interface:

• EDO-DRAM up to 40MHz data rate (80M bytes/sec.).

• FPM-DRAM up to 25MHz data rate (50M bytes/sec.).

• Memory size options:

• 512K bytes using one 256K×16 device.

• 2M bytes using one 1M×16 device.

• Performance Enhancement Register to tailor the memory control output timing for the DRAM

device.

2.2 CPU Interface

• Supports the following interfaces:

• 8/16-bit SH-4 bus interface.

• 8/16-bit SH-3 bus interface.

• 8/16-bit interface to 8/16/32-bit MC68000 microprocessors/microcontrollers.

• 8/16-bit interface to 8/16/32-bit MC68030 microprocessors/microcontrollers.

• Philips PR31500/PR31700 (MIPS).

• Toshiba TX3912 (MIPS)

• 16-bit Power PC (MPC821) microprocessor.

• 16-bit Epson E0C33 microprocessor.

• PC Card (PCMCIA).

• StrongARM (PC Card).

• NEC VR41xx (MIPS).

• ISA bus.

• Supports the following interface with external logic:

• GX486 microprocess or.

• One-stage write buffer for minimum wait-state CPU writes.

• Registers are memory-mapped – the M/R# pin selects between the display buffer and register

address space.

• The complete 2M byte display buffer address space is addressable as a single linear address

space through the 21-bit address bus.

Page 18

Epson Research and Development

Page 13

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

2.3 Display Support

• 4/8-bit monochrome passive LCD interface.

• 4/8/16-bit color passive LCD interface.

• Single-panel, single -driv e displ ays .

• Dual-panel, dual-drive displays.

• Direct support for 9/12-bit TFT/D-TFD; 18-bit TFT/D-TFD is supported up to 64K color depth

(16-bit data).

• Embedded RAMDAC (DAC)with direct analog CRT drive.

• Simultaneous display of CRT and passive or TFT/D-TFD panels.

2.4 Display Modes

• 1/2/4/8/15/16 bit-per-pixel (bpp) support on LCD/CRT.

• Up to 16 shades of gray using FRM on monochrome passive LCD panels.

• Up to 4096 colors on passive LCD panels; three 256x4 Look-Up Tables (LUT) are used to map

1/2/4/8 bpp modes into these colors, 15/16 bpp modes are mapped directly using the 4 most

significant bits of the red, green and blue colors.

• Up to 64K colors on TFT/D-TF D LCD panels and CRT; three 2 56x4 Look- Up Tables are us ed to

map 1/2/4/8 bpp modes into 4096 colors, 15/16 bpp modes are mapped directly.

2.5 Display Features

• SwivelView™: direct hardware 90° rotation of display image for “portrait” mode display.

• Split Screen Display: allows two different images to be simultaneously viewed on th e same

display.

• Virtual Display Support: displays images larger than the display size thr ough the use of panning.

• Double Buffering/multi-pages: provides smooth animation and instantaneous screen update.

• Acceleration of screen updates by allocating full display memory bandwidth to CPU (see

REG[23h] bit 7).

• Hardware 64x64 pixel 2-bit cursor or full screen 2-bit ink layer.

• Simultaneous display of CRT and passive panel or TFT/D-TFD panel.

• Normal mode for cases where LCD and CRT screen sizes are identical.

• Line-doubling for simultaneous display of 240-line images on 240-line LCD and 480-line

CRT.

• Even-scan or interlace modes for simultaneous display of 480-line images on 240-line LCD

and 480-line CRT.

2.6 Clock Source

• Single clock input for both the pixel and memory clocks.

• Memory clock can be input clock or (input clock/2), providing flexibility to use CPU bus clock

as input.

• Pixel clock can be the memory clock, (memory cloc k/2), (memor y clock/3 ) or (memory clock/4).

Page 19

Page 14

Epson Research and Development

Vancouver Design Center

S1D13505 Hardware Functional Specification

X23A-A-001-14 Issue Date: 01/02/02

2.7 Miscellaneous

• The memor y data bus, MD[15:0], is used to configure the chip at power-on.

• Three General Purpose Input/Output pins, GPIO[3:1], are available if the upper Memory

Address pins are not required for asymmetric DRAM support.

• Suspend power save mode can be initiated by either hardware or software.

• The SUSPEND# pin is used either as an input to initiate Suspend mode, or as a General Purpose

Output that can be used to control the LCD backlight. Power-on polarity is selected by an MD

configuration pin.

• Operating voltages from 2.7 volts to 5.5 volts are supported

• 128-pin QFP15 surface mount package

Page 20

Epson Research and Development

Page 15

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

3 Typical System Implementation Diagrams

Figure 3-1: Typical System Diagram (SH-4 Bus)

.

Figure 3-2: Typical System Diagram (SH-3 Bus)

S1D13505F00A

FPFRAME

FPSHIFT

FPLINE

DRDY

FPDAT[15:8]

FPDAT[7:0]

CLKI

Oscillator

FPFRAME

FPSHIFT

FPLINE

MOD

UD[7:0]

LD[7:0]

4/8/16-bit

LCD

Display

SH-4

BUS

RESET#

WE0#

D[15:0]

BS#

RD/WR#

RD#

RDY#

A[20:0]

CKIO

WE0#

RD/WR#

AB[20:0]

DB[15:0]

WE1#

BS#

RD#

M/R#

CS#

BUSCLK

WAIT#

RESET#

A[21]

CSn#

WE1#

LCDPWR

LCAS#

UCAS#

MA[8:0]

MD[15:0]

WE#

RAS#

Power

Management

SUSPEND#

RED,GREEN,BLUE

HRTC

VRTC

CRT

Display

IREF

IREF

WE#

A[8:0]

D[15:0]

RAS#

256Kx16

LCAS#

UCAS#

FPM/EDO-DRAM

S1D13505F00A

FPFRAME

FPSHIFT

FPLINE

DRDY

FPDAT[15:8]

FPDAT[7:0]

CLKI

Oscillator

FPFRAME

FPSHIFT

FPLINE

MOD

UD[7:0]

LD[7:0]

4/8/16-bit

LCD

Display

SH-3

BUS

RESET#

WE0#

D[15:0]

BS#

RD/WR#

RD#

WAIT#

A[20:0]

CKIO

WE0#

RD/WR#

AB[20:0]

DB[15:0]

WE1#

BS#

RD#

M/R#

CS#

BUSCLK

WAIT#

RESET#

A[21]

CSn#

WE1#

LCDPWR

LCAS#

UCAS#

MA[8:0]

MD[15:0]

WE#

RAS#

Power

Management

SUSPEND#

RED,GREEN,BLUE

HRTC

VRTC

CRT

Display

IREF

IREF

WE#

A[8:0]

D[15:0]

RAS#

256Kx16

LCAS#

UCAS#

FPM/EDO-DRAM

Page 21

Page 16

Epson Research and Development

Vancouver Design Center

S1D13505 Hardware Functional Specification

X23A-A-001-14 Issue Date: 01/02/02

.

Figure 3-3: Typical System Diagram (MC6 8K Bus 1, 16-Bit 68000)

.

Figure 3-4: Typical System Diagram (MC6 8K Bus 2, 32-Bit 68030)

S1D13505F00A

FPFRAME

FPSHIFT

FPLINE

DRDY

FPDAT[15:8]

FPDAT[7:0]

CLKI

Oscillator

FPFRAME

FPSHIFT

FPLINE

MOD

UD[7:0]

LD[7:0]

4/8/16-bit

LCD

Display

MC68000

BUS

RESET#

LDS#

D[15:0]

AS#

R/W#

DTACK #

A[20:1]

BCLK

AB0#

RD/WR#

AB[20:1]

DB[15:0]

WE1#

BS#

M/R#

CS#

BUSCLK

WAIT#

RESET#

A[23:21]

FC0, FC1

Decoder

Decoder

UDS#

LCDPWR

LCAS#

UCAS#

MA[8:0]

MD[15:0]

WE#

RAS#

Power

Management

SUSPEND#

RED,GREEN,BLUE

HRTC

VRTC

CRT

Display

IREF

IREF

WE#

A[8:0]

D[15:0]

RAS#

256Kx16

LCAS#

UCAS#

FPM/EDO-DRAM

S1D13505F00A

FPFRAME

FPSHIFT

FPLINE

DRDY

FPDAT[15:8]

FPDAT[7:0]

CLKI

Oscillator

FPFRAME

FPSHIFT

FPLINE

MOD

UD[7:0]

LD[7:0]

4/8/16-bit

LCD

Display

MC68030

BUS

RESET#

SIZ0

D[31:16]

AS#

R/W#

SIZ1

DSACK1#

A[20:0]

BCLK

WE0#

RD/WR#

AB[20:0]

DB[15:0]

WE1#

BS#

RD#

M/R#

CS#

BUSCLK

WAIT#

RESET#

A[31:21]

FC0, FC1

Decoder

Decoder

DS#

LCDPWR

WE#

A[8:0]

D[15:0]

RAS#

256Kx16

LCAS#

UCAS#

MA[8:0]

MD[15:0]

WE#

RAS#

LCAS#

UCAS#

FPM/EDO-DRAM

Power

Management

SUSPEND#

RED,GREEN,BLUE

HRTC

VRTC

CRT

Display

IREF

IREF

Page 22

Epson Research and Development

Page 17

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

.

Figure 3-5: Typical System Diagram (Generic Bus)

.

Figure 3-6: Typical System Diagram (NEC VR41xx (M I PS) Bus)

S1D13505F00A

FPFRAME

FPSHIFT

FPLINE

DRDY

FPDAT[15:8]

FPDAT[7:0]

CLKI

Oscillator

FPFRAME

FPSHIFT

FPLINE

MOD

UD[7:0]

LD[7:0]

4/8/16-bit

LCD

Display

Generic

BUS

RESET#

D[15:0]

RD#

WAIT#

A[20:0]

BCLK

RD/WR#

AB[20:0]

DB[15:0]

WE1#

RD#

M/R#

CS#

BUSCLK

WAIT#

RESET#

A[27:21]

CSn#

WE1#

LCDPWR

WE#

A[11:0]

D[15:0]

RAS#

1Mx16

LCAS#

UCAS#

MA[11:0]

MD[15:0]

WE#

RAS#

LCAS#

UCAS#

FPM/EDO-DRAM

Decoder

WE0#

WE0#

Power

Management

SUSPEND#

RED,GREEN,BLUE

HRTC

VRTC

CRT

Display

IREF

IREF

S1D13505F00A

FPFRAME

FPSHIFT

FPLINE

DRDY

FPDAT[15:8]

FPDAT[7:0]

CLKI

Oscillator

FPFRAME

FPSHIFT

FPLINE

MOD

UD[7:0]

LD[7:0]

4/8/16-bit

LCD

Display

MIPS

BUS

RESET

D[15:0]

MEMR#

RDY

A[20:0]

BCLK

RD/WR#

AB[20:0]

DB[15:0]

WE1#

RD#

M/R#

CS#

BUSCLK

WAIT#

RESET#

A[25:21]

CSn#

SBHE#

LCDPWR

WE#

A[11:0]

D[15:0]

RAS#

1Mx16

LCAS#

UCAS#

MA[11:0]

MD[15:0]

WE#

RAS#

LCAS#

UCAS#

FPM/EDO-DRAM

Decoder

WE0#

MEMW#

Power

Management

SUSPEND#

RED,GREEN,BLUE

HRTC

VRTC

CRT

Display

IREF

IREF

VDD

Page 23

Page 18

Epson Research and Development

Vancouver Design Center

S1D13505 Hardware Functional Specification

X23A-A-001-14 Issue Date: 01/02/02

.

Figure 3-7: Typical System Diagram (Philips PR31500/PR31700 Bus)

.

Figure 3-8: Typical System Diagram (Toshiba TX3912 Bus)

S1D13505F00A

FPFRAME

FPSHIFT

FPLINE

DRDY

FPDAT[15:8]

FPDAT[7:0]

CLKI

Oscillator

FPFRAME

FPSHIFT

FPLINE

MOD

UD[7:0]

LD[7:0]

4/8/16-bit

LCD

Display

LCDPWR

WE#

A[11:0]

D[15:0]

RAS#

1Mx16

LCAS#

UCAS#

MA[11:0]

MD[15:0]

WE#

RAS#

LCAS#

UCAS#

FPM/EDO-DRAM

Power

Management

SUSPEND#

RED,GREEN,BLUE

HRTC

VRTC

CRT

Display

IREF

IREF

PR31500

BUS

RESET#

/WE

D[31:16]

/CARDxCSL

/RD

/CARDxWAIT

A[12:0]

DCLKOUT

WE0#

RD/WR#

AB[12:0]

DB[15:0]

WE1#

BS#

RD#

M/R#

CS#

BUSCLK

WAIT#

RESET#

/CARDxCSH

AB[16:13]

ALE

/CARDREG

/CARDIORD

AB20

AB19

AB18

AB17

/CARDIOWR

/PR31700

Philips

S1D13505F00A

FPFRAME

FPSHIFT

FPLINE

DRDY

FPDAT[15:8]

FPDAT[7:0]

CLKI

Oscillator

FPFRAME

FPSHIFT

FPLINE

MOD

UD[7:0]

LD[7:0]

4/8/16-bit

LCD

Display

LCDPWR

WE#

A[11:0]

D[15:0]

RAS#

1Mx16

LCAS#

UCAS#

MA[11:0]

MD[15:0]

WE#

RAS#

LCAS#

UCAS#

FPM/EDO-DRAM

Power

Management

SUSPEND#

RED,GREEN,BLUE

HRTC

VRTC

CRT

Display

IREF

IREF

BUS

RESET#

WE*

D[23:16]

CARDxCSL*

RD*

CARDxWAIT*

A[12:0]

DCLKOUT

WE0#

RD/WR#

AB[12:0]

DB[15:8]

WE1#

BS#

RD#

M/R#

CS#

BUSCLK

WAIT#

RESET#

CARDxCSH*

AB[16:13]

ALE

CARDREG*

CARDIORD*

AB20

AB19

AB18

AB17

CARDIOWR*

Toshiba

TX3912

DB[7:0]

D[31:24]

Page 24

Epson Research and Development

Page 19

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

.

Figure 3-9: Typical System Diagram (Power PC Bus)

.

Figure 3-10: Typical System Diagram (PC Card (PCMCIA) Bus)

S1D13505F00A

FPFRAME

FPSHIFT

FPLINE

DRDY

FPDAT[15:8]

FPDAT[7:0]

CLKI

Oscillator

FPFRAME

FPSHIFT

FPLINE

MOD

UD[7:0]

LD[7:0]

4/8/16-bit

LCD

Display

PowerPC

BUS

RESET#

TSIZ1

D[0:15]

TS#

RD/WR#

TSIZ0

TA#

A[11:31]

CLKOUT

WE0#

RD/WR#

AB[20:0]

DB[15:0]

WE1#

BS#

RD#

M/R#

CS#

BUSCLK

WAIT#

RESET#

A[0:10]

Decoder

Decoder

BI#

LCDPWR

WE#

A[8:0]

D[15:0]

RAS#

256Kx16

LCAS#

UCAS#

MA[8:0]

MD[15:0]

WE#

RAS#

LCAS#

UCAS#

FPM/EDO-DRAM

Power

Management

SUSPEND#

RED,GREEN,BLUE

HRTC

VRTC

CRT

Display

IREF

IREF

S1D13505F00A

FPFRAME

FPSHIFT

FPLINE

DRDY

FPDAT[15:8]

FPDAT[7:0]

CLKI

Oscillator

FPFRAME

FPSHIFT

FPLINE

MOD

UD[7:0]

LD[7:0]

4/8/16-bit

LCD

Display

PC Card

BUS

RESET

D[15:0]

-OE

-WAIT

A[20:0]

BCLK

RD/WR#

AB[20:0]

DB[15:0]

WE1#

RD#

M/R#

CS#

BUSCLK

WAIT#

RESET#

A[25:21]

-CE2

LCDPWR

WE#

A[11:0]

D[15:0]

RAS#

1Mx16

LCAS#

UCAS#

MA[11:0]

MD[15:0]

WE#

RAS#

LCAS#

UCAS#

FPM/EDO-DRAM

WE0#

-WE

Power

Management

SUSPEND#

RED,GREEN,BLUE

HRTC

VRTC

CRT

Display

IREF

IREF

Decoder

Decoder

-CE1

Page 25

Page 20

Epson Research and Development

Vancouver Design Center

S1D13505 Hardware Functional Specification

X23A-A-001-14 Issue Date: 01/02/02

4 Internal Descriptio n

4.1 Block Diagram Showing Datapaths

4.2 Block Descriptions

4.2.1 Register

The Register block contains all the register latches

4.2.2 Host Interface

The Host Interface (I/F) block provides the means for the CPU/MPU to communicate with the

display buffer and internal registers via one of the supported bus interfaces.

4.2.3 CPU R/W

The CPU R/W block synchronizes the CPU requests for display buffer access. If SwivelView is

enabled, the data is rotated in this block.

Clocks

LCD

Memory

Controller

16-bit FPM/EDO-DRAM

LCD

Power Save

Register

CRTC

Look-

I/F

CPU/MPU

Host

I/F

CPU

R/W

Display

FIFO

CRT

Cursor

FIFO

Up

Tables

DAC

Page 26

Epson Research and Development

Page 21

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

4.2.4 Memory Controller

The Memory Controller block arbitrates between CPU accesses and display refresh access es as well

as generates the necessary signals to interface to one of th e supported 16-bit memory d evices (FPMDRAM or EDO-DRAM).

4.2.5 Display FIFO

The Display FIFO block fetches display data from the Memory Controller for display refresh.

4.2.6 Cursor FIFO

The Cursor FIFO block fetches Cursor/ink data from the Memory Controller for display refresh.

4.2.7 Look-Up Tables

The Look-Up Tables block contains three 256x4 Look-Up Tables (LUT), one for each primary

color. In monochrome mode, only the green LUT is selected and used. This block contains antisparkle circuitry. The cursor/ink and display data are merged in this block.

4.2.8 CRTC

The CRTC generates the sync timing for the LCD and CRT, defining the vertical and horizontal

display periods.

4.2.9 LCD Interface

The LCD Interface block performs Frame Rate Modulation (FRM) for passive LCD panels and

generates the correct data format and timing control signals for various LCD and TFT/D-TFD

panels.

4.2.10 DAC

The DAC is the Digital to Analog converter for analog CRT support.

4.2.11 Power Save

The Power Save block contains the power save mode circuitry.

4.2.12 Clocks

The Clocks module is the source of all clocks in the chip.

Page 27

Page 22

Epson Research and Development

Vancouver Design Center

S1D13505 Hardware Functional Specification

X23A-A-001-14 Issue Date: 01/02/02

5 Pins

5.1

Pinout Diagram

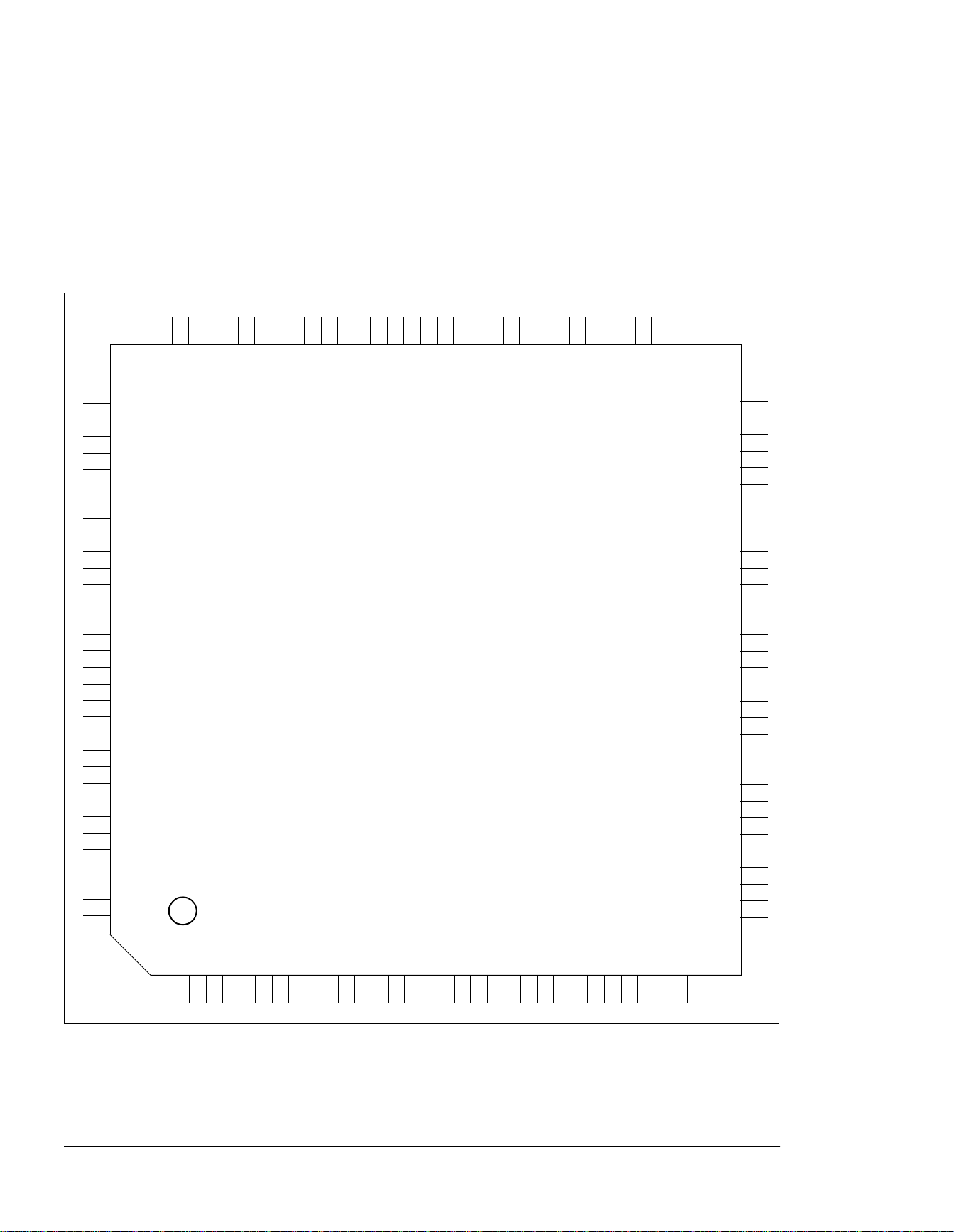

Figure 5-1: Pinout Diagram

128-pin QFP15 surface mount package

1234567891011121314151617181920212223242526272829303132

96 95 94 93 92 91 90 89 88 87 86 85 84 83 7475 73 72 71 70 69 68 67 66 6582 81 80 79 78 77 76

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

58

59

60

61

62

63

51

52

53

54

55

56

57

64

S1D13505

RD/WR#

WAIT#

VDD

VSS

DB15

DB14

DB12

DB8

DB5

DB3

DB2

DB1

DB0

DB13

DB4

AB2

RESET#

VDD

MA6

MA8

DB7

FPDAT3

MA3

MA4

MA2

MA5

MD6

MA11

MA0

MA7

MA10

MA9

VDD

BLUE

VSS

DACVDD

GREEN

FPDAT13

FPDAT10

RAS#

WE#

UCAS#

VSS

MD7

MD8

MD5

MD10

MD4

MD11

MD3

MD12

MD2

MD13

MD1

AB3

BS#

WE1#

WE0#

RD#

M/R#

CS#

AB0

AB1

AB11

AB12

AB15

AB16

AB17

AB18

AB19

AB20

VDD

VSS

DACVSS

IREF

DACVDD

VDD

FPDAT2

FPDAT4

VSS

FPSHIFT

DRDY

LCDPWR

FPLINE

FPFRAME

VSS

MD15

FPDAT15

FPDAT14

VSS

DACVDD

MD14

DB10

DB9

VSS

DB11

DB6

MA1

LCAS#

MD9

FPDAT5

FPDAT7

VDD

TESTEN

FPDAT8

MD0

FPDAT9

FPDAT12

FPDAT0

FPDAT1

VRTC

FPDAT11

HRTC

AB14

AB13

AB7

AB4

AB5

AB8

AB9

AB10

AB6

RED

FPDAT6

CLKI

BUSCLK

SUSPEND#

DACVSS

Page 28

Epson Research and Development

Page 23

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

5.2 Pin Descriptio n

Key:

5.2.1 Host Interface

I = Input

O=Output

IO = Bi-Directional (Input/Output)

A=Analog

P=Power pin

C = CMOS level input

CD = CMOS level input with pull down resistor (typical values of 100K

Ω/180ΚΩ

at 5V/3.3V respectively)

CS = CMOS level Schmitt input

COx = CMOS output driver, x denotes driver type (see tables 6-3, 6-4, 6-5 for details)

TSx = Tri-state CMOS output driver, x denotes driver type (see tables 6-3, 6-4, 6-5 for details)

TSxD =

Tri-state CMOS output driver with pull down resistor (typical values of 100K

Ω/180ΚΩ

at 5V/3.3V)

respectively), x denotes driver type (see tables 6-3, 6-4, 6-5 for details)

CNx = CMOS low-noise output driver, x denotes driver type (see tables 6-3, 6-4, 6-5 for details)

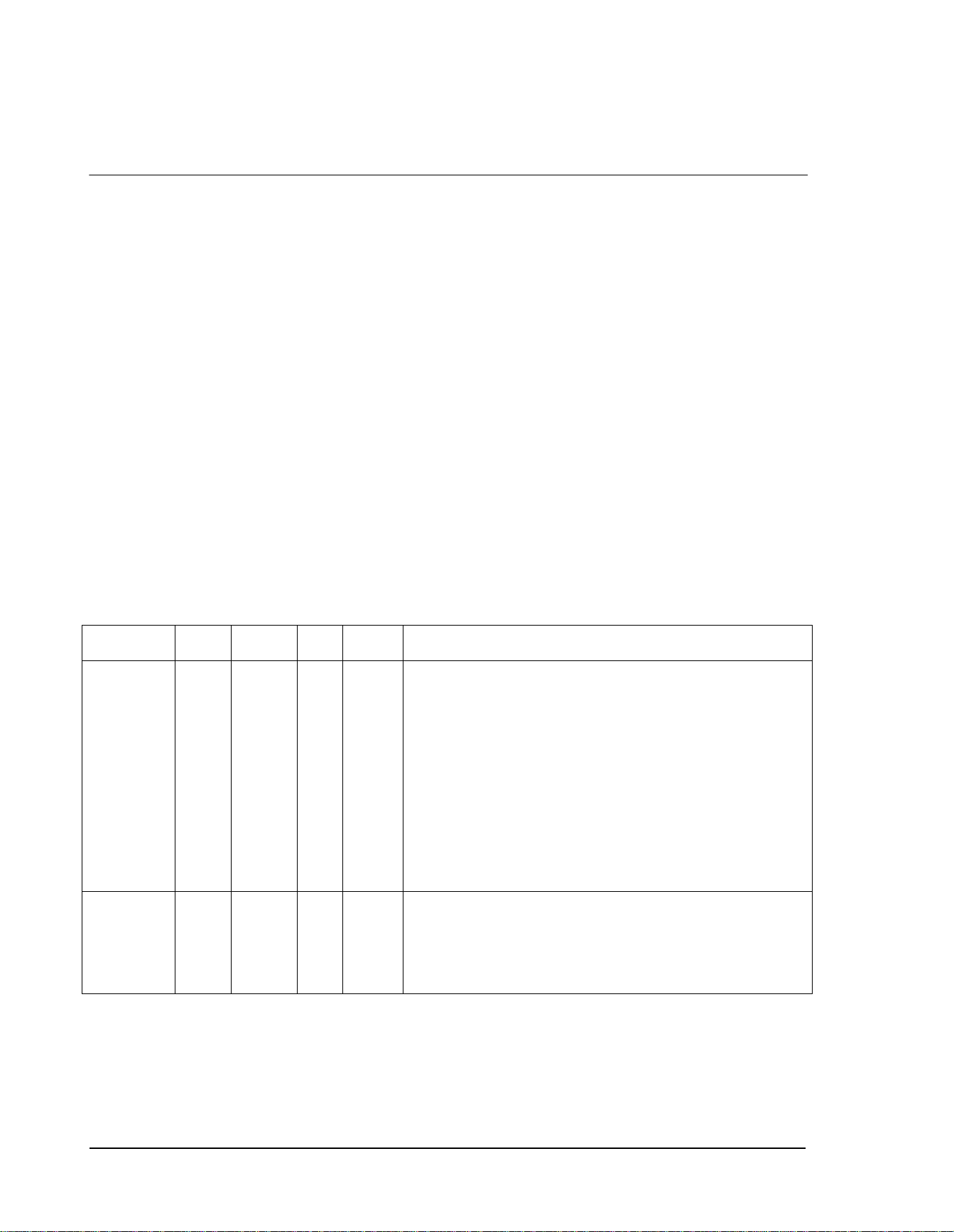

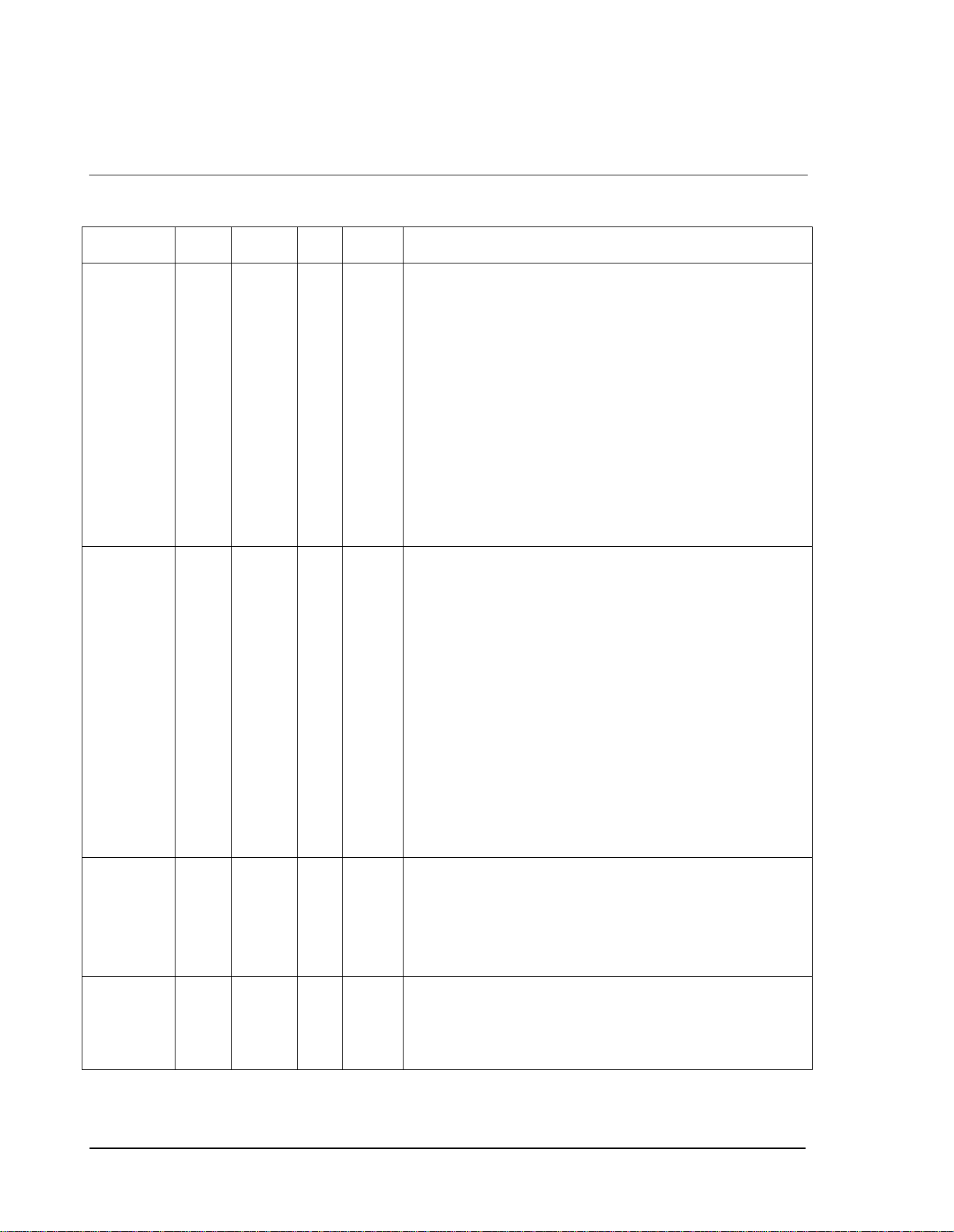

Table 5-1: Host Interface Pin Descriptions

Pin Name T yp e Pin # Cell

RESET#

State

Description

AB0 I 3

CS Hi-Z

• For SH-3/SH-4 Bus, this pin inputs system address bit 0 (A0).

• For MC68K Bus 1, this pin inputs the lower data strobe (LDS#).

• For MC68K Bus 2, this pin inputs system address bit 0 (A0).

• For Generic Bus, this pin inputs system address bit 0 (A0).

• For MIPS/ISA Bus, this pin inputs system address bit 0 (SA0).

• For Philips PR31500/31700 Bu s, this pin inputs system address bit 0

(A0).

• For Toshiba TX3912 Bus, this pin inputs system address bit 0 (A0).

• For PowerPC Bus, this pin inputs system address bit 31 (A31).

• For PC Card (PCMCIA) Bus, this pin inputs system address bit 0

(A0).

See

“Host Bus Interface Pin M app ing ”

for summary. See th e re spe ct ive

AC Timing diagram for detailed functionality.

AB[12:1] I

119-128,

1, 2

CHi-Z

• For PowerPC Bus, these pins input the system address bits 19

through 30 (A[19:30]).

• For all other busses, these pins input the system address bits 12

through 1 (A[12:1]).

See

“Host Bus Interface Pin M app ing ”

for summary. See th e re spe ct ive

AC Timing diagram for detailed functionality.

Page 29

Page 24

Epson Research and Development

Vancouver Design Center

S1D13505 Hardware Functional Specification

X23A-A-001-14 Issue Date: 01/02/02

AB[16:13] I 115-118

CHi-Z

• For Philips PR31500/31700 Bus, these pins are connected to V

DD

.

• For Toshiba TX3912 Bus, these pins are connected to VDD.

• For PowerPC Bus, these pins input the system address bits 15

through 18 (A[15:18]).

• For all other busses, these pins input the system address bits 16

through 13 (A[16:13]).

See

“Host Bus Interface Pin Mapping”

for summary. See the respective

AC Timing diagram for detailed functionality.

AB17 I 114

CHi-Z

• For Philips PR31500/31700 Bus, this pin inputs the IO write

command (/CARDIOWR).

• For Toshiba TX3912 Bus, this pin inputs the IO write command

(CARDIOWR*).

• For PowerPC Bus, this pin inputs the system address bit 14 (A14).

• For all other busses, this pin inputs the system address bit 17 (A17).

See

“Host Bus Interface Pin Mapping”

for summary. See the respective

AC Timing diagram for detailed functionality.

AB18 I 113

CHi-Z

• For Philips PR31500/31700 Bus, this pin inputs the IO read

command (/CARDIORD).

• For Toshiba TX3912 Bus, this pin inputs the IO read command

(CARDIORD*).

• For PowerPC Bus, this pin inputs the system address bit 13 (A13).

• For all other busses, this pin inputs the system address bit 18 (A18).

See

“Host Bus Interface Pin Mapping”

for summary. See the respective

AC Timing diagram for detailed functionality.

AB19 I 112

CHi-Z

• For Philips PR31500/31700 Bus, this pin inputs the card control

register access (/CARDREG).

• For Toshiba TX3912 Bus, this pin inputs the card control register

(CARDREG*).

• For PowerPC Bus, this pin inputs the system address bit 12 (A12).

• For all other busses, this pin inputs the system address bit 19 (A19).

See

“Host Bus Interface Pin Mapping”

for summary. See the respective

AC Timing diagram for detailed functionality.

AB20 I 111

CHi-Z

• For the MIPS/ISA Bus, this pin inputs system address bit 20. Note

that for the ISA Bus, the unlatched LA20 must first be latched before

input to AB20.

• For Philips PR31500/31700 Bus, this pin inputs the address latch

enable (ALE).

• For Toshiba TX3912 Bus, this pin inputs the address latch enable

(ALE).

• For PowerPC Bus, this pin inputs the system address bit 11 (A11).

• For all other busses, this pin inputs the system address bit 20 (A20).

See

“Host Bus Interface Pin Mapping”

for summary. See the respective

AC Timing diagram for detailed functionality.

Table 5-1: Host Interface Pin Descriptions (Continued)

Pin Name Type Pin # Cell

RESET#

State

Description

Page 30

Epson Research and Development

Page 25

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

DB[15:0] IO 16-31

C/TS2 Hi-Z

These pins are the system data bus. For 8-bit bus modes, unused data

pins should be tied to VDD.

• For SH-3/SH-4 Bus, these pins are connected to D[15:0].

• For MC68K Bus 1, these pins are connected to D[15:0].

• For MC68K Bus 2, these pins are connected to D[31:16] for 32-bit

devices (e.g. MC68030) or D[15:0 ] for 16-bit devices (e.g. M C68 340 ).

• For Generic Bus, these pins are connected to D[15:0].

• For MIPS/ISA Bus, these pins are connected to SD[15:0].

• For Philips PR31500/31700 Bus, these pins are connected to

D[31:16].

• For Toshiba TX3912 Bus, pins [15:8] are connected to D[23:16] and

pins [7:0] are connected to D[31:24].

• For PowerPC Bus, these pins are connected to D[0:15].

• For PC Card (PCMCIA) Bus, these pins are connected to D[15:0].

See

“Host Bus Interface Pin M app ing ”

for summary. See th e re spe ct ive

AC Timing diagram for detailed functionality.

WE1# IO 9

CS/TS

2

Hi-Z

This is a multi-purpose pin:

• For SH-3/SH-4 Bus, this pin inputs the write enable signal for the

upper data byte (WE1#).

• For MC68K Bus 1, this pin inputs the upper data strobe (UDS#).

• For MC68K Bus 2, this pin inputs the data strobe (DS#).

• For Generic Bus, this pin inputs the write enable signal for the upper

data byte (WE1#).

• For MIPS/ISA Bus, this pin inputs the syste m by te high ena b le sign al

(SBHE#).

• For Philips PR31500/31700 Bus, this pin inputs the odd byte access

enable signal (/CARDxCSH).

• For Toshiba TX3912 Bus, this pin inputs the odd byte access enable

signal (CARDxCSH*).

• For PowerPC Bus, this pin outputs the burst inhibit signal (BI#).

• For PC Card (PCMCIA) Bus, this pin inputs the card enable 2 signal

(-CE2).

See

“Host Bus Interface Pin M app ing ”

for summary. See th e re spe ct ive

AC Timing diagram for detailed functionality.

M/R# I 5 C

Hi-Z

• For Philips PR31500/31700 Bus, this pin is connected to V

DD

.

• For Toshiba TX3912 Bus, this pin is connected to V

DD

.

• For all other busses, this input pin is used to select between the

display buffer and register address spa ces o f the S1 D13505. M/R# is

set high to access the display buffer and low to access the registers.

See

Register Mapping

.

See Table 5-6:, “CPU Interface Pin Mapping,” on page 34.

CS# I 4

CHi-Z

• For Philips PR31500/31700 Bus, this pin is connected to V

DD

.

• For Toshiba TX3912 Bus, this pin is connected to V

DD

.

• For all other busses, this is the Chip Select input.

See Table 5-6:, “CPU Interface Pin Mapping,” on page 34. See the

respective AC Timing diagram for detailed functionality.

Table 5-1: Host Interface Pin Descriptions (Continued)

Pin Name T yp e Pin # Cell

RESET#

State

Description

Page 31

Page 26

Epson Research and Development

Vancouver Design Center

S1D13505 Hardware Functional Specification

X23A-A-001-14 Issue Date: 01/02/02

BUSCLK I 13

CHi-Z

This pin inputs the system bus clock. It is possible to apply a 2x clock

and divide it by 2 internally - see MD12 in

Summary of Configuration

Options

.

• For SH-3/SH-4 Bus, this pin is connected to CKIO.

• For MC68K Bus 1, this pin is connected to CLK.

• For MC68K Bus 2, this pin is connected to CLK.

• For Generic Bus, this pin is connected to BCLK.

• For MIPS/ISA Bus, this pin is connected to CLK.

• For Philips PR31500/31700 Bus, this pin is connected to DCLKOUT.

• For Toshiba TX3912 Bus, this pin is connected to DCLKOUT.

• For PowerPC Bus, this pin is connected to CLKOUT.

• For PC Card (PCMCIA) Bus, this pin is connected to CLKI.

See

“Host Bus Interface Pin Mapping”

for summary. See the respective

AC Timing diagram for detailed functionality.

BS# I 6

CS Hi-Z

This is a multi-purpose pin:

• For SH-3/SH-4 Bus, this pin inputs the bus start signal (BS#).

• For MC68K Bus 1, this pin inputs the address strobe (AS#).

• For MC68K Bus 2, this pin inputs the address strobe (AS#).

• For Generic Bus, this pin is connected to V

DD

.

• For MIPS/ISA Bus, this pin is connected to V

DD

.

• For Philips PR31500/31700 Bus, this pin is connected to VDD.

• For Toshiba TX3912 Bus, this pin is connected to VDD.

• For PowerPC Bus, this pin inputs the Transfer Start signal (TS#).

• For PC Card (PCMCIA) Bus, this pin is connected to V

DD

.

See

“Host Bus Interface Pin Mapping”

for summary. See the respective

AC Timing diagram for detailed functionality.

RD/WR# I 10

CS Hi-Z

This is a multi-purpose pin:

• For SH-3/SH-4 Bus, this pin inputs the read write signal (RD/WR#).

The S1D13505 needs this signal for early decode of the bus cycle.

• For MC68K Bus 1, this pin inputs the read write signal (R/W#).

• For MC68K Bus 2, this pin inputs the read write signal (R/W#).

• For Generic Bus, this pin input s the read comman d for the upp er data

byte (RD1#).

• For MIPS/ISA Bus, this pin is connected to V

DD

.

• For Philips PR31500/31700 Bus, this pin input s the even byte access

enable signal (/CARDxCSL).

• For Toshiba TX3912 Bus, this p in in puts t he even byte access enab l e

signal (CARDxCSL*).

• For PowerPC Bus, this pin inputs the read write signal (RD/WR#).

• For PC Card (PCMCIA) Bus, this pin inputs the card enable 1 signal

(-CE1).

See

“Host Bus Interface Pin Mapping”

for summary. See the respective

AC Timing diagram for detailed functionality.

Table 5-1: Host Interface Pin Descriptions (Continued)

Pin Name Type Pin # Cell

RESET#

State

Description

Page 32

Epson Research and Development

Page 27

Vancouver Design Center

Hardware Functional Specification S1D13505

Issue Date: 01/02/02 X23A-A-001-14

RD# I 7

CS Hi-Z

This is a multi-purpose pin:

• For SH-3/SH-4 Bus, this pin inputs the read signal (RD#).

• For MC68K Bus 1, this pin is connected to V

DD

.

• For MC68K Bus 2, this pin inputs the bus size bit 1 (SIZ1).

• For Generic Bus, this pin inputs the read comma nd f or the low er data

byte (RD0#).

• For MIPS/ISA Bus, this pin inputs the memory read signal (MEMR#).

• For Philips PR31500/31700 Bus, this pin inputs the memory read

command (/RD).

• For Toshiba TX3912 Bus, this pin inputs the mem ory read command

(RD*).

• For PowerPC Bus, this pin inputs the transfer size 0 signal (TSIZ0).

• For PC Card (PCMCIA) Bus, this pin inputs the output enab le si gna l

(-OE).

See

“Host Bus Interface Pin M app ing ”

for summary. See th e re spe ct ive

AC Timing diagram for detailed functionality.

WE0# I 8

CS Hi-Z

This is a multi-purpose pin:

• For SH-3/SH-4 Bus, this pin inputs the write enable signal for the

lower data byte (WE0#).

• For MC68K Bus 1, this pin must be connected to V

DD

• For MC68K Bus 2, this pin inputs the bus size bit 0 (SIZ0).

• For Generic Bus, this pin inputs the write enable signal for the lower

data byte (WE0#).

• For MIPS/ISA Bus, this pin inputs the memory write signal

(MEMW#).

• For Philips PR31500/31700 Bus, this pin inputs the memory write

command (/WE).

• For Toshiba TX3912 Bus, this pi n i nputs the memory write command

(WE*).

• For PowerPC Bus, this pin inputs the Trans fer Size 1 signal (TSIZ1).

• For PC Card (PCMCIA) Bus, this pin inputs the write enable signal (WE).

See

“Host Bus Interface Pin M app ing ”

for summary. See th e re spe ct ive

AC Timing diagram for detailed functionality.

Table 5-1: Host Interface Pin Descriptions (Continued)

Pin Name T yp e Pin # Cell

RESET#

State

Description

Page 33

Page 28

Epson Research and Development

Vancouver Design Center

S1D13505 Hardware Functional Specification

X23A-A-001-14 Issue Date: 01/02/02

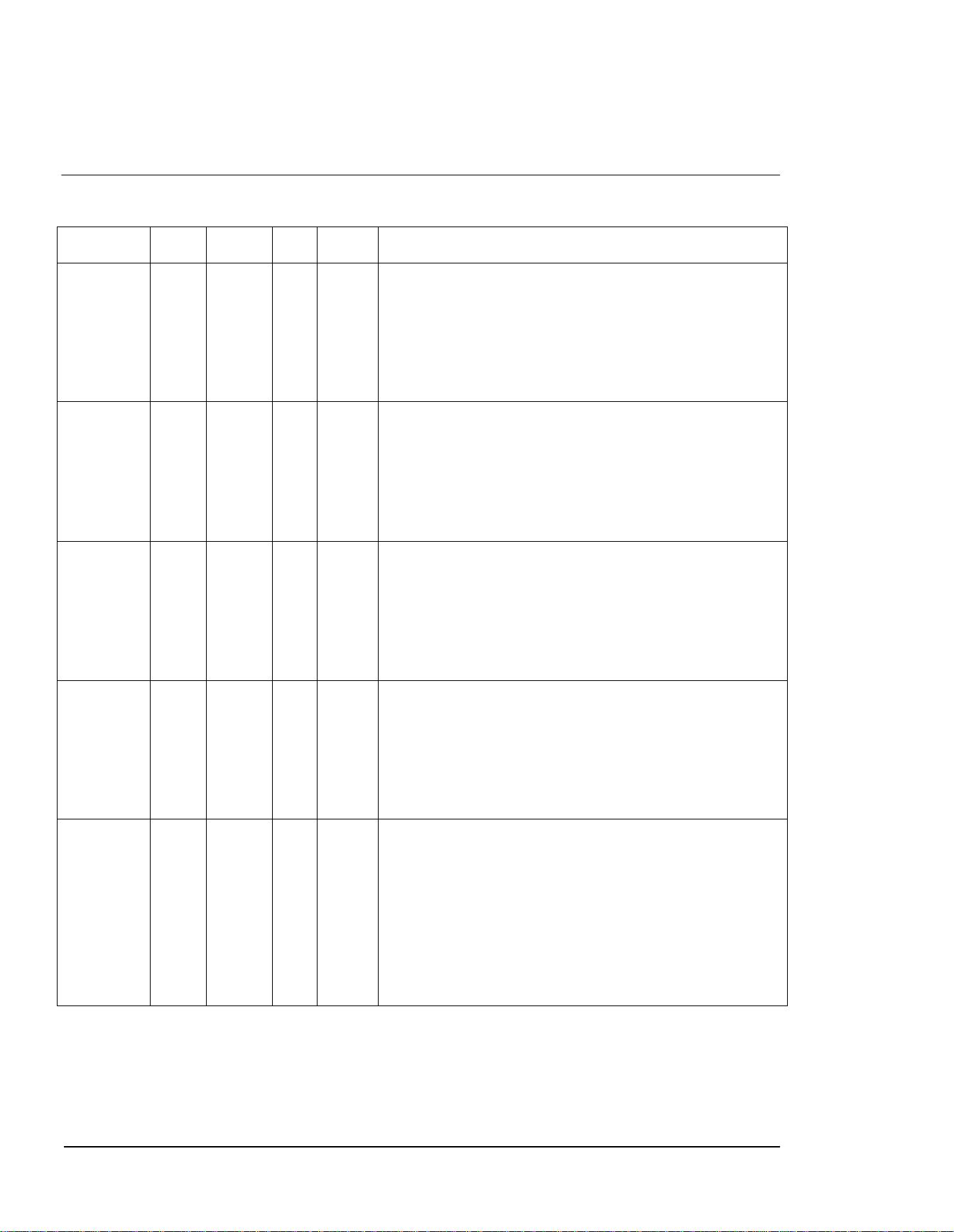

WAIT# O 15

TS2 Hi-Z

The active polarity of the WAIT # output is configurab le; the state of MD5

on the rising edge of RESET# defines the active pol arity of WAIT# - see

“Summary of Configuration Options”

.

• For SH-3 Bus, this pin o utputs the wait request signal (WAIT#); MD5

must be pulled low during reset by the internal pull-down resistor.

• For SH-4 Bus, this pin outputs th e ready sig nal (RDY#); MD5 must be

pulled high during reset by an external pull-up resistor.

• For MC68K Bus 1, this pin outputs the data transfer acknowledge