Page 1

MF1153-03

CMOS 4-BIT SINGLE CHIP MICROCOMPUTER

S1C63558

Technical Manual

S1C63558 Technical Hardware

Page 2

NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko

Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any

liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or

circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such

as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there

is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright

infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic

products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from

the Ministry of International Trade and Industry or other approval from another government agency.

© SEIKO EPSON CORPORATION 2001, All rights reserved.

Page 3

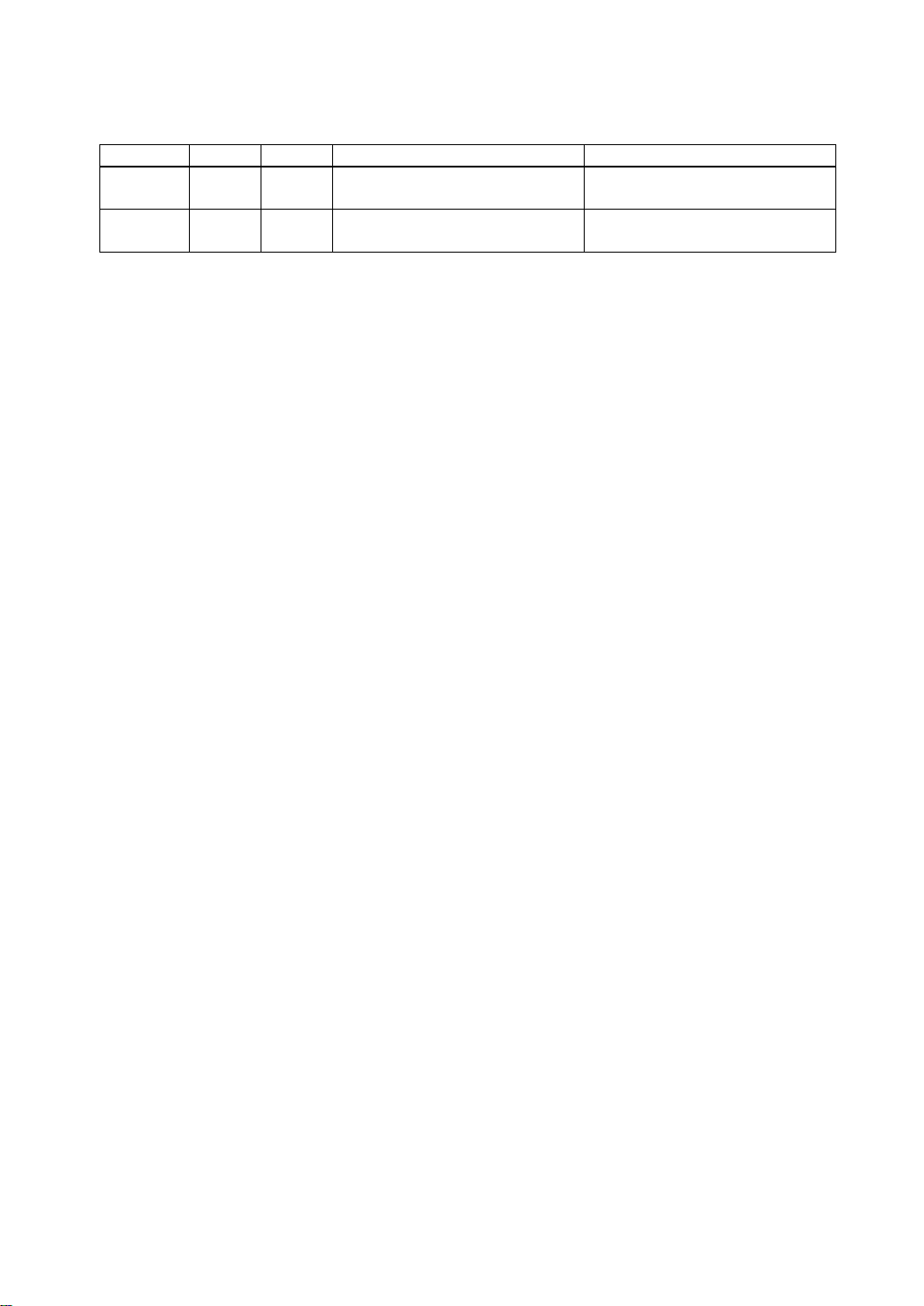

Revisions and Additions for this manual

Chapter

2

4

Section

2.1.2

4.7.3

Page

8

49

Item

Table 2.1.2.1 LCD drive voltage when

generated internally

Table 4.7.3.1 LCD drive voltage when

generated internally

Contents

The table was revised.

The table was revised.

Page 4

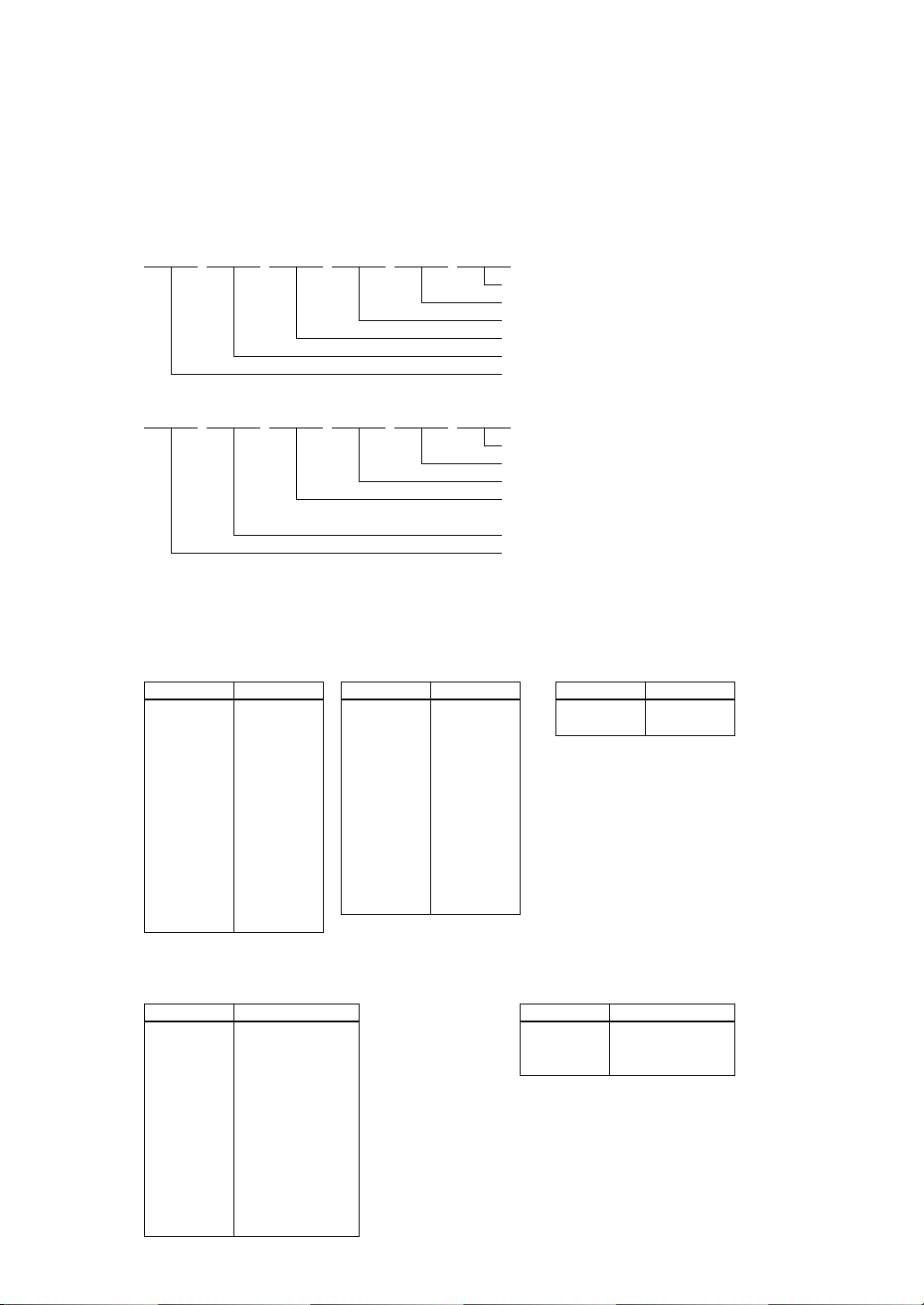

Page 5

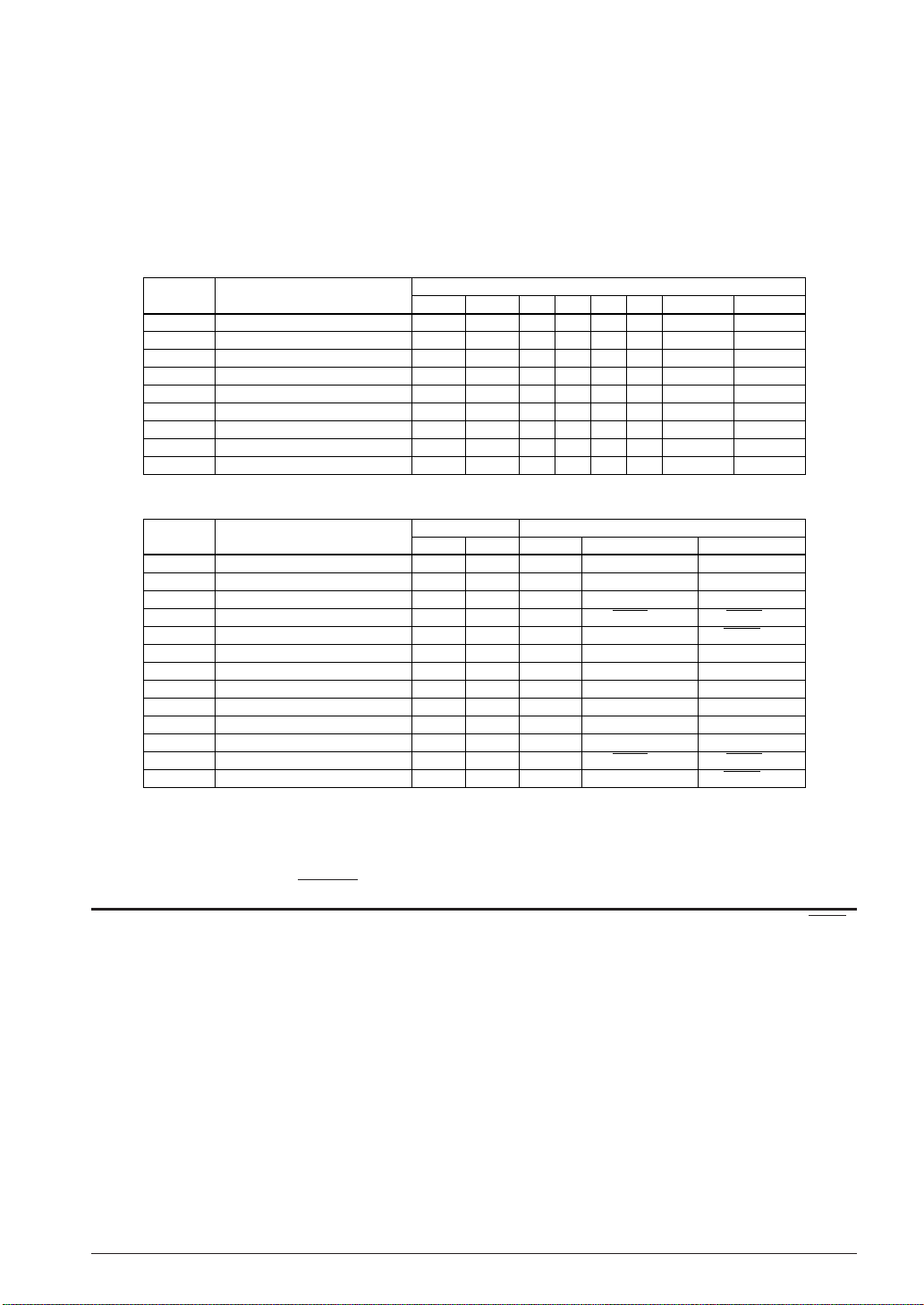

The information of the product number change

Starting April 1, 2001, the product number has been changed as listed below. Please use the new

product number when you place an order. For further information, please contact Epson sales

representative.

Configuration of product number

Devices

S1 C 63158 F 0A01

Development tools

S5U1

∗1: For details about tool types, see the tables below. (In some manuals, tool types are represented by one digit.)

∗2: Actual versions are not written in the manuals.

C 63000 A1 1

00

Packing specification

Specification

Package (D: die form; F: QFP)

Model number

Model name (C: microcomputer, digital products)

Product classification (S1: semiconductor)

00

Packing specification

Version (1: Version 1 ∗2)

Tool type (A1: Assembler Package ∗1)

Corresponding model number

(63000: common to S1C63 Family)

Tool classification (C: microcomputer use)

Product classification

(S5U1: development tool for semiconductor products)

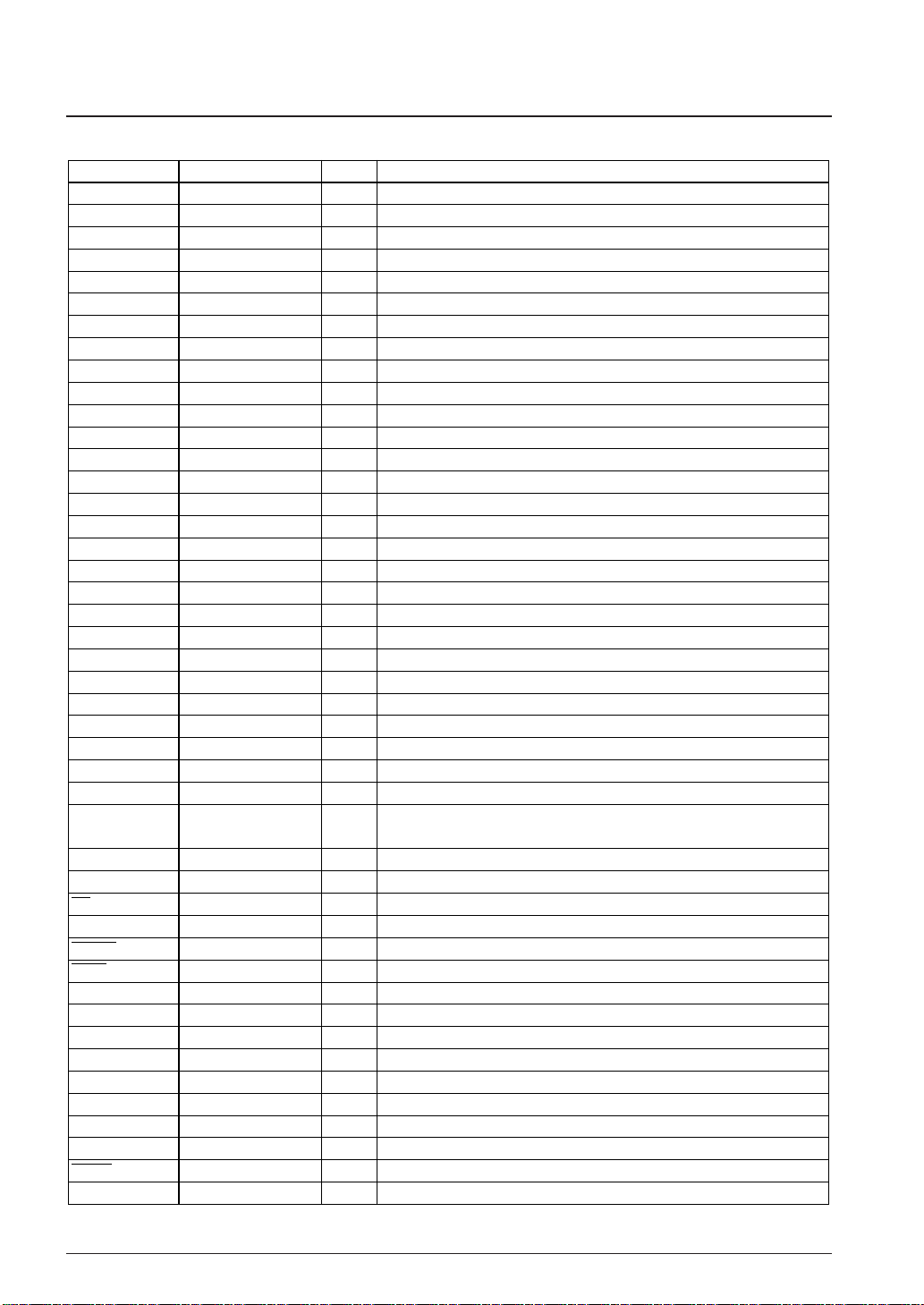

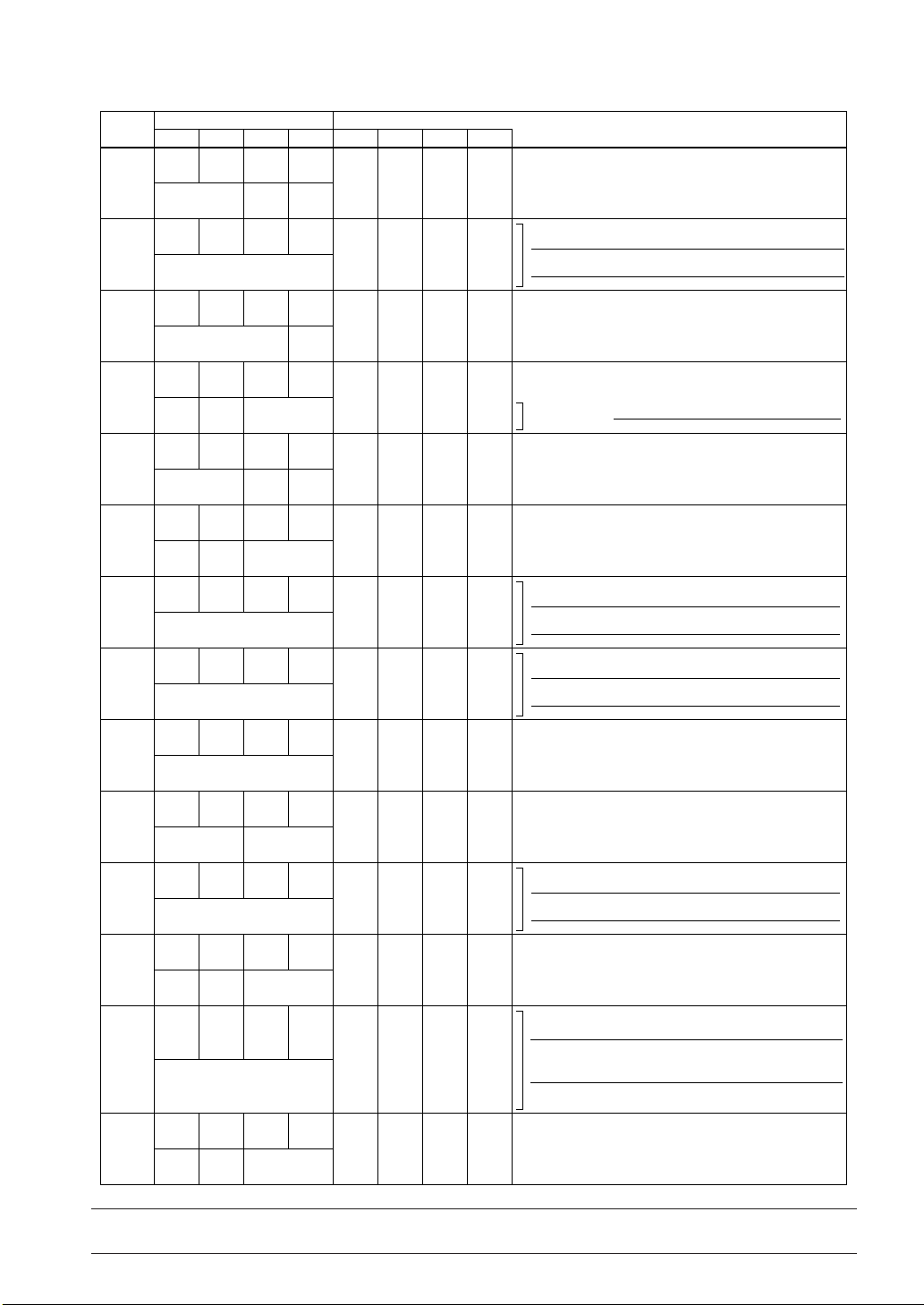

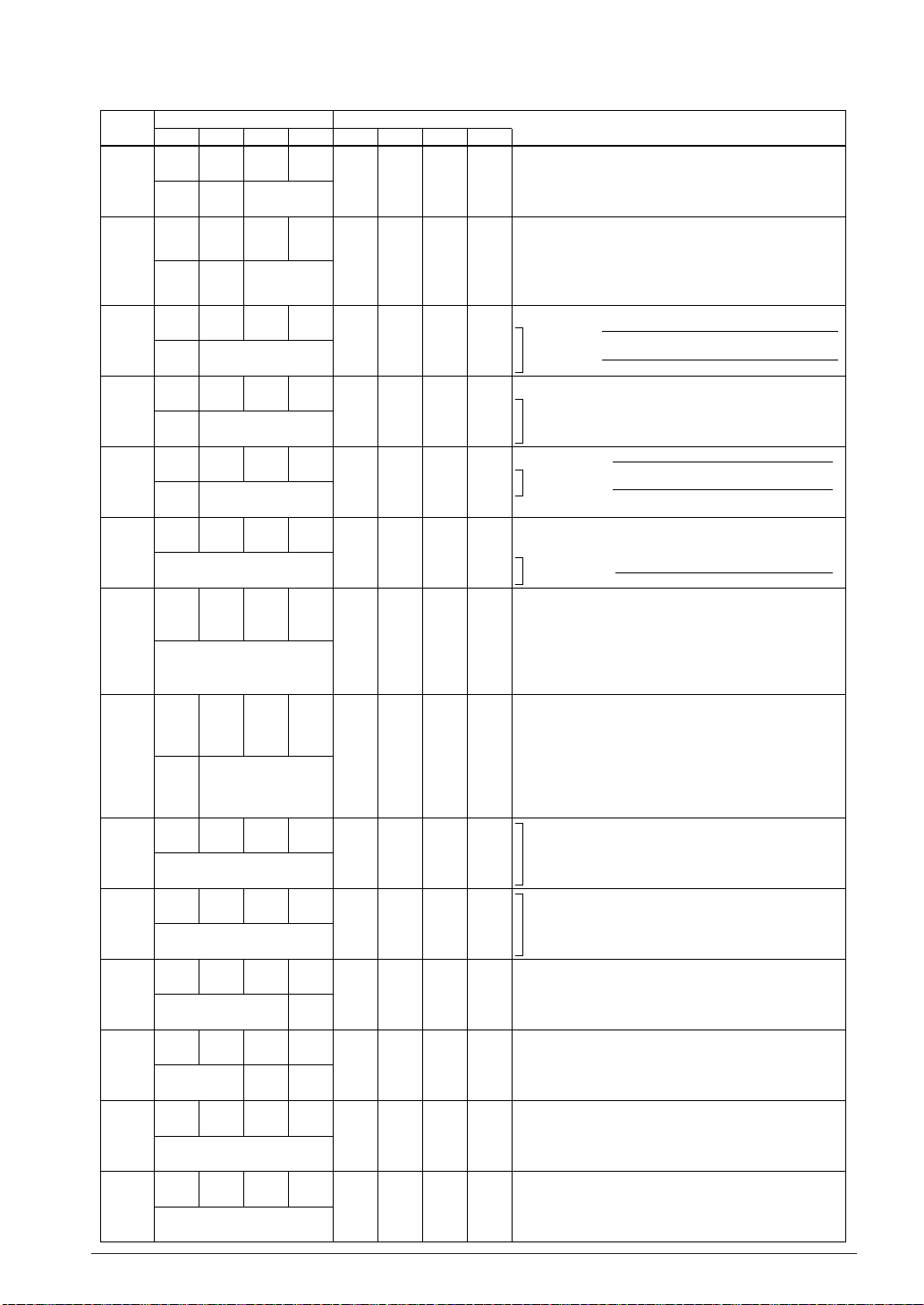

Comparison table between new and previous number

S1C63 Family processors

Previous No.

E0C63158

E0C63256

E0C63358

E0C63P366

E0C63404

E0C63406

E0C63408

E0C63F408

E0C63454

E0C63455

E0C63458

E0C63466

E0C63P466

New No.

S1C63158

S1C63256

S1C63358

S1C6P366

S1C63404

S1C63406

S1C63408

S1C6F408

S1C63454

S1C63455

S1C63458

S1C63466

S1C6P466

Previous No.

E0C63467

E0C63557

E0C63558

E0C63567

E0C63F567

E0C63658

E0C63666

E0C63F666

E0C63A08

E0C63B07

E0C63B08

E0C63B58

New No.

S1C63467

S1C63557

S1C63558

S1C63567

S1C6F567

S1C63658

S1C63666

S1C6F666

S1C63A08

S1C63B07

S1C63B08

S1C63B58

S1C63 Family peripheral products

Previous No.

E0C5250

E0C5251

New No.

S1C05250

S1C05251

Comparison table between new and previous number of development tools

Development tools for the S1C63 Family Development tools for the S1C63/88 Family

Previous No.

ADP63366

ADP63466

ASM63

GAM63001

ICE63

PRC63001

PRC63002

PRC63004

PRC63005

PRC63006

PRC63007

URS63366

New No.

S5U1C63366X

S5U1C63466X

S5U1C63000A

S5U1C63000G

S5U1C63000H1

S5U1C63001P

S5U1C63002P

S5U1C63004P

S5U1C63005P

S5U1C63006P

S5U1C63007P

S5U1C63366Y

Previous No.

ADS00002

GWH00002

URM00002

New No.

S5U1C88000X1

S5U1C88000W2

S5U1C88000W1

Page 6

Page 7

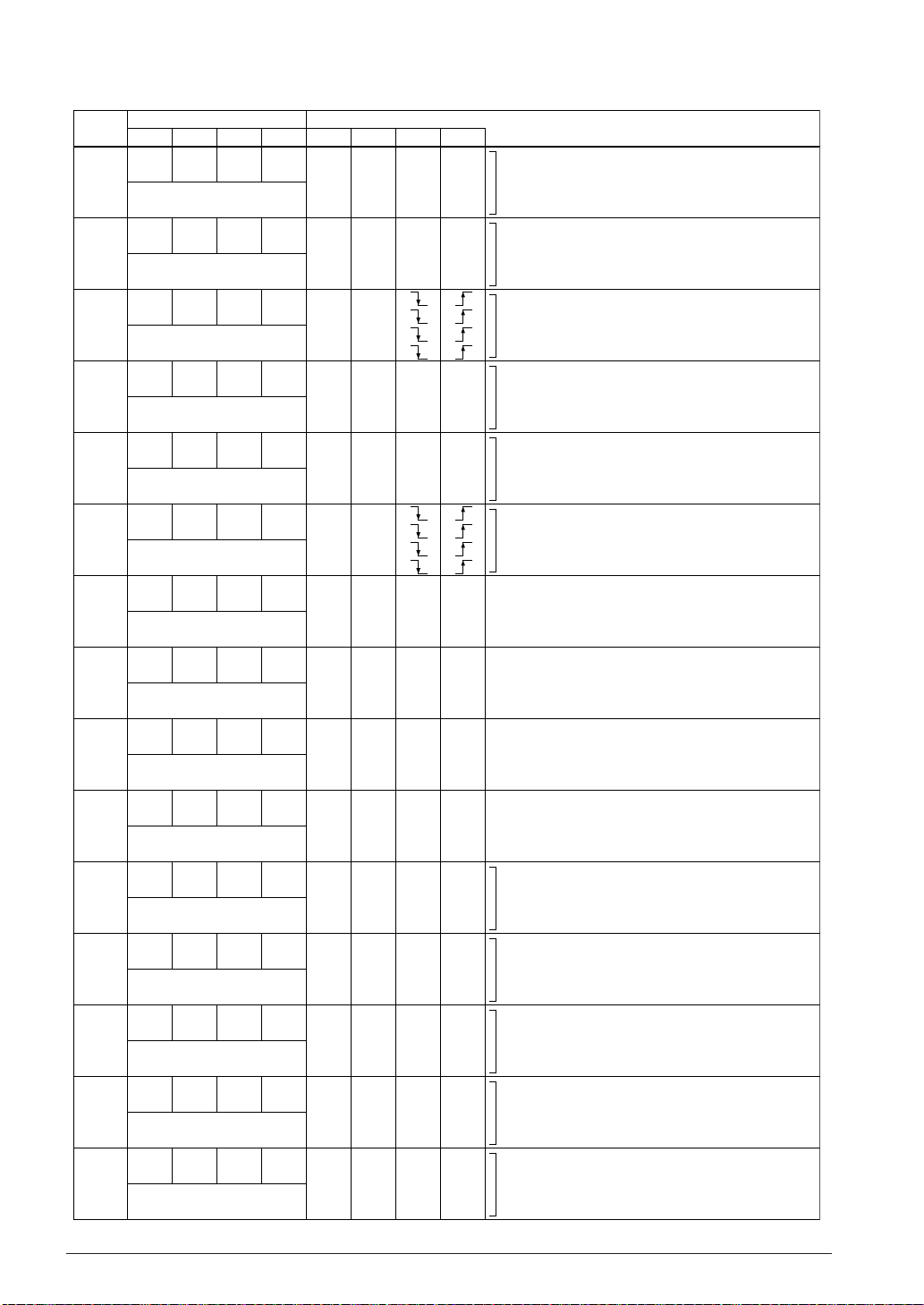

CONTENTS

CONTENTS

CHAPTER

1OUTLINE ________________________________________________ 1

1.1 Features ........................................................................................................ 1

1.2 Block Diagram ..............................................................................................2

1.3 Pin Layout Diagram ..................................................................................... 3

1.4 Pin Description .............................................................................................4

1.5 Mask Option.................................................................................................. 5

CHAPTER 2POWER SUPPLY AND INITIAL RESET ____________________________ 8

2.1 Power Supply ................................................................................................ 8

2.1.1 Voltage <VD1> for oscillation circuit and internal circuits...................... 8

2.1.2 Voltage <VC1–VC5> for LCD driving ........................................................ 8

2.2 Initial Reset ...................................................................................................9

2.2.1 Reset terminal (RESET) ............................................................................. 9

2.2.2 Simultaneous low input to terminals K00–K03 ........................................ 10

2.2.3 Internal register at initial resetting .......................................................... 10

2.2.4 Terminal settings at initial resetting ......................................................... 11

2.3 Test Terminal (TEST) ................................................................................... 11

CHAPTER 3 CPU, ROM, RAM________________________________________ 12

3.1 CPU..............................................................................................................12

3.2 Code ROM ................................................................................................... 12

3.3 RAM .............................................................................................................12

3.4 Data ROM .................................................................................................... 13

CHAPTER 4PERIPHERAL CIRCUITS AND OPERATION__________________________ 14

4.1 Memory Map................................................................................................ 14

4.2 Watchdog Timer ........................................................................................... 23

4.2.1 Configuration of watchdog timer.............................................................. 23

4.2.2 Interrupt function ...................................................................................... 23

4.2.3 I/O memory of watchdog timer ................................................................. 24

4.2.4 Programming notes................................................................................... 24

4.3 Oscillation Circuit ....................................................................................... 25

4.3.1 Configuration of oscillation circuit .......................................................... 25

4.3.2 OSC1 oscillation circuit............................................................................ 25

4.3.3 OSC3 oscillation circuit............................................................................ 26

4.3.4 Switching the CPU operating clock.......................................................... 26

4.3.5 Clock frequency and instruction execution time ...................................... 26

4.3.6 I/O memory of oscillation circuit.............................................................. 27

4.3.7 Programming notes................................................................................... 27

4.4 Input Ports (K00–K03 and K10–K13).........................................................28

4.4.1 Configuration of input ports ..................................................................... 28

4.4.2 Interrupt function ...................................................................................... 28

4.4.3 Mask option ............................................................................................... 29

4.4.4 I/O memory of input ports......................................................................... 30

4.4.5 Programming notes................................................................................... 32

4.5 Output Ports (R00–R03, R10–R13 and R20–R23)...................................... 33

4.5.1 Configuration of output ports ................................................................... 33

4.5.2 Mask option ............................................................................................... 33

S1C63558 TECHNICAL MANUAL EPSON i

Page 8

CONTENTS

4.5.3 High impedance control............................................................................ 34

4.5.4 Special output ............................................................................................ 34

4.5.5 I/O memory of output ports....................................................................... 37

4.5.6 Programming notes................................................................................... 40

4.6 I/O Ports (P00–P03, P10–P13, P20–P23 and P30–P33) .......................... 41

4.6.1 Configuration of I/O ports ........................................................................ 41

4.6.2 Mask option ............................................................................................... 42

4.6.3 I/O control registers and input/output mode ............................................ 42

4.6.4 Pull-up during input mode ........................................................................ 42

4.6.5 Special outputs (CL, FR)........................................................................... 43

4.6.6 I/O memory of I/O ports............................................................................ 44

4.6.7 Programming notes................................................................................... 48

4.7 LCD Driver (COM0–COM16, SEG0–SEG39) ........................................... 49

4.7.1 Configuration of LCD driver .................................................................... 49

4.7.2 Mask option ............................................................................................... 49

4.7.3 Power supply for LCD driving.................................................................. 49

4.7.4 LCD display control (ON/OFF) and switching of duty............................ 49

4.7.5 Display memory......................................................................................... 51

4.7.6 LCD contrast adjustment .......................................................................... 53

4.7.7 I/O memory of LCD driver........................................................................ 54

4.7.8 Programming notes................................................................................... 56

4.8 Clock Timer.................................................................................................. 57

4.8.1 Configuration of clock timer..................................................................... 57

4.8.2 Data reading and hold function................................................................ 57

4.8.3 Interrupt function ...................................................................................... 58

4.8.4 I/O memory of clock timer ........................................................................ 59

4.8.5 Programming notes................................................................................... 60

4.9 Stopwatch T imer .......................................................................................... 61

4.9.1 Configuration of stopwatch timer ............................................................. 61

4.9.2 Count-up pattern ....................................................................................... 61

4.9.3 Interrupt function ...................................................................................... 62

4.9.4 I/O memory of stopwatch timer ................................................................ 63

4.9.5 Programming notes................................................................................... 64

4.10 Programmable Timer................................................................................... 65

4.10.1 Configuration of programmable timer ................................................... 65

4.10.2 Setting of initial value and counting down ............................................. 66

4.10.3 Counter mode .......................................................................................... 67

4.10.4 Setting of input clock in timer mode ....................................................... 68

4.10.5 Interrupt function .................................................................................... 69

4.10.6 Setting of TOUT output ........................................................................... 69

4.10.7 Transfer rate setting for serial interface ................................................ 70

4.10.8 I/O memory of programmable timer....................................................... 71

4.10.9 Programming notes................................................................................. 76

4.11 Serial Interface ............................................................................................77

4.11.1 Configuration of serial interface ............................................................ 77

4.11.2 Mask option ............................................................................................. 78

4.11.3 Transfer modes ........................................................................................ 78

4.11.4 Clock source ............................................................................................ 80

4.11.5 Transmit-receive control ......................................................................... 81

4.11.6 Operation of clock synchronous transfer................................................ 82

4.11.7 Operation of asynchronous transfer ....................................................... 86

4.11.8 Interrupt function .................................................................................... 90

4.11.9 I/O memory of serial interface ................................................................ 92

4.11.10 Programming notes ............................................................................... 99

4.12 Sound Generator......................................................................................... 100

4.12.1 Configuration of sound generator ......................................................... 100

4.12.2 Buzzer output circuit .............................................................................. 100

ii EPSON S1C63558 TECHNICAL MANUAL

Page 9

CONTENTS

4.12.3 Control of buzzer output......................................................................... 101

4.12.4 Setting of buzzer frequency and sound level.......................................... 102

4.12.5 Digital envelope ..................................................................................... 103

4.12.6 One-shot output ...................................................................................... 104

4.12.7 I/O memory of sound generator............................................................. 105

4.12.8 Programming notes................................................................................ 108

4.13 SVD (Supply Voltage Detection) Circuit .................................................... 109

4.13.1 Configuration of SVD circuit ................................................................. 109

4.13.2 Mask option ............................................................................................ 109

4.13.3 SVD operation ........................................................................................ 109

4.13.4 I/O memory of SVD circuit..................................................................... 110

4.13.5 Programming notes................................................................................ 111

4.14 Telephone Function (Tone/Pulse Dialer) ................................................... 112

4.14.1 Configuration of tone/pulse dialer ........................................................ 112

4.14.2 Mask option ............................................................................................ 113

4.14.3 Operation of telephone function ............................................................ 113

4.14.4 Tone mode (DTMF) ................................................................................ 116

4.14.5 Pulse mode (DP) .................................................................................... 119

4.14.6 Pause ...................................................................................................... 122

4.14.7 Flash ....................................................................................................... 124

4.14.8 Hold-line................................................................................................. 125

4.14.9 Interrupt.................................................................................................. 126

4.14.10 I/O memory of telephone function ....................................................... 127

4.14.11 Programming notes .............................................................................. 135

4.15 FSK Demodulator .......................................................................................136

4.15.1 Configuration of FSK demodulator ....................................................... 136

4.15.2 Mask option ............................................................................................ 138

4.15.3 Ring/carrier detection and interrupt ..................................................... 139

4.15.4 Inputting FSK data ................................................................................. 140

4.15.5 I/O memory of FSK demodulator .......................................................... 142

4.15.6 Programming notes................................................................................ 144

4.16 Interrupt and HALT .................................................................................... 145

4.16.1 Interrupt factor....................................................................................... 147

4.16.2 Interrupt mask ........................................................................................ 148

4.16.3 Interrupt vector ...................................................................................... 148

4.16.4 I/O memory of interrupt ......................................................................... 149

4.16.5 Programming notes................................................................................ 151

CHAPTER 5SUMMARY OF NOTES ______________________________________ 152

5.1 Notes for Low Current Consumption.......................................................... 152

5.2 Summary of Notes by Function...................................................................153

5.3 Precautions on Mounting ........................................................................... 157

CHAPTER 6BASIC EXTERNAL WIRING DIAGRAM ___________________________ 159

CHAPTER 7ELECTRICAL CHARACTERISTICS _______________________________ 160

7.1 Absolute Maximum Rating..........................................................................160

7.2 Recommended Operating Conditions......................................................... 160

7.3 DC Characteristics ..................................................................................... 161

7.4 Analog Circuit Characteristics and Power Current Consumption............ 162

7.5 Oscillation Characteristics......................................................................... 163

7.6 Serial Interface (1), (2) AC Characteristics...............................................164

7.7 FSK Demodulator Characteristics .............................................................165

S1C63558 TECHNICAL MANUAL EPSON iii

Page 10

CONTENTS

7.8 Telephone Function Characteristics...........................................................166

7.9 Timing Chart............................................................................................... 166

7.10 Characteristic Curves (reference value) .................................................... 167

CHAPTER 8PACKAGE _______________________________________________ 169

8.1 Plastic Package...........................................................................................169

8.2 Ceramic Package for Test Samples ............................................................170

CHAPTER 9PAD LAYOUT ____________________________________________ 171

9.1 Diagram of Pad Layout .............................................................................. 171

9.2 Pad Coordinates ......................................................................................... 172

iv EPSON S1C63558 TECHNICAL MANUAL

Page 11

CHAPTER 1: OUTLINE

CHAPTER 1OUTLINE

The S1C63558 is a microcomputer which has a high-performance 4-bit CPU S1C63000 as the core

CPU, ROM (8,192 words × 13 bits), RAM (5,120 words × 4 bits), serial interface, watchdog timer, programmable timer, time base counters (2 systems), SVD circuit, a dot-matrix LCD driver that can drive a

maximum 40 segments × 17 commons, DTMF/DP generator, FSK demodulator and sound generator

built-in. The S1C63558 features high speed operation and low current consumption in an operating

voltage range (2.2 V to 5.5 V), this makes it suitable for applications working with batteries. It is also

suitable for caller ID and portable data bank systems because it has a large capacity of RAM built-in.

1.1 Features

OSC1 oscillation circuit ......................

OSC3 oscillation circuit ...................... 3.58 MHz (Typ.) ceramic oscillation circuit

Instruction set ..................................... Basic instruction: 46 types (411 instructions with all)

Instruction execution time................... During operation at 32.768 kHz: 61 µsec 122 µsec 183 µsec

ROM capacity ..................................... Code ROM: 8,192 words × 13 bits

RAM capacity...................................... Data memory: 5,120 words × 4 bits

Input port............................................. 8 bits (Pull-up resistors may be supplemented ∗1)

Output port .......................................... 12 bits (It is possible to switch the 8 bits to special output ∗2)

I/O port ................................................ 16 bits (It is possible to switch the 2 bits to special output and

Serial interface .................................... 2 ch.

LCD driver...........................................

Time base counter .............................. 2 systems (Clock timer, stopwatch timer)

Programmable timer ........................... Built-in, 2 inputs × 8 bits, with event counter function

Watchdog timer................................... Built-in

DTMF generator ................................. Built-in

DP generator ...................................... Built-in

FSK demodulator ................................ Built-in (Compatible with ITU-T V.23/Bell 202)

Sound generator ................................. With envelope and 1-shot output functions

Supply voltage detection (SVD) circuit ..

External interrupt ................................ Input port interrupt: 2 systems

Internal interrupt ................................. Clock timer interrupt: 4 systems

Power supply voltage ......................... 2.2 V to 5.5 V

Operating temperature range ............. -20°C to 70°C

Current consumption (Typ.) ................ Low-speed operation (OSC1: crystal oscillation):

Package .............................................. QFP15-128pin (plastic) or chip

32.768 kHz (Typ.) crystal oscillation circuit

Addressing mode: 8 types

During operation at 3.58 MHz: 0.56 µsec 1.12 µsec 1.68 µsec

Data ROM: 2,048 words × 4 bits (= 8K bits)

Display memory: 816 bits (192 words × 4 bits + 48 × 1 bit)

the 4 bits to serial I/F input/output ∗2)

(8-bit clock synchronous or asynchronous system is selectable)

40 segments × 8, 16 or 17 commons (∗2)/48 segments × 8 commons (∗1)

12 values, programmable (2.20 V to 3.30 V)

(It is possible to switch 1 value to the external voltage detection ∗1)

Stopwatch timer interrupt: 2 systems

Programmable timer interrupt: 2 systems

Serial interface interrupt: 6 systems

Dialer interrupt: 1 system

FSK interrupt: 2 systems

During HALT (32 kHz) 3.0 V (LCD power OFF) 1.5 µA

3.0 V (LCD power ON) 4 µA

During operation (32 kHz) 3.0 V (LCD power ON) 10 µA

High-speed operation (OSC3: ceramic oscillation):

During operation (3.58 MHz) 3.0 V (LCD power ON) 600 µA

During FSK operation 5.5 V (LCD power ON) 1,800 µA

∗1: Can be selected with mask option ∗2: Can be selected with software

S1C63558 TECHNICAL MANUAL EPSON 1

Page 12

CHAPTER 1: OUTLINE

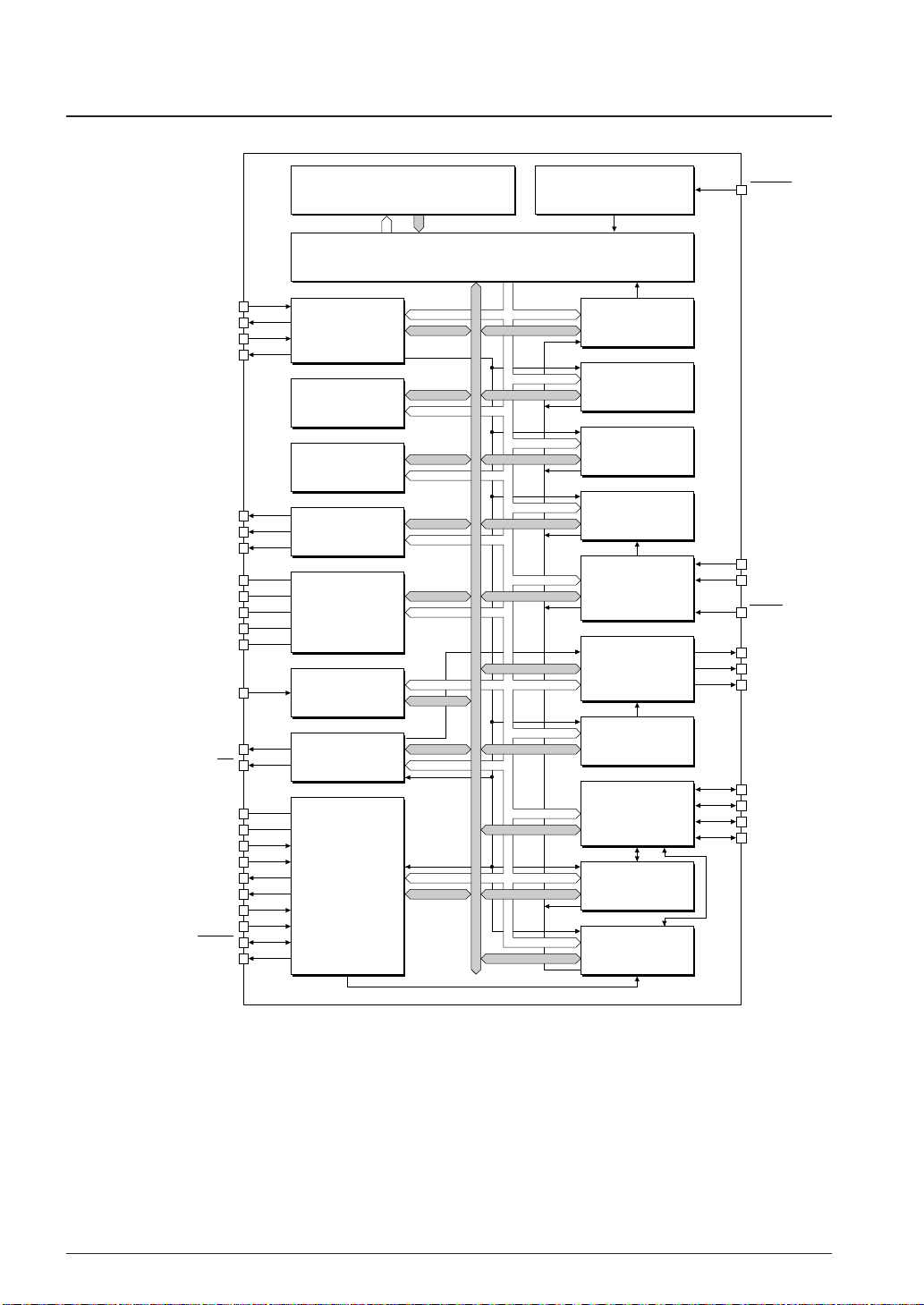

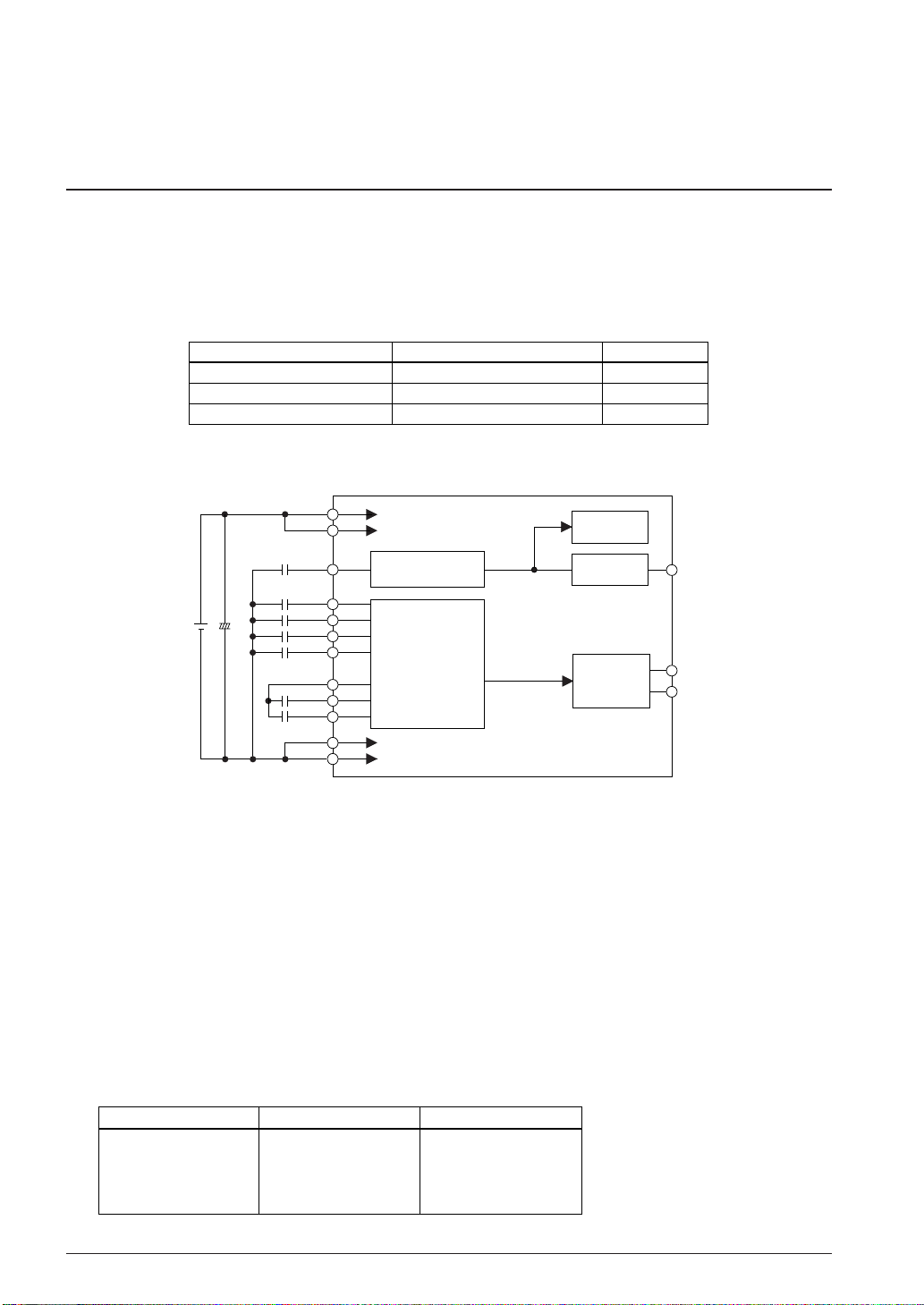

1.2 Block Diagram

OSC1

OSC2

OSC3

OSC4

COM0–7

SEG0–39

(SEG47–40∗1) COM8–16

VDD

VC1–5

CA–CC

VD1

VSS

SVD

ROM

8,192 words × 13 bits

OSC

RAM

5,120 words × 4 bits

Data ROM

2,048 words × 4 bits

LCD Driver

40 SEG × 17 COM

Power

Controller

SVD

System Reset

Core CPU S1C63000

Control

Interrupt

Generator

Stopwatch

Timer

Clock

Timer

Programmable

Timer/Counter

Input Port

Output Port

RESET

K00–K03

K10–K13

TEST

R00–R03

R10–R13

R20–R23

TONE

DP

AVDD

AVSS

TIP

RING

FB

BPOUT

CDIN

RDIN

RDRC

VREF

Telephone

Function

Demodulator

∗1: Mask option

FSK

Fig. 1.2.1 Block diagram

Sound

Generator

I/O Port

Serial

Interface (1)

Serial

Interface (2)

P00–P03

P10–P13

P20–P23

P30–P33

2 EPSON S1C63558 TECHNICAL MANUAL

Page 13

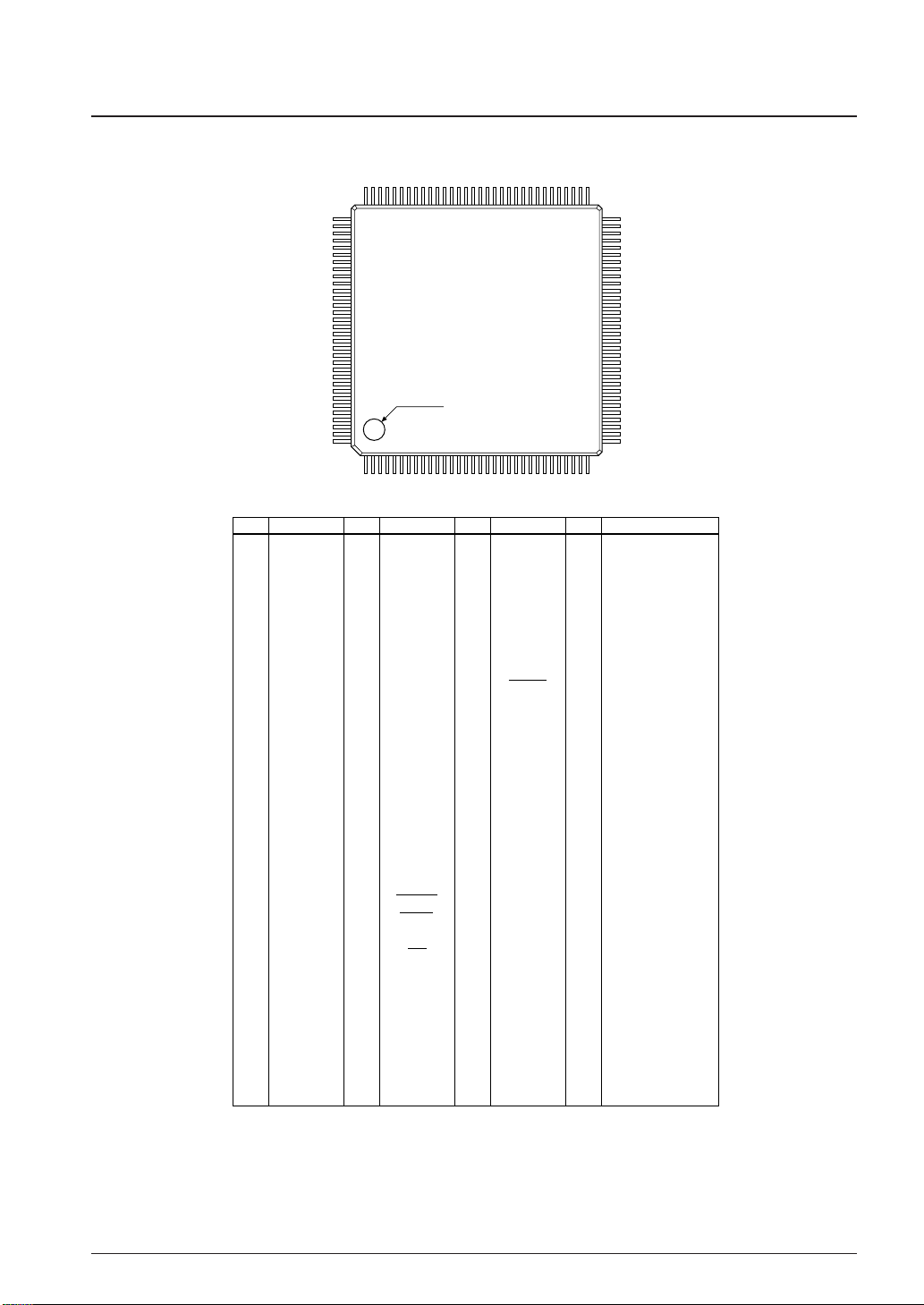

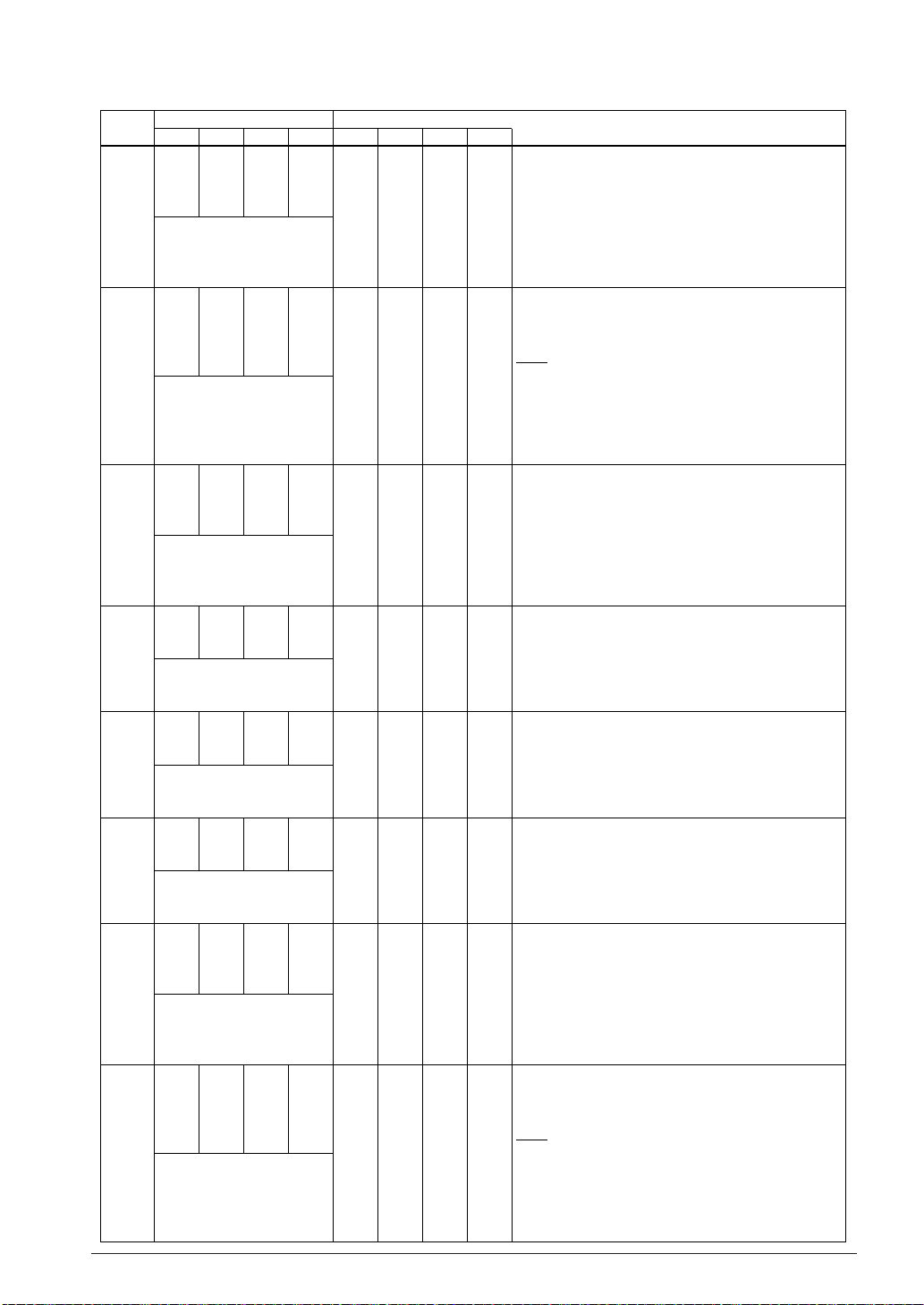

1.3 Pin Layout Diagram

QFP15-128pin

CHAPTER 1: OUTLINE

6596

No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

97

128

Pin name

N.C.

SEG34

SEG33

SEG32

SEG31

SEG30

SEG29

SEG28

SEG27

SEG26

SEG25

SEG24

SEG23

SEG22

SEG21

SEG20

SEG19

SEG18

SEG17

SEG16

SEG15

SEG14

SEG13

SEG12

SEG11

SEG10

SEG9

SEG8

SEG7

SEG6

SEG5

N.C.

S1C63558

INDEX

No.

Pin name

33

SEG4

34

SEG3

35

SEG2

36

SEG1

37

SEG0

38

COM7

39

COM6

40

COM5

41

COM4

42

COM3

43

COM2

44

COM1

45

COM0

46

VSS

47

OSC1

48

OSC2

49

VD1

50

OSC3

51

OSC4

52

VDD

53

RESET

54

TEST

55

TONE

56

57

R23

58

R22

59

R21

60

R20

61

R13

62

R12

63

R11

64

N.C.

Fig. 1.3.1 Pin layout diagram

DP

No.

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

Pin name

BPOUT

RDRC

N.C.

R10

R03

R02

R01

R00

CDIN

RDIN

VREF

AVSS

FB

RING

TIP

AVDD

P33

P32

P31

P30

P23

P22

P21

P20

P13

P12

P11

P10

P03

P02

P01

N.C.

321

No.

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

COM8/SEG47

116

COM9/SEG47

117

COM10/SEG46

118

COM11/SEG45

119

COM12/SEG44

120

COM13/SEG43

121

COM14/SEG42

122

COM15/SEG41

123

COM16/SEG40

124

125

126

127

128

N.C. : No Connection∗1: Mask option

64

33

Pin name

N.C.

P00

K13

K12

K11

K10

K03

K02

K01

K00

SVD

VC1

VC23

VC4

VC5

CC

CB

CA

∗1

∗1

∗1

∗1

∗1

∗1

∗1

∗1

∗1

SEG39

SEG38

SEG37

SEG36

SEG35

S1C63558 TECHNICAL MANUAL EPSON 3

Page 14

CHAPTER 1: OUTLINE

1.4 Pin Description

Pin name

V

DD

V

SS

V

D1

VC1–V

C5

CA–CC

OSC1

OSC2

OSC3

OSC4

K00–K03

K10–K13

P00–P03

P10–P13

P20

P21

P22

P23

P30–P33

R00

R01

R02

R03

R10

R11

R12

R13

R20–R23

COM0–COM7

COM8–COM16

(SEG47–SEG40)

SEG0–SEG39

SVD

DP

TONE

RESET

TEST

AV

DD

AV

SS

RDIN

TIP

RING

FB

BPOUT

CDIN

RDRC

V

REF

Pin No.

52

46

49

108–111

114–112

47

48

50

51

106–103

102–99

98, 95–93

92–89

88

87

86

85

84–81

70

69

68

67

66

63

62

61

60–57

45–38

115–123

37–33, 31–2, 128–124

107

56

55

53

54

80

76

74

79

78

77

72

71

73

75

Table 1.4.1 Pin description

I/O

Power (+) supply pin

–

Power (–) supply pin

–

Oscillation system regulated voltage output pin

–

LCD system power supply pin (1/4 bias generated internally)

–

LCD system boosting/reducing capacitor connecting pin

–

Crystal oscillation input pin

I

Crystal oscillation output pin

O

Ceramic oscillation input pin

I

Ceramic oscillation output pin

O

Input port

I

Input port

I

I/O port

I/O

I/O port (switching to serial I/F (1) input/output is possible by software)

I/O

I/O port

I/O

I/O port

I/O

I/O port (switching to CL signal output is possible by software)

I/O

I/O port (switching to FR signal output is possible by software)

I/O

I/O port (switching to serial I/F (2) input/output is possible by software)

I/O

Output port (switching to XBZ signal output is possible by software)

O

Output port (switching to BZ signal output is possible by software)

O

Output port (switching to TOUT signal output is possible by software)

O

Output port (switching to FOUT signal output is possible by software)

O

Output port (switching to XTMUTE signal output is possible by software)

O

Output port (switching to XRMUTE signal output is possible by software)

O

Output port (switching to HDO signal output is possible by software)

O

Output port (switching to HFO signal output is possible by software)

O

Output port

O

LCD common output pin (1/8, 1/16, 1/17 duty can be selected by software)

O

LCD common output pin

O

or LCD segment output pin (mask option)

LCD segment output pin

O

SVD external voltage input pin

I

Dial pulse output pin

O

DTMF output pin

O

Initial reset input pin

I

Testing input pin

I

Power (+) supply pin for FSK demodulator

–

Power (-) supply pin for FSK demodulator

–

Ring detection input pin

I

TIP input pin

I

RING input pin

I

Input amplifier output pin

O

Band-pass filter output pin

O

Carrier detection input pin

I

I/O pin for connecting RC network

I/O

Reference voltage output pin (1/2 V

O

Function

DD

)

4 EPSON S1C63558 TECHNICAL MANUAL

Page 15

CHAPTER 1: OUTLINE

1.5 Mask Option

Mask options shown below are provided for the S1C63558. Several hardware specifications are prepared

in each mask option, and one of them can be selected according to the application. The function option

generator FOG63558, that has been prepared as the development software tool of S1C63558, is used for

this selection. Mask pattern of the IC is finally generated based on the data created by the FOG63558.

Refer to the "S5U1C63558D Manual" for the FOG63558.

<Functions selectable with S1C63558 mask options>

(1) External reset by simultaneous LOW input to the input port (K00–K03)

This function resets the IC when several keys are pressed simultaneously. The mask option is used to

select whether this function is used or not. Further when the function is used, a combination of the

input ports (K00–K03), which are connected to the keys to be pressed simultaneously, can be selected.

Refer to Section 2.2.2, "Simultaneous low input to terminals K00–K03", for details.

(2) Time authorize circuit for the simultaneous LOW input reset function

When using the external reset function (shown in 1 above), using the time authorize circuit or not can

be selected by the mask option. The reset function works only when the input time of simultaneous

LOW is more than the rule time if the time authorize circuit is being used.

Refer to Section 2.2.2, "Simultaneous low input to terminals K00–K03", for details.

(3) Input port pull-up resistor

The mask option is used to select whether the pull-up resistor is supplemented to the input ports or

not. It is possible to select for each bit of the input ports.

Refer to Section 4.4.3, "Mask option", for details.

(4) Output specification of the output port

Either complementary output or N-channel open drain output can be selected as the output specification for the output ports. The selection is done in 1-bit units.

Refer to Section 4.5.2, "Mask option", for details.

(5) Output specification / pull-up resistor of the I/O ports

Either complementary output or N-channel open drain output can be selected as the output specification when the I/O ports are in the output mode. The selection is done in 1-bit units.

Further, whether or not the pull-up resistors working in the input mode are supplemented can be

selected. The selection is done in 1-bit units or 4-bit units depending on the I/O port.

1-bit unit: P20, P21, P22, P23

4-bit unit: P00–P03, P10–P13, P30–P33

Refer to Section 4.6.2, "Mask option", for details.

(6) Configuration of the LCD segment

The COM8–COM16 terminals allow selection of terminal specification between COM outputs and

SEG45–SEG40 outputs.

Refer to Section 4.7.2, "Mask option", for details.

(7) External voltage detection of SVD circuit

External voltage (SVD terminal–V

(V

DD terminal–VSS terminal) detection. The SVD terminal is used to input the external voltage to be

SS terminal) detection can be selected in addition to supply voltage

detected.

Refer to Section 4.13.2, "Mask option", for details.

S1C63558 TECHNICAL MANUAL EPSON 5

Page 16

CHAPTER 1: OUTLINE

(8) Output specification of the DP terminal

Either complementary output or N-channel open drain output can be selected as the output specification for the DP (dial pulse output) terminal.

Refer to Section 4.14.2, "Mask option", for details.

(9) Gain of FSK demodulator input amplifier

The gain of the FSK demodulator input amplifier can be either fixed at 1 using the internal feedback

resistor or varied using external resistors.

Refer to Section 4.15.2, "Mask option", for details.

(10)Output specification of other special output terminals

The following special output terminals are shared with the output (R) terminals or the I/O (P)

terminals. Consequently, the output specification (complementary output or N-channel open drain

output) of the shared terminal applies to the special output.

Special output signal Shared port

XBZ, BZ, TOUT, FOUT Output ports R00–R03

XRMUTE, XTMUTE, HDO, HFO Output ports R10–R13

Serial interface input/output I/O ports P10–P13

CL, FR I/O ports P22, P23

<Mask option list>

The following is the option list for the S1C63558. Multiple selections are available in each option item as

indicated in the option list. Refer to Chapter 4, "Peripheral Circuits and Operation", to select the specifications that meet the application system. Be sure to select the specifications for unused functions too,

according to the instruction provided. Use fog63558 in the S5U1C63000A package for this selection. Refer

to the "S5U1C63558D Manual" for details.

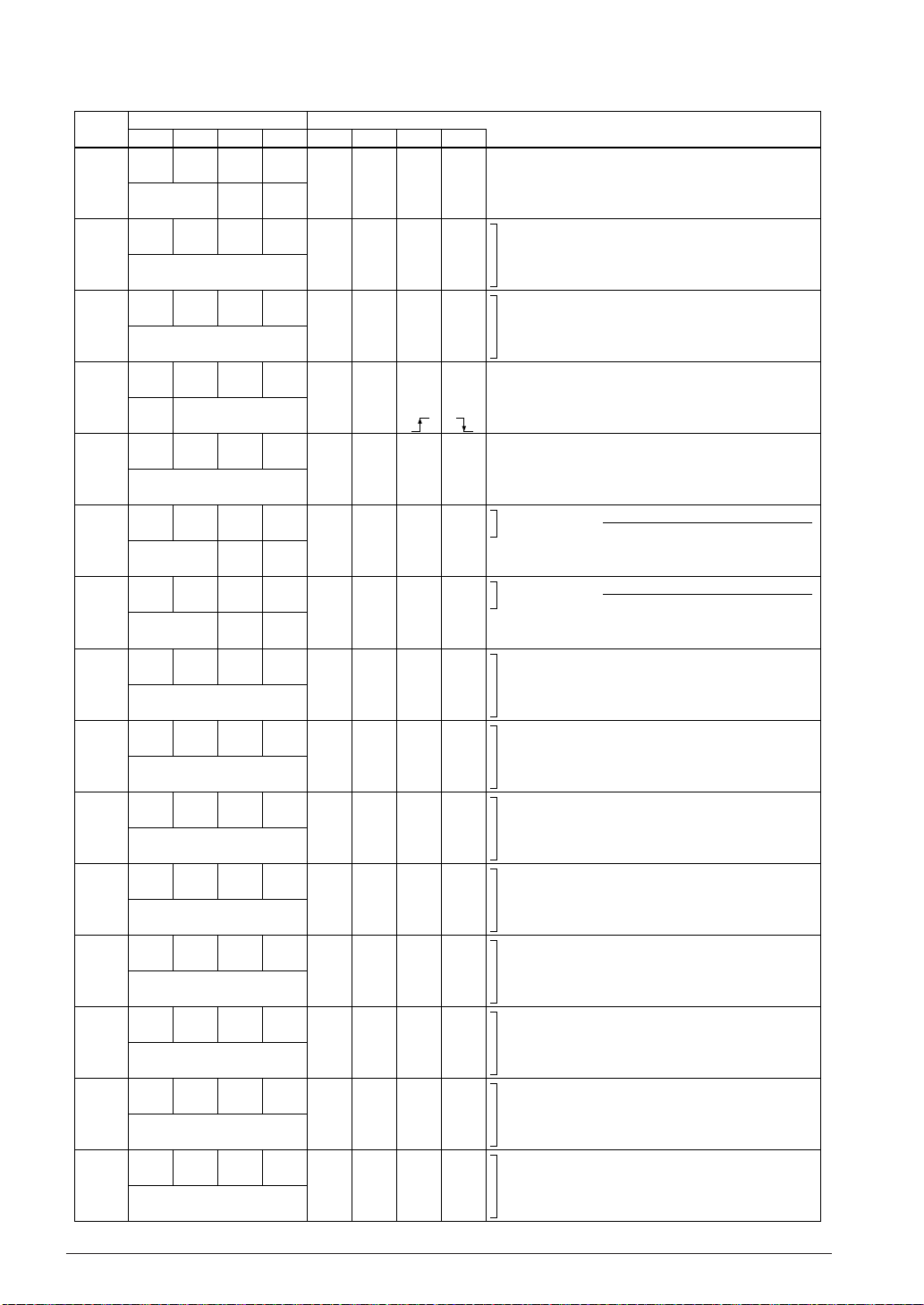

1. MULTIPLE KEY ENTRY RESET COMBINATION

■■ 1. Not Use

■■ 2. Use <K00, K01, K02, K03>

■■ 3. Use <K00, K01, K02>

■■ 4. Use <K00, K01>

2. MULTIPLE KEY ENTRY RESET TIME AUTHORIZE

■■ 1. Not Use

■■ 2. Use

3. INPUT PORT PULL UP RESISTOR

• K00 ■■ 1. With Resistor ■■ 2. Gate Direct

• K01 ■■ 1. With Resistor ■■ 2. Gate Direct

• K02 ■■ 1. With Resistor ■■ 2. Gate Direct

• K03 ■■ 1. With Resistor ■■ 2. Gate Direct

• K10 ■■ 1. With Resistor ■■ 2. Gate Direct

• K11 ■■ 1. With Resistor ■■ 2. Gate Direct

• K12 ■■ 1. With Resistor ■■ 2. Gate Direct

• K13 ■■ 1. With Resistor ■■ 2. Gate Direct

4. OUTPUT PORT OUTPUT SPECIFICATION

• R00 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• R01 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• R02 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• R03 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• R10 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• R11 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• R12 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• R13 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• R20 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• R21 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• R22 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• R23 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

6 EPSON S1C63558 TECHNICAL MANUAL

Page 17

5. I/O PORT OUTPUT SPECIFICATION

• P00 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• P01 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• P02 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• P03 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• P10 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• P11 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• P12 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• P13 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• P20 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• P21 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• P22 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• P23 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• P30 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• P31 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• P32 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

• P33 ■■ 1. Complementary ■■ 2. Nch-OpenDrain

6. I/O PORT PULL UP RESISTOR

• P0x ■■ 1. With Resistor ■■ 2. Gate Direct

• P1x ■■ 1. With Resistor ■■ 2. Gate Direct

• P20 ■■ 1. With Resistor ■■ 2. Gate Direct

• P21 ■■ 1. With Resistor ■■ 2. Gate Direct

• P22 ■■ 1. With Resistor ■■ 2. Gate Direct

• P23 ■■ 1. With Resistor ■■ 2. Gate Direct

• P3x ■■ 1. With Resistor ■■ 2. Gate Direct

CHAPTER 1: OUTLINE

7. DP PORT OUTPUT SPECIFICATION

■■ 1. Complementary ■■ 2. Nch-OpenDrain

8. SVD EXTERNAL VOLTAGE DETECTION

■■ 1. Not Use

■■ 2. Use

9. LCD DRIVER SPECIFICATION

■■ 1. 40 seg ∗ 17 com

■■ 2. 48 seg ∗ 8 com

10. FSK INTERNAL FEEDBACK RESISTOR

■■ 1. Use

■■ 2. Not Use

S1C63558 TECHNICAL MANUAL EPSON 7

Page 18

CHAPTER 2: POWER SUPPLY AND INITIAL RESET

CHAPTER

2P

OWER SUPPLY AND INITIAL

R

ESET

2.1 P ower Supply

The S1C63558 operating power voltage is as follows:

Supply voltage V

The S1C63558 operates by applying a single power supply within the above range between V

The S1C63558 itself generates the voltage necessary for all the internal circuits by the built-in power

supply circuits shown in Table 2.1.1.

Note: • Do not drive external loads with the output voltage from the internal power supply circuits.

• See Chapter 7, "Electrical Characteristics", for voltage values and drive capability.

DD = 2.2 V to 5.5 V

Oscillation and internal circuits

LCD driver

FSK demodulator

External

power

supply

+

-

Circuit

AVDD

VC23

AVSS

Table 2.1.1 Power supply circuits

Power supply circuit

Oscillation system voltage regulator

LCD system voltage circuit

Analog system power supply

VDD

V

VC1

VC4

VC5

CA

CB

CC

VSS

D1

Oscillation system

voltage regulator

LCD system

voltage circuit

VD1

VC1 ~ VC5

Output voltage

AVDD, AV

Internal

circuits

Oscillation

circuit

LCD driver

V

D1

VC1–V

DD and VSS.

C5

DD

OSC1~4

COM0~16

SEG0~39

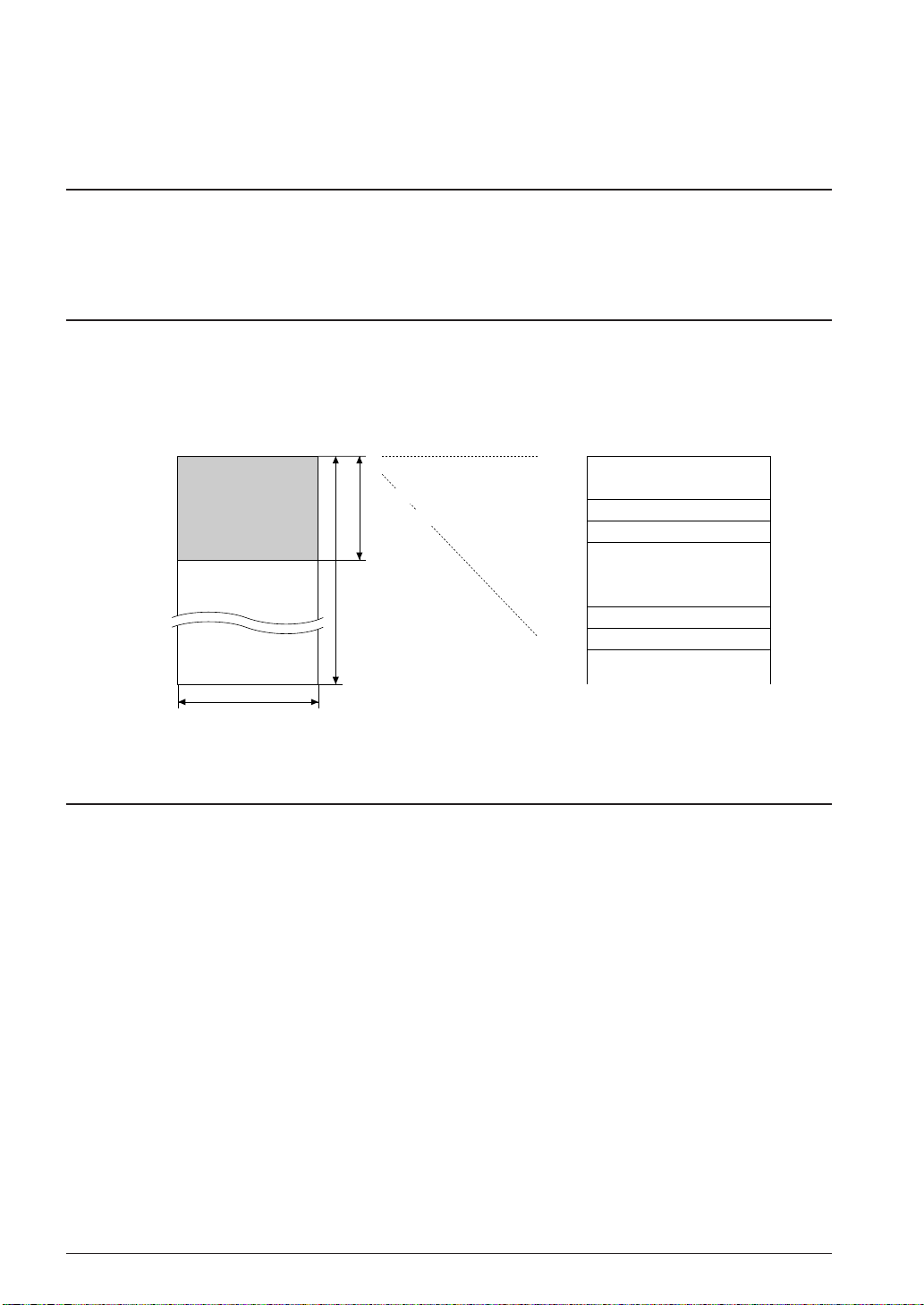

Fig. 2.1.1 Configuration of power supply

2.1.1 V oltage <VD1> for oscillation circuit and internal circuits

VD1 is a voltage for the oscillation circuit and the internal logic circuits, and is generated by the oscillation

system voltage regulator for stabilizing the oscillation. The V

D1 voltage is fixed at 2.1 V, so it is not

necessary to control by software.

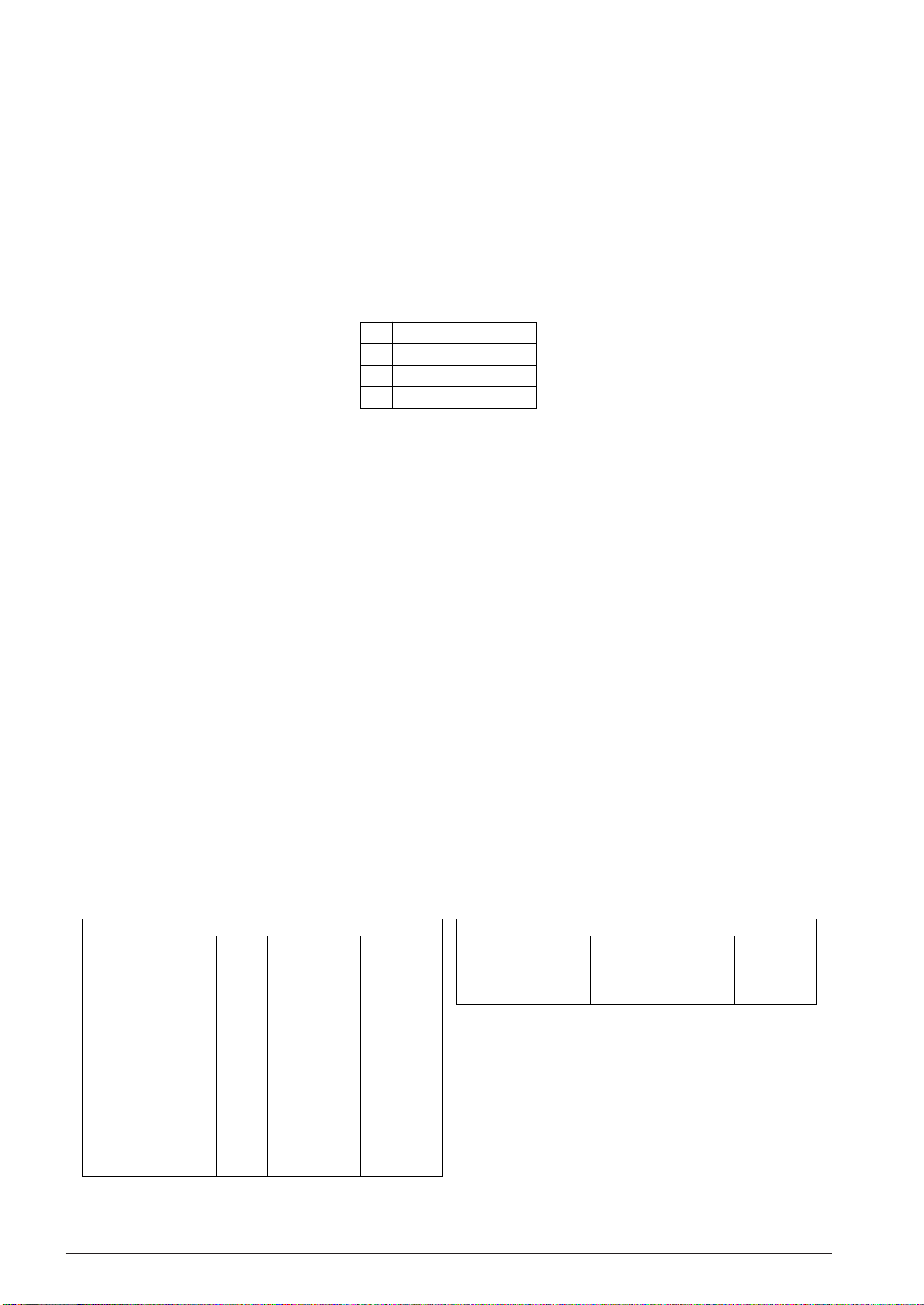

2.1.2 V oltage <VC1–VC5> for LCD driving

VC1, VC23, VC4 and VC5 are the LCD (1/4 bias) drive voltages generated by the LCD system voltage

circuit. These four output voltages can only be supplied to the externally expanded LCD driver.

The LCD system voltage circuit generates V

other voltages by boosting or reducing the voltage of V

voltage values and boost/reduce status.

Table 2.1.2.1 LCD drive voltage when generated internally

LCD drive voltage

V

C1

V

C23

V

C4

V

C5

Boost/reduce status

VC2 × 0.5

V

C2

(standard)

C2

V

C2

V

Refer to Section 4.7, "LCD Driver", for control of the LCD drive voltage.

8 EPSON S1C63558 TECHNICAL MANUAL

C23 with the voltage regulator built-in, and generates three

C23. Table 2.1.2.1 shows the VC1, VC23, VC4 and VC5

Voltage value [V]

× 1.5

× 2

1.13

2.25

3.38

4.50

Note: The LCD drive voltage can

be adjusted by the software

(see Section 4.7.5). Values

in the above table are

typical values.

Page 19

CHAPTER 2: POWER SUPPLY AND INITIAL RESET

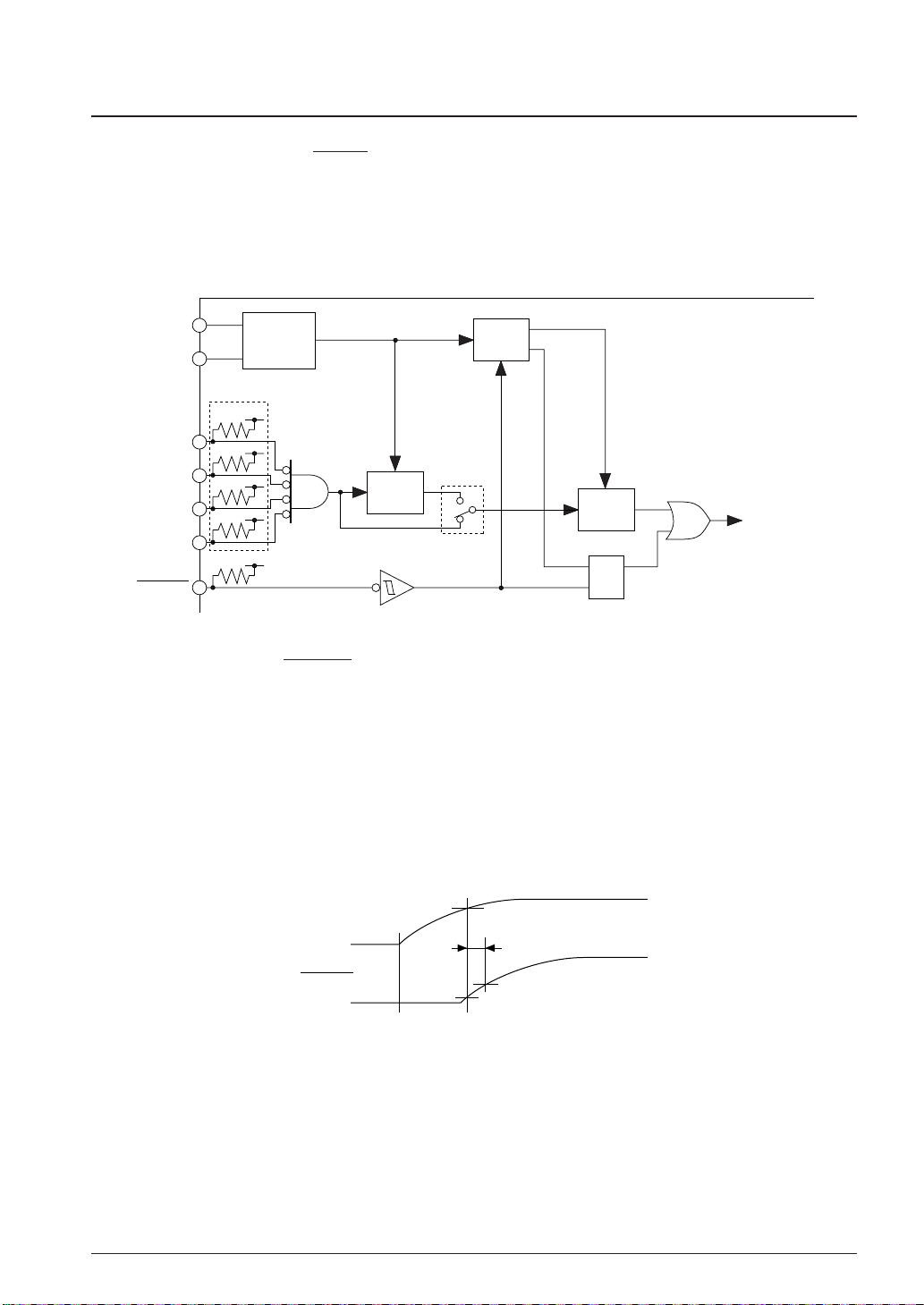

2.2 Initial Reset

To initialize the S1C63558 circuits, initial reset must be executed. There are two ways of doing this.

(1) External initial reset by the RESET terminal

(2) External initial reset by simultaneous low input to terminals K00–K03 (mask option setting)

The circuits are initialized by either (1) or (2). When the power is turned on, be sure to initialize using the

reset function. It is not guaranteed that the circuits are initialized by only turning the power on.

Figure 2.2.1 shows the configuration of the initial reset circuit.

OSC1

OSC2

oscillation

Mask option

V

DD

OSC1

circuit

Divider

1 Hz

2 Hz

K00

K01

K02

K03

RESET

authorize

V

DD

Time

circuit

Mask option

Noise

reject

circuit

RQ

S

Internal

initial

reset

Fig. 2.2.1 Configuration of initial reset circuit

2.2.1 Reset terminal (RESET)

Initial reset can be executed externally by setting the reset terminal to a low level (VSS). After that the

initial reset is released by setting the reset terminal to a high level (V

The reset input signal is maintained by the RS latch and becomes the internal initial reset signal. The RS

latch is designed to be released by a 2 Hz signal (high) that is divided by the OSC1 clock. Therefore in

normal operation, a maximum of 250 msec (when f

OSC1 = 32.768 kHz) is needed until the internal initial

reset is released after the reset terminal goes to high level. Be sure to maintain a reset input of 0.1 msec or

more.

However, when turning the power on, the reset terminal should be set at a low level as in the timing

shown in Figure 2.2.1.1.

DD) and the CPU starts operating.

2.2 V

V

DD

2.0 msec or more

RESET

Power on

0.5•V

DD

0.1•VDD or less (low level)

Fig. 2.2.1.1 Initial reset at power on

The reset terminal should be set to 0.1•V

more. After that, a level of 0.5•V

S1C63558 TECHNICAL MANUAL EPSON 9

DD or less should be maintained more than 2.0 msec.

DD or less (low level) until the supply voltage becomes 2.2 V or

Page 20

CHAPTER 2: POWER SUPPLY AND INITIAL RESET

2.2.2 Simultaneous low input to terminals K00–K03

Another way of executing initial reset externally is to input a low signal simultaneously to the input ports

(K00–K03) selected with the mask option.

Since this initial reset passes through the noise reject circuit, maintain the specified input port terminals at

low level for at least 1.5 msec (when the oscillation frequency f

tion. The noise reject circuit does not operate immediately after turning the power on until the oscillation

circuit starts oscillating. Therefore, maintain the specified input port terminals at low level for at least 1.5

msec (when the oscillation frequency f

OSC1 is 32.768 kHz) after oscillation starts.

Table 2.2.2.1 shows the combinations of input ports (K00–K03) that can be selected with the mask option.

Table 2.2.2.1 Combinations of input ports

Not use

1

K00∗K01∗K02∗K03

2

K00∗K01∗K02

3

K00∗K01

4

When, for instance, mask option 2 (K00∗K01∗K02∗K03) is selected, initial reset is executed when the

signals input to the four ports K00–K03 are all low at the same time. When 3 or 4 is selected, the initial

reset is done when a key entry including a combination of selected input ports is made.

Further, the time authorize circuit can be selected with the mask option. The time authorize circuit checks

the input time of the simultaneous low input and performs initial reset if that time is the defined time (1

to 2 sec) or more.

If using this function, make sure that the specified ports do not go low at the same time during ordinary

operation.

OSC1 is 32.768 kHz) during normal opera-

2.2.3 Internal register at initial resetting

Initial reset initializes the CPU as shown in Table 2.2.3.1.

The registers and flags which are not initialized by initial reset should be initialized in the program if

necessary.

In particular, the stack pointers SP1 and SP2 must be set as a pair because all the interrupts including

NMI are masked after initial reset until both the SP1 and SP2 stack pointers are set with software.

When data is written to the EXT register, the E flag is set and the following instruction will be executed in

the extended addressing mode. If an instruction which does not permit extended operation is used as the

following instruction, the operation is not guaranteed. Therefore, do not write data to the EXT register for

initialization only.

Refer to the "S1C63000 Core CPU Manual" for extended addressing and usable instructions.

Table 2.2.3.1 Initial values

Name

Data register A

Data register B

Extension register EXT

Index register X

Index register Y

Program counter

Stack pointer SP1

Stack pointer SP2

Zero flag

Carry flag

Interrupt flag

Extension flag

Queue register

CPU core

Symbol

A

B

EXT

X

Y

PC

SP1

SP2

Z

C

I

E

Q

Number of bits

4

4

8

16

16

16

8

8

1

1

1

1

16

Setting value

Undefined

Undefined

Undefined

Undefined

Undefined

0110H

Undefined

Undefined

Undefined

Undefined

0

0

Undefined

Name

RAM

Display memory

Other pheripheral circuits

∗ See Section 4.1, "Memory Map".

Peripheral circuits

Number of bits

4

4

–

Setting value

Undefined

Undefined

∗

10 EPSON S1C63558 TECHNICAL MANUAL

Page 21

CHAPTER 2: POWER SUPPLY AND INITIAL RESET

2.2.4 Terminal settings at initial resetting

The output port (R) terminals and I/O port (P) terminals are shared with special output terminals and

input/output terminals of the serial interface. These functions are selected by the software. At initial

reset, these terminals are set to the general purpose output port terminals and I/O port terminals. Set

them according to the system in the initial routine. In addition, take care of the initial status of output

terminals when designing a system.

Table 2.2.4.1 shows the list of the shared terminal settings.

Table 2.2.4.1(a) List of shared terminal settings (Rxx)

Terminal

name

R00

R01

R02

R03

R10

R11

R12

R13

R20–R23

at initial reset

R00 (HIGH output)

R01 (HIGH output)

R02 (HIGH output)

R03 (HIGH output)

R10 (HIGH output)

R11 (HIGH output)

R12 (HIGH output)

R13 (HIGH output)

R20–R23 (HIGH output)

FOUT

FOUT

TOUT

TOUT

Table 2.2.4.1(b) List of shared terminal settings (Pxx)

Terminal

name

P00–P03

P10

P11

P12

P13

P20

P21

P22

P23

P30

P31

P32

P33

∗1 When "with pull-up" is selected by mask option (high impedance when "gate direct" is selected)

∗2 The P10–P13 I/O terminals are used for serial I/F (1) and the P30–P33 I/O terminals are for serial I/F (2).

at initial reset

P00–P03 (Input & Pull-up *1)

P10 (Input & Pull-up *1)

P11 (Input & Pull-up *1)

P12 (Input & Pull-up *1)

P13 (Input & Pull-up *1)

P20 (Input & Pull-up *1)

P21 (Input & Pull-up *1)

P22 (Input & Pull-up *1)

P23 (Input & Pull-up *1)

P30 (Input & Pull-up *1)

P31 (Input & Pull-up *1)

P32 (Input & Pull-up *1)

P33 (Input & Pull-up *1)

Special output Serial I/F *2 Terminal status

CL

FRFRAsync.

CL

For setting procedure of the functions, see explanations for each of the peripheral circuits.

Special outputTerminal status

BZBZXBZ

XBZ

SIN(I)

SOUT(O)

SIN(I)

SOUT(O)

HDO

HDO

SIN(I)

SIN(I)

XRMUTE

XRMUTE

HFO

HFO

Clk-sync. Master

SOUT(O)

SCLK(O)

SOUT(O)

SCLK(O)

XTMUTE

XTMUTE

Clk-sync. Slave

SIN(I)

SOUT(O)

SCLK(I)

SRDY(O)

SIN(I)

SOUT(O)

SCLK(I)

SRDY(O)

2.3 Test Terminal (TEST)

This is the terminal used for the factory inspection of the IC. During normal operation, connect the TEST

terminal to V

S1C63558 TECHNICAL MANUAL EPSON 11

DD.

Page 22

CHAPTER 3: CPU, ROM, RAM

CHAPTER 3 CPU, R OM, RAM

3.1 CPU

The S1C63558 has a 4-bit core CPU S1C63000 built-in as its CPU part.

Refer to the "S1C63000 Core CPU Manual" for the S1C63000.

Note:

The SLP instruction cannot be used because the SLEEP operation is not assumed in the S1C63558.

3.2 Code ROM

The built-in code ROM is a mask ROM for loading programs, and has a capacity of 8,192 steps × 13 bits.

The core CPU can linearly access the program space up to step FFFFH from step 0000H, however, the

program area of the S1C63558 is step 0000H to step 1FFFH. The program start address after initial reset is

assigned to step 0110H. The non-maskable interrupt (NMI) vector and hardware interrupt vectors are

allocated to step 0100H and steps 0104H–010EH, respectively.

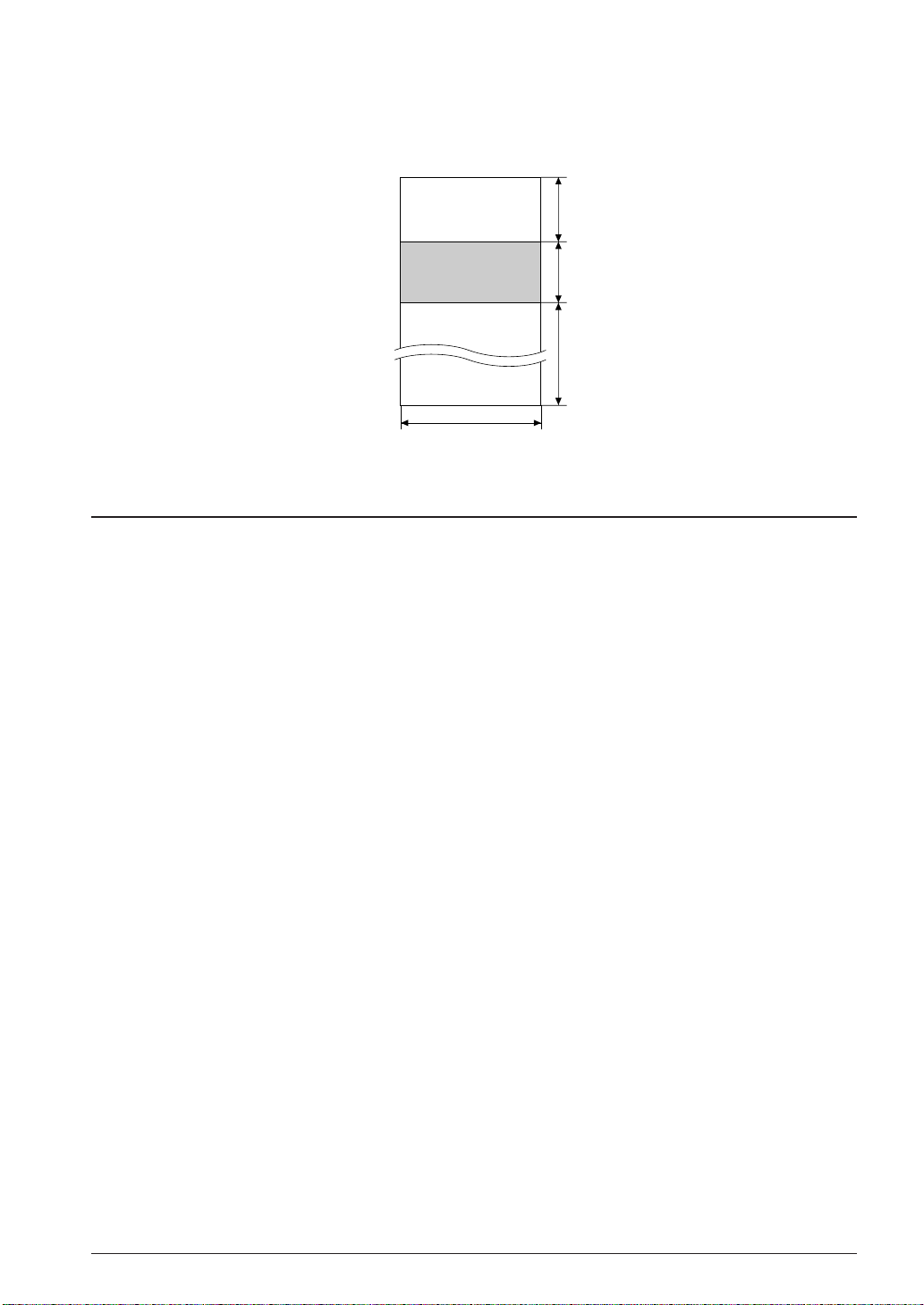

0000H

1FFFH

2000H

FFFFH

ROM

Unused area

13 bits

S1C63558

program area

S1C63000 core CPU

program space

0000H

0100H

0104H

010EH

0110H

Program area

NMI vector

Hardware

interrupt vectors

Program start address

Program area

Fig. 3.2.1 Configuration of code ROM

3.3 RAM

The RAM is a data memory for storing various kinds of data, and has a capacity of 5,120 words × 4 bits.

The RAM area is assigned to addresses 0000H to 13FFH on the data memory map. Addresses 0100H to

01FFH are 4-bit/16-bit data accessible areas and in other areas it is only possible to access 4-bit data.

When programming, keep the following points in mind.

(1) Part of the RAM area is used as a stack area for subroutine call and register evacuation, so pay

attention not to overlap the data area and stack area.

(2) The S1C63000 core CPU handles the stack using the stack pointer for 4-bit data (SP2) and the stack

pointer for 16-bit data (SP1).

16-bit data are accessed in stack handling by SP1, therefore, this stack area should be allocated to the

area where 4-bit/16-bit access is possible (0100H to 01FFH). The stack pointers SP1 and SP2 change

cyclically within their respective range: the range of SP1 is 0000H to 03FFH and the range of SP2 is

0000H to 00FFH. Therefore, pay attention to the SP1 value because it may be set to 0200H or more

exceeding the 4-bit/16-bit accessible range in the S1C63558 or it may be set to 00FFH or less. Memory

accesses except for stack operations by SP1 are 4-bit data access.

After initial reset, all the interrupts including NMI are masked until both the stack pointers SP1 and

SP2 are set by software. Further, if either SP1 or SP2 is re-set when both are set already, the interrupts

including NMI are masked again until the other is re-set. Therefore, the settings of SP1 and SP2 must

be done as a pair.

12 EPSON S1C63558 TECHNICAL MANUAL

Page 23

CHAPTER 3: CPU, ROM, RAM

(3) Subroutine calls use 4 words (for PC evacuation) in the stack area for 16-bit data (SP1). Interrupts use

4 words (for PC evacuation) in the stack area for 16-bit data (SP1) and 1 word (for F register evacuation) in the stack area for 4-bit data.

0000H

00FFH

0100H

01FFH

0200H

13FFH

4 bits

4-bit access area

(SP2 stack area)

4/16-bit access area

(SP1 stack area)

4-bit access area

(Data area)

Fig. 3.3.1 Configuration of data RAM

3.4 Data ROM

The data ROM is a mask ROM for loading various static data such as a character generator, and has a

capacity of 2,048 words × 4 bits. The data ROM is assigned to addresses 8000H to 87FFH on the data

memory map, and the data can be read using the same data memory access instructions as the RAM.

S1C63558 TECHNICAL MANUAL EPSON 13

Page 24

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Memory Map)

CHAPTER 4

The peripheral circuits of S1C63558 (timer, I/O, etc.) are interfaced with the CPU in the memory

mapped I/O method. Thus, all the peripheral circuits can be controlled by accessing the I/O memory on

the memory map using the memory operation instructions. The following sections explain the detailed

operation of each peripheral circuit.

P

ERIPHERAL

C

IRCUITS AND

O

PERA TION

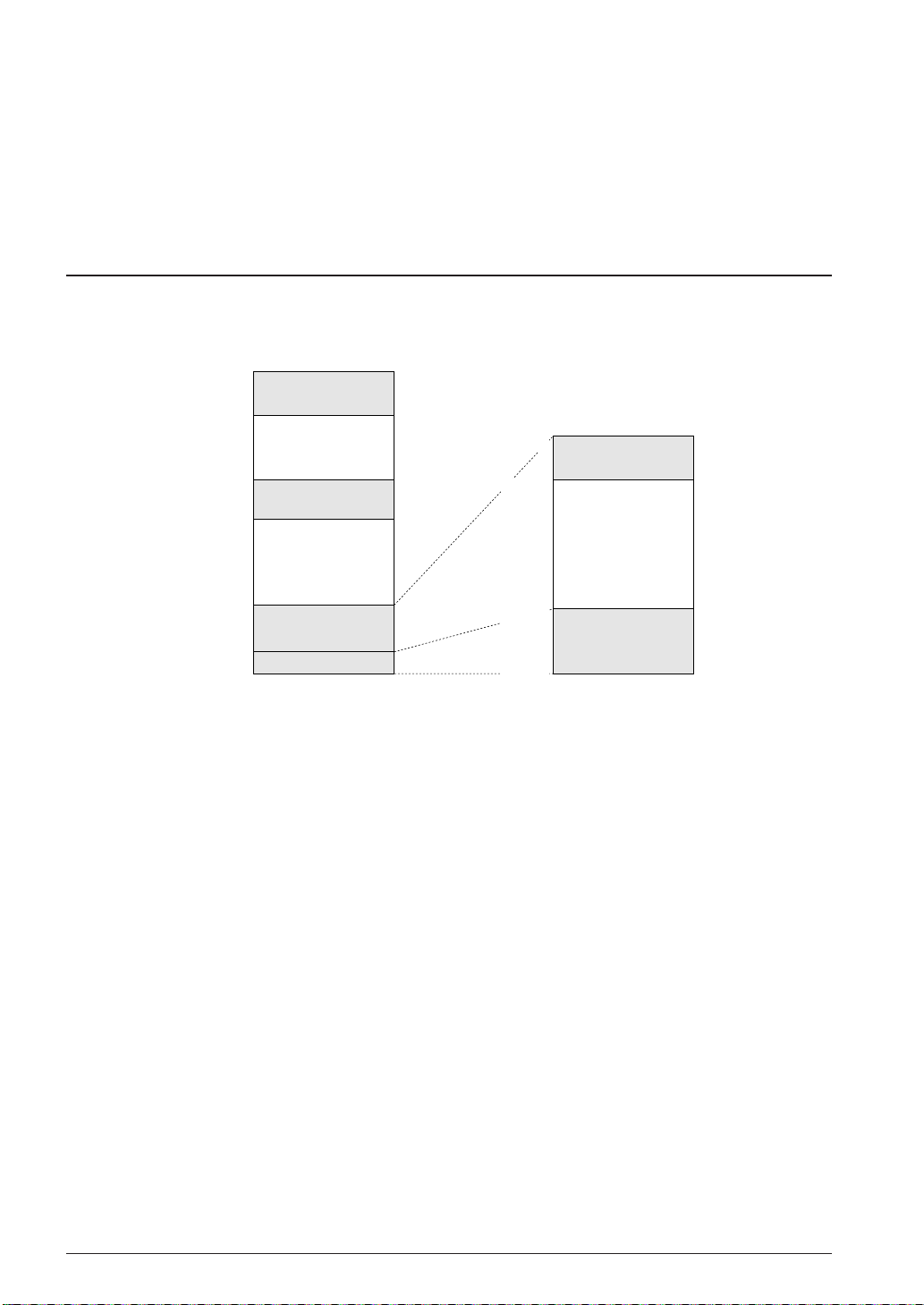

4.1 Memory Map

The S1C63558 data memory consists of 5,120-word RAM, 2,048-word data ROM, 816-bit display memory

and 97-word peripheral I/O memory. Figure 4.1.1 shows the overall memory map of the S1C63558, and

Tables 4.1.1(a)–(h) the peripheral circuits' (I/O space) memory maps.

0000H

RAM area

1400H

F000H

Display memory area

F25EH

Unused area

FF00H

Peripheral I/O area

FFFFH

8000H

8800H

F000H

FF00H

FFFFH

Unused area

Data ROM area

Unused area

I/O memory area

Fig. 4.1.1 Memory map

Note: Memory is not implemented in unused areas within the memory map. Further, some non-imple-

mentation areas and unused (access prohibition) areas exist in the display memory area and the

peripheral I/O area. If the program that accesses these areas is generated, its operation cannot be

guaranteed. Refer to Section 4.7.5, "Display memory", for the display memory, and the I/O

memory maps shown in Tables 4.1.1 (a)–(h) for the peripheral I/O area.

14 EPSON S1C63558 TECHNICAL MANUAL

Page 25

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Memory Map)

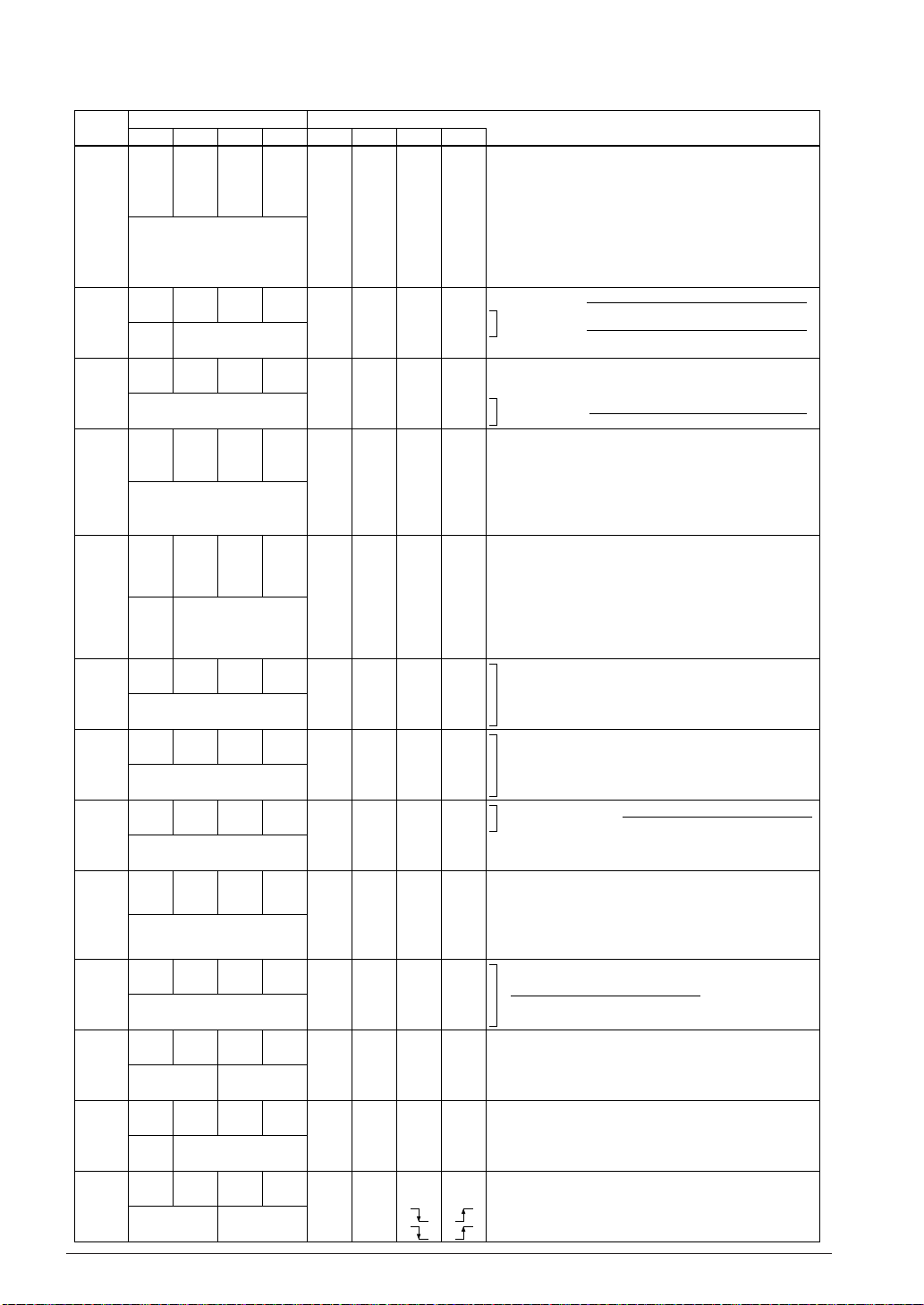

Table 4.1.1 (a) I/O memory map (FF00H–FF18H)

Address Comment

CLKCHG OSCC 0 Dummy

FF00H

SVDS3 SVDS2 SVDS1 SVDS0

FF04H

FF05H

FOUTE 0 FOFQ1 FOFQ0

FF06H

FF07H

FF10H

PTS3 PTS2 PTS1 PTS0

FF11H

FTS3 FTS2 FTS1 FTS0

FF12H

CHFO CHDO CRMO CTMO

FF13H

FF14H

IDP3 IDP2 IDP1 IDP0

FF15H

CTO 0 SINR SINC

FF16H

R/W R R/W

TCD3 TCD2 TCD1 TCD0

FF17H

HSON 0 CRMUT CTMUT

FF18H

R/W R R/W

Register

D3 D2

D1 D0 Name Init

R R/WR/W

R/W

00SVDDT SVDON

R R/W

R/W R R/W

00WDEN WDRST

R/W WR

TPS 0 MB DRS

R/W R R/W

R/W

R/W

R/W

HF HOLD PAUSE FLASH

R/W W

R/W

R/W

CLKCHG

OSCC

∗

3

0

Dummy

SVDS3

SVDS2

SVDS1

SVDS0

∗

3

0

∗

3

0

SVDDT

SVDON

FOUTE

∗

3

0

FOFQ1

FOFQ0

∗

3

0

∗

3

0

WDEN

∗

WDRST

TPS

∗

3

0

MB

DRS

PTS3

PTS2

PTS1

PTS0

FTS3

FTS2

FTS1

FTS0

CHFO

CHDO

CRMO

CTMO

HF

HOLD

∗

PAUSE

∗

FLASH

IDP3

IDP2

IDP1

IDP0

CTO

∗

3

0

SINR

SINC

TCD3

TCD2

TCD1

TCD0

HSON

∗

3

0

CRMUT

CTMUT

∗1

10

0

OSC3OnOSC1

0

∗

2

–

0

0

0

0

0

∗

2

–

∗

2

–

00LowOnNormal

0

FOUT DC

∗

2

–

0

0

∗

2

–

∗

2

–

1

Reset

0

–

0

0

∗

2

33.3:66.6

Enable

Reset

Pulse

20pps

3

0

1

0

0

0

1

1

0

0

HFO

0

HDO

XRMUTE

0

XTMUTE

0

0

Yes

0

3

3

On

0

Yes

0

Yes

1

0

0

0

0

On

∗

2

–

1

Enable

1

Enable

0

0

0

0

0

Off

∗

2

–

1

Mute

1

Mute

CPU clock switch

Off

OSC3 oscillation On/Off

Unused

General-purpose register

SVD criteria voltage setting

[SVDS3–0]

Voltage(V)

[SVDS3–0]

Voltage(V)

0

2.20/1.05

8

2.60

2.20

2.70

1

2

3

2.20

2.20

9

10

2.80

11

2.90

2.20

3.00

Unused

Unused

SVD evaluation data

Off

SVD circuit On/Off

R03 output selection (R03 should be fixed at "1".)

Unused

FOUT

frequency

selection

[FOFQ1, 0]

Frequency

f

OSC1

0

/641f

Unused

Unused

Disable

Watchdog timer enable

Invalid

Watchdog timer reset (writing)

Tone / pulse mode selection

Tone

Unused

40:60

Make : Break ratio selection

10pps

Dialing pulse rate selection

Pause time selection (initial value: 4 sec)

[PTS3–0]

Time(sec)

[PTS3–0]

Time(sec)

Flash time selection (initial value: 563 ms)

[FTS3–0]

Time(ms)

[FTS3–0]

Time(ms)

DC

R13 output selection (R13 should be fixed at "1".)

DC

R12 output selection (R12 should be fixed at "1".)

DC

R11 output selection (R11 should be fixed at "1".)

DC

R10 output selection (R10 should be fixed at "1".)

Hand free

No

Hold-line function

Off

Pause function

No

Flash function

No

Inter-digit pause selection for dial pulse (initial value: 750 ms)

[IDP3–0]

Time(ms)

[IDP3–0]

Time(ms)

Continuous tone output On/Off

Off

750

750

0

1

2

3

×

1

94

844

94

844

2

9

10

9

10

1

2

188

9

10

938

1

2

188

9

10

938

8

8

0

×

8

0

×

8

3

11

11

3

281

11

1031

3

281

11

1031

4

4

12

12

4

375

12

1125

4

375

12

1125

Unused

Disable

DTMF row frequency output enable

Disable

DTMF column frequency output enable

Telephone code for dialing

1

2

3

[TCD3–0]

DTMF

DP

[TCD3–0]

DTMF

DP

Hook switch On/Off

On

0

(R1C4)

×

8

(R3C2)

8

(R1C1)

1

9

(R3C3)

9

(R1C2)

2

10

(R4C2)

10

(R1C3)

3

11

(R4C3)

11

4

(R2C1)

4

12

(R4C1)

12

Unused

0

Receive mute control

0

Transmit mute control

Remarks

∗1 Initial value at initial reset ∗3 Constantly "0" when being read

∗2 Not set in the circuit ∗4 Depends on the input status of the RDIN terminal

12

4

OSC1

1219

1219

(R2C2)

(R2C4)

2.30

3.10

13

13

469

13

469

13

13

13

5

13

/82f

5

5

5

5

5

5

2.40

14

3.20

OSC1

6

6

14

14

6

563

14

1313

6

563

14

1313

6

(R2C3)

6

14

(R4C4)

14

6

2.50

15

3.30

3

OSC3

f

7

7

15

15

7

656

15

1406

7

656

15

1406

7

(R3C1)

7

15

(R3C4)

15

7

S1C63558 TECHNICAL MANUAL EPSON 15

Page 26

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Memory Map)

Table 4.1.1 (b) I/O memory map (FF20H–FF42H)

Address Comment

SIK03 SIK02 SIK01 SIK00

FF20H

FF21H

KCP03 KCP02 KCP01 KCP00

FF22H

SIK13 SIK12 SIK11 SIK10

FF24H

(EVIN)

FF25H

KCP13 KCP12 KCP11 KCP10

FF26H

R03HIZ R02HIZ R01HIZ R00HIZ

FF30H

(FOUT)

FF31H

R13HIZ R12HIZ R11HIZ R10HIZ

FF32H

(HFO)

FF33H

R23HIZ R22HIZ R21HIZ R20HIZ

FF34H

FF35H

IOC03 IOC02 IOC01 IOC00

FF40H

PUL03 PUL02 PUL01 PUL00

FF41H

FF42H

Register

D3 D2

D1 D0 Name Init

R/W

K03 K02 K01 K00

R

R/W

R/W

K13

K12 K11 K10

R

R/W

R/W

R03

R02

R01

(BZ)

R00

(XBZ)

(TOUT)

R/W

R/W

R13

R12

R11

(XRMUTE)

(XTMUTE)

R10

(HDO)

R/W

R/W

R23 R22 R21 R20

R/W

R/W

R/W

P03 P02 P01 P00

R/W

SIK03

SIK02

SIK01

SIK00

K03

K02

K01

K00

KCP03

KCP02

KCP01

KCP00

SIK13

SIK12

SIK11

SIK10

K13

K12

K11

K10

KCP13

KCP12

KCP11

KCP10

R03HIZ

R02HIZ

R01HIZ

R00HIZ

R03

R02

R01

R00

R13HIZ

R12HIZ

R11HIZ

R10HIZ

R13

R12

R11

R10

R23HIZ

R22HIZ

R21HIZ

R20HIZ

R23

R22

R21

R20

IOC03

IOC02

IOC01

IOC00

PUL03

PUL02

PUL01

PUL00

P03

P02

P01

P00

0

0

0

0

–

–

–

–

1

1

1

1

0

0

0

0

–

–

–

–

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

–

–

–

–

∗1

10

Enable

Enable

Enable

Enable

∗

2

High

∗

2

High

∗

2

High

∗

2

High

Enable

Enable

Enable

Enable

∗

2

High

∗

2

High

∗

2

High

∗

2

High

Hi-Z

Hi-Z

Hi-Z

Hi-Z

High

High

High

High

Hi-Z

Hi-Z

Hi-Z

Hi-Z

High

High

High

High

Hi-Z

Hi-Z

Hi-Z

Hi-Z

High

High

High

High

Output

Output

Output

Output

On

On

On

On

∗

2

High

∗

2

High

∗

2

High

∗

2

High

Disable

Disable

K00–K03 interrupt selection register

Disable

Disable

Low

Low

K00–K03 input port data

Low

Low

K00–K03 input comparison register

Disable

Disable

K10–K13 interrupt selection register

Disable

Disable

Low

Low

K10–K13 input port data

Low

Low

K10–K13 input comparison register

R03 (FOUTE=0)/FOUT (FOUTE=1) Hi-z control

Output

R02 (PTOUT=0)/TOUT (PTOUT=1) Hi-z control

Output

R01 (BZOUT=0)/BZ (BZOUT=1) Hi-z control

Output

R00 (XBZOUT=0)/XBZ (XBZOUT=1) Hi-z control

Output

R03

Low

Low

Low

Low

Output

Output

Output

Output

Low

Low

Low

Low

output port data (

R02

output port data (

R01

output port data (

R00

output port data (

R13 (CHFO=0)/HFO (CHFO=1) Hi-z control

R12 (CHDO=0)/HDO (CHDO=1) Hi-z control

R11 (CRMO=0)/XRMUTE (CRMO=1) Hi-z control

R10 (CTMO=0)/XTMUTE (CTMO=1) Hi-z control

R13 output port data (CHFO=0) Fix at "1" when HFO is used.

R12 output port data (CHDO=0) Fix at "1" when HDO is used.

R11 output port data (CRMO=0) Fix at "1" when XRMUTE is used.

R10 output port data (CTMO=0) Fix at "1" when XTMUTE is used.

FOUTE=0

PTOUT=0

BZOUT=0

XBZOUT=0

Output

Output

R20–R23 Hi-z control

Output

Output

Low

Low

R20–R23 output port data

Low

Low

Input

Input

P00–P03 I/O control register

Input

Input

Off

Off

P00–P03 pull-up control register

Off

Off

Low

Low

P00–P03 I/O port data

Low

Low

) Fix at "1" when

) Fix at "1" when

) Fix at "1" when

) Fix at "1" when

FOUT

TOUT

BZ

is used.

XBZ

is used.

is used.

is used.

16 EPSON S1C63558 TECHNICAL MANUAL

Page 27

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Memory Map)

Table 4.1.1 (c) I/O memory map (FF44H–FF4DH)

Address Comment

IOC13 IOC12 IOC11 IOC10

FF44H

PUL13 PUL12 PUL11 PUL10

FF45H

P13

(XSRDY)

FF46H

IOC23 IOC22 IOC21 IOC20

FF48H

PUL23 PUL22 PUL21 PUL20

FF49H

P23

(FR)

FF4AH

IOC33 IOC32 IOC31 IOC30

FF4CH

PUL33 PUL32 PUL31 PUL30

FF4DH

D3 D2

P12

(XSCLK)

P22

(CL)

Register

D1 D0 Name Init

R/W

R/W

P11

(SOUT)

P10

(SIN)

R/W

R/W

R/W

P21 P20

R/W

R/W

R/W

IOC13

IOC12

IOC11

IOC10

PUL13

PUL12

PUL11

PUL10

P13

P12

P11

P10

IOC23

IOC22

IOC21

IOC20

PUL23

PUL22

PUL21

PUL20

P23

P22

P21

P20

IOC33

IOC32

IOC31

IOC30

PUL33

PUL32

PUL31

PUL30

–

–

–

–

–

–

–

–

∗1

0

0

0

0

1

1

1

1

∗

2

∗

2

∗

2

∗

2

0

0

0

0

1

1

1

1

∗

2

∗

2

∗

2

∗

2

0

0

0

0

1

1

1

1

10

Input

Output

Input

Output

Input

Output

Input

Output

Off

On

Off

On

Off

On

Off

On

Low

High

Low

High

Low

High

Low

High

Input

Output

Input

Output

Input

Output

Input

Output

Off

On

Off

On

Off

On

Off

On

Low

High

Low

High

Low

High

Low

High

Input

Output

Input

Output

Input

Output

Input

Output

Off

On

Off

On

Off

On

Off

On

P13 I/O control register

General-purpose register when SIF (clock sync. slave) is selected

P12 I/O control register

General-purpose register when SIF (clock sync.) is selected

P11 I/O control register (ESIF=0)

General-purpose register when SIF is selected

P10 I/O control register (ESIF=0)

General-purpose register when SIF is selected

P13 pull-up control register

General-purpose register when SIF (clock sync. slave) is selected

P12 pull-up control register

General-purpose register when SIF (clock sync. master) is selected

SCLK (I) pull-up control register

when SIF (clock sync. slave) is selected

P11 pull-up control register (ESIF=0)

General-purpose register when SIF is selected

P10 pull-up control register (ESIF=0)

SIN pull-up control register when SIF is selected

P13 I/O port data

General-purpose register when SIF (clock sync. slave) is selected

P12 I/O port data

General-purpose register when SIF (clock sync.) is selected

P11 I/O port data (ESIF=0)

General-purpose register when SIF is selected

P10 I/O port data (ESIF=0)

General-purpose register when SIF is selected

P23 I/O control register (EXLCDC=0)

General-purpose register when FR output is selected

P22 I/O control register (EXLCDC=0)

General-purpose register when CL output is selected

P21 I/O control register

P20 I/O control register

P23 pull-up control register (EXLCDC=0)

General-purpose register when FR output is selected

P22 pull-up control register (EXLCDC=0)

General-purpose register when CL output is selected

P21 pull-up control register

P20 pull-up control register

P23 I/O port data (EXLCDC=0)

General-purpose register when FR output is selected

P22 I/O port data (EXLCDC=0)

General-purpose register when CL output is selected

P21 I/O port data

P20 I/O port data

P33 I/O control register

General-purpose register when SIF (clock sync. slave) is selected

P32 I/O control register

General-purpose register when SIF (clock sync.) is selected

P31 I/O control register (ESIFS=0)

General-purpose register when SIF is selected

P30 I/O control register (ESIFS=0)

General-purpose register when SIF is selected

P33 pull-up control register

General-purpose register when SIF (clock sync. slave) is selected

P32 pull-up control register

General-purpose register when SIF (clock sync. master) is selected

SCLK (I) pull-up control register

when SIF (clock sync. slave) is selected

P31 pull-up control register (ESIFS=0)

General-purpose register when SIF is selected

P30 pull-up control register (ESIFS=0)

SIN pull-up control register when SIF is selected

S1C63558 TECHNICAL MANUAL EPSON 17

Page 28

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Memory Map)

Table 4.1.1 (d) I/O memory map (FF4EH–FF67H)

Address Comment

(XSRDYS)

FF4EH

FF58H

EPRS PMDS SCS1S SCS0S

FF59H

RXTRGS RXENS TXTRGS TXENS

FF5AH

FF5BH

TRXD3S TRXD2S TRXD1S TRXD0S

FF5CH

TRXD7S TRXD6S TRXD5S TRXD4S

FF5DH

LDUTY1 LDUTY0 Dummy LPWR

FF60H

EXLCDC ALOFF ALON LPAGE

FF61H

FF62H

FF65H

FSKON 0 RDET CDET

FF66H

FF67H

Register

D3 D2

P33

(XSCLKS)

D1 D0 Name Init

P32

P31

(SINS)

(SOUTS)

P30

R/W

SMD1S SMD0S ESIFS

0

R R/W

R/W

R/W

0 FERS PERS OERS

R R/W